(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7632142号

(P7632142)

(45)発行日 令和7年2月19日(2025.2.19)

(24)登録日 令和7年2月10日(2025.2.10)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| H 1 0 D | 84/80 (2025.01) | F I | H 0 1 L | 29/78 | 6 5 7 F |

| H 1 0 D | 30/66 (2025.01) |     | H 0 1 L | 29/78 | 6 5 7 D |

| H 1 0 D | 12/00 (2025.01) |     | H 0 1 L | 29/78 | 6 5 3 A |

| H 1 0 D | 62/10 (2025.01) |     | H 0 1 L | 29/78 | 6 5 5 F |

| H 1 0 D | 8/50 (2025.01)  |     | H 0 1 L | 29/78 | 6 5 7 G |

請求項の数 4 (全22頁) 最終頁に続く

(21)出願番号 特願2021-116409(P2021-116409)

(22)出願日 令和3年7月14日(2021.7.14)

(65)公開番号 特開2023-12751(P2023-12751A)

(43)公開日 令和5年1月26日(2023.1.26)

審査請求日 令和5年11月8日(2023.11.8)

(73)特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74)代理人 110001128

弁理士法人ゆうあい特許事務所

杉浦 寛人

愛知県刈谷市昭和町1丁目1番地 株式

会社デンソー内

(72)発明者 住友 正清

愛知県刈谷市昭和町1丁目1番地 株式

会社デンソー内

審査官 西村 治郎

最終頁に続く

(54)【発明の名称】 半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

メイン素子(Me)が形成されたメイン領域(Rm)およびセンス素子(Se)が形成されたセンス領域(Rs)を有し、前記センス素子に流れるセンス電流に基づいて前記メイン素子に流れるメイン電流が検出される半導体装置であって、

前記メイン素子および前記センス素子は、

第1導電型のドリフト層(11)と、

前記ドリフト層上に形成された第2導電型のベース層(12)と、

前記ベース層の表層部に形成され、前記ドリフト層より高不純物濃度とされた第1導電型のエミッタ領域(16)と、

前記エミッタ領域と前記ドリフト層との間に挟まれた前記ベース層の表面に配置されたゲート絶縁膜(14)と、

前記ゲート絶縁膜上に配置されたゲート電極(15)と、

前記ドリフト層を挟んで前記ベース層と反対側に形成された他面層(21)と、

前記エミッタ領域および前記ベース層と電気的に接続される第1電極(19)と、

前記他面層と電気的に接続される第2電極(22)と、を備え、

前記メイン素子の他面層は、第2導電型のコレクタ層(21a)で構成されており、

前記センス素子の他面層は、前記ドリフト層と前記ベース層との積層方向に沿って、前記コレクタ層よりも第2導電型の不純物量が少なくされた低不純物層(21b、21c)を含んで構成されており、

10

20

前記センス素子は、前記低不純物層の構成が異なる第1センス素子(Se1)および第2センス素子(Se2)を有し、

前記第1センス素子および前記第2センス素子は、前記メイン素子に対して並列に接続されている半導体装置。

【請求項2】

前記低不純物層は、前記コレクタ層よりも不純物濃度のピーク濃度が低くされた第2導電型の低不純物濃度層(21c)を含んで構成されている請求項1に記載の半導体装置。

【請求項3】

メイン素子(Me)が形成されたメイン領域(Rm)およびセンス素子(Se)が形成されたセンス領域(Rs)を有し、前記センス素子に流れるセンス電流に基づいて前記メイン素子に流れるメイン電流が検出される半導体装置であって、

前記メイン素子および前記センス素子は、

第1導電型のドリフト層(11)と、

前記ドリフト層上に形成された第2導電型のベース層(12)と、

前記ベース層の表層部に形成され、前記ドリフト層より高不純物濃度とされた第1導電型のエミッタ領域(16)と、

前記エミッタ領域と前記ドリフト層との間に挟まれた前記ベース層の表面に配置されたゲート絶縁膜(14)と、

前記ゲート絶縁膜上に配置されたゲート電極(15)と、

前記ドリフト層を挟んで前記ベース層と反対側に形成された他面層(21)と、

前記エミッタ領域および前記ベース層と電気的に接続される第1電極(19)と、

前記他面層と電気的に接続される第2電極(22)と、を備え、

前記メイン素子の他面層は、第2導電型のコレクタ層(21a)で構成されており、

前記センス素子の他面層は、前記ドリフト層と前記ベース層との積層方向に沿って、前記コレクタ層よりも第2導電型の不純物量が少なくされた低不純物層(21b、21c)を含んで構成されており、

前記低不純物層は、前記コレクタ層よりも不純物濃度のピーク濃度が低くされた第2導電型の低不純物濃度層(21c)を含んで構成されている半導体装置。

【請求項4】

前記メイン領域は、前記コレクタ層を有するIGBT素子が形成されたIGBT領域(1a)と、前記他面層としての第1導電型のカソード層(21d)を有するFWD素子が形成されたFWD領域(1b)とを有し、

前記低不純物層は、第1導電型の逆導電型層(21b)を含んで構成され、

前記逆導電型層は、前記カソード層と同じ厚さとされると共に同じ不純物濃度とされている請求項1ないし3のいずれか1つに記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、メイン素子が形成されたメイン領域およびセンス素子が形成されたセンス領域を有する半導体装置に関するものである。

【背景技術】

【0002】

従来より、メイン素子が形成されたメイン領域およびセンス素子が形成されたセンス領域を有する半導体装置が提案されている(例えば、特許文献1参照)。具体的には、この半導体装置では、メイン素子およびセンス素子として、同じIGBT(Insulated Gate Bipolar Transistorの略)素子が形成されている。また、メイン素子およびセンス素子(すなわち、メイン領域およびセンス領域)は、所定の面積比となるように形成されている。

【0003】

このような半導体装置は、センス素子に検出抵抗が直列に接続され、検出抵抗の両端電圧を検出信号としてメイン素子に流れるメイン電流が形成される。すなわち、まず、セン

10

20

30

40

50

ス素子に流れるセンス電流が検出信号に基づいて導出される。また、メイン素子に流れる電流およびセンス素子に流れる電流は、メイン素子とセンス素子の面積比に依存する。このため、メイン素子に流れるメイン電流は、センス素子に流れるセンス電流、およびメイン素子とセンス素子との面積比によって導出される。

【先行技術文献】

【特許文献】

【0004】

【文献】特開2018-101737号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、上記のような半導体装置では、検出信号に基づいて半導体装置が定常状態（すなわち、正常状態）であるか異常状態であるかの状態判定も行われる。このため、上記のような半導体装置では、定常状態での定常検出信号と、異常状態での異常検出信号との差電圧が大きくなるようにして誤判定されることを抑制できるようにすることが好ましい。

【0006】

この場合、例えば、差電圧を大きくするために飽和電流を大きくして異常検出信号が大きくなるようにする構造が考えられ、IGBT素子におけるコレクタ層の不純物濃度を高くすることが考えられる。しかしながら、このような構成では、スイッチングオフ損失が大きくなる可能性がある。

【0007】

本発明は上記点に鑑み、スイッチングオフ損失が大きくなることを抑制しつつ、定常検出信号と異常検出信号との差電圧を大きくできる半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記目的を達成するための請求項1および3では、メイン素子（Me）が形成されたメイン領域（Rm）およびセンス素子（Se）が形成されたセンス領域（Rs）を有し、センス素子に流れるセンス電流に基づいてメイン素子に流れるメイン電流が検出される半導体装置であって、メイン素子およびセンス素子は、第1導電型のドリフト層（11）と、ドリフト層上に形成された第2導電型のベース層（12）と、ベース層の表層部に形成され、ドリフト層より高不純物濃度とされた第1導電型のエミッタ領域（16）と、エミッタ領域とドリフト層との間に挟まれたベース層の表面に配置されたゲート絶縁膜（14）と、ゲート絶縁膜上に配置されたゲート電極（15）と、ドリフト層を挟んでベース層と反対側に形成された他面層（21）と、エミッタ領域およびベース層と電気的に接続される第1電極（19）と、他面層と電気的に接続される第2電極（22）と、を備え、メイン素子の他面層は、第2導電型のコレクタ層（21a）で構成されており、センス素子の他面層は、ドリフト層とベース層との積層方向に沿って、コレクタ層よりも第2導電型の不純物量が少なくされた低不純物層（21b、21c）を含んで構成されている。

そして、請求項1では、センス素子は、低不純物層の構成が異なる第1センス素子（Se1）および第2センス素子（Se2）を有し、第1センス素子および第2センス素子は、メイン素子に対して並列に接続されている。

請求項3では、低不純物層は、コレクタ層よりも不純物濃度のピーク濃度が低くされた第2導電型の低不純物濃度層（21c）を含んで構成されている。

【0009】

これによれば、センス素子は、低不純物層を含んで構成されており、他面層側からのキャリア（例えば、正孔）の注入が抑制される。このため、定常状態でセンス素子に流れるセンス電流を小さくでき、定常検出信号を小さくできる。したがって、定常検出信号と異常検出信号との差電圧を十分に大きくできる。また、この半導体装置では、コレクタ層の不純物濃度を必要以上に高くする必要がないため、スイッチングオフ損失が大きくなることも抑制できる。

10

20

30

40

50

## 【0010】

なお、各構成要素等に付された括弧付きの参照符号は、その構成要素等と後述する実施形態に記載の具体的な構成要素等との対応関係の一例を示すものである。

## 【図面の簡単な説明】

## 【0011】

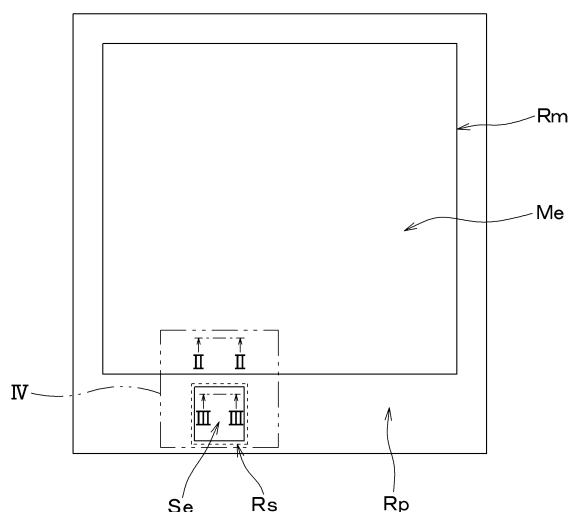

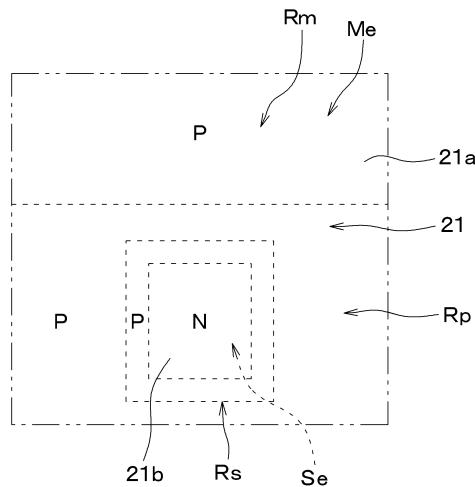

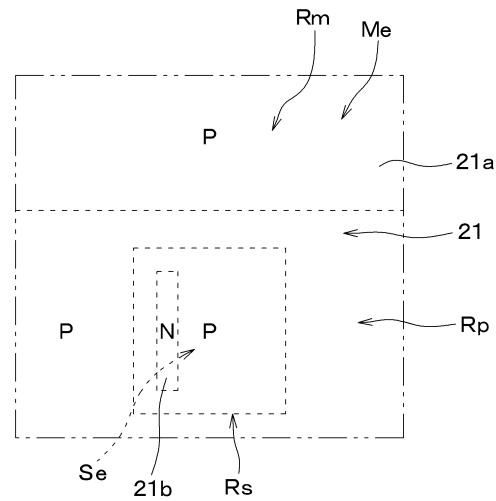

【図1】第1実施形態における半導体装置の平面図である。

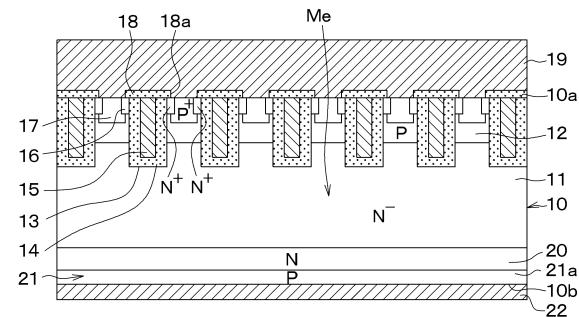

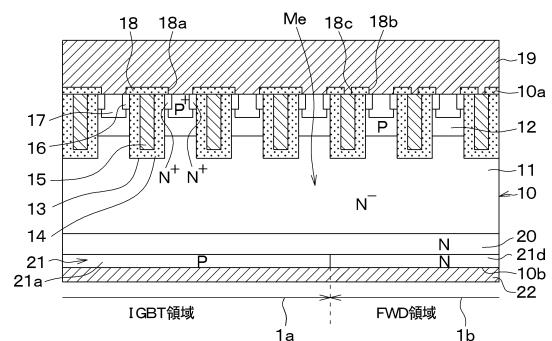

【図2】図1中のII-II線に沿った断面図である。

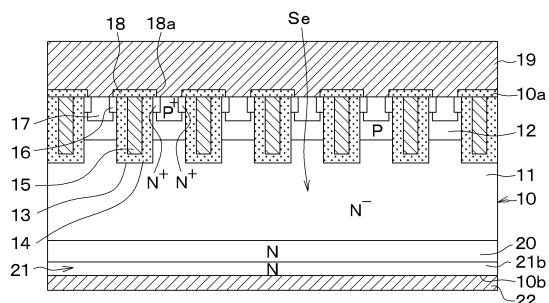

【図3】図1中のIII-III線に沿った断面図である。

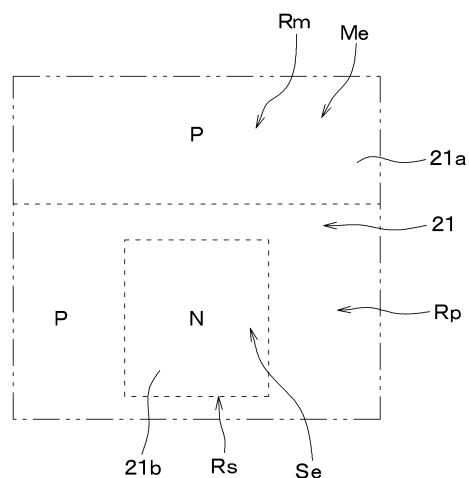

【図4】図1中の領域IVにおける半導体基板の他面側の平面図である。

【図5】センス素子に検出抵抗を接続した回路図である。

10

【図6】定常検出信号を得るために構成した回路図である。

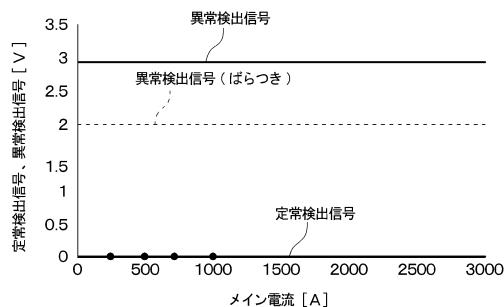

【図7】比較対象の半導体装置における定常検出信号を示す図である。

【図8】第1実施形態の半導体装置における定常検出信号を示す図である。

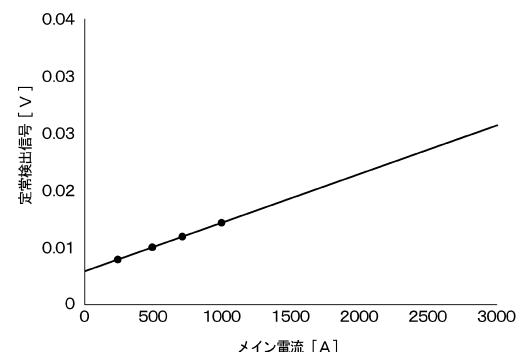

【図9】図8中の領域IXの拡大図である。

【図10】異常検出信号を得るために構成した回路図である。

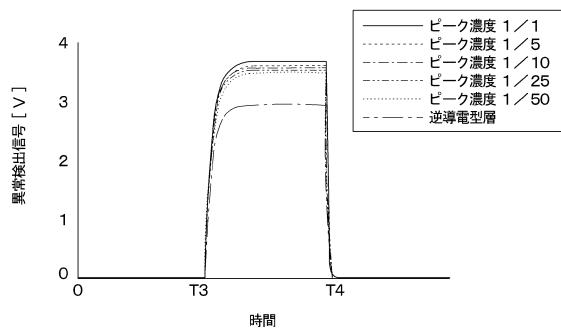

【図11】比較対象の半導体装置および第1実施形態の半導体装置における異常検出信号を示す図である。

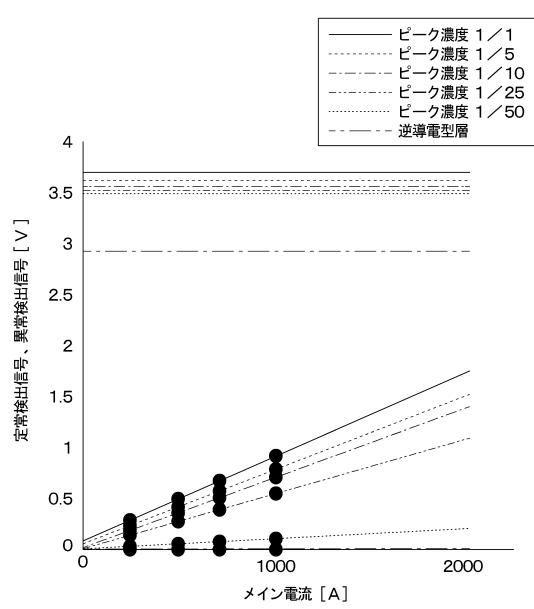

【図12】比較対象の半導体装置における定常検出信号および異常検出信号の関係を示す図である。

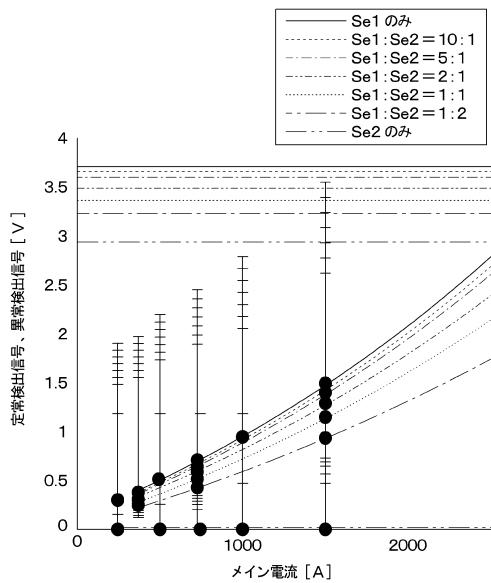

【図13】第1実施形態の半導体装置における定常検出信号および異常検出信号の関係を示す図である。

20

【図14】第1実施形態の半導体装置における定常検出信号および異常検出信号の関係を示す図である。

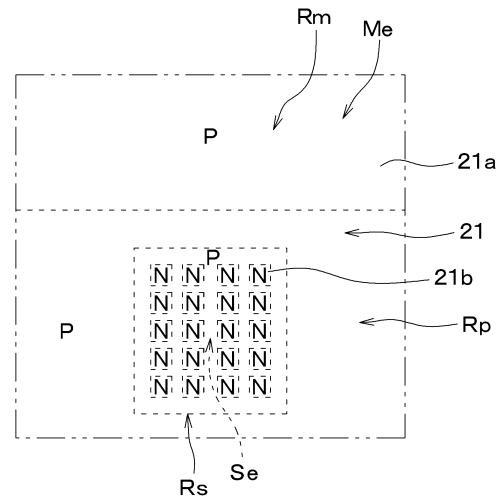

【図15A】第1実施形態の変形例における半導体基板の他面側の平面図である。

【図15B】第1実施形態の変形例における半導体基板の他面側の平面図である。

【図15C】第1実施形態の変形例における半導体基板の他面側の平面図である。

【図15D】第1実施形態の変形例における半導体基板の他面側の平面図である。

【図15E】第1実施形態の変形例における半導体基板の他面側の平面図である。

【図15F】第1実施形態の変形例における半導体基板の他面側の平面図である。

【図15G】第1実施形態の変形例における半導体基板の他面側の平面図である。

30

【図16】第2実施形態における半導体装置に検出抵抗を接続した回路図である。

【図17】第1センス素子と第2センス素子との比率と、定常検出信号との関係を示す図である。

【図18】第1センス素子と第2センス素子との比率と、異常検出信号との関係を示す図である。

【図19】定常検出信号および異常検出信号の関係を示す図である。

【図20】第3実施形態における半導体基板の他面側の平面図である。

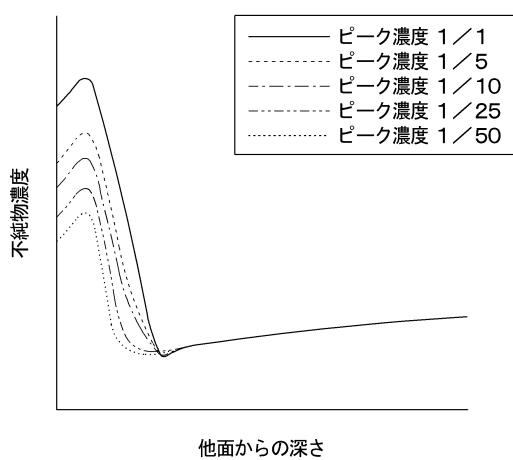

【図21】他面からの深さと、不純物濃度との関係を示す図である。

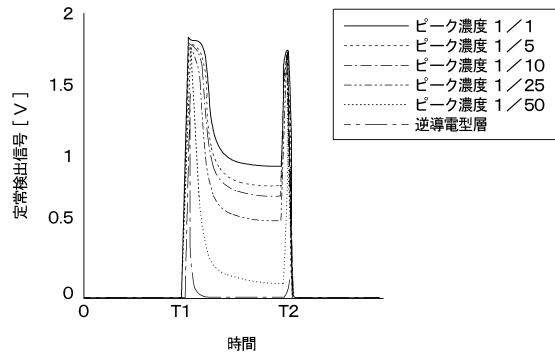

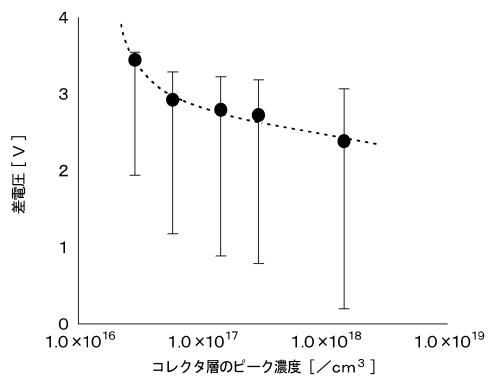

【図22】ピーク濃度と定常検出信号との関係を示す図である。

【図23】ピーク濃度と異常検出信号との関係を示す図である。

40

【図24】定常検出信号および異常検出信号の関係を示す図である。

【図25】コレクタ層のピーク濃度と、差電圧との関係を示す図である。

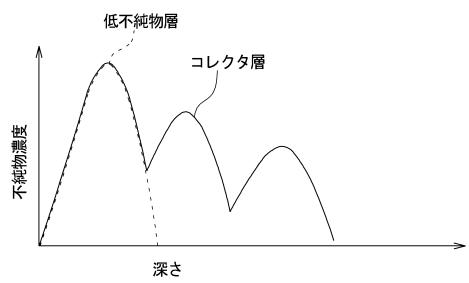

【図26】第3実施形態の変形例における不純物濃度を示す図である。

【図27】第4実施形態におけるメイン領域の断面図である。

## 【発明を実施するための形態】

## 【0012】

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、同一符号を付して説明を行う。

## 【0013】

(第1実施形態)

50

第1実施形態について、図面を参照しつつ説明する。なお、本実施形態の半導体装置は、例えば、大電流が流れる電気自動車に搭載されて用いられるに好適である。

【0014】

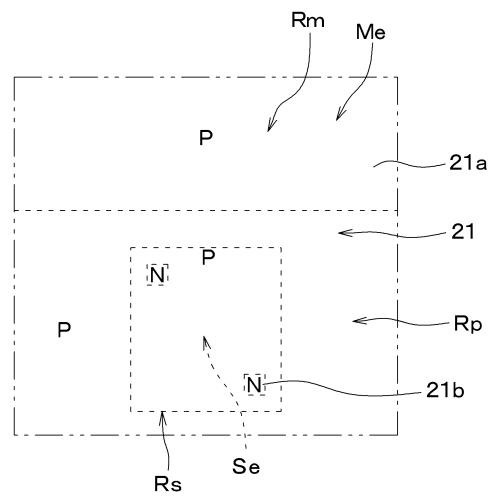

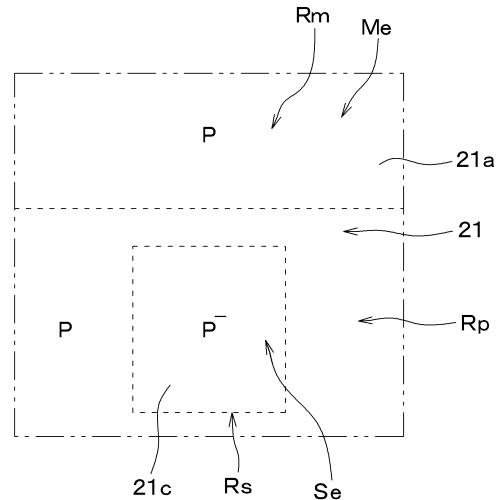

本実施形態の半導体装置は、図1に示されるように、メイン素子M<sub>e</sub>が形成されるメイン領域R<sub>m</sub>、センス素子S<sub>e</sub>が形成されるセンス領域R<sub>s</sub>、周辺領域R<sub>p</sub>を有している。以下、メイン領域R<sub>m</sub>およびセンス領域R<sub>s</sub>の構成について、図1～図4を参照しつつ説明する。

【0015】

なお、本実施形態のメイン素子M<sub>e</sub>およびセンス素子S<sub>e</sub>は、具体的には後述するが、半導体基板10の他面10b側の構成が異なっている以外は同様の構成とされている。また、メイン素子M<sub>e</sub>およびセンス素子S<sub>e</sub>は、所定の面積比（例えば、3000:1）となるように形成されている。そして、本実施形態の半導体装置は、センス素子S<sub>e</sub>に流れるセンス電流および面積比によってメイン素子M<sub>e</sub>に流れるメイン電流が検出（すなわち、導出）される。

【0016】

半導体装置は、半導体基板10を用いて構成されている。半導体基板10は、N<sup>-</sup>型のドリフト層11を有しており、ドリフト層11上に、比較的不純物濃度が低く設定されたP型のベース層12が配置されている。以下、半導体基板10のうちのベース層12側の面を半導体基板10の一面10aとし、半導体基板10のうちのドリフト層11側の面を他面10bとして説明する。

【0017】

半導体基板10には、一面10a側からベース層12を貫通してドリフト層11に達するように複数のトレンチ13が形成され、このトレンチ13によってベース層12が複数個に分離されている。なお、複数のトレンチ13は、半導体基板10の一面10aの面方向のうちの一方向（すなわち、図2中紙面奥行き方向）を長手方向とし、各トレンチ13が等間隔にストライプ状となるように延設されている。

【0018】

また、本実施形態では、トレンチ13は、メイン領域R<sub>m</sub>に形成されている部分とセンス領域R<sub>s</sub>に形成されている部分とが繋がった状態となるように構成されている。つまり、トレンチ13は、メイン領域R<sub>m</sub>から周辺領域R<sub>p</sub>を介してセンス領域R<sub>s</sub>まで延設されている。但し、トレンチ13は、メイン領域R<sub>m</sub>に形成されている部分とセンス領域R<sub>s</sub>に形成されている部分とが分断されていてもよい。

【0019】

各トレンチ13内は、各トレンチ13の壁面を覆うように形成されたゲート絶縁膜14と、このゲート絶縁膜14の上に形成されたポリシリコン等により構成されるゲート電極15とにより埋め込まれている。これにより、トレンチゲート構造が構成されている。なお、本実施形態では、トレンチ13の壁面のうちのベース層12を露出させる部分が、後述するエミッタ領域16とドリフト層11との間に配置されたベース層12の表面に相当する。

【0020】

そして、ベース層12の表層部には、N<sup>+</sup>型のエミッタ領域16と、エミッタ領域16に挟まれるP<sup>+</sup>型のコンタクト領域17とが形成されている。具体的には、エミッタ領域16は、ドリフト層11よりも高不純物濃度で構成され、トレンチ13の側面に接するように形成されている。一方、コンタクト領域17は、ベース層12よりも高不純物濃度で構成され、エミッタ領域16を挟んでトレンチ13と反対側に形成されている。

【0021】

より詳しくは、エミッタ領域16は、トレンチ13間の領域において、トレンチ13の長手方向に沿ってトレンチ13の側面に接するように棒状に延設されている。コンタクト領域17は、2つのエミッタ領域16に挟まれてトレンチ13の長手方向（すなわち、エミッタ領域16）に沿って棒状に延設されている。なお、本実施形態のコンタクト領域1

10

20

30

40

50

7は、半導体基板10の一面10aを基準としてエミッタ領域16よりも深く形成されている。

#### 【0022】

ここで、本実施形態では、エミッタ領域16は、メイン領域Rmおよびセンス領域Rsに形成されており、周辺領域Rpには形成されていない。つまり、本実施形態では、半導体基板10の一面10a側では、エミッタ領域16が形成されている部分がメイン領域Rmまたはセンス領域Rsとされており、エミッタ領域16が形成されていない部分が周辺領域Rpとされている。言い換えると、半導体基板10の一面10a側では、エミッタ領域16が形成されているか否かにより、メイン領域Rm、センス領域Rs、周辺領域Rpが区画されている。

10

#### 【0023】

なお、センス領域Rsにおける半導体基板10の他面10b側は、センス領域Rsの一面10a側よりも平面領域が大きくされている。具体的には、半導体基板10の他面10b側では、一面10a側よりも半導体基板10の厚さ分だけ全体的に広い領域がセンス領域Rsとされている。図1では、センス領域Rsにおける他面10b側の領域を点線で示し、センス領域Rsにおける一面10a側の領域を実線で示している。

#### 【0024】

ベース層12（すなわち、半導体基板10の一面10a）上にはBPSG（Borophosphosilicate Glassの略）等で構成される層間絶縁膜18が形成されている。そして、層間絶縁膜18には、エミッタ領域16の一部およびコンタクト領域17を露出させるコンタクトホール18aが形成されている。

20

#### 【0025】

層間絶縁膜18上には上部電極19が形成されている。そして、この上部電極19は、コンタクトホール18aを介してエミッタ領域16およびコンタクト領域17と電気的に接続されている。なお、本実施形態では、上部電極19が第1電極に相当する。

#### 【0026】

ドリフト層11のうちのベース層12側と反対側（すなわち、半導体基板10の他面10b側）には、N型のフィールドストップ層（以下では、単にFS層という）20が形成されている。このFS層20は、必ずしも必要なものではないが、空乏層の広がりを防ぐことで耐圧と定常損失の性能向上を図ると共に、半導体基板10の他面10b側から注入される正孔の注入量を制御するために備えてある。

30

#### 【0027】

そして、FS層20を挟んでドリフト層11と反対側には、他面層21が形成されている。具体的には、メイン領域Rmにおいては、図2および図4に示されるように、他面層21として、P型のコレクタ層21aが形成されている。一方、センス領域Rsにおいては、図3および図4に示されるように、他面層21として、コレクタ層21aと導電型が反対とされたN型の逆導電型層21bが形成されている。つまり、センス領域Rsには、半導体基板10の厚さ方向に沿って、コレクタ層21aよりもP型の不純物量が少なくされた逆導電型層21bが形成されている。本実施形態のセンス領域Rsでは、全体に逆導電型層21bが形成されており、コレクタ層21aが形成されていない。すなわち、本実施形態のセンス領域Rsでは、他面10b側の全体が逆導電型層21bとされている。

40

#### 【0028】

なお、本実施形態の周辺領域Rpは、メイン領域Rmと同様のコレクタ層21aが形成されている。また、本実施形態では、逆導電型層21bが低不純物層に相当している。そして、半導体基板10の厚さ方向に沿ってとは、言い換えると、ドリフト層11とベース層12との積層方向に沿ってともいうことができる。

#### 【0029】

コレクタ層21aおよび逆導電型層21b上（すなわち、半導体基板10の他面10b）には下部電極22が形成されている。なお、本実施形態では、下部電極22が第2電極に相当している。

50

## 【0030】

以上が本実施形態における半導体装置の構成である。なお、本実施形態では、N型、N-型、N<sup>+</sup>型が第1導電型に相当し、P型、P<sup>+</sup>型が第2導電型に相当している。

## 【0031】

次に、このような半導体装置の作動および効果について説明する。

## 【0032】

このような半導体装置は、上部電極19に下部電極22より低い電圧が印加されると共に、ゲート電極15に所定の閾値電圧以上の電圧が印加されると、ベース層12のうちのトレンチ13と接する部分にN型の反転層（すなわち、チャネル）が形成される。そして、エミッタ領域16から反転層を介して電子がドリフト層11に供給されると共に、コレクタ層21aから正孔がドリフト層11に供給され、伝導度変調によりドリフト層11の抵抗値が低下してオン状態となる。

10

## 【0033】

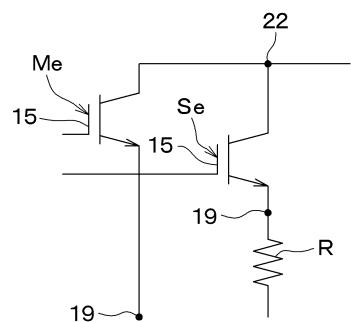

そして、このような半導体装置は、図5に示されるように、センス素子Seの上部電極19に検出抵抗Rが接続され、メイン素子Meに流れるメイン電流が次のように検出される。まず、半導体装置では、検出抵抗Rに流れる電流とセンス素子Seに流れるセンス電流とが等しいため、検出抵抗Rの両端電圧である検出信号に基づき、センス素子Seに流れるセンス電流が検出される。また、メイン素子Meとセンス素子Seとが所定の面積比で形成されており、メイン素子Meに流れるメイン電流およびセンス素子Seに流れるセンス電流は、面積比に比例する。したがって、メイン領域Rmに流れるメイン電流は、面積比とセンス電流に基づいて導出される。

20

## 【0034】

また、このような半導体装置は、検出信号に基づいて定常状態であるか異常状態であるかの状態判定も行われる。この場合、上記のように、定常状態の定常検出信号（以下では、単に定常検出信号ともいう）と異常状態の異常検出信号（以下では、異常検出信号ともいう）との差である差電圧が大きくなるようにして誤判定を抑制することが好ましい。このため、本実施形態のセンス素子Seは、定常検出信号と異常検出信号との差が大きくなるように、他面層21が逆導電型層21bを含んで構成されている。

## 【0035】

以下、本実施形態における定常検出信号および異常検出信号について、比較対象の半導体装置における定常検出信号および異常検出信号と比較しつつ説明する。なお、ここでの比較対象の半導体装置は、センス領域Rsの他面層21の全体がメイン領域Rmのコレクタ層21aと同じ構成とされた半導体装置としている。また、以下では、メイン領域Rmとセンス領域Rsの面積比を3000:1とした場合のシミュレーション結果を例に挙げて説明する。さらに、以下では、ゲート電極15に所定の閾値電圧以上の電圧が印加された後、ゲート電極15への所定電圧の印加を停止するまでの期間T1から期間T2の間の検出信号を定常検出信号とする。同様に、以下では、ゲート電極15に所定の閾値電圧以上の電圧が印加された後、ゲート電極15への所定電圧の印加を停止するまでの期間T3から期間T4の間の検出信号を異常検出信号とする。

30

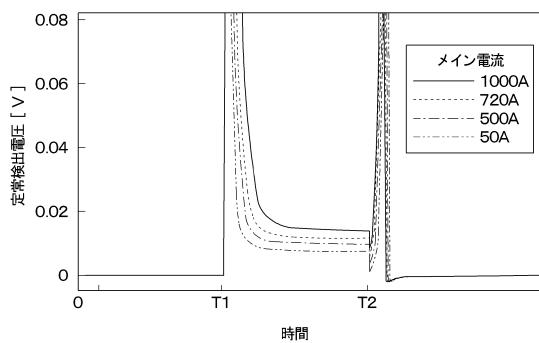

## 【0036】

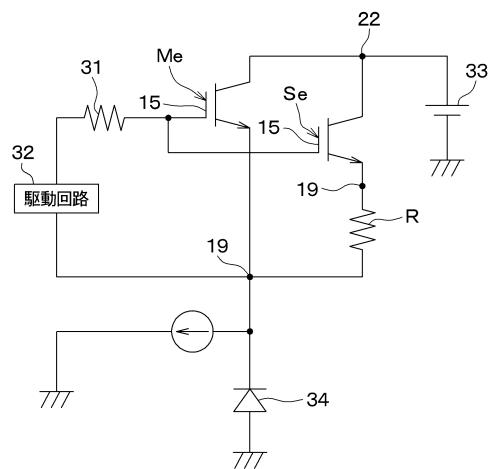

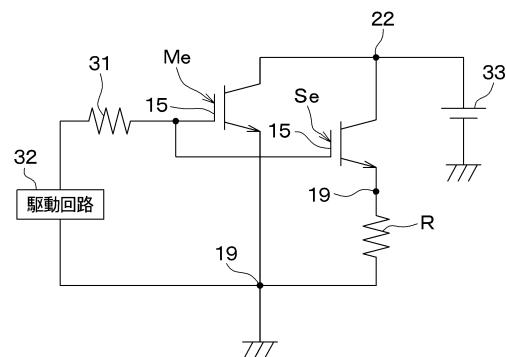

まず、図6に示される検査回路を構成して得られた定常検出信号のシミュレーション結果について、図7～図9を参照しつつ説明する。なお、この検査回路は、メイン素子Meおよびセンス素子Seのゲート電極15に調整抵抗31を介して駆動回路32が接続されると共に、下部電極22に電源33の正極側が接続されている。また、メイン素子Meの上部電極19、およびセンス素子Seの上部電極19に接続された検出抵抗Rにダイオード34が接続されている。

40

## 【0037】

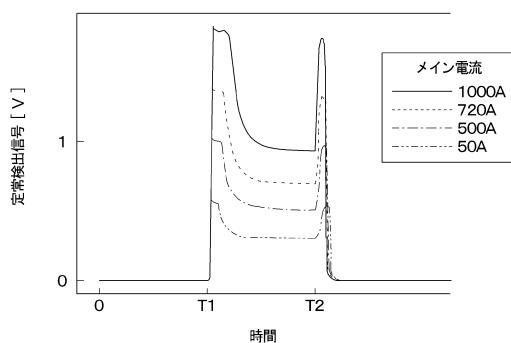

図7に示されるように、比較対象の半導体装置では、メイン電流が大きくなるにつれて定常検出信号も大きくなる。一方、本実施形態の半導体装置では、センス領域Rsの他面層21の全体が逆導電型層21bとされているため、半導体基板10の他面10b側から

50

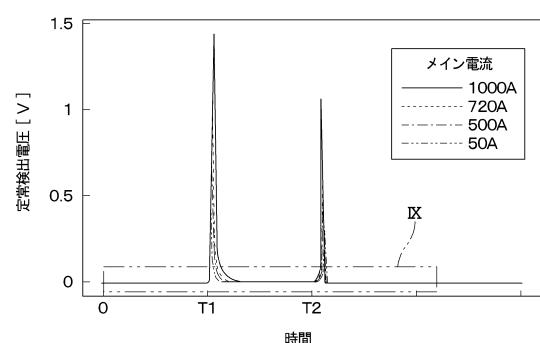

の正孔の供給が抑制される。このため、本実施形態の半導体装置では、センス電流が小さくなり、図8および図9に示されるように、比較対象の半導体装置と比較すると、定常検出信号が極めて小さくなる。そして、本実施形態の半導体装置における定常検出信号は、メイン電流が大きくなることで僅かに大きくなるが、比較対象の半導体装置ほどの変化はない。

#### 【0038】

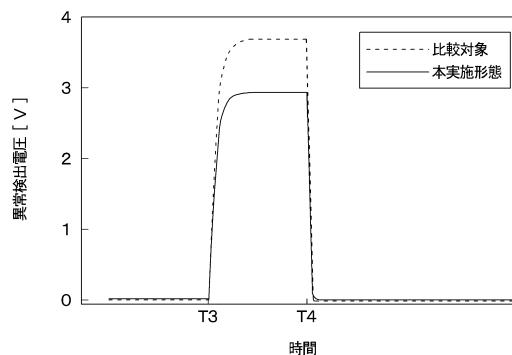

次に、図10に示される検査回路を構成して得られた異常検出信号のシミュレーション結果について、図11を参照しつつ説明する。なお、この検査回路は、メイン素子Meおよびセンス素子Seのゲート電極15に調整抵抗31を介して駆動回路32が接続されると共に、下部電極22に電源33の正極側が接続されている。また、メイン素子Meの上部電極19、およびセンス素子Seの上部電極19に接続された検出抵抗Rは、グランドに接続されている。そして、図11および図12は、ゲート-エミッタ間電圧Vgeを一般的なゲート駆動電圧である15V程度とした場合の異常検出信号を示している。

10

#### 【0039】

図11に示されるように、比較対象の半導体装置では、メイン素子Meに定常状態よりも極めて多い異常電流が流れた場合、異常検出信号が約3.6Vとなる。一方、本実施形態の半導体装置では、逆導電型層21bが形成されているが、メイン素子Meに多量の異常電流が流れる場合にはセンス素子Seにも所定量のセンス電流が流れ、異常検出信号が約2.9Vとなる。つまり、本実施形態の半導体装置における定常検出信号および異常検出信号は、比較対象の半導体装置における定常検出信号および異常検出信号に対し、定常検出信号の減少率の方が異常検出信号の減少率よりも極めて大きくなる。

20

#### 【0040】

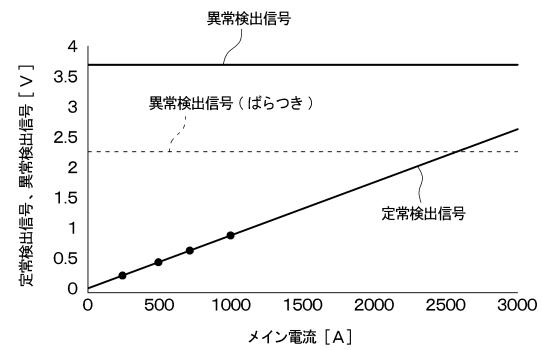

そして、異常検出信号と定常検出信号とを重ね合わせると、比較対象の半導体装置では図12に示されるようになり、本実施形態の半導体装置では図13および図14に示されるようになる。

#### 【0041】

具体的には、比較対象の半導体装置では、図12に示されるように、メイン電流が大きくなるほど定常検出信号も大きくなり、定常検出信号と異常検出信号との差電圧が小さくなる。このため、例えば、異常検出信号が約3.6Vとなるように半導体装置を製造したとしても、設計バラツキ等によって実際の異常検出信号が約2.3V程度となってしまった場合には、メイン電流が大きくなると異常検出信号より定常検出信号の方が大きくなる可能性がある。例えば、図12では、メイン電流が2600A程度になると、定常検出信号が異常検出信号よりも大きくなる。したがって、比較対象のような半導体装置では、予め異常検出信号がさらに大きくなるように飽和電流を大きくすることが必要になる。

30

#### 【0042】

一方、本実施形態の半導体装置では、図13および図14に示されるように、定常状態検出信号が十分に小さい値に抑えられ、定常検出信号と異常検出信号との差電圧を十分に大きくできる。なお、図14は、図13における定常検出信号の拡大図である。このため、本実施形態の半導体装置によれば、メイン電流が大きくなつたとしても、異常検出信号より定常検出信号の方が大きくなることを抑制できる。また、本実施形態の半導体装置では、逆導電型層21bを形成することによって定常検出信号が小さくなるようにしているため、センス素子Seは抵抗が大きくなる。したがって、本実施形態の半導体装置では、定常状態ではセンス素子Seにセンス電流が流れ難くなり、飽和電流の設計の自由度を向上できる。

40

#### 【0043】

以上説明した本実施形態によれば、センス素子Seは、逆導電型層21bを含んで構成されており、半導体基板10の他面10b側からの正孔の注入が抑制される。このため、定常状態でセンス素子Seに流れるセンス電流を小さくでき、定常検出信号を極めて小さくできる。したがって、定常検出信号と異常検出信号との差電圧を十分に大きくでき、誤判定されることを抑制できる。

50

## 【0044】

また、本実施形態の半導体装置では、メイン素子M<sub>e</sub>におけるコレクタ層21aの不純物濃度を必要以上に高くする必要がないため、スイッチングオフ損失が大きくなることも抑制できる。

## 【0045】

## (第1実施形態の変形例)

上記第1実施形態の変形例について説明する。上記第1実施形態において、センス領域R<sub>s</sub>の他面層21は、全体が逆導電型層21bで構成されていなくてもよく、図15A～図15Gのように構成されていてもよい。なお、図15A～図15Gは、図1中の領域IVに相当する部分における半導体基板10の他面10b側の平面図である。

10

## 【0046】

例えば、図15Aに示されるように、センス領域R<sub>s</sub>の他面層21は、内縁部に逆導電型層21bが形成され、逆導電型層21bを囲むようにコレクタ層21aが形成されていてもよい。つまり、センス領域R<sub>s</sub>の他面層21は、コレクタ層21aおよび逆導電型層21bを有する構成とされていてもよい。

## 【0047】

この場合、逆導電型層21bは、図15Bのように一方向を長手方向として複数形成されていてもよいし、図15Cのように一方向を長手方向として1つのみ形成されていてもよい。なお、図15Bおよび図15Cでは、センス領域R<sub>s</sub>からメイン領域R<sub>m</sub>に向かう方向に沿って逆導電型層21bが延設されている。また、逆導電型層21bは、図15Dに示されるように、センス領域R<sub>s</sub>からメイン領域R<sub>m</sub>に向かう方向と直交する方向に沿って延設されていてもよい。さらに、逆導電型層21bは、図15Eに示されるように、センス領域R<sub>s</sub>からメイン領域R<sub>m</sub>に向かう方向に沿って延設された部分と、当該方向と直交する方向に延設された部分とが連結されていてもよい。また、逆導電型層21bは、図15Fに示されるように、ドット状に形成されていてもよい。この場合、逆導電型層21bは、図15Gに示されるように、一部の逆導電型層21bのみが配置される構成とされといてもよい。さらに、特に図示しないが、逆導電型層21bは、これらを適宜組み合わせて形成されていてもよいし、さらに別の形状とされていてもよい。

20

## 【0048】

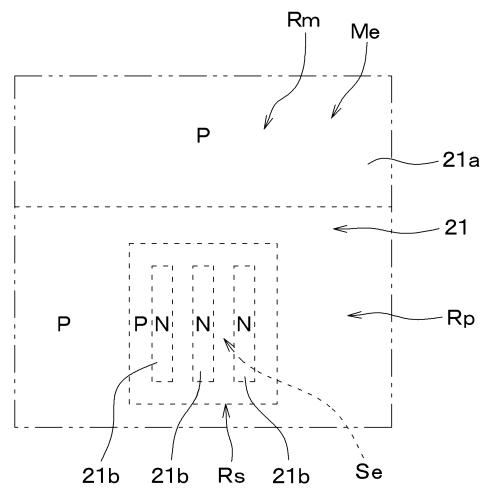

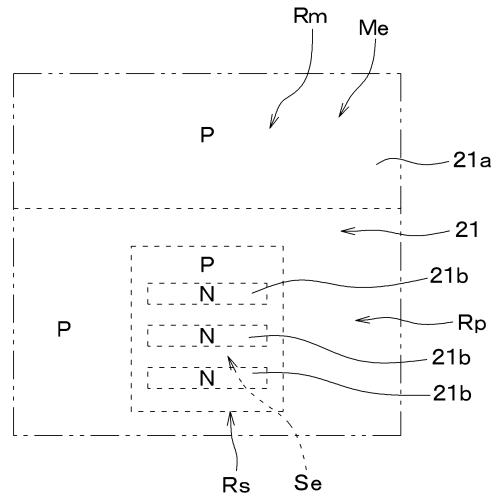

## (第2実施形態)

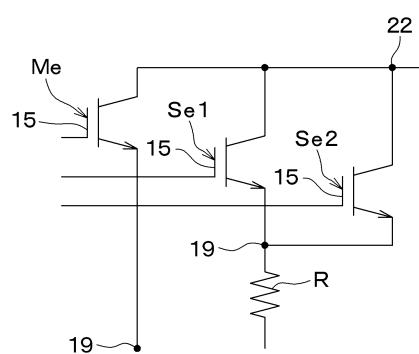

第2実施形態について説明する。本実施形態は、第1実施形態に対し、メイン素子M<sub>e</sub>に対して複数のセンス素子S<sub>e</sub>を並列に配置したものである。その他に関しては、第1実施形態と同様であるため、ここでは説明を省略する。

30

## 【0049】

まず、上記のように、比較対象の半導体装置では、定常検出信号が大きくなり、異常検出信号との差が小さくなる可能性がある。一方、上記第1実施形態の半導体装置では、定常検出信号を十分に小さくできるが、定常検出信号が小さくなり過ぎることで定常状態におけるメイン電流の検出精度が低下する可能性がある。

## 【0050】

このため、本実施形態の半導体装置は、図16に示されるように、メイン素子M<sub>e</sub>に対し、特性の異なる第1センス素子S<sub>e1</sub>および第2センス素子S<sub>e2</sub>が並列に接続されて構成されている。具体的には、本実施形態の第1センス素子S<sub>e1</sub>は、メイン素子M<sub>e</sub>と同様の構成とされており、他面層21としてのコレクタ層21aがセンス領域R<sub>s</sub>の全体に形成されている。一方、第2センス素子S<sub>e2</sub>は、上記第1実施形態におけるセンス素子S<sub>e</sub>と同様の構成とされており、他面層21としての逆導電型層21bがセンス領域R<sub>s</sub>の全体に形成されている。

40

## 【0051】

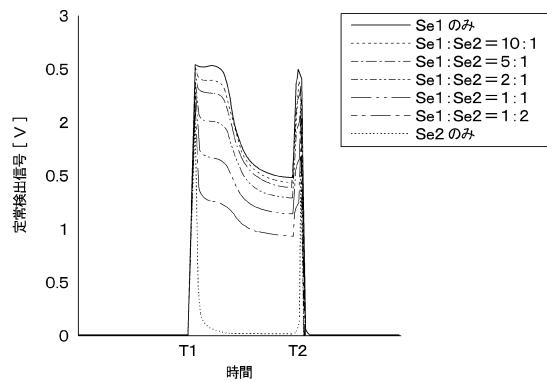

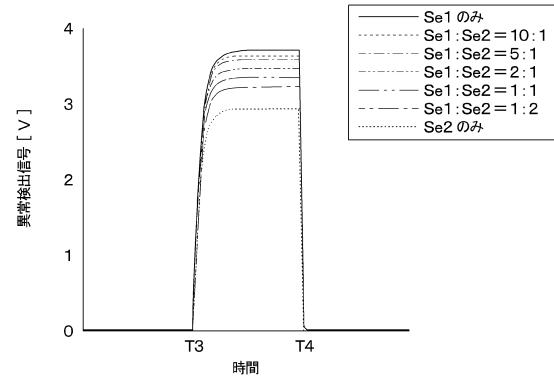

このような半導体装置では、図17および図18に示されるように、第1センス素子S<sub>e1</sub>と第2センス素子S<sub>e2</sub>との面積比を調整することにより、定常検出信号および異常検出信号の値を容易に調整できる。具体的には、図17および図18に示されるように、

50

定常検出信号および異常検出信号は、第1センス素子Se1の比率を高くするほど大きくなる。なお、図17は、メイン電流が1500Aである場合の定常検出信号を示している。図18は、ゲート-エミッタ間電圧Vgeを一般的なゲート駆動電圧である15V程度とした場合の異常検出信号を示している。

#### 【0052】

そして、図19に示されるように、定常検出信号と異常検出信号とは、第1センス素子Se1の比率が高くなるほど、差電圧が小さくなり易い。しかしながら、上記のように、定常検出信号は、第1センス素子Se1の比率を大きくすることで大きくなる。したがって、第1センス素子Se1および第2センス素子Se2は、要求される特性に応じて比率が調整されることが好ましい。この場合、図19に示されるように設計ばらつきを考慮し、定常検出信号が異常検出信号より大きくなることがないようにすることが好ましい。

10

#### 【0053】

なお、本実施形態の定常検出信号は、図6と同様の検査回路を構成して得られたシミュレーション結果である。同様に、本実施形態の異常検出信号は、図10と同様の検査回路を構成して得られたシミュレーション結果である。

#### 【0054】

以上説明した本実施形態によれば、センス素子Seが逆導電型層21bを含んで構成されるため、定常検出信号を十分に小さくでき、上記第1実施形態と同様の効果を得ることができる。

20

#### 【0055】

(1) 本実施形態では、メイン素子Meに対し、特性の異なる第1センス素子Se1および第2センス素子Se2が並列に接続されて構成されている。このため、第1センス素子Se1と第2センス素子Se2との比率を調整することにより、定常検出信号の大きさおよび異常検出信号の大きさを容易に変更できる。

#### 【0056】

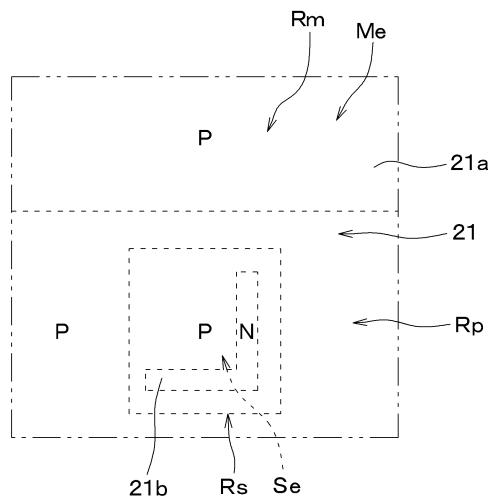

##### (第3実施形態)

第3実施形態について説明する。本実施形態は、第1実施形態に対し、センス素子Seの構成を変更したものである。その他に関しては、第1実施形態と同様であるため、ここでは説明を省略する。

30

#### 【0057】

本実施形態のセンス領域Rsは、図20に示されるように、他面層21として、半導体基板10の厚さ方向に沿ってコレクタ層21aよりもP型の不純物量が少なくされたP-型の低不純物濃度層21cが形成されている。言い換えると、センス領域Rsは、他面層21として、コレクタ層21aよりもドーズ量が少なくされたP-型の低不純物濃度層21cが形成されている。

40

#### 【0058】

具体的には、本実施形態では、メイン素子Meのコレクタ層21aおよびセンス素子Seの低不純物濃度層21cは、それぞれ半導体基板10の他面10b側からイオン注入が行われることで形成されている。そして、本実施形態の低不純物濃度層21cは、半導体基板10の他面10bからの深さがコレクタ層21aと同じとされているが、コレクタ層21aよりもピーク濃度が低くされている。なお、図20は、図1中の領域IVに相当する部分における半導体基板の他面側の平面図である。

#### 【0059】

このようなセンス素子Seでは、図21に示されるように、低不純物濃度層21cの不純物濃度は、ピーク濃度が低くなるほど小さくなる。なお、図21は、コレクタ層21aのピーク濃度を基準としており、例えば、図21中のピーク濃度1/1は、コレクタ層21aのピーク濃度と同じであることを意味している。

#### 【0060】

そして、図22および図23に示されるように、定常検出信号および異常検出信号は、低不純物濃度層21cのピーク濃度が低くなるほど小さくなる。但し、低不純物濃度層2

50

1 c のピーク濃度に依存する定常検出信号の減少率は、異常検出信号の減少率よりも大きくなる。また、低不純物濃度層 2 1 c は、例えば、ピーク濃度がコレクタ層 2 1 a のピーク濃度の 1 / 50 である場合であっても、P 型層である。このため、定常検出信号および異常検出信号は、上記第 1 実施形態のように他面層 2 1 が逆導電型層 2 1 b である場合と比較すると大きくなる。なお、図 2 2 は、メイン電流が 1 0 0 0 A である場合の定常検出信号を示している。図 2 3 は、ゲート - エミッタ間電圧  $V_{ge}$  を一般的なゲート駆動電圧である 15 V 程度とした場合の異常検出信号を示している。

#### 【 0 0 6 1 】

そして、図 2 4 に示されるように、定常検出信号と異常検出信号とは、コレクタ層 2 1 a のピーク濃度が高くなるほど差電圧が小さくなり易い。つまり、定常検出信号と異常検出信号とは、低不純物濃度層 2 1 c のピーク電圧が高くなるほど差電圧が小さくなり易い。したがって、低不純物濃度層 2 1 c のピーク濃度は、要求される特性に応じて調整されることが好ましい。この場合、図 2 5 に示されるように設計ばらつきを考慮し、定常検出信号が異常検出信号より大きくなることがないようにすることが好ましい。つまり、図 2 5 では、設計ばらつきを考慮し、差電圧が 0 V 以上となるようにすることが好ましい。

#### 【 0 0 6 2 】

なお、本実施形態の定常検出信号は、図 6 と同様の検査回路を構成して得られたシミュレーション結果である。同様に、本実施形態の異常検出信号は、図 1 0 と同様の検査回路を構成して得られたシミュレーション結果である。

#### 【 0 0 6 3 】

以上説明した本実施形態によれば、センス素子 S e が P - 型とされた低不純物濃度層 2 1 c を含んで構成されている。このため、上記第 1 実施形態と同様の効果を得ることができる。

#### 【 0 0 6 4 】

( 1 ) 本実施形態では、センス素子 S e が P - 型とされた低不純物濃度層 2 1 c を含んで構成されている。このため、センス素子 S e の他面層 2 1 が逆導電型層 2 1 b のみで構成されている場合と比較して、センス素子 S e の定常検出信号が小さくなり過ぎることを抑制できる。

#### 【 0 0 6 5 】

##### ( 第 3 実施形態の変形例 )

上記第 3 実施形態では、低不純物層として、ピーク濃度がコレクタ層 2 1 a のピーク濃度よりも低くされている低不純物濃度層 2 1 c を説明した。しかしながら、低不純物層は、次のように構成されていてもよい。例えば、図 2 6 に示されるように、低不純物層は、コレクタ層 2 1 a とピーク濃度が等しくされているが、半導体基板 1 0 の厚さ方向に沿った不純物量が少なくなるように、コレクタ層 2 1 a よりも半導体基板 1 0 の他面 1 0 b からの深さが浅くされていてもよい。言い換えると、低不純物層は、コレクタ層 2 1 a とピーク濃度が等しくされているが、コレクタ層 2 1 a よりも厚さが薄くされた構成とされていてもよい。

#### 【 0 0 6 6 】

なお、このようなコレクタ層 2 1 a および低不純物層は、例えば、次のように形成される。すなわち、加速電圧を変更しつつ複数回のイオン注入を行うことによってコレクタ層 2 1 a を形成すると共に、1 回のイオン注入を行うことによって低不純物濃度層 2 1 c を形成することにより、上記のコレクタ層 2 1 a および低不純物層が形成される。

#### 【 0 0 6 7 】

また、上記第 3 実施形態において、低不純物濃度層 2 1 c の形状は、上記第 1 実施形態の変形例のように適宜変更可能である。さらに、上記第 3 実施形態を上記第 1 実施形態に組み合わせ、センス素子 S e は、他面層 2 1 として、逆導電型層 2 1 b および低不純物濃度層 2 1 c を有する構成とされていてもよい。

#### 【 0 0 6 8 】

##### ( 第 4 実施形態 )

10

20

30

40

50

第4実施形態について説明する。本実施形態は、第1実施形態に対し、メイン領域Rmの構成を変更したものである。その他に関しては、第1実施形態と同様であるため、ここでは説明を省略する。

【0069】

本実施形態の半導体装置では、図27に示されるように、メイン領域Rmは、IGBT素子が形成されるIGBT領域1aと、IGBT領域1aに隣接し、FWD素子として機能するFWD領域1bとを有している。つまり、本実施形態の半導体装置は、同じ半導体基板10にIGBT領域1aとFWD領域1bとが形成されたRC(Reverse Conductionの略)-IGBTとされている。なお、本実施形態では、後述するように、半導体基板10の他面10bに位置するコレクタ層21a上の部分がIGBT領域1aとされ、半導体基板10の他面10bに位置するカソード層21d上の部分がFWD領域1bとされている。

10

【0070】

IGBT領域1aは、上記第1実施形態のメイン領域Rmと同じ構成とされている。FWD領域1bは、本実施形態では、半導体基板10の一面10a側の構成がIGBT領域と同様の構成とされている。そして、層間絶縁膜18には、FWD領域1bにおいて、コンタクト領域17等を露出させるコンタクトホール18bが形成されていると共に、ゲート電極15を露出させるコンタクトホール18cが形成されている。

【0071】

上部電極19は、FWD領域1bにおいて、コンタクトホール18bを介してコンタクト領域17と電気的に接続されている。そして、本実施形態の上部電極19は、IGBT領域1aにおいてエミッタ電極として機能し、FWD領域1bにおいてアノード電極として機能する。また、本実施形態の上部電極19は、FWD領域1bにおいて、ゲート電極15とも電気的に接続されている。すなわち、FWD領域1bにおけるゲート電極15は、上部電極19と同電位とされている。

20

【0072】

また、半導体基板10の他面10b側においては、コレクタ層21aと隣接するように、他面層21として、N型のカソード層21dが形成されている。そして、本実施形態の半導体装置は、半導体基板10の他面10bに位置するコレクタ層21a上の部分がIGBT領域1aとされ、半導体基板10の他面10bに位置するカソード層21d上の部分がFWD領域1bとされている。なお、本実施形態のカソード層21dは、センス領域Rsにおける逆導電型層21bと同じ不純物濃度で構成されていると共に、同じ深さで形成されている。

30

【0073】

以上説明した本実施形態によれば、センス素子Seが逆導電型層21bを含んで構成されているため、定常検出信号を十分に小さくでき、上記第1実施形態と同様の効果を得ることができる。

【0074】

(1) 本実施形態では、メイン領域RmにFWD領域1bが備えられた半導体装置とされている。そして、FWD領域1bのカソード層21dは、センス領域Rsにおける逆導電型層21bと同じ不純物濃度で構成されていると共に、同じ深さで形成されている。このため、本実施形態では、カソード層21dを形成する際に逆導電型層21bを同時に形成することができる。したがって、製造工程を増加させることなく、逆導電型層21bを配置することができる。

40

【0075】

(第4実施形態の変形例)

上記第4実施形態の変形例について説明する。上記第4実施形態において、FWD領域1bの構成は、適宜変更可能である。例えば、FWD領域1bには、ゲート電極15やエミッタ領域16等が形成されていなくてもよい。なお、IGBT領域1aとFWD領域1bとを含んでメイン領域Rmが構成される場合、メイン領域Rmは、電流が主に流れる領

50

域ということもできる。

【0076】

(他の実施形態)

本開示は、実施形態に準拠して記述されたが、本開示は当該実施形態や構造に限定されるものではないと理解される。本開示は、様々な変形例や均等範囲内の変形をも包含する。加えて、様々な組み合わせや形態、さらには、それらに一要素のみ、それ以上、あるいはそれ以下、を含む他の組み合わせや形態をも、本開示の範疇や思想範囲に入るものである。

【0077】

例えば、上記各実施形態では、第1導電型をN型とし、第2導電型をP型とした半導体装置を説明したが、第1導電型をP型とし、第2導電型をN型とした半導体装置としてもよい。

10

【0078】

また、上記各実施形態では、トレンチゲート構造を有するメイン素子Meおよびセンス素子Seを備えた半導体装置について説明したが、プレーナゲート構造を有するメイン素子Meおよびセンス素子Seを備えた半導体装置としてもよい。

【0079】

さらに、上記各実施形態において、エミッタ領域16とコンタクト領域17との配置の仕方は、適宜変更可能である。例えば、エミッタ領域16およびコンタクト領域17は、トレンチ13の長手方向に沿って交互に配置されていてもよい。

20

【0080】

そして、上記各実施形態を適宜組み合わせた半導体装置とすることもできる。例えば、上記第2実施形態を上記第3、第4実施形態に組み合わせ、センス素子Seが特性の異なる第1センス素子Se1および第2センス素子Se2を有する構成とされていてもよい。また、上記第3実施形態を上記第4実施形態に組み合わせ、センス素子Seの他面層21が低不純物濃度層21cで構成されていてもよい。さらに、上記各実施形態を組み合わせたもの同士をさらに組み合わせてもよい。

【符号の説明】

【0081】

1 1 ドリフト層

30

1 2 ベース層

1 4 ゲート絶縁膜

1 5 ゲート電極

1 6 エミッタ領域

1 9 上部電極(第1電極)

2 1 他面層

2 1 a コレクタ層

2 1 b 逆導電型層(低不純物層)

2 1 c 低不純物濃度層(低不純物層)

2 2 下部電極(第2電極)

40

Me メイン素子

Se センス素子

Rm メイン領域

Rs センス領域

50

【四面】

【 四 1 】

【 図 2 】

【 図 3 】

【図4】

【図 5】

【図 6】

10

【図 7】

【図 8】

20

30

40

50

【図 9】

【図 10】

10

【図 11】

【図 12】

20

【図 13】

【図 14】

30

40

50

【図 15 A】

【図 15 B】

10

【図 15 C】

【図 15 D】

20

30

40

50

【図 15 E】

【図 15 F】

【図 15 G】

【図 16】

【図 1 7】

【図 1 8】

【図 1 9】

【図 2 0】

10

20

30

40

50

【図 2 1】

【図 2 2】

【図 2 3】

【図 2 4】

10

20

30

40

50

【図 2 5】

【図 2 6】

10

【図 2 7】

20

30

40

50

## フロントページの続き

## (51)国際特許分類

**H 1 0 D 30/65 (2025.01)**

| F I     |       |         |

|---------|-------|---------|

| H 0 1 L | 29/78 | 6 5 5 D |

| H 0 1 L | 29/06 | 3 0 1 D |

| H 0 1 L | 29/06 | 3 0 1 V |

| H 0 1 L | 29/91 | C       |

| H 0 1 L | 27/06 | 1 0 2 A |

| H 0 1 L | 29/78 | 3 0 1 D |

| H 0 1 L | 27/06 | 3 1 1 A |

## (56)参考文献

国際公開第2020/208738 (WO, A1)

特開2019-021885 (JP, A)

国際公開第2022/172328 (WO, A1)

特開2009-117786 (JP, A)

特開2015-176927 (JP, A)

特開2012-119658 (JP, A)

## (58)調査した分野

(Int.Cl. , DB名)

|         |               |

|---------|---------------|

| H 0 1 L | 2 1 / 3 3 6   |

| H 0 1 L | 2 1 / 7 6     |

| H 0 1 L | 2 1 / 8 2 3 4 |

| H 0 1 L | 2 7 / 0 6     |

| H 0 1 L | 2 9 / 0 6     |

| H 0 1 L | 2 9 / 1 2     |

| H 0 1 L | 2 9 / 7 3 9   |

| H 0 1 L | 2 9 / 7 8     |

| H 0 1 L | 2 9 / 8 6 1   |

| H 0 1 L | 2 9 / 8 6 8   |