(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7547551号

(P7547551)

(45)発行日 令和6年9月9日(2024.9.9)

(24)登録日 令和6年8月30日(2024.8.30)

(51)国際特許分類

|        |                  |        |        |         |

|--------|------------------|--------|--------|---------|

| H 01 L | 27/146 (2006.01) | H 01 L | 27/146 | A       |

| H 01 L | 21/336 (2006.01) | H 01 L | 27/146 | F       |

| H 01 L | 29/78 (2006.01)  | H 01 L | 29/78  | 3 0 1 S |

| H 01 L | 21/8234(2006.01) | H 01 L | 27/088 | B       |

| H 01 L | 27/088(2006.01)  | H 01 L | 29/78  | 3 0 1 G |

請求項の数 10 外国語出願 (全42頁)

(21)出願番号 特願2023-77536(P2023-77536)

(22)出願日 令和5年5月10日(2023.5.10)

(65)公開番号 特開2024-31790(P2024-31790A)

(43)公開日 令和6年3月7日(2024.3.7)

審査請求日 令和5年5月10日(2023.5.10)

(31)優先権主張番号 63/401,291

(32)優先日 令和4年8月26日(2022.8.26)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 18/150,372

(32)優先日 令和5年1月5日(2023.1.5)

(33)優先権主張国・地域又は機関

米国(US)

(73)特許権者 500262038

台湾積體電路製造股 ふん 有限公司

Taiwan Semiconductor Manufacturing Co

mpany, Ltd.

台湾新竹市新竹科學工業園區力行六路八

號

No. 8, Li-Hsin Rd. 6,

Hsinchu Science Park, Hsinchu, TAIWAN

(74)代理人 100147485

弁理士 杉村 憲司

(74)代理人 230118913

弁護士 杉村 光嗣

(74)代理人 100164448

最終頁に続く

(54)【発明の名称】 積層型CMOSイメージセンサ

## (57)【特許請求の範囲】

## 【請求項1】

第1基板を含む第1集積回路( I C )チップと、

前記第1 I Cチップと積層される第2 I Cチップと、

前記第1 I Cチップと前記第2 I Cチップとにまたがる画素センサと

を含み、

前記画素センサは、前記第1 I Cチップにおいて第1トランジスタと受光素子とを含み

、前記第2 I Cチップにおいて複数の第2トランジスタを更に含み、

前記受光素子は前記第1基板にあり、前記第1トランジスタは前記第1基板の表側上に

あり、

前記第1 I Cチップは、受光素子の前記表側内に延伸するシャロートレンチアイソレー

ション( S T I )構造を有さず、

前記第1 I Cチップは、

前記第1基板に前記第1基板の前記表側から延伸し、前記受光素子を囲むグリッド状上部

形状を有する第1ドープウェルと、

前記第1基板内の前記第1ドープウェルの下方にある第2ドープウェルであって、前記第

2ドープウェルは、前記第1ドープウェルと同じドープ型を有し、前記第2ドープウェル

は、前記第1ドープウェルとは異なるドーピングプロファイル及び/又は濃度を有し、前

記第2ドープウェルは、前記第1ドープウェルから前記第1基板の前記表側とは反対の前

記第1基板の裏側まで延伸する、前記第2ドープウェルと、

前記第1基板の前記表側とは反対で前記第1基板の前記表側から離間した前記第1基板の前記裏側から前記第2ドープウェル内まで延伸するディープトレンチアイソレーション構造と、を備える、

イメージセンサ。

**【請求項2】**

前記表側は、前記受光素子に面する前記第1ドープウェルの第1側壁から前記受光素子とは逆を向く前記第1ドープウェルの第2側壁まで、実質的に平面プロファイルを有する、請求項1に記載のイメージセンサ。

**【請求項3】**

前記画素センサに隣接して前記画素センサの繰り返しとなる第2画素センサ

を更に含み、

前記表側は、前記画素センサから前記第2画素センサまで、実質的に平面プロファイルを有する、

請求項1に記載のイメージセンサ。

**【請求項4】**

前記第2ICチップは、

前記第2トランジスタが配置される第2基板と、

前記第2基板内に延伸し、前記第2トランジスタを互いに分離するSTI構造と

を含む、

請求項1に記載のイメージセンサ。

10

**【請求項5】**

前記画素センサは、前記第1ICチップにおいて1つのみのトランジスタを有し、前記第2ICチップにおいて3つのみ又はそれ以上のトランジスタを有する、

請求項1に記載のイメージセンサ。

**【請求項6】**

第1半導体基板と、

前記第1半導体基板において隣接する第1受光素子及び第2受光素子と、

前記第1半導体基板の表側表面上で前記第1受光素子に隣接する第1トランジスタと、

前記第1半導体基板内の第1ドープウェルであって、前記第1ドープウェルは、ソース又

はドレイン領域とは逆のドープ型を有し、前記第1及び第2受光素子間で第1柱状プロフ

ァイルを有する、前記第1ドープウェルと、

前記第1半導体基板内の第1ドープウェルの下方にある第2ドープウェルであって、前記第2ドープウェルは、前記第1ドープウェルと同じドープ型を有し、前記第2ドープウェルは、前記第1ドープウェルとは異なるドーピングプロファイル及び/又は濃度を有し、

前記第2ドープウェルは、第2柱状プロファイルを有し、前記第1及び第2受光素子間に

あり、前記第1ドープウェルから前記表側表面とは反対の前記第1半導体基板の裏側表面

まで延伸し、前記第1柱状プロファイル及び前記第2柱状プロファイルが共通の幅を共有

する、前記第2ドープウェルと、

前記第1半導体基板の前記表側表面とは反対で前記表側表面から離間した前記第1半導体

基板の前記裏側表面から前記第2ドープウェル内まで延伸する、ディープトレンチアイソ

レーション構造と、

30

第2半導体基板と、

前記第2半導体基板上の複数の第2トランジスタと

を含み、

前記第1トランジスタは、前記第1半導体基板においてソース又はドレイン領域を有し、

前記第1受光素子と前記第1トランジスタ及び前記第2トランジスタが画素センサを形

成し、

前記表側表面は、前記第1受光素子から前記第2受光素子まで継続的に前記ソース又は

ドレイン領域の頂部と面一である、

イメージセンサ。

40

50

**【請求項 7】**

前記第1ドープウェルは前記第1受光素子と前記第2受光素子とを分離し、前記第1受光素子に面する第1側壁と、前記第2受光素子に面する第2側壁とを有し、

前記表側表面は、前記第1側壁から前記第2側壁まで継続的に前記ソース又はドレイン領域の頂部と面一である、

請求項6に記載のイメージセンサ。

**【請求項 8】**

前記第1柱状プロファイルの頂部は、前記第1受光素子から前記第2受光素子まで実質的に平坦である、

請求項6に記載のイメージセンサ。

10

**【請求項 9】**

イメージセンサを形成するための方法であって、

第1基板に受光素子を形成することと、

前記第1基板上に、前記受光素子と隣接する第1トランジスタを形成することであって、前記受光素子と前記第1トランジスタは第1画素センサ部分を形成することとを含む、第1集積回路（I C）チップを形成することと、

第2基板上に複数の第2トランジスタを形成することであって、前記第2トランジスタは第2画素センサ部分を形成することとを含む、第2 I Cチップを形成することと、

画素センサを形成するため前記第1画素センサ部分と前記第2画素センサ部分が積層されて共に電気的に結合されるよう、前記第1 I Cチップと前記第2 I Cチップとを接合することとを含み、

20

前記第1トランジスタは前記第1基板の半導体表面上にあり、

前記第1 I Cチップは、前記受光素子で前記半導体表面内に延伸するシャロートレンチアイソレーション（S T I）構造を有さず、

前記第1 I Cチップは、

前記第1基板に前記第1基板の表側から延伸し、前記受光素子及び前記第1トランジスタが形成される画素領域を囲んで区分する、第1ドープウェルと、

前記第1基板内の前記第1ドープウェルの下方にある第2ドープウェルであって、前記第2ドープウェルは、前記第1ドープウェルと同じドープ型を有し、前記第2ドープウェルは、前記第1ドープウェルとは異なるドーピングプロファイル及び／又は濃度を有し、前記第2ドープウェルは、前記第1ドープウェルから前記第1基板の前記表側とは反対の前記第1基板の裏側まで延伸する、前記第2ドープウェルと、

30

前記第1基板の前記表側とは反対で前記第1基板の前記表側から離間した前記第1基板の前記裏側から前記第2ドープウェル内まで延伸するディープトレンチアイソレーション構造と、を備える、

方法。

**【請求項 10】**

前記第1 I Cチップを形成することは、前記第1ドープウェルを形成するため第1基板をドーピングすることを含み、

40

前記半導体表面は、前記第1トランジスタの完成時に、前記第1ドープウェルの第1側壁から前記第1ドープウェルの第2側壁まで平坦であり、

前記受光素子の共通する側で、前記第1側壁は前記受光素子と面し、前記第2側壁は前記受光素子とは逆を向く、

請求項9に記載の方法。

**【発明の詳細な説明】****【背景技術】****【0001】**

イメージセンサを備えた集積回路（I C）は、例えば、カメラ、携帯電話等といった現

50

代の幅広い電子機器で使用されている。イメージセンサの種類には、例えば、相補型金属酸化膜半導体（C M O S）イメージセンサと電荷結合素子（C C D）イメージセンサを含む。C C Dイメージセンサに比べ、C M O Sイメージセンサは、低電力消費、小さなサイズ、高速データ処理、データの直接出力、そして低製造コストのため、益々好まれている。

【発明の概要】

【発明が解決しようとする課題】

【0 0 0 2】

より低い製造コスト、より高いデバイス集積密度、より速い速度、より好ましい性能を達成するための積層型C M O Sイメージセンサを提供する。

【課題を解決するための手段】

【0 0 0 3】

1つの実施形態において、本発明は、第1基板を含む第1集積回路（I C）チップと、第1I Cチップに積層される第2I Cチップと、第1及び第2I Cチップを跨ぐ画素センサとを含むイメージセンサを提供し、画素センサは第1I Cチップにおいて第1トランジスタと受光素子とを含み、第2I Cチップにおいて複数の第2トランジスタを更に含み、受光素子は第1基板にあり、第1トランジスタは第1基板の表側上にあり、第1I Cチップは受光素子の表側に延伸するシャロートレンチアイソレーション（S T I）構造を有さない。

【0 0 0 4】

いくつかの実施形態において、本発明は、第1半導体基板と、第1半導体基板に隣接する第1受光素子及び第2受光素子と、第1半導体基板の表側表面で第1受光素子に隣接する第1トランジスタと、第2半導体基板と、第2半導体基板上の複数の第2トランジスタとを含むイメージセンサを提供し、第1トランジスタは第1半導体基板においてソース又はドレイン領域を有し、第1受光素子と第1トランジスタ及び第2トランジスタは画素センサを形成し、前記表側表面は第1受光素子から第2受光素子まで継続的にソース又はドレイン領域と面一である。

【0 0 0 5】

1つの実施形態において、本発明はイメージセンサを形成するための方法を提供し、該方法は、第1基板に受光素子を形成することを含む第1集積回路（I C）チップを形成することと、第1基板上に受光素子に隣接する第1トランジスタを形成することであって、受光素子と第1トランジスタが第1画素センサ部分を形成することと、第2基板上に複数の第2トランジスタを形成することを含む第2I Cチップを形成することであって、第2トランジスタが第2画素センサ部分を形成することと、画素センサを形成するために第1画素センサ部分と第2画素センサ部分とが積層されて共に電気的に結合されるよう、第1I Cチップと第2I Cチップとを接合することであって、第1トランジスタは第1基板の半導体表面上にあり、第1I Cチップは受光素子の半導体表面に延伸するシャロートレンチアイソレーション（S T I）構造を有さないことを含む。

【発明の効果】

【0 0 0 6】

3チップ積層型C M O Sイメージセンサにおいて、イメージセンサの性能の大きなトレードオフなしに第1I CチップからS T I構造を省くことができる。第1I CチップでS T I構造を省くことにより、ドープされた分離領域の幅を狭くすることができ、よって受光素子の領域の占有をより少なくすることができる。つまり、これは第1I Cチップでの画素センサの微細化を高めることを可能とする。更に、受光素子は比較的大きく且つ第1I Cチップにあるが第2I Cチップにはないため、第1I Cチップでの画素センサの部分は画素センサの微細化を制限するものであり得る。よって、第1I Cチップでの画素センサの微細化は画素センサ全体の微細化の効果を奏する。

【図面の簡単な説明】

【0 0 0 7】

本発明の態様は、添付図面と共に以下の詳細な説明を読むことで最もよく理解される。

10

20

30

40

50

本業界の標準的な慣行に従い、様々な機能は縮尺どおりに描かれていないことに注意されたい。実際、添付図面に示される様々な機能の寸法は、説明を明確にするために任意に拡大又は縮小されている可能性がある。

【0008】

【図1】第1集積回路（IC）チップが受光素子を収容し、受光素子でシャロートレンチアイソレーション（STI）構造を有さない、積層型イメージセンサのいくつかの実施形態の概略図を表す。

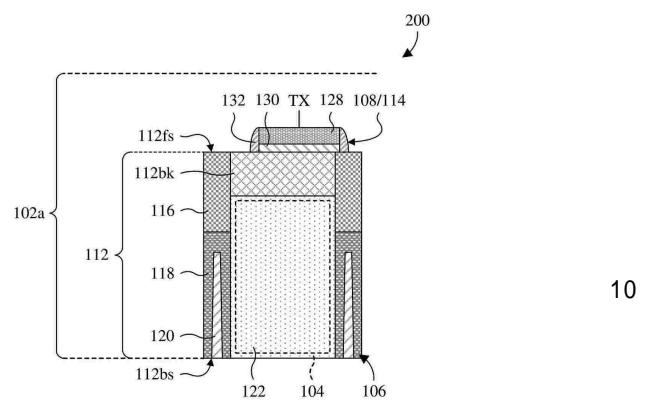

【図2】図1の第1ICチップのいくつかの実施形態のもう1つの断面図を表す。

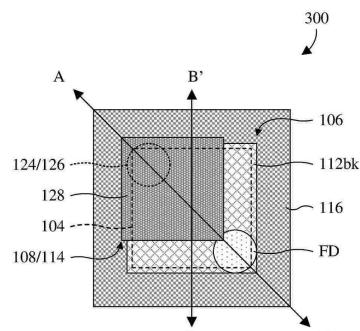

【図3】図1の第1ICチップのいくつかの実施形態の上部レイアウト図を表す。

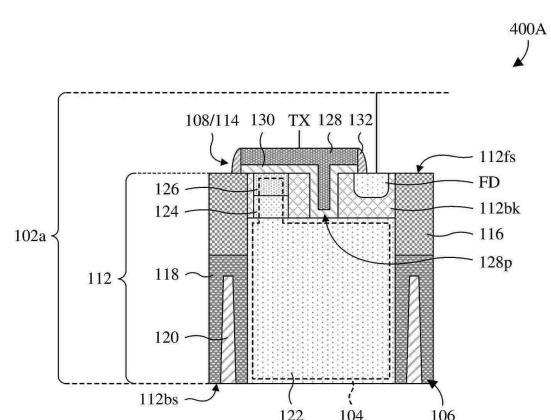

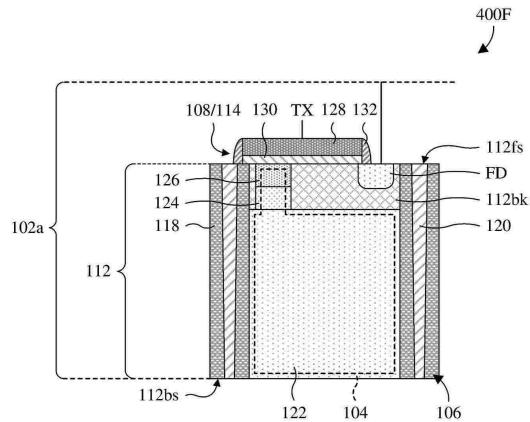

【図4】図1の第1ICチップのいくつかの代替的な実施形態の断面図を表す。

10

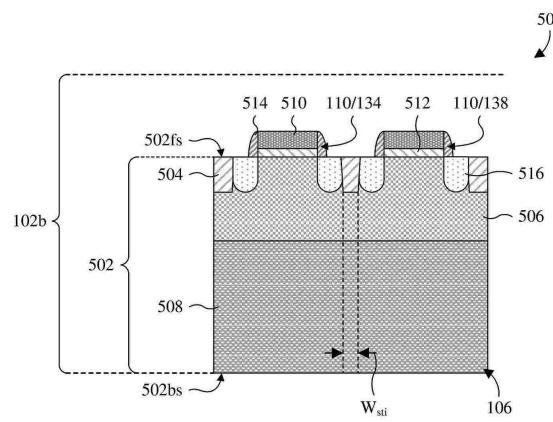

【図5】図1の第2ICチップのいくつかの実施形態の断面図を表す。

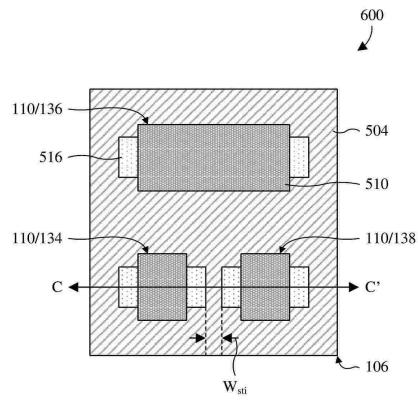

【図6】図5の第2ICチップのいくつかの実施形態の上部レイアウト図を表す。

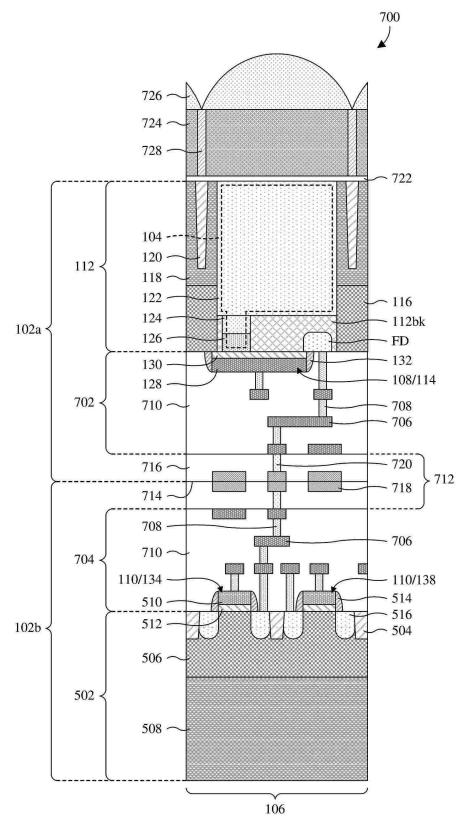

【図7】第2ICチップを断面で表した、図1の積層型イメージセンサのいくつかの実施形態の断面図を表す。

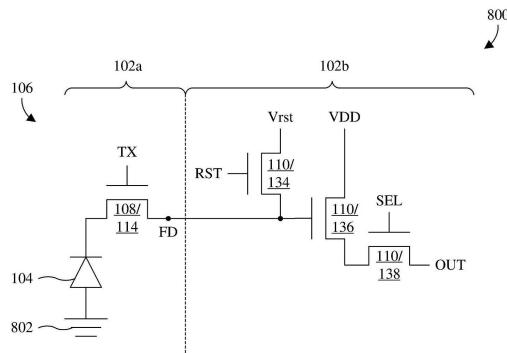

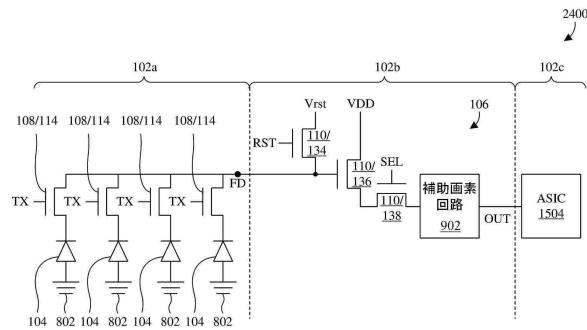

【図8】図1の積層型イメージセンサのいくつかの実施形態の回路図を表す。

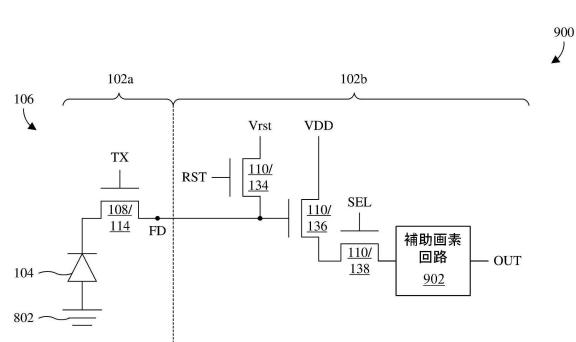

【図9】図1の積層型イメージセンサのいくつかの代替的な実施形態の回路図を表す。

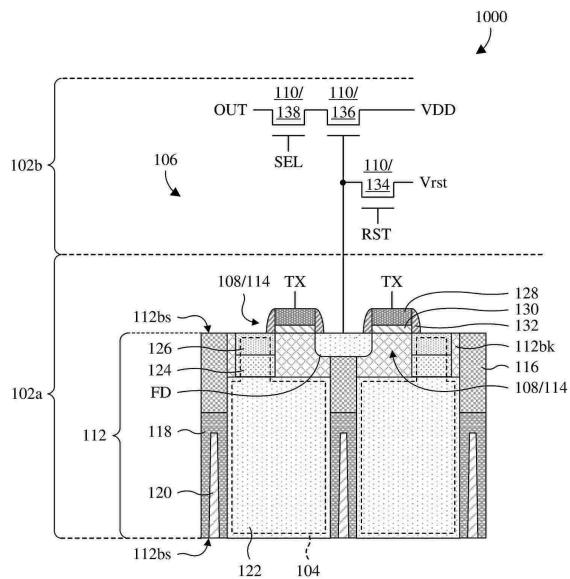

【図10】画素センサが複数の受光素子と複数の第1トランジスタとを含む、図1の積層型イメージセンサのいくつかの代替的な実施形態の概略図を表す。

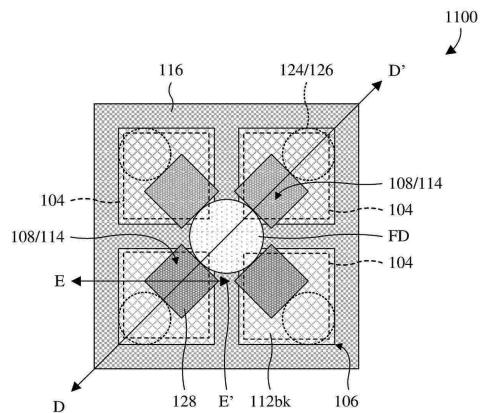

【図11】図10の第1ICチップのいくつかの実施形態の上部レイアウト図を表す。

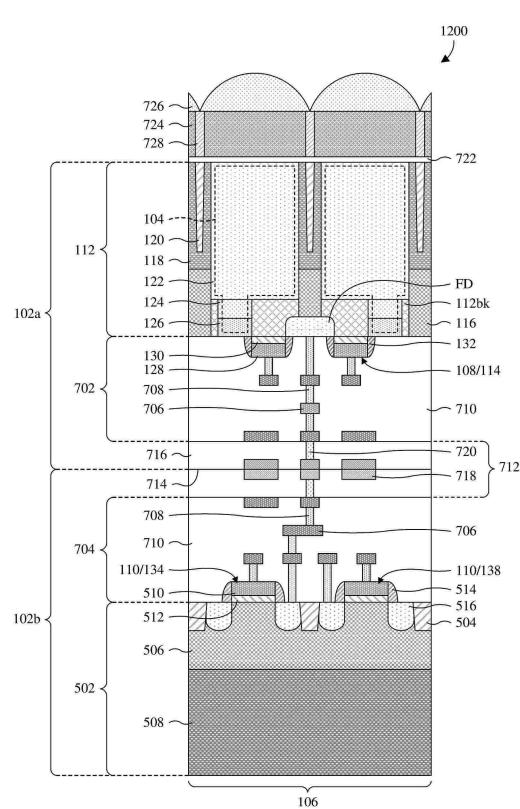

【図12】第2ICチップを断面で表した、図10の積層型イメージセンサのいくつかの実施形態の断面図を表す。

20

【図13】図10の積層型イメージセンサのいくつかの実施形態の回路図を表す。

【図14】図10の積層型イメージセンサのいくつかの代替的な実施形態の回路図を表す。

【図15】積層型イメージセンサが3つのICチップを含み、受光素子を収容するICチップがSTI構造を有さない、積層型イメージセンサのいくつかの実施形態のブロック図を表す。

【図16】図15A～図15Dの積層型イメージセンサのいくつかの代替的な実施形態のブロック図を表す。

【図17】図15A～図15Dの積層型イメージセンサの第1ICチップのいくつかの実施形態の上部レイアウト図を表す。

30

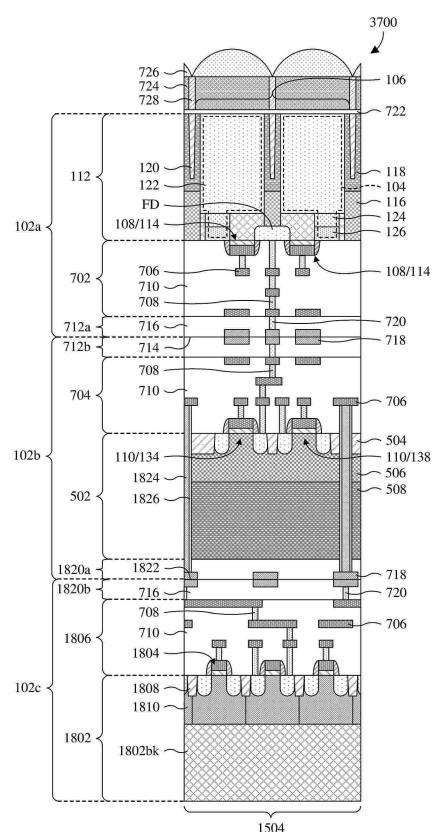

【図18】図15A～図15Dの積層型イメージセンサのいくつかの実施形態の断面図を表す。

【図19】図18の画素センサのいくつかの実施形態の回路図を表す。

【図20】図18の画素センサのいくつかの代替的な実施形態の回路図を表す。

【図21】図15A～図15Dの積層型イメージセンサの第1ICチップのいくつかの代替的な実施形態の上部レイアウト図を表す。

【図22】図15A～図15Dの積層型イメージセンサのいくつかの代替的な実施形態の断面図を表す。

【図23】図22の画素センサのいくつかの実施形態の回路図を表す。

【図24】図22の画素センサのいくつかの代替的な実施形態の回路図を表す。

40

【図25】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

【図26】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

【図27】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

【図28】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

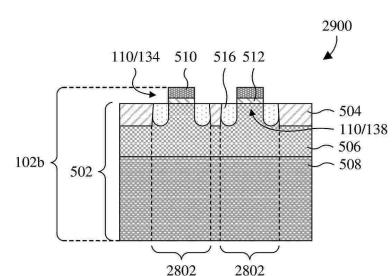

【図29】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

50

【図30】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

【図31】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

【図32】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

【図33】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

【図34】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

【図35】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

【図36】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

【図37】画素センサの受光素子を収容する第1ICチップでSTI構造を有さないイメージセンサを形成するための方法のいくつかの実施形態の一連の断面図を表す。

【図38】図25～図37の方法のいくつかの実施形態のプロック図を表す。

【発明を実施するための形態】

【0009】

本発明は、本発明の異なる特徴を実装するための多くの異なる実施形態又は実施例を提供する。本発明を単純化するため、要素及び配置の特定の実施例を以下に説明する。当然ながら、これらは例示であり、限定することを意図していない。例えば、以下の説明における、第2の特徴の上方又は第2の特徴上の第1の特徴の形成は、第1及び第2の特徴が直接的に接触して形成される実施形態を含んでよく、また第1及び第2の特徴が直接的に接触しないように、第1と第2の特徴の間に追加的な特徴が形成された実施形態であってもよい。加えて、本発明は様々な実施例において参照符号及び/又は文字を繰り返す可能性がある。この繰り返しは単純化及び明確化を目的としたものであり、それ自体は言及される様々な実施形態及び/又は構成の間の関係性を規定するものではない。

【0010】

更に、「下」、「下方」、「上方」、「上部」等といった空間的相対語は、図に表される1つの要素又は特徴の別の要素又は特徴に対する関係性を説明するための記述を容易にするために用いられ得る。空間的相対語は、図示された方向に加え、使用中又は動作中の装置の異なる方向を包含することを意図している。装置は他に方向付けられてもよく(90度又は他の方向に回転)、ここで使用される空間的相対記述語は同様にそのように解釈されてよい。

【0011】

積層型相補型金属酸化膜半導体(CMOS)イメージセンサは、積層された第1集積回路(IC)チップと第2ICチップとを含んでよい。第1ICチップは、グリッドパターンにて繰り返される画素センサを収容し、第2ICチップは、画素センサの各繰り返しで画素センサに電気的に結合された特定用途向けIC(ASIC)を収容する。画素センサは、第1ICチップに局在化する受光素子と複数のトランジスタとを含む。受光素子は、入射放射線に応じて電荷を蓄積するよう構成される。トランジスタは、蓄積された電荷の読み出しを容易にするよう構成された画素回路を含む。

【0012】

半導体製造業では、より低い製造コスト、より高いデバイス集積密度、より速い速度、より好ましい性能等を達成するため、CMOSイメージセンサの微細化を追求し続けている。しかし、画素センサのトランジスタは画素センサの微細化を制限する。このため、積層型CMOSイメージセンサは、更なる微細化を容易にするため、第1ICチップと、第2ICチップと、第3ICチップとを代わりに含んでよい。画素センサは第1及び第2ICチップの間で分けられ、第3ICチップはASICを収容する。画素センサの受光素子

10

20

30

40

50

と転送トランジスタは第1 I Cチップ上にあり、画素センサの残りのトランジスタは第2 I Cチップ上にある。

【0013】

2チップ積層型及び3チップ積層型の両方のCMOSイメージセンサは、画素センサのトランジスタを互いに分離するため、シャロートレンチアイソレーション(STI)構造を有する。しかし、STI構造形成の間の基板のエッチングは、受光素子が配置される基板に結晶損傷を引き起こす可能性がある。結晶損傷は、受光素子の性能を低下させる漏洩/暗電流を引き起こす可能性があり、よってドープウェルがSTI構造の周囲に形成される可能性がある。ドープウェルは結晶損傷をパッシベートして漏洩/暗電流を抑制する。しかし、漏洩/暗電流を十分に抑制するため、ドープウェルは幅が広くなる。このため、ドープウェルは受光素子のための領域サイズを大きく減少させ、よってイメージセンサの微細化を制限してしまう。

【0014】

本発明の様々な実施形態は、微細化が高められた積層型CMOSイメージセンサを対象とする。少なくとも上述した3チップ積層型CMOSイメージセンサにおいて、イメージセンサの性能への大きなトレードオフなしに第1 I CチップからSTI構造を省くことができることを理解されたい。第1 I CチップでSTI構造を省くことで、ドープされた分離領域は幅が狭くなり、よって受光素子の領域の占有をより少なくすることができる。。つまり、これは第1 I Cチップでの画素センサの微細化を高めることを可能とする。更に、受光素子は比較的大きく且つ第1 I Cチップにはあるが第2 I Cチップにはないため、第1 I Cチップでの画素センサの部分が画素センサの微細化を制限するものとなる。よって、第1 I Cチップでの画素センサの微細化は、画素センサ全体の微細化の効果を奏することができる。

【0015】

図1を参照し、第1 I Cチップ102aが受光素子104を収容し、受光素子104でSTI構造を有さない積層型CMOSイメージセンサのいくつかの実施形態の概略図100を提供する。以下でより詳細に説明するように、受光素子104でSTI構造を省くことは、受光素子104を含む画素センサ106の微細化を高めることを可能とする。

【0016】

積層型CMOSイメージセンサは、第1 I Cチップ102aと第2 I Cチップ102bとを含む。第1 I Cチップ102aと第2 I Cチップ102bは積層され、画素センサ106は第1 I Cチップ102aと第2 I Cチップ102bとにまたがる。画素センサ106は、第1 I Cチップ102aで受光素子104と第1トランジスタ108を含み、第2 I Cチップ102bで複数の第2トランジスタ110を更に含む。画素センサ106は、例えば、4トランジスタ(4T)CMOSアクティブピクセルセンサ(APS)等であつてよい。

【0017】

受光素子104は第1半導体基板112にあり、入射放射線に応じて電荷を蓄積するよう構成される。受光素子104は、例えば、PINダイオード等であつてよい。第1トランジスタ108は、第1半導体基板112の表側112fs上にあり、第1半導体基板112の表側112fs上により部分的に定義される。更に、第1トランジスタ108は転送トランジスタ114に対応し、電荷を受光素子104から浮遊拡散ノードFDへ転送するよう構成される。第2トランジスタ110は、転送トランジスタ114との連携により受光素子104の読み出しを容易にするよう構成される。

【0018】

例えば、画素間の電気的分離といった電気的分離を提供するため受光素子104を囲む分離構造として、分離構造は、シャローウェル116と、ディープウェル118と、ディープトレンチアイソレーション(DTI)構造120とを含む。シャローウェル116とディープウェル118は、第1半導体基板112のドープ領域に対応し、柱状プロファイルを有する。ただし、代替的な実施形態において、他の適切なプロファイルが可能である

10

20

30

40

50

。更に、シャローウェル 116 とディープウェル 118 は共通するドープ型を共有するが、異なるドーピングプロファイル及び / 又は濃度を有する。シャローウェル 116 及びディープウェル 118 の側壁は P N 接合を形成し、画素センサ 106 を隣接する画素センサ及び / 又は構造から電気的に分離する空乏領域となる。

#### 【0019】

D T I 構造 120 は誘電体材料であるか誘電体材料を含み、第 1 半導体基板 112 の裏側 112bs からディープウェル 118 内に延伸する。更に、D T I 構造 120 は、第 1 半導体基板 112 を部分的にのみ通って延伸する。誘電体材料は、例えば、high-k 誘電体材料、他の適切な誘電体材料、又は前記の組合せであるか、それを含んでよい。代替的な実施形態において、D T I 構造 120 は異なる高さを有する。いくつかの実施形態において、シャローウェル 116 の高さは、D T I 構造 120 の高さが増加するにつれて減少する。

#### 【0020】

上述したように、イメージセンサは受光素子 104 で S T I 構造を有さない。S T I 構造は、例えば、第 1 半導体基板 112 の領域間の電気的な分離を提供するため第 1 半導体基板 112 の表側 112fs に延伸する、酸化ケイ素等の誘電体構造に対応してよい。S T I 構造を有さない分離構造は、性能の大きなトレードオフなしに第 1 I C チップ 102a での画素センサ 106 の部分の電気的分離を提供するのに十分であることを理解されたい。上述したように、分離構造は、シャローウェル 116 と、ディープウェル 118 と、D T I 構造 120 とを含む。

#### 【0021】

S T I 構造が第 1 半導体基板 112 の表側 112fs 内に延伸する場合、S T I 構造形成の間の基板のエッチングは、結晶損傷を引き起こす可能性がある。結晶損傷は、受光素子の性能を低下させる漏洩 / 暗電流を引き起こす可能性がある。シャローウェル 116 が S T I 構造での漏洩 / 暗電流を抑制するため S T I 構造の周囲に形成されるてよい。しかし、漏洩 / 暗電流を十分に抑制するため、シャローウェル 116 は幅が広くなる。この広い幅は受光素子 104 のための領域サイズを減少させ、よって微細化を制限してしまう。

#### 【0022】

S T I 構造を省くことで、シャローウェル 116 は幅が狭くなり、よって占有する受光素子 104 の領域が少ない。つまり、これは受光素子 104 のフルウェルキャパシティ (FWC) を拡大し、受光素子 104 からの電荷転送を高め、これは第 1 I C チップ 102a での画素センサ 106 の微細化を高めることを可能とする。

#### 【0023】

受光素子 104 は比較的大きく且つ第 1 I C チップ 102a にあって第 2 I C チップ 102b にはないため、第 1 I C チップ 102a での画素センサ 106 の部分が、画素センサ 106 の微細化を制限するものとなる。よって、第 1 I C チップ 102a での画素センサ 106 の微細化は、画素センサ 106 全体の微細化の効果を奏することができる。更に、第 2 I C チップ 102b での画素センサ 106 の部分は空間に余裕がある可能性がある。第 2 I C チップ 102b での空間の余裕により、S T I 構造は画素センサ 106 の微細化を制限することなく第 2 I C チップ 102b で用いられることができる。これは、第 2 I C チップ 102b での電気的分離を高める。

#### 【0024】

続けて図 1 を参照し、第 1 半導体基板 112 は、受光素子 104 を形成する複数のドープ領域を含む。ドープ領域は、第 1 半導体基板 112 の裏側 112bs で第 1 ドープ領域 122 を含み、第 1 半導体基板 112 の表側 112fs で第 2 ドープ領域 124 と第 1 ドープ領域 122 を覆う第 3 ドープ領域 126 とを含む。

#### 【0025】

第 1 ドープ領域 122 と第 2 ドープ領域 124 は第 1 のドープ型を共有し、第 3 ドープ領域 126 はシャローウェル 116 及びディープウェル 118 と第 2 のドープ型を共有する。第 1 のドープ型と第 2 のドープ型は逆である。例えば、第 1 のドープ型は n 型であつ

10

20

30

40

50

てよく第2のドープ型はp型であってよい、又はその逆である。第3ドープ領域126は、第2ドープ領域124により第1ドープ領域122から分離され、第1半導体基板112のバルク領域112b kは第2ドープ領域124と第3ドープ領域126を囲む。いくつかの実施形態において、バルク領域112b kは第2のドープ型を有するか、ドーピングされない。

#### 【0026】

浮遊拡散ノードFDは第1半導体基板112のバルク領域112b kにあり、第1半導体基板112のドープ領域に対応する。更に、浮遊拡散ノードFDは第1のドープ型を有する。よって、浮遊拡散ノードFDは第1ドープ領域122及び第2ドープ領域124とドープ型を共有する。

10

#### 【0027】

受光素子104の動作の間、入射放射線に応じて電荷が第1ドープ領域122と第2ドープ領域124に蓄積される。いくつかの実施形態において、受光素子104は電荷蓄積の間、逆バイアスがかけられる。更に、転送トランジスタ114の動作の間、転送トランジスタ114は受光素子104で蓄積された電荷を浮遊拡散ノードFDへ選択的に転送する。

#### 【0028】

転送トランジスタ114は転送信号TXによりゲートされ、第1ゲート電極128と、第1ゲート誘電体層130と、第1側壁スペーサ132と、第1ソース／ドレイン領域の対とを含む。第1ゲート電極128と第1ゲート誘電体層130はゲートスタックを形成し、そこでは第1ゲート電極128が第1ゲート誘電体層130により第1半導体基板112から分離される。第1側壁スペーサ132は、ゲートスタックの側壁上にある。第1ソース／ドレイン領域のうちの1つは浮遊拡散ノードFDにより形成され、第1ソース／ドレイン領域のうちのもう1つは第1ドープ領域122と第2ドープ領域124により集合的に形成される。ソース／ドレイン領域は、文脈によって、ソース又はドレインを個別又は集合的に指してよい。

20

#### 【0029】

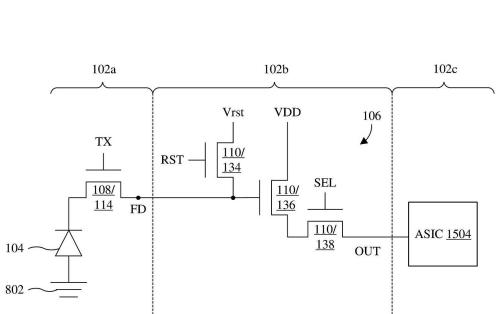

第2トランジスタ110は、リセットトランジスタ134と、ソースフォロアトランジスタ136と、選択トランジスタ138とを含む。リセットトランジスタ134はリセット信号RSTによりゲートされ、浮遊拡散ノードFDから、リセット電圧V<sub>rst</sub>が印加される端子に電気的に結合される。リセットトランジスタ134は、浮遊拡散ノードFDをリセット電圧V<sub>rst</sub>に電気的に結合することにより、浮遊拡散ノードFDをリセット電圧V<sub>rst</sub>にリセットするよう構成される。更に、転送トランジスタ114がON状態にあるとき、このリセットトランジスタ134による電気的な結合は、受光素子104をピンニング電圧にリセットしてもよく、さもなくば受光素子104を既知の状態にリセットしてよい。

30

#### 【0030】

ソースフォロアトランジスタ136は浮遊拡散ノードFDでの電荷によりゲートされ、選択トランジスタ138は選択信号SELによりゲートされる。更に、ソースフォロアトランジスタ136と選択トランジスタ138は、電源電圧VDDが印加される端子から出力端子OUTへ直列に電気的に結合される。ソースフォロアトランジスタ136は、浮遊拡散ノードFDでの電圧をバッファリング及び増幅するよう構成される。選択トランジスタ138は、バッファリング及び増幅された電圧をソースフォロアトランジスタ136から出力端OUTへ選択的に通過させるよう構成される。

40

#### 【0031】

いくつかの実施形態において、第1トランジスタ108と第2トランジスタ110は、金属酸化膜半導体電界効果トランジスタ(MOSFET)、フィン電界効果トランジスタ(FinFET)、全周ゲート電界効果トランジスタ(GAAFET)、ナノシート電界効果トランジスタ等、又はこれらの任意の組合せである。いくつかの実施形態において、第1半導体基板112は、シリコン、ゲルマニウム等、又はこれらの任意の組合せのバ

50

ルク基板、シリコン・オン・インシュレータ（S O I）基板、又は他の適切なタイプの半導体基板であるか、それを含む。

【 0 0 3 2 】

いくつかの実施形態において、S T I構造が省かれるため、イメージセンサは狭い画素ピッチを有することができる。そのような狭いピッチは、例えば約0.7マイクロメートル未満、約0.5マイクロメートル等の画素ピッチであってよい、及び／又は、例えば約0.5～0.7マイクロメートル等の画素ピッチであってよい。

【 0 0 3 3 】

いくつかの実施形態において、S T I構造が省かれるため、第1半導体基板112の頂面は、シャローウェル116の第1側壁から、第1側壁と反対側のシャローウェル116の第2側壁まで継続して、平面又は平坦なプロファイル、又は実質的に平面又は平坦なプロファイルを有する。実質的に平面又は平坦なプロファイルは、例えば両方共に10%、5%、1%、又は他の適切なパーセンテージ内の平均上昇である最高高さ及び最低高さを有してよい。更に、いくつかの実施形態において、S T I構造が省かれるため、第1半導体基板112の頂面は、第1側壁から第2側壁まで継続的に、第1半導体基板112のドープ領域（例えば、ドープ領域の頂面）と面一である。少なくともいくつかのそのような実施形態において、頂面は第1側壁から第2側壁まで継続して共通した高さである。ドープ領域は、例えば、浮遊拡散ノードF D、第3ドープ領域126、他の適切な領域、又はこれらの任意の組合せである。共通した高さは、例えば、第1ゲート誘電体層130又は第1側壁スペーサ132が直接第1半導体基板112に接触する高さであってよい。

10

【 0 0 3 4 】

いくつかの実施形態において、第1側壁は受光素子104と面しており、第2側面は受光素子104とは逆を向く。そのような実施形態において、第1側壁と第2側壁は画素センサ106の共通する側上にある。他の実施形態において、第1側壁は第1の方向において受光素子104から逆を向き、第2側壁は第1の方向とは逆の第2の方向に受光素子104から逆を向く。そのような他の実施形態において、第1側壁と第2側壁は画素センサ106の反対側上にある。

20

【 0 0 3 5 】

いくつかの実施形態において、S T I構造が省かれるため、第1半導体基板112は、D T I構造120からドープ領域を伴う高さレベル（例えば、ドープ領域の頂面）まで垂直方向に直線的に連続している。上述したように、ドープ領域は、例えば、浮遊拡散ノードF D、第3ドープ領域126、又はこれらの任意の組合せであってよい。更に、いくつかの実施形態において、S T I構造が省かれるため、第1半導体基板112は、D T I構造120から、第1ゲート誘電体層130又は第1側壁スペーサ132が直接第1半導体基板112に接触する高さレベルまで、垂直方向に直線的に連続している。垂直方向は、例えば、第1半導体基板112の頂面又は底面に直交するか、第1ゲート電極128の頂面又は底面に直交する等であってよい。

30

【 0 0 3 6 】

いくつかの実施形態において、S T I構造が省かれるため、シャローウェル116とディープウェル118は共通する幅を共有する。いくつかのそのような実施形態において、共通する幅は、シャローウェル116とディープウェル118とが直接接触する界面での幅である。S T I構造が存在する場合、S T I構造での漏洩／暗電流を抑制するためシャローウェル116の幅はディープウェル118の幅よりも大きくなる。

40

【 0 0 3 7 】

いくつかの実施形態において、S T I構造は、画素センサ106及び／又は受光素子104にてであるかに関わらず、第1半導体基板112全体にわたって省かれる。少なくともいくつかのそのような実施形態において、表側112f sでの第1半導体基板112の表面（例えば、表側表面）は、第1半導体基板112全体にわたって、平面又は平坦なプロファイル、又は実質的に平面又は平坦なプロファイルを有してよい。実質的に平面又は平坦なプロファイルは、例えば両方共に10%、5%、1%、又は他の適切なパーセンテージ内の平均上昇である最高高さ及び最低高さを有してよい。

50

ージ内の平均上昇である最高高さ及び最低高さを有してよい。

【0038】

図1に見られるように、第1ICチップ102aは断面で表されている。図2は、第1ICチップ102aのいくつかの実施形態のもう1つの断面図200を表し、浮遊拡散ノードFDは断面図200の外側にある。

【0039】

図3を参照し、図1の第1ICチップ102aのいくつかの実施形態の上部レイアウト図300を提供する。図1における第1ICチップ102aの図示された部分は、図3におけるA-A'線に沿った断面図に対応する。更に、図2の断面図200は図3のB-B'線に沿って得られるものである。

10

【0040】

シャローウェル116は、受光素子104を他の受光素子及び/又は構造から分離するため、受光素子104の周囲の閉環状経路に延伸する。更に、第1ゲート電極128と浮遊拡散ノードFDは受光素子104の対角線上に対向する角にある。代替的な実施形態において、シャローウェル116は他の適切な形状を有する、及び/又は、第1ゲート電極128、浮遊拡散ノードFD、及び受光素子104の相対的配置は異なる。

【0041】

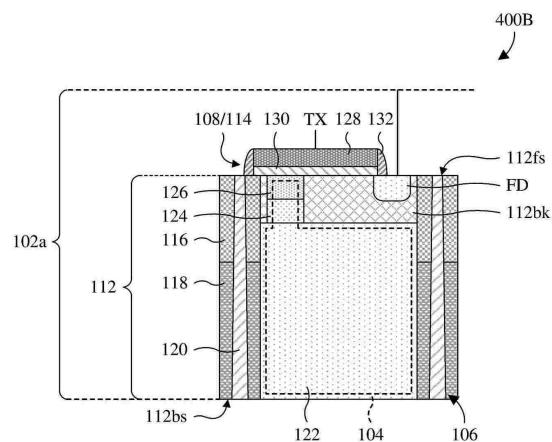

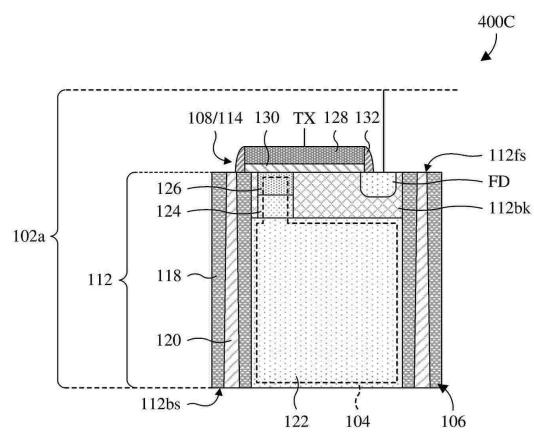

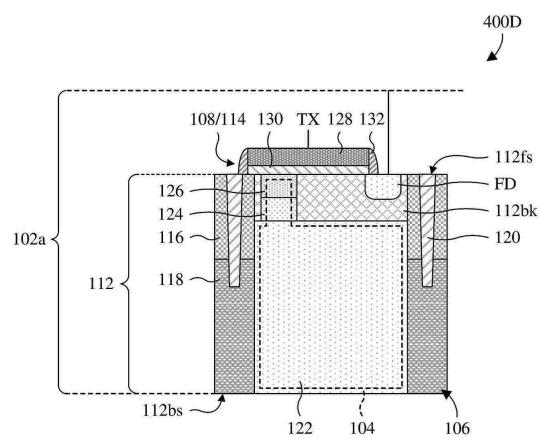

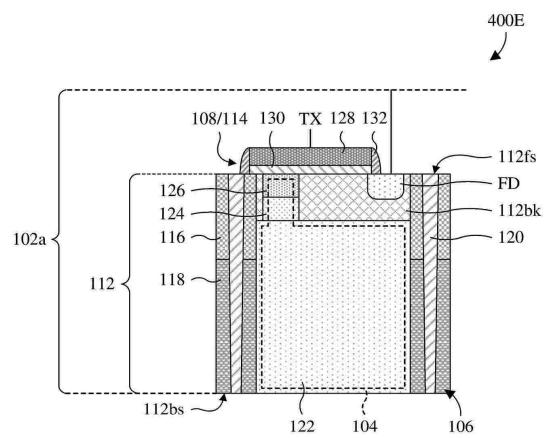

図1に見られるように、第1ICチップ102aは断面で表されている。図4A～図4Fは、図1の第1ICチップ102aの実施形態を置き換えることのできる、第1ICチップ102aのいくつかの代替的な実施形態の断面図400A～400Fを表す。

20

【0042】

図4Aにおいて、第1ゲート電極128は、第1半導体基板112内に突出する突出部128pを有する。

【0043】

図4Bにおいて、DTI構造120は第1半導体基板112を完全に貫通するよう延伸する。図4Cにおいて、DTI構造120は図4Bにおけるものと同様であるが、シャローウェル116が更に省かれている。

【0044】

図4Dにおいて、DTI構造120は、前述した実施形態のような半導体基板112の裏側112bs内ではなく、半導体基板112の表側112fs内に延伸する。これは、表側112fsから裏側112bsへ向かって減少するDTI構造120の幅により表される。図4Eにおいて、DTI構造120が第1半導体基板112を完全に貫通するよう延伸することを除き、DTI構造120は図4Dにおけるものと同様である。図4Fにおいて、DTI構造120は図4Eにおけるものと同様であるが、シャローウェル116が更に省かれている。

30

【0045】

図1に見られるように、第2ICチップ102bが回路図により表されている。図5は、リセットトランジスタ134及び選択トランジスタ138での第2ICチップ102bのいくつかの実施形態の断面図500を表す。リセットトランジスタ134と選択トランジスタ138を含む第2トランジスタ110は、第2半導体基板502の表側502fs上にあり、STI構造504により互いに分離されている。STI構造504は表側502fs内に延伸し、酸化ケイ素及び/又は他の適切な誘電体材料であるか、それを含んでよい。これに対し、第1ICチップ102aは上述したようにSTI構造を有さない。

40

【0046】

いくつかの実施形態において、直接リセットトランジスタ134と選択トランジスタ138との間にあるSTI構造504の幅Wst1は、約60～80ナノメートル、約60～70ナノメートル、約70～80ナノメートル、又は他の適切な値である。幅Wst1が過度に狭い場合（例えば、60ナノメートル未満）、トランジスタ間漏洩が起こる可能性がある。幅Wst1が過度に広い場合（例えば、80ナノメートルよりも広い）、画素センサ106のサイズが、利点がほぼ又は全くなしに大きくなってしまう。

50

## 【0047】

第2半導体基板502は、シャローウェル506とディープウェル508とを含む。シャローウェル506は、第2半導体基板502の表側502fsにあり、ディープウェル508は表側502fsとは反対側の第2半導体基板502の裏側502bsでシャローウェル506の下にある。シャローウェル506とディープウェル508はドープ型を共有するが、異なるドープ濃度及び/又はプロファイルを有する。例えば、シャローウェル506とディープウェル508は、n型又はp型であってよい。更に、ディープウェル508はシャローウェル506によりSTI構造504から間隔が開けられている。第2半導体基板502は、シリコン、ゲルマニウム等、又はこれらの任意の組合せのバルク基板、SOI基板、又は他の適切なタイプの半導体基板であるか、それを含む。

10

## 【0048】

第2トランジスタ110は、個別の第2ゲート電極510と、個別の第2ゲート誘電体層512と、個別の第2側壁スペーサ514と、個別の第2ソース/ドレイン領域516の対とを含む。第2ゲート電極510は、それぞれ第2ゲート誘電体層512と積層され、第2ゲート誘電体層512は第2ゲート電極510を第2半導体基板502から分離する。

## 【0049】

第2ソース/ドレイン領域516は第2半導体基板502内にあり、各第2ゲート電極510は第2ソース/ドレイン領域516のそれぞれの対の間にあり。第2ソース/ドレイン領域516は、第2半導体基板502のドープ領域に対応する。更に、第2ソース/ドレイン領域516はシャローウェル506とは逆のドープ型を有する。例えば、第2ソース/ドレイン領域516はn型であってよく、シャローウェル506はp型であってよい、又はその逆である。ソース/ドレイン領域は、文脈によって、ソース又はドレインを個別又は集合的に指してよい。

20

## 【0050】

図6を参照し、図5の第2ICチップのいくつかの実施形態の上部レイアウト図600を提供する。図5の断面図500は、例えばC-C'線に沿って得ることができる。リセットトランジスタ134とソースフォロアトランジスタ136と選択トランジスタ138とを含む第2トランジスタ110は、STI構造504により互いに分離される。STI構造504は、第2トランジスタ110の周囲で個別に閉経路に延伸する。

30

## 【0051】

図7を参照し、図1のイメージセンサのいくつかの実施形態の断面図700を提供し、第2ICチップ102bを断面図で表す。第2ICチップ102bの断面図は、例えば図5の断面図500に対応してよい。更に、第1ICチップ102aと第2ICチップ102bは、対応する相互接続構造により共に電気的に結合される。

## 【0052】

第1ICチップ102aは、第1半導体基板112の表側で第1半導体基板112の下にある第1相互接続構造702を含む。更に、第1相互接続構造702は第1トランジスタ108に電気的に結合される。第2ICチップ102bは第1ICチップ102aの下にあり、第2相互接続構造704を含む。第2相互接続構造704は、第2半導体基板502の表側で第2半導体基板502の上にある。更に、第2半導体基板502は第2トランジスタ110に電気的に結合される。

40

## 【0053】

第1相互接続構造702と第2相互接続構造704は、対応する相互接続誘電体層710において、複数のワイヤ706と複数のビア708とを含む。ワイヤ706とビア708は導電性であり、導電経路を定義するため交互に積層される複数のワイヤレベルと複数のビアレベルとにそれぞれグループ化される。いくつかの実施形態において、ワイヤ706及びビア708は、銅、アルミニウム、タンタル、チタン等、又はこれらの任意の組合せであるか、それを含む。

## 【0054】

50

第1接合構造712が第1ICチップ102aと第2ICチップ102bとの間にあり、第1接合界面714での第1ICチップ102aと第2ICチップ102bの接合を容易にする。そのような接合は、例えば第1接合界面714での金属間接合及び誘電体間接合の組合せを含んでよい。

【0055】

第1接合構造712は、複数の接合誘電体層716と、複数の接合パッド718と、複数の接合ビア720とを含む。接合誘電体層716は、第1ICチップ102a及び第2ICチップ102bに個別であり、接合界面714で直接接触する。同様に、接合パッド718は第1ICチップ102a及び第2ICチップ102bに個別であり、接合界面714で直接接触する。更に、接合パッド718は接合誘電体層716内にそれぞれ嵌め込まれる。接合ビア720は、それぞれ接合誘電体層716内にあり、それぞれ接合パッド718から第1相互接続構造702、第2相互接続構造704へと延伸する。接合パッド718及び接合ビア720は導電性である。例えば、接合パッド718及び接合ビア720は、例えば、銅、アルミニウム、タンタル、チタン等、又はこれらの任意の組合せであるか、それを含んでよい。

【0056】

裏側パッシベーション層722、複数のカラーフィルタ724、及び複数のマイクロレンズ726が、第1半導体基板112の裏側で第1半導体基板112の上にある。裏側パッシベーション層722は誘電体であり、放射線に対して透明である。カラーフィルタ724は裏側パッシベーション層722の上にあり、マイクロレンズ726はそれぞれカラーフィルタ724の上にある。各カラーフィルタ724は、第2のカラー波長を遮断しつつ第1のカラー波長を透過するよう構成される。各マイクロレンズ726は、量子効率を向上させるため、入射放射線を対応する受光素子（例えば受光素子104）上に集束させるよう構成される。

【0057】

グリッド構造728がマイクロレンズ726を互いに分離させ、量子効率を向上させるため、グリッド構造の側壁に入射した放射線を反射する。グリッド構造728は、例えば、金属、誘電体材料等、又はこれらの任意の組合せであるか、それを含んでよい。

【0058】

図8を参照し、図1のイメージセンサのいくつかの実施形態の回路図800を提供する。第2ICチップ102bでの回路図800の部分は、図1に関して説明したものと同様である。第1ICチップ102aでの回路図800の部分では、受光素子104のカソードが転送トランジスタ114のソース／ドレイン領域に電気的に結合される。更に、受光素子104のアノードは接地802が適用される端子に電気的に結合される。アノードは、例えば、図7において、バルク領域112bk、シャローウェル116、ディープウェル118、第3ドープ領域126等、又はこれらの任意の組合せにより形成されてよい。カソードは、例えば、図7において、第1ドープ領域122、第2ドープ領域124等により形成されてよい。

【0059】

いくつかの実施形態において、画素センサ106は第1ICチップ102aにおいて1つのみのトランジスタ（例えば第1トランジスタ108）を有し、第2ICチップ102bにおいて3つのみ又はそれ以上のトランジスタ（例えば第2トランジスタ110）を有する。他の実施形態において、画素センサ106は第1ICチップ102aにおいて他の適切な数のトランジスタを有する、及び／又は、第2ICチップ102bにおいて他の適切な数のトランジスタを有する。

【0060】

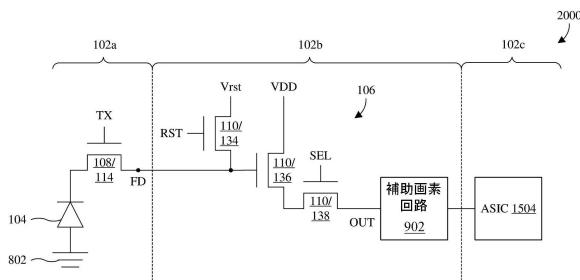

図9を参照し、図1のイメージセンサのいくつかの代替的な実施形態の回路図900を提供する。回路図900は、画素センサ106が第2ICチップ102bで補助画素回路902を更に含むことを除き、図8の回路図800と同様である。補助画素回路902は、選択トランジスタ138と画素センサ106の出力端OUTとの間に電気的に結合され

10

20

30

40

50

る。更に、補助画素回路 902 はトランジスタ等により形成される。補助画素回路 902 は、選択トランジスタ 138 からの信号を出力端 OUT へ渡す前に、該信号に追加的な処理を実行するよう構成される。そのような追加的な処理は、例えばノイズフィルタリング等を含んでよい。

#### 【0061】

受光素子 104 は比較的大きく且つ第 1 IC チップ 102a にあって第 2 IC チップ 102b にはないため、第 1 IC チップ 102a での画素センサ 106 の部分が、画素センサ 106 の微細化を制限するものとなる。このため、第 2 IC チップ 102b での画素センサ 106 の部分は、画素センサ 106 を大きくすることなく補助画素回路 902 の画素センサ 106 への統合を可能とする空間を有することができる。

10

#### 【0062】

図 10 を参照し、図 1 のイメージセンサのいくつかの代替的な実施形態の概略図 1000 を提供し、画素センサ 106 は複数の受光素子 104 と複数の第 1 トランジスタ 108 とを含む。受光素子 104 は第 1 トランジスタ 108 と一対一で対にされ、受光素子 - トランジスタの対は浮遊拡散ノード FD の周囲に配置される副画素を形成する。更に、各第 1 トランジスタ 108 は、浮遊拡散ノード FD を共有する転送トランジスタ 114 であり、対応する受光素子 104 から蓄積された電荷を浮遊拡散ノード FD へと転送するよう構成される。各受光素子 - トランジスタの対について、受光素子 104 と転送トランジスタ 114 は、図 1 に関して説明したそれらの対応物と同様である。

20

#### 【0063】

図 11 を参照し、図 10 の第 1 IC チップ 102a のいくつかの実施形態の上部レイアウト図 1100 を提供する。図 10 における第 1 IC チップ 102a の図示した部分は、図 11 の D - D' 線に沿って得られる断面図に対応する。画素センサ 106 は象限に分割される。象限は、浮遊拡散ノード FD の周囲に配置され、それぞれが図 10 に関して説明した副画素を含む。代替的な実施形態において、画素センサ 106 はより多くの又はより少ない副画素を有してよい。上述したように、副画素は受光素子 - トランジスタの対に対応する。

20

#### 【0064】

図 2 を図 1 におけるイメージセンサの実施形態について説明したが、図 2 は図 10 におけるイメージセンサの実施形態にも対応することができる。このように、図 2 の断面図 200 は図 11 の E - E' 線に沿って得ることができる。更に、図 4A ~ 図 4F は図 1 におけるイメージセンサの実施形態の変形を説明しているが、該変形は図 10 におけるイメージセンサの実施形態にも適用することができる。

30

#### 【0065】

図 12 を参照し、図 10 のイメージセンサのいくつかの実施形態の断面図 1200 を提供し、第 2 IC チップ 102b を断面で表す。第 2 IC チップ 102b の断面は、例えば図 5 の断面図 500 に対応することができる。第 1 IC チップ 102a と第 2 IC チップ 102b は、第 1 相互接続構造 702 及び第 2 相互接続構造 704 と第 1 接合構造 712 とにより、互いに電気的に結合される。更に、裏側パッシベーション層 722、カラーフィルタ 724、マイクロレンズ 726、及びグリッド構造 728 が第 1 IC チップ 102a の上にある。

40

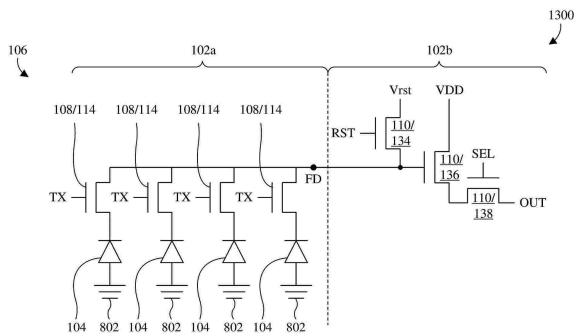

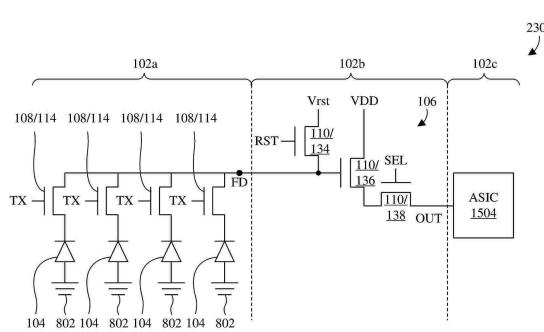

#### 【0066】

図 13 を参照し、図 10 のイメージセンサのいくつかの実施形態の回路図 1300 を提供する。第 2 IC チップ 102b での回路図 1300 の部分は、図 1 と図 10 に関して説明したものと同様である。第 1 IC チップ 102a での回路図 1300 の部分では、画素センサ 106 は複数の受光素子 104 と複数の第 1 トランジスタ 108 とを含む。受光素子 104 は第 1 トランジスタ 108 と一対一で対にされる。更に、受光素子 - トランジスタの対は、浮遊拡散ノード FD を共有する副画素を形成し、各受光素子 - トランジスタの対は図 8 に関して説明したように浮遊拡散ノード FD に結合される。

#### 【0067】

50

いくつかの実施形態において、画素センサ 106 は、第 1 I C チップ 102a において画素センサ 106 が有する受光素子の総数と同一である、第 1 I C チップ 102a におけるトランジスタの総数を有する。例えば、画素センサ 106 は、第 1 I C チップ 102a においてトランジスタ（例えば第 1 トランジスタ 108）を 4 つのみ有し、第 2 I C チップ 102b において受光素子（例えば受光素子 104）を 4 つのみ有する。いくつかの実施形態において、画素センサ 106 は第 2 I C チップ 102b において 3 つのみ又はそれ以上のトランジスタ（例えば第 2 トランジスタ 110）を有する。

#### 【0068】

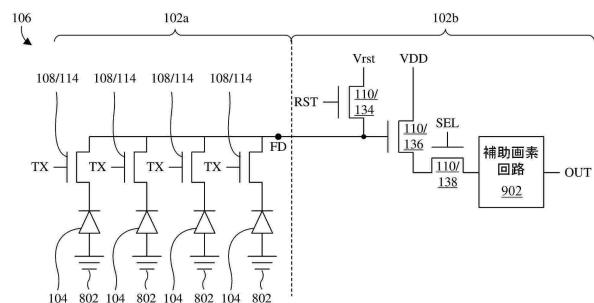

図 14 を参照し、図 10 のイメージセンサのいくつかの代替的な実施形態の回路図 1400 を提供する。回路図 1400 は、画素センサ 106 が第 2 I C チップ 102b で補助画素回路 902 を更に含むことを除き、図 13 の回路図で説明したものと同様である。補助画素回路 902 は、選択トランジスタ 138 と画素センサ 106 の出力端 OUT との間に電気的に結合される。更に、補助画素回路 902 は図 9 に関して説明したものと同様である。

10

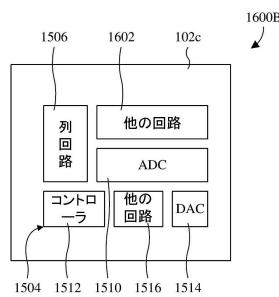

#### 【0069】

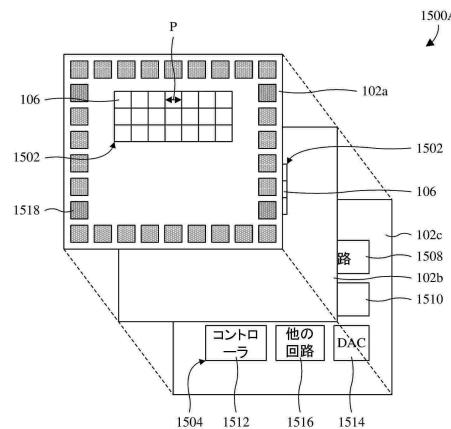

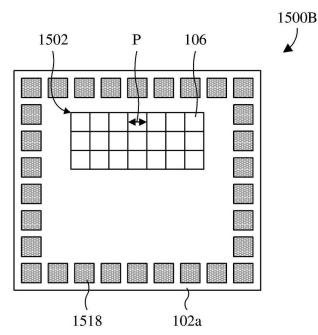

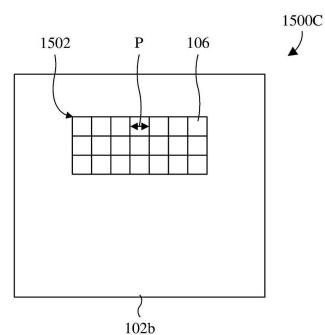

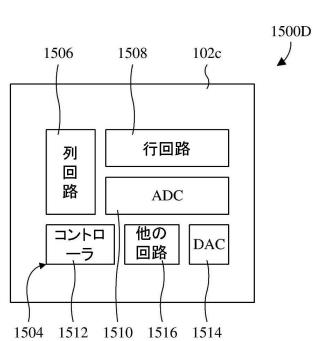

図 15A～図 15D を参照し、イメージセンサのいくつかの実施形態のブロック図 1500A～1500D を提供し、イメージセンサは、第 1 I C チップ 102a と第 2 I C チップ 102b と第 3 I C チップ 102c とを含む。図 15A は、イメージセンサの分解図 1500A を表し、図 15B～図 15D はそれぞれ、第 1 I C チップ 102a、第 2 I C チップ 102b、第 3 I C チップ 102c のブロック図 1500B～ブロック図 1500D を表す。

20

#### 【0070】

第 1 I C チップ 102a は第 2 I C チップ 102b の上にあり、画素アレイ 1502 が第 1 I C チップ 102a と第 2 I C チップ 102b とにまたがる。画素アレイ 1502 は、複数の行と複数の列に配置された複数の画素センサ 106 を含む。例えば、画素アレイ 1502 は、3 つの列と 7 つの行を有してよい。いくつかの実施形態において、画素センサ 106 のピッチ P は 0.7 マイクロメートル未満、0.5 マイクロメートル等、及び／又は、約 0.5～0.7 マイクロメートル、約 0.3～0.5 マイクロメートル等である。各画素センサ 106 は、図 1～3、4A～4F、5～14 のうちの任意の 1 つ又は組合せに関して図示及び説明したものと同様である。よって、第 1 I C チップ 102a は画素センサ 106 の微細化を高めることを可能とするため画素センサ 106 で STI 構造を有さず、第 2 I C チップ 102b はトランジスタ間の向上された電気的分離のため STI 構造を有する。

30

#### 【0071】

第 3 I C チップ 102c は第 2 I C チップ 102b の下にあり、イメージシグナル処理 (ISP) のための特定用途向け集積回路 (ASIC) 1504 を収容する。ASIC 1504 は、例えば、列回路 1506、行回路 1508、アナログ - デジタル変換回路 (ADC) 1510、コントローラ回路 1512、デジタル - アナログ変換回路 (DAC) 1514、他の適切な回路 1516 等、又はこれらの任意の組合せを含んでよい。更に、ASIC 1504 は、例えば、入出力 (I/O) デバイス、コアデバイス等、又はこれらの任意の組合せを含む論理デバイスにより形成されてよい。

40

#### 【0072】

複数のパッド 1518 は、互いに間隔が空けられて、画素アレイ 1502 を囲むため環状パターンにて第 1 I C チップ 102a の周辺に沿っている。パッド 1518 は導電性であり、イメージセンサ外部から画素アレイ 1502 及び ASIC 1504 への電気的な結合を提供する。パッド 1518 から画素アレイ 1502 及び ASIC 1504 への電気的な結合は、例えば、基板貫通ビア (TSV)、相互接続構造、接合構造等により達成されてよく、それらの例は後述する。

#### 【0073】

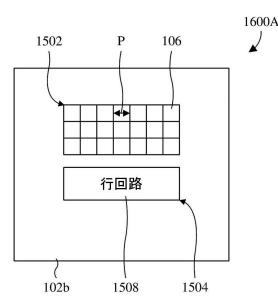

図 16A と図 16B を参照し、図 15A～図 15D のイメージセンサのいくつかの代替

50

的な実施形態のブロック図 1600A、1600B を提供し、ASIC1504 は第 2 IC チップ 102b と第 3 IC チップ 102c とにまたがる。図 16A と図 16B は、図 15A ~ 図 15D における第 2 IC チップ 102b と第 3 IC チップ 102c の代替に対応する。第 1 IC チップ 102a はこれらの代替的な実施形態において変化はない。

#### 【0074】

行回路 1508 は第 3 IC チップ 102c ではなく第 2 IC チップ 102b にある。代替的な実施形態において、1つ以上の列回路 1506、コントローラ回路 1512 等、又はこれらの任意の組合せが、第 3 IC チップ 102c ではなく第 2 IC チップ 102b に追加的に又は代替的にあってよい。ASIC1504 を第 2 IC チップ 102b と第 3 IC チップ 102c にわたって広げることで、第 2 IC チップ 102b での未使用空間を使用することが可能となり、イメージセンサにより多くの回路を有することを可能とする。例えば、イメージセンサは第 3 IC チップ 102c でもう1つの回路 1602 を含んでよい。

10

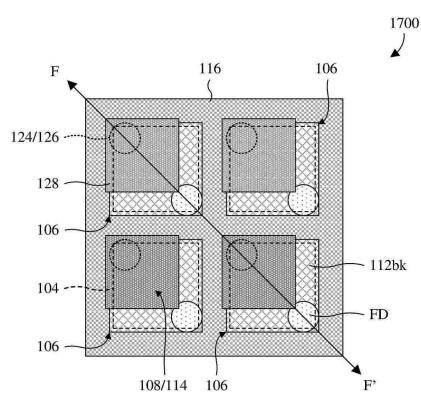

#### 【0075】

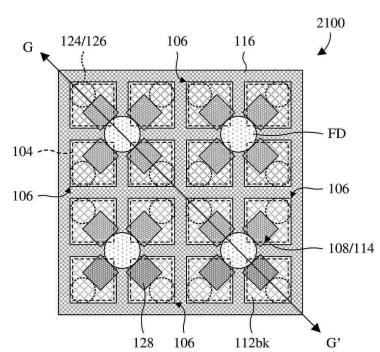

図 17 を参照し、図 15A ~ 図 15D の第 1 IC チップ 102a のいくつかの実施形態の上部レイアウト図 1700 を提供する。上部レイアウト図 1700 は、図 15A ~ 図 15D の画素アレイ 1502 の 2 × 2 サブアレイに対応し、各画素センサは図 3 に関して説明したような上部レイアウトを有する。シャローウェル 116 は、個別に各受光素子 104 を囲むグリッド形状パターンを有する。

20

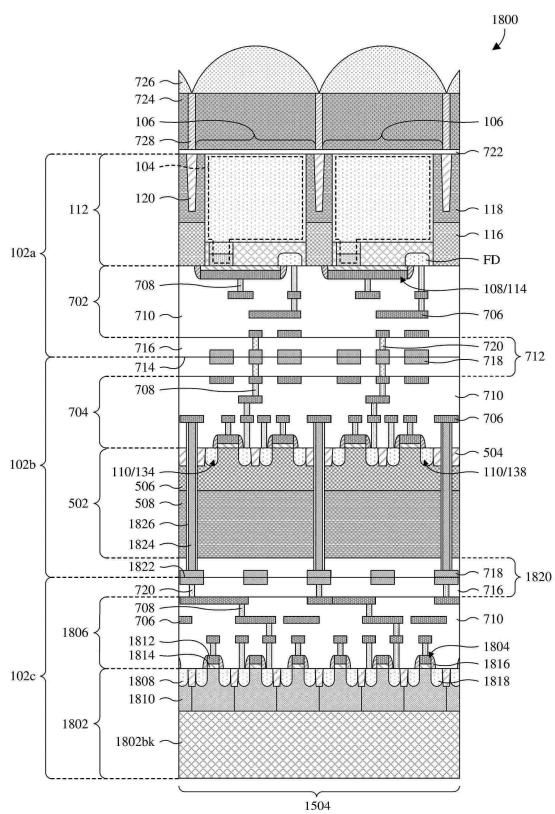

#### 【0076】

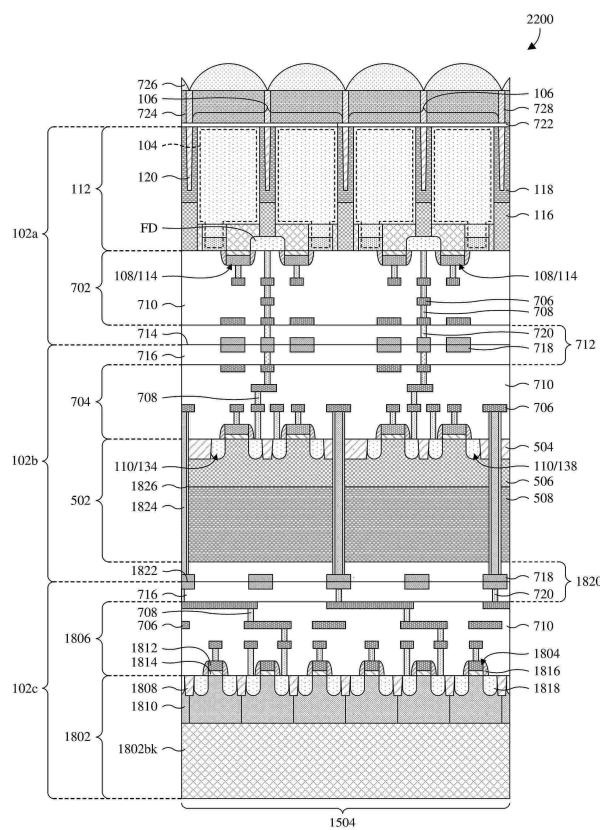

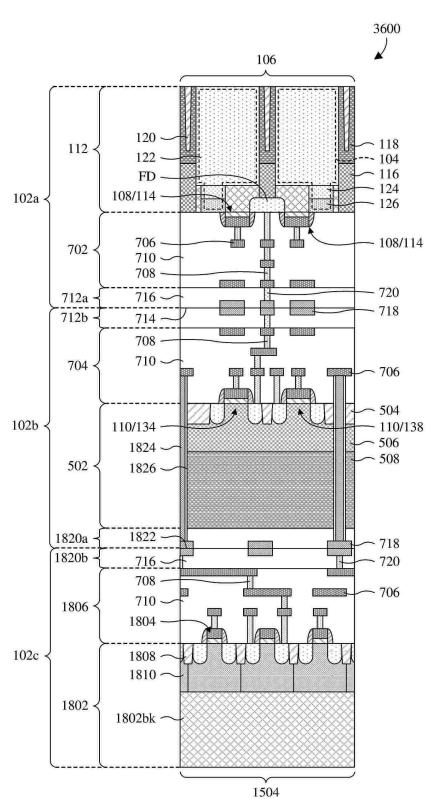

図 18 を参照し、図 15A ~ 図 15D のイメージセンサのいくつかの実施形態の断面図 1800 を提供する。断面図 1800 は、例えば図 17 の F - F' 線に沿って得ることができる。イメージセンサは、図 7 に関して説明したような複数の画素センサ 106 を含み、第 3 IC チップ 102c を更に含む。

30

#### 【0077】

第 3 IC チップ 102c は第 2 IC チップ 102b の下にあって第 2 IC チップ 102b に電気的に結合される。更に、第 3 IC チップ 102c は、第 3 半導体基板 1802 と、複数の第 3 トランジスタ 1804 と、第 3 相互接続構造 1806 とを含む。第 3 トランジスタ 1804 と第 3 相互接続構造 1806 は、第 3 半導体基板 1806 の表側で第 3 半導体基板 1806 の上にある。更に、第 3 トランジスタ 1804 は、第 3 半導体基板 1802 と第 3 相互接続構造 1806との間にある。

30

#### 【0078】

第 3 トランジスタ 1804 は、第 3 半導体基板 1802 の表側内に延伸する STI 構造 1808 により分離される。STI 構造 1808 は、例えば酸化ケイ素等であるか、それを含んでよい。更に、第 3 トランジスタ 1804 は、それぞれ第 3 半導体基板 1802 のドープウェル 1810 上にある。いくつかの実施形態において、ドープウェル 1810 は第 3 トランジスタ 1804 に個別である。各ドープウェル 1810 は p 型か n 型であり、いくつかの実施形態において、各ドープウェル 1810 は隣接するドープウェルとは逆のドープ型を有する。いくつかの実施形態において、第 3 半導体基板 1802 のバルク領域 1802bk はドープされている（例えば p 型か n 型）。他の実施形態において、第 3 半導体基板 1802 のバルク領域 1802bk は元来のものである。

40

#### 【0079】

第 3 トランジスタ 1804 は ASIC1504 を形成し、例えば、MOSFET、FinFET、GAA-FET 等、又はこれらの任意の組合せであってよい。いくつかの実施形態において、第 3 トランジスタ 1804 のいくつかは n 型電界効果トランジスタであり、第 3 トランジスタ 1804 のいくつかは p 型電界効果トランジスタである。第 3 トランジスタ 1804 は、個別の第 3 ゲート電極 1812 と、個別の第 3 ゲート誘電体層 1814 と、個別の第 3 側壁スペーサ 1816 と、個別のソース / ドレイン領域 1818 の対とを含む。

#### 【0080】

50

第3ゲート電極1812はそれぞれ第3ゲート誘電体層1814と積層され、第3ゲート誘電体層1814は第3ゲート電極1812を第3半導体基板1802から分離する。第3ソース／ドレイン領域1818は第3半導体基板1802内にあり、各第3ゲート電極1812は第3ソース／ドレイン領域1818のそれぞれの対の第3ソース／ドレイン領域間にある。ソース／ドレイン領域は、文脈によって、ソース又はドレインを個別又は集合的に指してよい。

#### 【0081】

第3相互接続構造1806は第3トランジスタ1804の上にあり、第3トランジスタ1804に電気的に結合される。第3相互接続構造1806は上述した第1相互接続構造702、第2相互接続構造704と同様であり、よって対応する相互接続誘電体層710において積層される複数のワイヤ706と複数のビア708とを含む。

10

#### 【0082】

第2接合構造1820が第2ICチップ102bと第3ICチップ102cとの間にあり、第2接合界面1822での第2ICチップ102bと第3ICチップ102cの接合を容易にする。そのような接合は、例えば接合界面での金属間接合及び誘電体間接合を含んでよい。

#### 【0083】

第2接合構造1820は概ね上述した第1接合構造712と同様であり、第2接合構造1820は、複数の接合誘電体層716と、複数の接合パッド718と、複数の接合ビア720とを含む。接合誘電体層716は第2ICチップ102c及び第3ICチップ102cに個別であり、第2接合界面1822で直接接触する。接合パッド718は第2ICチップ102b及び第3ICチップ102cに個別であり、接合界面1822で直接接触する。更に、接合パッド718は接合誘電体層716内にそれぞれ嵌め込まれる。接合ビア720は第3ICチップ102cの接合誘電体層716内にあり、それぞれ第3ICチップ102cの接合パッド718から第3相互接続構造1806へと延伸する。

20

#### 【0084】

複数のTSV1824が、第2相互接続構造704から第2接合構造1820へ、第2半導体基板502を貫通するよう延伸する。TSV1824は導電性であり、よって第2相互接続構造704と第2接合構造1820との間の電気的な結合を容易にする。更に、TSV1824はTSV誘電体層1826により第2半導体基板502から分離される。

30

#### 【0085】

図19を参照し、図18のイメージセンサのいくつかの実施形態の回路図1900を提供する。回路図1900は、ASIC1504の包含を除き、図8の回路図800と類似である。更に、回路図1900は単一の画素センサ106を図示していることを理解されたい。

#### 【0086】

図20を参照し、図18のイメージセンサのいくつかの代替的な実施形態の回路図2000を提供する。回路図2000は、第2ICチップ102bでの補助画素回路902の包含を除き、図19の回路図1900に類似である。補助画素回路902は、選択トランジスタ138と画素センサ106の出力端OUTとの間に電気的に結合される。補助画素回路902は、選択トランジスタ138からの信号を出力端OUTへ渡す前に、該信号に追加的な処理を実行するよう構成される。

40

#### 【0087】

図21を参照し、図15A～図15Dの第1ICチップ102aのいくつかの代替的な実施形態の上部レイアウト図2100を提供する。上部レイアウト図2100は図15A～図15Dの画素アレイ1502の2×2サブアレイに対応し、各画素センサは図11に關して図示及び説明したような上部レイアウトを有する。シャローウェル116は、個別に各受光素子104を囲むグリッド形状パターンを有する。

#### 【0088】

図22を参照し、図15A～図15Dのイメージセンサのいくつかの代替的な実施形態

50

の断面図 2200 を提供する。断面図 2200 は、例えば図 21 の G - G' 線に沿って得ることができる。イメージセンサは、それぞれ図 12 に関して説明したような複数の画素センサ 106 を含み、第 3 IC チップ 102c を更に含む。第 3 IC チップ 102c は、例えば図 18 で説明したようなものであってよい。

#### 【0089】

図 23 を参照し、図 22 のイメージセンサのいくつかの実施形態の回路図 2300 を提供する。回路図 2300 は、ASIC 1504 の包含を除き、図 13 の回路図 1300 に類似である。更に、回路図 2300 は単一の画素センサ 106 を図示していることを理解されたい。

#### 【0090】

図 24 を参照し、図 22 のイメージセンサのいくつかの代替的な実施形態の回路図 2400 を提供する。回路図 2400 は、第 2 IC チップ 102b での補助画素回路 902 の包含を除き、図 23 の断面図 2300 に類似である。補助画素回路 902 は、選択トランジスタ 138 と画素センサ 106 の出力端 OUT との間に電気的に結合される。補助画素回路 902 は、選択トランジスタ 138 からの信号を出力端 OUT へ渡す前に、該信号に追加的な処理を実行するよう構成される。

#### 【0091】

図 25 ~ 図 37 を参照し、イメージセンサを形成するための方法のいくつかの実施形態の一連の断面図 2500 ~ 3700 を提供し、イメージセンサは受光素子を収容する第 1 IC チップで STI 構造を有さない。該方法は、例えば図 22 のイメージセンサを形成するため採用されてよい。

10

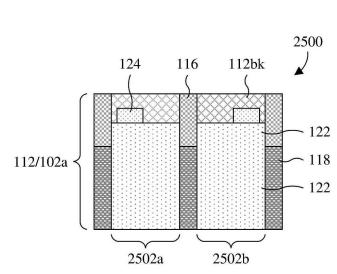

#### 【0092】

図 25 ~ 図 27 の断面図 2500 ~ 2700 に表すように、第 1 IC チップ 102a が形成される。第 1 IC チップ 102a は画素センサの第 1 部分を含み、画素センサの第 1 部分で STI 構造を有さない。画素センサの第 1 部分の上部レイアウトは、例えば図 11 に示すようなものであってよい、及び / 又は、断面図 2500 ~ 2700 は、例えば図 11 における D - D' 線に沿って得られるものであってよい。図 23 と図 24 は、第 1 IC チップ 102a のいくつかの実施形態の回路図 2300、2400 を提供する。

#### 【0093】

画素センサの第 1 部分は、複数の受光素子 104 と複数の第 1 トランジスタ 108 を含む。受光素子 104 は、第 1 トランジスタ 108 と一対一に対応する。更に、各第 1 トランジスタ 108 は、対応する受光素子 104 で蓄積された電荷を、第 1 トランジスタ 108 に共通の浮遊拡散ノード FD へ選択的に転送するよう構成される。よって、第 1 トランジスタ 108 は転送トランジスタ 114 と見なされてもよい。

20

#### 【0094】

図 25 の断面図 2500 に具体的に表すように、一連のドーピング処理が第 1 半導体基板 112 上で実行される。一連のドーピング処理は、複数の第 1 ドープ領域 122 と、複数の第 2 ドープ領域 124 と、シャローウェル 116 と、ディープウェル 118 とを形成する。シャローウェル 116 とディープウェル 118 は第 1 のドープ型を共有するが、異なるドーピングプロファイル及び / 又は濃度を有する。更に、シャローウェル 116 とディープウェル 118 は、第 1 半導体基板 112 において第 1 受光素子領域 2502a と第 2 受光素子領域 2502b とを区分する。

30

#### 【0095】

第 1 ドープ領域 122 は、それぞれ第 1 受光素子領域 2502a と第 2 受光素子領域 2502b にある。第 2 ドープ領域 124 は、それぞれ第 1 受光素子領域 2502a と第 2 受光素子領域 2502b における第 1 ドープ領域 122 の上にある。更に、第 2 ドープ領域 124 は第 1 半導体基板 112 のバルク領域 112bk により囲まれる。第 1 ドープ領域 122 と第 2 ドープ領域 124 は第 2 のドープ型を共有するが、異なるドーピングプロファイル及び / 又は濃度を有する。第 1 のドープ型と第 2 のドープ型は互いに逆である。例えば、第 1 のドープ型は p 型であってよく、第 2 のドープ型は n 型であってよい、又は

40

50

その逆である。いくつかの実施形態において、バルク領域 112bk は第 1 のドープ型を有する。他の実施形態において、バルク領域 112bk は元来のものである。

#### 【0096】

いくつかの実施形態において、一連のドーピング処理は、1) 第 1 ドープ領域 122 に対応するドープ層を形成するための第 1 半導体基板 112 のプランケットドーピングと、2) ドープ層の後にシャローウェル 116 とディープウェル 118 を形成するための選択的ドーピングと、3) シャローウェル 116 とディープウェル 118 の後に第 2 ドープ領域 124 を形成するための選択的ドーピングとを含む。プランケットドーピングは、例えばマスクなし(例えばフォトリソグラフィマスク等なし)でのドーピングであってよく、選択的ドーピングは、例えば配置されたマスクを用いた(例えばフォトリソグラフィマスク等を用いた)ドーピングであってよい。ドーピング処理は、例えばイオン注入等により実行されてよい。

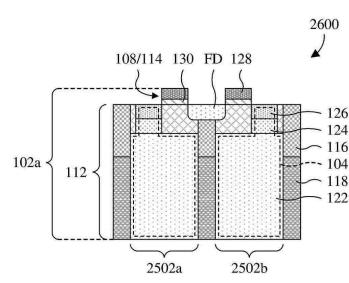

#### 【0097】

図 26 の断面図 2600 に表すように、複数の第 1 ゲート電極 128 と複数の第 1 ゲート誘電体層 130 が第 1 半導体基板 112 の表側上に形成される。第 1 ゲート誘電体層 130 は、それぞれ第 1 受光素子領域 2502a と第 2 受光素子領域 2502b にあり、第 1 ゲート電極 128 は、それぞれ第 1 ゲート誘電体層 130 の上にある。第 1 ゲート電極 128 と第 1 ゲート誘電体層 130 の形成は、例えば、誘電体層と導電層を堆積することと、続いて誘電体層と導電層をそれぞれ第 1 ゲート誘電体層 130 と第 1 ゲート電極 128 にパターニングすることとを含んでよい。

#### 【0098】

また、図 26 の断面図 2600 に表すように、第 1 半導体基板 112 において複数の第 3 ドープ領域 126 と浮遊拡散ノード FD を形成するため、一連のドーピング処理が実行される。浮遊拡散ノード FD は、第 1 ゲート電極 128 間でシャローウェル 116 の上にある。更に、浮遊拡散ノード FD は、シャローウェル 116 とディープウェル 118 により共有される第 1 のドープ型とは逆の第 2 のドープ型を有する。換言すれば、浮遊拡散ノード FD は第 1 ドープ領域 122 及び第 2 ドープ領域 124 とドープ型を共有する。

#### 【0099】

第 3 ドープ領域 126 は、それぞれ第 1 受光素子領域 2502a と第 2 受光素子領域 2502b において第 2 ドープ領域 124 の上にある。更に、第 3 ドープ領域 126 は、第 1 ドープ領域 122 及び第 2 ドープ領域 124 により共有される第 2 のドープ型とは逆の第 1 のドープ型を有する。換言すれば、第 3 ドープ領域 126 は、シャローウェル 116 及びディープウェル 118 とドープ型を共有する。従って、第 3 ドープ領域 126 は浮遊拡散ノード FD とは逆のドープ型を有する。

#### 【0100】

いくつかの実施形態において、一連のドーピング処理は、1) 第 3 ドープ領域 126 を形成するための選択的ドーピングと、2) 第 3 ドープ領域 126 形成の前又は後に浮遊拡散ノード FD を形成するための選択的ドーピングとを含む。選択的ドーピングは、例えば配置されたマスクを用いた(例えばフォトリソグラフィマスク等を用いた)ドーピングであってよい。ドーピング処理は、例えばイオン注入等により実行されてよい。

#### 【0101】

第 3 ドープ領域 126 は、第 1 ドープ領域 122 及び第 2 ドープ領域 124 と共に、それぞれ第 1 受光素子領域 2502a と第 2 受光素子領域 2502b で受光素子 104 を形成する、更に、第 1 ゲート誘電体層 130 と第 1 ゲート電極 128 は、浮遊拡散ノード FD と第 1 ドープ領域 122 及び第 2 ドープ領域 124 と共に、第 1 トランジスタ 108 を形成する。浮遊拡散ノード FD は、第 1 トランジスタ 108 に共通のソース / ドレイン領域を形成し、第 1 ドープ領域 122 と第 2 ドープ領域 124 は、第 1 トランジスタ 108 に個別のソース / ドレイン領域を形成する。

#### 【0102】

受光素子 104 の使用の間、入射放射線に応じて電荷が第 1 ドープ領域 122 と第 2 ド

10

20

30

40

50

ープ領域 124 に蓄積される。よって、第 1 ドープ領域 122 と第 2 ドープ領域 124 はコレクタ領域と見なされてよい。更に、第 1 トランジスタ 108 は蓄積された電荷を浮遊拡散ノード FD へ選択的に転送する。よって、第 1 トランジスタ 108 は転送トランジスタ 114 と見なされてよい。

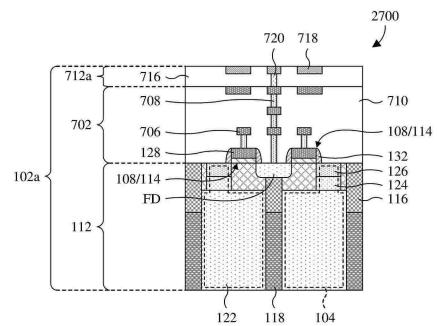

#### 【0103】

図 27 の断面図 2700 に表すように、複数の第 1 側壁スペーサ 132 が第 1 ゲート電極 128 の側壁上に形成される。第 1 側壁スペーサ 132 は誘電体であり、例えば第 1 ゲート電極 128 上に誘電体層を堆積し、続いて該誘電体層をエッチバックすることにより形成されてよい。ただし、他の適切な処理も可能である。

#### 【0104】

また、図 27 の断面図 2700 に表すように、第 1 相互接続構造 702 が第 1 トランジスタ 108 と浮遊拡散ノード FD の上方に形成されて、第 1 トランジスタ 108 と浮遊拡散ノード FD に電気的に結合される。第 1 相互接続構造 702 は、相互接続誘電体層 710 において複数のワイヤ 706 と複数のビア 708 を含む。ワイヤ 706 とビア 708 はそれぞれ、導電経路を定義するため交互に積層される複数のワイヤレベルと複数のビアレベルとにグループ化される。

#### 【0105】

また、図 27 の断面図 2700 に表すように、第 1 接合副構造 712a が第 1 相互接続構造 702 上に形成される。第 1 接合副構造 712a は、接合誘電体層 716 において複数の接合パッド 718 と接合ビア 720 を含む。接合パッド 718 と接合誘電体層 716 は共通接合面を形成し、接合ビア 720 は対応する接合パッド 718 から第 1 相互接続構造 702 へと延伸する。

#### 【0106】

図 28 ~ 図 30 の断面図 2800 ~ 3000 に表すように、第 2 IC チップ 102b が形成される。第 2 IC チップ 102b は画素センサの第 2 部分を含み、画素センサのデバイスを電気的に分離する STI 構造を更に含む。画素センサの第 2 部分の上部レイアウトは、例えば図 6 に示すようなものであり、及び / 又は断面図 2800 ~ 3000 は、例えば図 6 の C - C' 線に沿って得られるものであってよい。図 23 と図 24 は、第 2 IC チップ 102b のいくつかの実施形態の回路図 2300、2400 を提供する。

#### 【0107】

図 28 の断面図 2800 に具体的に表すように、一連のドーピング処理が第 2 半導体基板 502 上で実行される。一連のドーピング処理は、シャローウェル 506 と、シャローウェル 506 の下にあるディープウェル 508 とを形成する。シャローウェル 506 とディープウェル 508 はドープ型（例えば、p 型又は n 型）を共有するが、異なるドーピングプロファイル及び / 又は濃度を有する。

#### 【0108】

いくつかの実施形態において、一連のドーピング処理は、1) ディープウェル 508 を形成するための第 2 半導体基板 502 のプランケットドーピングと、2) シャローウェル 506 を形成するための第 2 半導体基板 502 のプランケットドーピングとを含む。プランケットドーピングは、例えばマスクなし（例えばフォトリソグラフィマスク等なし）でのドーピングであってよい。ドーピング処理は、例えばイオン注入等により実行されてよい。

#### 【0109】

また、図 28 の断面図 2800 に表すように、STI 構造 504 が、第 2 半導体基板 502 のデバイス領域 2802 を区分するため第 2 半導体基板 502 の表側内に延伸して形成される。以降で見られるように、デバイス領域 2802 は以降で形成される画素センサのトランジスタに対応する。STI 構造 504 は、酸化ケイ素及び / 又は他の適切な誘電体材料であるか、それを含む。

#### 【0110】

いくつかの実施形態において、STI 構造 504 を形成するための処理は、1) トレン

10

20

30

40

50

チを形成するため第2半導体基板502をパターニングすることと、2)トレンチに誘電体層を堆積することと、3)トレンチ外の誘電体層の部分を除去するため誘電体層に平坦化を実行することとを含む。パターニングは、例えばフォトリソグラフィ/エッチング等により実行されてよい。

#### 【0111】

図29の断面図2900に表すように、リセットトランジスタ134と選択トランジスタ138とを含む複数の第2トランジスタ110が、第2半導体基板502の表側上に形成される。第2トランジスタ110は、STI構造504により区分されたデバイス領域2802上にそれぞれ形成され、STI構造504により互いに分離されて電気的に分離される。

10

#### 【0112】

第2トランジスタ110は、個別の第2ゲート電極510と、個別の第2ゲート誘電体層512と、個別の第2ソース/ドレイン領域516の対とを含む。第2ゲート電極510は、それぞれ第2ゲート誘電体層512と積層され、第2ゲート誘電体層512は第2ゲート電極510を第2半導体基板502から分離する。第2ソース/ドレイン領域516は第2半導体基板502にあり、各第2ゲート電極510は第2ソース/ドレイン領域516のそれぞれの対の第2ソース/ドレイン領域間にある。

#### 【0113】

第2ゲート電極510と第2ゲート誘電体層512の形成は、例えば、誘電体層と導電層を堆積することと、続いて誘電体層と導電層をそれぞれ第2ゲート誘電体層512と第2ゲート電極510にパターニングすることとを含んでよい。第2ソース/ドレイン領域516の形成は、例えば、第2半導体基板502の選択的ドーピングを含んでよい。選択的ドーピングは、例えば配置されたマスクを用いた（例えばフォトリソグラフィマスク等を用いた）ドーピングであってよい。ドーピング処理は、例えばイオン注入等により実行されてよい。

20

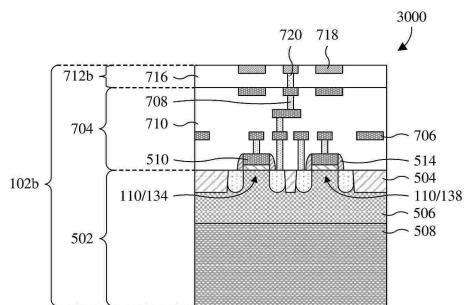

#### 【0114】

図30の断面図3000に表すように、複数の第2側壁スペーサ514が第2ゲート電極510の側壁上に形成される。第2側壁スペーサ514は誘電体であり、例えば第2ゲート電極510上に誘電体層を堆積し、続いて該誘電体層をエッチバックすることにより形成されてよい。ただし、他の適切な処理も可能である。

30

#### 【0115】

また、図30の断面図3000に表すように、第2相互接続構造704が第2トランジスタ110の上方に形成されて、第2トランジスタ110に電気的に結合される。レイアウトが異なる以外は、第2相互接続構造704は上述した第1相互接続構造702と同様である。よって、第2相互接続構造704は相互接続誘電体層710において積層された複数のワイヤ706と複数のビア708とを含む。

#### 【0116】

また、図30の断面図3000に表すように、第2接合副構造712bが第2相互接続構造704上に形成される。第2接合副構造712bは、上述した第1接合副構造712aと同様であり、よって接合誘電体層716において複数の接合パッド718と接合ビア720とを含む。

40

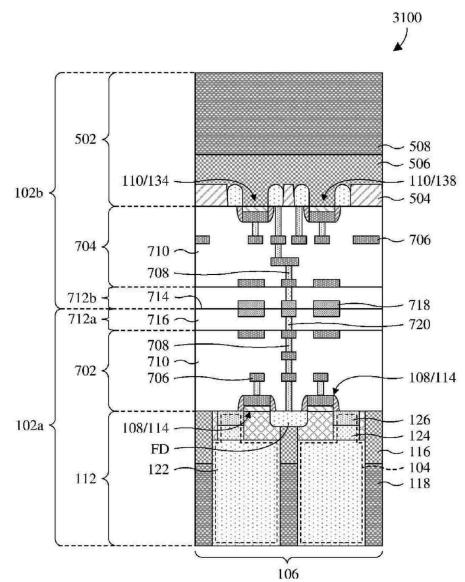

#### 【0117】

図31の断面図3100に表すように、図30の第2ICチップ102bが上下に反転されて第1接合界面714で図27の第1ICチップ102aに接合される。該接合は、第1接合界面714での金属間接合と誘電体間接合の両方を含む。更に、該接合は、図27の画素センサの第1部分と図30の画素センサの第2部分から画素センサ106を形成する。画素センサ106は、例えば図23又は図24のような回路図を有してよい。

#### 【0118】

図31に見られるように、イメージセンサは受光素子104でSTI構造を有さない。以降に形成されるシャローウェル116及びディープウェル118とDTI構造が、性能

50

の大きなトレードオフなしに第 1 I C チップ 102a での画素センサ 106 の部分の電気的分離を提供するのに十分であることを理解されたい。

【 0119 】

S T I 構造が第 1 半導体基板 112 の表側内に延伸する場合、S T I 構造形成の間の基板のエッチングは結晶損傷を引き起こす可能性がある。この結晶損傷は、受光素子の性能を低下させる漏洩 / 暗電流を引き起こす可能性がある。シャローウェル 116 が、S T I 構造での漏洩 / 暗電流を抑制するために S T I 構造の周囲に形成されることができる。しかし、漏洩 / 暗電流を十分に抑制するため、シャローウェル 116 は幅が広くなる。この広い幅は、受光素子 104 のための領域サイズを減少させ、よって微細化を制限してしまう。

10

【 0120 】

受光素子 104 で S T I 構造を省くことで、シャローウェル 116 は狭い幅を有することができ、よって受光素子の領域の占有をより少なくすることができる。これは受光素子 104 の F W C を拡大し、受光素子 104 からの電荷転送を高め、これは画素センサ 106 の微細化を高めることを可能とする。

【 0121 】

受光素子 104 は比較的大きく且つ第 1 I C チップ 102a にあって第 2 I C チップ 102b にはないため、第 1 I C チップ 102a での画素センサ 106 の部分が、画素センサ 106 の微細化を制限するものとなる。よって、第 1 I C チップ 102a での画素センサ 106 の微細化は、画素センサ 106 全体の微細化の効果を奏することができる。更に、第 2 I C チップ 102b での画素センサ 106 の部分は、空間に余裕がある可能性がある。第 2 I C チップ 102b での空間の余裕のため、S T I 構造は画素センサ 106 の微細化を制限することなく第 2 I C チップ 102b で用いられることができる。そのような S T I 構造は、第 2 I C チップ 102b での電気的分離を高める。

20

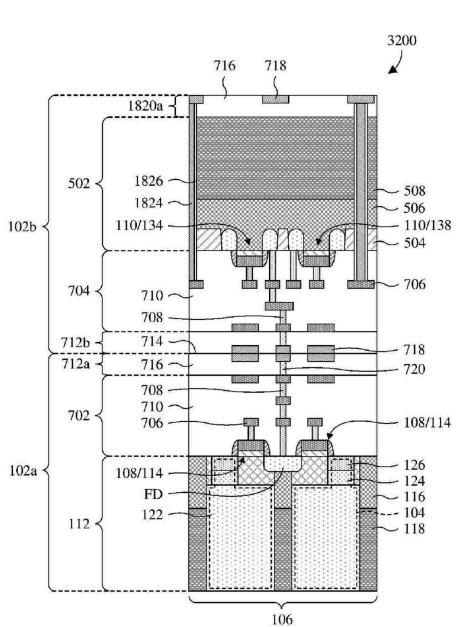

【 0122 】

図 32 の断面図 3200 に表すように、複数の T S V 1824 が第 2 半導体基板 502 を貫通して第 2 相互接続構造 704 へ延伸するよう形成される。更に、T S V 1824 は、T S V 1824 に個別の T S V 誘電体層 1826 により第 2 半導体基板 502 から分離されて形成される。T S V 1824 は導電性であり、第 2 半導体基板 502 の裏側から第 2 相互接続構造 704 への電気的な結合を提供する。

30

【 0123 】

また、図 32 の断面図 3200 に表すように、第 3 接合副構造 1820a が第 2 半導体基板 502 の裏側上に形成される。第 3 接合副構造 1820a は第 1 接合副構造 712a に類似であり、よって接合誘電体層 716 において複数の接合パッド 718 を含む。ただし、第 1 接合副構造 712a とは異なり、第 3 接合副構造 1820a は接合ビア 720 を有さない。代わりに、T S V 1824 が第 3 接合構造 1820a の接合パッド 718 へ延伸する。

【 0124 】

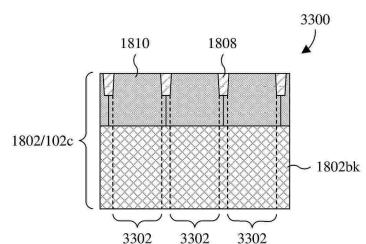

図 33 ~ 図 35 の断面図 3300 ~ 3500 に表すように、第 3 I C チップ 102c が形成される。第 3 I C チップ 102c は A S I C 1504 を含み、A S I C 1504 のデバイスを電気的に分離する S T I 構造を更に含む。A S I C 1504 は、例えば、画素センサ 106 及び他の画素センサの出力に I S P を実行するよう構成されてよい。A S I C 1504 のブロック図は、例えば図 15D 又は図 16B に示すようなものであってよい。

40

【 0125 】

図 33 の断面図 3300 により具体的に表すように、S T I 構造 1808 が、デバイス領域 3302 を区分するため第 3 半導体基板 1802 の表側内に延伸するよう形成される。以降に見られるように、デバイス領域 3302 は以降で形成される A S I C 1504 のトランジスタに対応する。S T I 構造 1808 は、酸化ケイ素及び / 又は他の適切な誘電体材料であるか、それを含んでよい。

【 0126 】

50

いくつかの実施形態において、S T I 構造 1 8 0 8 を形成するための処理は、1) トレンチを形成するため第3半導体基板 1 8 0 2 をパターニングすることと、2) トレンチに誘電体層を堆積することと、3) トレンチ外の誘電体層の部分を除去するため誘電体層に平坦化を実行することとを含む。パターニングは、例えばフォトリソグラフィ / エッチング等により実行されてよい。

#### 【 0 1 2 7 】

また、図 3 3 の断面図 3 3 0 0 に表すように、一連のドーピング処理が第3半導体基板 1 8 0 2 上で実行される。一連のドーピング処理は、それぞれデバイス領域 3 3 0 2 で、第3半導体基板 1 8 0 2 のバルク領域 1 8 0 2 b k の上にある複数のドープウェル 1 8 1 0 を形成する。ドープウェル 1 8 1 0 は、例えば n 型及び p 型といった異なるドープ型を有してよい。

10

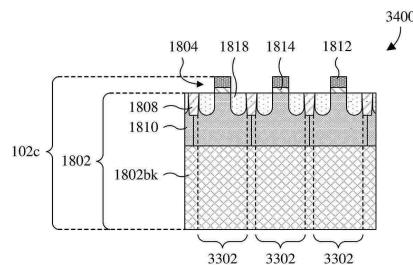

#### 【 0 1 2 8 】

いくつかの実施形態において、一連のドーピング処理は、1) 第1のドープ型を有するドープウェル 1 8 1 0 を形成するための第3半導体基板 1 8 0 2 の選択的ドーピングと、2) 第1のドープ型とは逆の第2のドープ型を有するドープウェル 1 8 1 0 を形成するための第3半導体基板 1 8 0 2 の選択的ドーピングとを含む。選択的ドーピングは、例えば配置されたマスクを用いた(例えばフォトリソグラフィマスク等を用いた)ドーピングであってよい。ドーピング処理は、例えばイオン注入等により実行されてよい。

#### 【 0 1 2 9 】

図 3 4 の断面図 3 4 0 0 に表すように、複数の第3トランジスタ 1 8 0 4 が第3半導体基板 1 8 0 2 の表側上に形成される。第3トランジスタ 1 8 0 4 は、S T I 構造 1 8 0 8 により区分されたデバイス領域 3 3 0 2 上にそれぞれ形成され、S T I 構造 1 8 0 8 により分離されて電気的に分離される。

20

#### 【 0 1 3 0 】

第3トランジスタ 1 8 0 4 は、個別の第3ゲート電極 1 8 1 2 と、個別の第3ゲート誘電体層 1 8 1 4 と、個別の第3ソース / ドレイン領域 1 8 1 8 の対とを含む。第3ゲート電極 1 8 1 2 は、それぞれ第3ゲート誘電体層 1 8 1 4 と積層され、第3ゲート誘電体層 1 8 1 4 は第3ゲート電極 1 8 1 2 を第3半導体基板 1 8 0 2 から分離する。第3ソース / ドレイン領域 1 8 1 8 は第3半導体基板 1 8 0 2 にあり、各第3ゲート電極 1 8 1 2 は第3ソース / ドレイン領域 1 8 1 8 のそれぞれの対の第3ソース / ドレイン領域間にある。

30

#### 【 0 1 3 1 】

第3ゲート電極 1 8 1 2 と第3ゲート誘電体層 1 8 1 4 の形成は、例えば、誘電体層と導電層を堆積することと、続いて誘電体層と導電層をそれぞれ第3ゲート誘電体層 1 8 1 4 と第3ゲート電極 1 8 1 2 にパターニングすることとを含んでよい。第3ソース / ドレイン領域 1 8 1 8 の形成は、例えば、第3半導体基板 1 8 0 2 の選択的ドーピングを含んでよい。選択的ドーピングは、例えば配置されたマスクを用いた(例えばフォトリソグラフィマスク等を用いた)ドーピングであってよい。ドーピング処理は、例えばイオン注入等により実行されてよい。

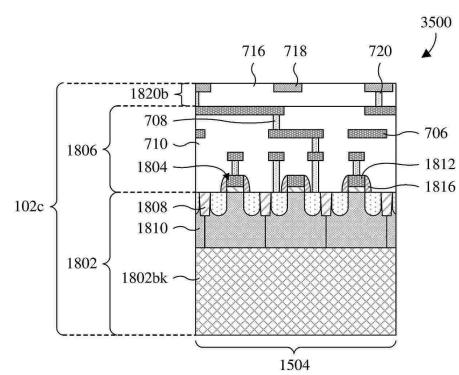

#### 【 0 1 3 2 】

図 3 5 の断面図 3 5 0 0 に表すように、複数の第3側壁スペーサ 1 8 1 6 が第3ゲート電極 1 8 1 2 の側壁上に形成される。第3側壁スペーサ 1 8 1 6 は誘電体であり、例えば第3ゲート電極 1 8 1 2 上に誘電体層を堆積し、続いて該誘電体層をエッチバックすることにより形成されてよい。ただし、他の適切な処理も可能である。

40

#### 【 0 1 3 3 】

また、図 3 5 の断面図 3 5 0 0 に表すように、第3相互接続構造 1 8 0 6 が第3トランジスタ 1 8 0 4 の上方に形成されて、第3トランジスタ 1 8 0 4 に電気的に結合される。レイアウトが異なる以外は、第3相互接続構造 1 8 0 6 は上述した第1相互接続構造 7 0 2 と同様である。よって、第3相互接続構造 1 8 0 6 は相互接続誘電体層 7 1 0 において積層された複数のワイヤ 7 0 6 と複数のビア 7 0 8 とを含む。

#### 【 0 1 3 4 】

50

第3相互接続構造1806は、ASIC1504を形成するため第3トランジスタ1804と電気的に結合される。ASICは、イメージセンサの画素センサ106及び他の画素センサの出力のISPのために構成される。ASIC1504は、例えば、列回路、行回路、ADC、コントローラ回路、DAC、他の適切な回路1516等、又はこれらの任意の組合せを含んでよい。

#### 【0135】

また、図35の断面図3500に表すように、第4接合副構造1820bが第3相互接続構造1806上に形成される。第4接合副構造1820bは上述した第1接合副構造712aに類似であり、よって接合誘電体層716において複数の接合パッド718と接合ビア720とを含む。

10

#### 【0136】

図36の断面図3600に表すように、図32の構造が上下に反転されて第2接合界面1822で図35の第3ICチップ102cに接合される。該接合は、画素センサ106をASIC1504に電気的に結合し、金属間接合と誘電体間接合の両方を含む。

#### 【0137】

また、図36の断面図3600に表すように、DTI構造120が第1半導体基板112の裏側内に延伸するよう形成される。DTI構造120は、hig h-k誘電体等、又はそれらの組合せであるか、それを含んでよい。いくつかの実施形態において、DTI構造120を形成するため処理は、1)トレンチを形成するため第3半導体基板1802をパターニングすることと、2)トレンチに誘電体層を堆積することと、3)トレンチ外の誘電体層の部分を除去するため誘電体層に平坦化を実行することとを含む。パターニングは、例えばフォトリソグラフィ/エッチング等により実行されてよい。

20

#### 【0138】

図37の断面図3700に表すように、裏側パッシベーション層722と、複数のカラーフィルタ724と、複数のマイクロレンズ726と、グリッド構造728が、第1半導体基板112の裏側上に形成される。裏側パッシベーション層722は、第1半導体基板112の裏側を覆う。カラーフィルタ724は裏側パッシベーション層722の上にあり、それぞれ受光素子104の上にある。更に、カラーフィルタ724はグリッド構造728により互いに分離される。マイクロレンズ726はそれぞれカラーフィルタ724の上にある。

30

#### 【0139】

図25～図37を方法を参照して説明したが、これら図に示した構造は該方法に限定されず、方法とは独立していることを理解されたい。図25～図37を一連の行為として説明したが、行為の順序は他の実施形態において変更されてよいことを理解されたい。図25～図37を特定の行為の組として図示及び説明したが、図示及び/又は説明したいくつかの行為は他の実施形態において省略されてよい。更に、図示及び/又は説明されていない行為が他の実施形態において含まれてよい。

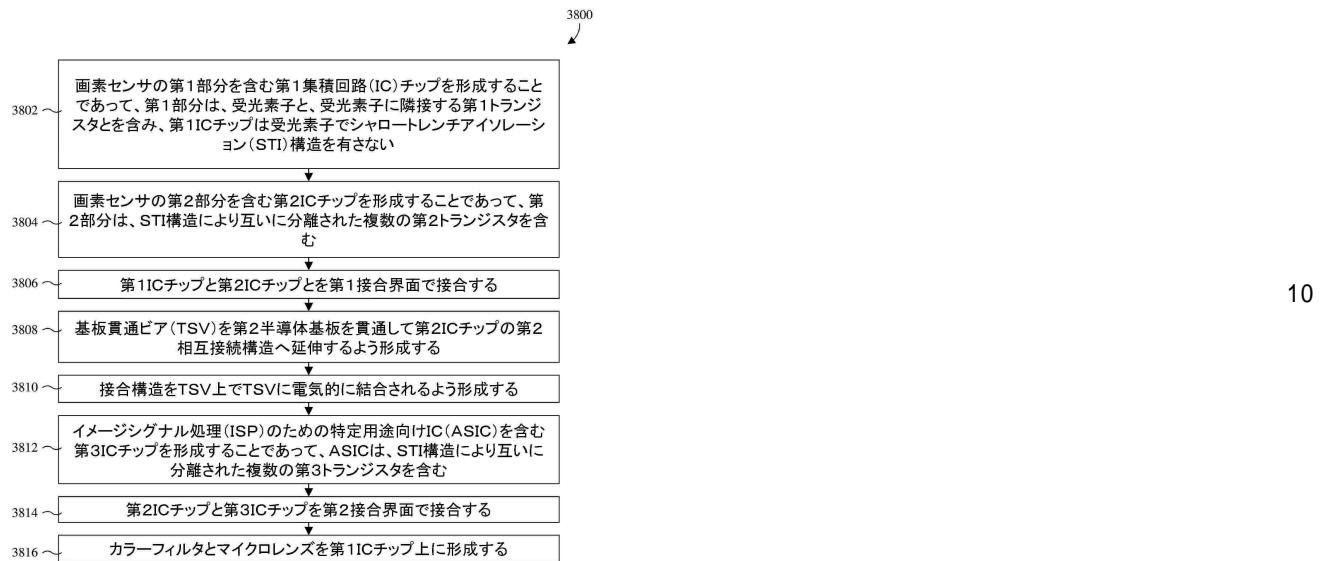

#### 【0140】

図38を参照し、図25～図37の方法のいくつかの実施形態のプロック図3800を提供する。

40

#### 【0141】

ステップ3802で、画素センサの第1部分を含む第1ICチップが形成される。第1部分は、受光素子と、受光素子に隣接する第1トランジスタとを含む。更に、第1ICチップは受光素子でSTI構造を有さない。STI構造を省くことは、画素センサの微細化を高めることを可能とする。例えば、図25～図27を参照されたい。

#### 【0142】

ステップ3804で、画素センサの第2部分を含む第2ICチップが形成される。第2部分は、STI構造により互いに分離された複数の第2トランジスタを含む。図28～図30を参照されたい。画素センサは、例えば4TAPS等であってよい。

#### 【0143】

50

ステップ 3806 で、第 1 IC チップと第 2 IC チップが第 1 接合界面で接合される。例えば、図 31 を参照されたい。

【0144】

ステップ 3808 で、TSV は第 2 半導体基板を貫通して第 2 IC チップの第 2 相互接続構造へ延伸するよう形成される。例えば、図 32 を参照されたい。

【0145】

ステップ 3810 で、接合構造が TSV 上に形成されて TSV に電気的に結合される。例えば、図 32 を参照されたい。

【0146】

ステップ 3812 で、イメージシグナル処理 (ISP) のための ASIC を含む第 3 IC チップが形成される。ASIC は、STI 構造により互いに分離された複数の第 3 トランジスタを含む。例えば、図 33 ~ 図 35 を参照されたい。

10

【0147】

ステップ 3814 で、第 2 IC チップと第 3 IC チップが第 2 接合界面で接合される。例えば、図 36 を参照されたい。

【0148】

ステップ 3816 で、カラーフィルタとマイクロレンズが第 1 IC チップ上に積層されて形成される。例えば、図 37 を参照されたい。

【0149】

図 38 のブロック図 3800 を一連の行為又はイベントとして図示し説明したが、そのような行為又はイベントの図示された順序は限定として解釈されるものではないことを理解されたい。例えば、いくつかの行為は、これら図示及び / 又は説明されるものとは別に、他の順序で、及び / 又は、他の行為又はイベントと同時に行われてよい。更に、ここでの 1 つ以上の様態又は実施形態を実施するために、図示された行為の全てが必要とされなくてよく、ここで図示された 1 つ以上の行為は 1 つ以上の別の行為又はフェーズにおいて行われてもよい。

20

【0150】

いくつかの実施形態において、本発明は、第 1 基板を含む第 1 IC チップと、前記第 1 IC チップと積層される第 2 IC チップと、前記第 1 IC チップと前記第 2 IC チップとにまたがる画素センサとを含む、イメージセンサを提供し、前記画素センサは、前記第 1 IC チップにおいて第 1 トランジスタと受光素子とを含み、前記第 2 IC チップにおいて複数の第 2 トランジスタを更に含み、前記受光素子は前記第 1 基板にあり、前記第 1 トランジスタは前記第 1 基板の表側上にあり、前記第 1 IC チップは、受光素子の表側内に延伸するシャロートレンチアイソレーション (STI) 構造を有さない。いくつかの実施形態において、前記第 1 IC チップは、前記第 1 基板に前記表側から延伸し、前記受光素子を囲むグリッド状上部形状を有するドープウェルを含み、前記表側は、前記受光素子に面する前記ドープウェルの第 1 側壁から前記受光素子とは逆を向く前記ドープウェルの第 2 側壁まで、実質的に平面プロファイルを有する。いくつかの実施形態において、前記ドープウェルは、前記第 1 トランジスタのソース又はドレイン領域とは逆のドープ型を有する。いくつかの実施形態において、前記画素センサに隣接して前記画素センサの繰り返しとなる第 2 画素センサを更に含み、前記表側は、前記画素センサから前記第 2 画素センサまで、実質的に平面プロファイルを有する。いくつかの実施形態において、前記第 2 IC チップは、前記第 2 トランジスタが配置される第 2 基板と、前記第 2 基板内に延伸し、前記第 2 トランジスタを互いに分離する STI 構造とを含む。いくつかの実施形態において、前記イメージセンサは、前記第 2 IC チップが中間となるように前記第 1 IC チップと前記第 2 IC チップに積層される第 3 IC チップと、前記第 2 IC チップと前記第 3 IC チップとにまたがる ISP のための ASIC とを更に含む。いくつかの実施形態において、前記画素センサは、前記第 1 IC チップにおいて 1 つのみのトランジスタを有し、前記第 2 IC チップにおいて 3 つのみ又はそれ以上のトランジスタを有する。いくつかの実施形態において、前記複数の第 2 トランジスタは、リセットトランジスタと、ソースフォロア

30

40

50

トランジスタと、選択トランジスタとを含み、前記ソースフォロアトランジスタと前記選択トランジスタは直列に電気的に結合され、前記ソースフォロアトランジスタのゲート電極は、前記リセットトランジスタのソース／ドレイン領域と前記第1トランジスタのソース／ドレイン領域に電気的に結合される。

【 0 1 5 1 】

いくつかの実施形態において、本発明は、第1半導体基板と、前記第1半導体基板において隣接する第1受光素子及び第2受光素子と、前記第1半導体基板の表側表面上で前記第1受光素子に隣接する第1トランジスタと、第2半導体基板と、前記第2半導体基板上の複数の第2トランジスタとを含む、もう1つのイメージセンサを提供し、前記第1トランジスタは、前記第1半導体基板においてソース又はドレイン領域を有し、前記第1受光素子と前記第1トランジスタ及び前記第2トランジスタが画素センサを形成し、前記表側表面は、前記第1受光素子から前記第2受光素子まで継続的に前記ソース又はドレイン領域の頂部と面一である。いくつかの実施形態において、前記イメージセンサは前記第1半導体基板においてドープウェルを更に含み、前記ドープウェルは前記第1受光素子と前記第2受光素子とを分離し、前記第1受光素子に面する第1側壁と、前記第2受光素子に面する第2側壁とを有し、前記表側表面は、前記第1側壁から前記第2側壁まで継続的に前記ソース又はドレイン領域の頂部と面一である。いくつかの実施形態において、前記イメージセンサは前記第1半導体基板においてドープウェルを更に含み、前記ドープウェルは前記ソース又はドレイン領域とは逆のドープ型を有し、前記第1受光素子と前記第2受光素子との間で柱状プロファイルを有し、前記柱状プロファイルの頂部は、前記第1受光素子から前記第2受光素子まで実質的に平坦である。いくつかの実施形態において、前記イメージセンサは前記第1半導体基板において、前記ドープウェルの下にある第2ドープウェルを更に含み、前記第2ドープウェルは前記逆のドープ型を有し、前記第1受光素子と前記第2受光素子との間にあって前記ドープウェルから前記第1半導体基板の前記表側表面とは反対の裏側表面へ延伸する柱状プロファイルを有し、前記ドープウェルの前記柱状プロファイルと前記第2ドープウェルの前記柱状プロファイルが共通の幅を共有する。いくつかの実施形態において、前記イメージセンサは、前記第1半導体基板の前記表側表面とは反対であり前記表側表面から間隔が空けられた前記第1半導体基板の裏側表面内に延伸する、D T I構造を更に含み、前記D T I構造は、前記第1受光素子と前記第2受光素子とを分離する部分を有し、前記第1半導体基板は、前記部分から前記ソース又はドレイン領域の前記頂部と面一である高さレベルまで垂直方向に続く。いくつかの実施形態において、前記画素センサは、4 T A P Sである。

〔 0 1 5 2 〕

記第2 I Cチップのそれぞれの誘電体層が前記界面で接合される接合により実行される。いくつかの実施形態において、前記第2 I Cチップを形成することは、デバイス領域を囲んで区分するトレーニチを形成するため前記第2基板をパターニングすることと、前記トレーニチを誘電体材料で充填することであって、前記第2トランジスタはそれぞれ前記デバイス領域上に形成され、前記誘電体材料は前記第2トランジスタを互いに分離し且つ電気的に分離することとを含む。いくつかの実施形態において、前記第1 I Cチップを形成することは、前記第1基板において前記受光素子に隣接する第2受光素子を形成することを含み、前記半導体表面は、前記第1トランジスタの形成後に、前記第1トランジスタのソース又はドレイン領域の頂部と面一の高さで、前記受光素子から前記第2受光素子まで継続して延伸する。いくつかの実施形態において、前記方法は、第3基板上に複数の第3トランジスタを形成することと、前記第3トランジスタを覆う相互接続構造を形成することであって、前記第3トランジスタと前記相互接続構造がA S I Cを形成することとを含む、第3 I Cチップを形成することと、前記第2 I Cチップが前記第1 I Cチップと前記第3 I Cチップとの中間となるよう、そして前記A S I Cが前記画素センサに電気的に結合されるよう、前記第2 I Cチップと前記第3 I Cチップを接合することとを更に含む。

#### 【0153】

上記は、当業者が本発明の態様をより好ましく理解できるように、いくつかの実施形態の特徴を概説している。当業者は、ここで紹介した実施形態と同一の目的を実行するため、及び／又は同一の利点を達成するため、他の処理及び構造を設計又は改変するための基礎として、本開示を容易に用いることができるることを理解すべきである。当業者はまた、そのような均等な構造は本発明の精神及び範囲から逸脱せず、本発明の精神及び範囲から逸脱することなく様々な改変、置き換え、及び変更を行うことができるることを理解すべきである。

#### 【産業上の利用可能性】

#### 【0154】

本発明のイメージセンサ及びイメージセンサを形成するための方法は、様々な積層型C M O Sイメージセンサに適用することができる。

#### 【符号の設定】

#### 【0155】

1 0 0、1 0 0 0 : 概略図

2 0 0、4 0 0 A、4 0 0 B、4 0 0 C、4 0 0 D、4 0 0 E、4 0 0 F、5 0 0、7 0 0、1 2 0 0、1 8 0 0、2 2 0 0、2 5 0 0、2 6 0 0、2 7 0 0、2 8 0 0、2 9 0 0、3 0 0 0、3 1 0 0、3 2 0 0、3 3 0 0、3 4 0 0、3 5 0 0、3 5 0 0、3 6 0 0、3 7 0 0 : 断面図

3 0 0、6 0 0、1 1 0 0、1 7 0 0、2 1 0 0 : 上部レイアウト図

8 0 0、9 0 0、1 3 0 0、1 4 0 0、1 9 0 0、2 0 0 0、2 3 0 0、2 4 0 0 : 回路図

1 5 0 0 A、1 5 0 0 B、1 5 0 0 C、1 5 0 0 D、1 6 0 0 A、1 6 0 0 B、3 8 0 0 : ブロック図

1 0 2 a : 第1 I Cチップ

1 0 2 b : 第2 I Cチップ

1 0 2 c : 第3 I Cチップ

1 0 4 : 受光素子

1 0 6 : 画素センサ

1 0 8 : 第1トランジスタ

1 1 0 : 第2トランジスタ

1 1 2 : 第1半導体基板

1 1 2 b s : 裏側

1 1 2 b k : バルク領域

1 1 2 f s : 表側

10

20

30

40

50

|                                     |    |

|-------------------------------------|----|

| 1 1 4 : 転送トランジスタ                    |    |

| 1 1 6 : シャローウェル                     |    |

| 1 1 8 : ディープウェル                     |    |

| 1 2 0 : D T I 構造                    |    |

| 1 2 2 : 第 1 ドープ領域                   |    |

| 1 2 4 : 第 2 ドープ領域                   |    |

| 1 2 6 : 第 3 ドープ領域                   |    |

| 1 2 8 : 第 1 ゲート電極                   |    |

| 1 2 8 p : 突出部                       | 10 |

| 1 3 0 : 第 1 ゲート誘電体層                 |    |

| 1 3 2 : 第 1 側壁スペーサ                  |    |

| 1 3 4 : リセットトランジスタ                  |    |

| 1 3 6 : ソースフォロアトランジスタ               |    |

| 1 3 8 : 選択トランジスタ                    |    |

| 5 0 2 : 第 2 半導体基板                   |    |

| 5 0 2 b s : 裏側                      |    |

| 5 0 2 f s : 表側                      |    |

| 5 0 4 : S T I 構造                    |    |

| 5 0 6 : シャローウェル                     |    |

| 5 0 8 : ディープウェル                     | 20 |

| 5 1 0 : 第 2 ゲート電極                   |    |

| 5 1 2 : 第 2 ゲート誘電体層                 |    |

| 5 1 4 : 第 2 側壁スペーサ                  |    |

| 5 1 6 : 第 2 ソース / ドレイン領域            |    |

| 7 0 2 : 第 1 相互接続構造                  |    |

| 7 0 4 : 第 2 相互接続構造                  |    |

| 7 0 6 : ワイヤ                         |    |

| 7 0 8 : ビア                          |    |

| 7 1 0 : 相互接続誘電体層                    |    |

| 7 1 2 : 第 1 接合構造                    | 30 |

| 7 1 2 a : 第 1 接合副構造                 |    |

| 7 1 2 b : 第 2 接合副構造                 |    |

| 7 1 4 : 第 1 接合界面                    |    |

| 7 1 6 : 接合誘電体層                      |    |

| 7 1 8 : 接合パッド                       |    |

| 7 2 0 : 接合ビア                        |    |

| 7 2 2 : 裏側パッセーション層                  |    |

| 7 2 4 : カラーフィルタ                     |    |

| 7 2 6 : マイクロレンズ                     |    |

| 7 2 8 : グリッド構造                      | 40 |

| 8 0 2 : 接地                          |    |

| 9 0 2 : 補助画素回路                      |    |

| 1 5 0 2 : 画素アレイ                     |    |

| 1 5 0 4 : A S I C                   |    |

| 1 5 0 8 : 行回路                       |    |

| 1 5 1 0 : アナログ - デジタル変換回路 ( A D C ) |    |

| 1 5 1 2 : コントローラ回路                  |    |

| 1 5 1 4 : デジタル - アナログ変換回路 ( D A C ) |    |

| 1 5 1 6 : 他の適切な回路                   |    |

| 1 5 1 8 : パッド                       | 50 |

|                                                                        |    |

|------------------------------------------------------------------------|----|

| 1 6 0 2 : もう 1 つの回路                                                    |    |

| 1 8 0 2 : 第 3 半導体基板                                                    |    |

| 1 8 0 2 b k : バルク領域                                                    |    |

| 1 8 0 4 : 第 3 トランジスタ                                                   |    |

| 1 8 0 6 : 第 3 相互接続構造                                                   |    |

| 1 8 0 8 : S T I 構造                                                     |    |

| 1 8 1 0 : ドープウェル                                                       |    |

| 1 8 1 2 : 第 3 ゲート電極                                                    |    |

| 1 8 1 4 : 第 3 ゲート誘電体層                                                  |    |

| 1 8 1 6 : 第 3 側壁スペーサ                                                   | 10 |

| 1 8 1 8 : 第 3 ソース / ドレイン領域                                             |    |

| 1 8 2 0 : 第 2 接合構造                                                     |    |

| 1 8 2 0 a : 第 3 接合副構造                                                  |    |

| 1 8 2 0 b : 第 4 接合副構造                                                  |    |

| 1 8 2 2 : 第 2 接合界面                                                     |    |

| 1 8 2 4 : T S V                                                        |    |

| 1 8 2 6 : T S V 誘電体層                                                   |    |

| 2 5 0 2 a : 第 1 受光素子領域                                                 |    |

| 2 5 0 2 b : 第 2 受光素子領域                                                 |    |

| 2 8 0 2 : デバイス領域                                                       | 20 |

| 3 8 0 2, 3 8 0 4, 3 8 0 6, 3 8 0 8, 3 8 1 0, 3 8 1 2, 3 8 1 4, 3 8 1 6 |    |

| : ステップ                                                                 |    |

| A - A '、 B - B '、 C - C '、 D - D '、 E - E '、 F - F '、 G - G ' : 線      |    |

| F D : 浮遊拡散ノード                                                          |    |

| P : ピッチ                                                                |    |

| O U T : 出力端                                                            |    |

| R S T : リセット信号                                                         |    |

| S E L : 選択信号                                                           |    |

| T X : 転送信号                                                             |    |

| V D D : 電源電圧                                                           | 30 |

| V r s t : リセット電圧                                                       |    |

| W s t i : 幅                                                            |    |

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4 A】

30

40

50

【図 4 B】

【図 4 C】

10

【図 4 D】

【図 4 E】

20

30

40

50

### 【図4F】

【図5】

【 四 6 】

【 図 7 】

【 义 8 】

【 図 9 】

【図10】

【図11】

【図 1 2】

【図 1 3】

10

20

【図 1 4】

【図 1 5 A】

30

40

50

【図 15 B】

【図 15 C】

10

【図 15 D】

【図 16 A】

20

30

40

50

【図 16 B】

【図 17】

10

【図 18】

20

【図 19】

30

40

50

【図 2 0】

【図 2 1】

10

【図 2 2】

【図 2 3】

20

30

40

50

【図 2 4】

【図 2 5】

10

【図 2 6】

【図 2 7】

20

【図 2 8】

【図 2 9】

30

40

50

【図30】

【図31】

10

20

【図32】

【図33】

30

40

50

【図34】

【図35】

10

20

【図36】

【図37】

30

40

50

## 【図38】

20

30

40

50

## フロントページの続き

弁理士 山口 雄輔

(72)発明者 鍾 積賢

台灣新竹科學工業園區新竹市力行六路八號

(72)発明者 王 子睿

台灣新竹科學工業園區新竹市力行六路八號

(72)発明者 王 銓中

台灣新竹科學工業園區新竹市力行六路八號

(72)発明者 楊 敦年

台灣新竹科學工業園區新竹市力行六路八號

(72)発明者 許 慈軒

台灣新竹科學工業園區新竹市力行六路八號

審査官 小山 満

(56)参考文献 国際公開第2022/176626 (WO, A1)

特開2012-015274 (JP, A)

欧州特許出願公開第04297093 (EP, A1)

米国特許出願公開第2013/0099291 (US, A1)

国際公開第2012/001910 (WO, A1)

特開2022-107525 (JP, A)

国際公開第2022/138914 (WO, A1)

米国特許出願公開第2021/0091127 (US, A1)

国際公開第2020/075391 (WO, A1)

特開2010-225818 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 27/146

H01L 21/336

H01L 21/8234

H01L 29/78

H01L 27/088