(51) International Patent Classification:

**H03C 3/40** (2006.01)      **H03C 5/00** (2006.01)

**H03F 3/217** (2006.01)

HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

(21) International Application Number:

**PCT/US2015/013245**

(22) International Filing Date:

28 January 2015 (28.01.2015)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

14/167,972      29 January 2014 (29.01.2014)      US

(71) Applicant: **QUALCOMM INCORPORATED** [US/US];

ATTN: International IP Administration, 5775 Morehouse Drive, San Diego, California 92121-1714 (US).

(72) Inventors: **TALWALKAR, Niranjan Anand**; 5775 Morehouse Drive, San Diego, California 92121-1714 (US).

**KASTURIA, Sanjay**; 5775 Morehouse Drive, San Diego, California 92121-1714 (US).

(74) Agents: **LEWIN, Mario J.** et al.; 15201 Mason Road, Suite 1000-312, Cypress, Texas 77433 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT,

(84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### Declarations under Rule 4.17:

- as to applicant's entitlement to apply for and be granted a patent (Rule 4.17(ii))

- as to the applicant's entitlement to claim the priority of the earlier application (Rule 4.17(iii))

#### Published:

- with international search report (Art. 21(3))

- before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

(54) Title: MODULATION THROUGH DIFFERENTIALLY DELAYED CLOCKS

FIG.2

(57) Abstract: A clock modulator can include two configurable delay units and can receive a baseband signal and a clock signal. The two configurable delay units can generate two delayed clock signals, each with different delay amounts. The delay amounts can be based on the baseband signal. The delayed clock signals can be combined to generate a modulated clock signal. A quadrature modulated clock signal can be generated when a first clock modulator receives a first baseband signal and a first clock signal and a second clock modulator receives a second baseband signal and a second clock signal. The first clock signal can be a ninety-degree phase shifted version of the second clock signal. The modulated clock signal from the first clock modulator can be combined with the modulated clock signal from the second clock modulator to generate the quadrature modulated clock signal.

## MODULATION THROUGH DIFFERENTIALLY DELAYED CLOCKS

### RELATED APPLICATIONS

[0001] This application claims the priority benefit of U.S. Application Serial No. 14/167,972 filed Jan 29, 2014.

### BACKGROUND

[0002] Embodiments of the inventive subject matter generally relate to the field of communications and, more particularly, to generating a modulated signal using differentially delayed clock signals.

[0003] Modulation techniques typically involve a baseband signal and a carrier signal. The baseband signal is a signal that can include information intended for transmission through a medium. The baseband signal can be used to modulate the carrier signal and generate a modulated signal. The modulated signal, carrying the information from the baseband signal, can be transmitted to a receiver. A number of modulation techniques can be used to modulate the carrier signal with the baseband signal. For example, a wireless device, such as an access point, can modulate a signal using Orthogonal Frequency-Division Multiplexing (OFDM) modulation techniques in accordance with IEEE 802.11 specifications. The wireless device can include an OFDM modulator to generate the modulated signal and a transmitter to transmit the modulated signal through the medium.

[0004] Transmitting the modulated signal can consume a large amount of power, especially when compared to other circuits and components that may be included in a device with the modulator. Transmitter designs that are more power efficient, such as switched mode transmitters, are often used to reduce power consumption. However, the switching nature of the switched mode transmitter is inherently complex, and does not lend itself to easy implementation with typical signal modulation techniques.

## SUMMARY

**[0005]** Various embodiments of a clock modulator are disclosed. In some embodiments, the clock modulator can receive a first clock signal and a first baseband signal. The first clock signal can be delayed to generate a first delayed clock signal and a second delayed clock signal. The amount of delay, for each delayed clock signal, can be based on the first baseband signal. The first delayed clock signal and the second delayed clock signal can be combined to generate a modulated clock signal.

**[0006]** In some embodiments, the clock modulator can receive a first clock signal, a second clock signal, a first baseband signal and a second baseband signal. The second clock signal can be a phase-shifted version of the first clock signal. The first clock signal can be delayed to generate the first and the second delayed clock signals while the second clock signal can be delayed to generate a third delayed clock signal and a fourth delayed clock signals. The first delayed clock signal, the second delayed clock signal, the third delayed clock signal and the fourth delayed clock signal can be combined to generate a quadrature modulated clock signal.

**[0007]** In some embodiments, a device comprises: a first configurable delay unit configured to receive a first clock signal and a first baseband signal and to generate a first delayed clock signal based, at least in part, on the first baseband signal; a second configurable delay unit configured to receive the first clock signal and the first baseband signal and to generate a second delayed clock signal based, at least in part, on the first baseband signal, wherein the second delayed clock signal is different from the first delayed clock signal; and a combiner configured to combine the first delayed clock signal and the second delayed clock signal to generate a modulated clock signal.

**[0008]** In some embodiments, the first configurable delay unit is further configured to delay the first clock signal by a first delay amount to generate the first delayed clock signal, wherein the first delay amount is based, at least in part, on the first baseband signal.

**[0009]** In some embodiments, the second configurable delay unit is further configured to delay the first clock signal by a second delay amount to generate the second delayed clock signal, wherein the second delay amount is based, at least in part, on the first baseband signal.

[0010] In some embodiments, the combiner is further configured to generate the modulated clock signal with a pulse having a pulse width based, at least in part, on the first baseband signal.

[0011] In some embodiments, the pulse width is based, at least in part, on a sum of a first delay amount and a second delay amount, wherein the first delay amount and the second delay amount are based, at least in part, on the first baseband signal.

[0012] In some embodiments, the device further comprises a first driver configured to receive the first delayed clock signal and to generate a first amplified delayed clock signal; and a second driver configured to receive the second delayed clock signal and to generate a second amplified delayed clock signal, wherein the combiner is further configured to combine the first amplified delayed clock signal and the second amplified delayed clock signal to generate the modulated clock signal.

[0013] In some embodiments, the first driver and the second driver are switched mode drivers.

[0014] In some embodiments, the device further comprises a digital to analog converter coupled with the first configurable delay unit, the digital to analog converter configured to receive the first baseband signal and provide an analog signal to the first configurable delay unit, wherein the first configurable delay unit is further configured to generate the first delayed clock signal based, at least in part, on the analog signal.

[0015] In some embodiments, the combiner is further configured to combine the first delayed clock signal and the second delayed clock signal by subtracting the first delayed clock signal from the second delayed clock signal to generate the modulated clock signal.

[0016] In some embodiments, the device further comprises a third configurable delay unit configured to receive a second clock signal and a second baseband signal and to generate a third delayed clock signal based, at least in part, on the second baseband signal; and a fourth configurable delay unit configured to receive the second clock signal and the second baseband signal and to generate a fourth delayed clock signal based, at least in part, on the second baseband signal, wherein the combiner is further configured to combine the first delayed clock

signal, the second delayed clock signal, the third delayed clock signal and the fourth delayed clock signal to generate the modulated clock signal.

**[0017]** In some embodiments, the second clock signal is related to the first clock signal by a phase shift.

**[0018]** In some embodiments, a method comprises: receiving a first clock signal; receiving a first baseband signal; generating a first delayed clock signal based, at least in part, on the first baseband signal and the first clock signal; generating a second delayed clock signal based, at least in part, on the first baseband signal and the first clock signal, wherein the first delayed clock signal is different from the second delayed clock signal; and combining the first delayed clock signal and the second delayed clock signal to generate a modulated clock signal.

**[0019]** In some embodiments, generating the first delayed clock signal further comprises delaying the first clock signal by a first delay amount, wherein the first delay amount is based, at least in part, on the first baseband signal.

**[0020]** In some embodiments, generating the second delayed clock signal further comprises delaying the first clock signal by a second delay amount, wherein the second delay amount is based, at least in part, on the first baseband signal.

**[0021]** In some embodiments, the modulated clock signal includes a pulse having a pulse width based, at least in part, on the first baseband signal.

**[0022]** In some embodiments, the pulse width is based, at least in part, on a sum of a first delay amount and a second delay amount, wherein the first delay amount and the second delay amount are based, at least in part, on the first baseband signal.

**[0023]** In some embodiments, the method further comprises amplifying the first delayed clock signal; and amplifying the second delayed clock signal, wherein the combining the first delayed clock signal and the second delayed clock signal further comprises combining a first amplified delayed clock signal and a second amplified delayed clock signal to generate the modulated clock signal.

[0024] In some embodiments, amplifying the first delayed clock signal further comprises amplifying through a switched mode driver.

[0025] In some embodiments, the combining further comprises subtracting the first delayed clock signal from the second delayed clock signal to generate the modulated clock signal.

[0026] In some embodiments, the method further comprises receiving a second clock signal; receiving a second baseband signal; generating a third delayed clock signal based, at least in part, on the second baseband signal and the second clock signal; and generating a fourth delayed clock signal based, at least in part, on the second baseband signal and the second clock signal, wherein the combining further comprises combining the first delayed clock signal, the second delayed clock signal, the third delayed clock signal and the fourth delayed clock signal to generate the modulated clock signal.

[0027] In some embodiments, the second clock signal is related to the first clock signal by a phase shift.

[0028] In some embodiments, a system comprises a modulator for generating a modulated clock signal, the modulator comprises: a first configurable delay unit configured to receive a first clock signal and a first baseband signal and to generate a first delayed clock signal based, at least in part, on the first baseband signal; a second configurable delay unit configured to receive the first clock signal and the first baseband signal and to generate a second delayed clock signal based, at least in part, on the first baseband signal, wherein the second delayed clock signal is different from the first delayed clock signal; and a combiner configured to generate the modulated clock signal based, at least in part, on the first delayed clock signal and the second delayed clock signal.

[0029] In some embodiments, the system further comprises a pre-processor configured to receive the first baseband signal and to provide a modified first baseband signal to the first configurable delay unit.

[0030] In some embodiments, the pre-processor is configured to pre-distort the first baseband signal.

[0031] In some embodiments, the system further comprises a first driver configured to receive the first delayed clock signal and to generate a first amplified delayed clock signal; and a second driver configured to receive the second delayed clock signal and to generate a second amplified delayed clock signal, wherein the combiner is further configured to combine the first amplified delayed clock signal and the second amplified delayed clock signal to generate the modulated clock signal.

[0032] In some embodiments, the modulator further comprises a third configurable delay unit configured to receive a second clock signal and a second baseband signal and to generate a third delayed clock signal based, at least in part, on the second baseband signal, a fourth configurable delay unit configured to receive the second clock signal and the second baseband signal and to generate a fourth delayed clock signal based, at least in part, on the second baseband signal, wherein the combiner is further configured to combine the first delayed clock signal, the second delayed clock signal, the third delayed clock signal and the fourth delayed clock signal to generate the modulated clock signal.

[0033] In some embodiments, the system further comprises an antenna configured to transmit the modulated clock signal; and a switch configured to selectively couple the modulated clock signal to the antenna.

[0034] In some embodiments, the system further comprises a filter configured to receive the modulated clock signal from the modulator and to provide a filtered modulated clock signal to the switch.

[0035] In some embodiments, the filter has at least one of a low-pass, a band-pass and a high-pass filter profile.

[0036] In some embodiments, a non-transitory machine-readable storage media having machine executable instructions stored therein, the machine executable instructions comprises instructions to receive a first clock signal; receive a first baseband signal; generate a first delayed clock signal with a first delay amount based, at least in part, on the first baseband signal and the first clock signal; generate a second delayed clock signal with a second delay amount based, at least in part, on the first baseband signal and the first clock signal, wherein the first delay amount

is different from the second delay amount; and combine the first delayed clock signal and the second delayed clock signal to generate a modulated clock signal.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0037] The present embodiments may be better understood, and numerous objects, features, and advantages made apparent to those skilled in the art by referencing the accompanying drawings.

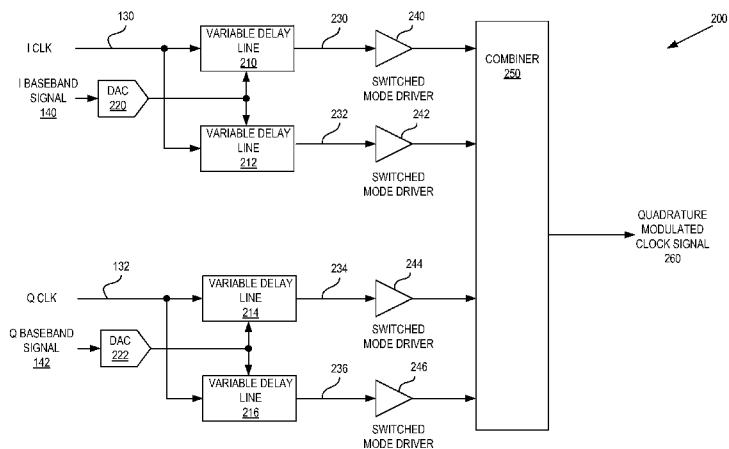

[0038] **Figure 1** is a simplified diagram of a clock modulator.

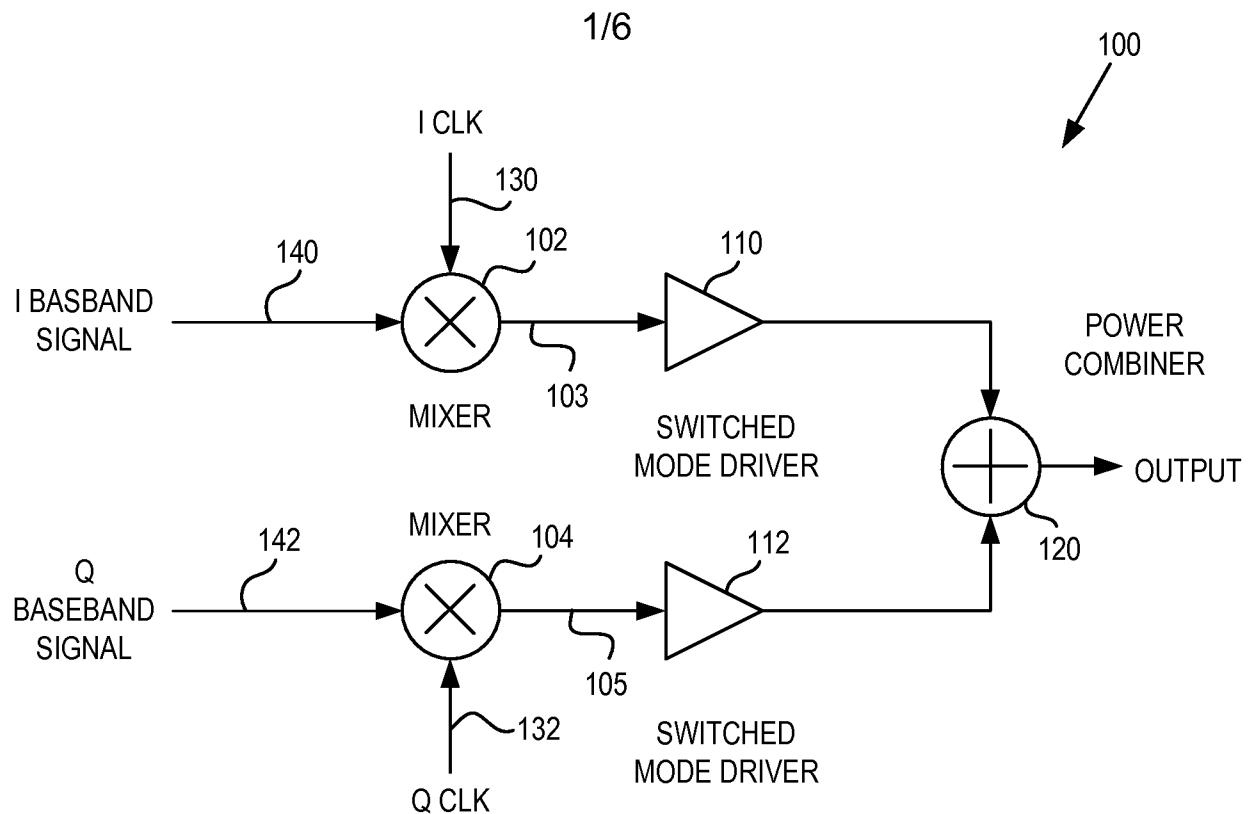

[0039] **Figure 2** is a block diagram of one embodiment of a quadrature clock modulator.

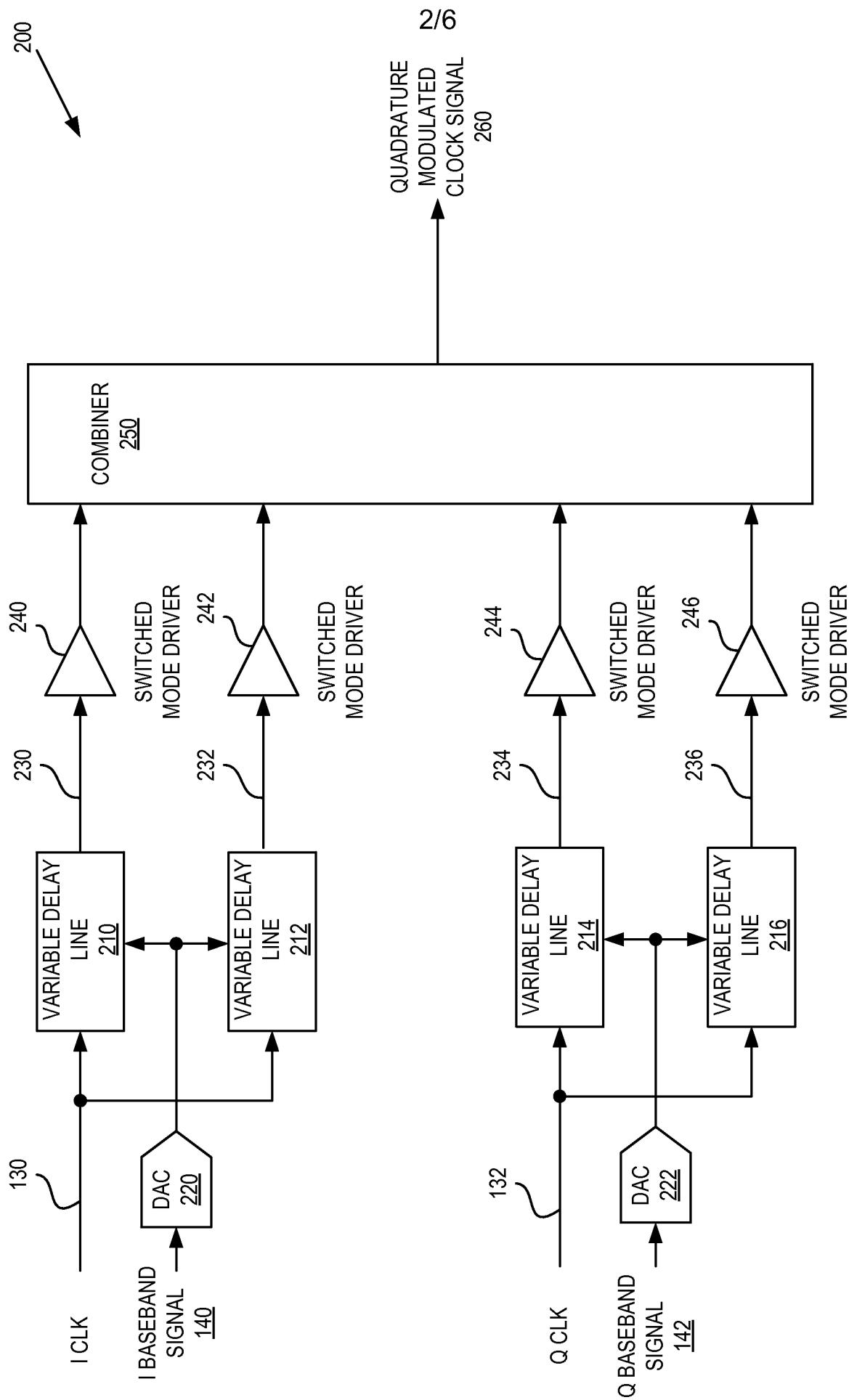

[0040] **Figure 3** is a waveform diagram depicting example waveform shapes and timing relationships of clocks signals.

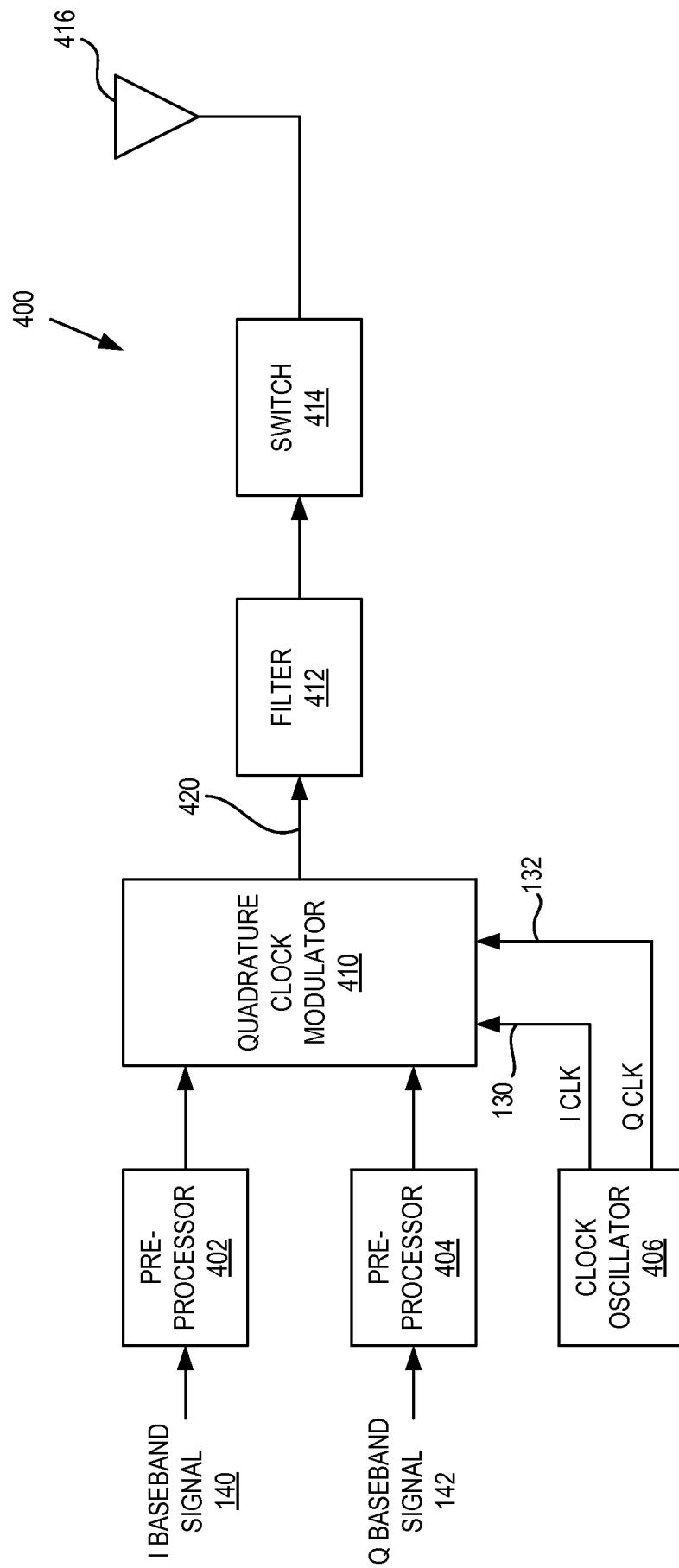

[0041] **Figure 4** is a block diagram depicting one embodiment of a transmitter including a quadrature clock modulator.

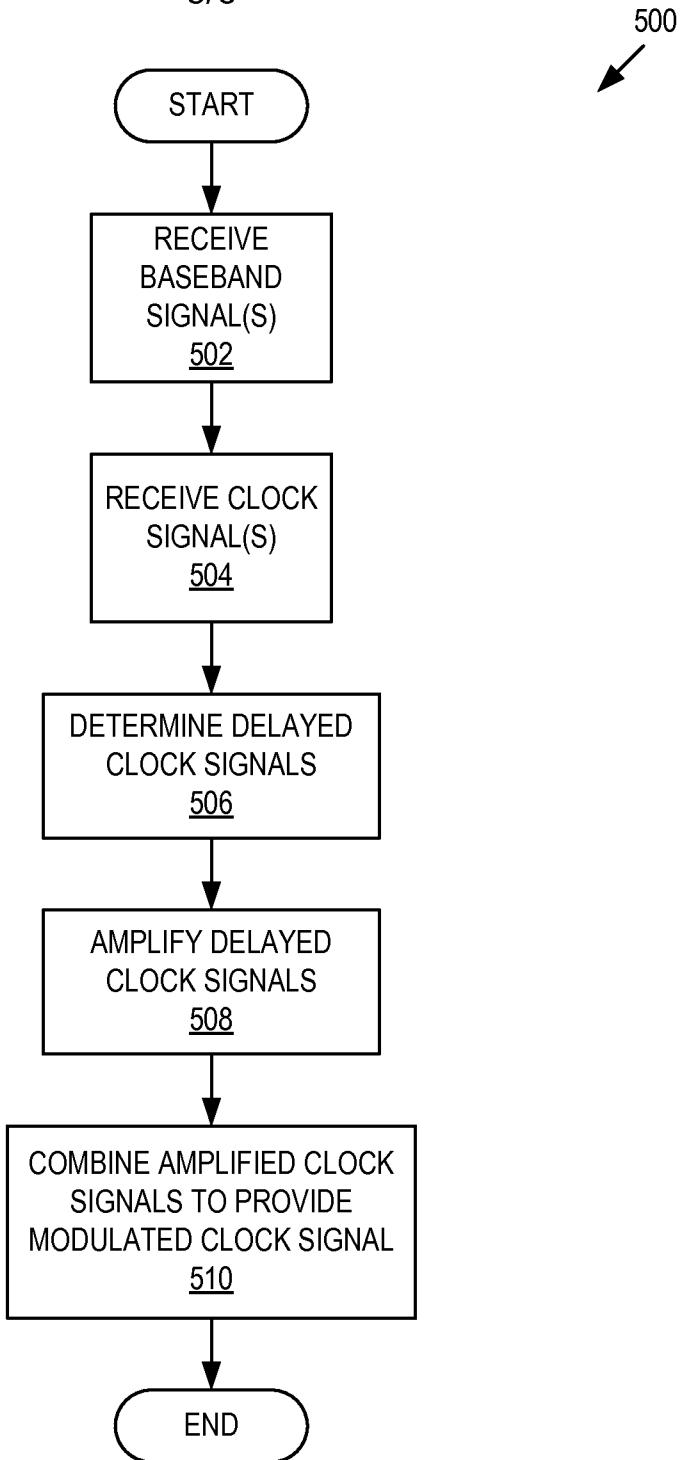

[0042] **Figure 5** is a flow diagram illustrating example operations for providing a modulated clock signal.

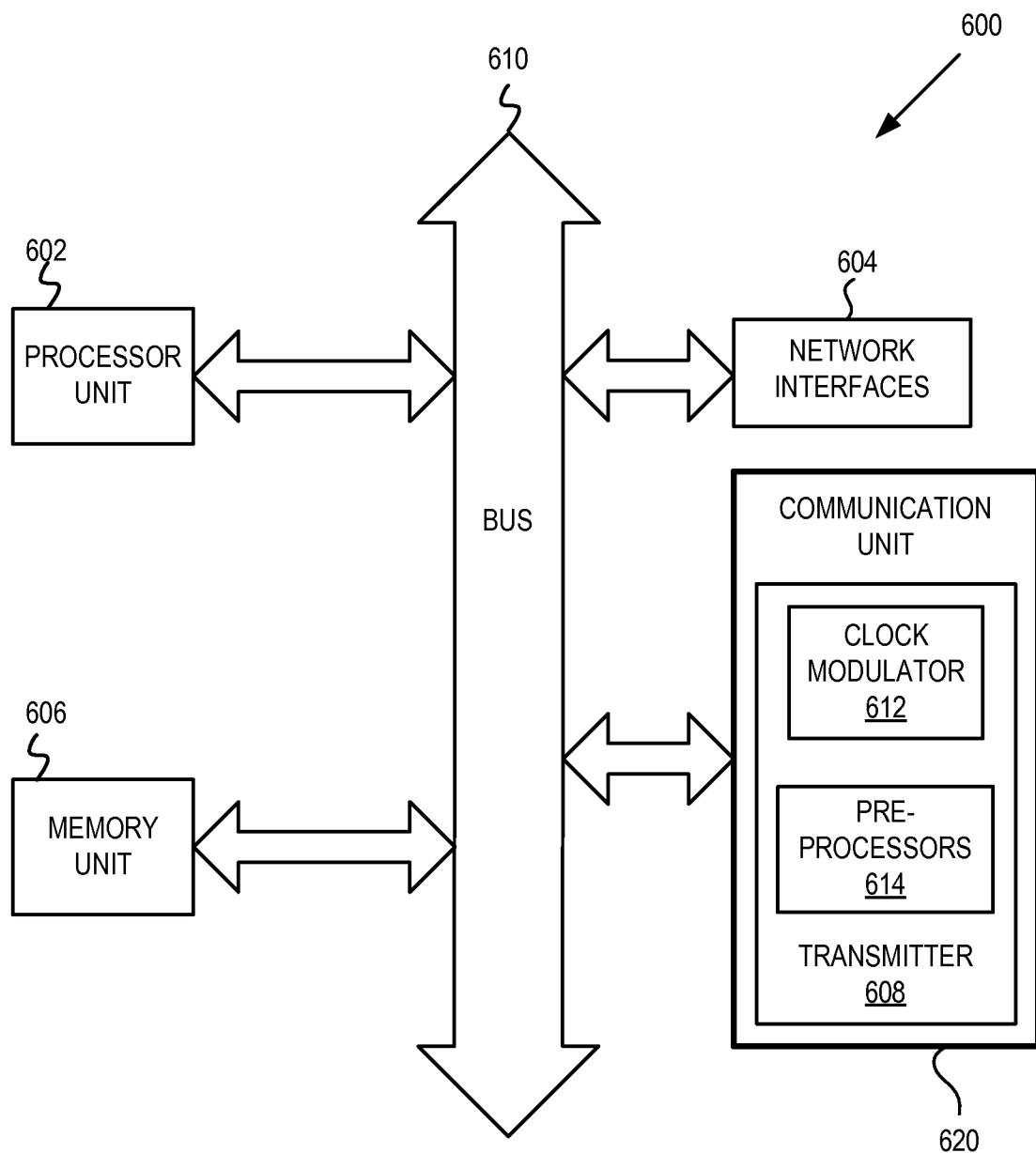

[0043] **Figure 6** is a block diagram of an exemplary embodiment of an electronic device including a quadrature clock modulator.

#### DESCRIPTION OF EMBODIMENT(S)

[0044] The description that follows includes exemplary systems, methods, techniques, instruction sequences and computer program products that embody techniques of the present inventive subject matter. However, it is understood that the described embodiments may be practiced without these specific details. For instance, although examples refer to devices operating in accordance with IEEE 802.11 specifications, other wireless, wired (e.g., Ethernet, power line communications (PLC) and the like) or hybrid devices operating in accordance with other standards or specifications can be used. A hybrid device can include components for both wireless and wired systems. For example, a hybrid device can include wireless components for

communicating in accordance with IEEE 802.11 specifications and wired components for communication in accordance with PLC specifications. In other instances, well-known instruction instances, protocols, structures and techniques have not been shown in detail in order not to obfuscate the description.

**[0045]** A first device in a communication network can include a modulator and a transmitter. The first device can communicate with a second device by transmitting a modulated signal to a receiver in the second device. The modulated signal, generated by the modulator, can convey information from the transmitter to the receiver via a communication medium of the network. The information for transmission can be included in a baseband signal. For example, in one modulation scheme a carrier signal is modulated by the baseband signal to generate the modulated signal. The modulated signal can undergo further processing (such as filtering) before being coupled to an amplifier and transmitted.

**[0046]** The amplifier typically adds energy to (e.g., amplifies) the modulated carrier signal to increase transmission range and reliability. As the modulated carrier signal is amplified, distortion may be introduced by the amplifier. Common distortions such as phase distortion, gain distortion and frequency distortion can increase the number of processing steps used to receive and demodulate a transmitted modulated carrier signal. An amplifier with a linear gain inherently has low amounts of distortion. Class A or class A/B amplifier designs are examples of amplifiers with a linear gain. However, class A or class A/B amplifiers can be power inefficient. In some cases, the class A or class A/B amplifiers can be responsible for a large amount of the power consumption of the device. Class D (switched mode) amplifiers may be preferred over class A or class A/B amplifiers since they are typically more power efficient. Class D amplifiers, however, do not typically have a linear gain. As a result, receiving and demodulating the modulated carrier signals from class D amplifiers can require more processing steps compared to more linear amplifiers due, in part, to the added distortion from the amplifier.

**[0047]** In some embodiments, a clock modulator can include two configurable delay units and a combiner. Each configurable delay unit can receive a baseband signal and a clock signal. Each configurable delay unit can delay the clock signal by a delay amount based, at least in part, on the baseband signal. The delay amount provided by each configurable delay unit may be

different. A first configurable delay unit can delay the clock signal by a first delay amount to generate a first delayed clock signal. The second configurable delay unit can delay the clock signal by a second delay amount to generate a second delayed clock signal. In one embodiment, an overall delay amount is determined by a time difference between the first delayed clock signal and the second delayed clock signal. The first delayed clock signal and the second delayed clock signal are referred to as differentially delayed clock signals. The differentially delayed clock signals can be combined to generate a modulated clock signal.

**[0048]** In another embodiment, the clock modulator can receive two baseband signals and two clock signals. In one embodiment, the clock signals can be related to each other by a phase shift of approximately ninety-degrees. Clock signals with approximately a ninety-degree phase shift relationship are referred to as quadrature clocks. In this embodiment, the clock modulator can include four configurable delay units and a combiner. A first clock signal and a first baseband signal are coupled to a first configurable delay unit and a second configurable delay unit. As described above, the configurable delay units generate a first delayed clock signal and a second delayed clock signal. A second clock signal and a second baseband signal are coupled to a third configurable delay unit and a fourth configurable delay unit. The third configurable delay unit and the fourth configurable delay unit are similar to the other configurable delay units described above. The third configurable delay unit and the fourth configurable delay unit generate a third delayed clock signal and a fourth delayed clock signal, respectively. The first, second, third and fourth delayed clock signals are combined by a combiner to generate the modulated clock signal, also referred to as a quadrature modulated clock signal.

**[0049]** **Figure 1** is a simplified diagram of a clock modulator 100. The simplified diagram highlights conceptual operations of the clock modulator 100. The clock modulator 100 can receive a first baseband signal, a second baseband signal, first clock signal and a second clock signal. The two clock signals can be related to each other by a phase shift. When the phase shift is approximately ninety-degrees, the clock signals are said to be in a quadrature relationship. When the clock signals are in a quadrature relationship, the clock modulator 100 is a quadrature clock modulator.

[0050] The first clock signal can be referred to as the I CLK signal 130 (in-phase clock) and a second clock signal can be referred to as the Q CLK signal 132 (quadrature clock). In one embodiment, the I CLK and Q CLK signals 130 and 132 can be approximately 2.4 GHz. In other embodiments, other frequencies may be used. For example, the I CLK and Q CLK signals 130 and 132 can be 1.2 GHz or the I CLK and Q CLK signals 130 and 132 can be 5.4 GHz. The first and the second baseband signals can carry data. For example, the baseband signals can be time varied to carry data. Although time-varying, the baseband signals can be limited to a predetermined bandwidth. For example, the baseband signals can be limited to 50 MHz. In one embodiment, the frequency of the I CLK signal 130 and the Q CLK signal 132 can be at least ten times greater than the bandwidth of the baseband signal. Limiting the bandwidth of the baseband signal with respect to the I CLK signal 130 and the Q CLK signal 132 can reduce non-linear modulation of I CLK signal 130 and the Q CLK signal 132. Modulation of these clock signals is described in more detail below. The first baseband signal can be referred to as an I baseband signal 140 and the second baseband signal can be referred to as a Q baseband signal 142.

[0051] The I CLK signal 130 and the I baseband signal 140 are coupled to mixer 102. The mixer 102 can multiply (or “mix”) signals together. Conceptually, mixing two signals creates a signal with at least two components, a “sum” component and a “difference” component. For example, the results of mixing two signals F1 and F2 generates a signal with a  $F1 + F2$  (sum) component and a  $F1 - F2$  (difference) component. When the signal F1 is a signal with a first frequency and the signal F2 is a signal with a second frequency, then mixing signals F1 and F2 generates a signal with a first component that has a frequency based on the first frequency plus the second frequency and a second component based on the first frequency minus the second frequency. Often, the output of the mixer is filtered to remove one of the two components. The mixing operation can be performed with analog multipliers or digital multipliers. When one of the two signals provided to a mixer is a variable signal (e.g., a time varying or frequency varying signal), the output of the mixer is said to be a modulated signal. The variable signal is said to modulate a non-varying signal through the mixer. The non-varying signal can be a clock signal, such as the I CLK signal 130. The frequency of the I CLK signal 130 can be constant. The variable signal can be a time varying data signal such as I baseband signal 140 or Q baseband signal 142.

[0052] The I baseband signal 140 and the I CLK signal 130 can be mixed together with the mixer 102 to generate a first modulated clock signal 103. That is, the I CLK signal 130 is modulated by the I baseband signal 140 to generate the first modulated clock signal 103. In a similar manner, the mixer 104 can mix the Q baseband signal 142 and the Q CLK signal 132 together to generate a second modulated clock signal 105. That is, the Q CLK signal 132 is modulated by the Q baseband signal 142 to generate the second modulated clock signal 105. In one embodiment, the I baseband signal 140 and the Q baseband signal 142 are variable signals (time varying or frequency varying) and the I CLK signal 130 and the Q CLK signal 132 are non-varying signals.

[0053] The mixer 102 is coupled to a switched mode driver 110. The switched mode driver 110 can amplify the first modulated clock signal 103 received from the mixer 102. Similarly, the mixer 104 is coupled to a switched mode driver 112 that can amplify the second modulated clock signal 105 received from the mixer 104. The outputs of the switched mode drivers 110 and 112 are coupled to a power combiner 120. The power combiner 120 can sum together (i.e., combine) the output of the switched mode driver 110 and the output of the switched mode driver 112. Since the I CLK signal 130 and the Q CLK signal 132 have a quadrature relationship, the output of the power combiner 120 can include the first modulated clock signal 103 (amplified) in quadrature with the second modulated clock signal 105 (amplified). The output of the power combiner 120 can be referred to as a quadrature modulated clock signal.

[0054] **Figure 2** is a block diagram of one embodiment of a quadrature clock modulator 200. The quadrature clock modulator 200 can receive the I CLK signal 130, the Q CLK signal 132, the I baseband signal 140 and the Q baseband signal 142 and generate a quadrature modulated clock signal 260.

[0055] In one embodiment, the quadrature clock modulator 200 includes two configurable delay units to process the I CLK signal 130 and the I baseband signal 140. In this embodiment, the configurable delay units are implemented as variable delay lines. In other embodiments, the configurable delay units can be implemented as tapped delay lines, programmable delay lines or any other technically feasible delay unit. A first variable delay line 210 and a second variable delay line 212 can each receive the I CLK signal 130. In this embodiment, the I baseband signal

140 is coupled to the first and the second variable delay lines 210 and 212 through a first digital to analog converter (DAC) 220. The first DAC 220 can convert the I baseband signal 140 from a digital signal to an analog signal. For example, the first DAC 220 can generate an analog voltage signal or analog current signal. The first DAC 220 can convert the I baseband signal 140 into an analog signal for coupling to the first and second variable delay lines 210 and 212.

[0056] The first and the second variable delay lines 210 and 212 delay the I CLK signal 130. The first variable delay line 210 is configured to generate a first delayed clock signal 230 with a first delay amount. Similarly, the second variable delay line 212 generates a second delayed clock signal 232 with a second delay amount. The first and the second delay amounts are determined such that the first delayed clock signal 230 is different from the second delayed clock signal 232 by a delay amount  $\delta$ .

[0057] The delay amount  $\delta$  can be based, at least in part, on the I baseband signal 140. In one embodiment the delay amount  $\delta$  can be based on I baseband signal values. For example, the I baseband signal 140 can be configured to represent an arbitrary data stream. The I baseband signal 140 can include values, such as numeric values, to represent data stream values. Other examples of I baseband signal 140 values can include integer and floating point numbers, alphanumeric data, symbol data or any other technically feasible values. If the values of the I baseband signal 140 increase, then the delay amount  $\delta$  can increase commensurately. Conversely, if values of the I baseband signal 140 decrease, then the delay amount  $\delta$  can decrease commensurately. Operation of generating the first and the second delayed clock signals 230 and 232 from the first variable delay line 210 and the second variable delay line 212 is described in more detail below in conjunction with Figure 3.

[0058] The delay amount  $\delta$  can be generated by the first variable delay line 210 and the second variable delay line 212. In one embodiment, the delay amount  $\delta$  can be split between the first variable delay line 210 and the second variable delay line 212. The delay amounts generated by the first variable delay line 210 and the second variable delay line 212 are combined in a combiner 250. That is, the combiner 250 can combine the delay amounts split between the first variable delay line 210 and the second variable delay line 212. Details regarding the configuration of the first and the second variable delay lines 210 and 212 to

provide the delay amount  $\delta$  and operation of the combiner 250 are described in more detail below in conjunction with Figure 3. In one embodiment, the delay amount  $\delta$  is split evenly between the first variable delay line 210 and the second variable delay line 212. In other embodiments, the delay amount  $\delta$  may be split unevenly between first variable delay line 210 and the second variable delay line 212.

[0059] As described above, the delay amount  $\delta$  is not fixed, but can vary in response to the I baseband signal 140. For example, the I baseband signal 140 can include numeric values to represent a time varying data stream. Since the delay amount  $\delta$  can vary in response to the I baseband signal 140, in this example, the delay amount  $\delta$  can be a time varying delay amount.

[0060] The first delayed clock signal 230 and the second delayed clock signal 232 are coupled to a first switched mode driver 240 and a second switched mode driver 242 respectively. The first and the second switched mode drivers 240 and 242 can increase the energy of the first and the second delayed clock signals 230 and 232. In one embodiment, the first and the second switched mode drivers 240 and 242 can be class D output drivers. In another embodiment, the first and the second switched mode drivers 240 and 242 can be inverters with high current outputs. The outputs of the first and the second switched mode drivers 240 and 242 can be coupled to the combiner 250. Although the first and the second switched mode drivers 240 and 242 are coupled to the output of the first and the second variable delay lines 210 and 212, in other embodiments, amplification can be provided by different devices coupled to different components. For example, the first delayed clock signal 230 and the second delayed clock signal 232 can be amplified by an amplifier coupled to the output of the combiner 250.

[0061] The combiner 250 can combine outputs from the first and the second switched mode drivers 240 and 242. In one embodiment, the combiner 250 can subtract a first output from the second switched mode driver 242 from a second output of the first switched mode driver 240. The operation of combining the outputs of the first and the second switched mode drivers 240 and 242 is described in more detail below in conjunction with Figure 3.

[0062] The Q CLK signal 132 is coupled to a third and fourth variable delay lines 214 and 216 respectively. The Q baseband signal 142 is coupled through a second DAC 222 to the third and the fourth variable delay lines 214 and 216. The third variable delay line 214 generates a

third delayed clock signal 234 with a third delay amount. Similarly, the fourth variable delay line 216 generates a fourth delayed clock signal 236 with a fourth delay amount. The third and the fourth delay amounts are determined such that the third delayed clock signal 234 is different from the fourth delayed clock signal 236 by a delay amount based, at least in part, on the Q baseband signal 142. For example if values of the Q baseband signal 142 increase or decrease, then the delay amount based on the Q baseband signal 142 can increase or decrease commensurately.

[0063] The third delayed clock signal 234 and the fourth delayed clock signal 236 are coupled to a third switched mode driver 244 and a fourth switched mode driver 246 respectively. The third and the fourth switched mode drivers 244 and 246 can increase the energy of the third and the fourth delayed clock signals 234, and 236. The combiner 250 can receive outputs from the third switched mode driver 244 and the fourth switched mode driver 246 and can combine these outputs with the outputs from the first switched mode driver 240 and the second switched mode driver 242. The output of the combiner 250 is a quadrature modulated clock signal 260.

[0064] As described above, processing of the Q CLK signal 132 is similar to the processing of the I CLK signal 130. However, the Q baseband signal 142 can be independent of the I baseband signal 140. Therefore, any delay amounts based on the Q baseband signal 142 can be independent from any delay amounts based on the I baseband signal 140. In one embodiment, elements of the quadrature clock modulator 200 can be symmetric. That is, elements used in processing the I CLK signal 130 and the I baseband signal 140 can be similar to corresponding elements used in processing the Q CLK signal 132 and the Q baseband signal 142. For example, the first switched mode driver 240 can amplify (increase the energy of) signals related to the I CLK signal 130 and the I baseband signal 140 with a similar amount of gain used by the third switched mode driver 244 used to amplify signals related to the Q CLK signal 132 and the Q baseband signal 142. In another embodiment, elements of the quadrature clock modulator 200 can be non-symmetric.

[0065] **Figure 3** is a waveform diagram 300 depicting example waveform shapes and timing relationships of clock signals. In particular, waveform diagram 300 shows a relationship between the clock signals, the delayed clock signals and a combination of the delayed clock

signals that may be found in the quadrature clock modulator 200 of Figure 2. A partial clock waveform 301 is shown at the top of the waveform diagram 300. The clock waveform 301 can have a period T and can have a duty cycle of approximately fifty percent. Thus, the portion of the clock waveform 301 shown between the dashed lines is approximately one-half of the period T of the clock waveform 301. The I CLK signal 130 and the Q CLK signal 132 can have a waveform similar to the clock waveform 301.

[0066] As a clock signal, such as I CLK signal 130, is delayed by the first variable delay line 210 and the second variable delay line 212, the first delayed clock signal 230 and the second delayed clock signal 232 are generated respectively. As described above, the I baseband signal 140 is coupled to the first variable delay line 210 and the second variable delay line 212. In one embodiment, a delay amount  $\delta$  responsive to the I baseband signal 140 can be distributed between the first and the second variable delay lines 210 and 212. For example, a delay of  $-(\delta/2)$  can be provided by the first variable delay line 210 and a delay of  $+(\delta/2)$  can be provided by the second variable delay line 212. Since negative delay amounts can be difficult to generate, in one embodiment, a fixed time constant C can be introduced by both the first variable delay line 210 and the second variable delay line 212. The fixed time constant C can help configure the first variable delay line 210 and the second variable delay line 212 to generate positive delays amounts. For example, if the fixed time constant C is greater than the delay amount  $\delta$ , then subtraction of a portion of the delay amount (such as  $(\delta/2)$ ) will result in a positive delay amount to be generated by either the first variable delay line 210 or the second variable delay line 212.

[0067] Returning to Figure 3, waveform 302 can represent the first delayed clock signal 230 from the first variable delay line 210. In this example, the first variable delay line 210 provides a delay amount of  $C - (\delta/2)$ . The shaded region in waveform 302 highlights the delay amount of  $C - (\delta/2)$ . Waveform 303 can represent the second delayed clock signal 232 from the second variable delay line 212. As shown, the second variable delay line 212 provides a delay amount of  $C + (\delta/2)$ . The shaded region in waveform 303 highlights the delay amount of  $C + (\delta/2)$ . The waveforms 302 and 303 can be combined to form a modulated clock signal. In one embodiment, the waveforms 302 and 303 can be combined in the combiner 250 of Figure 2. One embodiment of a combined waveform is shown in waveform 304. The waveform 304 can be produced by subtracting waveform 303 from waveform 302. Note that in one embodiment, combined

waveform 304 can include a positive pulse 310 and a negative pulse 312. The positive pulse 310 and the negative pulse 312 each have a pulse width of  $\delta$  as shown.

[0068] Waveform diagram 300 depicts one approach for implementing a delay amount  $\delta$  responsive to a baseband signal. In another embodiment, the delay amount  $\delta$  does not need to be distributed evenly between the first variable delay line 210 and the second variable delay line 212, but instead the delay amount  $\delta$  can be unevenly divided.

[0069] The waveform 304 depicts a combination of two clock signals (waveforms 302 and 303). The clock signal shown in waveform 302 and the clock signal shown in waveform 303 have each been delayed such that the delay amount between the two clock signals is  $\delta$ . As described above, the delay amount  $\delta$  can be based, at least in part on a signal, such as the I baseband signal 140 or the Q baseband signal 142. That is, the delay amount  $\delta$  can vary as the signal I baseband signal 140 or the Q baseband signal 142 varies.

[0070] **Figure 4** is a block diagram depicting one embodiment of a transmitter 400 including a quadrature clock modulator 410. The quadrature clock modulator 410 can operate in a similar manner as the quadrature clock modulator 200 of Figure 2. The transmitter 400 can include a clock oscillator 406, which can generate the I CLK signal 130 and the Q CLK signal 132. The I CLK signal 130 and the Q CLK signal 132 can be coupled to the quadrature clock modulator 410. In one embodiment, the Q CLK signal 132 can be a phase-shifted version of the I CLK signal 130. For example, the I CLK signal 130 can be phase-shifted by approximately ninety-degrees with respect to the Q CLK signal 132. In other embodiments, other phase shifts are possible. For example, the I CLK signal 130 can be phase-shifted from the Q CLK signal 132 by one hundred and eighty-degrees.

[0071] The transmitter 400 can receive the I baseband signal 140 and the Q baseband signal 142. The I baseband signal 140 is coupled to the quadrature clock modulator 410 through a first pre-processor 402. Similarly, the Q baseband signal 142 is coupled to the quadrature clock modulator 410 through a second pre-processor 404. The first and the second pre-processors 402 and 404 can provide an adjustment or a correction to the operation of the transmitter 400. For example, the first and the second pre-processors 402 and 404 can apply a pre-distortion to the I baseband signal 140 and/or the Q baseband signal 142 to compensate for, or correct a distortion

that is introduced by processing in the transmitter 400. In one embodiment, the first pre-processor 402 and/or the second pre-processor 404 can include a look-up table. The first pre-processor 402 and/or the second pre-processor 404 can be configured to receive a baseband signal and generate a corrected baseband signal based on information included in the look-up table. For example, the information in the look-up table can describe a pre-distortion or a correction function.

[0072] As described above in Figure 2, the quadrature clock modulator 410 can generate a quadrature modulated clock signal 420. The quadrature clock modulator 410 can include one or more drivers, such as the first, second, third and fourth switched mode drivers 240 – 246. The first, second, third and fourth switched mode drivers 240 – 246 can add energy to signals within the quadrature clock modulator 410, which can enable transmission of the quadrature modulated clock signal 420 through a communication medium.

[0073] The quadrature modulated clock signal 420 is coupled to a filter 412. The filter 412 can have a high-pass, a low-pass or a band-pass filter profile. In some embodiments, the filter 412 can include a combination of two or more filter profiles. The output of the filter 412 can be coupled to a switch 414. The switch 414 can couple or disconnect the output of the filter 412 from an antenna 416. In one embodiment, the switch 414 can be a transmit/receive switch used to isolate a receiver (not shown) from the antenna 416.

[0074] **Figure 5** is a flow diagram 500 illustrating example operations for providing a modulated clock signal. The example operations can be carried out by one or more components in the quadrature clock modulator 200 or transmitter 400. The flow begins in block 502 when a baseband signal is received. In one embodiment, the received baseband signal can be the I baseband signal 140 or the Q baseband signal 142. In another embodiment, the received baseband signal can include both the I baseband signal 140 and the Q baseband signal 142. Proceeding to block 504, a clock signal is received. In one embodiment, the received clock signal can be the I CLK signal 130 or the Q CLK signal 132. In another embodiment, the received clock signal can include both the I CLK signal 130 and the Q CLK signal 132.

[0075] Proceeding to block 506, delayed clock signals are determined. In one embodiment, the first delayed clock signal 230 and the second delayed clock signal 232 are determined. In

another embodiment, the third delayed clock signal 234, and the fourth delayed clock signal 236 can be determined in addition to the first and the second delayed clock signals 230 and 232. As described above, the delay amount for the clock signals can be based, at least in part, on a baseband signal. In one embodiment, the delay amount for the first delayed clock signal 230 and the second delayed clock signal 232 can be based on the I baseband signal 140 and the delay amount for the third delayed clock signal 234 and the fourth delayed clock signal 236 can be based on the Q baseband signal 142. The delay amount in the first delayed clock signal 230 can be different from the delay amount in the second delayed clock signal 232. The delay amount for the third delayed clock signal 234 can be different from the delay amount for the fourth delayed clock signal 236.

**[0076]** Proceeding to block 508, the delayed clock signals can be amplified. In one embodiment, the first delayed clock signal 230 and the second delayed clock signal 232 can be amplified. In another embodiment, the third delayed clock signal 234 and the fourth delayed clock signal 236 can be amplified in addition to the first and the second delayed clock signals 230 and 232. In one embodiment, the delayed clock signals can be amplified via switched mode drivers, such as class D output drivers. In other embodiments, the delayed clock signals can be amplified with an inverter. In still other embodiments, any technically feasible amplifiers can be used.

**[0077]** Proceeding to block 510, the amplified delayed clock signals can be combined to generate a modulated clock signal and the flow can end. In one embodiment, the combiner 250 can combine the amplified delayed clock signals from the first switched mode driver 240 and the second switched mode driver 242. In another embodiment, the combiner 250 can combine the amplified delayed clock signals from first switched mode driver 240, the second switched mode driver 242, the third switched mode driver 244 and the fourth switched mode driver 246. In one embodiment, the amplified delayed clock signals can be combined by subtracting the first amplified delayed clock signal from the second amplified delayed clock signal. In another embodiment, the amplified delayed clock signals can be combined by subtracting the first amplified delayed clock signal from the second amplified delayed clock signal to generate a first difference signal. The third amplified delayed clock signal can be subtracted from the fourth amplified delayed clock signal to generate a second difference signal. The first difference signal

and the second difference signal can be combined together thereby combining all four amplified delayed clock signals.

**[0078]** Figures 1 – 5 and the operations described herein are examples meant to aid in the understanding of the embodiments and should not be used to limit the scope of the embodiments or the claims. Embodiments may perform additional operations, fewer operations, operations in a different order, operations in parallel, and some operations differently. For example, the clock signal can be received in block 504 before the baseband signal is received in block 502.

**[0079]** As will be appreciated by one skilled in the art, aspects of the present inventive subject matter may be embodied as a system, method, or computer program product. Accordingly, aspects of the present inventive subject matter may take the form of an entirely hardware embodiment, a software embodiment (including firmware, resident software, micro-code, etc.) or an embodiment combining software and hardware aspects that may all generally be referred to herein as a "circuit," "module" or "system." Furthermore, aspects of the present inventive subject matter may take the form of a computer program product embodied in one or more computer readable medium(s) having computer readable program code embodied thereon.

**[0080]** Any combination of one or more computer readable medium(s) may be used. The computer readable medium may be a computer readable storage medium. A computer readable storage medium may be, for example, an electronic, magnetic, optical, electromagnetic, infrared, or semiconductor system, apparatus, or device, or any suitable combination of the foregoing. More specific examples of the computer readable storage medium may include a portable computer diskette, a hard disk, a random access memory (RAM), a read-only memory (ROM), an erasable programmable read-only memory (EPROM or Flash memory), a portable compact disc read-only memory (CD-ROM), an optical storage device, a magnetic storage device, or any suitable combination of the foregoing. In the context of this document, a computer readable storage medium may be any tangible medium that can contain, or store a program for use by or in connection with an instruction execution system, apparatus, or device.

**[0081]** Program code embodied on a computer readable medium may be transmitted using any appropriate medium, including but not limited to wireless, wireline, optical fiber cable, RF, etc., or any suitable combination of the foregoing.

[0082] The computer readable medium can include instructions for carrying out operations for aspects of the present inventive subject matter and may be written in any combination of one or more programming languages. Examples of programming languages can include an object oriented programming language such as Java, Smalltalk, C++ or the like and conventional procedural programming languages, such as the "C" programming language. The program code may execute entirely on the user's computer, partly on the user's computer, as a stand-alone software package, partly on the user's computer and partly on a remote computer or entirely on the remote computer or server. In the latter scenario, the remote computer may be connected to the user's computer through any type of network, including a local area network (LAN) or a wide area network (WAN), or the connection may be made to an external computer (for example, through the Internet using an Internet Service Provider).

[0083] Aspects of the present inventive subject matter are described with reference to flowchart illustrations and/or block diagrams of methods, apparatus (systems) and computer program products. It will be understood that each block of the flowchart illustrations and/or block diagrams, and combinations of blocks in the flowchart illustrations and/or block diagrams, can be implemented by computer program instructions. These computer program instructions may be provided to a processor of a general purpose computer, special purpose computer, or other programmable data processing apparatus to be executed.

[0084] The computer program instructions can be executed to direct a computer, other programmable data processing apparatus, or other devices to function in a particular manner in order to produce an article of manufacture including instructions which implement the function/act specified in the flowchart and/or block diagram block or blocks.

[0085] The computer program instructions may also be loaded onto a computer, other programmable data processing apparatus, or other devices. The computer program instructions can be executed to cause a series of operational steps to be performed to produce a computer implemented process such that the executed instructions can provide processes for implementing the functions/acts specified in the flowchart and/or block diagram block or blocks.

[0086] **Figure 6** is a block diagram of an exemplary embodiment of an electronic device 600 including a clock modulator 612. In some implementations, the electronic device 600 may be

one of a laptop computer, a tablet computer, a mobile phone, a powerline communication device, a smart appliance (PDA), access point, wireless station or other electronic systems. The electronic device 600 can include processor unit 602 (possibly including multiple processors, multiple cores, multiple nodes, and/or implementing multi-threading, etc.). The electronic device 600 can also include memory unit 606. Memory unit 606 may be system memory (e.g., one or more of cache, SRAM, DRAM, zero capacitor RAM, Twin Transistor RAM, eDRAM, EDO RAM, DDR RAM, EEPROM, NRAM, RRAM, SONOS, PRAM, etc.) or any one or more of the above already described possible realizations of machine-readable media. Electronic device 600 can include bus 610 (e.g., PCI, ISA, PCI-Express, HyperTransport®, InfiniBand®, NuBus, AHB, AXI, etc.). Electronic device 600 can include a network interface 604 that includes at least one of a wireless network interface (e.g., a WLAN interface, a BLUETOOTH® interface, a WiMAX interface, a ZigBee® interface, a Wireless USB interface, etc.) and a wired network interface (e.g., an Ethernet interface, a powerline communication interface, etc.). In some implementations, electronic device 600 may support multiple network interfaces - each of which is configured to couple the electronic device 600 to a different communication network.

**[0087]** The electronic device 600 can include a communication unit 620. The communication unit 620 can include a radio or hybrid radios with transmitters and receivers for wired and wireless networking. For example, the communication unit 620 can include a transmitter 608. The transmitter 608 can be similar to the transmitter 400 as described above. The transmitter 608 can include the clock modulator 612. The transmitter 608 can transmit a modulated clock signal. The clock modulator 612 can be similar to the quadrature clock modulator 200 described above. The transmitter 608 can also include one or more pre-processors 614. The pre-processors 614 can be similar to the first and the second pre-processors 402 and 404 described above. The pre-processors 614 can correct or pre-distort signals, such as baseband signals to compensate for distortion caused by the clock modulator 612. In some embodiments, other portions of the transmitter 608 can be distributed within the processor unit 602, the memory unit 606 and the bus 610.

**[0088]** The memory unit 606 can embody functionality to implement embodiments described in Figures 1 – 5 above. In one embodiment, memory unit 606 can include one or more functionalities that facilitate providing two or more delayed clock signals, where the delay

amount of the delayed clock signals is based, at least in part, on a baseband signal. In other embodiment, the memory unit 606 can be used to implement a look-up table that can provide at least a portion of the functionality of the pre-processors 614.

[0089] Any one of these functionalities may be partially (or entirely) implemented in hardware and/or on the processor unit 602. For example, the functionality may be implemented with an application specific integrated circuit, in logic implemented in the processor unit 602, in a co-processor on a peripheral device or card, etc. Further, realizations may include fewer or additional components not illustrated in Figure 6 (e.g., video cards, audio cards, additional network interfaces, peripheral devices, etc.). The processor unit 602, the memory unit 606, the network interface 604 are coupled to bus 610. Although illustrated as being coupled to the bus 610, the memory unit 606 may be coupled to the processor unit 602.

[0090] While the embodiments are described with reference to various implementations and exploitations, it will be understood that these embodiments are illustrative and that the scope of the inventive subject matter is not limited to them. In general, techniques for providing delayed clock signals and combining the delayed clock signals as described herein may be implemented with facilities consistent with any hardware system or hardware systems. Many variations, modifications, additions, and improvements are possible.

[0091] Plural instances may be provided for components, operations or structures described herein as a single instance. Finally, boundaries between various components, operations and data stores are somewhat arbitrary, and particular operations are illustrated in the context of specific illustrative configurations. Other allocations of functionality are envisioned and may fall within the scope of the inventive subject matter. In general, structures and functionality presented as separate components in the exemplary configurations may be implemented as a combined structure or component. Similarly, structures and functionality presented as a single component may be implemented as separate components. These and other variations, modifications, additions, and improvements may fall within the scope of the inventive subject matter.

## CLAIMS

1. A device comprising:

- a first configurable delay unit configured to receive a first clock signal and a first baseband signal and to generate a first delayed clock signal based, at least in part, on the first baseband signal;

- a second configurable delay unit configured to receive the first clock signal and the first baseband signal and to generate a second delayed clock signal based, at least in part, on the first baseband signal, wherein the second delayed clock signal is different from the first delayed clock signal; and

- a combiner configured to combine the first delayed clock signal and the second delayed clock signal to generate a modulated clock signal.

2. The device of claim 1, wherein the first configurable delay unit is further configured to delay the first clock signal by a first delay amount to generate the first delayed clock signal, wherein the first delay amount is based, at least in part, on the first baseband signal.

3. The device of claim 2, wherein the second configurable delay unit is further configured to delay the first clock signal by a second delay amount to generate the second delayed clock signal, wherein the second delay amount is based, at least in part, on the first baseband signal.

4. The device of claim 1, wherein the combiner is further configured to generate the modulated clock signal with a pulse having a pulse width based, at least in part, on the first baseband signal.

5. The device of claim 4, wherein the pulse width is based, at least in part, on a sum of a first delay amount and a second delay amount, wherein the first delay amount and the second delay amount are based, at least in part, on the first baseband signal.

6. The device of claim 1, further comprising:

a first driver configured to receive the first delayed clock signal and to generate a first amplified delayed clock signal; and

a second driver configured to receive the second delayed clock signal and to generate a second amplified delayed clock signal,

wherein the combiner is further configured to combine the first amplified delayed clock signal and the second amplified delayed clock signal to generate the modulated clock signal.

7. The device of claim 6, wherein the first driver and the second driver are switched mode drivers.

8. The device of claim 1, further comprising a digital to analog converter coupled with the first configurable delay unit, the digital to analog converter configured to receive the first baseband signal and provide an analog signal to the first configurable delay unit, wherein the first configurable delay unit is further configured to generate the first delayed clock signal based, at least in part, on the analog signal.

9. The device of claim 1, wherein the combiner is further configured to combine the first delayed clock signal and the second delayed clock signal by subtracting the first delayed clock signal from the second delayed clock signal to generate the modulated clock signal.

10. The device of claim 1, further comprising:

- a third configurable delay unit configured to receive a second clock signal and a second baseband signal and to generate a third delayed clock signal based, at least in part, on the second baseband signal; and

- a fourth configurable delay unit configured to receive the second clock signal and the second baseband signal and to generate a fourth delayed clock signal based, at least in part, on the second baseband signal,wherein the combiner is further configured to combine the first delayed clock signal, the second delayed clock signal, the third delayed clock signal and the fourth delayed clock signal to generate the modulated clock signal.

11. The device of claim 10, wherein the second clock signal is related to the first clock signal by a phase shift.

12. A method comprising:

- receiving a first clock signal;

- receiving a first baseband signal;

- generating a first delayed clock signal based, at least in part, on the first baseband signal and the first clock signal;

- generating a second delayed clock signal based, at least in part, on the first baseband signal and the first clock signal, wherein the first delayed clock signal is different from the second delayed clock signal; and

- combining the first delayed clock signal and the second delayed clock signal to generate a modulated clock signal.

13. The method of claim 12, wherein generating the first delayed clock signal further comprises delaying the first clock signal by a first delay amount, wherein the first delay amount is based, at least in part, on the first baseband signal.

14. The method of claim 13, wherein generating the second delayed clock signal further comprises delaying the first clock signal by a second delay amount, wherein the second delay amount is based, at least in part, on the first baseband signal.

15. The method of claim 12, wherein the modulated clock signal includes a pulse having a pulse width based, at least in part, on the first baseband signal.

16. The method of claim 15, wherein the pulse width is based, at least in part, on a sum of a first delay amount and a second delay amount, wherein the first delay amount and the second delay amount are based, at least in part, on the first baseband signal.

17. The method of claim 12, further comprising:

- amplifying the first delayed clock signal; and

- amplifying the second delayed clock signal,

wherein the combining the first delayed clock signal and the second delayed clock signal further comprises combining a first amplified delayed clock signal and a second amplified delayed clock signal to generate the modulated clock signal.

18. The method of claim 17, wherein amplifying the first delayed clock signal further comprises amplifying through a switched mode driver.

19. The method of claim 12, wherein the combining further comprises subtracting the first delayed clock signal from the second delayed clock signal to generate the modulated clock signal.

20. The method of claim 12, further comprising:

- receiving a second clock signal;

- receiving a second baseband signal;

- generating a third delayed clock signal based, at least in part, on the second baseband signal and the second clock signal; and

- generating a fourth delayed clock signal based, at least in part, on the second baseband signal and the second clock signal,wherein the combining further comprises combining the first delayed clock signal, the second delayed clock signal, the third delayed clock signal and the fourth delayed clock signal to generate the modulated clock signal.

21. The method of claim 20, wherein the second clock signal is related to the first clock signal by a phase shift.

22. A system comprising:

- a modulator for generating a modulated clock signal, the modulator comprising:

- a first configurable delay unit configured to receive a first clock signal and a first baseband signal and to generate a first delayed clock signal based, at least in part, on the first baseband signal,

- a second configurable delay unit configured to receive the first clock signal and the first baseband signal and to generate a second delayed clock signal

based, at least in part, on the first baseband signal, wherein the second delayed clock signal is different from the first delayed clock signal, and a combiner configured to generate the modulated clock signal based, at least in part, on the first delayed clock signal and the second delayed clock signal.

23. The system of claim 22, further comprising:

a pre-processor configured to receive the first baseband signal and to provide a modified first baseband signal to the first configurable delay unit.

24. The system of claim 23, wherein the pre-processor is configured to pre-distort the first baseband signal.

25. The system of claim 22, further comprising:

a first driver configured to receive the first delayed clock signal and to generate a first amplified delayed clock signal; and

a second driver configured to receive the second delayed clock signal and to generate a second amplified delayed clock signal,

wherein the combiner is further configured to combine the first amplified delayed clock signal and the second amplified delayed clock signal to generate the modulated clock signal.

26. The system of claim 22, wherein the modulator further comprises:

a third configurable delay unit configured to receive a second clock signal and a second baseband signal and to generate a third delayed clock signal based, at least in part, on the second baseband signal,

a fourth configurable delay unit configured to receive the second clock signal and the second baseband signal and to generate a fourth delayed clock signal based, at least in part, on the second baseband signal,

wherein the combiner is further configured to combine the first delayed clock signal, the second delayed clock signal, the third delayed clock signal and the fourth delayed clock signal to generate the modulated clock signal.

27. The system of claim 22, further comprising:

an antenna configured to transmit the modulated clock signal; and

a switch configured to selectively couple the modulated clock signal to the antenna.

28. The system of claim 27, further comprising a filter configured to receive the modulated clock signal from the modulator and to provide a filtered modulated clock signal to the switch.

29. The system of claim 28 wherein the filter has at least one of a low-pass, a band-pass and a high-pass filter profile.

30. A non-transitory machine-readable storage media having machine executable instructions stored therein, the machine executable instructions comprising instructions to:

receive a first clock signal;

receive a first baseband signal;

generate a first delayed clock signal with a first delay amount based, at least in part, on the first baseband signal and the first clock signal;

generate a second delayed clock signal with a second delay amount based, at least in part, on the first baseband signal and the first clock signal, wherein the first delay amount is different from the second delay amount; and

combine the first delayed clock signal and the second delayed clock signal to generate a modulated clock signal.

FIG.1

3/6

FIG.3

4/6

FIG.4

5/6

FIG.5

6/6

FIG. 6

# INTERNATIONAL SEARCH REPORT

International application No

PCT/US2015/013245

**A. CLASSIFICATION OF SUBJECT MATTER**

INV. H03C3/40 H03F3/217 H03C5/00

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

**B. FIELDS SEARCHED**

Minimum documentation searched (classification system followed by classification symbols)

H03C H03F

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data

**C. DOCUMENTS CONSIDERED TO BE RELEVANT**

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                  | Relevant to claim No.             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| X         | US 2009/149151 A1 (BRYANT CARL [SE])<br>11 June 2009 (2009-06-11)<br><br>figures 4A, 9A, 13b, 14<br>-----                                                                                                                                                                           | 1-5,<br>10-16,<br>20-22,<br>26,30 |

| A         | BELL LABS ET AL: "Linear amplification with nonlinear components", IEEE TRANSACTIONS ON COMMUNICATIONS, IEEE SERVICE CENTER, PISCATAWAY, NJ. USA, vol. Com-22, no. 12, 31 December 1974 (1974-12-31), pages 1942-1945, XP008126911, ISSN: 0090-6778<br>figures 1, 2<br>-----<br>-/- | 1-5,<br>10-16,<br>20-22,<br>26,30 |

Further documents are listed in the continuation of Box C.

See patent family annex.

\* Special categories of cited documents :

"A" document defining the general state of the art which is not considered to be of particular relevance

"E" earlier application or patent but published on or after the international filing date

"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

"O" document referring to an oral disclosure, use, exhibition or other means

"P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

|                                                                                                                                                                      |                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Date of the actual completion of the international search<br><br>2 July 2015                                                                                         | Date of mailing of the international search report<br><br>13/07/2015 |

| Name and mailing address of the ISA/<br>European Patent Office, P.B. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040,<br>Fax: (+31-70) 340-3016 | Authorized officer<br><br>Schnabel, Florian                          |

## INTERNATIONAL SEARCH REPORT

|                              |

|------------------------------|

| International application No |

| PCT/US2015/013245            |

## C(Continuation). DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                  | Relevant to claim No.     |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| X         | US 2011/216818 A1 (APOSTOLIDOU MELINA [NL] ET AL) 8 September 2011 (2011-09-08)<br>paragraph [0007]; claim 9; figures 2, 3<br>----- | 1,6,7,<br>17,18,<br>23-25 |

| A         | US 2010/097153 A1 (REXBERG LEONARD [SE] ET AL) 22 April 2010 (2010-04-22)<br>figure 6<br>-----                                      | 1,6,7,<br>17,18,<br>23-25 |

| A         | US 2009/311980 A1 (SJOLAND HENRIK [SE] SJOELAND HENRIK [SE]) 17 December 2009 (2009-12-17)<br>figure 3<br>-----                     | 1,6,7,<br>17,18,<br>23-25 |

| A         | US 2009/146754 A1 (BRYANT CARL [SE]) 11 June 2009 (2009-06-11)<br>figure 4B<br>-----                                                | 1,6,7,<br>17,18,<br>23-25 |

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/US2015/013245

### Box No. II Observations where certain claims were found unsearchable (Continuation of item 2 of first sheet)

This international search report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:

1.  Claims Nos.:

because they relate to subject matter not required to be searched by this Authority, namely:

2.  Claims Nos.:

because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful international search can be carried out, specifically:

3.  Claims Nos.:

because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).

### Box No. III Observations where unity of invention is lacking (Continuation of item 3 of first sheet)

This International Searching Authority found multiple inventions in this international application, as follows:

see additional sheet

1.  As all required additional search fees were timely paid by the applicant, this international search report covers all searchable claims.

2.  As all searchable claims could be searched without effort justifying an additional fees, this Authority did not invite payment of additional fees.

3.  As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:

1-7, 10-18, 20-26, 30

4.  No required additional search fees were timely paid by the applicant. Consequently, this international search report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.:

#### Remark on Protest

The additional search fees were accompanied by the applicant's protest and, where applicable, the payment of a protest fee.

The additional search fees were accompanied by the applicant's protest but the applicable protest fee was not paid within the time limit specified in the invitation.

No protest accompanied the payment of additional search fees.

**FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210**

This International Searching Authority found multiple (groups of) inventions in this international application, as follows:

1. claims: 1-5, 10-16, 20-22, 26, 30

Device with specific delay units

---

2. claims: 6, 7, 17, 18, 25

Device with drivers between delay units and combiner;

---

3. claim: 8

Device with DAC

---

4. claims: 9, 19

Device with combiner subtracting first from second delayed clock signal

---

5. claims: 23, 24

Device with preprocessor

---

6. claims: 27-29

Device with filter after combiner

---

**INTERNATIONAL SEARCH REPORT**

Information on patent family members

International application No

PCT/US2015/013245

| Patent document cited in search report | Publication date | Patent family member(s) |                                                                                           | Publication date                                                   |

|----------------------------------------|------------------|-------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| US 2009149151                          | A1               | 11-06-2009              | NONE                                                                                      |                                                                    |

| US 2011216818                          | A1               | 08-09-2011              | CN 102210096 A<br>EP 2345155 A1<br>US 2011216818 A1<br>WO 2010052668 A1                   | 05-10-2011<br>20-07-2011<br>08-09-2011<br>14-05-2010               |

| US 2010097153                          | A1               | 22-04-2010              | EP 2087586 A1<br>JP 5006403 B2<br>JP 2010507965 A<br>US 2010097153 A1<br>WO 2008051127 A1 | 12-08-2009<br>22-08-2012<br>11-03-2010<br>22-04-2010<br>02-05-2008 |

| US 2009311980                          | A1               | 17-12-2009              | EP 2301146 A1<br>US 2009311980 A1<br>WO 2009153218 A1                                     | 30-03-2011<br>17-12-2009<br>23-12-2009                             |

| US 2009146754                          | A1               | 11-06-2009              | NONE                                                                                      |                                                                    |