## (12) 发明专利申请

(10) 申请公布号 CN 117215971 A

(43) 申请公布日 2023.12.12

(21) 申请号 202311023201.9

(51) Int.Cl.

(22) 申请日 2014.10.21

G06F 12/06 (2006.01)

### (30) 优先权数据

61/893,662 2013.10.21 US

61/893,675 2013.10.21 US

61/893,683 2013.10.21 US

61/895,049 2013.10.24 US

### (62) 分案原申请数据

201480066082.8 2014.10.21

(71) 申请人 FLC环球有限公司

地址 美国内华达州

(72) 发明人 S·苏塔德加

(74) 专利代理机构 北京市金杜律师事务所

11256

专利代理人 姚杰

权利要求书2页 说明书16页 附图3页

### (54) 发明名称

最终级高速缓存系统和对应的方法

### (57) 摘要

本公开的实施例涉及最终级高速缓存系统和对应的方法。数据访问系统包括处理器和最终级高速缓存模块。处理器被配置为生成用于访问第一物理地址的请求。最终级高速缓存模块包括动态随机访问存储器 (DRAM)、最终级高速缓存控制器和DRAM控制器。最终级高速缓存控制器被配置为(i)从处理器接收请求，并且(ii)将第一物理地址转换为第一虚拟地址。DRAM控制器被配置为(i)将第一虚拟地址转换为第二物理地址，并且(ii)基于第二物理地址来访问DRAM存储器。

1.一种数据访问系统,包括:

处理器,其被配置为生成用于访问第一物理地址的请求;以及

最终级高速缓存模块,其包括:

动态随机访问存储器,

最终级高速缓存控制器,其被配置为(i)从所述处理器接收所述请求,并且(ii)将所述第一物理地址转换为第一虚拟地址,以及

动态随机访问存储器控制器,其被配置为(i)将所述第一虚拟地址转换为第二物理地址,并且(ii)基于所述第二物理地址来访问所述动态随机访问存储器。

2.根据权利要求1所述的数据访问系统,其中所述最终级高速缓存控制器被配置为执行所述第一物理地址到所述第一虚拟地址的全集关联转化。

3.根据权利要求1所述的数据访问系统,还包括存储驱动器,其中:

所述存储驱动器与所述动态随机访问存储器是分离的;

所述第二物理地址是所述动态随机访问存储器或所述存储驱动器中的地址;并且

所述最终级高速缓存控制器被配置为基于所述第二物理地址来确定是要访问所述动态随机访问存储器还是所述存储驱动器。

4.根据权利要求3所述的数据访问系统,其中所述存储驱动器具有比所述动态随机访问存储器多的存储容量。

5.根据权利要求3所述的数据访问系统,其中所述存储驱动器具有比所述动态随机访问存储器多一数量级的存储容量。

6.根据权利要求3所述的数据访问系统,其中往来于所述动态随机访问存储器的数据传送速率比往来于所述存储驱动器的数据传送速率快。

7.根据权利要求3所述的数据访问系统,其中所述存储驱动器包括固态存储器或旋转存储介质。

8.根据权利要求3所述的数据访问系统,其中:

所述存储驱动器包括动态随机访问存储器;并且

所述存储驱动器的所述动态随机访问存储器具有比所述最终级高速缓存模块的所述动态随机访问存储器慢的数据传送速率。

9.根据权利要求1所述的数据访问系统,还包括存储驱动器,其中:

所述动态随机访问存储器被实现为高速缓存并且与所述存储驱动器是分离的;并且

所述最终级高速缓存控制器被配置为:(i)基于所述第一物理地址来确定是否要访问所述动态随机访问存储器,并且(ii)确定针对所述第一物理地址已经发生高速缓存未命中,并且(iii)基于所述高速缓存未命中,信号通知所述处理器已经发生所述高速缓存未命中,或者访问所述存储驱动器。

10.根据权利要求1所述的数据访问系统,还包括存储驱动器,其中:

所述动态随机访问存储器被实现为高速缓存并且与所述存储驱动器是分离的;

所述动态随机访问存储器控制器被配置为:(i)基于所述第一虚拟地址来确定是否要访问所述动态随机访问存储器,并且(ii)确定针对所述第一虚拟地址已经发生高速缓存未命中,并且(iii)基于所述高速缓存未命中,信号通知所述最终级高速缓存控制器已经发生所述高速缓存未命中;并且

所述最终级高速缓存控制器被配置为响应于指示已经发生所述高速缓存未命中的信号来访问所述存储驱动器。

## 最终级高速缓存系统和对应的方法

[0001] 本申请是国际申请号为PCT/US2014/061603、国际申请日为2014年10月21日、进入中国国家阶段日期为2016年6月2日、中国国家申请号为201480066082.8的发明专利申请的分案申请。

[0002] 相关申请的交叉引用

[0003] 本申请要求于2014年10月21日提交的第14/519,826号美国专利申请的优先权并还要求于2013年10月21日提交的第61/893,662号美国临时申请、于2013年10月21日提交的第61/893,675号美国临时申请以及于2013年10月21日提交的第61/893,683号美国临时申请以及于2013年10月24日提交的第61/895,049号美国临时申请的权益。通过引用将以上提及的申请的全部内容并入本文。

### 技术领域

[0004] 本公开内容涉及集成电路，并且更具体地涉及与片上系统相关联的高速缓存。

### 背景技术

[0005] 为了总体呈现本公开内容的背景提供本文提供的背景技术。当前署名的发明人到在该背景技术部分中描述的工作的程度的工作以及可能另外在提交时未评定为现有技术的说明书的各方面既未明确地也未隐含地被认可为针对本公开内容的现有技术。

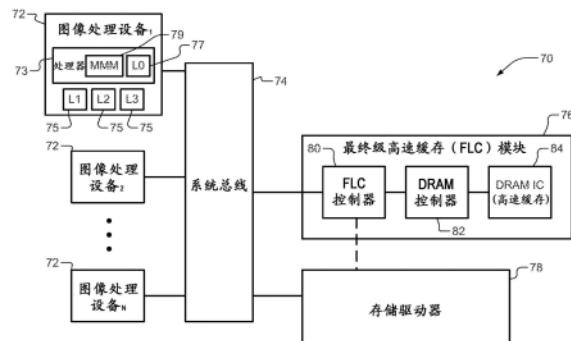

[0006] 诸如计算机、移动电话、平板电脑等等的设备通常包括片上系统(SoC)。图1示出了包括SoC 12和一个或多个动态随机访问存储器(DRAM)14的设备10的示例。DRAM 14能够被实现为连接到SoC 12但与SoC 12分离的一个或多个集成电路。设备10还能够包括连接到SoC 12的端口17的一个或多个存储驱动器16。存储驱动器16能够包括闪速存储器、固态驱动器、硬盘驱动器和/或混合驱动器。混合驱动器包括具有固态存储器的固态驱动器和具有旋转存储介质的硬盘驱动器。

[0007] SoC 12能够包括一个或多个图像处理设备20、系统总线22和存储器控制器24。图像处理设备20中的每个能够包括例如：具有中央处理器(或中央处理单元(CPU))28的控制模块26；图形处理器(或图形处理单元(GPU))30；录像机32；相机图像信号处理器(ISP)34；诸如吉比特(Gb)以太网接口36的以太网接口；诸如通用串行总线(USB)接口38和串行高级技术附件(SATA)接口40的串行接口；以及外围组件互连快速(PCIe)接口42。图像处理设备20经由系统总线22和存储器控制器24访问DRAM 14。DRAM 14被用作主存储器。例如，图像处理设备20中的一个图像处理设备当访问DRAM 14中的一个DRAM中的对应物理位置时将物理地址提供给存储器控制器24。图像处理设备20还能够经由系统总线22访问存储驱动器16。

[0008] SoC 12和/或存储器控制器24能够经由SoC 12的一个或多个访问端口44连接到DRAM 14。DRAM 14存储用户数据、系统数据和/或程序。SoC 12能够使用第一数据来运行程序以生成第二数据。第一数据能够在运行程序之前被存储在DRAM 14中。SoC 12能够在运行程序期间和/或之后将第二数据存储在DRAM 14中。DRAM 14能够具有高带宽接口和每比特低成本存储器存储容量并且能够处置广泛的应用。

[0009] SoC 12包括高速缓存存储器,其能够包括以下各项中的一项或多项:零级(L0)高速缓存、一级(L1)高速缓存、二级(L2)高速缓存或三级(L3)高速缓存。L0-L3高速缓存被布置在SoC 12上、紧密靠近图像处理设备20中的对应的图像处理设备。在示出的示例中,控制模块26包括中央处理器28和L1-L3高速缓存50。中央处理器28包括L0高速缓存52。中央处理器28还包括存储器管理单元(MMU)54,其能够控制对高速缓存50、52的访问。

[0010] 随着高速缓存的级增加,高速缓存的访问延时和存储容量增大。例如,L1高速缓存通常具有比L2高速缓存和L3高速缓存少的存储容量。然而,L1高速缓存通常具有比L2高速缓存和L3高速缓存低的延时。

[0011] SoC 12内的高速缓存通常被实现为静态随机访问存储器(SRAM)。由于高速缓存到图像处理设备20的紧密靠近,高速缓存能够以与图像处理设备20相同的时钟频率来操作。因此,高速缓存展示出比DRAM 14短的延时时间段。

[0012] SoC 12中的高速缓存的数量和大小取决于应用。例如,电话听筒(或移动电话)可以不包括L3高速缓存并且与个人计算机相比能够具有尺寸更小的L1高速缓存和L2高速缓存。类似地,DRAM 14中的每个DRAM的数量和大小取决于应用。例如,移动电话当前具有1-4吉字节(GB)的DRAM,个人计算机当前具有4-16GB的DRAM,并且服务器当前具有32GB-512GB的DRAM。一般地,成本随DRAM的量增大而增大。

[0013] 除了DRAM的成本,针对相同量的存储容量减小DRAM的封装大小变得越来越困难。此外,随着在设备中包含的DRAM的大小和数量增大,DRAM的电容增大,与DRAM相关联的导电元件的数量和/或长度增大,并且与DRAM相关联的缓冲增大。另外,随着DRAM的电容增大,DRAM的操作频率减小并且DRAM的延时时间段增大。

[0014] 在操作期间,根据需要将程序和/或数据从DRAM 14传送到SoC12中的高速缓存。这些传送与在(i)各高速缓存,以及(ii)对应的处理器和/或图像处理设备之间的数据交换相比具有更高的延时。出于这个原因,归因于较长的延时时间段通常避免对DRAM 14的访问。

[0015] 在启动期间,能够将程序从存储驱动器16传送到DRAM 14。例如,中央处理器28能够在启动期间将程序从存储驱动器16传送到DRAM 14。在启动期间,中央处理器28能够尝试访问存储在DRAM 14中的数据。与该访问尝试相关联的命中率可以最初接近或等于0%。然而,命中率在启动的最后接近100%。

## 发明内容

[0016] 提供了一种数据访问系统并且其包括处理器和最终级高速缓存模块。处理器被配置为生成用于访问第一物理地址的请求。最终级高速缓存模块包括动态随机访问存储器(DRAM)、最终级高速缓存控制器和DRAM控制器。最终级高速缓存控制器被配置为(i)从处理器接收请求,并且(ii)将第一物理地址转换为第一虚拟地址。DRAM控制器被配置为(i)将第一虚拟地址转换为第二物理地址,并且(ii)基于第二物理地址来访问DRAM存储器。

[0017] 提供了一种用于访问最终级高速缓存模块的动态随机访问存储器的方法。该方法包括:经由处理器生成用于请求访问第一物理地址的请求;在最终级高速缓存控制器处从处理器接收请求;经由最终级高速缓存控制器将第一物理地址转换为第一虚拟地址;经由动态随机访问存储器控制器将第一虚拟地址转换为第二物理地址;以及基于第二物理地址来访问动态随机访问存储器。

[0018] 本公开内容的适用性的另外的领域将从详细描述的说明书、权利要求书和附图变得显而易见。详细描述的说明书和具体示例仅仅旨在为了说明的目的而不旨在限制本公开内容的范围。

## 附图说明

- [0019] 图1是根据现有技术的设备的功能框图。

- [0020] 图2是根据本公开内容的实施例的数据访问系统的功能框图。

- [0021] 图3是图示了图2的数据访问系统的DRAM和存储驱动器的功能框图。

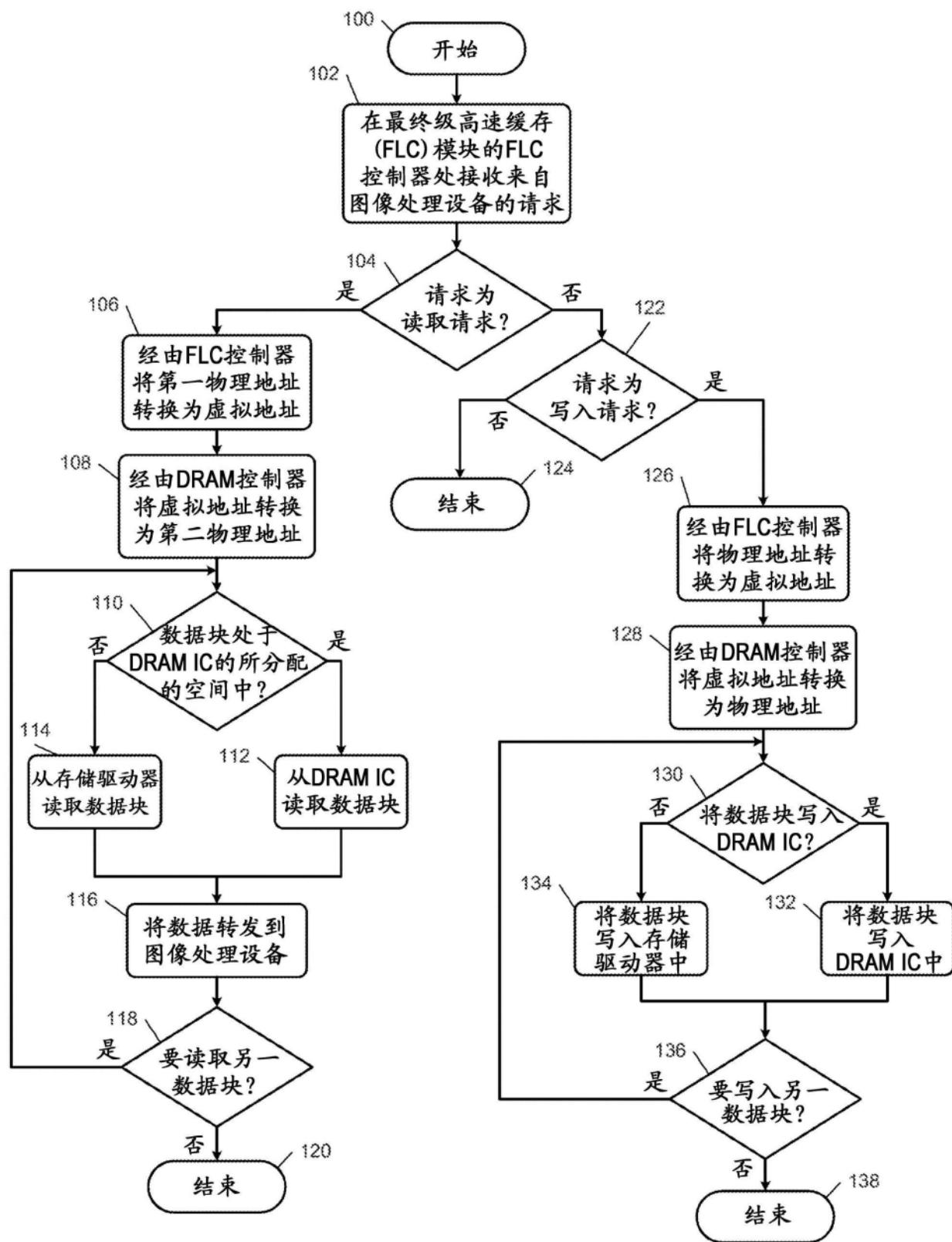

- [0022] 图4图示了操作图2的数据访问系统的方法。

- [0023] 在附图中，附图标记可以被重复利用以识别相似的和/或相同的元件。

## 具体实施方式

[0024] 下面的示例中的至少一些示例包括最终级高速缓存 (final level cache “FLC”) 模块和存储驱动器。FLC模块被用作虚拟存储，并且存储驱动器被用作物理存储。数据在从物理存储读取或写入物理存储之前首先从虚拟存储读取或被写入虚拟存储。FLC模块和存储驱动器中的存储器在本文中被称为内容可寻址存储器 (CAM)。FLC模块的控制模块使用下面描述的CAM技术来控制对FLC模块和存储驱动器中的存储器的访问。CAM技术和其他所公开的特征在使存储器访问速率最大化并使功率消耗最小化的同时减小设备中的DRAM的所需要的存储能力。该设备可以是网络设备或无线网络设备。设备的示例包括但不限于计算机、移动电话、平板电脑、相机等等。下面的示例中的DRAM一般不被用作主存储器，而是相反被用作虚拟存储器和/或被用作最终级的高速缓存。

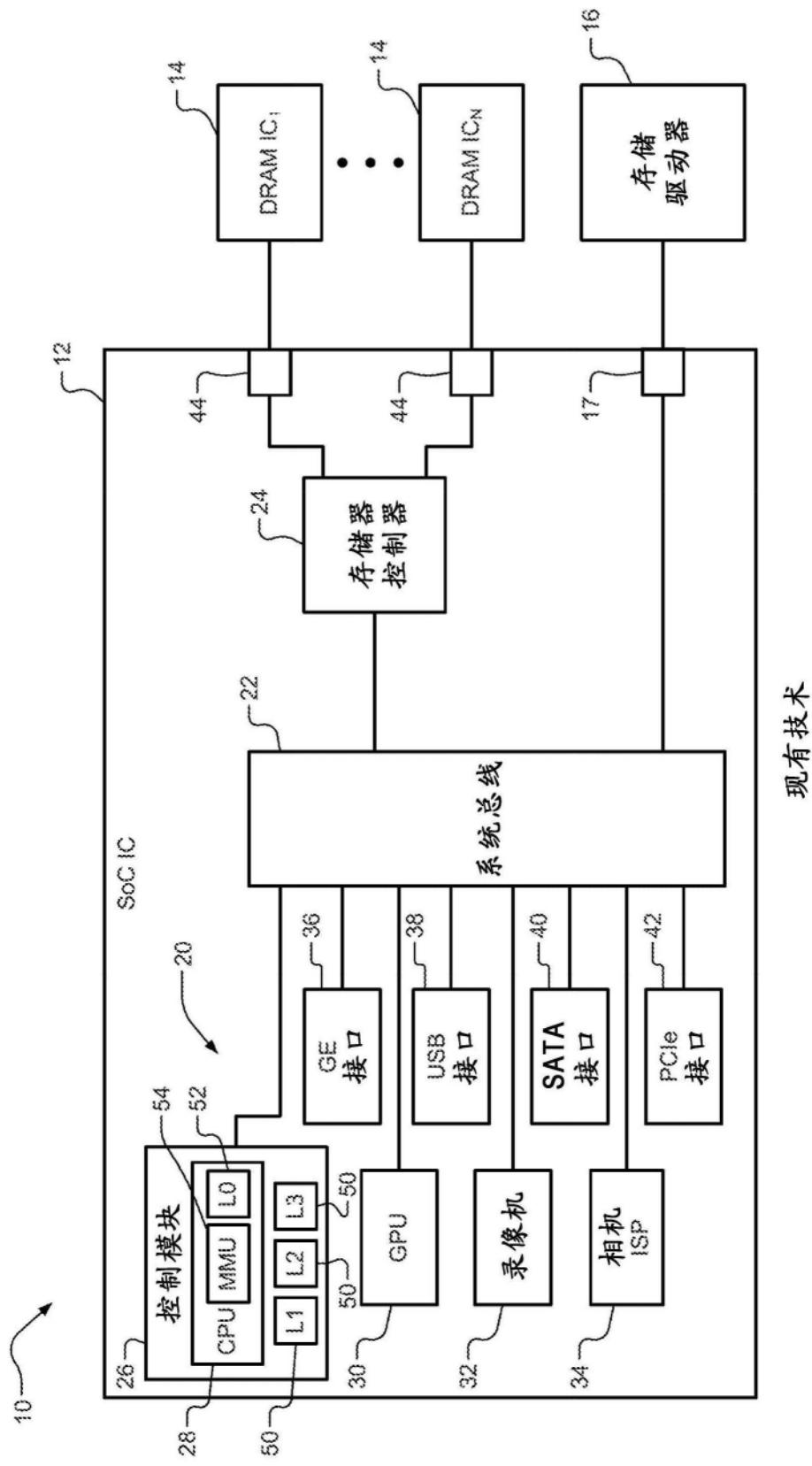

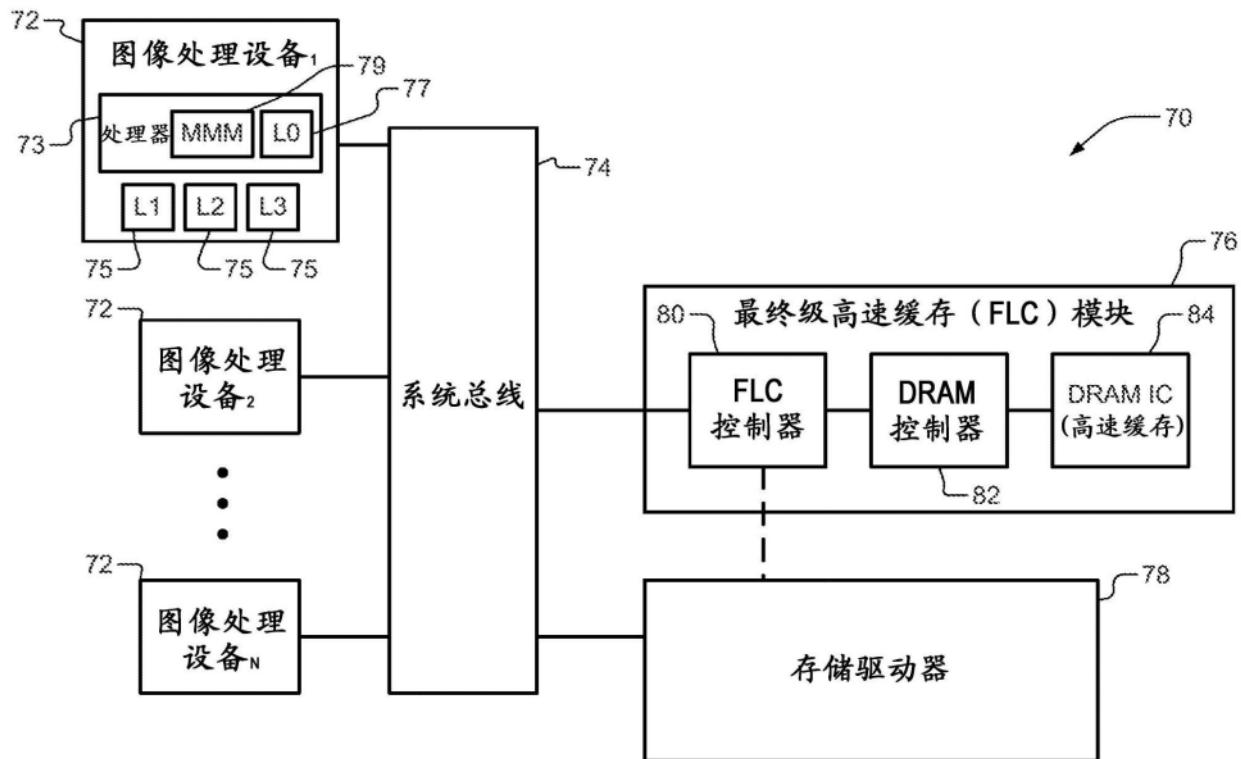

[0025] 图2示出了数据访问系统70，其包括图像处理设备72、系统总线74、FLC模块76和存储驱动器78。数据访问系统70可以被实现在例如计算机、移动电话、平板电脑、服务器和/或其他设备中。图像处理设备72可以包括例如：中央处理器 (或中央处理单元 (CPU))；图形处理器 (或图形处理单元 (GPU))；录像机；相机图像信号处理器 (ISP)；诸如吉比特 (Gb) 以太网接口的以太网接口；诸如通用串行总线 (USB) 接口和串行高级技术附件 (SATA) 接口的串行接口；以及外围组件互连快速 (PCIe) 接口；和/或其他图像处理设备。图像处理设备72可以被实现在一个或多个模块中。作为示例，图像处理设备72中的第一图像处理设备被示出为包括高速缓存存储器，例如以下各项中的一项或多项：零级 (L0) 高速缓存、一级 (L1) 高速缓存、二级 (L2) 高速缓存或三级 (L3) 高速缓存。在示出的示例中，第一图像处理设备可以包括中央处理器73和L1-L3高速缓存75。中央处理器73可以包括L0高速缓存77。中央处理器73还可以包括存储器管理模块 (MMU) 79，其能够控制对高速缓存75、77的访问。下面描述的由图像处理设备执行的任务可以由例如中央处理器73和/或MMU 79执行。

[0026] 图像处理设备72还经由系统总线74连接到FLC模块76。图像处理设备72经由总线和 (i) 在图像处理设备72与系统总线74之间以及 (ii) 在系统总线74与存储驱动器78之间的接口连接到存储驱动器78。接口可以包括例如以太网接口、串行接口、PCIe接口和/或嵌入式多媒体控制器 (eMMC) 接口。存储驱动器78可以位于世界上的远离图像处理设备72和/或FLC控制器80的任何地方。存储驱动器78可以经由一个或多个网络 (例如，WLAN、互联网络或远程存储网络 (云)) 与图像处理设备72和/或FLC控制器80进行通信。

[0027] FLC模块76包括FLC控制器80、DRAM控制器82和DRAM IC 84。DRAM IC 84主要被用作虚拟存储,而存储驱动器78被用作物理存储。图像处理设备72对DRAM IC 84和存储驱动器78进行寻址,如同它们是单个存储设备。当读取和/或写入数据时,图像处理设备72将存储请求发送到FLC控制器80。FLC控制器80经由DRAM控制器82访问DRAM IC 84和/或访问存储驱动器78。FLC控制器80可以(如由虚线所指示的)直接地或经由系统总线74访问存储驱动器。

[0028] 本文描述了数据访问系统70的各种示例。在第一示例中,FLC模块76被实现在与图像处理设备72、系统总线74和存储驱动器78分离的SoC中。在第二示例中,图像处理设备72中的一个图像处理设备是CPU实现的图像处理设备。图像处理设备72中的一个图像处理设备可以被实现在与FLC模块76和存储驱动器78分离的SoC中。作为另一示例,图像处理设备72和系统总线74被实现在与FLC模块76和存储驱动器78分离的SoC中。在另一示例中,图像处理设备72、系统总线74和FLC模块76被实现在与存储驱动器78分离的SoC中。下面描述了数据访问系统70的其他示例。

[0029] DRAM IC 84可以被用作最终级的高速缓存。DRAM IC 84可以具有各种存储容量。例如,DRAM IC 84可以具有用于移动电话应用的1-4GB的存储容量,用于个人计算机应用的4-32GB的存储容量,以及用于服务器应用的32GB-1太字节(T)的存储容量。

[0030] 存储驱动器78可以包括闪速存储器(例如,NAND闪速存储器)、固态存储器、固态驱动器(SSD)、硬盘驱动器(HHD)和/或其他非易失性存储器。存储驱动器78可以是混合驱动器并且包括例如固态存储器和旋转存储介质。存储驱动器78可以具有比DRAM IC 84多的存储容量。例如,存储驱动器78可以包括比DRAM IC 84多4-16倍的存储。作为另一示例,存储驱动器78可以具有比DRAM IC 84多一数量级的存储容量。DRAM IC 84可以包括高速DRAM,并且存储驱动器78可以包括低速DRAM。换言之,DRAM IC 84的速度比存储驱动器78中的DRAM的速度快。

[0031] 存储在DRAM IC 84中的数据可以是最近访问的、最经常访问的和/或具有最高相关联的优先级的数据。存储在DRAM IC 84中的数据可以包括被锁定的数据。被锁定的数据指的是总是存储在DRAM IC 84中的数据。被锁定的数据可以被更新。存储在DRAM IC 84中的数据可以比存储在存储驱动器78中的数据更频繁地被访问和/或具有更高优先级。

[0032] 在一些示例中,存储在DRAM IC 84中的数据不包括不频繁(例如,在比预定时间段内被访问多于预定次数)使用的软件应用、字体、软件代码、支持不同口语的备选代码和数据等等。这能够帮助使DRAM IC 84的大小要求最小化。不频繁使用的软件代码可以被称为“垃圾代码”并且可以不在启动过程期间从存储驱动器78被下载到DRAM IC 84。启动过程可以包括加载仅仅频繁使用的数据。随着DRAM IC 84的大小减小,性能提高并且功率消耗、电容和缓冲减小。随着电容和缓冲减小,延时减小。此外,通过消耗较少的功率,提高对应的设备的电池寿命。

[0033] FLC控制器80响应于从图像处理设备72接收到请求来执行CAM技术。CAM技术包括将由图像处理设备72提供的请求的第一物理地址转换为虚拟地址。这些虚拟地址与由图像处理设备72原先生成的虚拟地址无关且不同,并被映射到由图像处理设备72寻址的第一物理地址。DRAM控制器82将由FLC控制器80生成的虚拟地址转换(或映射)到第二物理地址。如果第二物理地址未处于DRAM IC 84中,则FLC控制器80可以(i)从存储驱动器78取读数据,

或者(ii)可以向图像处理设备72中的对应的图像处理设备指示(或信号通知)已经发生高速缓存未命中。从存储驱动器78取读数据可以包括将由FLC控制器80生成的虚拟地址映射到第三物理地址以访问存储驱动器78中的数据。高速缓存未命中可以由FLC控制器80在将物理地址转化为虚拟地址时检测到和/或由DRAM控制器82在将虚拟地址转换为第二物理地址时检测到。DRAM控制器82可以信号通知FLC控制器80已经发生高速缓存未命中,并且接着FLC控制器80可以信号通知图像处理设备72中的一个图像处理设备高速缓存未命中或者可以针对数据对存储驱动器78进行访问。

[0034] 如果FLC控制器80信号通知图像处理设备72中的一个图像处理设备已经发生高速缓存未命中,则图像处理设备72中的对应的图像处理设备可以访问存储驱动器78中的数据。这可以包括(i)基于第一物理地址来访问存储驱动器78中的数据,(ii)将原先生成的虚拟地址映射到第三物理地址并且接着基于第三物理地址来访问存储驱动器78,或者(iii)将第一物理地址映射到第三物理地址并且接着基于第三物理地址来访问存储驱动器78。CAM技术包括在DRAM IC 84与存储驱动器78之间进行地址映射。

[0035] 例如,CAM技术可以提供全集关联地址转化。这可以包括将第一物理地址与存储在FLC控制器80的目录中的所有虚拟地址进行比较。全集关联地址转化可以由FLC控制器80用于将对应的数据请求的第一物理地址转化为第二虚拟地址(或由FLC控制器80生成的虚拟地址)。这可以包括将第一物理地址与第一目录中的所有地址进行比较以找到用于转换到虚拟地址的匹配。全集关联地址转化还可以由DRAM控制器82用于将第二虚拟地址与第二目录、DRAM IC 84和/或存储驱动器78中的所有入口的所有地址进行比较以找到用于转换到第二虚拟地址的匹配。在初始启动之后位于DRAM IC 84中的数据的命中率可以取决于DRAM IC 84的大小高达100%。DRAM IC 84的大小可以被调整以确保在处理器和/或图像处理器设备的最小空闲时间的情况下接近100%的命中率。例如,这可以使用用于移动电话应用的1-4GB DRAM IC、用于个人计算机应用的4-32GB DRAM IC以及用于服务器应用的32-500GB DRAM IC来完成。

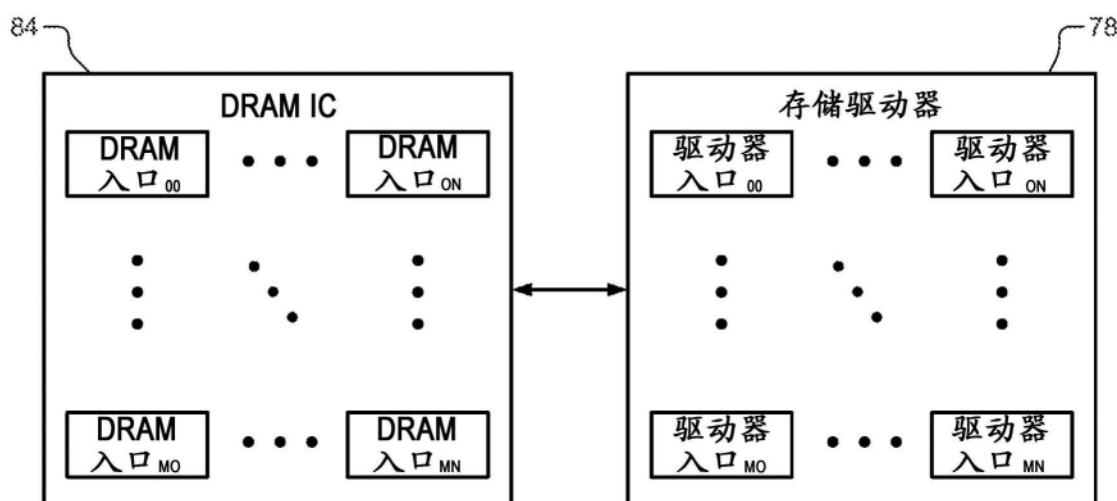

[0036] 除了图2,图3示出了数据访问系统70的DRAM IC 84和存储驱动器78的入口。DRAM IC 84可以包括DRAM入口<sub>00-MN</sub>。存储驱动器78可以具有驱动器入口<sub>00-MN</sub>。DRAM入口<sub>00-MN</sub>中的每个入口的地址可以被映射到驱动器入口<sub>00-MN</sub>中的一个或多个地址。结果,存储在DRAM入口<sub>00-MN</sub>中的一个或多个DRAM入口中的数据的第一部分可以对应于存储在驱动器入口<sub>00-MN</sub>中的数据的第二部分。存储在DRAM入口<sub>00-MN</sub>中的数据可以包括提供关于存储在驱动器入口<sub>00-MN</sub>中的数据的信息的元数据。该信息可以包括存储在驱动器入口<sub>00-MN</sub>中的数据的数据类型和/或数据长度。

[0037] 作为示例,DRAM入口<sub>00-MN</sub>中的每个DRAM入口可以具有例如16KB的存储容量。驱动器入口<sub>00-MN</sub>中的驱动器入口可以具有16GB的存储容量。如果数据要从DRAM入口<sub>00-MN</sub>中的一个DRAM入口被读取或被写入DRAM入口<sub>00-MN</sub>中的一个DRAM入口并且DRAM入口<sub>00-MN</sub>中的一个DRAM入口是满的和/或不具有与请求相关联的所有数据,则访问驱动器入口<sub>00-MN</sub>中的对应的驱动器入口。因此,DRAM IC 84和存储驱动器78可以被划分成存储器块。DRAM IC 84中的每个存储器块可以具有存储驱动器78中的相应的一个或多个存储器块。存储器的这种映射和划分对于图2的图像处理设备72可以是透明的。

[0038] 在操作期间,图像处理设备72中的一个图像处理设备可以生成针对数据块的请求

信号。如果数据块不位于DRAM IC 84中，则FLC控制器80可以访问存储驱动器78中的数据块。当FLC控制器80正在从存储驱动器78访问数据时，FLC控制器80可以将总线错误信号(或警报信号)发送回到请求数据的图像处理设备。总线错误信号可以指示FLC控制器80正在访问数据并且结果系统总线74未准备好将数据传送到图像处理设备72。总线错误信号的传输可以被称为从FLC模块76到图像处理设备和/或图像处理设72的SoC的“总线终止”。图像处理设备72可以在等待总线准备好的同时执行其他任务。其他任务可以包括使用已经存储在例如图像处理设备的SoC中的一个或多个高速缓存(例如,L0-L3高速缓存)中的数据。这还使处理器和/或图像处理设备的空闲时间最小化。

[0039] 如果执行顺序访问，则FLC控制器80和/或DRAM控制器82可以执行对存储在预计要在未来被访问的地址处的数据的预测性取读。这可以发生在启动期间和/或在启动之后。FLC控制器80和/或DRAM控制器82可以：跟踪数据和/或软件使用；评价要被运行的代码行；跟踪存储器访问模式；并且基于该信息来预测预计要被访问的数据的下一地址。下一地址可以是DRAM IC 84和/或存储驱动器78的地址。作为示例，FLC控制器80和/或DRAM控制器82在独立于和/或没有先前接收针对数据的请求的情况下可以访问存储在存储驱动器78中的数据并将数据传送到DRAM IC 84。作为另一示例，FLC控制器80和/或DRAM控制器82在独立于和/或没有先前接收针对数据的请求的情况下可以访问存储在DRAM IC 84中的数据并将数据传送到系统总线74和/或图像处理设备72中的一个。

[0040] 参考图4的方法进一步描述数据访问系统70的操作。尽管下面的任务主要参考图2-4中的示例进行描述，但是这些任务可以容易地被修改以适用于本公开内容的其他示例。这些任务可以迭代地被执行。

[0041] 该方法在100处开始。在102处，FLC控制器80从图像处理设备72中的一个图像处理设备接收请求。该请求可以是读取请求或写入请求。

[0042] 在104处，FLC控制器80确定接收到的请求是否为读取请求。在该请求为读取请求时执行任务106，否则执行任务122。在106处，FLC控制器80将在接收到的请求中提供的第一物理地址转换为虚拟地址。虚拟地址可以与DRAM IC 84中的物理地址和/或存储驱动器78中的物理地址相关联。

[0043] 在108处，DRAM控制器82将虚拟地址转换为第二物理地址。FLC控制器80和/或DRAM控制器82可以包括用于将第一物理地址映射到虚拟地址和用于将虚拟地址映射到第二物理地址的一个或多个转化映射表。这些表可以在FLC控制器80与DRAM控制器82之间共享。

[0044] 在110处，DRAM控制器82确定第二物理地址是否处于DRAM IC 84中并且因此确定对应的数据块是否处于DRAM IC 84的所分配的空间中。如果第二物理地址处于DRAM IC 84中，则执行任务112，否则执行任务114。

[0045] 在112处并且基于第二物理地址，DRAM控制器82从DRAM IC 84读取与接收到的请求相关联的一个或多个第一数据块。第一数据块中的每个数据块可以具有DRAM IC 84中的对应的物理地址。

[0046] 在114处并且基于第二物理地址，FLC控制器80从存储驱动器78读取与接收到的请求相关联的一个或多个第二数据块。一个或多个第二数据块可以包括第一数据块。第二数据块中的每个数据块可以具有存储驱动器78中的对应的物理地址。第二数据块和存储驱动器78的对应地址可以分别对应于第一数据块和DRAM IC 84的对应地址。

[0047] 在116处,将从DRAM IC 84或存储驱动器78读取的数据转发到发送接收到的请求的图像处理设备。在118处,针对在102处接收到的请求,FLC控制器80和/或DRAM控制器82可以确定是否存在要从DRAM IC 84和/或存储驱动器78读取的额外的数据。如果存在要读取的额外的数据,则执行任务110,否则该方法可以在120处结束。作为返回到任务110的备选并且针对在102处接收到的请求,如果存在要读取的额外的数据并且如果存在要转换的另一物理地址,则可以在任务118之后执行任务106。

[0048] 在122处,FLC控制器80确定接收到的请求是否为写入请求。如果接收到的请求为写入请求,则执行任务126,否则该方法可以在124处结束。在126处,FLC控制器80将在接收到的请求中提供的第一物理地址转换为虚拟地址。虚拟地址可以与DRAM IC 84中的物理地址和/或存储驱动器78中的物理地址相关联。在128处,DRAM控制器82将虚拟地址转换为第二物理地址。任务126和128可以使用以上提到的映射表来完成。

[0049] 在130处,DRAM控制器82确定第二物理地址是否处于DRAM IC 84中并且因此确定对应的数据块是否要被写入DRAM IC 84中的所分配的空间。如果第二物理地址处于DRAM IC 84中,则执行任务132,否则执行任务134。

[0050] 在132处并且基于第二物理地址,DRAM控制器82将接收到的请求相关联的一个或多个第一数据块写入DRAM IC 84。第一数据块中的每个数据块可以具有DRAM IC 84中的对应的物理地址。

[0051] 在134处并且基于第二物理地址,FLC控制器80将与接收到的请求相关联的一个或多个第二数据块写入存储驱动器78。一个或多个第二数据块可以包括第一数据块。第二数据块中的每个数据块可以具有存储驱动器78中的对应的物理地址。第二数据块和存储驱动器78的对应地址可以分别对应于第一数据块和DRAM IC 84的对应地址。

[0052] 在136处,针对在102处接收到的请求,FLC控制器80和/或DRAM控制器82可以确定是否存在要写入DRAM IC 84和/或存储驱动器78的额外的数据。如果存在要写入的额外的数据,则执行任务130,否则该方法可以在138处结束。作为返回到任务130的备选并且针对在102处接收到的请求,如果存在要写入的额外的数据并且如果存在要转换的另一物理地址,则可以在任务136之后执行任务126。

[0053] 图4的上述任务旨在为说明性示例;可以取决于应用顺序地、同步地、同时地、连续地、在交叠的时间段期间或者以不同的顺序来执行这些任务。此外,取决于示例和/或事件的顺序,可以不执行或跳过这些任务中的任何。

[0054] 上述示例可以经由网络中的服务器(可以被称为“云”)实现。各服务器中的每个服务器可以包括FLC模块(例如,FLC模块76)并相互通信。各服务器可以共享存储在DRAM IC和存储驱动器中的DRAM和/或存储器。各服务器中的每个服务器可以经由网络访问其他服务器中的DRAM和/或存储驱动器。FLC模块中的每个FLC模块可以与图2的FLC模块类似地操作,但是还可以经由云访问其他服务器中的每个服务器中的DRAM和/或存储器。在服务器与云之间传输的信号可以在传输之前被加密并在到达云的服务器和/或网络设备后解密。服务器还可以共享和/或访问云中的存储器。作为示例,由各服务器中的一个服务器的FLC控制器生成的虚拟地址可以对应于以下中的物理地址:FLC控制器的FLC模块的DRAM;各服务器中的一个服务器的存储驱动器;其他服务器中的一个服务器的FLC模块的DRAM;其他服务器中的一个服务器的存储驱动器;或者云的存储设备。各服务器中的一个服务器的FLC控制器

和/或图像处理设备可以在发生高速缓存未命中时访问其他FLC模块、存储驱动器和/或存储设备中的DRAM和/或存储器。

[0055] 上述示例还可以被实现在包括以下的数据访问系统中：具有多个芯片的多芯片模块；交换机；具有初级FLC模块的初级芯片。多芯片模块经由交换机连接到初级芯片模块。FLC模块中的每个FLC模块可以与图2的FLC模块类似地操作，但是还可以经由交换机访问其他芯片中的每个芯片中的DRAM和/或存储器。作为示例，由各芯片中的一个芯片的FLC控制器生成的虚拟地址可以对应于以下中的物理地址：FLC控制器的FLC模块的DRAM；各芯片中的一个芯片的存储驱动器；其他芯片中的一个芯片的FLC模块的DRAM；其他芯片中的一个芯片的存储驱动器；或者云的存储设备。各芯片中的一个芯片的FLC控制器和/或图像处理设备可以在发生高速缓存未命中时访问其他FLC模块、存储驱动器和/或存储设备中的DRAM和/或存储器。

[0056] 作为示例，多芯片模块中的次级DRAM和初级芯片中的初级DRAM中的每个可以具有1GB的存储容量。初级芯片中的存储驱动器可以具有例如64GB的存储容量。作为另一示例，数据访问系统可以被使用在汽车中。初级芯片可以为例如中央控制器、模块、处理器、引擎控制模块、传输控制模块和/或混合控制模块。初级芯片可以被用于控制相关系统的对应方面，例如油门位置、火花定时、燃油定时、在传动轮之间的转变等等。多芯片模块中的次级芯片中的每个次级芯片可以与特定车辆系统相关联，特定车辆系统例如照明系统、娱乐系统、空调系统、排气系统、导航系统、音频系统、视频系统、制动系统、操纵系统等等并且被用于控制对应系统的各方面。

[0057] 作为又一示例，上述示例还可以被实现在包括主机（或SoC）和混合驱动器的数据访问系统中。主机可以包括中央处理器或其他图像处理设备并且经由接口与混合驱动器进行通信。接口例如为例如GE接口、USB接口、SATA接口、PCIe接口或其他适当的接口。混合驱动器可以包括第一存储驱动器和第二存储驱动器。第一存储驱动器包括FLC模块（例如，图2的FLC模块76）。FLC模块的FLC控制器在确定是否从FLC模块和第二存储驱动器的DRAM读取数据和/或将数据写入FLC模块和第二存储驱动器的DRAM时执行CAM技术。

[0058] 作为另一示例，上述示例还可以被实现在包括SoC、第一DRAM（或高速缓存）、第二DRAM和非易失性存储器的存储系统中。SoC与第一DRAM、分立DRAM和非易失性存储器是分离的。第一DRAM可以存储高优先级和/或频繁访问的数据。高百分比的数据访问请求可以被指向存储在第一DRAM中的数据。作为示例，99%或更多的数据访问请求可以被指向存储在第一DRAM中的数据和/或剩余的1%或更少的数据访问请求可以被指向存储在第二DRAM和/或非易失性存储器中的数据。低优先级和/或较不频繁地访问的数据可以被存储在第二DRAM和/或非易失性存储器中。作为示例，用户可以打开多个网页浏览器。第二DRAM能够具有高带宽接口和每位低成本的存储器存储容量并且能够处置广泛的应用。第二DRAM通常展示比高速缓存或第一DRAM长的延时时间段。针对当前使用的或最频繁使用的网页浏览器的内容可以被存储在第二DRAM和/或非易失性存储器中。

[0059] SoC可以包括一个或多个控制模块、接口模块、高速缓存（或FLC）模块以及图形模块。高速缓存模块可以与图2的FLC模块类似地操作。控制模块经由接口模块连接到高速缓存模块。高速缓存模块被配置为基于相应的层次级别来访问第一DRAM、第二DRAM和非易失性存储器。各控制模块中的每个控制模块可以包括相应的L1高速缓存、L2高速缓存和L3高

速缓存。各控制模块中的每个控制模块还可以包括一个或多个额外的高速缓存，例如L4高速缓存或其他最高级高速缓存。许多信号线（或导电元件）可以存在于SoC与第一DRAM之间。这允许在SoC与第一DRAM之间对数据的快速并行和/或串行传送。在SoC与第一DRAM之间的数据传送比(i)在SoC与第二DRAM之间以及(ii)在SoC与非易失性存储器之间的数据传送快。

[0060] 第一DRAM可以含有具有与L3高速缓存622、L4高速缓存和/或最高级高速缓存相同或比其高的层次级别的第一部分。第一DRAM的第二部分可以具有与第二DRAM和/或非易失性存储器相同或比其低的层次级别。第二DRAM可以具有比第一DRAM高的层次级别。非易失性存储器可以具有与第二DRAM相同或比其高的层次级别。控制模块可以基于高速缓存需要来改变第一DRAM、第二DRAM和/或非易失性存储器中的每个的部分或全部的层次级别。

[0061] 控制模块、连接到接口模块的图形模块和/或连接到接口模块的（在SoC的内部或外部的）其他设备可以将请求信号发送到高速缓存模块以存储和/或访问第一DRAM、第二DRAM和/或非易失性存储器中的数据。高速缓存模块可以控制对第一DRAM、第二DRAM和非易失性存储器的访问。作为示例，控制模块、图像模块和/或连接到接口模块的其他设备可以不知道连接到SoC的DRAM的数量和/或大小。

[0062] 高速缓存模块可以将从控制模块、图像模块和/或连接到接口模块的其他设备接收到的第一逻辑块地址和请求转换为(i)第一DRAM、第二DRAM和/或非易失性存储器的物理块地址，或者(ii)第二逻辑块地址。第二逻辑块地址可以通过第一DRAM、第二DRAM和/或非易失性存储器被转换为物理块地址。高速缓存模块可以存储用于将第一逻辑块地址转换为第二逻辑块地址和/或将第一逻辑块地址转换为物理块地址的一个或多个查找表（例如，全集关联查找表）。结果，高速缓存模块以及第一DRAM、第二DRAM和非易失性存储器中的一个或多个可以用作与控制模块、图像模块和/或连接到接口模块的其他设备相关的单个存储器。图形模块可以控制视频数据从控制模块和/或SoC到显示器和/或其他视频设备的输出。

[0063] 控制模块可以在(i)高速缓存模块以及(ii)L1高速缓存、L2高速缓存和L3高速缓存之间交换（或传送）数据、数据集、程序和/或其部分。高速缓存模块可以在第一DRAM、第二DRAM和非易失性存储器中的两个或更多个之间交换（或传送）数据、数据集、程序和/或其部分。这可以独立于控制模块和/或在没有从控制模块接收到执行传送的控制信号的情况下执行。数据、数据集、程序和/或其部分在第一DRAM、第二DRAM和非易失性存储器中的一个或多个中的存储位置可以基于对应的优先级、使用的频率、访问的频率和/或与数据、数据集、程序和/或其部分相关联的其他参数。对数据、数据集、程序和/或其部分的传送可以包括传送数据块。数据块中的每个数据块可以具有预定大小。作为示例，从第二DRAM到第一DRAM的数据的交换可以包括多个传送事件，其中每个传送事件包括传送数据块（例如，16KB的数据）。

[0064] 高速缓存模块可以使用第一DRAM作为关联高速缓存、指向的映射的高速缓存和/或全关联高速缓存并使用对应的高速缓存协议来访问第一DRAM。高速缓存模块可以被称为最末（或最高）级高速缓存（LLC）控制器。

[0065] 第一DRAM可以具有第一预定量的存储容量（例如，0.25GB、0.5GB、1GB或8GB）。0.5GB第一DRAM是典型L2高速缓存的512倍。第二DRAM可以具有第二预定量的存储容量（例如，针对非基于服务器的系统为1GB或更多或者针对基于服务器的系统为256GB或者更多）。

非易失性存储器可以具有第三预定量的存储容量(例如,256GB或更多)。非易失性存储器可以包括固态存储器,例如闪速存储器或磁阻随机访问存储器(MRAM)和/或旋转磁性介质。非易失性存储器可以包括SSD和HDD。尽管存储系统具有第二DRAM和非易失性存储器,但是第二DRAM和非易失性存储器中的任一个可以不被包含在存储系统中。

[0066] 作为另一示例,上述示例还可以被实现在包括SoC和DRAM IC的存储系统中。SoC可以包括经由环形总线访问DRAM IC的多个控制模块(或处理器)。环形总线可以是使访问延时最小化的双向总线。如果成本比性能更重要,则环形总线可以为单向总线。中介设备可以位于控制模块与环形总线之间和/或在环形总线与DRAM IC之间。例如,上述高速缓存模块可以位于控制模块与环形总线之间或者在环形总线与DRAM IC之间。

[0067] DRAM IC可以为L3高速缓存、L4高速缓存和/或最高级高速缓存。控制模块可以共享DRAM IC和/或具有DRAM IC的指定部分。例如,DRAM IC的第一部分可以被分配为针对第一控制模块的高速缓存。DRAM IC的第二部分可以被分配为针对第二控制模块的高速缓存。DRAM IC的第三部分可以被分配为针对第三控制模块的高速缓存。DRAM IC的第四部分可以不被作为高速缓存分配。

[0068] 作为另一示例,上述示例还可以被实现在服务器系统中。服务器系统可以被称为存储系统并且包括多个服务器。服务器包括相应的存储系统,其经由网络(或云)相互通信。各存储系统中的一个或多个存储系统可以位于云中。存储系统中的每个存储系统可以包括相应的SoC。

[0069] SoC可以具有相应的第一DRAM、第二DRAM、固态非易失性存储器、非易失性存储器和I/O端口。I/O端口可以经由诸如外围组件互连快速(PCIe)信道的相应的I/O信道和诸如外围组件互连快速(PCIe)信道的相应网络接口与云进行通信。I/O端口、I/O信道和网络接口可以为以太网端口、信道和网络接口并且以预定速度(例如,每秒1吉比特(Gb/s)、10Gb/s、50Gb/s等等)传送数据。网络接口中的一些可以位于云中。多个存储系统的连接提供低成本的分布式的且可扩展的服务器系统。所公开的存储系统和/或服务器系统中的多个可以相互通信并且被包含在网络(云)中。

[0070] 固态非易失性存储器中的每个固态非易失性存储器可以包括例如NAND闪速存储器和/或其他固态存储器。非易失性存储器中的每个非易失性存储器可以包括固态存储器和/或旋转磁性介质。非易失性存储器中的每个非易失性存储器可以包括SSD和/或HDD。

[0071] 服务器系统的架构提供DRAM作为高速缓存。DRAM可以被分配作为针对相应SoC的L3高速缓存、L4高速缓存和/或最高级高速缓存并且具有高带宽和大存储容量。堆叠的DRAM可以包括例如DDR3存储器、DDR4存储器、低功率两倍数据速率类型四(LPDDR4)存储器、宽I/O2存储器、HMC存储器和/或其他适当的DRAM。SoC中的每个SoC可以具有一个或多个控制模块。控制模块经由相应的环形总线与对应的DRAM进行通信。环形总线可以是双向总线。这提供在控制模块与对应的DRAM之间的高带宽和最小延时。

[0072] 控制模块中的每个可以访问存储在以下各项中的数据和/或程序:相同SoC或不同SoC的控制模块;DRAM中的任何DRAM;固态非易失性存储器中的任何固态非易失性存储器;和/或非易失性存储器中的任何非易失性存储器。

[0073] SoC和/或SoC的端口可以具有媒体访问控制器(MAC)地址。SoC的控制模块(或处理器)可以具有相应的处理器集群地址。控制模块中的每个控制模块可以使用对应的MAC地址

和处理器集群地址来访问相同SoC中或另一SoC中的其他控制模块。SoC的控制模块中的每个控制模块可以访问DRAM。第一SoC的控制模块可以通过发送具有第二SoC的MAC地址和第二SoC中的第二控制模块的处理器集群地址的请求信号来请求存储在连接到第二SoC的DRAM中的数据和/或程序。

[0074] SoC和/或SoC中的控制模块中的每个可以存储一个或多个地址转化表。地址转化表可以包括和/或提供针对以下的转化:SoC的MAC地址;控制模块的处理器集群地址;DRAM、固态非易失性存储器以及非易失性存储器中的存储器单元的逻辑块地址;和/或DRAM、固态非易失性存储器以及非易失性存储器中的存储器单元的物理块地址。

[0075] 作为示例,数据和程序可以被存储在固态非易失性存储器和/或非易失性存储器中。数据和程序和/或其部分可以通过网络被分布到SoC和控制模块。由控制室模块运行所需要的程序和/或数据可以在本地被存储在控制模块位于其中的SoC的DRAM、固态非易失性存储器和/或非易失性存储器中。控制模块可以接着从DRAM、固态非易失性存储器和/或非易失性存储器访问运行所需要的程序和/或数据并将这些程序和数据传送到控制模块中的高速缓存。在SoC与网络之间和/或在各SoC之间的通信可以包括无线通信。

[0076] 作为另一示例,上述示例还可以被实现在包括SoC的服务器系统中。SoC中的一些SoC可以被包含在相应的服务器中并且可以被称为服务器SoC。SoC中的一些SoC(被称为同伴SoC)可以被包含在第一SoC的服务器中或者可以与第一SoC的服务器是分离的。第一SoC包括相应的:控制模块(例如,中央处理模块)的集群;集群内环形总线、FLC模块、存储器控制模块、FLC环形总线以及一个或多个跳跃总线。跳跃总线(i)经由芯片间总线构件和对应的端口在服务器SoC与同伴SoC之间延伸以及(ii)通过同伴SoC延伸。跳跃总线可以指的是延伸到跳跃总线站、适配器或节点以及一个或多个SoC的对应端口和从其延伸的总线。跳跃总线可以通过跳跃总线和/或一个或多个SoC延伸。往来于跳跃总线的单次数据传送可以被称为单跳。可以当在发送设备与接收设备之间传送数据时执行多跳。数据可以在每个时钟周期在各总线站之间行进直到数据到达目的地。本文公开的每个总线站可以被实现为模块并且包括用于基于时钟信号来将数据在各设备之间进行传送的逻辑。此外,本文公开的每个总线可以具有用于数据的串行和/或并行传输的任何数量的信道。

[0077] 控制模块的集群中的每个集群具有集群内环形总线中的对应集群内环形总线。集群内环形总线是双向的并且提供在集群中的每个集群中的控制模块之间的通信。集群内环形总线可以具有用于由控制模块访问在集群内环形总线上传输的数据信号的环形总线站。环形总线站可以表现为信号复示器(repeater)和/或访问节点。控制模块可以经由环形总线站连接到集群内环形总线并访问集群内环形总线。数据可以围绕集群内环形总线从在环形总线站的第一环形总线站处的第一控制模块被传输到在环形总线站的第二环形总线站处的第二控制模块。控制模块中的每个控制模块可以是中央处理单元或处理器。

[0078] 存储器控制模块中的每个存储器控制模块可以控制对FLC模块中的相应FLC模块的访问。FLC模块可以被堆叠在服务器SoC上。FLC模块中的每个FLC模块包括FLC(或DRAM)并且可以被实现为本文所公开的FLC模块中的任何FLC模块并且与本文所公开的FLC模块中的任何FLC模块类似地操作。存储器控制模块可以访问在FLC环形总线上的相应环形总线站处的FLC环形总线并且在环形总线站与FLC模块之间传送数据。备选地,FLC模块可以直接访问在相应环形总线站处的FLC环形总线。存储器控制模块中的每个存储器控制模块可以包括

存储器时钟，其生成针对FLC模块中的相应FLC模块和/或针对环形总线和/或跳跃总线的总线站的存储器时钟信号。总线站可以间接地经由环形总线和/或跳跃总线或者直接从存储器控制模块接收存储器时钟信号。数据可以基于存储器时钟信号通过总线站进行循环。

[0079] FLC环形总线可以是双向总线并且具有两种类型的环形总线站 $S_{RB}$ 和 $S_{RH}$ 。环形总线站中的每个环形总线站可以执行为信号复示器和/或访问节点。环形总线站 $S_{RB}$ 连接到除了跳跃总线之外的设备。该设备可以包括：集群间环形总线0；FLC模块和/或存储器控制模块；以及图形处理模块。集群间环形总线提供(i)在各集群之间以及(ii)在交叉环形站之间的连接。交叉环形总线站提供对集群间环形总线的访问并且可以将集群间环形总线连接到在在(i)各集群以及(ii)环形总线站之间延伸的环形总线延伸。环形总线站处于FLC环形总线上。集群间环形总线和交叉环形总线站提供(iii)在第一集群与第二FLC环形总线的环形总线站之间以及(iv)在第二集群与第一FLC环形总线的环形总线站之间的连接。这允许控制模块访问第二FLC模块的FLC并且允许控制模块访问第一FLC模块的FLC。

[0080] 集群间环形总线可以包括芯片内迹线和芯片间迹线。芯片内迹线在服务器SoC的内部并且在(i)环形总线站中的一个与(ii)端口中的一个之间延伸。芯片外迹线在服务器SoC的外部并且在端口的相对应之间延伸。

[0081] 服务器SoC中的每个服务器SoC的环形总线站 $S_{RH}$ 连接到FLC环形总线和跳跃总线中的对应一者。跳跃总线中的每个跳跃总线具有多个跳跃总线站 $S_{HB}$ ，其提供对跳跃总线中的每个跳跃总线的相应接口访问。跳跃总线站 $S_{HB}$ 可以被执行为信号复示器和/或访问节点。

[0082] 第一跳跃总线、环形总线站和第一跳跃总线站提供在(i)FLC环形总线与(ii)服务器SoC中的液晶显示器(LCD)接口以及同伴SoC的接口之间的连接。LCD接口可以连接到显示器并且可以经由GPM控制。同伴SoC的接口包括串行附接小型计算机系统接口(SAS)接口和PCIe接口。同伴SoC的接口是图像处理器(IP)接口。

[0083] 接口连接到相应的端口，相应的端口可以连接到诸如外围设备的设备。SAS接口和PCIe接口可以分别经由端口连接到SAS兼容设备和PCIe兼容设备。作为示例，存储驱动器可以连接到端口。存储驱动器可以是硬盘驱动器、固态驱动器或混合驱动器。端口可以连接到图像处理设备。以上公开了图像处理设备的示例。第四SoC可以经由芯片间总线构件(还被称为菊链构件)菊链到第三SoC。芯片间总线构件是第一跳跃总线的构件。额外的SoC可以经由连接到第一跳跃总线的端口菊链到第四SoC。服务器SoC、控制模块和FLC模块可以经由FLC环形总线、第一跳跃总线和/或第三SoC来与第四SoC进行通信。作为示例，SoC可以是南桥芯片并且控制在(i)服务器SoC与(ii)连接到端口的外围设备之间的通信和中断的传送。

[0084] 第二跳跃总线提供经由环形总线站和第二跳跃总线站在(i)FLC环形总线与(ii)服务器SoC中的接口之间的连接。服务器SoC中的接口可以包括以太网接口、一个或多个PCIe接口以及混合(或组合)接口。以太网接口可以为10GE接口并且经由第一以太网总线连接到网络。以太网接口可以经由第一以太网总线、网络和第二以太网总线与第二SoC进行通信。网络可以为以太网络、云网络和/或其他以太网兼容网络。一个或多个PCIe接口可以包括例如第三代PCIe接口PCIe3和迷你型PCIe接口(mPCIe)。PCIe接口可以连接到固态驱动器。混合接口可以是SATA和PCIe兼容的以根据SATA和/或PCIe协议来将数据传送到SATA兼容的设备和/或PCIe兼容的设备和/或从SATA兼容的设备和/或PCIe兼容的设备传送。作为示例，PCIe接口可以连接到存储驱动器，例如固态驱动器或混合驱动器。接口具有用于连接

到在服务器SoC的外部的设备的相应端口。

[0085] 第三跳跃总线可以经由环形总线站连接到环形总线并且可以经由跳跃总线站连接到LCD接口和端口。LCD接口可以连接到显示器并且可以经由GPM控制。端口可以连接到一个或多个同伴SoC。第四跳跃总线可以经由环形总线站连接到(i)环形总线并且(ii)可以经由跳跃总线站连接到接口。接口可以为以太网接口、PCIe接口和混合接口。接口具有相应的端口。

[0086] 服务器SoC和/或其他服务器SoC可以经由集群间环形总线互相通信。服务器SoC和/或其他服务器SoC可以经由相应的以太网接口和网络互相通信。

[0087] 同伴SoC可以包括相应的控制模块。控制模块可以访问和/或控制经由跳跃总线站对接口的访问。在一个实施例中，不包括控制模块。控制模块可以连接到各跳跃总线站的对应的跳跃总线站和/或各接口的对应的接口并且与其进行通信。

[0088] 作为另一示例，上述示例还可以被实现在移动设备的电路中。移动设备可以是计算机、蜂窝电话、或其他无线网络设备。电路包括SoC。SoC可以被称为移动SoC。SoC可以被称为同伴SoC。移动SoC包括：控制模块的集群；集群内环形总线，FLC模块，存储器控制模块，FLC环形总线，以及一个或多个跳跃总线。跳跃总线(i)经由芯片间总线构件和对应的端口在移动SoC与同伴SoC之间以及(ii)通过同伴SoC延伸。

[0089] 集群内环形总线是双向的并且提供在各控制模块之间的通信。集群内环形总线可以具有用于由控制模块访问在集群内环形总线上传输的数据信号的环形总线站。环形总线站可以执行为信号复示器和/或访问节点。控制模块可以经由环形总线站连接到集群内环形总线并访问集群内环形总线。数据可以围绕集群内环形总线从在环形总线站的第一环形总线站处的第一控制模块被传输到在环形总线站的第二环形总线站处的第二控制模块。数据可以在在每个时钟周期行进在总线站之间直到数据到达目的地。控制模块中的每个控制模块可以是中央处理单元或处理器。

[0090] 存储器控制模块可以控制对FLC模块的访问。在一个实施例中，不包括存储器控制模块。FLC模块可以被堆叠在移动SoC上。FLC模块可以为FLC或DRAM并且可以被实现为本文所公开的FLC模块中的任何FLC模块并且与本文所公开的FLC模块中的任何FLC模块类似地操作。存储器控制模块可以访问在FLC环形总线上的相应环形总线站处的FLC环形总线并且在环形总线站与FLC模块之间传送数据。备选地，FLC模块可以直接访问在相应环形总线站处的FLC环形总线。存储器控制模块可以包括存储器时钟，其生成针对FLC模块、环形总线和/或跳跃总线的总线站的存储器时钟信号。总线站可以间接地经由环形总线和/或跳跃总线或者直接从存储器控制模块接收存储器时钟信号。数据可以基于存储器时钟信号而通过总线站进行循环。

[0091] FLC环形总线可以是双向总线并且具有两种类型的环形总线站S<sub>RB</sub>和S<sub>RH</sub>。环形总线站中的每个环形总线站可以执行为信号复示器和/或访问节点。环形总线站S<sub>RB</sub>连接到除了跳跃总线之外的设备。该设备可以包括：集群；FLC模块和/或存储器控制模块；以及图形处理模块。

[0092] 移动SoC的环形总线站S<sub>RH</sub>连接到FLC环形总线和跳跃总线中的对应一个。跳跃总线中的每个跳跃总线具有多个跳跃总线站S<sub>HB</sub>，其提供对跳跃总线的对应的跳跃总线的接口访问。跳跃总线站S<sub>HB</sub>可以执行为信号复示器和/或访问节点。

[0093] 第一跳跃总线、环形总线站和第一跳跃总线站连接在(i)FLC环形总线与(ii)液晶显示器(LCD)接口、视频处理模块(VPM)、以及同伴SoC的接口之间。LCD接口处于服务器SoC中并且可以连接到显示器并且可以经由GPM控制。同伴SoC的接口包括蜂窝接口、无线局域网(WLAN)接口以及图像信号处理器接口。蜂窝接口可以包括用于与其他移动和/或无线设备进行无线通信的物理层设备。物理层设备可以根据长期演进(LTE)标准和/或第三代(3G)移动电信标准、第四代(4G)移动电信标准和/或第五代(5G)移动电信标准来操作和/或发送和接收信号。WLAN接口可以根据蓝牙®、Wi-Fi®和/或其他WLAN协议来操作并且与移动设备的WLAN设备中的其他网络设备进行通信。ISP接口可以连接到在同伴SoC的外部的图像处理设备(或图像信号处理设备),例如存储驱动器或其他图像处理设备。接口可以经由相应的端口连接到在同伴SoC的外部的设备。ISP接口可以连接到在移动设备的外部的设备。

[0094] 同伴SoC可以经由芯片间总线构件连接到移动SoC。芯片间总线构件是第一跳跃总线的构件。额外的SoC可以经由连接到第一跳跃总线的端口菊链到同伴SoC。移动SoC、控制模块和FLC模块可以经由FLC环形总线和第一跳跃总线与同伴SoC进行通信。

[0095] 第二跳跃总线提供经由环形总线站和第二跳跃总线站在(i)FLC环形总线与(ii)移动SoC中的接口之间的连接。移动SoC中的接口可以包括以太网接口、一个或多个PCIe接口以及混合(或组合)接口。以太网接口可以为10GE接口并且经由端口连接到以太网络。一个或多个PCIe接口可以包括例如第三代PCIe接口PCIe3和迷你型PCIe接口(mPCIe)。PCIe接口可以连接到固态驱动器。混合接口可以是SATA和PCIe兼容的以根据SATA和/或PCIe协议来将数据传送到SATA兼容的设备和/或PCIe兼容的设备和/或从SATA兼容的设备和/或PCIe兼容的设备传送。作为示例,PCIe接口可以经由端口连接到存储驱动器。存储驱动器可以为固态驱动器或混合驱动器。接口具有用于连接到在移动SoC的外部的设备的相应端口。

[0096] 同伴SoC可以包括控制模块。控制模块可以经由跳跃总线站访问和/或控制对VPM和接口的访问。在一个实施例中,不包括控制模块。控制模块可以连接到跳跃总线站、VPM 1198和/或接口并且与跳跃总线站、VPM 1198和/或接口进行通信。

[0097] 本公开内容中描述的无线通信能够以与IEEE标准802.11-2012、IEEE标准802.16-2009、IEEE标准802.20-2008和/或蓝牙核心规范v4.0完全或部分兼容地来执行。在各种实施方案中,蓝牙核心规范v4.0可以通过蓝牙核心规范附录2、3或4中的一个或多个来修改。在各种实施方案中,IEEE 802.11-2012可以由制定的IEEE标准802.11ac、制定的IEEE标准802.11ad和/或制定的IEEE标准802.11ah来补充。

[0098] 尽管术语第一、第二、第三等等可以在本文中用于描述各种芯片、模块、信号、元件和/或组件,但是这些项目不应由这些术语限制。这些术语可以仅仅被用于将一个项目与另一项目区分开。诸如“第一”、“第二”和其他数值术语的术语当在本文中使用时不暗示序列或顺序,除非由上下文清楚地指示。因此,下面讨论的第一项目能够被命名为第二项目,而不脱离示例性示例的教导。

[0099] 此外,各种术语被用于描述在各组件之间的物理关系。当第一元件被称为“连接到”、“接合到”或“耦合到”第二元件时,第一元件可以直接连接、接合、设置、应用或耦合到第二元件,或者可能存在居间元件。相反,当元件被称为“直接连接到”、“直接接合到”或“直接耦合到”另一元件时,可以不存在居间元件。以第一元件“连接到”、“接合到”或“耦合到”

第二元件开始暗示第一元件可以“直接连接到”、“直接接合到”或“直接耦合到”第二元件。用于描述在各元件之间的关系的其他词语应当以类似的方式来解读(例如，“在…之间”对比“直接在…之间”，“相邻”对比“直接相邻”，等等)。

[0100] 前面的描述实质上仅仅是说明性的并且不旨在以任何方式限制本公开内容、其应用或使用。本公开内容的广泛教导能够以各种形式来实现。因此,当本公开内容包括特定示例时,本公开内容的真实范围不应当受此限制,因为其他修改在研究附图、说明书和下面的权利要求书后将变得显而易见。如本文中所使用的,短语A、B和C中的至少一个应当被理解为意味着使用非排他性的逻辑OR的逻辑(A OR B OR C),并且不应当被理解为意味着“A中的至少一个、B中的至少一个和C中的至少一个”。应当理解,方法内的一个或多个步骤可以以不同顺序(或并发地)来运行而不改变本公开内容的原理。

[0101] 在本申请中,包括下面的定义,术语‘模块’或术语‘控制器’可以利用术语‘电路’来代替。术语‘模块’和术语‘控制器’可以指代以下各项、为其的部分或者包括以下各项:专用集成电路(ASIC);数字分立电路、模拟分立电路或混合的模拟/数字分立电路;数字集成电路、模拟集成电路或混合的模拟/数字集成电路;组合逻辑电路;现场可编程门阵列(FPGA);运行代码的(共享、专用或组)处理器电路;存储由处理器电路运行的代码的(共享、专用或组)存储器电路;提供所描述的功能的其他适当的硬件组件;或者以上的一些或全部的组合(例如片上系统中)。

[0102] 模块或控制器可以包括一个或多个接口电路。在一些示例中,接口电路可以包括连接到局域网(LAN)、互联网、广域网(WAN)或其组合的有线接口或无线接口。本公开内容的任何给出的模块或控制器的功能可以被分布在经由接口电路连接的多个模块和/或控制器之中。例如,多个模块和/或控制器可以允许负载均衡。在另一示例中,服务器(也被称为远程或云)模块或(远程或云)控制器可以代表客户端模块和/或客户端控制器来完成某种功能。

[0103] 如以上所使用的术语代码可以包括软件、固件和/或微代码,并且可以指代程序、例程、函数、类、数据结构和/或对象。术语共享处理器包括运行来自多个模块和/或控制器的一些或所有代码的单个处理器电路。术语组处理器电路包括与额外的处理器电路组合地运行来自一个或多个模块和/或控制器的一些或所有代码的处理器电路。对多个处理器的引用包括在分立管芯上的多个处理器电路、在单个管芯上的多个处理器电路、单个处理器电路的多核心、单个处理器电路的多线程、或者以上的组合。术语共享存储器电路包括存储来自多个模块和/或控制器的一些或所有代码的单个存储器电路。术语组存储器电路包括与额外的存储器组合地存储来自一个或多个模块和/或控制器的一些或所有代码的存储器电路。

[0104] 术语存储器电路是术语计算机可读介质的子集。如本文中所使用的计算机可读介质不包括通过介质(例如在载波上)传播的瞬态电信号或电磁信号;术语计算机可读介质可以因此被认为是有形的且非瞬态的。非瞬态的有形的计算机可读介质的非限制性示例是非易失性存储器电路(例如闪速存储器电路、可擦可编程只读存储器电路或者掩码只读存储器电路)、易失性存储器电路(例如静态随机访问存储器电路或动态随机访问存储器电路)、磁性存储介质(例如模拟或数字磁带或硬盘驱动器)以及光学存储介质(例如CD、DVD或蓝光碟)。

[0105] 本申请中描述的装置和方法可以部分地或完全地由通过将通用计算机配置为运行体现在计算机程序中的一个或多个特定功能的专用计算机实现。以上描述的功能框和流程图元件用作软件说明，其能够由技术人员或程序员的日常工作转化成计算机程序。

[0106] 计算机程序包括存储在至少一个非瞬态的有形的计算机可读介质上的机器可执行指令。计算机程序还可以包括或依靠所存储的数据。计算机程序可以包括与专用计算机的硬件交互的基本输入/输出系统(BIOS)、与专用计算机的特定设备交互的设备驱动器、一个或多个操作系统、用户应用、背景服务、背景应用等等。

[0107] 计算机程序可以包括：(i)要解析的描述性文本，例如HTML(超文本标记语言)或XML(可扩展标记语言)，(ii)汇编代码，(iii)由编译器从源代码生成的目标代码，(iv)用于由解释器运行的源代码，(v)用于由即时编译器编译和运行的源代码，等等。仅仅作为示例，源代码可以使用来自包括以下的语言的语法来编写：C、C++、C#、面向对象C、Haskell、Go、SQL、R、Lisp、**Java®**、Fortran、Perl、Pascal、Curl、OCaml、**Javascript®**、HTML5、Ada、ASP(动态服务器页面)、PHP、Scala、Eiffel、Smalltalk、Erlang、Ruby、**Flash®**、Visual Basic®、Lua和Python®。

[0108] 权利要求书中记载的元件中没有一个旨在为35U.S.C. §112(f)的意义内的装置加功能元件，除非元件使用短语“用于…的装置”来明确记载，或者在使用“用于…的操作”或“用于…的步骤”的方法权利要求的情况下。

图1

图2

图3

图4