(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5743377号

(P5743377)

(45) 発行日 平成27年7月1日(2015.7.1)

(24) 登録日 平成27年5月15日(2015.5.15)

|                |           |        |        |       |

|----------------|-----------|--------|--------|-------|

| (51) Int.Cl.   | F 1       |        |        |       |

| HO 1 L 21/336  | (2006.01) | HO 1 L | 29/78  | 301 G |

| HO 1 L 29/78   | (2006.01) | HO 1 L | 21/28  | 301 R |

| HO 1 L 21/28   | (2006.01) | HO 1 L | 21/285 | C     |

| HO 1 L 21/285  | (2006.01) | HO 1 L | 27/08  | 321 D |

| HO 1 L 21/8238 | (2006.01) | HO 1 L | 29/58  | G     |

請求項の数 3 (全 11 頁) 最終頁に続く

|               |                               |           |                                                                                                                                                                    |

|---------------|-------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2008-522827 (P2008-522827)  | (73) 特許権者 | 390040660<br>アプライド マテリアルズ インコーポレ<br>イテッド<br>A P P L I E D M A T E R I A L S, I<br>N C O R P O R A T E D<br>アメリカ合衆国 カリフォルニア州 95<br>054 サンタ クララ バウアーズ ア<br>ベニュー 3050 |

| (86) (22) 出願日 | 平成18年7月12日 (2006.7.12)        | (74) 代理人  | 100109726<br>弁理士 園田 吉隆                                                                                                                                             |

| (65) 公表番号     | 特表2009-503817 (P2009-503817A) | (74) 代理人  | 100101199<br>弁理士 小林 義教                                                                                                                                             |

| (43) 公表日      | 平成21年1月29日 (2009.1.29)        |           |                                                                                                                                                                    |

| (86) 國際出願番号   | PCT/US2006/027165             |           |                                                                                                                                                                    |

| (87) 國際公開番号   | W02007/018944                 |           |                                                                                                                                                                    |

| (87) 國際公開日    | 平成19年2月15日 (2007.2.15)        |           |                                                                                                                                                                    |

| 審査請求日         | 平成21年6月4日 (2009.6.4)          |           |                                                                                                                                                                    |

| 審判番号          | 不服2013-24122 (P2013-24122/J1) |           |                                                                                                                                                                    |

| 審判請求日         | 平成25年12月4日 (2013.12.4)        |           |                                                                                                                                                                    |

| (31) 優先権主張番号  | 11/185,180                    |           |                                                                                                                                                                    |

| (32) 優先日      | 平成17年7月20日 (2005.7.20)        |           |                                                                                                                                                                    |

| (33) 優先権主張国   | 米国 (US)                       |           |                                                                                                                                                                    |

最終頁に続く

(54) 【発明の名称】ゲート電極構造及び製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート電極を形成する方法であって、

半導体基板上に誘電体層を形成するステップと、

原子層堆積によって該誘電体層上に第一金属領域を形成するステップと、

該第一金属領域上に第二金属領域を形成するステップと、

を含み、

該第一金属領域と該第二金属領域は、ゲート電極として二層構造をなすこと、

該第一金属領域と該第二金属領域がクラスタシステム内に形成され、該第一金属領域が

該第二金属領域の堆積前に空気に曝されず、

該第一金属領域の厚さを 20 オングストロームから 80 オングストロームの間で変化させ、

該第一金属領域は TaN の層であり、該第二金属領域は少なくとも 200 オングストロームの厚さの Ta の層である、

前記方法。

## 【請求項 2】

電界効果トランジスタを形成する方法であって、

半導体基板において一組のソース領域とドレイン領域を形成するステップと、

該半導体基板上に誘電体層を形成するステップと、

原子層堆積を用いて該ゲート誘電体層の上に第一金属領域を堆積させるステップと、

10

20

該第一金属領域が第二金属領域の形成前に空気に曝されることなく、該第一金属領域の上に該第二金属領域を形成するステップと、

を含み、

該第一金属領域と該第二金属領域は、ゲート電極として二層構造をなすこと、

該第一金属領域の厚さを20オングストロームから80オングストロームの間で変化させ、

該第一金属領域はTaNの層であり、該第二金属領域は少なくとも200オングストロームの厚さのTaの層である、

前記方法。

【請求項3】

該第一金属領域と該第二金属領域がクラスタシステム内に形成される、請求項2記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般的には、集積回路製造中に用いられる材料及び方法に関するものである。

【背景技術】

【0002】

マイクロ電子デバイスは、種々の導電層が互いに相互接続して電子信号をデバイス内に伝達することを可能にする集積回路として半導体基板上に製造される。このようなデバイスの一例は、相補型金属酸化膜半導体(CMOS)電界効果トランジスタ(FET)である。

【0003】

ゲート電極は、集積回路の一部である。例えば、CMOSトランジスタは、半導体基板に形成されるソース領域とドレイン領域との間に配置されたゲート構造を備える。ゲート構造は、一般に、ゲート電極とゲート誘電体を備える。ゲート電極は、ゲート誘電体の上に配置されて、ゲート誘電体の下のドレイン領域とソース領域との間に形成されるチャネル領域における電荷キャリアの流れを制御する。ゲート誘電体は、典型的には、約4.0以上の誘電率を有する薄い(例えば、10~50オングストローム)材質層を備える(例えば、二酸化ケイ素(SiO<sub>2</sub>)、オキシ窒化ケイ素(SiON)、二酸化ハフニウム(HfO<sub>2</sub>)等)。シリコンCMOSデバイスのゲート長が100nm未満まで縮小されるにつれて、新たな高誘電率(K)材料がおそらく酸化シリコンに取って代わるであろう。更に、金属ゲートもおそらく多結晶シリコン(ポリシリコン)ゲートに取って代わるであろう。例えば、あるCMOSトランジスタにおいて、ゲート電極は、金属(例えば、チタン(Ti)、タンタル(Ta)、タンゲステン(W)等)及び金属含有導電性化合物(例えば、窒化チタン(TiN)、窒化タンタル(TaN)、窒化タンゲステン(WN)等)の少なくとも一つから形成されるのがよい。ゲート電極の従来の材料としてのポリシリコンを金属や金属含有化合物で置換すると、ポリシリコン減少効果と関連している、望まれていない電圧降下を減少させるだけでなく、ドライブ電流性能やCMOSトランジスタの操作可能な速度が増大する。

【0004】

上述したように、ポリシリコンゲートの代わりとして代替材料が研究されてきた。更に、ポリシリコンゲートの代わりとして代替構造が研究されてきた。このような構造の例としては、異なる仕事関数値を有する導電金属から作られた二層構造が含まれる。これらの構造は、ここでは二層ゲート又はサンドイッチゲートと呼ばれ、基板上に形成されたゲート誘電体を含み、第一金属層と第二金属層がゲート誘電体の上に形成されている。半導体ゲート電極に対する改善は代替ゲート構造や材料の使用によってなされてきたが、集積回路デバイスの性能を改善するためにいっそうの改善が求められている。

【概要】

## 【0005】

本発明の一態様は、ゲート電極を形成する方法であって、半導体基板上に誘電体層を形成するステップと、原子層堆積によって誘電体層上に第一金属領域を形成するステップと、第一金属領域上に第二金属領域を形成するステップとを含む、前記方法に関する。ある種の実施形態において、第一金属領域はTaNを含み、第二金属領域はTaを含む。他の実施形態において、第一金属領域と第二金属領域は、クラスタシステム又は装置における堆積によって形成され、ここで、第一金属領域が形成され、第一金属領域の上に第二金属領域が形成され、第一金属領域は空気又は周囲大気に曝されない。

## 【0006】

本発明の他の態様は、電界効果トランジスタを形成する方法であって、半導体基板において一組のソース領域とドレイン領域を形成するステップと、半導体基板上に誘電体層を形成するステップと；原子層堆積を用いてゲート誘電体層の上に第一金属領域を堆積させるステップ、更に、第一金属層の上に第二金属領域を形成するステップとを含む、前記方法に関する。本明細書に開示される方法が特定のステップの順序に限定されることは理解される。例えば、すぐ上に記載される方法において、ソース領域とドレイン領域は、誘電体層と金属ゲート電極の形成の前か後に形成されてもよい。ある種の実施形態によれば、第一金属領域にはTaNが含まれ、第二金属領域にはTaが含まれる。ある種の実施形態において、第二金属領域はクラスタシステム内に第二金属領域の上に形成され、第一金属領域は第二金属層の形成前に空気又は周囲大気に曝されていない。

## 【0007】

ある種の実施形態によれば、第一金属領域の厚さを約0～80オングストロームの第一量だけ変化させると、組み合わせた第一領域と第二領域の有効仕事関数が第一領域の厚さを第二領域の形成前に空気に曝した以外は（例えば、非クラスタシステムにおいて第一領域と第二領域を形成することによって）同じ第一量だけ変化させた場合と比較して組み合わせた第一領域と第二領域の有効仕事関数の変化より少なくとも約20%だけ大きくなる。他の実施形態において、本方法は、第一金属領域の厚さを約0～80オングストロームの第一量だけ変化させることによって、組み合わせた第一領域と第二領域の仕事関数を第一領域の厚さが第二領域の形成前に空気に曝された以外は同じ第一量だけ変化させた場合と比較して組み合わせた第一領域と第二領域の有効仕事関数の変化より少なくとも約40%、60%又は80%だけ大きくするのに有効である。例えば、第一金属領域がTaNを含み、第二金属領域がTaを含む場合、約0～80オングストロームに第一金属領域の厚さを変化させることによる組み合わせた第一領域と第二領域の仕事関数の調整は、第二金属領域が900オングストロームで一定に保持され、第二金属領域が第一金属領域を空気に曝さずに第二金属領域に形成される場合、少なくとも約120mV、140mV、160mV、180mV又は200mVである。相対的に、第一金属領域が空気に曝された後に同じTaN iTaゲートスタック構造が形成される場合、0～80オングストロームに第一金属領域厚さを変化させることによって示される仕事関数調整は多くても約100mVである。

## 【0008】

本発明の他の態様は、集積回路を製造する方法であって、第一ドーパントプロファイルとともに、誘電体層と、誘電体層の上にTaNから作られた第一金属領域と、第一金属領域の上にTaから作られた第二金属領域とを備えるゲートスタックを有する第一導電型の少なくとも第一電界効果トランジスタを形成するステップと；第二ドーパントプロファイルとともに、誘電体層と、誘電体層の上に第一金属領域と、第一金属領域の上に第二金属領域を備えるゲートスタックを有する第二導電型の少なくとも第二電界効果トランジスタを形成するステップとを含み、ここで、第一ドーパントプロファイルと第二ドーパントプロファイルが実質的に同じである、前記方法に関する。一つ以上の実施形態において、本方法は、約0～80オングストロームの第一量だけ第一金属領域の厚さを変化させることによって第二領域の形成前に空気に曝された以外は第一領域の厚さが同じ第一量だけ変化させた場合の組み合わせた第一領域と第二領域の有効仕事関数の変化より少なくとも20

10

20

30

40

50

%、40%、60%、又は80%だけ組み合わせた第一領域と第二領域の仕事関数を大きくするのに有効である。

【0009】

他の実施形態において、少なくとも二つの電界効果トランジスタを含む集積回路が提供される。一実施態様によれば、集積回路は、第一ドーパントプロファイルとともに、誘電体層と、誘電体層の上に第一金属領域と、第一金属領域の上に第二金属領域とを備えるゲートスタックとを有する第一導電型と、第二ドーパントプロファイルとともに、誘電体層と、誘電体層の上に第一金属領域と、第一金属領域の上に第二金属領域とを備えるゲートスタックとを有する第一導電型の少なくとも第二電界効果トランジスタとを含み、ここで、第一ドーパントプロファイルと第二ドーパントプロファイルは実質的に同じであり、第一電界効果トランジスタと第二電界効果トランジスタの第二金属領域の厚さは実質的に同じであり、第一電界効果トランジスタと第二電界効果トランジスタの第一金属領域の厚さは約0オングストローム～20オングストロームであり、第一電界効果トランジスタの第一金属領域の厚さは第二電界効果トランジスタの第一金属領域の厚さと異なり、第一電界効果トランジスタのゲートスタックの仕事関数は第二電界効果トランジスタの仕事関数と少なくとも約20%だけ異なる。他の実施形態において、電界効果トランジスタのゲートスタック間の仕事関数の差は少なくとも40%、60%、60%だけ異なる。

10

【0010】

例え、ゲートスタックの第一金属領域がTaNから作られ、第二金属領域がTaから作られ、第一金属領域の厚さが約0オングストローム～80オングストロームに変化する場合、第一ゲートスタックにおける組み合わせた第一領域と第二領域の仕事関数は第二ゲートスタックの仕事関数と少なくとも約120mVだけ異なり得る。他の実施形態において、第一ゲートスタックと第二ゲートスタックの仕事関数は、第一領域の厚さの変化だけ作用する、少なくとも約160mV、180mV又は200mVだけ異なり得る。

20

【0011】

本発明の種々の態様及び実施形態の利点は、以下の詳細な説明から明らかである。上記の一般的な説明及び以下の詳細な説明はいずれも例示であり、特許を請求する本発明を更に説明するためのものであることは理解されるべきである。

【0012】

本発明の内容のより完全な認識は、添付の図面を参照する以下の詳細な説明によって理解され得る。

30

【詳細な説明】

【0013】

本発明の幾つかの例示的実施形態を記載する前に、本発明が以下の説明に示される構成又はプロセスステップの詳細に限定されないことは理解されるべきである。本発明は、他の実施形態も、種々の方法で実施されるか又は行われることも可能である。

【0014】

本発明の一態様は、ゲート電極及びゲート電極を含むデバイスを含むがこれらに限定されない製造品に関する。本発明の他の態様は、ゲート電極及びゲート電極を含むデバイスを製造する方法に関する。

40

【0015】

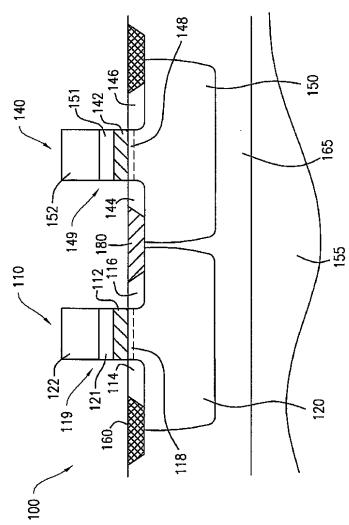

本発明の一つ以上の実施形態は、相補型金属酸化物半導体(CMOS)集積回路デバイスを形成するのに特に有用である方法を提供し、それに関連して記載される。他のデバイスや適用もまた、本発明の範囲内である。図1は、典型的なCMOSデバイスにおけるFET対を示す断面図の部分である。図示されるFET対は、NMOSFETとPMOSFETを備えているが、CMOSデバイスが追加のFETを含むことができ、且つ同じ導電型を有するFETを含むことができることは理解される。デバイス100は、p型材料によってドープされたシリコンウェハ155と、ウェハ155上のp型エピタキシャルシリコン層165と、エピタキシャル層165内で画成されたp型ウェル領域120とn型ウェル領域150と、p-ウェル120内で画成されたn型トランジスタ(NMOSFE

50

T ) 110 と n - ウェル 150 内で画成された p 型トランジスタ ( PMOS FET ) 140 とを備える。領域 180 は、NMOS 110 と PMOS 140 トランジスタを電気的に絶縁し、領域 160 は、一組のトランジスタ 110 と 140 を基板 155 上の他の半導体デバイスから電気的に絶縁する。

【 0016 】

本発明の一つ以上の実施形態によれば、NMOS トランジスタ 110 は、ゲート領域 119 と、ソース域 114 と、ドレイン領域 116 とを備える。ゲート領域 119 には、第一金属領域 121 と第二金属領域 122 とが含まれる。ソース領域とドレイン領域は、ゲート領域 119 の対向側の n 型領域である。チャネル領域 118 は、ソース域 114 とドレイン領域 116 との間におかれる。ゲート誘電体層 112 は、チャネル領域 118 と第一金属領域 121 を分離する。ゲート誘電体層 112 は、第一金属領域 121 をチャネル領域 118 から電気的に絶縁する。ゲート誘電体層 112 と第一金属領域 121 と第二金属領域 122 は、共にここではゲートスタックと呼ばれてもよい。ゲート誘電体領域 112 は、オキシ窒化物又は高 K 誘電体、例えば、HfO<sub>2</sub> であるのがよい。本明細書で用いられる高 K 誘電体は、約 4 より大きい誘電率を有する材料を意味する。第一金属領域 121 は、ALD によって形成されることが好ましい導体材料、典型的には窒化タンタル ( TaN ) のような金属を含む。第二金属領域 122 は、PVDF のような適切ないかなるプロセスによっても形成することができる金属、例えば、タンタルを含む。適切な電圧が p 型シリコンウェハ 155 とゲート領域 122 との間に印加される場合、p - ウェル 120 からの電子は、誘電体層 112 のすぐ下の領域 118 へ移動し、それによって、n 型チャネル 118 を生成する。ソース 114 とドレイン 116 との間に印加された電圧は、電流をソース 114 とドレイン 116 との間に流れさせる。

【 0017 】

一つ以上の実施形態によれば、PMOS トランジスタ 140 は、ゲート領域 149 と、ソース領域 144 と、ドレイン領域 146 とを備える。ゲート領域 149 には、第一金属領域 151 と第二金属領域 152 が含まれる。ソース領域とドレイン領域は、ゲート領域 149 の対向側の p 型領域である。チャネル領域 148 は、ソース領域 144 とドレイン領域 146 との間におかれる。ゲート誘電体 142 は、チャネル領域 148 と第一金属領域 151 を分離する。誘電体 142 は、第一金属領域 151 をチャネル領域 148 から電気的に絶縁する。誘電体は、オキシ窒化物又は高 K 誘電体、例えば、HfO<sub>2</sub> であり得る。ゲート誘電層 142 と第一金属領域 151 と第二金属領域 152 は、共に本明細書ではゲートスタックと呼ばれてもよい。

【 0018 】

一つ以上の実施形態において、第一金属領域 151 は、金属、典型的には TaN を含む。第二金属領域 152 は、金属、例えば、タンタルを含む。適切な電圧が p 型シリコンウェハ 155 とゲート領域 149 との間に印加される場合、n - ウェル 150 からの正孔は、誘電体層 142 のすぐ下の領域 148 へ移動し、それによって、p 型チャネル 148 を生成する。ソース 144 とドレイン 146 との間に印加された電圧は、電流をソース 144 とドレイン 146 との間に流れさせる。

【 0019 】

MOS デバイス設計は、複雑なプロセスである。例えば、MOSFET の設計において、ドライブ電流を最大にすることによってなされる改善によってリーク電流が増大する。逆に、リーク電流低下のような改善によって、ドライブ電流が負に影響する。金属ゲート電極は、ポリシリコンゲートと関連している減少効果を排除することによってドライブ電流を改善することができるが、金属が望まれていない仕事関数値を示すことから金属ゲートはリーク電流を増大してしまい、トランジスタデバイスの所望の電気的性質を負に影響させる。

【 0020 】

本発明の一つ以上の実施形態によれば、CMOS デバイスの改善された電気的性質は、電極仕事関数を変えることによって実現させることができ、デバイスの閾値電圧を変える

10

20

30

40

50

。このことにより、チャネルドーピングの減少を可能にすることことができ、ドーパントが減少したチャネル領域と通常関連している閾値未満のリーク電流が増加せずに、キャリア移動度とドライブ電流を改善することが予想される。

【0021】

一つ以上の実施形態によれば、組み合わせた第一領域と第二領域の仕事関数は、第一金属領域の厚さを約0~80オングストロームに変化させることによって変わり得る。第二金属領域の厚さがある値を超えて、第二金属領域の厚さを変化させることによってゲートスタックの仕事関数に影響しない場合、第一金属領域の厚さを変化させることによってゲートスタックの仕事関数が変わる。一つ以上の実施形態によれば、第二金属領域の形成前に第一金属領域を空気に曝さずに第一領域と第二金属領域を形成することによって、第一金属領域が第二金属領域の形成前に空気に曝された場合に形成されたゲートスタックの仕事関数調整と比較してゲートスタックのかなり大きい仕事関数調整が達成され得る。一つ以上の実施形態によれば、第一金属領域と第二金属領域は、クラスタシステム内に形成されることができ、第一領域は空気から分離され、第二金属領域はクラスタシステム内に形成される。

10

【0022】

本明細書に用いられる用語“ゲート”は、ゲートとドレインとソースを有する三つの末端電界効果トランジスタの絶縁ゲート電極を意味する。仕事関数は、デバイスを形成するために用いられた材料の電子特性と構造特性によって影響される。通常、MOSトランジスタにおけるゲート電極の仕事関数は、デバイスから許容され得る電気的性能を得るために伝導帯端に近く又は価電子帯端に近くなければならない。許容され得る仕事関数を得る材料は限定され、これらの材料の一部は半導体製造プロセスにおいて用いるのが難しい。NMOSデバイスに用いられる材料の例としては、Al及びTaSiNが挙げられるが、これらに限定されない。PMOSデバイスにおけるこのような材料の例としては、W、Ru、及びNiが挙げられるが、これらに限定されない。

20

【0023】

本発明の例示的実施形態には、電界効果トランジスタの仕事関数の改善された変調とゲート誘電体への不純物拡散の阻止が含まれる。一つ以上の実施形態によれば、原子層堆積(ALD)によって第一金属領域121、151の形成によって改善が達成される。ALD装置は、米国特許第6,287,965号に開示され、この開示内容は本明細書に援用されている。他のALDシステムや方法は、米国特許第6,784,096号、米国特許出願公開第2004/019069号に開示され、この開示内容は本明細書に援用されている。ある種の実施形態において、クラスタ装置においてゲート電極119、149を形成することによって改善が更に実現され、第一金属領域121、151と第二金属領域122、152が真空中でロードロックシステム内で堆積され、第一金属領域121、151が形成された後、空気に曝されない。ロードロックシステムで形成されるデバイスの第一金属領域の厚さを変化させることにより、第一金属領域が第二金属領域の形成前に空気に曝されている形成されたゲートスタックと比較してより広い範囲のゲートスタックの仕事関数調整が可能である。

30

【0024】

誘電体層112、142がオキシ窒化物である実施形態において、急速熱処理(RTP)を酸化物の形成に用いることができ、減結合プラズマ窒化物形成(NAD)をオキシ窒化物形成に用いることができる。高K誘電体が用いられる実施形態において、原子層堆積(ALD)を高K誘電体層の製造に用いることができる。好ましい実施形態では、誘電体層はALDによって形成される。金属層は、物理気相堆積(PVD)によって形成することができる。具体的な金属の選択は、個々の適用に左右される。基板やゲートスタック構造(第一金属領域と第二金属領域と誘電体層)によっては、60nmノード未満の仕事関数の要求は、二つのグループ: 近バンド端仕事関数とミッドギャップ仕事関数に分けることができる。バルクCMOS適用については、近バンド端仕事関数を有する金属材料を用いることができる。シリコンオンインシュレータ(SOI)適用については、ミッドギャ

40

50

ツップ仕事関数を有する金属材料を用いることができる。

【0025】

ある種の実施形態においては、第一金属領域のALD、一具体的実施形態においては、第一金属領域のTaNのALDにより、それによって形成された二層ゲート構造の一つ以上の利点が得られる。一つ以上の実施形態において、誘電体層上に引き続き形成されるPVD金属層は誘電体層に対する接着を増強する。ある種の実施形態において、ALD堆積誘電体層は、また、化学バリヤが改善されて、引き続き形成されたPVD金属がプロセスの間も後も誘電体層と相互作用することを防止することを援助する。ALDの使用により、ALDプロセスが他のプロセスより誘電体層に対する損傷が少ないとからより安定な誘電体層が得られる。一つ以上の実施形態において、ALD堆積された誘電体層は、より良好な仕事関数調整を与え、いすれが、誘電体層の物理的厚さの制御によってデバイス閾値の微調整を可能にする。

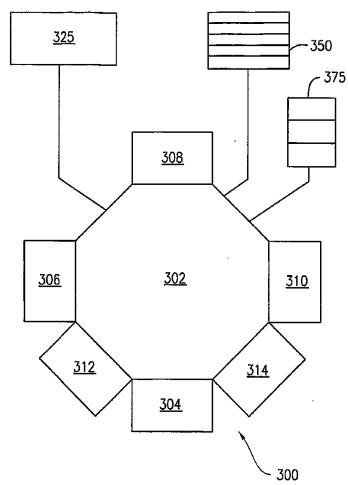

【0026】

例示的なクラスタシステム又はツール300を図2に示す。クラスタツールは、サイクルタイムを短縮させること、操作者が処理するウエハを少なくすること、微粒子汚染を減少させること、分子汚染を減少させること、また、難しいプロセスを開始させることのために、ロードロックチャンバ又は真空チャンバ内で幾つかのプロセスを組み合わせている。クラスタシステムの例としては、アプライドマテリアルズ、サンタクララ、カリフォルニアから入手できるCentura又はEnduraシステムが挙げられる。図2は、米国特許出願公開第20040050325号、出願第101243,377号に記載されるガス分配システムを有する基板クラスタ処理システム300の一実施態様を示す概略図であり、この開示内容は本明細書に援用されている。処理システム300には、一つ以上のロードロックチャンバ304と、一つ以上のプロセスチャンバ306、308、310、312と、クールダウンチャンバ314とが含まれてもよく、全てが中央トランスファチャンバ302に取り付けられている。処理システム300には、更に、処理システム300の種々の動作を制御するためのシステムコントローラ325と、処理システム300に種々の形のエネルギーを供給するための電源350と、処理システム300内に含まれる種々の真空チャンバを排気するためのポンプ375とが含まれてもよい。各処理チャンバは、多くの基板処理操作、例えば、周期的な層堆積、化学気相堆積(CVD)、物理気相堆積(PVD)、原子層堆積(ALD)エッティング、前洗浄、脱ガス、位置合わせ、他の基板プロセスを行うために取り付けられ得る。トランスファツール、例えば、ロボット(図示せず)は、基板を一つ以上のチャンバへ、また、一つ以上のチャンバから搬送するために用いることができる。

【0027】

一つ以上のトランスファチャンバ302は、基板をシステム300内に搬送することを可能にしつつ超高真空条件を維持するために用いられる。システム300によって行われる具体的なプロセスが必要でないならば基板処理チャンバのいすれかがシステム300から除去されてもよい。一つの配置例において、処理チャンバ306と308は、高K誘電体層と第一金属領域を堆積させるように適合させた原子層堆積チャンバであってもよく、処理チャンバ310は、バルク第二金属領域を形成するように適合された周期的な堆積チャンバ、化学気相堆積チャンバ、又は物理気相堆積チャンバであってもよい。相互接続特徴部のアーチャ又は開口部にエッティングするために取り付けられた一つ以上のエッティングチャンバのような追加の処理チャンバが設けられてもよい。

【0028】

システム300の具体的な一配置は、本発明の一実施形態を示すためのものであり、本発明の範囲を制限するために用いるべきでない。他のツール/装置は、例えば、Novellusシステムズ、米国によって販売されるINOVAシステムを用いることができる。クラスタ又はマルチチャンバ処理システムの他の一例は、1993年2月16日に発行された“Stage Vacuum Wafer Processing System and Method”と称する米国特許第5,186,718号に開示され、この開示内容は本明細書に援用されている。

## 【0029】

クラスタシステムにおいてTaNを含む第一金属領域のALD堆積と第一金属領域の上にTaを含有する第二金属領域のPVD堆積が第一金属領域の厚さの変化の関数としてどのように仕事関数調整に影響したかを調べるために実験を行った。本明細書に用いられるクラスタ堆積、クラスタツール、また、クラスタシステムは、基板がデバイスの領域又は層の形成の間に周囲条件又は空気に曝されないように真空圧下でロードロックシステムでの領域又は層の連続形成を意味する。

## 【0030】

クラスタ堆積が閾値電圧に影響を及ぼすかを決定するためにTaN/Taから作られたゲートスタックの第一金属領域の種々の厚さの関数として閾値電圧調整の範囲を調べた。非クラスタ堆積が金属領域間の接合部に広範囲な酸化を導入するかを決定するために第一金属領域と第二金属領域間の接合部もまた調べた。金属/金属接合部での酸化がこのパラメータに影響を及ぼすかを決定するために等価酸化物厚さ(EOT)もまた調べた。本明細書に用いられるEOTは、高k誘電体MOSゲートの性能をSiO<sub>2</sub>ベースのMOSゲートの性能と比較するために用いられる数を意味する。言い換えれば、EOTは、より高誘電率kを特徴とする誘電体で得られたものと同じゲート容量を得るために必要とされるSiO<sub>2</sub>ゲート酸化物の厚さを示す。例えば、1nmのEOTは、k=39(SiO<sub>2</sub>のkは、3.9である)を特徴とする10nm厚誘電体の使用から得られる。

10

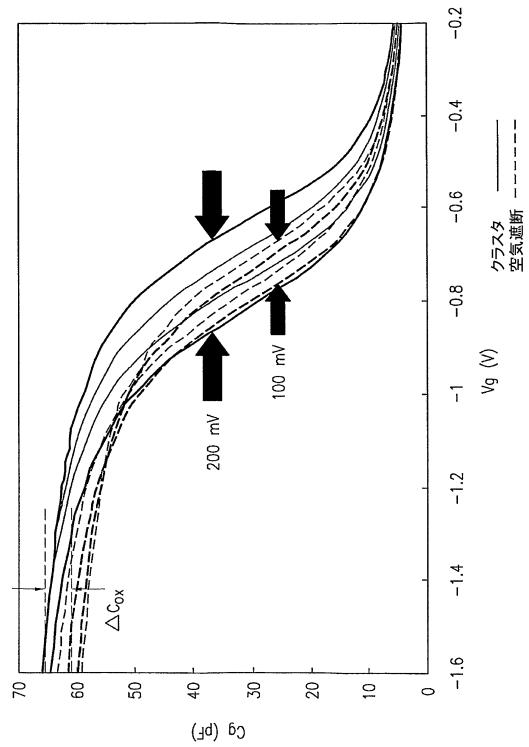

## 【0031】

2つのグループのシリコン基板、熱酸化によって形成されるオキシ窒化ケイ素50オングストローム厚ゲート誘電体層の上に第一金属領域と第二金属領域を形成するためにクラスタ堆積を用いる第一グループと、第一金属領域の堆積後とゲートスタックの第二金属領域の堆積前の4時間基板が空気に曝された第二グループを処理した。いずれのグループも、第一金属領域は、20、40、60、80オングストロームの厚さでTaNのALDによって形成し、第二金属領域は、Taの900オングストローム層のPVDによって形成した。第二金属領域の厚さが200オングストロームより大きい場合、第二金属領域の厚さを変化させても組み合わせた第一領域と第二領域の仕事関数にほとんど影響しなかった。続いての処理には基板のリソグラフィとエッチングが必要であり、その後、約450における後アニールを続けた。

20

## 【0032】

30

図3は、両グループのデバイスの容量と電圧を示すグラフである。図3に示されるように、実線のグループによって示されるクラスタ堆積グループは、TaN層の厚さを約20~80オングストロームに変化させた場合、200mVの仕事関数調整を示した。TaNを少なくとも4時間の空気に曝すことを試みる処理した第二グループ(図3では“空気遮断”を意味する破線のグループによって示される)は、TaN層の厚さを20~80オングストロームに変化させた場合、100mVの仕事関数調整しか示さなかった。上記のように、両グループのデバイスにおいて、Taから作られる第二金属領域は厚さが約900オングストロームに一定に保持した。

## 【0033】

40

従って、クラスタ装置又はシステムを用いるゲートスタックの調製物は、仕事関数の調整が劇的に改善し、ゲートレベルに適当な仕事関数とCMOSデバイス製造により広い範囲の仕事関数調整が確実になる。この例は、約0~80オングストロームの第一量だけ第一金属領域の厚さを変化させることによって第一領域の厚さを同じ第一量だけ変化させるが第二領域の形成前に空気に曝される場合の組み合わせた第一領域と第二領域の有効仕事関数の変化より少なくとも20%だけ組み合わせた第一領域と第二領域の有効仕事関数を大きくすることが可能であることを証明している。また図3を参照すると、クラスタシステム内に第一金属領域と第二金属領域を形成する他の利点はより低い範囲の印加電圧で厚さによるC<sub>x</sub>の変化が小さいことである。

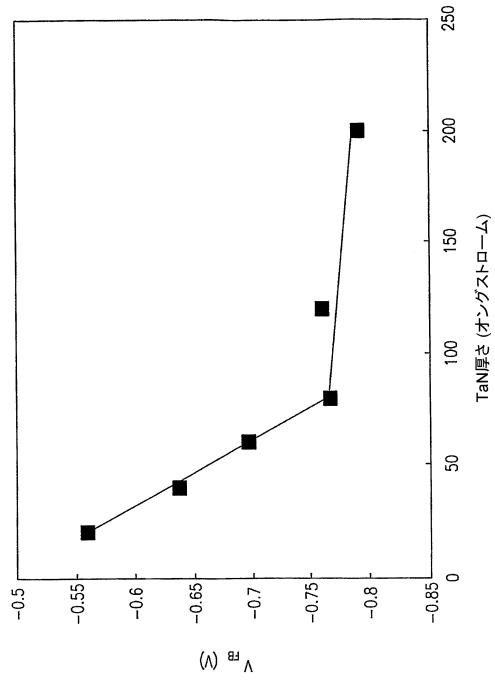

## 【0034】

ここで図4を参照すると、クラスタシステム内に形成された、Ta最上領域を有するA

50

L D によって堆積された T a N 層の閾値電圧と T a N 厚さが示される。閾値電圧の値の調整は、約 -0.55 V ~ -0.75 V に変化させることができ。上記のように、閾値電圧がゲートスタックの仕事関数に影響されるので、第一金属領域と第二金属領域のクラスタ堆積によって示されるより広い範囲の仕事関数調整がデバイスのより大きい範囲の閾値電圧調整を可能にする。この一連の実験で見出される他の効果は、クラスタシステムにおける第一金属領域と第二金属領域の形成によって金属接合部での酸化が減少し、ゲートスタックの E O T 値が保持されることである。

#### 【 0 0 3 5 】

従って、C M O S ゲートスタックの仕事関数調整の改善は、A L D を用いる第一金属領域の形成によって実現することができる。A L D を用いることにより、第一金属領域は、他の形成プロセスを用いて達成され得るよりかなり薄い寸法に縮小し得る。第一金属領域の A L D 形成によって第一金属領域と第二金属領域間の結合が改善される。A L D の使用によって接合部をより良く制御する能力は、N M O S デバイスとP M O S デバイスが有益である。クラスタシステムで A L D を用いて第一金属領域を形成することによりゲートスタックの仕事関数調整の制御が更に大きくなる。本発明のある種の実施形態は、トランジスタが同一のドーパントプロファイルを有する場合でさえ、閾値電圧が異なる種々のトランジスタを有する集積回路の生成を可能にする。従って、本発明の実施形態によれば、一つ以上の導電型（例えばP M O S、N M O S、又はそれらの双方）を有する複数のF E T を有する集積回路を構成することができ、ここで、一導電型のトランジスタは、20%、40%、60%又は80%も変化させることができる異なる閾値電圧以外は実質的に同じチャネルドーピングプロファイルと第二金属ゲート層厚さを有することができる。

10

20

#### 【 0 0 3 6 】

種々の修正や変更が本発明の精神又は範囲から逸脱することなく本発明になされ得ることが当業者に明らかである。従って、本発明は、添付の特許請求の範囲とそれらの等価物の範囲内であれば本発明の修正や変更を包含するものである。

#### 【 図面の簡単な説明 】

#### 【 0 0 3 7 】

【図1】図1は、電界効果トランジスタ対の断面図である。

【図2】図2は、基板処理システムの一実施形態を示す概略図である。

【図3】図3は、本発明の実施形態に従って作られたゲートスタックの電気容量と電圧とを示すグラフである。

30

【図4】図4は、本発明の実施形態に従って作られたゲートスタックの閾値電圧と第一金属領域の厚さとを示すグラフである。

#### 【 符号の説明 】

#### 【 0 0 3 8 】

100...デバイス、110...n型トランジスタ、112...誘電体層、114...ソース領域、116...ドレイン領域、118...チャネル領域、119...ゲート領域、120...p型ウェル領域、121...第一金属領域、122...第二金属領域、140...p型トランジスタ、142...ゲート誘電体層、148...p型チャネル、149...ゲート領域、150...n型ウェル領域、151...第一金属領域、152...第二金属領域、155...シリコンウエハ、180...領域、300...クラスタシステム、302...中央トランスファチャンバ、304...ロードロックチャンバ、306、308、310、312...プロセスチャンバ、314...クールダウンチャンバ、325...システムコントローラ、350...電源、375...ポンプ。

40

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

【図4】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 27/092 (2006.01)

H 01 L 29/423 (2006.01)

H 01 L 29/49 (2006.01)

(72)発明者 ハング, スティーヴン

アメリカ合衆国, カリフォルニア州, サニーヴェール, マンゴー アヴェニュー 915

(72)発明者マイナー, ゲリー

アメリカ合衆国, カリフォルニア州, フレモント, クラウン リッジ コモン 48865

合議体

審判長 小野田 誠

審判官 恩田 春香

審判官 飯田 清司

(56)参考文献 特開2004-186693 (JP, A)

国際公開第2004/019394 (WO, A1)

特開2001-93986 (JP, A)

特開2003-23152 (JP, A)

特開2000-243853 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L29/78