(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4212067号

(P4212067)

(45) 発行日 平成21年1月21日(2009.1.21)

(24) 登録日 平成20年11月7日(2008.11.7)

(51) Int.Cl.

F 1

|             |              |                  |        |       |

|-------------|--------------|------------------|--------|-------|

| <b>HO4N</b> | <b>5/455</b> | <b>(2006.01)</b> | HO 4 N | 5/455 |

| <b>HO4N</b> | <b>5/00</b>  | <b>(2006.01)</b> | HO 4 N | 5/00  |

| <b>HO4N</b> | <b>5/12</b>  | <b>(2006.01)</b> | HO 4 N | 5/12  |

B

A

請求項の数 6 (全 17 頁)

|              |                       |

|--------------|-----------------------|

| (21) 出願番号    | 特願平9-57163            |

| (22) 出願日     | 平成9年2月26日(1997.2.26)  |

| (65) 公開番号    | 特開平9-247569           |

| (43) 公開日     | 平成9年9月19日(1997.9.19)  |

| 審査請求日        | 平成16年1月26日(2004.1.26) |

| (31) 優先権主張番号 | 012339                |

| (32) 優先日     | 平成8年2月27日(1996.2.27)  |

| (33) 優先権主張国  | 米国(US)                |

| (31) 優先権主張番号 | 721780                |

| (32) 優先日     | 平成8年9月25日(1996.9.25)  |

| (33) 優先権主張国  | 米国(US)                |

|                                                             |                                            |

|-------------------------------------------------------------|--------------------------------------------|

| (73) 特許権者                                                   | 391000818                                  |

| トムソン コンシューマ エレクトロニクス インコーポレイテッド                             | THOMSON CONSUMER ELECTRONICS, INCORPORATED |

| アメリカ合衆国 インディアナ州 46290-1024 インディアナポリス ノース・メリディアン・ストリート 10330 | INDIANAPOLIS, INDIANA 46290-1024           |

| (74) 代理人                                                    | 100115864                                  |

| 弁理士                                                         | 木越 力                                       |

最終頁に続く

(54) 【発明の名称】デジタル信号処理装置におけるタイミング再生装置

## (57) 【特許請求の範囲】

## 【請求項 1】

受信信号を表わすサンプルのサンプル源と、

前記サンプル源に結合されており且つ制御信号に応答して送信機からの連続するシンボルに同期した時点で取り出されたサンプルを生成する補間装置と、

前記制御信号を供給する制御回路網であって、(a)前記補間装置からの出力信号と(b)前記連続するシンボルの所望のシンボル・レートに基づく公称遅延信号とに応じた前記制御信号を供給する被制御遅延回路網を含む前記制御回路網と、

から成る連続するシンボルを表わす信号を受信するデジタル信号処理装置用のタイミング再生装置であって、

前記制御回路網が、

前記補間装置に結合されており、該補間装置によって生成された送信機同期化サンプルのサンプリング時点と前記連続するシンボルの時点との間の位相誤差を検出する位相誤差検出器と、

前記公称遅延信号の信号源と、

前記位相誤差検出器と前記公称遅延信号の信号源とに結合された合計器と、

前記合計器に結合されていて、前記補間装置用の前記制御信号を生成する数値制御遅延装置と、

から成る、前記タイミング再生装置。

## 【請求項 2】

10

20

前記数値制御遅延装置が、

次の送信機同期化サンプルが前記補間装置によって取り出される前に残っている時間を

表わす信号を保持するアキュムレータと、

前記アキュムレータに結合されていて、送信機同期化サンプルが取り出されるときに送

信機同期化サンプル・クロック可能化信号を発生する回路と、

前記アキュムレータに結合されていて、前記制御信号を発生する回路と、から成る請求

項1記載のタイミング再生装置。

**【請求項3】**

さらに固定された周波数を有するクロック信号の信号源を有し、

前記アキュムレータは、整数部分と分数部分とを有する固定された点の数を保持する回

路からなり、前記数の値は前記固定された周波数のクロック信号の周期に基づいて表わさ

れ、

前記送信機同期化サンプル・クロック可能化信号を発生する回路は、前記固定された周

波数のクロック信号に応答して、前記アキュムレータ中の前記整数部分がゼロに達するま

で前記整数部分をカウントダウンし、

前記制御信号を発生する回路は前記アキュムレータ中の前記数の前記分数部分に応答す

る、

請求項2記載のタイミング再生装置。

**【請求項4】**

前記補間装置は4個のタップを有する区分的放物線フィルタから成る請求項1記載のタ

イミング再生装置。

**【請求項5】**

前記受信信号は複数のシンボル・レートの1つで生成された連続するシンボルを表わし

、

前記公称遅延信号の信号源は、前記受信信号中の連続するシンボル相互間の公称時間遅

延に相当する遅延値を有する前記公称遅延信号を発生する、

請求項1記載のタイミング再生装置。

**【請求項6】**

さらに、前記位相誤差検出器と前記合計器との間に結合されたループフィルタを有する

、請求項1記載のタイミング再生装置。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、デジタル信号処理システムに関するものであり、特に、テレビジョン信号受信機のようなデジタル信号受信機で使用するのに適したタイミング再生装置に関する。

**【0002】**

**【従来の技術】**

デジタル受信機において、デジタル・ビデオおよび関連する情報を含む送信された信号からデータを回復するには一般に3つの機能の実行（インプリメンテーション）、すなわちシンボル同期化(symbol synchronization)用のタイミング再生、搬送波再生(周波数変調)および等化を必要とする。タイミング再生は、受信機のクロック(タイムベース(時間基準))が送信機のクロックに同期化されるようにする処理である。これによって受信したシンボル値(symbol value)の判断命令処理(decision-directed processing)に伴うスライシング誤差(slicing error)の機会を低減し、受信信号を時間的に最適の点でサンプリングすることができるようになる。ある種の受信機では、受信信号は送信機のシンボル・レート(symbol rate)の倍数でサンプリングされる。例えば、ある受信機では受信信号は送信機のシンボル・レートの2倍の率でサンプリングされる。いずれの場合も、受信機のサンプル・クロックを送信機のシンボル・クロックに同期化させる必要がある。

**【0003】**

搬送波の再生(recovery)は、受信したRF信号がより低い中間周波数通過帯域に周波数

10

20

30

40

50

シフトされたのち、変調用ベースバンド情報の再生が可能になるようにベースバンドに周波数シフトされる処理である。等化は、送信チャンネルの擾乱が受信信号に及ぼす影響を補償する処理である。さらに詳しく云えば、送信チャンネルの擾乱によって引き起こされるシンボル間干渉 ( I S I : Intersymbol Interference ) を等化によって取り除くことができる。

#### 【 0 0 0 4 】

I S I は所定のシンボルの値を先行するシンボルおよび後続するシンボルの値によって歪ませる。これらの機能およびこれに関連する機能については、アメリカ合衆国 マサチューセッツ州 ボストンにあるクラウ・アカデミック・プレス(Kluwer Academic Press) 発行の文献リー・アンド・メッサーシュミット・イン・ディジタル・コミュニケーション(Leee and Messerschmitt in Digital Communication)において詳細に説明されている。10

#### 【 0 0 0 5 】

##### 【発明が解決しようとする課題】

従来の受信機は、サンプリング・クロック信号を送信機のシンボル・クロックにロックできるように比較的安定しており、しかも制御可能なサンプリング・クロック信号源を必要とした。この機能を持たせるために電圧制御水晶発振器 ( V C X O ) が使用されていた。電圧制御水晶発振器によって発生されるクロック信号は、制御可能な範囲が比較的狭いが安定しており、そのためこれを送信機のシンボル・クロックにロックすることができる。しかしながら、V C X O のような電圧制御発振器はアナログ構成であるため比較的高価であり、またその寿命期間中にドリフトし易い。さらに、異なるシンボル周波数を有する異なる送信機 ( 例えば、欧州の衛星システム ) からの信号を受信する必要があれば、このような各送信機に対して別々のV C X O を設ける必要があり、受信機のコストがさらに高くなる。20

#### 【 0 0 0 6 】

1 シンボル・レート以上を実現することができるシンボル・タイミング再生システムを提供することが望ましい。さらに、例えば各受信シンボル・レート毎に設けられた多数の電圧制御水晶発振器を有する周知の形式のタイミング再生システムに比べて、例えばハードウェアに要求される条件に関するような性能上の利点、コスト上の利点を得ることができるタイミング再生システムを提供することが望ましいことが認められた。

#### 【 0 0 0 7 】

##### 【課題を解決するための手段】

本発明の原理によれば、ディジタル信号受信機用のタイミング再生システムは、送信機からの連続するシンボル ( symbol : 記号 , 符号 ) を表わす信号を受信する。シンボル源に結合された補間装置は制御信号に応答して、送信機からの連続するシンボルに同期したタイミングで取り出されたサンプルを生成する。制御信号を供給する制御回路網は、上記補間装置からの出力信号と公称遅延オフセット信号とに応答する制御遅延回路網を含んでいる。30

#### 【 0 0 0 8 】

とりわけ、このシステムは受信信号を表わすサンプル源を有し、このサンプルは固定された周波数で取り出される。補間装置は上記サンプル源に結合されており且つ制御信号に応答する。補間装置は、送信機からの連続するシンボルに同期したタイミングで取り出されたサンプルを生成する。位相誤差検出器が補間装置に結合されていて、該補間装置によって生成される送信機同期化サンプルのサンプリング時点と連続する送信機のシンボルの時点との間の誤差を検出して位相誤差信号を発生する。位相誤差信号は合計器 (summer) の一方の入力端子に結合されており、公称遅延信号源が上記合計器の他方の入力端子に結合されている。数値制御遅延装置は上記合計器からの信号に応答して補間装置用の制御信号を生成する。40

#### 【 0 0 0 9 】

本発明によるタイミング再生システムは、先ず初めに所望の最高送信機シンボル・レートの 2 倍よりも僅かに高い固定された周波数で受信信号をサンプリングすることによって動50

作する。この最初にサンプリングされた信号は次いで補間装置によって処理されて、送信機シンボル・レートに同期した一連のサンプルを生成する。これらの同期したサンプルはディジタル位相誤差検出器に供給される。ディジタル位相誤差検出器の出力は二次ループフィルタに供給される。所望の公称サンプリング時間遅延を表わす予め設定された値は上記ループフィルタの出力信号に加算される。

#### 【0010】

予め設定された公称遅延とループフィルタからの出力信号との組合せによって数値制御遅延装置を制御し、該数値制御遅延装置は整数クロック遅延成分信号および分数クロック遅延成分信号を供給する。クロック遅延成分信号の整数部分は、送信機シンボル・レートに同期した受信機サンプリング・クロック信号の生成を制御する。このサンプリング・クロック信号はさらに周波数分割されて受信機のシンボル・クロック信号を生成する。遅延成分信号の分数部分は、補間フィルタによって生成されたサンプリングされた信号が所望のサンプリング時点で受信された信号の値を表わすように上記補間フィルタの制御入力に供給される。

10

#### 【0011】

本発明によるタイミング再生システムは、シンボルのタイミング基準に対して多数のアナログ電圧制御水晶発振器を使用することを必要とすることなく可変シンボル・レートタイミング再生を実現することができるという効果がある。これは予め設定された公称遅延をタイミング制御ループに導入することにより達成される。受信機中のプロセッサによって制御されることがある公称遅延レジスタは、最初のサンプリング率の2分の1よりも低い任意所望の受信機サンプリング率を選択できるようにする。

20

#### 【0012】

特定のシンボル・レート毎に多数の特定の水晶発振器を使用することに伴う問題、例えばハードウェアが複雑になり、コストが高くなるという問題、さらに捕捉時間が水晶発振器の周波数をどの程度速く同調させることができるかという点に左右されるという問題を解消することができる。ここに開示されたディジタル・システムは、電圧制御水晶発振器の機能をもたせることができ、単一の固定周波数発振器を使用することができるという効果が得られる。

#### 【0013】

送信機のシンボル・レートの2倍で入力信号をサンプリングする受信機にとって、この発明による装置は最初の固定されたサンプリング率の2分の1以下の任意の送信機シンボル・レートを実現することができる。試験された引き込み範囲は+/-1000 ppm以上であるので、必要とする周波数精度は市販の水晶（クリスタル）を使用して容易に得ることができる。このシステムは試験され、1000 ppmのタイミング・オフセットがあつても、500サンプルの後そのコンステレーション(constellation：配列、配置、集合)を明らかにし、数千のサンプルの後そのコンステレーションをロックすることにより、比較的短時間でタイミング・ロックが得られることが判った。電圧制御水晶発振器を排除したことと相まってその優れた特性により、単一のシンボル・レートを含む場合も本発明のシステムを有効なものにしている。

30

#### 【0014】

さらに、ここに開示されたシステムは、欧州の衛星通信の応用分野で使用されるようなシンボル・レートのような多数のシンボル・レートにも対処することができるという利点がある。以下に述べる実施例で、受信機は送信機のシンボル・レートの2倍で入力信号をサンプリングする。例えば、ここに開示されたタイミング再生システムは、62MHzの初期サンプル・クロック周波数を使用して毎秒2000万個のシンボル（20Mシンボル/秒）乃至30Mシンボル/秒のシンボル・レートを実現し得ることが判った。

40

#### 【0015】

これは、62/30および62/20の初期サンプル・クロック周波数対シンボル・クロック率を与える。これらの分数表示で、分子は初期サンプリング率であり、分母はシンボル・レート（Mシンボル/秒）である。従って、この場合は、20Mシンボル/秒と3

50

0 M シンボル / 秒の両方のシンボル・レートの再生は、単一の固定された水晶制御発振器から供給される单一の固定された 62 MHz の初期サンプリング・クロック周波数を使用することにより実現することができる。

請求の範囲と実施例との対応関係を図面で使われている参考番号で示すと次の通りである。

(請求項 1) 受信信号を表わすサンプル源(10)と、

前記サンプル源に結合されており且つ制御信号に応答して送信機からの連続するシンボルに同期した時点で取り出されたサンプルを生成する補間装置(12)と、

前記制御信号を供給する制御回路網(16、20-30、34-36)であって、(a)前記補間装置からの出力信号と(b)公称遅延(31)信号とに応答する被制御遅延回路網を含む前記制御回路網と、

10

から成る連続するシンボルを表わす信号を受信するデジタル信号処理装置におけるタイミング再生装置。

(請求項 2) 前記制御回路網が、

前記補間装置に結合されており、該補間装置によって生成された送信機同期化サンプルのサンプリング時点と前記連続する送信機のシンボルの時点との間の位相誤差を検出する位相誤差検出器と、

公称遅延信号の信号源と、

前記位相誤差検出器と前記公称遅延信号の信号源とに結合された合計器と、

20

前記合計器に結合されていて、前記補間装置用の制御信号を生成する数値制御遅延装置と、

から成る請求項 1 記載のタイミング再生装置。

(請求項 3) 前記サンプルが固定された周波数で取り出される請求項 1 記載のタイミング再生装置。

(請求項 4) 前記数値制御遅延装置が、

次の送信機同期化サンプルが前記補間装置によって取り出される前に残っている時間を表わす信号を保持するアキュムレータと、

前記アキュムレータに結合されていて、送信機同期化サンプルが取り出されるときに送信機同期化サンプル・クロック可能化信号を発生する回路と、

30

前記アキュムレータに結合されていて、前記補間装置用の制御信号を発生する回路と、から成る請求項 2 記載のタイミング再生装置。

(請求項 5) さらに固定された周波数を有するクロック信号の信号源を有し、

前記アキュムレータは、整数部分と分数部分とを有する固定された点の数を保持する回路からなり、前記数の値は固定された周波数のクロック信号の周期に基づいて表わされ、

前記送信機同期化サンプル・クロック可能化信号を発生する回路は、固定された周波数クロック信号に応答して、前記アキュムレータ中の整数部分がゼロに達するまで前記整数部分をカウントダウンし、

前記補間装置用の制御信号を発生する回路は前記アキュムレータ中の数の分数部分に応答する、

40

請求項 4 記載のタイミング再生装置。

(請求項 6) 前記補間装置は 4 個のタップを有する区分的放物線フィルタから成る請求項 2 記載のタイミング再生装置。

(請求項 7) 前記受信信号は複数のシンボル・レートの 1 つで生成された連続するシンボルを表わし、

前記公称遅延信号の信号源は、受信信号中の連続するシンボル相互間の公称時間遅延に相当する遅延値を有する公称遅延信号を発生する、

請求項 2 記載のタイミング再生装置。

(請求項 8) 前記固定された周波数は予想される最高送信機同期化サンプル率の 2 倍よりも高い、請求項 3 記載のタイミング再生装置。

(請求項 9) 前記固定された周波数は送信機同期化サンプル率の 2 倍よりも高い、

50

請求項 3 記載のタイミング再生装置。

(請求項 10) 前記固定された周波数は 62 MHz であり、送信機同期化シンボル・レートは 30 Mシンボル／秒である請求項 9 記載のタイミング再生装置。

(請求項 11) 前記固定された周波数は 62 MHz であり、送信機同期化シンボル・レートは 20 Mシンボル／秒である請求項 9 記載のタイミング再生装置。

(請求項 12) さらに、前記位相誤差検出器と前記合計器との間に結合されたループフィルタを有する、請求項 2 記載のタイミング再生装置。

#### 【0016】

##### 【発明の実施の形態】

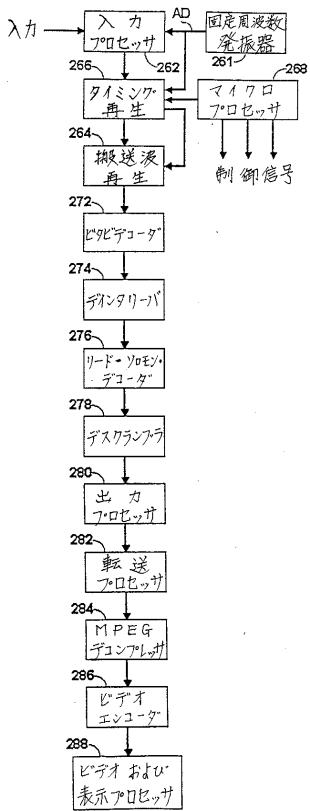

図 1 は、本発明の原理によるタイミング再生回路網を含む QPSK 变調入力信号の受信機、例えば直接放送用衛星受信機のブロック図である。図 1 に示すブロックは、本発明によるシンボル・タイミング再生回路網であるユニット 266 を除いて、その機能および構成において通常のものである。10

#### 【0017】

入力端子 (INPUT) は、アンテナあるいはケーブル接続のような変調された QPSK の源 (図示せず) に結合されている。入力端子 (INPUT) は入力プロセッサ 262 に結合されており、該入力プロセッサには入力チャンネル・チューナ、RF (無線周波数) 増幅器、IF (中間周波数) 増幅器および入力信号をさらに処理するのに適したより低い周波数バンドに通降変換するためのミキサ段、自動利得制御回路網、および出力アナログ - ディジタル変換器 (ADC) が含まれている。これらはいずれも図示されていないが、周知の形態で構成されている。例えば水晶発振器からなる固定周波数発振器 261 は、固定されたサンプリング周波数のクロック信号 AD をアナログ - ディジタル変換器および他の回路素子 (例えば、タイミング再生回路網 266) に以下に詳細に説明する様で供給する。20

#### 【0018】

入力プロセッサ 262 からのベースバンドに近い出力信号は本発明によるタイミング再生回路網 266 に供給される。タイミング再生回路網 266 は、以下に詳細に説明する様で、送信機のシンボル・クロックに同期した送信信号を表わすサンプルおよび他のタイミング信号を生成する。図示の実施例では、送信されたシンボル当たり 2 個のサンプルが生成される。送信機同期化サンプルおよび他のタイミング信号は搬送波再生回路網 264 に供給され、該搬送波再生回路網 264 はその信号を復調してベースバンドに変換する。周知のように、再生回路網 264 はイコライザ、ローテータ、スライサおよび位相誤差検出回路網、さらにイコライザおよびローテータの動作を制御する位相制御装置を含んでいる。30

#### 【0019】

搬送波再生回路網 264 からのベースバンド復調信号はビタビ(Viterbi) ・デコーダ 272 によって解読 (デコーディング) され、デインタリーバ(deinterleaver) 274 によってデインタリーブされ、次いでリード - ソロモン (Reed-Solomon) 誤差検出および訂正器 (図ではリード - ソロモン・デコーダと記載されている) 276 によって誤差が検出され且つ訂正される。これらの各回路網あるいは装置の機能については、例えば、前述のリー・アンド・メッサー・シュミット (Lee and Messerschmitt) のテキスト中に特に詳細に説明されている。40

#### 【0020】

リード - ソロモン誤差検出および訂正器 276 からの誤差訂正された信号はデスクランbler (descrambler) 278 において随時デスクランbler (暗号回復) される。デスクランbler 278 からの信号は出力プロセッサ 280 に供給され、該出力プロセッサ 280 はデスクランblerされたデータを他の信号処理回路網にインタフェースするのに必要な機能を与える。これらの機能にはデータを適當な論理レベルに一致させること、他の回路網とのインタフェースが容易にするためのクロック信号の供給が含まれている。

#### 【0021】

50

20

30

40

50

出力プロセッサ 280 からのデータは MPEG コンパチブル転送プロセッサ 282 によって処理される。本発明を実施したシステムでは、MPEG コンパチビリティは必須ではないが、該 MPEG コンパチブル転送プロセッサ 282 はビデオデータのデコンプレッションで使用される同期と誤差指示情報とを与える。転送プロセッサ 282 はヘッダ情報の解析に基づく形式に従ってデータを分ける。転送プロセッサ 282 からの出力データは MPEG デコンプレッサ 284 によってデコンプレス(decompress)されて、ビデオエンコーダ 286 により例えば NTSC や PAL のような予め設定されたフォーマットにエンコードするのに適したビデオデータを供給する。ビデオエンコーダ 286 からの出力信号は画像表示装置(図示せず)を含むビデオおよび表示プロセッサ 288 に供給される。

## 【0022】

10

システムのマイクロプロセッサ 268 は、タイミング再生回路網 266 を含む受信機中の各素子に周知の態様で初期化パラメータおよび他の制御信号を供給する。システムのマイクロプロセッサ 268 によってタイミング再生回路網 266 に与えられる特定のパラメータおよび制御信号については、以下に詳細に説明する。

## 【0023】

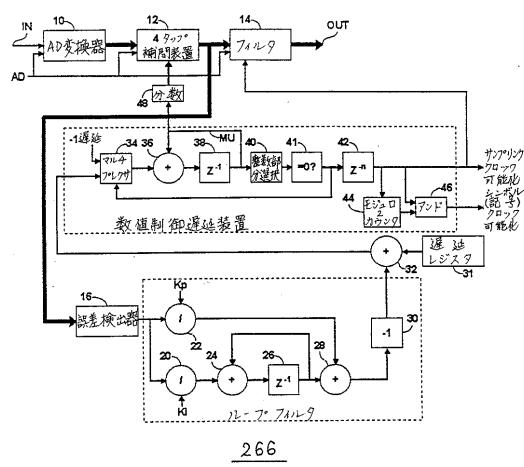

図 2 は本発明の原理によるシンボル・タイミング再生システムをより詳細に示したプロック図である。図 2 で、アナログ信号あるいは単一のディジタル信号は細線で示され、周知の形態の実数(同相)成分信号および虚数(直角位相)成分信号からなる複素ディジタル信号は太線で示されている。図 2 に示すシンボル・タイミング再生システムでは、設計者が入力サンプル率の 2 分の 1 以下の任意所望のシンボル・レートを選択することができるよう公称遅延レジスタを含むという有利な特徴が得られ、またより高次のコンステレーション(constellation: 配列; 配置, 集合)のためにより正確な補間装置を使用することができるという有利な特徴が得られる。数値制御遅延演算手段の出力にシンボル・クロック可能化信号およびサンプル・クロック可能化信号を誘導することにより、位相および周波数ロック用のアナログ素子を使用することなく完全な同期設計が可能になる。

20

## 【0024】

図 2 で、送信機からの受信信号を表わす入力アナログ信号 IN は、先ず図 1 における入力プロセッサ 262 の一部であるアナログ - ディジタル (A/D) 変換器 10 によってサンプリングされ且つ複素ディジタル形式に変換される。A/D 変換器 10 は図 1 の固定周波数水晶発振器 261 によって局部的に発生された初期固定周波数サンプル・クロック A/D によってクロック制御される。A/D 変換器 10 からの複素ディジタル・データストリームは、初期固定周波数サンプル・クロック信号 A/D によってクロック制御される複素 4 タップ補間装置 12 (これについては以下で詳細に説明する) に供給される。上述の補間機能は本質的にタイミング調整機能であり、ときにはディジタル位相シフトおよびサンプリング率変換と称されることがある。

30

## 【0025】

補間装置 12 の出力は固定周波数サンプル・クロック信号 A/D に同期して生成された複素サンプルのストリームで、これは上記固定周波数サンプル・クロック信号 A/D およびサンプル・クロック可能化信号(以下で説明するように発生される)に応答する固定(非適応形)複素パルス成形フィルタ 14 によってパルス成形濾波される。フィルタ 14 の出力は濾波された複素サンプルのストリームで、これは図 1 に示すシステムの他の装置、回路網に供給される。補間装置 12 の出力はまた位相誤差検出器(以下に詳細に説明する)にも供給される。

40

## 【0026】

位相誤差検出器 16 の出力は、図示の実施例ではバレル・シフタ(barrel shifter)として構成された割算器 20 および 22 にそれぞれ供給される。フィルタのループ積分定数 K\_i は割算器 20 に供給され、ループ比例定数 K\_p は割算器 22 に供給される。ループ積分定数 K\_i およびループ比例定数 K\_p の値は周知の態様で(図 1 の)システムのマイクロプロセッサ 268 によって計算され、割算器 20、22 にそれぞれ供給される。割算器 20 の出力は加算器(adder) 24 の第 1 の入力端子に結合されている。加算器 24 の出力は遅延

50

装置 2 6 に結合され、該遅延装置 2 6 の出力は加算器 2 4 の第 2 の入力および加算器 2 8 の第 1 の入力に結合されている。

【 0 0 2 7 】

割算器 2 0 からの信号は加算器 2 4 において遅延装置 2 6 から供給される上記加算器 2 4 の遅延信号と加算される。遅延装置 2 6 からの信号はまた加算器 2 8 において割算器 2 2 の出力と加算される。加算器 2 8 の出力はインバータ回路 3 0 によって利得 1 で反転される。第 1 の割算器 2 0 および第 2 の割算器 2 2 、加算器 2 4 および 2 8 、遅延装置 2 6 、およびインバータ回路 3 0 は組み合わされて 2 次ループフィルタを構成する。インバータ回路 3 0 の出力はループフィルタの出力を構成している。この出力は、補間装置 1 2 からサンプルが生成される補間時点と送信機のクロックに同期した理想的なサンプリング時点との間の差を表わす。

10

【 0 0 2 8 】

公称遅延レジスタ 3 1 は図 1 のシステムのマイクロプロセッサ 2 6 8 から送信機同期化サンプリング時点相互間の公称時間あるいは期待時間を表わす値を受信する。この公称遅延値は以下に詳細に説明するような態様でシステムのマイクロプロセッサによって計算される。図示の実施例では、受信信号はシンボル・レート(symbol rate) で 2 回サンプリングされ、それによってサンプリング信号相互間の公称遅延は送信されたシンボル相互間の期待時間隔(expected interval) の 2 分の 1 になる。

【 0 0 2 9 】

公称遅延レジスタ 3 1 の出力は合計器(summer) 3 2 の第 1 の入力端子に結合されている。

20 ループフィルタの出力は合計器 3 2 において予め設定された公称遅延値と加算される。合計器 3 2 からの出力信号は送信機のシンボル・クロックと同期したサンプル相互間の瞬時遅延値を表わすディジタル信号である。公称遅延レジスタ 3 1 は、捕捉を促進するために受信機のタイミング・ループが最初入力シンボル・レートに密に近似し得るようにするために設けられている。システムの引き込み範囲は位相誤差検出器 1 6 の特性のみによって制限される。

【 0 0 3 0 】

合計器 3 2 からの信号の値は、固定された周波数のクロック周期の数について表わされ、サンプリング時点相互間の全(full)固定周波数クロック・パルスの数を表わす整数部分と、2 個の隣接する固定周波数サンプル相互間のサンプリング時点を表わす分数部分とを含んでいる。図示の実施例では、合計器 3 2 からのディジタル信号は、整数部分を担持する 2 個の上位ビットと、分数部分を担持する残りのビットとを有する 2 2 ビット固定点デイジタル信号である。図 1 のシステムのマイクロプロセッサは次に示す態様で公称遅延レジスタ 3 1 にある値を挿入する。先ず初めに、公称遅延レジスタ 3 1 はこれに挿入された論理“ 1 ”の値の信号をもっている。次いでこの信号は 2 0 位置左ヘシフトされる。これによって論理“ 1 ”信号は整数部分の最下位ビットに配置される。これは次のデジタル論理式(1)によって表わされる。

30

【 0 0 3 1 】

$1 << R_S - I_S \quad (1)$

【 0 0 3 2 】

ここで、 $R_S$  は公称遅延レジスタのサイズ、例えば図示の実施例では 2 2 であり、 $I_S$  は整数部分のサイズ、例えばこの実施例では 2 である。従って、図示の実施例では(1)式は次の(2)式のようになる。

40

【 0 0 3 3 】

$1 << (22 - 2) \quad (2)$

【 0 0 3 4 】

次いで、固定周波数クロック周期の数として表わされる送信機同期化サンプル相互間の公称遅延を決定するためにシステムのマイクロプロセッサによって次の(3)式の計算を行なう。

【 0 0 3 5 】

50

$$D = F R / (2 \cdot S) \quad (3)$$

**【0036】**

ここで、Dは固定周波数クロック周期の数として表わされる送信機同期化サンプル相互間の公称遅延であり、FRは固定された周波数のクロック周波数であり、Sは送信機のシンボル周波数である。

**【0037】**

この計算の結果は公称遅延レジスタ31の先行する内容と組み合わされる。式(1)および/または(2)の結果によって公称遅延レジスタ31に既に挿入された値“1”を補償するために、式(3)で計算された公称遅延値Dから値“1”を減算する必要がある。従って、図1のシステムのマイクロプロセッサによって公称遅延レジスタ31に置かれる公称遅延値は次の(4)式によって表わされる。

10

**【0038】**

$$DR_{31} = \{1 << (22 - 2)\} \cdot \{FR / (2 \cdot S) - 1\} \quad (4)$$

**【0039】**

ここで、DR<sub>31</sub>はシステムのマイクロプロセッサによって公称遅延レジスタ31に蓄積される値である。

**【0040】**

合計器32からの出力信号はマルチプレクサ34の1つの入力に供給される。マルチプレクサ34の他の入力には-1の値を表わす値が入力される。加算器36はマルチプレクサ34の出力から第1の入力を受ける。加算器36の出力はアキュムレータとして作用する遅延装置38に結合されている。遅延装置38は、AD変換器10を駆動するためにも使用される固定周波数サンプル・クロック信号ADによってクロック制御される。

20

**【0041】**

遅延装置38の出力は、次の送信機同期化サンプルまでの時間遅延を表わすディジタル信号MUである。ディジタル信号MUは、次の送信機同期化サンプルまで固定周波数クロック信号ADの周期数を表わす整数部分と、最後のこの固定周波数クロック信号から送信機同期化サンプルの時間までの時間遅延を表わす分数部分とを含んでいる。

30

**【0042】**

図示の実施例では、ディジタル信号MUは、整数部分を担持する2個の上位ビットと分数部分を担持する残りのビットとを有する22ビットの固定点ディジタル信号である。これ以外の異なるサイズ、フォーマットも使用できることはディジタル演算回路の当業者にとっては明らかである。例えば、QAM受信機では時間遅延を表わすために26ビットディジタル信号が使用される。時間遅延信号MUは整数部分セレクタ(選択装置)40に供給され、該セレクタ40は信号MU(MU:0-1)から2個の最上位ビットを選択する。

**【0043】**

整数部分は比較回路41に供給され、該比較回路41は整数を0値信号と比較して整数部分が0に等しいときに信号を発生する。時間遅延信号MUはまた分数部分セレクタ48に供給され、該セレクタ48は信号MU(MU:2-9)の分数部分の8個の上位ビット、即ち時間遅延信号MUの分数部分の上位バイトを含む信号を発生する。分数部分のこの上位バイトは補間装置12の制御入力端子に結合されている。22ビットの全時間遅延信号MUは加算器36の第2の入力端子に供給される。

40

**【0044】**

比較器41の出力はマルチプレクサ34の制御入力および遅延装置42に供給される。遅延装置42は、(以下に詳細に説明するように)時間遅延信号MUとこの時間遅延信号MUに応答して発生される位相誤差検出器16の対応する出力との間の遅延を整合させるのに必要な遅延を与える。時間遅延装置42の出力はサンプル・クロック可能化信号で、これはモジュロ2カウンタ44の入力端子とアンドゲート46の第1の入力端子とに供給される。

**【0045】**

モジュロ2カウンタ44の出力端子はアンドゲート46の第2の入力端子に結合されてい

50

る。アンドゲート46の出力はシンボル・クロック可能化信号を生成する。モジュロ2カウンタ44は例えばD形フリップフロップを含み、この例では2で割る。この動作はシンボル当たり2個のサンプルが与えられるこのような応用例（アプリケーション）で使用される。例えば、シンボル当たり4個のサンプルが使用される他の応用例では、カウンタ44としてモジュロ4カウンタが使用され、4による割算が行われる。

[ 0 0 4 6 ]

動作について説明すると、固定周波数サンプル・クロック A/D の周波数は送信機の期待される(expected)最高シンボル周波数の 2 倍よりも僅かに高い。図 1 のシステムのマイクロプロセッサ 268 は現在受信されつつある信号のシンボル・レートに対する公称すなわち期待されるサンプリング時間周期を計算し、公称遅延レジスタ 31 をこの値でロード(load)する。これによってほど正確なサンプル周期で数値制御遅延(NCD)の動作を開始させる。

( 0 0 4 7 )

位相誤差検出器 16 および関連するループフィルタは数値制御遅延を送信された信号の実際のサンプル率に調整し且つロックするように動作する。遅延装置 42 からのサンプル・クロック可能化信号およびアンドゲート 46 からのシンボル・クロック可能化信号は、(図 1 に示されている) 受信機中の他の処理素子で使用される。例えば、(図 2 の) パルス成形フィルタ 14 は固定周波数サンプル・クロック A/D とサンプル可能化クロック信号の両方を受信する。

[ 0 0 4 8 ]

上述のように、合計器 32 は最後の送信機同期化サンプルから次の送信機同期化サンプルまでの瞬時時間遅延を表わすデジタル信号を生成し、数値制御遅延アキュムレータ 38 は次の送信機同期化サンプル時点までに残っている時間を表わすデジタル信号を生成する。図示の実施例では、これらの時間を表わす信号は整数部分を担持する 2 個の上位ビットと分数部分を担持する残りのビットとを有する固定点 22 ビット 2 進語によって表わされる。

[ 0 0 4 9 ]

[0.050]

アキュムレータ 38 に記憶されている時間遅延の整数部分が 0 より大であれば、比較器 41 の出力は論理 “0” の信号である。この状態では、次の送信機同期化サンプルが取り出される前に、固定周波数サンプル・クロック A/D の 1 以上の周期が経過しなければならない。アキュムレータ 38 の整数部分の値はカウントダウンされる。マルチプレクサ 34 は比較器 41 における論理 “1” の信号によって -1 の値の信号を加算器 36 に結合するように条件付けられる。

【0051】

次いで、加算器 36 は -1 の信号をアキュムレータ 38 の信号の値に加算し（即ち、アキュムレータ 38 の信号の値から 1 を減ずる）、アキュムレータ 38 に減少された値を新たに記憶させる。さらに、比較器 41 の出力は論理“0”信号であるから、サンプル・クロック可能化信号およびシンボル・クロック可能化信号（これらは共に遅延装置 42 によって適正に遅延されている）は共に無効である（有効でない）。

【0052】

アキュムレータ 38 の分数部分は、次の送信機同期化サンプルが取り出されるまでの固定周波数サンプル・クロック A/D の周期の分数を表わしている。分数部分の上位の 8 個のビットは補間装置 12 の遅延を制御するために使用される。これは本質的に固定周波数サン

プル・クロック A D のサイクル相互間の時間周期を 2 5 6 の部分に分割するものである。従って、補間装置は 2 5 6 の位相のポリフェーズ（多相）フィルタ・バンクでよい。次の送信機同期化サンプルが取り出されるまでに、さらに完全な固定周波数サンプル・クロック A D のサイクルが存在しなければ、アキュムレータ 3 8 中のその信号の整数部分は 0 である。この場合、比較器 4 1 からの出力信号は論理“ 1 ”の信号である。

#### 【 0 0 5 3 】

比較器 4 1 からの出力信号が論理“ 1 ”のときは、アキュムレータ 3 8 の値の分数部分の最上位バイトによって制御される時点でサンプルが補間装置 1 2 から取り出され、サンプル・クロック可能化信号が発生されて下流（ダウンストリーム）回路を付勢し、この新しく発生されたサンプルをクロック入力（クロックイン）し且つ処理する。さらに、モジュロ 2 カウンタ 4 4 がクロックされ、もし送信機のシンボル時点であれば、アンドゲート 4 6 はまたシンボル・クロック可能化信号を発生する。10

#### 【 0 0 5 4 】

同時に、マルチプレクサ 3 4 は合計器 3 2 からの信号を加算器 3 6 に通過させるように条件付けられている。加算器 3 6 は所望の送信機同期化サンプリング時点と数値制御遅延アキュムレータ 3 8 からの分数部分（上述のように、整数部分は 0 である）を結合し、それによって次の送信機同期化サンプルが取り出される時間がアキュムレータ 3 8 内に配置される。ループは、ループフィルタを経由する位相誤差検出器 1 6 の出力信号に応答して変化する数値制御遅延の値によって閉じられている。20

#### 【 0 0 5 5 】

サンプル・クロック可能化信号は、回路素子 1 4 、 1 6 、 2 6 、 4 4 、および 4 6 のようなシステムの各素子、各送信機同期化サンプルを処理する図 1 の下流の他の全ての処理回路素子に供給される。このような各回路素子は固定周波数サンプル・クロック信号 A D の他にサンプル可能化信号を必要とする。シンボル・クロック可能化信号は送信された各シンボルのタイミングで取り出された送信機同期化サンプルに対して有効になる。シンボル・クロック可能化信号は送信されたシンボルにより作用するこれらのシステムの素子、例えば図 1 の搬送波再生回路 2 6 4 のような搬送波再生回路網に関連する決定用素子に供給される。このような素子は固定周波数サンプル・クロック信号 A D とシンボル・クロック可能化信号の両方に応答して動作する。30

#### 【 0 0 5 6 】

例えば、図示の実施例が衛星放送システム（例えば、Satlink：サトリンク）で使用されるように構成されておれば、固定周波数サンプル・クロック信号 A D の周波数は 6 2 M H z に設定される。この例の放送信号のシンボル・レートは 3 0 M シンボル / 秒である。受信信号はシンボル・レートの 2 倍の率でサンプリングされるので、サンプル・クロック可能化信号は、平均サンプル率をシンボル当たり 2 個のサンプルの所望のサンプル率にするような態様で固定周波数クロック信号を不能化（ディスエーブル）する。40

#### 【 0 0 5 7 】

従って、3 0 M シンボル / 秒のシンボル・レートに対しては、6 0 M サンプル / 秒が存在することになり、毎秒 2 0 0 万個の不能化された固定周波数サンプル・クロック A D のサイクル数が存在することになる。補間装置 1 2 は、各可能化された固定周波数サンプル・クロック A D のサイクル毎にサンプルが所望の送信機同期化サンプリング時点で取り出されるように見える補間されたサンプルを生成する。すなわち、補間装置 1 2 からのサンプルは、この例では 6 0 M H z の適正なサンプリング周波数でクロックされた A D 変換器 1 0 からサンプルが取り出されたかのような値をもっている。サンプルは、時にはスキップされたクロック信号（毎秒 2 0 0 万個）をもつ 6 2 M H z の固定周波数のクロック信号 A D の変化時に現れる。40

#### 【 0 0 5 8 】

ここに開示されたシステムが Q P S K 入力信号を処理するために使用される場合は、ビット誤差率は誤差訂正コードがしばしば無効になる近くの 4 d B 信号 - ノイズ比（ S N R ）の閾値で僅か 0 . 1 d B だけ低下することが認められた。タイミング制御ループは 3 0 0 50

0 個のサンプル内で十分に収斂した。ループは約 0 . 5 dB の低下で 0 dB の S N R に収斂するようだった。

#### 【 0 0 5 9 】

これらの性能特性は、またここに開示されたタイミング再生システムを所謂グランド・アライアンス方式(Grand Alliance)の H D T V システムと共に使用するために提案された形式の残留側波帯 ( V S B ) 変調入力信号と共に使用するのにも適していることを示している。次の表はある S R 比に対するシステムの性能を要約して示したものである。ここで、 S R 比は、シンボル当たり 2 個のサンプルを使用した固定周波数サンプリング率 ( アナログ - ディジタル変換率 ) 対シンボル・レートの比である。

#### 【 0 0 6 0 】

【表 1】

10

| S R 比   | S / N 比 | 劣化      |

|---------|---------|---------|

| 62 / 30 | 9 dB    | 0.2 dB  |

| 62 / 30 | 6 dB    | 0.05 dB |

| 62 / 30 | 4 dB    | 0.1 dB  |

| 62 / 20 | 9 dB    | 0.1 dB  |

| 62 / 20 | 6 dB    | 0.00 dB |

| 62 / 20 | 4 dB    | 0.04 dB |

20

#### 【 0 0 6 1 】

同相 ( I ) 成分および直角 ( Q ) 成分の両方で入力信号をサンプリングする Q A M システムのようなシステムでは、固定周波数サンプル・クロック信号 A D の率が次の ( 5 ) 式によって特定される値よりも大であれば、このシステムを使用して、シンボル・レートの 2 倍以下で入力 I および Q の直角信号をサンプリングし、送信機同期化シンボル・レートの 2 倍で一連のディジタル送信機同期化サンプルを発生させることができる。

30

#### 【 0 0 6 2 】

$$F R = S \times B W_E + M \quad ( 5 )$$

#### 【 0 0 6 3 】

ここで、 F R は固定周波数クロック信号であり、 S はシンボル・レートであり、 B W\_E は超過帯域幅部分であり、 M は補間装置の平坦な振幅および群遅延帯域幅に対する限界である。

40

#### 【 0 0 6 4 】

小さな超過帯域幅を有するシステムでは、これは A D サンプル率を 10 % 乃至 30 % ( 理想的な条件の下では 49 . 9 % ) 減少させることができる。補間後ディジタル処理システムは単位クロック当たり多数のサンプルを処理する必要があり、より高いクロック率で動作するかあるいは並列法を使用してデータを処理する必要がある。

#### 【 0 0 6 5 】

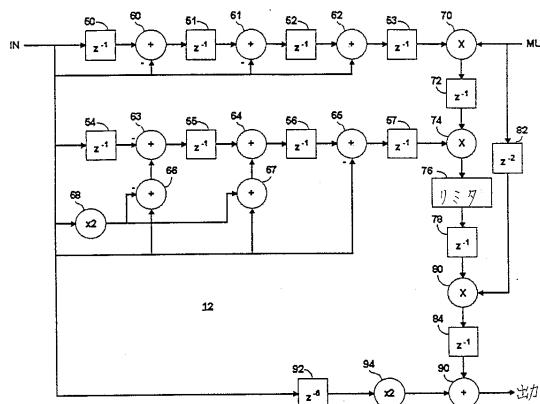

図 3 はハードウェア設計用の固定小数点演算で実行される ( 図 2 の ) ファロウ・アーキテクチャ区分的パラボラ補間装置 ( Farrow architecture piecewise parabolic interpolator ) 12 を示す。この例では、十分な性能をもった複雑でない補間装置を提供するものであるので、補間装置 12 は区分的 ( ピースワイズ ) パラボラ・フィルタを使用している。

50

64QAMあるいは256QAMのようなより高次のコンステレーション(constellation)用としてはより複雑な補間フィルタを必要とする場合がある。図2の合計器32に示すように正規の遅延信号をループフィルタからの出力信号に加えることにより、システムのマイクロプロセッサ(図示せず)が所望の送信機同期化サンプル相互間の公称遅延を制御し、そのループはその率を保持するだけでよいという利点が得られる。

#### 【0066】

特に図3の補間装置12は、「インプリメンテーション・アンド・パフォーマンス、IEEE Transactions on Communications」の第2編(Part II)におけるラーズ(Lars)氏他の論文「ディジタル・モデムにおける補間(Interpolation in Digital Modems)」に記載されている形式の4タップ区分的パラボラ・フィルタである。10

#### 【0067】

図3において、入力端子INは図2のAD変換器10の出力端子に結合されている。入力端子INは-32から+31までの範囲内の値を担持する6ビットのサンプルを受信し、該入力端子INは遅延素子50、合計器60、遅延素子51、合計器61、遅延素子52、合計器62および遅延素子53からなる直列接続回路、遅延素子54、合計器63の反転入力端子、遅延素子55、合計器64、遅延素子56、合計器65および遅延素子57からなる直列接続回路にそれぞれ結合されている。

#### 【0068】

入力端子INはまた合計器60、61、65の各反転入力端子、合計器62の非反転入力端子に結合されている。また、入力端子INは×2乗算器(マルチプライヤ)68の入力端子に結合されており、その出力端子は加算器67の入力端子および加算器66の反転入力端子に結合されている。加算器66は合計器63の入力端子に結合されており、加算器67は合計器64の入力端子に結合されている。入力端子INはまた加算器66と67の各第2の入力端子に結合されている。入力端子INはさらに6個の時間周期の遅延素子92と×2乗算器94との直列接続回路にも結合されている。20

#### 【0069】

制御入力端子MUは図2の数値制御遅延回路のアキュムレータ38の分数部分の最上位バイトに結合されている。制御入力端子MUは乗算器70、遅延素子72、乗算器74、リミタ76、遅延素子78、乗算器80、遅延素子84および加算器90からなる直列接続回路に接続されている。遅延素子53の出力端子は乗算器70の第2の入力端子に結合されており、遅延素子57の出力端子は乗算器74の第2の入力端子に結合されており、×2乗算器94の出力端子は加算器90の第2の入力端子に結合されている。制御入力端子MUと乗算器80の第2の入力端子との間には2周期遅延素子82が結合されている。加算器90の出力端子からは送信機同期化サンプルが発生し、この送信機同期化サンプルは出力端子OUTPUTに供給される。出力端子OUTPUTは図2のパルス成形フィルタ14に結合されている。30

#### 【0070】

図3に示した補間装置12は前述のラーズ(Lars)氏他の論文で説明されているような態様で動作する。制御信号MUは、送信機同期化サンプルが取り出される固定周波数サンプル・クロックADの隣接するサイクル相互間の分数時間を表わす。図3に示す補間装置12は制御信号MUによって表わされる時点でAD変換器10の隣接するサンプル相互間を補間するように動作し、出力端子OUTPUTに補間されたサンプルが発生する。40

#### 【0071】

図示の実施例では、制御信号MUの入力から補間されたサンプルの出力までの間に固定周波数クロック信号ADの3個の周期の遅延が存在する。この遅延は図2の数値制御遅延回路によって生成されるサンプル・クロック可能化信号とシンボル・クロック可能化信号の発生時に補償されなければならない。図2の遅延素子42はこの補償を行うもので、実施例の構成では3個のクロック周期遅延素子である。

#### 【0072】

10

20

30

40

50

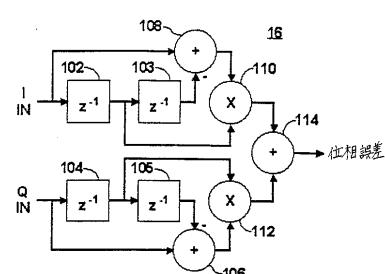

図4は図2の位相誤差検出器16のより詳細な構造を示すブロック図である。図4において、相互に直行する位相の同相(I)信号入力端子I INおよび直角位相(Q)信号入力端子Q INは図2の補間装置12の対応する各出力端子に結合されている。同相入力端子I INは遅延素子102、遅延素子103および合計器108の反転入力端子からなる直列接続回路に結合されている。同相入力端子I INはまた合計器108の第2の入力端子に結合されている。合計器108の出力端子は乗算器110の第1の入力端子に結合されており、遅延素子102の出力端子は上記乗算器110の第2の入力端子に結合されている。乗算器110の出力端子は合計器114の第1の入力端子に結合されている。

#### 【0073】

10

直角位相入力端子Q INは遅延素子104、遅延素子105および合計器106の反転入力端子からなる直列接続回路に結合されている。直角位相入力端子Q INはまた合計器106の第2の入力に結合されている。合計器106の出力端子は乗算器112の第1の入力端子に結合されており、遅延素子104の出力端子は上記乗算器112の第2の入力端子に結合されている。乗算器112の出力端子は合計器114の第2の入力端子に結合されている。合計器114の出力端子には、周知の態様で受信機中の数値制御遅延素子によって発生された送信機同期化サンプリング信号と送信された信号の実際のサンプリング時点との間の位相誤差を表わす信号が発生する。

#### 【0074】

20

#### 【発明の効果】

ここで述べたタイミング再生システムは、固定された周波数の発振器によって生成された単一のクロックに関連して多数のシンボル・レート入力信号に対処することができるという効果がある。さらに、サンプル・クロック可能化信号、シンボル・クロック可能化信号の両方を入力信号そのものから引き出すことができるという効果がある。本明細書中で説明したように、サンプル・クロック可能化信号は多数のシンボル・レートである率で補間装置の出力サンプルを示す。

#### 【0075】

30

上述のシステムは1個の固定されたパルス成形フィルタ14と固定周波数クロック発振器261を用いて多数の入力サンプリング率に対処することができるという効果がある。フィルタ14の構成は多数の入力クロック率に適合するように適応させる必要はない。タイミング再生回路網の後に配置されたパルス成形フィルタ14は、同じパルス成形特性をもって信号を濾波し、それによってその信号対ノイズ比を向上させることができる。

#### 【0076】

本発明によるシンボル・タイミング再生システムは、例えばアメリカ合衆国で使用するよう提案されている所謂グランド・アライアンス方式(Grand Alliance)の高精細度テレビジョン(HDTV)システムで使用されるようなVSB変調システムと同様に、BPSK、QPSK、CAP、QAMにも適用することができる。当業者にとっては、ここに開示されたシンボル・タイミング再生システムを所望の変調方式に適応させるためにはどのような設計変更を必要とするのかという点については十分に認識し得ることであり、また所望の変調方式と共に動作するように図示の素子をどのように設計すべきかという点についても十分に理解し得ることである。

40

#### 【0077】

上述の装置は比較的短い周期でロック状態を確保するものと認められていた。QPSKシンボル・コンステレーション(Symbol constellation)は数千のサンプルの後にロックされると認められ、またこのコンステレーションは1000ppmのタイミングのずれ(オフセット)があっても500個のサンプル後に見ることができる状態になる。これらの性能上の特徴と、電圧制御発振器の機能をデジタル的に行わせるハードウェアに要求される条件が減少することと相まって、このシステムが单一シンボル・レートに関して動作することを意図した場合の使用にもこのシステムを効果的なものとしている。

#### 【0078】

50

上述の実施例では、サンプル・クロック可能化信号は、固定周波数発振器 261 自体を可能化、不能化するのではなく、各回路に関するクロック可能化 / 不能化端子を経てクロック信号 A/D を可能化および不能化している。クロックをゲート制御することもまた採用可能であり、特定のシステムの要求に従って考慮されることはいうまでもない。

【図面の簡単な説明】

【図 1】QPSK 变調入力信号を受信するための本発明の原理によるタイミング再生回路網を含む受信機を表わすブロック図である。

【図 2】本発明の原理によるシンボル・タイミング再生システムのブロック図である。

【図 3】図 2 のシステムで使用される補間装置のより詳細なブロック図である。

【図 4】図 2 のシステムで使用される位相誤差検出器のより詳細なブロック図である。

10

【符号の説明】

- 10 10 アナログ - ディジタル変換器

- 12 12 補間装置

- 14 14 フィルタ

- 16 16 位相誤差検出器

- 31 31 遅延レジスタ（公称遅延信号源）

- 32 32 合計器

- 34 34 マルチプレクサ

- 36 36 加算器

- 38 38 遅延装置（アキュムレータ）

- 40 40 整数部分選択装置

- 41 41 比較器

- 42 42 遅延装置

- 44 44 モジュロ 2 カウンタ

- 46 46 アンドゲート

- 48 48 分数部分選択装置

- 261 261 固定周波数発振器

20

【図1】

【図2】

266

【図3】

【図4】

---

フロントページの続き

(72)発明者 ポール ゴザード ナットソン

アメリカ合衆国 インディアナ州 インディアナポリスサウス・エマーソン・アベニュー 148

(72)発明者 クマー ラマズワミイ

アメリカ合衆国 インディアナ州 インディアナポリスカレッジ・ドライブ #ビー 9417

(72)発明者 ディビッド ローウエル マクニーリイ

アメリカ合衆国 インディアナ州 インディアナポリスワーブラー・コート 7832

審査官 脇岡 剛

(56)参考文献 特開平05-260107(JP,A)

特開平03-088537(JP,A)

特開平01-296745(JP,A)

国際公開第94/028657(WO,A1)

Floyd M. Gardner, Interpolation in Digital Modems - Part I: Fundamentals, IEEE TRANSACTIONS ON COMMUNICATIONS, IEEE, 1993年 3月, Vol.41, No.3, pp.501-507

Lars Erup et al., Interpolation in Digital Modems - Part II: Interpolation and Performance, IEEE TRANSACTIONS ON COMMUNICATIONS, IEEE, 1993年 6月, Vol.41, No.6, pp.99-1008

Kartin Bucket et al., The Effect of Interpolation on the BER Performance of Narrowband BPSK and (0)QPSK on Rician-Fading C, IEEE TRANSACTIONS ON COMMUNICATIONS, IEEE, 1994年11月, Vol.42, No.11, pp.2929-2933

Vojin Zivojinovic et al., Design of optimum interpolation filters for digital demodulators, ISCAS '93, IEEE, 1993年, Vol.1, pp.140-143

(58)調査した分野(Int.Cl., DB名)

H04N 5/455

H04N 5/00

H04N 5/12