(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6945544号

(P6945544)

(45) 発行日 令和3年10月6日(2021.10.6)

(24) 登録日 令和3年9月16日(2021.9.16)

(51) Int.Cl.

G06F 12/04 (2006.01)

F 1

G06F 12/04 530

請求項の数 15 (全 28 頁)

(21) 出願番号 特願2018-548194 (P2018-548194)

(86) (22) 出願日 平成29年2月22日 (2017.2.22)

(65) 公表番号 特表2019-512794 (P2019-512794A)

(43) 公表日 令和1年5月16日 (2019.5.16)

(86) 國際出願番号 PCT/US2017/018876

(87) 國際公開番号 WO2017/160480

(87) 國際公開日 平成29年9月21日 (2017.9.21)

審査請求日 令和2年2月7日 (2020.2.7)

(31) 優先権主張番号 15/074,444

(32) 優先日 平成28年3月18日 (2016.3.18)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 アンドレス・アレハンドロ・オポータス・

ヴァレンズエラ

アメリカ合衆国・カリフォルニア・950

32・ロス・ガトス・(番地なし)・ピー

・オー・ボックス・320958

最終頁に続く

(54) 【発明の名称】プロセッサベースシステムにおけるメモリ内の圧縮メモリラインの優先度ベースのアクセス

## (57) 【特許請求の範囲】

## 【請求項 1】

プロセッサベースシステムにおけるメモリに記憶されたメモリラインにアクセスするためのメモリアクセスデバイスであつて、

第1の論理メモリアドレスを備える読み取りアクセス要求を受け取るように構成された制御ポートと、

前記メモリにアクセスするように構成されたメモリアクセスポートとを備え、

高優先度読み取りアクセス要求および低優先度読み取りアクセス要求の間で前記読み取りアクセス要求の優先度を決定し、

前記読み取りアクセス要求が前記高優先度読み取りアクセス要求であるとの決定に応答して、前記メモリアクセスポートを介して、前記読み取りアクセス要求の前記第1の論理メモリアドレスにおいて前記メモリから第1の圧縮高優先度メモリラインを取り出し、

前記読み取りアクセス要求が前記低優先度読み取りアクセス要求であるとの決定に応答して、前記メモリアクセスポートを介して、前記読み取りアクセス要求の前記第1の論理メモリアドレスから導出された複数の連続する物理メモリロケーションに対応する物理メモリアドレスにおいて前記メモリから第1の圧縮低優先度メモリラインを取り出す

ように構成されるメモリアクセスデバイス。

## 【請求項 2】

前記読み取りアクセス要求が前記高優先度読み取りアクセス要求であるとの決定に基づいて、

10

20

前記第1の圧縮高優先度メモリラインの高優先度メタデータを取り出し、

前記高優先度メタデータに基づいて前記第1の圧縮高優先度メモリラインから高優先度

データを取り出す

ようにさらに構成される、請求項1に記載のメモリアクセスデバイス。

【請求項3】

前記読み取りアクセス要求が前記高優先度読み取りアクセス要求であるとの決定に基づいて、

前記第1の論理メモリアドレスのパリティおよび前記高優先度メタデータに基づいて、

対応するメモリロケーションの端から前記第1の圧縮高優先度メモリラインを取り出すよ

うにさらに構成される、請求項2に記載のメモリアクセスデバイス。

【請求項4】

前記高優先度メタデータに基づいて、前記第1の圧縮高優先度メモリラインが例外を備

えると決定し、

前記高優先度メタデータから例外インデックスを取り出し、

前記メモリアクセスポートを介して、前記メモリ内の例外メモリロケーションにおいて

記憶された高優先度例外データを、前記例外インデックスに対応する物理メモリアドレス

において取り出し、

前記第1の圧縮高優先度メモリラインおよび前記高優先度例外データから前記高優先度

データを取り出す

ように構成されることによって、前記第1の圧縮高優先度メモリラインから前記高優先度

データを取り出すようにさらに構成される、請求項2に記載のメモリアクセスデバイス。

【請求項5】

前記読み取りアクセス要求の前記第1の論理メモリアドレスが所定の高優先度アドレス範

囲内にあると決定するように構成されることによって、前記読み取りアクセス要求が前記高

優先度読み取りアクセス要求であると決定するようにさらに構成される、請求項1に記載の

メモリアクセスデバイス。

【請求項6】

前記読み取りアクセス要求が前記低優先度読み取りアクセス要求であるとの決定に基づいて

、

前記読み取りアクセス要求の前記第1の論理メモリアドレスと所定の低優先度アドレス

範囲の最下位アドレスとの間の差に2を掛けることによって、低優先度アドレスインデッ

クスを決定し、

前記低優先度アドレスインデックスを所定の高優先度アドレス範囲の前記最下位アド

レスに加えることによって、前記複数の連続する物理メモリアドレスのうちの第1の物理

メモリアドレスを決定し、

前記第1の物理メモリアドレスで始まる前記複数の連続する物理メモリアドレスにお

いて記憶された前記第1の圧縮低優先度メモリラインを取り出す

ように構成されることによって、前記メモリから前記第1の圧縮低優先度メモリライン

を取り出すようにさらに構成される、請求項1に記載のメモリアクセスデバイス。

【請求項7】

前記第1の圧縮低優先度メモリラインの長さを備える低優先度メタデータを取り出し、

前記第1の圧縮低優先度メモリラインの前記長さに基づいて、前記第1の圧縮低優先度メ

モリラインから低優先度データを取り出す

ようにさらに構成される、請求項6に記載のメモリアクセスデバイス。

【請求項8】

前記低優先度メタデータに基づいて、前記第1の圧縮低優先度メモリラインが例外を備

えると決定し、

前記低優先度メタデータから例外ポインタを取り出し、

前記メモリアクセスポートを介して、前記メモリ内の例外メモリロケーションにおいて

記憶された低優先度例外データを、前記例外ポインタに対応する物理メモリアドレスにお

いて取り出し、

10

20

30

40

50

前記第1の圧縮低優先度メモリラインおよび前記低優先度例外データから前記低優先度データを取り出す

ように構成されることによって、前記第1の圧縮低優先度メモリラインから前記低優先度データを取り出すようにさらに構成される、請求項7に記載のメモリアクセスデバイス。

【請求項 9】

前記読み取りアクセス要求の前記第1の論理メモリアドレスが所定の低優先度アドレス範囲内にあると決定するように構成されることによって、前記読み取りアクセス要求が前記低優先度読み取りアクセス要求であると決定するようにさらに構成される、請求項1に記載のメモリアクセスデバイス。

【請求項 10】

プロセッサベースシステムにおけるメモリに記憶されたメモリラインにアクセスするための方法であって、

メモリアクセスデバイスによって、第1の論理メモリアドレスを備える読み取りアクセス要求を受け取るステップと、

高優先度読み取りアクセス要求および低優先度読み取りアクセス要求の間で前記読み取りアクセス要求の優先度を決定するステップと、

前記読み取りアクセス要求が前記高優先度読み取りアクセス要求であるとの決定に応答して、メモリアクセスポートを介して、前記読み取りアクセス要求の前記第1の論理メモリアドレスにおいて前記メモリから第1の圧縮高優先度メモリラインを取り出すステップと、

前記読み取りアクセス要求が前記低優先度読み取りアクセス要求であるとの決定に応答して、前記メモリアクセスポートを介して、前記読み取りアクセス要求の前記第1の論理メモリアドレスから導出された、複数の連続する物理メモリロケーションに対応する物理メモリアドレスにおいて前記メモリから第1の圧縮低優先度メモリラインを取り出すステップとを備える方法。

【請求項 11】

第2の論理メモリアドレスおよびデータを備える書き込みアクセス要求を受け取るステップと、

高優先度書き込みアクセス要求および低優先度書き込みアクセス要求の間で前記書き込みアクセス要求の優先度を決定するステップと、

前記書き込みアクセス要求が前記高優先度書き込みアクセス要求であるとの決定に応答して、前記メモリアクセスポートを介して、前記メモリ内の前記書き込みアクセス要求の前記データを、前記書き込みアクセス要求の前記第2の論理メモリアドレスにおける第2の圧縮高優先度メモリラインに記憶するステップと、

前記書き込みアクセス要求が前記低優先度書き込みアクセス要求であるとの決定に応答して、前記メモリアクセスポートを介して、前記メモリ内の前記書き込みアクセス要求の前記データを、前記書き込みアクセス要求の前記第2の論理メモリアドレスから導出された複数の連続する物理メモリアドレスにおける第2の圧縮低優先度メモリラインに記憶するステップと

をさらに備える、請求項10記載の方法。

【請求項 12】

前記書き込みアクセス要求が前記高優先度書き込みアクセス要求であるとの決定に基づいて、

前記書き込みアクセス要求の前記データを圧縮するステップと、

前記書き込みアクセス要求の前記圧縮されたデータを備える前記第2の圧縮高優先度メモリラインを、前記第2の論理メモリアドレスのパリティに基づいて、前記書き込みアクセス要求の前記第2の論理メモリアドレスに対応するメモリロケーションの端において記憶するステップと

をさらに備える、請求項11に記載の方法。

【請求項 13】

前記書き込みアクセス要求が前記高優先度書き込みアクセス要求であるとの決定に基づいて

10

20

30

40

50

、前記書込みアクセス要求の前記データを圧縮するステップと、

前記書込みアクセス要求の前記データの前記圧縮に基づいて、前記書込みアクセス要求の前記データが例外を引き起こすと決定するステップと、

前記書込みアクセス要求の前記データの第1の部分および例外インデックスを備える前記第2の圧縮低優先度メモリラインを、前記書込みアクセス要求の前記第2の論理メモリアドレスに対応する物理メモリアドレスにおいて記憶するステップと、

前記メモリ内の高優先度例外データを、例外メモリロケーションおよび前記例外インデックスに対応する物理メモリアドレスにおいて記憶するステップであって、前記高優先度例外データが、前記書込みアクセス要求の前記データの第2の部分を備える、ステップとをさらに備える、請求項11に記載の方法。 10

#### 【請求項14】

前記書込みアクセス要求の前記データを圧縮し、

前記書込みアクセス要求の前記第2の論理メモリアドレスと所定の低優先度アドレス範囲の最下位アドレスとの間の差に2を掛けることによって、低優先度アドレスインデックスを決定し、

前記低優先度アドレスインデックスを所定の高優先度アドレス範囲の前記最下位アドレスに加えることによって、前記複数の連続する物理メモリアドレスのうちの第1の物理メモリアドレスを決定し、

前記書込みアクセス要求の前記圧縮されたデータの第1の部分を備える前記第2の圧縮低優先度メモリラインの第1の部分を、前記第1の物理メモリアドレスの第1の端にある前記第1の物理メモリアドレスにおいて記憶し。 20

前記書込みアクセス要求の前記圧縮されたデータの第2の部分を備える前記第2の圧縮低優先度メモリラインの第2の部分を、第2の物理メモリアドレスの第2の端にある前記第1の物理メモリアドレスに連続する前記第2の物理メモリアドレスにおいて記憶することによって、前記第2の圧縮低優先度メモリライン内の前記書込みアクセス要求の前記データを前記複数の連続する物理メモリアドレスにおいて記憶するステップをさらに備える、請求項11に記載の方法。

#### 【請求項15】

前記書込みアクセス要求の前記データを圧縮し、

前記書込みアクセス要求の前記データの前記圧縮に基づいて、前記書込みアクセス要求の前記データが例外を引き起こすと決定し。 30

前記書込みアクセス要求の前記第2の論理メモリアドレスと所定の低優先度アドレス範囲の最下位アドレスとの間の差に2を掛けることによって、低優先度アドレスインデックスを決定し、

前記低優先度アドレスインデックスを所定の高優先度アドレス範囲の前記最下位アドレスに加えることによって、前記複数の連続する物理メモリアドレスのうちの第1の物理メモリアドレスを決定し、

前記書込みアクセス要求の前記データの第1の部分を備える前記第2の圧縮低優先度メモリラインの第1の部分を、前記第1の物理メモリアドレスの第1の端にある前記第1の物理メモリアドレスにおいて記憶し。 40

前記書込みアクセス要求の前記データの第2の部分を備える前記第2の圧縮低優先度メモリラインの第2の部分を、第2の物理メモリアドレスの第2の端にある前記第1の物理メモリアドレスに連続する前記第2の物理メモリアドレスにおいて記憶し、

例外ポインタを前記第2の圧縮低優先度メモリラインの前記第1の部分および前記第2の圧縮低優先度メモリラインの前記第2の部分のうちの少なくとも1つに記憶し、

前記書込みアクセス要求の前記データの第3の部分を前記例外ポインタに対応する第3の物理メモリアドレスにおいて記憶する

ことによって、前記第2の圧縮低優先度メモリライン内の前記書込みアクセス要求の前記データを前記複数の連続する物理メモリアドレスにおいて記憶するステップをさらに備え 50

る、請求項11に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

優先権出願

本出願は、その全体が参照により本明細書に組み込まれる、2016年3月18日に出願された「PRIORITY-BASED ACCESS OF COMPRESSED MEMORY LINES IN MEMORY IN A PROCESSOR-BASED SYSTEM」と題する米国特許出願第15/074,444号の優先権を主張する。

【0002】

本開示の技術は、一般に、データをコンピュータメモリに記憶することに関し、より詳細には、プロセッサベースシステムのメモリ内の圧縮メモリラインおよび非圧縮メモリラインにアクセスすることに関する。 10

【背景技術】

【0003】

コンピューティングデバイスは、社会に普及している。これらのデバイスは、サーバ、コンピュータ、セルラー電話、携帯情報端末(「PDA」)、ポータブルゲームコンソール、パームトップコンピュータ、および他の電子デバイスを含み得る。従来、コンピューティングデバイスは、多種多様なアプリケーションにおいて計算タスクを実行するプロセッサベースシステムを含む。プロセッサベースシステムは、機能をユーザに提供するためにシステムオンチップ(「SoC」)内で一緒に動作するように設計された他の集積回路に含まれ得る。典型的なプロセッサベースシステムは、ソフトウェア命令を実行する1つまたは複数のプロセッサを含む。ソフトウェア命令は、メモリ内のロケーションからデータをフェッチし、フェッチされたデータを使用して1つまたは複数のプロセッサ動作を実行し、記憶される結果を生成するようにプロセッサに命令する。例として、ソフトウェア命令は、システムまたはメインメモリに記憶され得る。ソフトウェア命令はまた、より速くフェッチするために、フェッチされ、キャッシュメモリに記憶され得る。たとえば、キャッシュメモリ(「キャッシュ」)は、プロセッサに局在するキャッシュメモリ、プロセッサブロック内のプロセッサ間で共有されるローカルキャッシュ、複数のプロセッサブロック間で共有されるキャッシュ、またはプロセッサベースシステムのメインメモリであり得る。この点について、システムまたはメインメモリからアクセスされるメモリラインのサイズは、効率性を目的として、メモリアクセスのためのシステムまたはメインメモリ内のアクセスされたメモリラインが、キャッシュメモリ内のキャッシュラインを一杯にすることを可能にするキャッシュラインのサイズであり得る。 20

【0004】

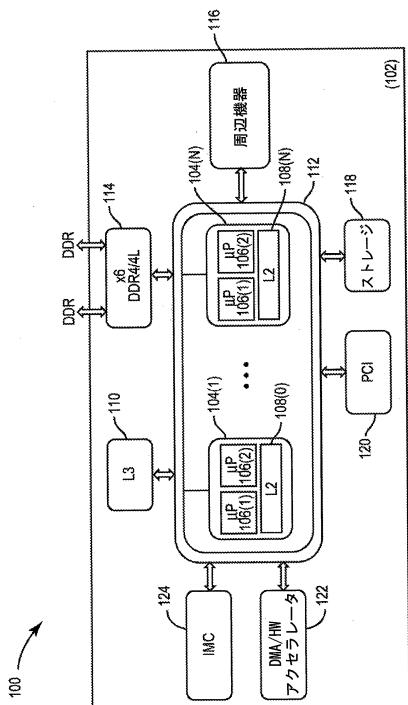

図1は、プロセッサベースシステム102を含む例示的なSoC100の概略図である。プロセッサベースシステム102は、複数のプロセッサブロック104(1)～104(N)を含み、ここにおいて、「N」は、所望の任意の数のプロセッサブロック104に等しい。各プロセッサブロック104(1)～104(N)は、それぞれ、2つのプロセッサ106(1)、106(2)と、共有レベル2(L2)キャッシュ108(1)～108(N)とを含む。共有レベル3(L3)キャッシュ110はまた、プロセッサブロック104(1)～104(N)の各々のいずれかによって使用されるか、またはプロセッサブロック104(1)～104(N)の各々の間で共有される、キャッシュされたデータを記憶するために設けられる。プロセッサブロック104(1)～104(N)の各々が、共有L3キャッシュ110、ならびに、メイン外部メモリ(たとえば、ダブルレートダイナミックランダムアクセスメモリ(DRAM)(DDR))にアクセスするためのメモリコントローラ114、周辺機器116、他のストレージ118、エクスプレス周辺構成要素相互接続(PCI)インターフェース120、ダイレクトメモリアクセス(DMA)コントローラ122、および統合メモリコントローラ(IMC)124を含む他の共有リソースにアクセスすることを可能にする、内部システムバス112が設けられる。 40

【0005】

プロセッサベースシステムの複雑性および性能が増大するにつれて、メモリのメモリ容量要件も増大し得る。しかしながら、プロセッサベースシステム内に追加のメモリ容量を 50

設けることで、集積回路上のメモリに必要なコストおよび面積が増大する。メモリラインごとにキャッシュラインのサイズが別々に圧縮されるキャッシュラインレベル圧縮などのメモリ容量圧縮は、物理的なメモリ容量を増加させることなしにプロセッサベースシステムの実効メモリ容量を増加させるために、オペレーティングシステムに対してトランスペアレントに用いられ得る。しかしながら、メモリ内の圧縮ラインをアドレス指定することは、メモリ読取りアクセスに応答して圧縮データを展開する際に処理時間が発生するので、メモリ読取りアクセスレイテンシを増加させる可能性がある。さらに、圧縮データをメモリに書き込むことは、メモリに書き込まれるべきデータを圧縮する際に処理時間が発生するので、メモリ書き込みレイテンシを増加させる可能性がある。またさらに、プロセッサは、固定サイズのキャッシュラインの論理メモリアドレスを、可変サイズの圧縮キャッシュラインを固定サイズのキャッシュラインに対応するメモリに記憶する対応する物理メモリアドレスにマッピングするので、データ圧縮は、メモリ管理の複雑性を増加させる可能性がある。その結果、たとえば、メモリ内の特定のキャッシュラインにアクセスすることは、その特定のキャッシュラインに対応するメモリ内の圧縮キャッシュラインのロケーションを決定するために、メモリ内のメタデータへのアクセスおよび追加のアドレス計算の層を必要とし得る。このことは、メモリ容量圧縮を用いるプロセッサベースシステムに対する複雑性、コスト、およびレイテンシを増大させる可能性がある。10

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0006】

20

本明細書で開示する態様は、プロセッサベースシステムにおけるメモリ内の圧縮メモリラインの優先度ベースのアクセスを含む。この点について、例示的な一態様では、プロセッサベースシステムにおけるメモリアクセスデバイス(たとえば、メモリコントローラまたは圧縮/圧縮解除エンジン)は、論理メモリアドレスを含む読取りアクセス要求を受け取って、メモリからメモリラインにアクセスする。メモリ内のアドレス指定可能な各メモリロケーションは、キャッシュラインサイズであり得るバーストデータ長のサイズまで、メモリラインのデータを記憶するように構成される。メモリアクセスデバイスは、読取りアクセス要求の優先度を決定する。読取りアクセス要求が高優先度読取りアクセス要求である場合、メモリアクセスデバイスは、メモリ内の圧縮メモリラインを記憶するメモリロケーションにアクセスするための物理メモリアドレスとして、読取りアクセス要求の論理メモリアドレスを使用する。メモリ内の圧縮メモリラインは、要求された高優先度データを圧縮形態で含む(すなわち、圧縮高優先度メモリライン)。このようにすると、高優先度読取りアクセス要求の論理メモリアドレスを対応する物理メモリアドレスに変換することに関連付けられたレイテンシは、メモリ内の対応する圧縮メモリラインのメモリロケーションを決定し、そのメモリロケーションにアクセスするために必要とされない。その結果、高優先度データに対するメモリ読取りアクセスレイテンシが低減され得る。30

#### 【0007】

メモリ内の圧縮高優先度メモリラインを、対応する高優先度データにアクセスするために使用される論理メモリアドレスにおいて記憶することは、高優先度データへのより速いアクセスを可能にする。そのことはまた、圧縮低優先度メモリラインを記憶するためのメモリ内の追加の空間を生み出す。たとえば、圧縮低優先度メモリラインは、メモリ内の記憶された圧縮高優先度メモリライン間の残りの空間である「穴(hole)」に記憶され得る。この点について、読取りアクセス要求が低優先度読取りアクセス要求である場合、メモリアクセスデバイスは、読取りアクセス要求の論理メモリアドレスを、その論理メモリアドレスに基づく物理メモリアドレスに変換する。次いで、メモリアクセスデバイスは、要求された低優先度データを圧縮形態で含むメモリ内の圧縮メモリライン、すなわち、圧縮低優先度メモリラインを記憶するメモリロケーションにアクセスするために、物理メモリアドレスを使用する。このようにすると、メモリ読取りアクセスのための論理メモリアドレスの変換が低優先度読取りアクセス要求に限定され、したがって、プロセッサベースシステムにおける圧縮メモリラインのより高い全体的なメモリアクセス効率を実現する。4050

**【0008】**

この点について、例示的な一態様では、プロセッサベースシステムにおけるメモリに記憶されたメモリラインにアクセスするためのメモリアクセスデバイスが提供される。メモリアクセスデバイスは、論理メモリアドレスを含む読み取りアクセス要求を受け取るように構成された制御ポートと、メモリにアクセスするように構成されたメモリアクセスポートとを備える。メモリアクセスデバイスは、高優先度読み取りアクセス要求および低優先度読み取りアクセス要求の間で読み取りアクセス要求の優先度を決定するように構成される。メモリアクセスデバイスは、読み取りアクセス要求が高優先度読み取りアクセス要求であるとの決定に応答して、メモリアクセスポートを介して、読み取りアクセス要求の論理メモリアドレスにおいてメモリから圧縮高優先度メモリラインを取り出すようにさらに構成される。メモリアクセスデバイスは、読み取りアクセス要求が低優先度読み取りアクセス要求であるとの決定に応答して、メモリアクセスポートを介して、読み取りアクセス要求の論理メモリアドレスに基づいて決定された物理メモリアドレスにおいてメモリから圧縮低優先度メモリラインを取り出すようにさらに構成される。10

**【0009】**

別の例示的な態様では、プロセッサベースシステムにおけるメモリに記憶されたメモリラインにアクセスするためのメモリアクセスデバイスが提供される。メモリラインにアクセスするためのメモリアクセスデバイスは、論理メモリアドレスを備える読み取りアクセス要求を受け取るための手段と、メモリにアクセスするための手段とを含む。メモリラインにアクセスするためのメモリアクセスデバイスは、高優先度読み取りアクセス要求および低優先度読み取りアクセス要求の間で読み取りアクセス要求の優先度を決定するための手段を備える。メモリラインにアクセスするためのメモリアクセスデバイスは、読み取りアクセス要求が高優先度読み取りアクセス要求であると決定するための手段に応答して、メモリにアクセスするための手段を介して、読み取りアクセス要求の論理メモリアドレスにおいてメモリから圧縮高優先度メモリラインを取り出すための手段をさらに備える。メモリラインにアクセスするためのメモリアクセスデバイスはまた、読み取りアクセス要求が低優先度読み取りアクセス要求であると決定するための手段に応答して、メモリにアクセスするための手段を介して、読み取りアクセス要求の論理メモリアドレスに基づいて決定された複数の物理メモリアドレスにおいてメモリから圧縮低優先度メモリラインを取り出すための手段を備える。20

**【0010】**

別の例示的な態様では、プロセッサベースシステムにおけるメモリに記憶されたメモリラインにアクセスするための方法が提供される。メモリラインにアクセスするための方法は、メモリアクセスデバイスによって読み取りアクセス要求を受け取るステップと、高優先度読み取りアクセス要求および低優先度読み取りアクセス要求の間で読み取りアクセス要求の優先度を決定するステップとを含む。メモリラインにアクセスするための方法は、読み取りアクセス要求が高優先度読み取りアクセス要求であるとの決定に応答して、メモリアクセスデバイスのメモリアクセスポートを介して、読み取りアクセス要求の論理メモリアドレスにおいて、メモリ内のメモリロケーションにおいて記憶された高優先度データを取り出すステップをさらに含む。メモリラインにアクセスするための方法は、読み取りアクセス要求が低優先度読み取りアクセス要求であるとの決定に応答して、メモリアクセスデバイスのメモリアクセスポートを介して、読み取りアクセス要求の論理メモリアドレスに基づいて決定された物理メモリアドレスにおいて、メモリ内の複数の連続するメモリロケーションにおいて記憶された低優先度データを取り出すステップをさらに含む。30

**【0011】**

別の態様では、メモリ内のメモリラインにアクセスするためのプロセッサベースシステムが提供される。プロセッサベースシステムは、メモリと、メモリに結合され、メモリにアクセスするように構成されたプロセッサと、メモリおよびプロセッサに結合されたメモリアクセスデバイスとを備える。メモリアクセスデバイスは、プロセッサから論理メモリアドレスを備える読み取りアクセス要求を受け取り、高優先度読み取りアクセス要求および低40

優先度読み取りアクセス要求の間で読み取りアクセス要求の優先度を決定するように構成される。メモリアクセスデバイスは、読み取りアクセス要求が高優先度読み取りアクセス要求であるとの決定に応答して、読み取りアクセス要求の論理メモリアドレスにおいてメモリから圧縮高優先度メモリラインを取り出すようにさらに構成される。メモリアクセスデバイスはまた、読み取りアクセス要求が低優先度読み取りアクセス要求であるとの決定に応答して、読み取りアクセス要求の論理メモリアドレスに基づいて決定された複数の物理メモリアドレスにおいてメモリから圧縮低優先度メモリラインを取り出すように構成される。

**【図面の簡単な説明】**

**【0012】**

【図1】プロセッサベースシステムを含む例示的なシステムオンチップ(「SoC」)の概略図である。

10

【図2】高優先度読み取りアクセス要求に対する読み取りアクセスレイテンシを低減するためにメモリ内の圧縮メモリラインの優先度ベースのアクセスを提供するように構成されたメモリアクセスデバイスを含む例示的なプロセッサベースシステムのブロック図である。

【図3】高優先度読み取りアクセス要求に対する読み取りアクセスレイテンシを低減するための図2のプロセッサベースシステムにおけるメモリ内の圧縮メモリラインの優先度ベースの読み取りアクセスのための例示的なプロセスを示すフローチャートである。

【図4】図2に示すプロセッサベースシステムにおけるメモリ内の高優先度データおよび低優先度データのための記憶された圧縮メモリラインの例示的なメモリ構成を示す図である。

20

【図5】図4に示す例示的なメモリ構成における記憶された圧縮メモリラインのメモリ構成のより例示的な詳細を示す図である。

【図6】図5のメモリ構成のために用いられ得るメモリ構成のさらなる例示的な詳細について説明するための例示的なメモリ構成を示す図である。

【図7A】図5のメモリ構成のために用いられ得るメモリ構成のさらなる例示的な詳細について説明するための例示的なメモリ構成を示す図である。

【図7B】図5のメモリ構成のために用いられ得るメモリ構成のさらなる例示的な詳細について説明するための例示的なメモリ構成を示す図である。

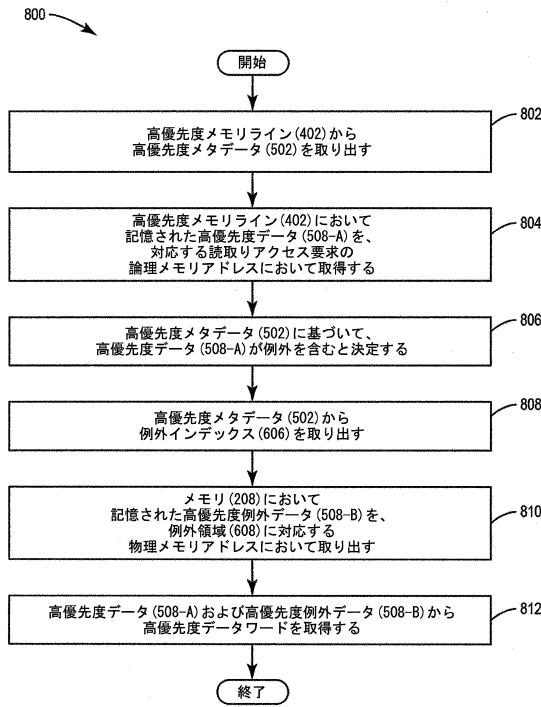

【図8】圧縮高優先度メモリラインが例外を示すときの、図2に示すプロセッサベースシステムにおけるメモリ内の圧縮高優先度メモリラインの優先度ベースの読み取りアクセスのための例示的なプロセスを示すフローチャートである。

30

【図9】圧縮低優先度メモリラインが例外を示すときの、図2に示すプロセッサベースシステムにおけるメモリ内の圧縮低優先度メモリラインの優先度ベースの読み取りアクセスのための例示的なプロセスを示すフローチャートである。

【図10】図2に示すプロセッサベースシステムにおけるメモリ内の圧縮メモリラインへの優先度ベースの書き込みアクセスのための例示的なプロセスを示すフローチャートである。

【図11】図2に示すプロセッサベースシステムにおけるメモリ内の低優先度圧縮メモリラインへの優先度ベースの書き込みアクセスのためのプロセスのさらなる例示的な詳細を示すフローチャートである。

40

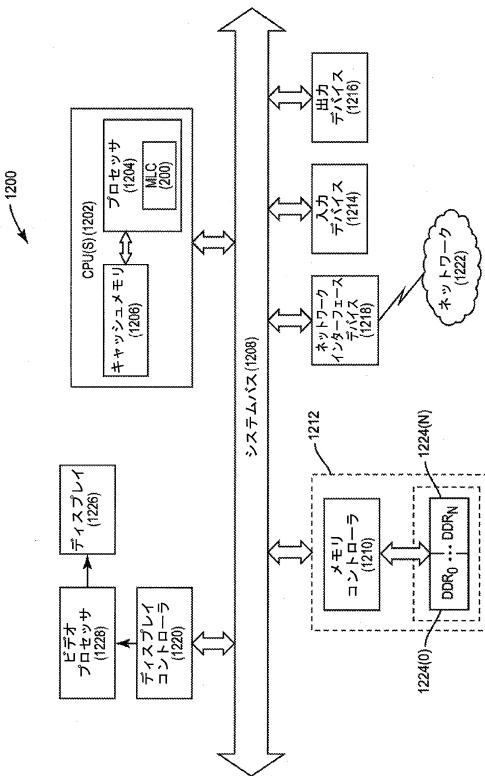

【図12】高優先度読み取りアクセス要求に対する読み取りアクセスレイテンシを低減するためにメモリ内の圧縮メモリラインの優先度ベースのアクセスを提供するように構成されたメモリアクセスデバイスを含むことができる例示的なプロセッサベースシステムのブロック図である。

**【発明を実施するための形態】**

**【0013】**

次に、図面を参照して、本開示のいくつかの例示的な態様について説明する。「例示的な」という語は、本明細書では「例、事例、または例示として機能すること」を意味するために使用される。「例示的な」として本明細書で説明するいずれの態様も、必ずしも他の態様よりも好ましいまたは有利であると解釈されるべきではない。

50

**【 0 0 1 4 】**

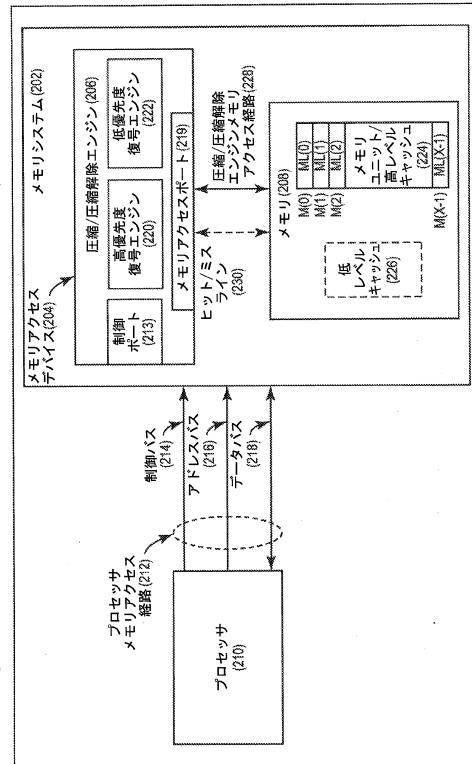

この点について、図2は、例示的なプロセッサベースシステム200のブロック図である。プロセッサベースシステム200における圧縮メモリラインの優先度ベースのアクセスの例示的な態様について説明する前に、プロセッサベースシステム200の例示的な構成要素の説明が最初に以下で提供される。

**【 0 0 1 5 】**

この点について、プロセッサベースシステム200は、高優先度読取りアクセス要求に対する読取りアクセスレイテンシを低減するためにメモリ内の圧縮メモリラインの優先度ベースのアクセスを提供するように構成されたメモリアクセスデバイス204を含むメモリシステム202を含む。たとえば、メモリアクセスデバイス204は、メモリシステム202用のメモリコントローラに含まれ得る。この例では、プロセッサベースシステム200におけるメモリアクセスデバイス204は、圧縮/圧縮解除エンジン206の形態で設けられる。圧縮/圧縮解除エンジン206は、高優先度読取りアクセス要求に対する読取りアクセスレイテンシを低減するために、メモリ208内のメモリロケーションM(0)～M(X-1)のメモリラインML(0)～ML(X-1)に記憶された圧縮メモリラインの優先度ベースのアクセスを提供するように構成され、ここで、「X」は、メモリ208に設けられた任意の数のメモリロケーションを表す。プロセッサベースシステム200は、プロセッサ210をさらに含む。プロセッサ210は、メモリ208に記憶されたプログラム命令を実行するか、またはプロセッサベースの機能を実行するためにメモリ208に記憶されたデータを別 の方法で利用するように構成される。

**【 0 0 1 6 】**

プロセッサ210は、プロセッサメモリアクセス経路212を介してメモリシステム202と通信する。圧縮/圧縮解除エンジン206は、プロセッサメモリアクセス経路212を介してプロセッサ210から読取りアクセス要求および書込みアクセス要求を受け取るように構成された制御ポート213を含む。プロセッサメモリアクセス経路212は、メモリシステム202へのアクセスを制御するための制御バス214と、メモリアクセスに対応するアドレスを提供するためのアドレスバス216と、メモリシステム202とデータを交換するためのデータバス218とを含む。圧縮/圧縮解除エンジン206は、メモリ208へのメモリ読取り/書込みアクセスを制御するように構成される。したがって、圧縮/圧縮解除エンジン206は、メモリ208へのアクセスを提供するメモリアクセスポート219をさらに含む。たとえば、圧縮/圧縮解除エンジン206は、メモリアクセスポート219を介してメモリ208からデータを取り出し、圧縮されている場合、取り出されたデータを圧縮解除し、取り出されたデータをプロセッサ210などの外部デバイスに与えるように構成される。圧縮/圧縮解除エンジン206は、プロセッサ210などの外部デバイスから受け取られたデータを圧縮し、メモリアクセスポート219を介してデータをメモリ208に記憶するようにさらに構成される。しかしながら、他の態様では、プロセッサは、メモリアクセスデバイス204として動作し、プロセッサメモリアクセス経路212を介してメモリ208に対して直接メモリ読取り/書込みアクセスを実行することができる。

**【 0 0 1 7 】**

引き続き図2を参照すると、圧縮/圧縮解除エンジン206は、メモリ208から高優先度データを読み込むように構成された高優先度復号エンジン220を含む。圧縮/圧縮解除エンジン206はまた、メモリ208から低優先度メモリラインを読み込むように構成された低優先度復号エンジン222を含む。

**【 0 0 1 8 】**

例示的なプロセッサベースシステム200では、メモリ208は、圧縮メモリラインを記憶するメモリユニット224を含む。メモリユニット224は、X個の物理メモリロケーションM(0)～M(X-1)を含み、各物理メモリロケーションMは、所定のサイズ、たとえば、64(64)バイトのデータのメモリラインMLを記憶するように構成される。圧縮メモリラインは、圧縮/圧縮解除エンジンメモリアクセス経路228を介して圧縮/圧縮解除エンジン206によってメモリユニット224に記憶され得る。上述のように、他の態様では、圧縮メモリラインは、プロセッサメモリアクセス経路212を介してプロセッサ210によってメモリユニット224に

10

20

30

40

50

記憶され得る。

#### 【0019】

例示的な態様では、各物理メモリロケーションMは、各メモリラインMLに、第1の圧縮メモリラインと第2の圧縮メモリラインの一部分とを記憶する。第2の圧縮メモリラインの一部分は、第1のメモリラインの圧縮によって対応するメモリラインML(0)～ML(X-1)に残された「穴」に記憶される。このことは、メモリユニット224がメモリユニット224のX個の物理メモリロケーションM(0)～M(X-1)のX個のメモリラインML(0)～ML(X-1)にX個よりも多い圧縮メモリラインを記憶することを可能にする。

#### 【0020】

例示的な一態様では、メモリ208はマルチレベルキャッシングメモリとして動作することができ、マルチレベルキャッシングの1つまたは複数のキャッシングレベルは、より速い読み取りアクセスのために、メモリユニット224から以前にアクセスされた非圧縮メモリラインを記憶することができる。この点について、メモリ208は、非圧縮メモリラインを記憶する随意の低レベルキャッシング226を含んでもよく、メモリユニット224は、圧縮メモリラインを記憶する高レベルキャッシングメモリとして動作してもよい。随意の低レベルキャッシング226は、アドレスバス216からアドレス情報を受け取ることができ、随意のヒット/ミスライン230を介して圧縮/圧縮解除エンジン206とヒット/ミス情報を交換することができる。この点について、読み取りアクセス要求のメモリアドレスが随意の低レベルキャッシング226においてキャッシングヒットになる場合、随意の低レベルキャッシング226は、随意のヒット/ミスライン230を介して圧縮/圧縮解除エンジン206にその旨をシグナリングし、要求されたデータをデータバス218を介してプロセッサ210に与える。しかしながら、読み取りアクセス要求の論理メモリアドレスが随意の低レベルキャッシング226においてキャッシングミスになる場合、随意の低レベルキャッシング226は、随意のヒット/ミスライン230を介して圧縮/圧縮解除エンジン206にその旨をシグナリングする。次いで、圧縮/圧縮解除エンジン206は、メモリユニット224における対応する圧縮メモリラインMLにアクセスし、圧縮メモリラインを圧縮解除し、圧縮解除されたデータを随意の低レベルキャッシング226に記憶することによって、要求されたデータにアクセスする。次いで、随意の低レベルキャッシング226は、要求されたデータをデータバス218を介してプロセッサ210に与える。簡単にするために、かつ限定としてではなく、これ以降は、メモリ208についてメモリユニット224のみを含むものとして説明する。

#### 【0021】

プロセッサベースシステム200におけるメモリ208内の圧縮メモリラインの優先度ベースのアクセスを提供するために、例示的な一態様では、圧縮/圧縮解除エンジン206は、メモリ208からデータにアクセスするための読み取りアクセス要求を受け取る。要求されたデータは所定のサイズであり、メモリ208内のアドレス指定可能な物理メモリロケーションM(0)～M(X-1)の各々は、所定のサイズの対応するメモリラインML(0)～ML(X-1)を記憶するように構成される。各メモリラインML(0)～ML(X-1)は、圧縮高優先度メモリラインを備える第1の圧縮メモリラインと、圧縮低優先度メモリラインの一部分を備える第2の圧縮メモリラインの一部分とを含むように構成される。このことは、メモリ208が、X個までの圧縮高優先度メモリラインを、対応する物理メモリロケーションM(0)～M(X-1)のメモリラインML(0)～ML(X-1)内にそれぞれ記憶し、したがって、X個までの圧縮高優先度メモリラインの各々を、対応する高優先度データの論理メモリアドレスに対応するメモリ208の物理メモリロケーションM(0)～M(X-1)に記憶することを可能にする。さらに、このことは、メモリ208が、追加の圧縮メモリライン、すなわち、圧縮低優先度メモリラインを、メモリ208のX個の物理メモリロケーションM(0)～M(X-1)内に記憶することを可能にし、したがって、メモリ208のサイズを増加させることなしにメモリ208の容量を増加させる。したがって、例示的な態様では、圧縮/圧縮解除エンジン206は、メモリ208の容量を増加させる一方で、低減されたレイテンシでメモリ208内の高優先度データにアクセスすることができる。

#### 【0022】

その点について、この例では、プロセッサメモリアクセス経路212を介して読み取りアク

10

20

30

40

50

セス要求を受け取ると、圧縮/圧縮解除エンジン206は、読み取りアクセス要求の優先度を決定する。読み取りアクセス要求が高優先度読み取りアクセス要求である場合、圧縮/圧縮解除エンジン206は、要求された高優先度データを含む物理メモリロケーションM(0)～M(X-1)にアクセスするための物理メモリアドレスとして、アドレスバス216において読み取りアクセス要求の論理メモリアドレスを使用する。メモリ208内の物理メモリロケーションM(0)～M(X-1)は、読み取りアクセス要求に対応する圧縮高優先度メモリラインを圧縮形態で含むメモリラインML(0)～ML(X-1)を含む。このようにすると、高優先度読み取りアクセス要求の論理メモリアドレスをメモリ208内の対応する物理メモリアドレスM(0)～M(X-1)に変換することに関連付けられたレイテンシは、要求された高優先度データにメモリ208からアクセスするために必要とされない。圧縮/圧縮解除エンジン206は、圧縮高優先度データを圧縮解除し、メモリシステム202は、要求された高優先度データをデータバス218を介してプロセッサ210に与える。

#### 【0023】

一方、読み取りアクセス要求が低優先度読み取りアクセス要求である場合、圧縮/圧縮解除エンジン206は、読み取りアクセス要求の論理メモリアドレスを、要求された低優先度データを記憶する連続するメモリロケーションM(0)～M(X-1)にアクセスするための物理メモリアドレスに変換する。連続する物理メモリロケーションM(0)～M(X-1)の各々は、対応する高優先度データの圧縮によって残された穴を含み、穴は、要求された低優先度データを圧縮形態で含むメモリラインML(0)～ML(X-1)を記憶するために結合する。したがって、圧縮/圧縮解除エンジン206は、圧縮低優先度データを圧縮解除し、要求された低優先度データをデータバス218を介して提供することができる。このようにすると、読み取りアクセス要求のための論理メモリアドレスの変換は必要とされないが、そのような変換は低優先度読み取りアクセス要求に限定され、したがって、プロセッサベースシステム200における圧縮メモリラインのより高い全体的なメモリアクセス効率を実現する。さらに、圧縮低優先度メモリラインは、高優先度データの圧縮によって残された穴に記憶され、したがって、メモリサイズを増加させることなしにメモリ容量を増加させる。

#### 【0024】

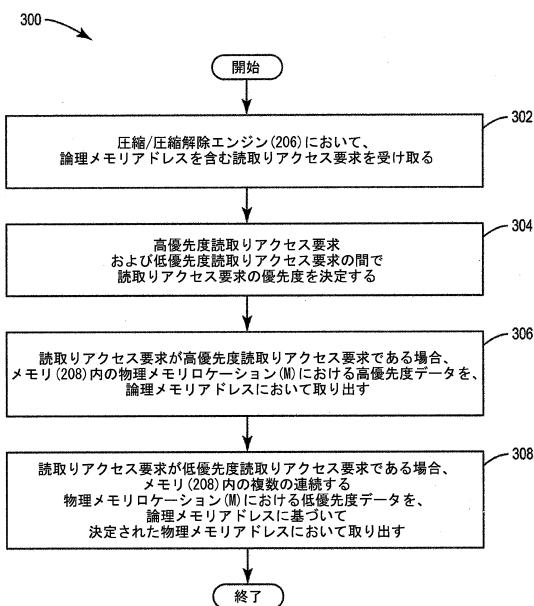

図3は、読み取りアクセスレイテンシを低減するために、図2のプロセッサベースシステム200におけるメモリ208内の圧縮メモリラインの優先度ベースの読み取りアクセス要求を実行する圧縮/圧縮解除エンジン206の例示的なプロセス300を示すフローチャートである。上記で説明したように、プロセッサベースシステム200の例では、圧縮/圧縮解除エンジン206は、メモリ208が随意の低レベルキャッシュ226を含まないとき、または随意の低レベルキャッシュ226が含まれるときに随意の低レベルキャッシュ226においてミスが生じた場合、メモリ読み取り要求を実行するよう求められる。例示的なプロセス300では、圧縮/圧縮解除エンジン206は、プロセッサメモリアクセス経路212を介してプロセッサ210から読み取りアクセス要求を受け取るように構成される(ブロック302)。読み取りアクセス要求は、アドレスバス216を介して提供される、メモリ208内の物理メモリロケーションM(0)～M(X-1)にアクセスするための論理メモリアドレスを含む。圧縮/圧縮解除エンジン206は、高優先度読み取りアクセス要求および低優先度読み取りアクセス要求の間で読み取りアクセス要求の優先度を決定するようにさらに構成される(ブロック304)。圧縮/圧縮解除エンジン206は、読み取りアクセス要求が高優先度読み取りアクセス要求である場合、圧縮/圧縮解除エンジンメモリアクセス経路228を介して、読み取りアクセス要求の論理メモリアドレスにおいて、メモリ208内の物理メモリロケーションM(0)～M(X-1)において記憶された高優先度データを取り出すようにさらに構成される(ブロック306)。圧縮/圧縮解除エンジン206は、読み取りアクセス要求が低優先度読み取りアクセス要求である場合、圧縮/圧縮解除エンジンメモリアクセス経路228を介して、読み取りアクセス要求の論理メモリアドレスに基づいて決定された、メモリ208内の複数の連続する物理メモリロケーションM(0)～M(X-1)において記憶された低優先度データを取り出すようにさらに構成される(ブロック308)。

#### 【0025】

したがって、メモリ208内の圧縮メモリラインの優先度ベースの読み取りアクセスのため

10

20

30

40

50

の例示的なプロセス300は、高優先度読み取りアクセス要求の論理メモリアドレスを対応する物理メモリアドレスに変換することを必要としない。このことは、メモリ208もしくは他のメモリ内のメタデータを用いてメタデータにアクセスするおよび/または変換を実行するためのインデックス付けと関連するレイテンシとを用いる必要をなくすことができる。したがって、たとえば、最も頻繁に使用されるデータを高優先度メモリラインに記憶することによって、これらの例示的な態様は、プロセッサベースシステム200において、要求されたデータの論理メモリアドレスの変換がデータの優先度にかかわらずアクセスのために必要とされるシステムの場合よりも高い全体的なメモリアクセス効率をもたらす。

#### 【 0 0 2 6 】

上記で説明したプロセッサベースシステム200におけるメモリ208内の圧縮メモリラインの優先度ベースのアクセスは、メモリ208の複数の所定の構成特性によってサポートされ得る。これらの所定の構成特性は、対応するアドレスのパリティおよび圧縮メモリラインの優先度、ならびにメモリ208のサイズに基づいた、メモリラインML(0)～ML(X-1)内の圧縮メモリラインのロケーションを含み得る。圧縮/圧縮解除エンジン206は、メモリ208からデータを効率的に取り出すために、これらの所定の構成特性を使用し得る。たとえば、圧縮/圧縮解除エンジン206は、要求された低優先度データを含む圧縮低優先度メモリラインの物理メモリロケーションM(0)～M(X-1)を決定するために、圧縮メモリラインの優先度およびメモリ208のサイズを知る必要がある。

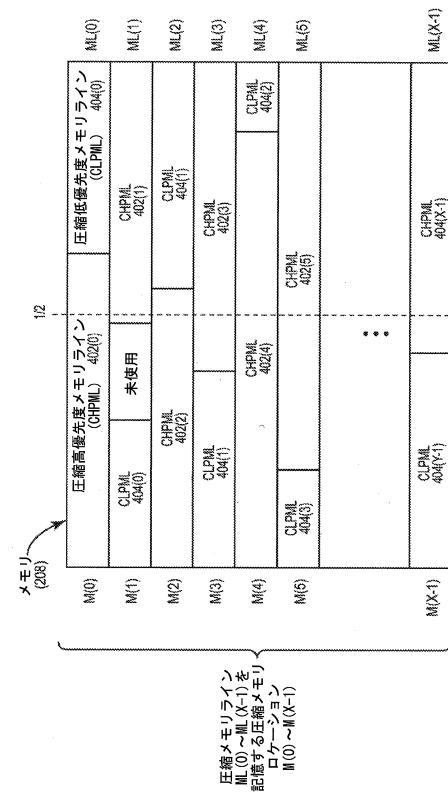

#### 【 0 0 2 7 】

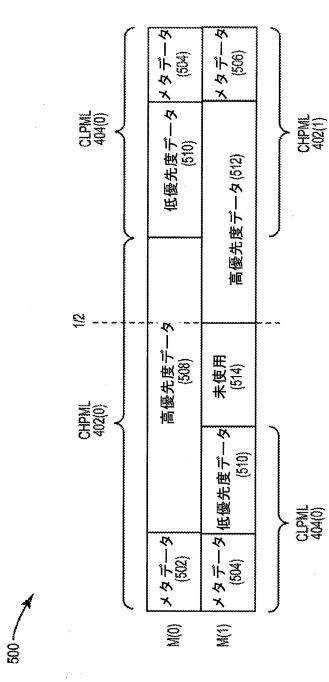

この点について、図4は、図2に示すプロセッサベースシステム200におけるメモリ208内の高優先度データおよび低優先度データのための記憶された圧縮メモリラインの例示的なメモリ構成400を示す図である。図2のメモリ208に関して、具体的にはメモリ208内のメモリユニット224に関して述べたように、メモリ208は、X個の物理メモリロケーションM(0)～M(X-1)を含み、物理メモリロケーションM(0)～M(X-1)の各々は、所定のサイズ、たとえば、64バイトのメモリラインML(0)～ML(X-1)を記憶するように構成される。例示的なメモリ構成400では、物理メモリロケーションM(0)～M(X-1)の各々は、(図4のCHPML402として示される)圧縮高優先度メモリライン402を含むメモリラインML(0)～ML(X-1)を記憶することが可能である。さらに、物理メモリロケーションM(0)～M(X-1)の各々は、対応する圧縮高優先度メモリライン402の圧縮によって物理メモリロケーションM(0)～M(X-1)に残された穴を少なくとも部分的に埋める(図4のCLPML404として示される)圧縮低優先度メモリラインの一部分を記憶することが可能である。メモリ208は、X個までの圧縮高優先度メモリライン402(0)～402(X-1)を記憶する。各圧縮高優先度メモリライン402は、対応するメモリラインML(0)～ML(X-1)に配置され、対応する非圧縮高優先度メモリライン、すなわち、対応する高優先度データの論理メモリアドレスと一致する、対応する物理メモリロケーションM(0)～M(X-1)に記憶される。この構成特性は、各圧縮高優先度メモリライン402が、メモリ208内の対応する物理メモリロケーションM(0)～M(X-1)から1つのみのメモリラインML(0)～ML(X-1)を読み取ることによってアクセスされることを可能にする。しかしながら、この構成特性を利用するためには、圧縮/圧縮解除エンジン206は、読み取りアクセス要求が高優先度アクセス要求であると決定する必要がある。

#### 【 0 0 2 8 】

この点について、圧縮/圧縮解除エンジン206は、読み取りアクセス要求の論理メモリアドレスが0からX-1にわたる高優先度アドレス範囲内にあると決定することによって、読み取りアクセス要求が高優先度読み取りアクセス要求であると決定するように構成される。詳細には、上述のように、メモリ208はX個の物理メモリロケーションM(0)～M(X-1)を含む。例示的な一態様では、物理メモリロケーションM(0)～M(X-1)の各々は、読み取りアクセス要求の論理メモリロケーションを物理メモリロケーションM(0)～M(X-1)として使用してアクセスされ得る、1つの圧縮高優先度メモリライン402を含む。したがって、例示的なメモリ構成400では、圧縮高優先度メモリライン402は、下側のX個の物理メモリロケーションM(0)～M(X-1)に記憶される。したがって、例示的な一態様では、高優先度アドレス範囲は0からX-1であり、圧縮/圧縮解除エンジン206は、読み取りアクセス要求の論理メモリアドレスが0か

10

20

30

40

50

らX-1の間に入ると決定することによって、読み取りアクセス要求が高優先度読み取りアクセス要求であると決定することができる。

#### 【0029】

この例では、読み取りアクセス要求の優先度を示すために読み取りアクセス要求の論理メモリアドレスを使用することは、受け取られた読み取りアクセス要求が高優先度アクセス要求であると決定するためにメモリ208または他のメモリ内のメタデータにアクセスする必要をなくす。さらに、各論理メモリアドレスは圧縮高優先度メモリライン402または圧縮低優先度メモリライン404のうちの1つに対応するので、圧縮/圧縮解除エンジン206は、読み取りアクセス要求の論理メモリアドレスが高優先度アドレス範囲外にあると決定することによって、読み取りアクセス要求が低優先度読み取りアクセス要求であると決定するようにさらに構成される。しかしながら、低優先度読み取りアクセス要求の場合、圧縮/圧縮解除エンジン206は、読み取りアクセス要求の論理メモリアドレスの変換を使用して、要求された低優先度データ、すなわち、対応する圧縮低優先度メモリライン404を含む物理メモリロケーションM(0)～M(X-1)を決定する必要がある。10

#### 【0030】

この点について、一様では、各圧縮低優先度メモリライン404は、対応する物理メモリロケーションM(0)～M(X-1)が低優先度読み取りアクセス要求の論理メモリアドレスから導出され得るように、メモリ構成400に記憶される。具体的には、この特定の例では、データは、2つの圧縮高優先度メモリライン402ごとに圧縮低優先度メモリライン404のうちの1つの圧縮低優先度メモリライン404が記憶されるように、メモリ208に記憶され、したがって、X個の物理メモリロケーションからX+Y個の論理メモリロケーションへのメモリ容量の50パーセント(50%)の増加を実現し、ここで、YはX/2であることに留意されたい。したがって、この様では、論理メモリロケーションの下側の3分の2、すなわち、論理メモリアドレス(0)～(X-1)は、圧縮高優先度メモリライン402(0)～402(X-1)に割り振られ、論理メモリロケーションの上側の3分の1、すなわち、論理メモリロケーション(X)～(X+Y-1)は、圧縮低優先度メモリライン404(0)～404(Y-1)に割り振られる。さらに、各圧縮低優先度メモリライン404は、物理メモリロケーションM(0)～M(X-1)のうちの2つの連続する物理メモリロケーションに記憶される。したがって、メモリ構成400の構成特性は、以下の式によつて、値Xおよび読み取りアクセス要求の対応する論理メモリロケーションに基づいて、対応する圧縮低優先度メモリライン404を記憶する複数の物理メモリロケーションM(0)～M(X-1)のうちの第1の物理メモリロケーションM(q)の決定を可能にする。20

$$q=2^*(\lceil m - X \rceil)$$

ここで、 $\lceil m \rceil$ は読み取りアクセス要求の論理メモリアドレスであり、Xはメモリ208内の物理メモリロケーションMの数である。

#### 【0031】

たとえば、メモリ208が512(512)個の物理メモリロケーションM(0)～M(511)を含む場合、メモリ208は、512個の圧縮高優先度メモリライン402(0)～402(511)および $512/2=256$ 個の圧縮低優先度メモリライン404(0)～404(255)を記憶することができ、メモリ208内の総容量は $512+256=768$ 個の論理メモリロケーションになる。さらに、読み取りアクセス要求の論理メモリアドレスが514(514)個である場合、物理メモリアドレスqは $2^*(514-512)=4$ である。したがって、読み取りアクセス要求の論理メモリアドレス514に対応する圧縮低優先度メモリライン404は、物理メモリロケーションM(4)、すなわち、図4のCLPML404(2)から始まる、連続する物理メモリロケーションM(0)～M(X-1)にある。したがって、この例示的な様は、論理メモリアドレス514を対応する連続する物理メモリロケーションM(4)～M(5)に変換することを必要とする。しかしながら、変換は、所定のすでに利用可能な値に基づいた単純な計算を必要とするにすぎず、このことは、変換を実行するためにメモリ208または他のメモリ内のメタデータにアクセスする必要および関連するレイテンシをなくす。40

#### 【0032】

したがって、メモリ構成400の構成特性は、圧縮/圧縮解除エンジン206が、読み取りアクセス要求において受け取られた論理メモリアドレスおよびメモリ208内の物理メモリロケーションM(0)～M(X-1)を決定する。50

ーションXの数に基づいて、その中の各圧縮低優先度メモリライン404の物理メモリロケーションM(0)～M(X-1)を決定することを可能にする。しかしながら、各物理メモリロケーションM(0)～M(X-1)は、圧縮高優先度メモリライン402と圧縮低優先度メモリライン404の一部分とを含むメモリラインML(0)～ML(X-1)を記憶するので、圧縮/圧縮解除エンジン206は、要求されたデータを対応するメモリラインML(0)～ML(X-1)から取り出すために、追加の情報を必要とする。この点について、例示的な一態様では、各圧縮高優先度メモリライン402は、対応する物理メモリアドレスのパリティに基づいて、対応する物理メモリロケーションM(0)～M(X-1)の端において記憶され、各圧縮低優先度メモリライン404は、連続的な圧縮高優先度メモリライン402の間に記憶され、各圧縮低優先度メモリライン404の各部分は、対応する物理メモリロケーションM(0)～M(X-1)の半分までを占有するために、対応する物理メモリロケーションM(0)～M(X-1)の端において記憶される。以下で詳細に説明するように、このことは、メモリ208への単一のメモリアクセスによる各圧縮メモリラインの取出しを容易にする。

#### 【0033】

この点について、メモリ構成400では、圧縮高優先度メモリライン402および圧縮低優先度メモリライン404は、次のように記憶される。対応する物理メモリロケーションM(0)～M(X-1)の物理メモリアドレスが偶数であるとき、圧縮高優先度メモリライン402は、対応する物理メモリロケーションM(0)～M(X-1)において記憶されたメモリラインML(0)～ML(X-1)の左端に記憶され、対応する物理メモリロケーションM(0)～M(X-1)の物理メモリアドレスが奇数であるとき、圧縮高優先度メモリライン402は、対応するメモリロケーションM(0)～M(X-1)において記憶されたメモリラインML(0)～ML(X-1)の右端に記憶される。たとえば、図4のメモリ構成400では、物理メモリロケーションM(0)において記憶される圧縮高優先度メモリライン402(0)は、物理メモリアドレス(0)が偶数であるので、物理メモリロケーションM(0)の左端において記憶される。さらに、物理メモリロケーションM(1)において記憶される圧縮高優先度メモリライン402(1)は、物理メモリアドレス(1)が奇数であるので、物理メモリロケーションM(1)の右端において記憶される。このことは、圧縮低優先度メモリライン404(0)が圧縮高優先度メモリライン402(0)と圧縮高優先度メモリライン402(1)との間に記憶されることを可能にし、その結果、圧縮低優先度メモリライン404(0)の第1の部分は物理メモリロケーションM(0)の右側にある穴において記憶され、圧縮低優先度メモリライン404(0)の第2の部分は物理メモリロケーションM(1)の左側にある穴において連続して記憶される。さらに、メモリ構成400に示すように、圧縮低優先度メモリライン404(0)の第1の部分および第2の部分は、それらの対応するメモリラインML(0)～ML(X-1)の半分より多くを占有しない。メモリ構成400のこれらの構成特性は、物理メモリロケーションM(0)のハーフキャッシュラインポイントから始まる単一のメモリアクセスで、メモリ208において圧縮低優先度メモリライン404(0)全体がアクセスされることを可能にする。したがって、メモリ208のメモリ構成400は、圧縮/圧縮解除エンジン206が、メモリ208の単一のメモリアクセスで、圧縮高優先度メモリライン402および圧縮低優先度メモリライン404のいずれかにアクセスすることを可能にする。

#### 【0034】

しかしながら、メモリ208内の物理メモリロケーションM(0)～M(X-1)から圧縮メモリラインを取り出すために、対応するメタデータが、この例では、その中の圧縮メモリラインの境界を決定するために使用される。この点について、図5は、図4に示すメモリ208のメモリ構成400における、記憶された圧縮高優先度メモリライン402(0)および402(1)ならびに圧縮低優先度メモリライン404(0)の例示的なメモリ構成500を詳細に示す図である。圧縮高優先度メモリライン402(0)および402(1)ならびに圧縮低優先度メモリライン404(0)の各々は、それぞれ、対応するメタデータ502、504、および506を含み、これらのメタデータは、たとえば、対応する圧縮メモリラインが例外を含むかどうかを示す。例外については、図6を参照しながら以下で説明する。各メタデータ502、504、および506は、それらの対応する圧縮メモリライン内の対応する物理メモリロケーションM(0)～M(X-1)の端に位置し、圧縮/圧縮解除エンジン206が、それぞれ、圧縮メモリライン402(0)、404(0)、402(1)

10

20

30

40

50

の対応する圧縮メモリラインからメタデータを取り出すことを可能にする。さらに、圧縮メモリライン402(0)、402(1)、404(0)の各々は、図示のように、それぞれ、高優先度データ508、低優先度データ510、および高優先度データ512を含むように構成される。メモリ構成500では、物理メモリロケーションM(1)は、未使用セクション514をさらに含む。この点について、任意の物理メモリロケーションM(0)～M(X-1)は、その中の圧縮高優先度メモリライン402および圧縮低優先度メモリライン404が物理メモリロケーションM(0)～M(X-1)全体を完全に占有しないとき、未使用セクション514を含み得る。

#### 【 0 0 3 5 】

したがって、メモリ構成500の構成特性は、圧縮/圧縮解除エンジン206が、追加のメタデータにアクセスする必要なしに、読み取りアクセス要求の論理メモリアドレスおよびメモリ208の物理メモリロケーションXの数に基づいた単純な計算によって、圧縮メモリライン402、404のうちの所望の圧縮メモリラインを含む物理メモリアドレスM(0)～M(X-1)を決定することを可能にする。たとえば、図2～図5を参照すると、論理メモリアドレスを含む読み取りアクセス要求を受け取ると(図3のブロック302)、圧縮/圧縮解除エンジン206は、論理メモリアドレスに基づいて読み取りアクセス要求の優先度を決定する。論理メモリアドレスが(0)である場合、かつメモリ208が512個の物理メモリロケーションを含む場合、圧縮/圧縮解除エンジン206は、読み取りアクセス要求が高優先度読み取りアクセス要求であると決定する。これは、論理メモリアドレスがメモリ208の物理メモリロケーションM(0)～M(X-1)の数よりも小さく、したがって、メモリ208の所定の高優先度アドレス範囲内にあるからである。次いで、圧縮/圧縮解除エンジン206は、読み取りアクセス要求(0)の論理メモリアドレスを対応する圧縮メモリラインML(0)の物理メモリアドレス(0)として使用して、物理メモリロケーションM(0)から圧縮高優先度メモリライン402(0)を取り出す。さらに、物理メモリアドレス(0)が偶数であるので、圧縮/圧縮解除エンジン206は、圧縮高優先度メモリライン402(0)が物理メモリロケーションM(0)の左端にあると決定する。次いで、圧縮/圧縮解除エンジン206は、圧縮高優先度メモリライン402(0)の左端および長さNから高優先度メタデータ502を取り出す。次いで、圧縮/圧縮解除エンジン206は、圧縮高優先度メモリライン402(0)から高優先度データ508を取り出し、圧縮されている場合、高優先度データ508を圧縮解除し、非圧縮高優先度データをデータバス218を介してプロセッサ210に与える。

#### 【 0 0 3 6 】

上記で説明したように、各物理メモリロケーションM(0)～M(X-1)は、所定のサイズまでのデータを記憶することができる。さらに、図5に示す例示的なメモリ構成500では、各物理メモリロケーションM(0)～M(X-1)は、圧縮高優先度メモリライン402と圧縮低優先度メモリライン404の一部分とを含み、圧縮メモリライン402、404の各圧縮メモリラインは、対応するメタデータフィールドおよび対応する圧縮データフィールドを含む。このことは、たとえば、高優先度データに割り振られる空間を制限する。一実施形態では、たとえば、64(64)バイトを記憶することができるメモリロケーションMの場合、最低でも4(4)バイトが高優先度メタデータおよび圧縮低優先度メモリライン404のために予約され得るので、60(60)バイトのみが高優先度データに割り振られ得る。しかしながら、高優先度データは、対応するデータフィールド内に収まるように圧縮可能ではなく、例外を引き起こす場合がある。この点について、例示的な実施形態では、非圧縮高優先度データの一部分を記憶するために、例外メモリ領域内の追加のメモリロケーションが割り振られる。このようにすると、高優先度データの部分が圧縮高優先度メモリライン402の対応するデータフィールドに非圧縮で記憶され、残りが追加のメモリロケーションに記憶される。したがって、圧縮/圧縮解除エンジン206は、例外が発生したと決定し、圧縮高優先度メモリライン402および例外領域内のメモリロケーションからデータを取り出すことによって例外を処理するように構成される。

#### 【 0 0 3 7 】

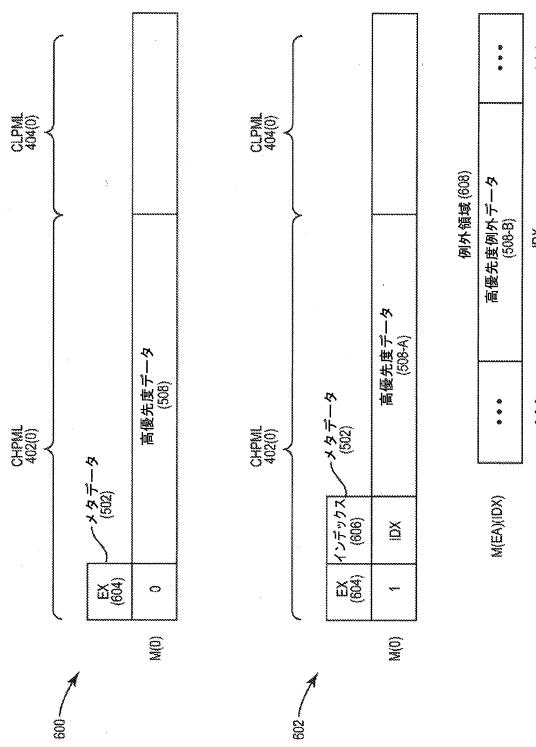

この点について、図6は、図5に示すメモリ構成500の態様を詳細に説明するメモリ構成600および602を示す図である。具体的には、メモリ構成600および602は、例示的な態様に

10

20

30

40

50

よる例外の使用を例示するために、圧縮高優先度メモリライン402(0)の高優先度メタデータ502のさらなる詳細を提供する。この点について、高優先度メタデータ502は、圧縮高優先度メモリライン402が例外を含むかどうかを圧縮/圧縮解除エンジン206に示すための例外フラグ604を含む。さらに、圧縮高優先度メモリライン402が例外を含むことを例外フラグ604が示すとき、高優先度メタデータ502は、例外領域608内の追加のデータのロケーションを圧縮/圧縮解除エンジン206に示すための例外インデックス606をさらに含む。

#### 【 0 0 3 8 】

この点について、メモリ構成600では、例外フラグ604は、圧縮高優先度メモリライン402(0)が例外を含まないことを示す偽に(たとえば、「0」に)設定される。したがって、図6のメモリ構成600では、要求された高優先度データは、高優先度データ508として圧縮形態で記憶され、それに応じて圧縮/圧縮解除エンジン206によって取り出され得る。しかしながら、メモリ構成602では、例外フラグ604は、圧縮高優先度メモリライン402(0)が例外を含むことを示す真に(たとえば、「1」に)設定される。さらに、例外により、高優先度メタデータ502は、インデックスIDXに設定された例外インデックス606をさらに含む。したがって、図6のメモリ構成602では、要求された高優先度データは、物理メモリロケーションM(0)における高優先度データ508-AとIDXによってインデックス付けされた例外領域608M(EA)に割り振られた物理メモリロケーションにおける高優先度例外データ508-Bの組合せとして非圧縮形態で記憶される。したがって、圧縮/圧縮解除エンジン206は、それに応じて要求された高優先度データを取り出すように構成される。

#### 【 0 0 3 9 】

上記で説明した例示的な態様では、高優先度データ508-Aおよび508-Bの部分は、非圧縮で記憶される。このことは、圧縮/圧縮解除エンジン206が、圧縮解除を実行する必要なしに、要求された高優先度データを取り出すこと、または、所定のサイズとなるであろう、取り出されたデータのサイズを決定することを可能にする。このことは、例外の使用によって実証されるように、対応するデータがうまく圧縮しない(すなわち、圧縮がサイズの著しい低減をもたらさない)ので、メモリ208のメモリ容量に著しく影響を及ぼさない。したがって、圧縮は大きな利益をもたらさない。さらに、例外領域は、既知のバイト数を記憶することのみを必要とするので、例外領域の使用率を最大化することができる。たとえば、64(64)バイトを記憶することができるメモリロケーションMの場合、最低でも4(4)バイトが高優先度メタデータおよび圧縮低優先度メモリライン404のために予約され得るので、60(60)バイトのみが高優先度データに割り振られ得る。したがって、60バイト未満に圧縮することができない高優先度データは、例外を引き起こすことになる。そのような高優先度データの場合、例示的な態様では、60バイトが高優先度データ508-Aとして非圧縮で記憶され、高優先度データの残りの4バイトのみが高優先度例外データ508-Bとして非圧縮で記憶される。したがって、例外領域に記憶されたデータの圧縮は、メモリ208の、または例外領域が存在するメモリのメモリ容量を著しく改善しない。

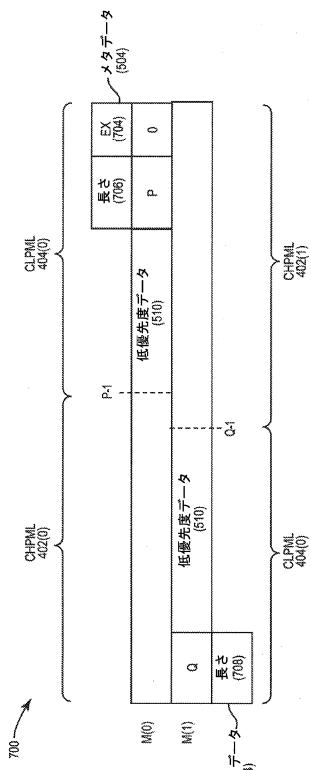

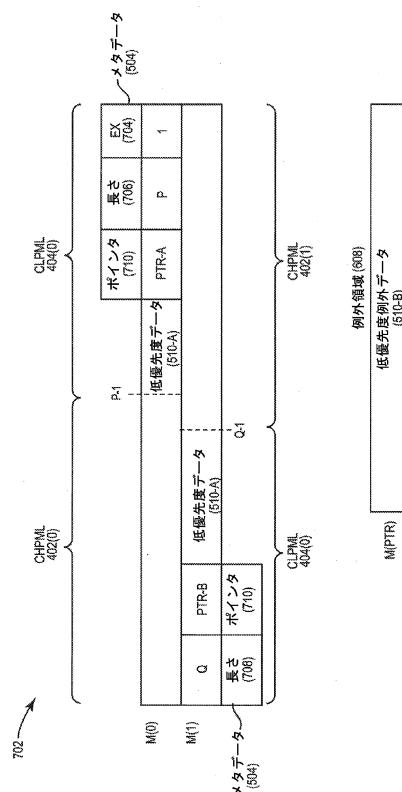

#### 【 0 0 4 0 】

上記の例示的な態様は、高優先度データの、特に、高優先度データ例外の記憶および読み取りに関するメモリ構成を提供する。低優先度データは、高優先度データの記憶および読み取りを補完するために記憶され読み取られる。その点について、図7Aおよび図7Bは、それぞれ、図5に示す例示的なメモリ構成500のさらなる態様を詳細に説明する例示的なメモリ構成700および702を示す図である。具体的には、メモリ構成700および702は、例示的な態様による例外の使用を例示するために、圧縮低優先度メモリライン404(0)の低優先度メタデータ504のさらなる例示的な詳細を提供する。この点について、低優先度メタデータ504は、例外フラグ704と、Pに設定された低優先度データ510の第1の部分の長さ706と、Qに設定された低優先度データ510の第2の部分の長さ708とを含む。さらに、低優先度メタデータ504は、対応する圧縮メモリラインが例外を含むことを例外フラグ704が示すとき、例外ポインタ710を含む。

#### 【 0 0 4 1 】

この点について、図7Aのメモリ構成700では、例外フラグは、圧縮低優先度メモリライ

10

20

30

40

50

ン404(0)が例外を含まないことを示す偽(たとえば、「0」)である。したがって、メモリ構成700では、要求された低優先度データは、連続する物理メモリロケーションM(0)～M(1)において低優先度データ510として圧縮形態で記憶され、それに応じて圧縮/圧縮解除エンジン206によって取り出され得る。しかしながら、図7Bのメモリ構成702では、例外フラグ704は真(たとえば、「1」)に設定され、例外ポインタ710は、PTR-AおよびPTR-Bとしてセグメント化されたアドレスPTRに設定される。したがって、メモリ構成702では、要求された低優先度データは、連続する物理メモリロケーションM(0)～M(1)における低優先度データ510-Aの一部分と例外領域608内の物理メモリロケーションM(PTR)における低優先度例外データ510-Bの別の部分を組み合わせることによって取り出される。例示的な様では、低優先度データは、例外の場合でも圧縮形態で記憶される。しかしながら、低優先度データは、非圧縮で記憶されてもよい。

#### 【0042】

この点について、図8は、圧縮高優先度メモリライン402が例外を示すときの、プロセッサベースシステム200におけるメモリ208内の圧縮高優先度メモリライン402の優先度ベースの読み取りアクセスのための例示的なプロセス800を示すフローチャートである。例示的なプロセス800は、メモリ208内の物理メモリロケーションM(0)～M(X-1)における高優先度データを、その中の圧縮高優先度メモリライン402が例外を示すとき、高優先度読み取りアクセス要求の論理メモリアドレスにおいて取り出す(ブロック306)ための例示的なプロセスについて説明しているので、図3のブロック306に関する。

#### 【0043】

この点について、論理メモリアドレスを含む読み取りアクセス要求を受け取り、読み取りアクセス要求が高優先度読み取りアクセス要求であると決定すると(図3のブロック302～304)、圧縮/圧縮解除エンジン206は、メモリ208の物理メモリロケーションM(0)～M(X-1)から高優先度メタデータ502を取り出す(ブロック802)。たとえば、図6を参照すると、論理メモリアドレスが0である場合、圧縮/圧縮解除エンジン206は、M(0)から圧縮高優先度メモリライン402(0)を、さらに、高優先度メタデータ502から例外フラグ604を取り出す。圧縮/圧縮解除エンジン206は、その中の圧縮高優先度メモリライン402から高優先度データを取得する(ブロック804)。次いで、圧縮/圧縮解除エンジン206は、高優先度メタデータ502に基づいて、高優先度データが例外を含むと決定する(ブロック806)。圧縮/圧縮解除エンジン206は、たとえば、高優先度メタデータ502内の例外フラグ604を読み取ることによって、このことを決定し得る。次いで、圧縮/圧縮解除エンジン206は、高優先度メタデータ502から例外インデックス606を取り出し(ブロック808)、例外インデックス606によってインデックス付けされた例外領域に対応する物理メモリアドレスにおいて記憶された高優先度例外データ508-Bを取り出す(ブロック810)。次いで、圧縮/圧縮解除エンジン206は、高優先度データ508-Aおよび高優先度例外データ508-Bから要求された高優先度データを取得する(ブロック812)。

#### 【0044】

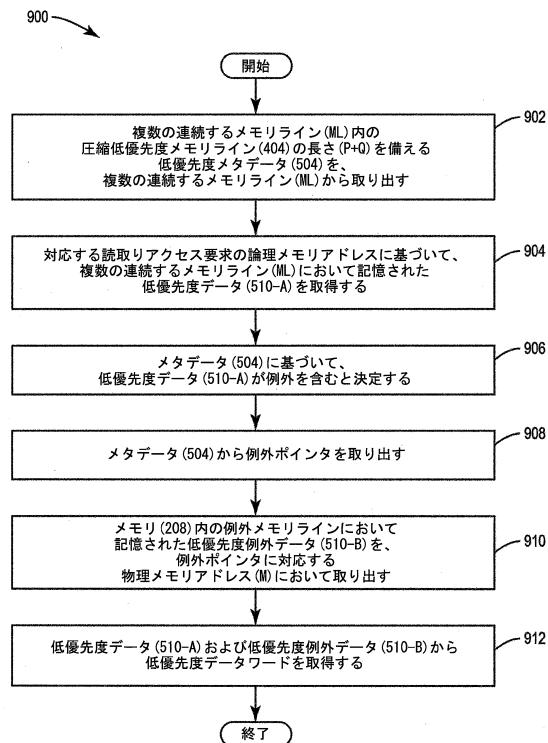

さらに、図9は、圧縮低優先度メモリライン404が例外を示すときの、プロセッサベースシステム200におけるメモリ208内の圧縮低優先度メモリライン404の優先度ベースの読み取りアクセスのための例示的なプロセス900を示すフローチャートである。例示的なプロセス900は、メモリ208内の複数の連続する物理メモリロケーションにおける低優先度データを、読み取りアクセス要求の論理メモリアドレスに基づいて決定された物理メモリアドレスにおいて取り出すための例示的なプロセスについて説明しているので、図3のブロック308に関する。

#### 【0045】

この点について、論理メモリアドレスを含む読み取りアクセス要求を受け取り、読み取りアクセス要求が低優先度読み取りアクセス要求であると決定すると(図3のブロック302～304)、圧縮/圧縮解除エンジン206は、メモリ208の物理メモリロケーションM(0)～M(X-1)から、その中の圧縮低優先度メモリライン404の長さを含む低優先度メタデータ504を取り出す(ブロック902)。たとえば、図7Bを参照すると、読み取りアクセス要求の論理メモリアドレ

10

20

30

40

50

スが、物理メモリアドレス0に変換されるXに設定される場合、圧縮/圧縮解除エンジン206は、連続する物理メモリロケーションM(0)～M(1)から圧縮低優先度メモリライン404(0)を取り出し、低優先度メタデータ504から長さPおよびQを取り出す。圧縮/圧縮解除エンジン206は、長さPおよびQを使用して、その中の圧縮低優先度メモリライン404から低優先度データを取得する(ブロック904)。たとえば、物理メモリアドレスが0である場合、圧縮/圧縮解除エンジン206は、長さPおよびQを使用して、連続する物理メモリロケーションM(0)～M(1)において圧縮低優先度メモリライン404(0)から低優先度データ510-Aを取得する。次いで、圧縮/圧縮解除エンジン206は、低優先度メタデータ504に基づいて、低優先度データが例外を含むと決定する(ブロック906)。圧縮/圧縮解除エンジン206は、たとえば、低優先度メタデータ504内の例外フラグ704を読み取ることによって、このことを決定し得る。次いで、圧縮/圧縮解除エンジン206は、低優先度メタデータ504から例外ポインタ710を取り出し(ブロック908)、メモリ208内の例外メモリラインにおいて記憶された低優先度例外データ510-Bを、例外ポインタM(PTR)に対応する物理メモリアドレスにおいて取り出す(ブロック910)。次いで、圧縮/圧縮解除エンジン206は、低優先度データ510-Aおよび低優先度例外データ510-Bから要求された低優先度データを取得する(ブロック912)。

#### 【 0 0 4 6 】

前述のように、プロセッサベースシステム200におけるメモリ208内の圧縮メモリラインの優先度ベースのアクセスは、メモリ208に書き込まれる圧縮メモリラインの構成によってサポートされ得る。具体的には、各メモリロケーションM(0)～M(X-1)は、圧縮高優先度メモリライン402と、圧縮低優先度メモリライン404の少なくとも一部分とを記憶する。この点について、例示的な一態様では、非圧縮高優先度データは、圧縮高優先度データを含む圧縮高優先度メモリライン402を記憶するメモリロケーションM(0)～M(X-1)の物理メモリアドレスが非圧縮高優先度データの論理メモリアドレスと一致するように、圧縮され、メモリ208に記憶される。さらに、非圧縮低優先度データは、圧縮され、高優先度データの圧縮によって残された穴においてメモリ208に記憶される。したがって、例示的な態様では、圧縮/圧縮解除エンジン206は、メモリ208の容量を増加させる一方で、低減されたレイテンシでメモリ208内の高優先度データにアクセスすることができる。さらに、別の例示的な態様では、圧縮低優先度データは、圧縮低優先度データの物理メモリアドレスが非圧縮低優先度データの論理メモリアドレスをインデックス付けすることによって決定されるように記憶されてもよく、論理メモリアドレスを対応する物理メモリアドレスに変換することを用いるためにメモリ208内のメタデータにアクセスする必要をなくすことによって、プロセッサベースシステム200における圧縮メモリラインの全体的なメモリアクセス効率をさらに増加させる。

#### 【 0 0 4 7 】

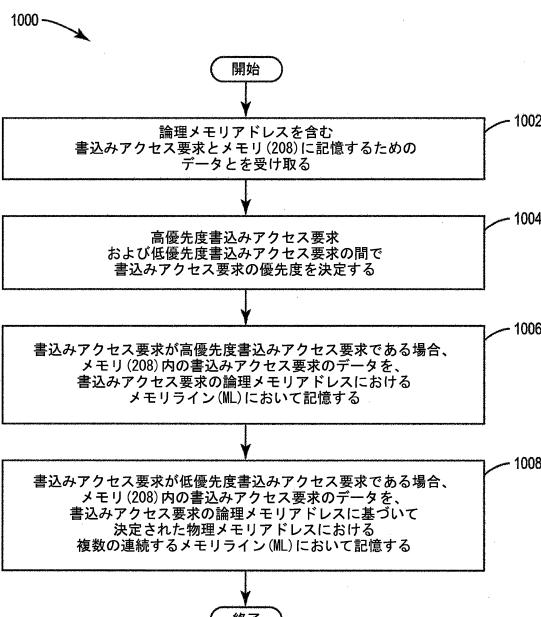

この点について、図10は、図2に示すプロセッサベースシステム200におけるメモリ208内の圧縮メモリラインの優先度ベースの書き込みアクセスのための例示的なプロセス1000を示すフローチャートである。例示的な態様では、プロセス1000は、圧縮/圧縮解除エンジンメモリアクセス経路228を介して圧縮/圧縮解除エンジン206によって実行される。プロセス1000はまた、プロセッサメモリアクセス経路212を介してプロセッサ210によって、またはプロセッサベースシステム200の外部にある他のプロセッサ(図示せず)によって実行され得る。

#### 【 0 0 4 8 】

この点について、例示的な態様では、圧縮/圧縮解除エンジン206は、論理メモリアドレスを備える書き込みアクセス要求をアドレスバス216を介して受け取り、メモリ208に記憶するためのデータをデータバス218を介して受け取る(ブロック1002)。圧縮/圧縮解除エンジン206は、高優先度書き込みアクセス要求および低優先度書き込みアクセス要求の間で書き込みアクセス要求の優先度を決定する(ブロック1004)。次いで、圧縮/圧縮解除エンジン206は、書き込みアクセス要求が高優先度書き込みアクセス要求である場合、圧縮/圧縮解除エンジンメモリアクセス経路228を介して、メモリ208内の書き込みアクセス要求のデータを、書き込みアクセス要求の論理メモリアドレスにおけるメモリロケーションM(0)～M(X-1)において

記憶する(ブロック1006)。しかしながら、書込みアクセス要求が低優先度書込みアクセス要求である場合、圧縮/圧縮解除エンジン206は、メモリ208内の書込みアクセス要求のデータを、書込みアクセス要求の論理メモリアドレスに基づいて決定された物理メモリアドレスにおけるメモリ208内の複数の連続するメモリロケーション( $M(0) \sim M(X-1)$ )において記憶する。

#### 【0049】

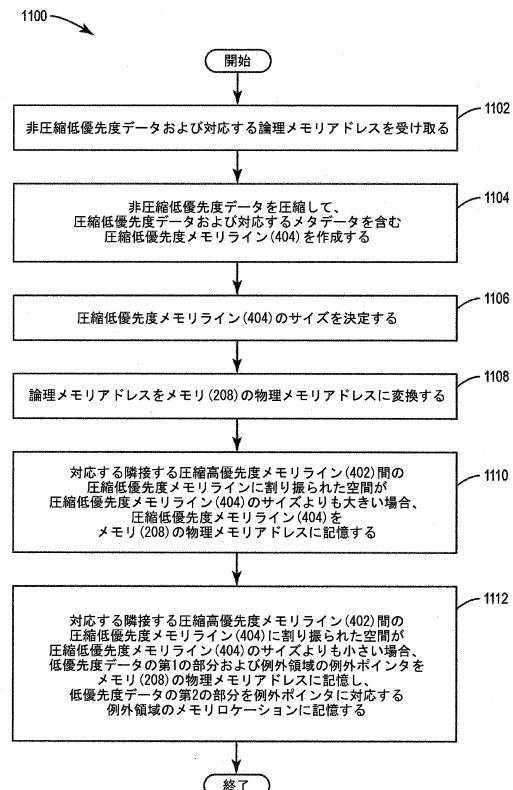

上述のように、書込みアクセス要求が高優先度書込みアクセス要求である場合、圧縮/圧縮解除エンジン206は、高優先度データを、対応する読み取りアクセス要求の論理メモリアドレスと一致するメモリ208の物理メモリアドレスにおいて記憶する。しかしながら、例示的な一態様では、書込みアクセス要求が低優先度書込みアクセス要求である場合、圧縮/圧縮解除エンジン206は、低優先度データを記憶するための適切な穴を決定しなければならない。この点について、図11は、図2に示すプロセッサベースシステム200におけるメモリ208内の低優先度圧縮メモリラインの優先度ベースの書込みアクセスのための詳細な例示的なプロセス1100を示すフローチャートである。圧縮/圧縮解除エンジン206は、非圧縮低優先度データを受け取る(ブロック1102)。圧縮/圧縮解除エンジン206は、非圧縮低優先度データを圧縮して、圧縮低優先度メモリライン404を作成する(ブロック1104)。圧縮低優先度メモリライン404は、圧縮低優先度データおよび対応するメタデータを含む。たとえば、図7Aを参照すると、低優先度メタデータ504は、圧縮低優先度メモリライン404の長さ $P+Q$ を含む。圧縮/圧縮解除エンジン206は、圧縮低優先度メモリライン404のサイズを決定し(ブロック1106)、論理メモリアドレスをメモリ208の物理メモリアドレスに変換する。圧縮/圧縮解除エンジン206は、対応する隣接する圧縮高優先度メモリライン402間の圧縮低優先度メモリライン404に割り振られた空間が、圧縮低優先度メモリライン404のサイズよりも大きい場合、圧縮低優先度メモリライン404を、メモリ208の物理メモリアドレスにおける物理メモリロケーション $M(0) \sim M(X-1)$ で始まる連続する物理メモリロケーションに記憶する(ブロック1110)。たとえば、図7Aを参照すると、物理メモリアドレスが0である場合、圧縮/圧縮解除エンジン206は、圧縮高優先度メモリライン402(0)と402(1)との空間が圧縮低優先度メモリライン404(0)のサイズよりも大きい場合、圧縮低優先度メモリライン404を物理メモリロケーション $M(0)$ および $M(1)$ において記憶する。

#### 【0050】

一方、圧縮/圧縮解除エンジン206は、対応する隣接する圧縮高優先度メモリライン402間の圧縮低優先度メモリライン404に割り振られた空間が圧縮低優先度メモリライン404のサイズよりも小さい場合、低優先度データの第1の部分および例外領域608の例外ポインタをメモリ208の物理メモリアドレスに記憶し、低優先度データの第2の部分を例外ポインタに対応する例外領域608のメモリロケーションにおいて記憶する。たとえば、図7Bを参照すると、物理メモリアドレスが0である場合、圧縮/圧縮解除エンジン206は、圧縮高優先度メモリライン402(0)と402(1)との間の空間が圧縮低優先度メモリライン404(0)のサイズよりも小さい場合、低優先度データ510-Aの第1の部分および例外ポインタPTRを物理メモリロケーション $M(0)$ および $M(1)$ に記憶し、例外領域内の低優先度データ510-Bの第2の部分を物理メモリロケーション $M(PTR)$ において記憶する。

#### 【0051】

本明細書で開示する態様による、プロセッサベースシステムにおけるメモリ内の圧縮メモリラインの優先度ベースのアクセスは、任意のプロセッサベースデバイスにおいて提供され得るか、または任意のプロセッサベースデバイスに統合され得る。例は、限定はしないが、セットトップボックス、エンターテインメントユニット、ナビゲーションデバイス、通信デバイス、固定ロケーションデータユニット、モバイルロケーションデータユニット、モバイルフォン、セルラーフォン、スマートフォン、タブレット、ファブレット、サーバ、コンピュータ、ポータブルコンピュータ、デスクトップコンピュータ、携帯情報端末(PDA)、モニタ、コンピュータモニタ、テレビジョン、チューナー、ラジオ、衛星ラジオ、音楽プレーヤ、デジタル音楽プレーヤ、ポータブル音楽プレーヤ、デジタルビデオプレーヤ、ビデオプレーヤ、デジタルビデオディスク(DVD)プレーヤ、ポータブルデジタル

ビデオプレーヤ、および自動車を含む。

#### 【0052】

この点について、図12は、図2に示す圧縮/圧縮解除エンジン206を含むことができる例示的なプロセッサベースシステム1200のブロック図である。この例では、プロセッサベースシステム1200は、各々が1つまたは複数のプロセッサ1204を含む、1つまたは複数の中央処理装置(CPU)1202を含む。1つまたは複数のプロセッサ1204は、図1のブロックベースのコンピュータプロセッサ100を備え得る。CPU1202は、マスタデバイスであってもよい。CPU1202は、一時的に記憶されているデータに迅速にアクセスするために、プロセッサ1204に結合されたキャッシュメモリ1206を有してもよい。CPU1202は、システムバス1208に結合され、プロセッサベースシステム1200に含まれるマスタデバイスとスレーブデバイスを相互結合することができる。よく知られているように、CPU1202は、システムバス1208を介してアドレス情報、制御情報、およびデータ情報を交換することによって、これらの他のデバイスと通信する。たとえば、CPU1202は、スレーブデバイスの一例としてのメモリコントローラ1210にバストランザクション要求を通信することができる。10

#### 【0053】

他のマスタデバイスおよびスレーブデバイスは、システムバス1208に接続され得る。図12に示すように、これらのデバイスは、例として、メモリシステム1212、1つまたは複数の入力デバイス1214、1つまたは複数の出力デバイス1216、1つまたは複数のネットワークインターフェースデバイス1218、および1つまたは複数のディスプレイコントローラ1220を含むことができる。入力デバイス1214は、限定はしないが、入力キー、スイッチ、音声プロセッサなどを含む、任意のタイプの入力デバイスを含むことができる。出力デバイス1216は、限定はしないが、オーディオ、ビデオ、他の視覚インジケータなどを含む、任意のタイプの出力デバイスを含むことができる。ネットワークインターフェースデバイス1218は、ネットワーク1222との間のデータの交換を可能にするように構成された任意のデバイスであり得る。ネットワーク1222は、限定はしないが、ワイヤードネットワークまたはワイヤレスネットワーク、プライベートネットワークまたは公衆ネットワーク、ローカルエリアネットワーク(LAN)、ワイヤレスローカルエリアネットワーク(WLAN)、ワイドエリアネットワーク(WAN)、BLUETOOTH(登録商標)ネットワーク、およびインターネットを含む、任意のタイプのネットワークであり得る。ネットワークインターフェースデバイス1218は、任意のタイプの所望の通信プロトコルをサポートするように構成され得る。メモリシステム1212は、1つまたは複数のメモリユニット1224(0~N)を含むことができる。20

#### 【0054】

CPU1202はまた、1つまたは複数のディスプレイ1226に送信される情報を制御するために、システムバス1208を介してディスプレイコントローラ1220にアクセスするように構成され得る。ディスプレイコントローラ1220は、1つまたは複数のビデオプロセッサ1228を介して表示されるべき情報をディスプレイ1226に送信し、ビデオプロセッサ1228は、表示されるべき情報をディスプレイ1226に適したフォーマットになるように処理する。ディスプレイ1226は、限定はしないが、陰極線管(CRT)、液晶ディスプレイ(LCD)、プラズマディスプレイなどを含む、任意のタイプのディスプレイを含むことができる。30

#### 【0055】

当業者は、本明細書で開示する態様に関して説明する様々な例示的な論理ブロック、モジュール、回路、およびアルゴリズムが、電子ハードウェア、メモリもしくは別のコンピュータ可読媒体に記憶され、プロセッサもしくは他の処理デバイスによって実行される命令、またはその両方の組合せとして実装され得ることをさらに諒解されよう。本明細書で説明するマスタデバイスおよびスレーブデバイスは、例として、任意の回路、ハードウェア構成要素、集積回路(IC)、またはICチップにおいて用いられ得る。本明細書で開示するメモリは、任意のタイプおよびサイズのメモリであってもよく、任意のタイプの所望の情報を記憶するように構成され得る。この互換性を明確に示すために、様々な例示的な構成要素、ブロック、モジュール、回路、およびステップについて、上記では概してそれらの機能に関して説明した。そのような機能がどのように実装されるかは、特定の適用例、設4050

計選択、および/またはシステム全体に課される設計制約によって決まる。当業者は、説明した機能を特定の適用例ごとに様々な方法で実装し得るが、そのような実装決定は、本開示の範囲からの逸脱を引き起こすものと解釈されるべきではない。

#### 【0056】

本明細書で開示する態様に関して説明する様々な例示的な論理ブロック、モジュール、および回路は、プロセッサ、デジタル信号プロセッサ(DSP)、特定用途向け集積回路(ASIC)、フィールドプログラマブルゲートアレイ(FPGA)もしくは他のプログラマブル論理デバイス、個別ゲートもしくはトランジスタ論理、個別ハードウェア構成要素、または本明細書で説明する機能を実行するように設計されたそれらの任意の組合せを用いて実装または実行され得る。プロセッサは、マイクロプロセッサであってもよいが、代替として、プロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、または状態機械であってもよい。プロセッサはまた、コンピューティングデバイスの組合せ(たとえば、DSPとマイクロプロセッサの組合せ、複数のマイクロプロセッサ、DSPコアと連携した1つもしくは複数のマイクロプロセッサ、または任意の他のそのような構成)として実装され得る。10

#### 【0057】

本明細書で開示する態様は、ハードウェアにおいて、また、ハードウェアに記憶された命令において具現化される場合があり、たとえば、ランダムアクセスメモリ(RAM)、フラッシュメモリ、読み取り専用メモリ(ROM)、電気的プログラマブルROM(EPROM)、電気的消去可能プログラマブルROM(EEPROM)、レジスタ、ハードディスク、リムーバブルディスク、CD-ROM、または当技術分野で知られている任意の他の形態のコンピュータ可読媒体内に存在する場合がある。例示的な記憶媒体は、プロセッサが記憶媒体から情報を読み取り、記憶媒体に情報を書き込むことができるよう、プロセッサに結合される。代替として、記憶媒体は、プロセッサと一緒にてもよい。プロセッサおよび記憶媒体は、ASIC内に存在する場合がある。ASICは、リモート局内に存在する場合がある。代替として、プロセッサおよび記憶媒体は、個別構成要素としてリモート局、基地局、またはサーバ内に存在する場合がある。20

#### 【0058】

本明細書の例示的な態様のいずれかにおいて説明した動作ステップは、例および説明を提供するために記載されていることにも留意されたい。説明した動作は、図示したシーケンス以外の多数の異なるシーケンスで実行されてもよい。さらに、単一の動作ステップにおいて説明した動作は、実際にはいくつかの異なるステップにおいて実行される場合がある。加えて、例示的な態様において説明した1つまたは複数の動作ステップが組み合わされる場合がある。当業者には容易に明らかになるように、フローチャート図に示す動作ステップは多数の異なる修正を受ける場合があることを理解されたい。当業者は、情報および信号が様々な異なる技術および技法のいずれかを使用して表され得ることも理解されよう。たとえば、上記の説明全体にわたって参照される場合があるデータ、命令、コマンド、情報、信号、ビット、シンボル、およびチップは、電圧、電流、電磁波、磁場もしくは磁性粒子、光場もしくは光学粒子、またはそれらの任意の組合せによって表され得る。30

#### 【0059】

本開示の前述の説明は、いかなる当業者も本開示を作製または使用できるようにするために提供される。本開示に対する様々な修正は、当業者に容易に明らかになり、本明細書で定義する一般原理は、本開示の趣旨または範囲から逸脱することなく他の変形形態に適用され得る。したがって、本開示は、本明細書で説明する例および設計に限定されるものではなく、本明細書で開示する原理および新規の特徴と一致する最も広い範囲を与えられるべきである。40

#### 【符号の説明】

#### 【0060】

100 SoC、ブロックベースのコンピュータプロセッサ

102 プロセッサベースシステム

50

|                     |                               |    |

|---------------------|-------------------------------|----|

| 104、104(1) ~ 104(N) | プロセッサブロック                     |    |

| 106(1)、106(2)       | プロセッサ                         |    |

| 108(1) ~ 108(N)     | 共有レベル2(L2)キャッシュ               |    |

| 110                 | 共有レベル3(L3)キャッシュ、共有L3キャッシュ     |    |

| 112                 | 内部システムバス                      |    |

| 114                 | メモリコントローラ                     |    |

| 116                 | 周辺機器                          |    |

| 118                 | ストレージ                         |    |

| 120                 | エクスプレス周辺構成要素相互接続(PCI)インターフェース |    |

| 122                 | ダイレクトメモリアクセス(DMA)コントローラ       | 10 |

| 124                 | 統合メモリコントローラ(IMC)              |    |

| 200                 | プロセッサベースシステム                  |    |

| 202                 | メモリシステム                       |    |

| 204                 | メモリアクセスデバイス                   |    |

| 206                 | 圧縮/圧縮解除エンジン                   |    |

| 208                 | メモリ                           |    |

| 210                 | プロセッサ                         |    |

| 212                 | プロセッサメモリアクセス経路                |    |

| 213                 | 制御ポート                         |    |

| 214                 | 制御バス                          | 20 |

| 216                 | アドレスバス                        |    |

| 218                 | データバス                         |    |

| 219                 | メモリアクセスポート                    |    |

| 220                 | 高優先度復号エンジン                    |    |

| 222                 | 低優先度復号エンジン                    |    |

| 224                 | メモリユニット                       |    |

| 226                 | 低レベルキャッシュ                     |    |

| 228                 | 圧縮/圧縮解除エンジンメモリアクセス経路          |    |

| 230                 | ヒット/ミスライン                     |    |

| 300                 | プロセス                          | 30 |

| 400                 | メモリ構成                         |    |

| 402                 | 圧縮高優先度メモリライン、CHPML            |    |

| 402(0) ~ 402(X-1)   | 圧縮高優先度メモリライン                  |    |

| 404                 | 圧縮低優先度メモリライン、CLPML            |    |

| 404(0) ~ 404(Y-1)   | 圧縮低優先度メモリライン                  |    |

| 500                 | メモリ構成                         |    |

| 502                 | メタデータ、高優先度メタデータ               |    |

| 504                 | メタデータ、低優先度メタデータ               |    |

| 506                 | メタデータ                         |    |

| 508                 | 高優先度データ                       | 40 |

| 508-A               | 高優先度データ                       |    |

| 508-B               | 高優先度例外データ                     |    |

| 510                 | 低優先度データ                       |    |

| 510-A               | 低優先度データ                       |    |

| 510-B               | 低優先度例外データ                     |    |

| 512                 | 高優先度データ                       |    |

| 514                 | 未使用セクション                      |    |

| 600                 | メモリ構成                         |    |

| 602                 | メモリ構成                         |    |

| 604                 | 例外フラグ                         | 50 |

|                    |                       |    |

|--------------------|-----------------------|----|

| 606                | 例外インデックス              |    |

| 608                | 例外領域                  |    |

| 700                | メモリ構成                 |    |

| 702                | メモリ構成                 |    |

| 704                | 例外フラグ                 |    |

| 706                | 長さ                    |    |

| 708                | 長さ                    |    |

| 710                | 例外ポインタ                |    |

| 800                | プロセス                  | 10 |

| 900                | プロセス                  |    |

| 1000               | プロセス                  |    |

| 1100               | プロセス                  |    |

| 1200               | プロセッサベースシステム          |    |

| 1202               | 中央処理装置(CPU)           |    |

| 1204               | プロセッサ                 |    |

| 1206               | キャッシュメモリ              |    |

| 1208               | システムバス                |    |

| 1210               | メモリコントローラ             |    |

| 1212               | メモリシステム               |    |

| 1214               | 入力デバイス                | 20 |

| 1216               | 出力デバイス                |    |

| 1218               | ネットワークインターフェースデバイス    |    |

| 1220               | ディスプレイコントローラ          |    |

| 1222               | ネットワーク                |    |

| 1224(0~N)          | メモリユニット               |    |

| 1226               | ディスプレイ                |    |

| 1228               | ビデオプロセッサ              |    |

| M                  | 物理メモリロケーション           |    |

| M(0) ~ M(X-1)      | メモリロケーション、物理メモリロケーション |    |

| M(PTR)             | 物理メモリロケーション、例外ポインタ    |    |

| ML、ML(0) ~ ML(X-1) | メモリライン                | 30 |

| N                  | 長さ                    |    |

| P                  | 長さ                    |    |

| Q                  | 長さ                    |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7A】

【図7B】

【図8】

【図9】

【図10】

【図11】

【図 1 2】

---

フロントページの続き

(72)発明者 アミン・アンサリ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 リチャード・シニア

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 ニエヤン・ゲン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 アナンド・ジャナキラマン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 グルヴィンダル・シン・チャプラ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

審査官 後藤 彰

(56)参考文献 米国特許出願公開第2001/0054131(US,A1)

(58)調査した分野(Int.Cl., DB名)

G 06 F 12 / 04