# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) 국제특허분류(Int. Cl.)

**G11C 16/10** (2006.01) **G11C 16/08** (2006.01)

(21) 출원번호

10-2009-0017706

(22) 출원일자

2009년03월02일

심사청구일자

2014년01월27일 10-2010-0098968

(65) 공개번호

(43) 공개일자

2010년09월10일

(56) 선행기술조사문헌

US20050160242 A1

US20100064092 A1

KR1020060090088 A

KR1020070091452 A

(45) 공고일자 2015년11월04일

(11) 등록번호 10-1565974

(24) 등록일자 2015년10월29일

(73) 특허권자

### 삼성전자주식회사

경기도 수원시 영통구 삼성로 129 (매탄동)

(72) 발명자

### 최상훈

서울특별시 동작구 동작대로33길 13-15 (사당동)

경기도 수원시 장안구 조원로 16, 103동 603호 ( 조원동, 벽산아파트)

(74) 대리인

특허법인 고려

전체 청구항 수 : 총 10 항

심사관 : 한선경

### (54) 발명의 명칭 불휘발성 메모리 장치, 그것의 프로그램 방법, 그리고 그것을 포함하는 메모리 시스템

### (57) 요 약

본 발명의 실시 예에 따른 불휘발성 메모리 장치의 프로그램 방법은 프로그램 데이터를 제 1 어드레스 영역에 저 장하고, 그리고 프로그램 데이터가 사용자 데이터가 아닌 신뢰 데이터이면, 프로그램 데이터를 제 2 어드레스 영 역에 추가적으로 저장하는 것을 포함한다.

### 대 표 도 - 도5

# 명세서

# 청구범위

#### 청구항 1

불휘발성 메모리 장치의 프로그램 방법에 있어서:

프로그램 데이터를 제 1 어드레스 영역에 저장하고;

상기 제 1 어드레스 영역이 최상위 어드레스 영역인지 그리고 상기 프로그램 데이터가 신뢰 데이터인지 판별하고; 그리고

상기 제 1 어드레스 영역이 상기 최상위 어드레스 영역(Most Significant Address Area)이 아니고, 그리고 상기 프로그램 데이터가 사용자 데이터가 아닌 상기 신뢰 데이터이면, 상기 프로그램 데이터를 제 2 어드레스 영역에 추가적으로 저장하는 것을 포함하는 프로그램 방법.

### 청구항 2

제 1 항에 있어서,

상기 제 1 어드레스 영역이 상기 최상위 어드레스 영역(Most Significant Address Area)이면, 상기 프로그램 데이터를 상기 제 2 어드레스 영역에 저장하지 않고 프로그램을 종료하는 것을 더 포함하는 프로그램 방법.

### 청구항 3

제 1 항에 있어서,

상기 제 1 어드레스 영역은 중간 비트 어드레스 영역(Central Significant Address Area)인 프로그램 방법.

### 청구항 4

제 1 항에 있어서,

상기 프로그램 데이터를 상기 제 2 어드레스 영역에 추가적으로 저장하는 것은

상기 제 1 어드레스 영역에 저장된 데이터를 읽고; 그리고

상기 읽어진 데이터를 상기 제 2 어드레스 영역에 저장하는 것을 포함하는 프로그램 방법.

# 청구항 5

제 1 항에 있어서,

상기 프로그램 데이터를 상기 제 2 어드레스 영역에 추가적으로 저장하는 것은

상기 제 1 어드레스를 카운트 업 또는 카운트 다운 하여 상기 제 2 어드레스 영역을 액세스하는 것을 포함하는 프로그램 방법.

### 청구항 6

제 1 항에 있어서,

상기 신뢰 데이터는 메타 데이터를 포함하는 프로그램 방법.

### 청구항 7

메모리 셀 어레이;

상기 메모리 셀 어레이에 데이터를 기입 및 독출하도록 구성되는 읽기/쓰기 회로; 그리고

상기 읽기/쓰기 회로를 제어하도록 구성되는 제어 로직을 포함하고,

상기 제어 로직은

프로그램 데이터를 상기 메모리 셀 어레이의 제 1 어드레스 영역에 저장하도록 상기 읽기/쓰기 회로를 제어하고:

상기 제 1 어드레스 영역이 최상위 어드레스 영역인지 그리고 상기 프로그램 데이터가 신뢰 데이터인지 판별하고; 그리고

상기 제 1 어드레스 영역이 상기 최상위 어드레스 영역이 아니고, 그리고 상기 프로그램 데이터가 사용자 데이터가 아닌 상기 신뢰 데이터이면, 상기 프로그램 데이터를 상기 메모리 셀 어레이의 제 2 어드레스 영역에 추가적으로 저장하도록 상기 읽기/쓰기 회로를 제어하는 불휘발성 메모리 장치.

### 청구항 8

불휘발성 메모리 장치; 그리고

상기 불휘발성 메모리 장치를 제어하도록 구성되는 컨트롤러를 포함하고,

상기 컨트롤러는

제 1 어드레스 영역의 어드레스 및 프로그램 데이터의 신뢰성 정보에 따라, 상기 프로그램 데이터를 상기 제 1 어드레스 영역, 또는 상기 제 1 어드레스 영역 및 제 2 어드레스 영역에 프로그램하도록 상기 불휘발성 메모리를 제어하고; 그리고

상기 프로그램 데이터의 상기 신뢰성 정보가 신뢰 데이터를 가리키고, 그리고 상기 제 1 어드레스 영역의 어드레스가 최상위 비트(Most Significant Bit)가 아닌 다른 비트를 가리킬 때, 상기 프로그램 데이터를 상기 제 1 어드레스 영역 및 상기 제 2 어드레스 영역에 프로그램하도록 상기 불휘발성 메모리를 제어하는 메모리 시스템.

#### 청구항 9

제 8 항에 있어서,

상기 불휘발성 메모리 장치 및 상기 컨트롤러는 반도체 디스크/드라이브(SSD, Solid State Disk/Drive)를 형성하는 메모리 시스템.

### 청구항 10

제 8 항에 있어서.

상기 불휘발성 메모리 장치 및 상기 컨트롤러는 메모리 카드를 형성하는 메모리 시스템.

### 발명의 설명

[0001]

[0002]

[0003]

### 발명의 상세한 설명

### 기술분야

본 발명은 반도체 메모리 장치에 관한 것으로, 더 상세하게는 불휘발성 메모리 장치, 그것의 프로그램 방법, 그리고 그것을 포함하는 메모리 시스템에 관한 것이다.

#### 배경기술

반도체 메모리 장치(semiconductor memory device)는 데이터를 저장해 두고 필요할 때 꺼내어 읽어볼 수 있는 기억장치이다. 반도체 메모리 장치는 크게 휘발성 메모리 장치(Volatile memory device)와 불휘발성 메모리 장치(Nonvolatile memory device)로 구분된다.

휘발성 메모리 장치는 전원 공급이 차단되면 저장하고 있던 데이터가 소멸되는 메모리 장치이다. 휘발성 메모리 장치에는 SRAM, DRAM, SDRAM 등이 있다. 불휘발성 메모리 장치는 전원 공급이 차단되어도 저장하고 있던 데이터가 소멸하지 않는 메모리 장치이다. 불휘발성 메모리 장치에는 ROM, PROM, EPROM, EPROM, 플래시 메모리 장치, PRAM, MRAM, RRAM, FRAM 등이 있다. 플래시 메모리 장치는 크게 노어 타입과 낸드 타입으로 구분된다.

# 발명의 내용

# 해결 하고자하는 과제

[0004] 본 발명의 목적은 최상위 어드레스 영역(Most Significant Address Area)의 프로그램 시에 최상위 어드레스 영역보다 하위 어드레스 영역의 데이터가 소실되는 것을 방지하는 불휘발성 메모리 장치, 그것의 프로그램 방법, 그리고 그것을 포함하는 메모리 시스템을 제공하는 데에 있다.

### 과제 해결수단

- [0005] 본 발명의 실시 예에 따른 불휘발성 메모리 장치의 프로그램 방법은 프로그램 데이터를 제 1 어드레스 영역에 저장하고; 그리고 상기 프로그램 데이터가 사용자 데이터가 아닌 신뢰 데이터이면, 상기 프로그램 데이터를 제 2 어드레스 영역에 추가적으로 저장하는 것을 포함한다.

- [0006] 실시 예로서, 상기 제 1 어드레스 영역이 최상위 어드레스 영역(Most Significant Address Area)이면, 상기 프로그램 데이터를 상기 제 1 어드레스 영역에 저장한다.

- [0007] 실시 에로서, 상기 제 1 어드레스 영역이 최상위 어드레스 영역보다 하위의 어드레스 영역이면, 상기 프로그램 데이터를 상기 제 1 및 제 2 어드레스 영역에 저장한다.

- [0008] 실시 예로서, 상기 프로그램 데이터를 상기 제 2 어드레스 영역에 추가적으로 저장하는 것은 상기 제 1 어드레스 영역에 저장된 데이터를 읽고; 그리고 상기 읽어진 데이터를 상기 제 2 어드레스 영역에 저장하는 것을 포함한다.

- [0009] 실시 예로서, 상기 프로그램 데이터를 상기 제 2 어드레스 영역에 추가적으로 저장하는 것은 상기 제 1 어드레스를 카운트 업 하여 상기 제 2 어드레스 영역을 액세스하는 것을 포함한다.

- [0010] 실시 예로서, 상기 신뢰 데이터는 메타 데이터를 포함한다.

- [0011] 본 발명의 실시 예에 따른 불휘발성 메모리 장치는 메모리 셀 어레이; 상기 메모리 셀 어레이에 데이터를 기입 및 독출하도록 구성되는 읽기/쓰기 회로; 그리고 상기 읽기/쓰기 회로를 제어하도록 구성되는 제어 로직을 포함하고, 상기 제어 로직은 프로그램 데이터가 상기 메모리 셀 어레이의 제 1 어드레스 영역에 저장되고; 상기 프로그램 데이터가 사용자 데이터가 아닌 신뢰 데이터이면, 상기 프로그램 데이터가 상기 메모리 셀 어레이의 제 2 어드레스 영역에 추가적으로 저장되도록 상기 읽기/쓰기 회로를 제어한다.

- 본 발명의 실시 예에 따른 메모리 시스템은 불휘발성 메모리 장치; 그리고 상기 불휘발성 메모리 장치를 제어하도록 구성되는 컨트롤러를 포함하고, 상기 컨트롤러는 프로그램 데이터를 상기 불휘발성 메모리 장치의 제 1 어드레스 영역에 저장되고; 상기 프로그램 데이터가 사용자 데이터가 아닌 신뢰 데이터이면, 상기 프로그램 데이터가 상기 불휘발성 메모리 장치의 제 2 어드레스 영역에 추가적으로 저장되도록 제어한다.

- [0013] 실시 예로서, 상기 불휘발성 메모리 장치 및 상기 컨트롤러는 반도체 디스크/드라이브(SSD, Solid State Disk/Drive)를 형성한다.

- [0014] 실시 예로서, 상기 불휘발성 메모리 장치 및 상기 컨트롤러는 메모리 카드를 형성한다.

#### 直 과

[0012]

[0015]

본 발명의 실시 예에 따른 불휘발성 메모리 장치는, 프로그램 데이터가 신뢰 데이터이고, 프로그램 데이터가 저장될 제 1 어드레스 영역이 최상위 어드레스 영역(Most Significant Address Area) 보다 하위의 어드레스 영역이면, 프로그램 데이터를 제 2 어드레스 영역에 추가적으로 저장한다. 따라서, 최상위 어드레스 영역의 프로그램 시에, 신뢰 데이터가 소실되는 것이 방지된다.

# 발명의 실시를 위한 구체적인 내용

- [0016] 본 발명의 실시 예에 따른 불휘발성 메모리 장치의 프로그램 방법은 프로그램 데이터를 제 1 어드레스 영역에 저장하고, 그리고 프로그램 데이터가 사용자 데이터가 아닌 신뢰 데이터이면, 프로그램 데이터를 제 2 어드레스 영역에 추가적으로 저장하는 것을 포함한다.

- [0017] 본 발명의 실시 예에 따른 불휘발성 메모리 장치는 메모리 셀 어레이, 메모리 셀 어레이에 데이터를 기입 및 독출하도록 구성되는 읽기/쓰기 회로, 그리고 읽기/쓰기 회로를 제어하도록 구성되는 제어 로직을 포함하고, 제어로직은 프로그램 데이터가 메모리 셀 어레이의 제 1 어드레스 영역에 저장되고, 프로그램 데이터가 사용자 데이

터가 아닌 신뢰 데이터이면, 프로그램 데이터가 메모리 셀 어레이의 제 2 어드레스 영역에 추가적으로 저장되도록 읽기/쓰기 회로를 제어한다.

- [0018] 본 발명의 실시 예에 따른 메모리 시스템은 불휘발성 메모리 장치, 그리고 불휘발성 메모리 장치를 제어하도록 구성되는 컨트롤러를 포함하고, 컨트롤러는 프로그램 데이터가 불휘발성 메모리 장치의 제 1 어드레스 영역에 저장되고, 프로그램 데이터가 사용자 데이터가 아닌 신뢰 데이터이면, 프로그램 데이터가 불휘발성 메모리 장치의 제 2 어드레스 영역에 추가적으로 저장되도록 제어한다.

- [0019] 이하에서, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자가 본 발명의 기술적 사상을 용이하게 실시할 수 있을 정도로 상세히 설명하기 위하여, 본 발명의 실시 예를 첨부된 도면을 참조하여 설명하기로 한다.

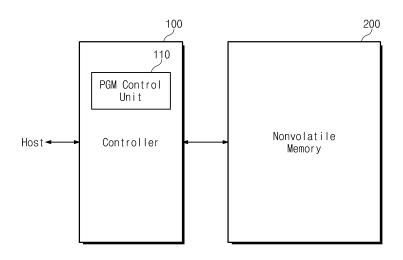

- [0020] 도 1은 본 발명의 실시 예에 따른 메모리 시스템(10)을 보여주는 블록도이다. 도 1을 참조하면, 본 발명의 실시 예에 따른 메모리 시스템(10)은 불휘발성 메모리 장치(200) 및 컨트롤러(100)를 포함한다.

- [0021] 컨트롤러(100)는 호스트(Host) 및 불휘발성 메모리 장치(200)에 연결된다. 컨트롤러(100)는 불휘발성 메모리 장치(200)로부터 읽은 데이터를 호스트(Host)에 전달하고, 호스트(Host)로부터 전달되는 데이터를 불휘발성 메모리 장치(200)에 저장한다.

- [0022] 컨트롤러(100)는 램, 프로세싱 유닛, 호스트 인터페이스, 그리고 메모리 인터페이스와 같은 잘 알려진 구성 요소들을 포함할 것이다. 램은 프로세싱 유닛의 동작 메모리로서 이용될 것이다. 프로세싱 유닛은 컨트롤러(100)의 제반 동작을 제어할 것이다.

- [0023] 호스트 인터페이스는 호스트(Host) 및 컨트롤러(100) 사이의 데이터 교환을 수행하기 위한 프로토콜을 포함할 것이다. 예시적으로, 컨트롤러(100)는 USB, MMC, PCI-E, ATA(Advanced Technology Attachment), Serial-ATA, Parallel-ATA, SCSI, ESDI, 그리고 IDE(Integrated Drive Electronics) 등과 같은 다양한 인터페이스 프로토콜 들 중 하나를 통해 외부(호스트)와 통신하도록 구성될 것이다.

- [0024] 메모리 인터페이스는 불휘발성 메모리 장치(200)와 인터페이싱할 것이다. 컨트롤러(100)는 오류 정정 블록을 추가적으로 포함할 수 있다. 오류 정정 블록은 불휘발성 메모리 장치(200)로부터 읽어진 데이터의 오류를 검출하고, 정정할 것이다.

- [0025] 불휘발성 메모리 장치(200)는 데이터를 저장하기 위한 메모리 셀 어레이, 메모리 셀 어레이에 데이터를 기입 및 독출하기 위한 읽기/쓰기 회로, 외부로부터 전달되는 어드레스를 디코딩하여 읽기/쓰기 회로에 전달하는 어드레스 디코더, 불휘발성 메모리 장치(200)의 제반 동작을 제어하기 위한 제어 로직 등을 포함할 것이다. 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200)는 도 2를 참조하여 더 상세하게 설명된다.

- [0026] 컨트롤러(100) 및 불휘발성 메모리 장치(200)는 하나의 반도체 장치로 집적될 수 있다. 예시적으로, 컨트롤러 (100) 및 불휘발성 메모리 장치(200)는 하나의 반도체 장치로 집적되어, 메모리 카드를 구성할 것이다. 예를 들면, 컨트롤러(100) 및 불휘발성 메모리 장치(200)는 하나의 반도체 장치로 집적되어 PC 카드(PCMCIA), 컴팩트 플래시 카드(CF), 스마트 미디어 카드(SM/SMC), 메모리 스틱, 멀티미디어 카드(MMC, RS-MMC, MMCmicro), SD 카드(SD, miniSD, microSD), 유니버설 플래시 기억장치(UFS) 등을 구성할 것이다.

- [0027] 다른 예로서, 컨트롤러(100) 및 불휘발성 메모리 장치(200)는 하나의 반도체 장치로 집적되어 반도체 디스크/드라이브(SSD, Solid State Disk/Drive)를 구성할 것이다. 메모리 시스템(10)이 반도체 디스크(SSD)로 이용되는 경우, 메모리 시스템(10)에 연결된 호스트(Host)의 동작 속도는 획기적으로 개선될 것이다.

- [0028] 다른 예로서, 메모리 시스템(10)은 컴퓨터, 휴대용 컴퓨터, UMPC, 워크스테이션, 넷북(net-book), PDA, 포터블 (portable) 컴퓨터, 웹 타블렛(web tablet), 무선 전화기(wireless phone), 모바일 폰(mobile phone), 스마트 폰(smart phone), 디지털 카메라(digital camera), 디지털 음성 녹음기/재생기(digital audio recorder/player), 디지털 정지/동 영상 녹화기/재생기(digital picture/video recorder/player), 정보를 무선 환경에서 송수신할 수 있는 장치, 홈 네트워크를 구성하는 다양한 전자 장치들 중 하나, 컴퓨터 네트워크를 구성하는 다양한 전자 장치들 중 하나, 또는 반도 체 드라이브(SSD, Solid State Drive) 또는 메모리 카드와 같은 컴퓨팅 시스템을 구성하는 다양한 구성 요소들 중 하나에 적용될 것이다.

- [0029] 다른 예로서, 불휘발성 메모리 장치(200) 또는 메모리 시스템(10)은 다양한 형태들의 패키지로 실장 될 수 있다. 예를 들면, 불휘발성 메모리 장치(200) 또는 메모리 시스템(10)은 PoP(Package on Package), Ball grid arrays(BGAs), Chip scale packages(CSPs), Plastic Leaded Chip Carrier(PLCC), Plastic Dual In-Line

Package(PDIP), Die in Waffle Pack, Die in Wafer Form, Chip On Board(COB), Ceramic Dual In-Line Package(CERDIP), Plastic Metric Quad Flat Pack(MQFP), Thin Quad Flatpack(TQFP), Small Outline(SOIC), Shrink Small Outline Package(SSOP), Thin Small Outline(TSOP), Thin Quad Flatpack(TQFP), System In Package(SIP), Multi Chip Package(MCP), Wafer-level Fabricated Package(WFP), Wafer-Level Processed Stack Package(WSP) 등과 같은 방식으로 패키지화되어 실장될 것이다.

- [0030]

- 본 발명의 실시 예에 따른 컨트롤러(100)는 프로그램 제어부(110)를 포함한다. 프로그램 제어부(110)는 불휘발성 메모리 장치(200)의 프로그램 동작을 제어하도록 구성된다. 예시적으로, 프로그램 제어부(110)는, 프로그램 데이터가 불휘발성 메모리 장치(200)제 1 어드레스 영역에 저장되고, 프로그램 데이터가 사용자 데이터가 아닌 신뢰 데이터이면, 프로그램 데이터가 불휘발성 메모리 장치(200)의 제 2 어드레스 영역에 추가적으로 저장되도록 제어할 것이다.

- [0031]

- 예시적으로, 신뢰 데이터는 불휘발성 메모리 장치(200) 또는 불휘발성 메모리 장치(200) 및 컨트롤러(100)를 포함하는 메모리 시스템(10)이 정상적으로 동작하기 위해 요구되는 데이터를 나타낼 것이다. 예를 들면, 신뢰 데이터는 불휘발성 메모리 장치(200)에 저장되는 데이터를 액세스하기 위해 요구되는 메타 데이터일 것이다. 예를 들면, 신뢰 데이터는 불휘발성 메모리 장치(200)를 구동하기 위해 요구되는 코드 데이터일 것이다.

- [0032]

- 예시적으로, 신뢰 데이터는 사용자에 의해 설정되는 데이터일 것이다. 예를 들면, 신뢰 데이터는 사용자에 의해 설정된 보안 데이터일 것이다. 신뢰 데이터의 종류는 한정되지 않는다. 신뢰 데이터는 불휘발성 메모리 장치 (200)에 저장되는 사용자 데이터와 비교하여 상대적으로 중요도가 높은 데이터를 나타낼 것이다.

- [0033]

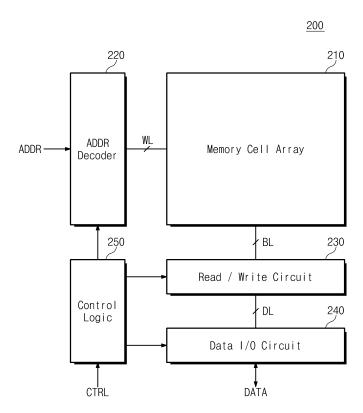

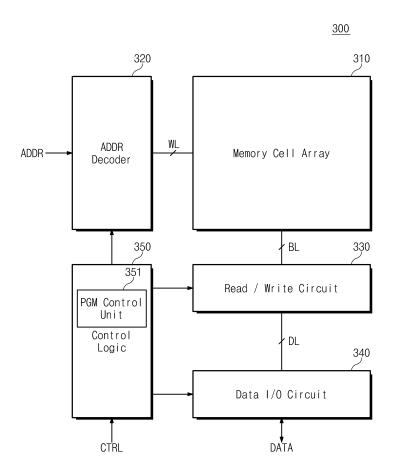

- 도 2는 도 1의 불휘발성 메모리 장치(200)를 보여주는 블록도이다. 도 2를 참조하면, 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200)는 메모리 셀 어레이(210), 어드레스 디코더(220), 읽기/쓰기 회로(230), 데이터 입 출력 회로(240), 그리고 제어 로직(250)을 포함한다.

- [0034]

- 메모리 셀 어레이(210)는 워드 라인(WL)을 통해 어드레스 디코더(220)에 연결되고, 비트 라인(BL)을 통해 읽기/쓰기 회로(230)에 연결된다. 메모리 셀 어레이(210)는 복수의 메모리 셀들을 포함한다. 메모리 셀들은 워드 라인(WL)을 통해 어드레스 디코더(220)에 연결된다. 메모리 셀들은 비트 라인(BL)을 통해 읽기/쓰기 회로(230)에 연결된다. 선택된 워드 라인 및 선택된 비트 라인에 연결된 메모리 셀에서 읽기 및 쓰기 동작이 수행될 것이다.

- [0035]

- 어드레스 디코더(220)는 워드 라인들(WL)을 통해 메모리 셀 어레이에 연결된다. 어드레스 디코더(220)는 제어로직(250)의 제어에 응답하여 동작한다. 어드레스 디코더(220)는 외부로부터 어드레스(ADDR)를 제공받는다. 예시적으로, 어드레스(ADDR)는 도 1의 컨트롤러(100)로부터 제공될 것이다. 어드레스 디코더(220)는 어드레스(ADDR) 중 행 어드레스를 디코딩하여 워드 라인들(WL)을 선택할 것이다. 어드레스 디코더(220)는 어드레스(ADDR) 중 열 어드레스를 디코딩하여 읽기/쓰기 회로에 전달할 것이다. 예시적으로, 어드레스 디코더(220)는 행디코더, 열 디코더, 어드레스 버퍼 등과 같은 잘 알려진 구성 요소를 포함할 것이다.

- [0036]

- 읽기/쓰기 회로(230)는 비트 라인들(BL)을 통해 메모리 셀 어레이(210)에 연결되고, 데이터 라인들(DL)을 통해 데이터 입출력 회로(240)에 연결된다. 읽기/쓰기 회로(230)는 제어 로직(250)의 제어에 응답하여 동작한다. 읽기/쓰기 회로(230)는 어드레스 디코더(220)로부터 제공되는 디코딩된 열 어드레스에 응답하여 비트 라인들(BL)을 선택한다.

- [0037]

- 읽기/쓰기 회로(230)는 데이터 입출력 회로(240)로부터 데이터 라인들(DL)을 통해 전달되는 데이터를 선택된 메모리 셀들에 저장할 것이다. 읽기/쓰기 회로(230)는 선택된 메모리 셀들로부터 읽어진 데이터를 데이터 라인들 (DL)을 통해 데이터 입출력 회로(240)에 전달할 것이다. 읽기/쓰기 회로(230)는 메모리 셀 어레이(210) 제 1 메모리 셀들로부터 읽어진 데이터를 메모리 셀 어레이(210)의 제 2 메모리 셀들에 기입할 것이다. 예를 들면, 읽기/쓰기 회로(230)는 카피백(copy-back) 동작을 수행할 것이다.

- [0038]

- 예시적으로, 읽기/쓰기 회로(230)는 페이지 버퍼, 열 선택 회로 등과 같이 잘 알려진 구성 요소들을 포함할 것이다. 다른 예로서, 읽기/쓰기 회로(230)는 쓰기 드라이버, 감지 증폭기, 열 선택 회로 등과 같이 잘 알려진 구성 요소들을 포함할 것이다.

- [0039]

- 데이터 입출력 회로(240)는 데이터 라인들(DL)을 통해 읽기/쓰기 회로(230)에 연결된다. 데이터 입출력 회로 (240)는 제어 로직(250)의 제어에 응답하여 동작한다. 데이터 입출력 회로(240)는 외부와 데이터(DATA)를 교환한다. 예시적으로, 데이터 입출력 회로(240)는 도 1의 컨트롤러(100)와 데이터를 교환할 것이다. 데이터 입출력 회로(240)는 외부로부터 전달되는 데이터(DATA)를 데이터 라인들(DL)을 통해 읽기/쓰기 회로에 전달할 것이다. 데이터 입출력 회로(240)는 읽기/쓰기 회로(230)로부터 전달되는 데이터(DATA)를 외부와 교환할 것이다. 예시적

으로, 데이터 입출력 회로(240)는 데이터 버퍼 등과 같이 잘 알려진 구성 요소를 포함할 것이다.

[0040] 제어 로직(250)은 어드레스 디코더(220), 읽기/쓰기 회로(230), 그리고 테이터 입출력 회로(240)를 제어한다. 제어 로직(250)은 불휘발성 메모리 장치(200)의 제반 동작을 제어한다. 제어 로직(250)은 외부로부터 제공되는 제어 신호(CTRL)에 응답하여 동작한다. 예시적으로, 제어 신호(CTRL)는 도 1의 컨트롤러(100)로부터 제공될 것이다.

메모리 셀 어레이(210)의 미리 설정된 수의 메모리 셀들은 어드레스 영역(Address Area)을 형성할 것이다. 예시적으로, 하나의 열 어드레스에 의해 액세스되는 메모리 셀들은 하나의 열 어드레스 영역을 형성할 것이다. 다른 예로서, 하나의 행 어드레스에 의해 액세스되는 메모리 셀들은 하나의 행 어드레스 영역을 형성할 것이다. 예시적으로, 어드레스 영역은 불휘발성 메모리 장치(200)에서 읽기 및 쓰기 동작이 수행되는 단위일 것이다.

명확한 설명을 위하여, 플래시 메모리 장치의 예를 참조하여, 본 발명의 실시 예가 설명된다. 즉, 불휘발성 메모리 장치(200)의 읽기 및 쓰기 동작의 단위는 워드 라인인 것으로 가정한다. 그러나, 본 발명의 기술적 사상은 플래시 메모리에 적용되는 것으로 한정되지 않는다. 본 발명의 기술적 사상은 셀 당 복수의 비트를 저장하는 멀티 레벨 메모리 셀들을 포함하는 불휘발성 메모리 장치에 적용될 것이다.

메모리 셀 어레이(210)의 메모리 셀들이 셀 당 하나의 비트를 저장하면, 하나의 워드 라인에 연결된 메모리 셀들은 하나의 어드레스 영역을 형성할 것이다. 메모리 셀 어레이(210)의 메모리 셀들이 셀 당 두 개의 비트를 저장하면, 하나의 워드 라인에 연결된 메모리 셀들은 두 개의 어드레스 영역을 형성할 것이다. 예를 들면, 하나의 워드 라인에 연결된 메모리 셀들은 최상위 비트들(MSB, Most Significant Bits)에 의해 형성되는 최상위 어드레스 영역(Most Significant Address Area) 및 최하위 비트들(LSB, Least Significant Bits)에 의해 형성되는 최하위 어드레스 영역(Least Significant Address Area)을 형성할 것이다.

메모리 셀 어레이(210)의 메모리 셀이 셀 당 n 비트를 저장하면, 하나의 워드 라인에 연결된 메모리 셀들은 n 개의 어드레스 영역을 형성할 것이다. 예를 들면, 하나의 워드 라인에 연결된 메모리 셀들은 최상위 비트들 (MSB, Most Significant Bits)에 의해 형성되는 최상위 어드레스 영역(Most Significant Address Area), 최하 위 비트들(LSB, Least Significant Bits)에 의해 형성되는 최하위 어드레스 영역(Least Significant Address Area), 그리고 최상위 비트(MSB) 및 최하위 비트(LSB) 사이의 중간 비트들(CSB, Central Significant Bits)에 의해 형성되는 n-2 개의 중간 어드레스 영역들(Central Significant Address Area)을 형성할 것이다.

명확한 설명을 위하여, 메모리 셀 어레이(210)의 메모리 셀들은 셀 당 두 개의 비트를 저장하는 것으로 가정한다. 즉, 하나의 워드 라인에 연결된 메모리 셀들은 두 개의 어드레스 영역을 형성하는 것으로 가정한다. 그러나, 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200)의 메모리 셀 어레이(210)의 메모리 셀들은 셀 당두 개의 비트를 저장하는 것으로 한정되지 않음이 이해될 것이다.

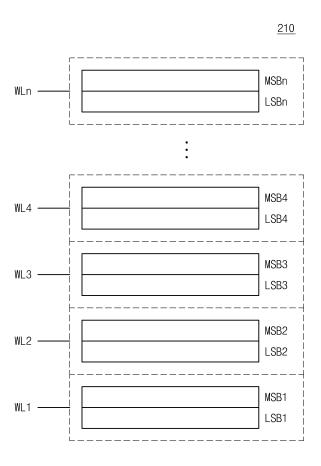

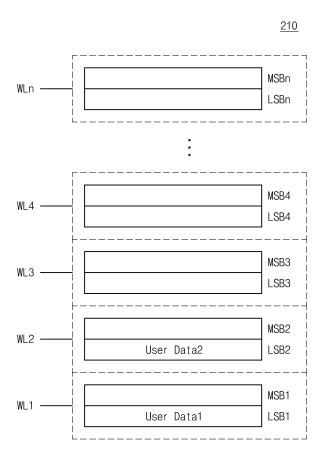

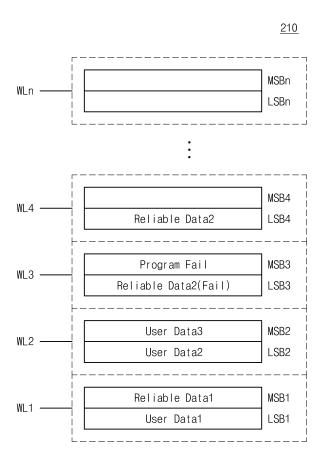

도 3은 도 2의 메모리 셀 어레이(210)의 어드레스 영역을 보여주는 다이어그램이다. 도 3을 참조하면, 복수의 워드 라인들(WL1-WLn)이 도시되어 있다. 각각의 워드 라인에 연결된 메모리 셀들(미도시)은 두 개의 어드레스 영역들을 형성한다. 도 3에서, 명확한 설명을 위하여, 메모리 셀들은 생략되어 있으며, 메모리 셀들에 의해 형성되는 어드레스 영역들(MSB1~MSBn, LSB1~LSBn)만 도시되어 있다.

워드 라인(WL1)에 연결된 메모리 셀들은 두 개의 어드레스 영역(MSB1, LSB)을 형성한다. 워드 라인(WL1)에 연결된 메모리 셀들에 저장되는 최상위 비트들(MSB, Most Significant Bits)은 최상위 어드레스 영역(MSB1)을 형성한다. 워드 라인(WL1)에 연결된 메모리 셀들에 저장되는 최하위 비트들(LSB, Least Significant Bits)은 최하위 어드레스 영역(LSB1)을 형성한다. 마찬가지로, 워드 라인들(WL1~WLn)에 연결된 메모리 셀들은 최상위 및 최하위 어드레스 영역들(MSB1~MSBn, LSB1~LSBn)을 형성한다.

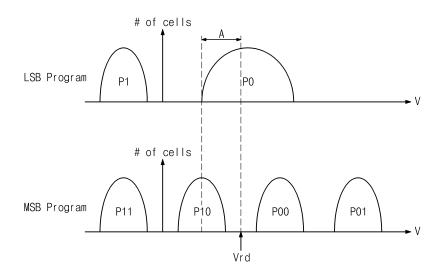

도 4는 도 1 내지 3의 메모리 셀 어레이(210)의 프로그램 동작을 설명하기 위한 다이어그램이다. 도 4에서, 가로 축은 전압(V)을 나타내며, 세로 축은 메모리 셀들의 수(# of cells)를 나타낸다. 즉, 도 4는 메모리 셀 어레이(210, 도 2 및 3 참조)의 메모리 셀들의 문턱 전압 산포를 나타낸다.

도 4에서, 상단부의 다이어그램은 최하위 비트(LSB) 프로그램 단계가 수행된 때의 메모리 셀들의 문턱 전압 산포를 나타낸다. 최하위 비트(LSB) 프로그램 단계에서, 메모리 셀 어레이(210)의 메모리 셀들은 소거 상태(P1) 또는 프로그램 상태(P0) 중 하나의 상태로 프로그램될 것이다. 도 4에서, 하단부의 다이어그램은 최상위 비트(MSB) 프로그램 단계가 수행된 때의 메모리 셀들의 문턱 전압 산포를 나타낸다. 최상위 비트(MSB) 프로그램 단계에서, 메모리 셀 어레이(210)의 메모리 셀들은 소거 상태(P11) 또는 프로그램 상태들(P10, P00, P01) 중 하나

[0043]

[0041]

[0042]

[0044]

[0045]

[0046]

[0047]

[0048]

[0049]

로 프로그램된다.

- [0050] 예시적으로, 최하위 비트(LSB) 프로그램 단계에서 소거 상태(P1)로 프로그램된 메모리 셀들은, 최상위 비트 (MSB) 프로그램 단계에서 소거 상태(P11) 또는 프로그램 상태(P10) 중 하나로 프로그램될 것이다. 예시적으로, 최하위 비트(LSB) 프로그램 단계에서 프로그램 상태(P0)로 프로그램된 메모리 셀들은, 최상위 비트(MSB) 프로그램 단계에서 프로그램 상태(P01) 중 하나로 프로그램될 것이다.

- [0051] 예시적으로, 소거 상태(P11)의 메모리 셀들은 "11" 데이터를 저장할 것이다. 프로그램 상태(P10)의 메모리 셀들은 "10" 데이터를 저장할 것이다. 프로그램 상태(P00)의 메모리 셀들은 "00" 데이터를 저장할 것이다. 프로그램 상태(P01)의 메모리 셀들은 "01" 데이터를 저장할 것이다.

- [0052] 도 4에서, 최상위 비트(MSB)가 프로그램된 메모리 셀들은, 문턱 전압의 증가에 따라 순차적으로 P11, P10, P00, P01 상태로 프로그램되는 것으로 도시되어 있다. 그러나, 본 발명의 실시 예에 따라 최상위 비트(MSB)가 프로그램된 메모리 셀들의 상태는 한정되지 않음이 이해될 것이다. 최상위 비트(MSB)가 프로그램된 메모리 셀들의 상태들의 순서는 다양하게 변경 및 응용될 수 있다.

- [0053] 도 2 내지 4를 참조하면, 최상위 비트(MSB) 프로그램 단계가 수행된 후에, 프로그램 상태(P10) 및 프로그램 상태(P00)는 읽기 전압(Vrd)에 의해 판별된다. 예시적으로, 메모리 셀의 문턱 전압이 읽기 전압(Vrd)보다 낮으면 소거 상태(P11) 또는 프로그램 상태(P10) 중 하나인 것으로 판별될 것이다. 예시적으로, 메모리 셀의 문턱 전압이 읽기 전압(Vrd) 보다 높으면, 프로그램 상태들(P00, P01) 중 하나인 것으로 판별될 것이다.

- [0054] 최상위 비트(MSB) 프로그램 시에 프로그램 상태(P0)는 프로그램 상태들(P00, P01) 중 하나로 프로그램된다. 즉, 최상위 비트(MSB) 프로그램 동작 시에, 프로그램 상태(P0)인 메모리 셀들의 문턱 전압은 상태(P0)에 대응하는 전압으로부터 상태들(P00, P01)중 하나에 대응하는 전압으로 증가할 것이다.

- [0055] 최상위 비트(MSB) 프로그램 동작 시에, 불휘발성 메모리 장치(200)의 전원이 오프되면, 최상위 비트(MSB) 프로그램은 중단될 것이다. 상태(P0)로부터 상태들(P00, P01) 중 하나로 프로그램되던 메모리 셀들 중 전압 구간 (A)에 대응하는 문턱 전압을 갖는 메모리 셀들은, 읽기 전압(Vrd)을 이용한 읽기 동작 시에 상태(P10)인 것으로 판별될 것이다. 즉, 최하위 비트(LSB) 프로그램 시에 "1"을 저장하도록 프로그램된 메모리 셀이, 최상위 비트 (MSB) 프로그램 시의 전원 오프로 인하여, 최하위 비트(LSB) 데이터로 "0"을 저장하는 것으로 판별될 것이다.

- [0056] 최상위 비트(MSB) 프로그램 동작은, 최하위 비트(LSB) 데이터를 저장하고 있는 메모리 셀에 데이터를 추가적으로 저장하기 위해 수행되는 프로그램 동작이다. 따라서, 최상위 비트(MSB) 프로그램 동작 시에 불휘발성 메모리 장치(200)의 전원이 오프되면, 최하위 비트(LSB) 데이터가 소실될 수 있음이 이해될 것이다.

- [0057] 최상위 비트(MSB) 프로그램 시의 전원 오프로 인해 소실되는 데이터가 사용자 데이터이면, 해당 데이터 및 관련된 데이터가 소실될 것이다. 최상위 비트(MSB) 프로그램 시의 전원 오프로 인해 소실되는 데이터가 불휘발성 메모리 장치(200)의 동작을 위해 요구되는 신뢰 데이터이면, 불휘발성 메모리 장치(200) 및 불휘발성 메모리 장치(200)를 포함하는 메모리 시스템(10)이 정상적으로 동작하지 않을 수 있음이 이해될 것이다.

- [0058] 상술한 바와 같이 신뢰 데이터의 소실로 인한 불휘발성 메모리 장치(200) 및 그것을 포함하는 메모리 시스템 (10)의 오동작을 방지하기 위하여, 본 발명의 실시 예에 따른 프로그램 제어부(110, 도 1 참조)는 프로그램 데이터가 불휘발성 메모리 장치(200)의 제 1 어드레스 영역에 저장되고, 프로그램 데이터가 사용자 데이터가 아닌 신뢰 데이터이면, 프로그램 데이터가 불휘발성 메모리 장치(200)의 제 2 어드레스 영역에 추가적으로 저장되도록 제어한다. 예시적으로, 신뢰 데이터는 불휘발성 메모리 장치(200) 및 불휘발성 메모리 장치(200)를 포함하는 메모리 시스템(10)을 구동하기 위해 요구되는 데이터일 것이다.

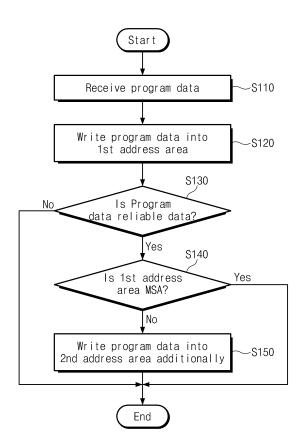

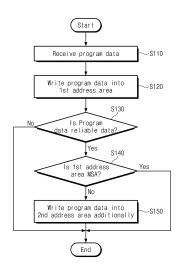

- [0059] 도 5는 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200, 도 1 및 3 참조)의 프로그램 방법을 보여주는 순서도이다. 도 6 내지 9는 도 5의 순서도에 따른 프로그램 과정을 설명하기 위한 다이어그램이다.

- [0060] 도 5를 참조하면, S110 단계에서, 메모리 시스템(10)은 프로그램 데이터를 전달받는다. 예시적으로, 프로그램 데이터는 외부(예를 들면, 호스트)로부터 컨트롤러(100, 도 1 참조)에 전달될 것이다. S120 단계에서, 프로그램 데이터는 불휘발성 메모리 장치(200)의 제 1 어드레스 영역에 기입된다. 프로그램 제어부(110)는 프로그램 데이터가 불휘발성 메모리 장치(200)의 제 1 어드레스 영역에 저장되도록 제어할 것이다.

- [0061] S130 단계에서, 프로그램 제어부(110)는 프로그램 데이터가 신뢰 데이터인지 판별한다. 프로그램 데이터가 신뢰 데이터가 아니면, 프로그램 데이터가 제 1 어드레스 영역에 저장된 상태로 프로그램 동작이 종료된다. 프로그램

데이터가 신뢰 데이터이면, S140 단계가 수행된다.

[0062] S140 단계에서, 프로그램 제어부(110)는 프로그램 데이터가 기입된 제 1 어드레스 영역이 최상위 어드레스 영역 인지 판별한다. 제 1 어드레스 영역이 최상위 어드레스 영역이면, 프로그램 데이터가 제 1 어드레스 영역에 저장된 상태로 프로그램 동작이 종료된다. 제 1 어드레스 영역이 최상위 어드레스 영역이 아니면, S150 단계가 수행된다.

[0063] S150 단계에서, 프로그램 제어부(110)는 프로그램 데이터가 불휘발성 메모리 장치(200)의 메모리 셀 어레이 (210)의 제 2 어드레스 영역에 추가적으로 기입되도록 제어한다. 즉, 프로그램 데이터가 신뢰 데이터이며, 프로그램 데이터가 기입되는 제 1 어드레스 영역이 최상위 어드레스 영역이 아니면, 프로그램 데이터는 제 2 어드레스 영역에 추가적으로 기입된다.

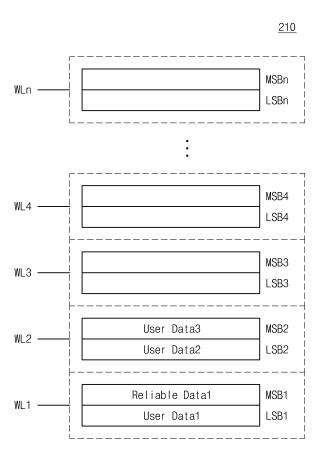

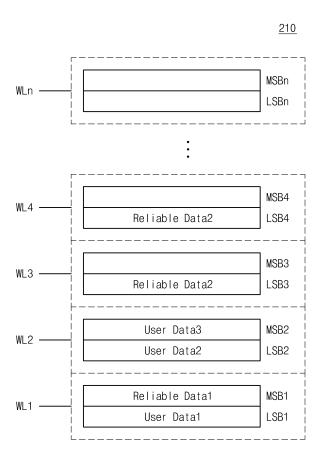

[0064] 도 6 내지 9는 도 3을 참조하여 설명된 최상위 어드레스 영역 및 최하위 어드레스 영역에 데이터가 기입되는 과정을 보여준다.

예시적으로, 커플링을 방지하기 위하여, 불휘발성 메모리 장치(200)에서, 두 개의 최하위 어드레스 영역(LSB1, LSB2)이 프로그램된 후, 두 개의 최상위 어드레스 영역(MSB1, MSB2)이 프로그램되는 것으로 가정하자. 이후에, 다시 두 개의 최하위 어드레스 영역(LSB3, LSB4)이 프로그램되고, 두 개의 최상위 어드레스 영역(MSB3, MSB4)이 프로그램될 것이다.

예시적으로, 두 개의 어드레스 영역에 대응하는 제 1 및 제 2 사용자 데이터(User Data1, User Data2)가 프로그램 데이터로 입력되는 것으로 가정하자. 도 5의 S130 단계를 참조하여 설명된 바와 같이, 프로그램 데이터가 사용자 데이터이므로, 프로그램 데이터는 대응하는 제 1 어드레스 영역에 저장될 것이다.

도 6을 참조하면, 제 1 사용자 데이터(User Data1)는 워드 라인(WL1)에 연결된 최하위 어드레스 영역(LSB1)에 저장된다. 프로그램 데이터가 사용자 데이터이므로, 제 1 사용자 데이터(User Data1)에 대한 프로그램 동작은 종료된다. 제 2 사용자 데이터(User Data2)는 워드 라인(WL2)에 연결된 최하위 어드레스 영역(LSB2)에 저장된다. 프로그램 데이터가 사용자 데이터이므로, 제 2 사용자 데이터(User Data2)에 대한 프로그램 동작은 종료된다.

이후에, 하나의 어드레스 영역에 대응하는 제 1 신뢰 데이터(Reliable Datal)와 하나의 어드레스 영역에 대응하는 제 3 사용자 데이터(User Data3)가 프로그램 데이터로 입력되는 것으로 가정하자. 도 7을 참조하면, 제 1 신뢰 데이터(Reliable Datal)는 워드 라인(WL1)에 연결된 최상위 어드레스 영역(MSB1)에 저장된다. 도 5의 S130 및 S140 단계를 참조하여 설명된 바와 같이, 프로그램 데이터는 신뢰 데이터이며, 프로그램 데이터가 저장되는 제 1 어드레스 영역(MSB1)은 최상위 어드레스 영역이므로, 제 1 신뢰 데이터(Reliable Datal)에 대한 프로그램 동작은 종료된다. 이후에, 워드 라인(WL2)에 연결된 최상위 어드레스 영역(MSB2)에 제 3 사용자 데이터(User Data3)가 기입된다.

최상위 어드레스 영역에 데이터가 기입되면, 이후에 해당 어드레스 영역에 대한 프로그램 동작은 수행되지 않을 것이다. 즉, 최상위 어드레스 영역에 신뢰 데이터가 기입되면, 프로그램 동작 시의 전원 오프로 인해 해당 신뢰 데이터가 소실되는 것은 발생되지 않을 것이다. 따라서, 프로그램 데이터가 신뢰 데이터이더라도, 프로그램 데이터가 기입되는 제 1 어드레스 영역이 최상위 어드레스 영역이면, 프로그램 데이터가 제 1 어드레스 여역에 저장되는 것으로 프로그램 동작이 종료될 것이다.

이후에, 하나의 어드레스 영역에 대응하는 제 2 신뢰 데이터(Reliable Data2)가 입력되는 것으로 가정하자. 도 8을 참조하면, 제 2 신뢰 데이터(Reliable Data2)는 워드 라인(WL3)에 연결된 최하위 어드레스 영역(LSB3)에 저장된다. 도 5의 S130 내지 S150 단계를 참조하여 설명된 바와 같이, 프로그램 데이터가 신뢰 데이터이며, 프로그램 데이터가 저장되는 제 1 어드레스 영역(LSB3)이 최상위 어드레스 영역이 아니므로, 신뢰 데이터는 제 2 어드레스 영역(LSB4)에 추가적으로 저장된다.

예시적으로, 제 1 어드레스 영역(LSB3)에 기입된 프로그램 데이터가 읽기/쓰기 회로(230, 도 2 참조)에 의해 읽어지고, 읽어진 데이터가 제 2 어드레스 영역(LSB4)에 저장될 것이다. 즉, 읽기/쓰기 회로(230)는 프로그램 데이터를 제 2 어드레스 영역(LSB4)에 저장하기 위해 카피백 동작을 수행할 것이다.

다른 예로서, 컨트롤러(100)로부터 불휘발성 메모리 장치(200)로 프로그램 데이터가 다시 전달될 것이다. 그리고, 컨트롤러(100)로부터 불휘발성 메모리 장치(200)로 프로그램 데이터가 기입될 제 2 어드레스 영역(LSB4)의 어드레스가 전달될 것이다. 불휘발성 메모리 장치(200)는 전달된 프로그램 데이터 및 제 2 어드레스 영역(LSB

[0067]

[0066]

[0065]

[0068]

[0069]

[0070]

[0072]

[0071]

4)의 어드레스에 기반하여, 프로그램 데이터를 제 2 어드레스 영역(LSB4)에 저장할 것이다.

[0073] 다른 예로서, 컨트롤러(100)로부터 불휘발성 메모리 장치(200)로 프로그램 데이터가 다시 전달될 것이다. 불휘 발성 메모리 장치(200)는 컨트롤러(100)의 제어에 응답하여 제 1 어드레스 영역(LSB3)의 어드레스(예를 들면, 행 어드레스)를 카운트 업 또는 카운트 다운할 것이다. 카운트 업 또는 카운트 다운에 의해 생성된 어드레스에 프로그램 데이터가 기입될 것이다.

다른 예로서, 불휘발성 메모리 장치(200)는 컨트롤러(100)로부터 제 2 어드레스 영역의 어드레스를 전달받거나, 또는 컨트롤러(100)로부터의 제어 신호에 응답하여 제 1 어드레스 영역의 어드레스를 카운터 업 또는 카운트 다 운하여 제 2 어드레스 영역의 어드레스를 생성하고, 데이터 입출력 회로(240) 또는 읽기/쓰기 회로(230)에 버퍼 링되어 있는 프로그램 데이터를 메모리 셀 어레이(210)의 제 2 어드레스 영역에 저장할 것이다.

제 1 어드레스 영역(LSB3)에 저장된 신뢰 데이터는 워드 라인(WL3)에 연결된 최상위 어드레스 영역(MSB3)의 프로그램 시에 소실될 수 있다. 제 1 어드레스 영역(LSB3)에 저장된 신뢰 데이터가 소실되면, 제 2 어드레스 영역(LSB4)에 저장된 신뢰 데이터가 사용될 것이다. 예시적으로, 제 1 어드레스 영역(LSB3)에 대한 액세스는 제 2 어드레스 영역(LSB4)에 대한 액세스로 매핑될 것이다.

예시적으로, 제 1 어드레스 영역(LSB3)에 저장된 신뢰 데이터가 소실되면, 제 2 어드레스 영역(LSB4)에 저장된 신뢰 데이터가 제 3 어드레스 영역으로 복사될 것이다. 즉, 신뢰 데이터는 적어도 두 개의 어드레스 영역에서 유지되도록 제어될 것이다.

이후에, 하나의 어드레스 영역에 대응하는 프로그램 데이터가 입력되는 것으로 가정하자. 도 9를 참조하면, 입력된 프로그램 데이터는 신뢰 데이터가 저장되어 있는 최하위 어드레스 영역(LSB3)에 대응하는 최상위 어드레스 영역(MSB3)에 기입될 것이다. 최상위 어드레스 영역(MSB3)에 대한 프로그램 동작 시에 불휘발성 메모리 장치(200)가 전원 오프되면, 프로그램 중인 최상위 어드레스 영역(MSB3)에 대응하는 최하위 어드레스 영역(LSB3)에 저장되어 있던 신뢰 데이터가 소실될 것이다. 이후에, 소실된 신뢰 데이터가 저장되어 있는 최하위 어드레스 영역(LSB4)에 대한 액세스는 정상적인 신뢰 데이터가 저장되어 있는 최하위 어드레스 영역(LSB4)에 대한 액세스로 매핑될 것이다.

상술한 바와 같이, 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200) 및 그것을 포함하는 메모리 시스템 (10)은 프로그램 데이터를 제 1 어드레스 영역에 저장하고, 프로그램 데이터가 사용자 데이터가 아닌 신뢰 데이터이면, 프로그램 데이터를 제 2 어드레스 영역에 추가적으로 저장한다. 따라서, 최상위 비트(MSB) 프로그램 시의 전원 오프로 인해, 대응하는 최하위 어드레스 영역에 저장되어 있는 신뢰 데이터가 소실되어 불휘발성 메모리 장치(200) 및 그것을 포함하는 메모리 시스템(10)이 오동작하는 것이 방지된다.

예시적으로, 도 5를 참조하여 설명된 제어 동작은 컨트롤러(100)의 프로그램 제어부(110)에 의해 수행될 것이다. 예시적으로, 제어부(110)는 컨트롤러(100)에서 디지털 회로, 아날로그 회로, 또는 디지털 회로와 아날 로그 회로의 하이브리드 형태로 구현되는 하드웨어일 것이다. 다른 예로서, 제어부(110)는 컨트롤러(100)에서 구동되는 소프트웨어 형태로 구현될 것이다. 예를 들면, 제어부(110)의 제어 동작은 플래시 변환 계층(Flash Translation Layer)의 일부로 구현될 것이다. 다른 예로서, 제어부(110)는 컨트롤러(100)에서 하드웨어 및 소프트웨어의 하이브리드 형태로 구현될 것이다.

상술한 실시 예에서, 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200)는 플래시 메모리 장치의 예를 참조하여 설명되었다. 그러나, 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200)는 플래시 메모리 장치로 한정되지 않는다. 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200)는 ROM, PROM, EPROM, 플래시 메모리 장치, PRAM, MRAM, RRAM, FRAM 등으로 구현될 수 있다. 예시적으로, 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200)는 셀 당 복수의 비트를 저장하는 멀티 레벨 메모리에 적용될 수 있다.

상술한 실시 예에서, 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200)는 셀 당 두 개의 비트를 저장하는 것으로 설명되었다. 그러나, 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200)는 셀 당 두 개의 비트를 저장하는 것으로 한정되지 않는다. 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200)는 셀 당 n 개의 비트를 저장하는 n 레벨 메모리 셀을 포함할 수 있다.

예시적으로, 메모리 셀에 저장되는 최상위 비트들(MSB)은 최상위 어드레스 영역을 형성할 것이다. 메모리 셀에 저장되는 최하위 비트들(LSB)은 최하위 어드레스 영역을 형성할 것이다. 메모리 셀에 저장되는 최상위 및 최하위 사이의 중간 비트들(CSB)은 중간 어드레스 영역을 형성할 것이다. 예시적으로, 프로그램 데이터가 신뢰 데이터이고, 프로그램 데이터가 기입되는 제 1 어드레스 영역이 최상위 어드레스 영역이 아니면, 프로그램 데이터는

[0076]

[0075]

[0074]

[0077]

[0078]

[0079]

[0800]

[0081]

[0082]

제 2 어드레스 영역에 추가적으로 기입될 것이다.

[0083] 상술한 실시 예에서, 어드레스 영역은 워드 라인에 연결된 메모리 셀들의 단위로 형성되는 것으로 설명되었다. 그러나, 본 발명의 실시 예에 따른 어드레스 영역은 워드 라인에 연결된 메모리 셀들의 단위로 형성되는 것으로 한정되지 않음이 이해될 것이다.

> 예시적으로, 불휘발성 메모리 장치(200)의 읽기/쓰기 동작이 m 개의 메모리 셀들의 단위로 수행되면, 어드레스 영역은 m 개의 메모리 셀들의 단위로 형성될 것이다. m 개의 메모리 셀들에 저장되는 최상위 비트들(MSB)은 최 상위 어드레스 영역을 형성할 것이다. m 개의 메모리 셀들에 저장되는 최하위 비트들(LSB)은 최하위 어드레스 영역을 형성할 것이다. m 개의 메모리 셀들에 최상위 비트들(MSB) 및 최하위 비트들(LSB) 사이의 중간 비트들 (CSB)이 저장되면, m 개의 메모리 셀들에 저장되는 중간 비트들(CSB)은 중간 어드레스 영역들을 형성할 것이다. m 개의 메모리 셀들에 프로그램되는 프로그램 데이터가 신뢰 데이터이고, 프로그램 데이터가 저장되는 어드레스 영역이 최상위 어드레스 영역이 아니면, 프로그램 데이터는 다른 어드레스 영역에 추가적으로 저장될 것이다.

> 상술한 실시 예에서, 커플링을 방지하기 위하여, 불휘발성 메모리 장치(200)의 프로그램 동작은 두 개의 최하위 어드레스 영역들 및 두 개의 최상위 어드레스 영역들에 대해 교대로 수행되는 것으로 설명되었다. 그러나, 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200)의 프로그램 동작은 두 개의 최하위 어드레스 영역들 및 두 개의 최하위 어드레스 영역들에 대해 교대로 수행되는 것으로 한정되지 않는다. 커플링을 방지하기 위한 프로그 램 패턴은 다양하게 변경 및 응용될 수 있으며, 생략될 수도 있음이 이해될 것이다.

> 도 10은 본 발명의 다른 실시 예에 따른 불휘발성 메모리 장치(300)를 보여주는 블록도이다. 도 10을 참조하면, 본 발명의 다른 실시 예에 따른 불휘발성 메모리 장치(300)는 메모리 셀 어레이(310), 어드레스 디코더(320), 읽기/쓰기 회로(330), 데이터 입출력 회로(340), 그리고 제어 로직(350)을 포함한다.

> 메모리 셀 어레이(310), 어드레스 디코더(320), 읽기/쓰기 회로(330), 그리고 데이터 입출력 회로(340)는 도 2 를 참조하여 설명된 메모리 셀 어레이(210), 어드레스 디코더(220), 읽기/쓰기 회로(230), 그리고 데이터 입출 력 회로(240)와 동일하게 구성되고 동작할 것이다. 따라서, 더 이상의 상세한 설명은 생략된다.

> 제어 로직(350)은 불휘발성 메모리 장치(300)의 제반 동작을 제어한다. 제어 로직(350)은 프로그램 제어부(35 1)를 포함한다. 프로그램 제어부(351)는 도 1 내지 9를 참조하여 설명된 프로그램 제어부(110)와 동일하게 동작 할 것이다. 즉, 프로그램 제어부(351)는 프로그램 데이터를 제 1 어드레스 영역에 저장하고, 프로그램 데이터가 사용자 데이터가 아닌 신뢰 데이터이면, 프로그램 데이터를 제 2 어드레스 영역에 추가적으로 저장하도록 구성 될 것이다. 도 1 내지 9를 참조하여 프로그램 제어부(110)의 동작이 상세히 설명되었으므로, 프로그램 제어부 (351)의 동작에 대한 더 이상의 상세한 설명은 생략된다.

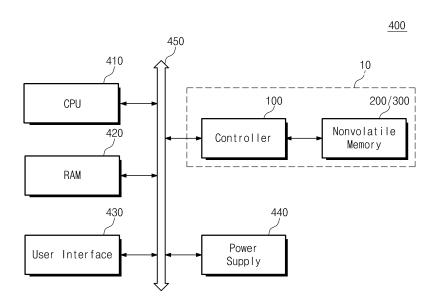

> 도 11은 본 발명의 실시 예에 따른 불휘발성 메모리 장치(200/300) 및 그것을 포함하는 메모리 시스템(10)을 갖 는 컴퓨팅 시스템(300)의 실시 예를 보여주는 블록도이다. 도 11을 참조하면, 본 발명의 실시 예에 따른 컴퓨팅 시스템(400)은 중앙 처리 장치(410), 램(420, RAM, Random Access Memory), 사용자 인터페이스(430), 전원 (440), 그리고 메모리 시스템(10)을 포함한다.

> 메모리 시스템(10)은 시스템 버스(450)를 통해, 중앙처리장치(410), 램(420), 사용자 인터페이스(430), 그리고 전원(440)에 전기적으로 연결된다. 사용자 인터페이스(430)를 통해 제공되거나, 중앙 처리 장치(410)에 의해서 처리된 데이터는 메모리 시스템(10)에 저장된다. 메모리 시스템(10)은 컨트롤러(100) 및 불휘발성 메모리 장치 (200/300)를 포함한다.

> 예시적으로, 도 1 내지 9를 참조하여 설명된 바와 같이, 메모리 시스템(10)은 컨트롤러(100) 및 불휘발성 메모 리 장치(200)를 포함할 것이다. 컨트롤러(100)는 프로그램 제어부를 포함할 것이다. 다른 예로서, 도 10을 참조 하여 설명된 바와 같이, 메모리 시스템(10)은 컨트롤러(100) 및 프로그램 제어부(351)를 구비한 제어 로직(35 0)을 포함하는 불휘발성 메모리 장치(300)를 포함할 것이다.

> 메모리 시스템(10)이 반도체 디스크 장치(SSD)로 장착되는 경우, 컴퓨팅 시스템(300)의 부팅 속도가 획기적으로 빨라질 수 있다. 도면에 도시되지 않았지만, 본 발명에 따른 시스템은 응용 칩셋(Application Chipset), 카메라 이미지 프로세서(Camera Image Processor) 등을 더 포함할 수 있음은 이 분야의 통상적인 지식을 습득한 자들에 게 이해될 것이다.

본 발명의 상세한 설명에서는 구체적인 실시 예에 관하여 설명하였으나, 본 발명의 범위와 기술적 사상에서 벗 어나지 않는 한도 내에서 여러 가지 변형이 가능함은 자명하다. 그러므로 본 발명의 범위는 상술한 실시 예에

[0093]

[0084]

[0085]

[0086]

[0087]

[0088]

[0089]

[0090]

[0091]

[0092]

- 11 -

국한되어 정해져서는 안되며 후술하는 특허청구범위뿐만 아니라 이 발명의 특허청구범위와 균등한 것들에 의해 정해져야 한다.

# 도면의 간단한 설명

[0094] 도 1은 본 발명의 실시 예에 따른 메모리 시스템을 보여주는 블록도이다.

도 2는 도 1의 불휘발성 메모리 장치를 보여주는 블록도이다.

도 3은 도 2의 메모리 셀 어레이의 어드레스 영역을 보여주는 다이어그램이다.

도 4는 도 1 내지 3의 메모리 셀 어레이의 프로그램 동작을 설명하기 위한 다이어그램이다.

도 5는 본 발명의 실시 예에 따른 불휘발성 메모리 장치의 프로그램 방법을 보여주는 순서도이다.

도 6 내지 9는 도 5의 순서도에 따른 프로그램 과정을 설명하기 위한 다이어그램이다.

도 10은 본 발명의 다른 실시 예에 따른 불휘발성 메모리 장치를 보여주는 블록도이다.

도 11은 본 발명의 실시 예에 따른 불휘발성 메모리 장치 및 그것을 포함하는 메모리 시스템을 갖는 컴퓨팅 시스템의 실시 예를 보여주는 블록도이다.

#### 도면

[0095]

[0096] [0097]

[0098]

[0099] [0100]

[0101]