(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5046819号

(P5046819)

(45) 発行日 平成24年10月10日(2012.10.10)

(24) 登録日 平成24年7月27日(2012.7.27)

|                         |                  |

|-------------------------|------------------|

| (51) Int.Cl.            | F 1              |

| B 41 J 2/16 (2006.01)   | B 41 J 3/04 103H |

| B 41 J 2/05 (2006.01)   | B 41 J 3/04 103B |

| H 01 L 21/306 (2006.01) | H 01 L 21/306 T  |

請求項の数 11 (全 11 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2007-238387 (P2007-238387) |

| (22) 出願日  | 平成19年9月13日 (2007.9.13)       |

| (65) 公開番号 | 特開2009-66933 (P2009-66933A)  |

| (43) 公開日  | 平成21年4月2日 (2009.4.2)         |

| 審査請求日     | 平成22年9月13日 (2010.9.13)       |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】スルーホールの形成方法およびインクジェットヘッド

## (57) 【特許請求の範囲】

## 【請求項 1】

シリコン基板の第1の面の側におけるスルーホールの入口孔が形成される領域の周囲に、前記シリコン基板よりも不純物濃度が高い第1の不純物領域を形成する工程と、

前記シリコン基板の深さ方向において前記第1の不純物領域に隣接する位置に、前記第1の不純物領域よりも不純物濃度が高い第2の不純物領域を形成する工程と、

前記第1の不純物領域および前記第2の不純物領域が形成された前記シリコン基板の前記第1の面の上に、エッチングストップ層を形成する工程と、

前記シリコン基板の前記第1の面の反対側の第2の面上に、前記スルーホールの出口孔が形成される領域に開口部を有するエッチングマスク層を形成する工程と、

前記開口部を通して、少なくとも前記エッチングストップ層が露出するまで、前記シリコン基板をエッチングする工程と、

を含むことを特徴とするスルーホールの形成方法。

## 【請求項 2】

前記エッチングする工程の後に、前記エッチングストップ層を除去する工程を含むことを特徴とする請求項1に記載のスルーホールの形成方法。

## 【請求項 3】

前記第2の不純物領域は、前記第1の不純物領域よりも、前記シリコン基板の前記第1の面の近くに配置されることを特徴とする請求項1又は請求項2に記載のスルーホールの形成方法。

**【請求項 4】**

前記第1の不純物領域の少なくとも一部は、前記第2の不純物領域よりも、前記スルーホールの近くに配置されることを特徴とする請求項3に記載のスルーホールの形成方法。

**【請求項 5】**

前記第2の不純物領域の少なくとも一部は、熱酸化膜と接していることを特徴とする請求項1乃至請求項4のいずれか1項に記載のスルーホールの形成方法。

**【請求項 6】**

前記第2の不純物領域の内径が前記第1の不純物領域の内径よりも小さいことを特徴とする請求項1乃至3のいずれか1項に記載のスルーホールの形成方法。

**【請求項 7】**

前記第1の不純物領域を形成する工程における加速エネルギーと前記第2の不純物領域を形成する工程における加速エネルギーとが互いに異なることを特徴とする請求項1乃至6のいずれか1項に記載のスルーホールの形成方法。

10

**【請求項 8】**

前記第1の不純物領域を形成する工程において、前記第1の不純物領域とともに、半導体素子の第1の部分が形成され、前記第2の不純物領域を形成する工程において、前記第2の不純物領域とともに、前記半導体素子の第2の部分が形成されることを特徴とする請求項1乃至7のいずれか1項に記載のスルーホールの形成方法。

**【請求項 9】**

前記シリコン基板は、第1の導電型のシリコン基板の前記第1の面の側に第2の導電型のウェル領域を有し、前記第1の不純物領域および前記第1の部分が第1の導電型であることを特徴とする請求項8に記載のスルーホールの形成方法。

20

**【請求項 10】**

MIS型電界効果トランジスタのゲート電極を形成する工程を更に含み、前記第2の不純物領域を形成する工程において、前記第2の部分が前記ゲート電極をマスクとして使用するイオン注入によって形成されることを特徴とする請求項8又は9に記載のスルーホールの形成方法。

**【請求項 11】**

請求項1乃至請求項10のいずれか1項に記載のスルーホールの形成方法によって形成されたスルーホールがインク供給口として形成されていることを特徴とするインクジェットヘッド。

30

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、スルーホールの形成方法およびインクジェットヘッドに関する。

**【背景技術】****【0002】**

従来、シリコン基板に等方性エッティング又は異方性エッティングによりスルーホールを形成し、各種デバイスに応用する研究がなされている。この技術はインクジェットヘッドのインク供給口の形成にも応用されている。

40

**【0003】**

インクジェットヘッドを形成する際には、特に、一つの基板上に多数の記録素子を配置する場合に、スルーホールのエッティング終端側のエッジと、インクジェット記録素子及びインク吐出口との距離がばらつくことがある。これにより、各ノズル間の印字特性にばらつきが生じ、印字画像の品質が著しく低下しうる。

**【0004】**

これに対し、本出願人は、シリコン基板のスルーホールが形成される領域の周囲に、不純物濃度の高い領域を形成し、スルーホールの大きさを制御する方法を提案している（特許文献1を参照）。

【特許文献1】特開2004-34533号公報

50

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

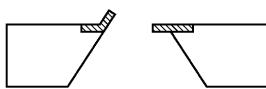

しかしながら、特許文献1の方法では、不純物濃度の高い領域の厚さが薄い場合、図4に示すように、機械的な強度が弱くなり、エッチングストップ層との間の応力によりそれが発生したり、割れが発生したりしうるという問題がある。また、不純物濃度の高い領域を厚くすると、そりは抑えられるが、生産性が落ちたり、コストが上がったりするという問題がある。

**【0006】**

本発明は、上記の問題点に鑑みてなされたものであり、スルーホールの位置精度を向上させるとともに、スルーホール周辺の機械強度を高めることを目的とする。10

**【課題を解決するための手段】****【0007】**

本発明の第1の側面は、スルーホールの形成方法に係り、シリコン基板の第1の面の側におけるスルーホールの入口孔が形成される領域の周囲に、前記シリコン基板よりも不純物濃度が高い第1の不純物領域を形成する工程と、前記シリコン基板の深さ方向において前記第1の不純物領域に隣接する位置に、前記第1の不純物領域よりも不純物濃度が高い第2の不純物領域を形成する工程と、前記第1の不純物領域および前記第2の不純物領域が形成された前記シリコン基板の前記第1の面の上に、エッチングストップ層を形成する工程と、前記シリコン基板の前記第1の面の反対側の第2の面の上に、前記スルーホールの出口孔が形成される領域に開口部を有するエッティングマスク層を形成する工程と、前記開口部を通して、少なくとも前記エッティングストップ層が露出するまで、前記シリコン基板をエッチングする工程と、を含むことを特徴とする。20

**【0008】**

本発明の第2の側面は、インクジェットヘッドに係り、上記のスルーホールの形成方法によって形成されたスルーホールがインク供給口として形成されていることを特徴とする。。

**【0010】**

本発明の第4の側面は、インクジェットヘッドに係り、上記のシリコン基板に形成されていることを特徴とする。30

**【発明の効果】****【0011】**

本発明によれば、スルーホールの位置精度を向上させるとともに、スルーホール周辺の機械強度を高めることができる。

**【発明を実施するための最良の形態】****【0012】**

以下、本発明の好適な実施の形態について、図面を参照して詳細に説明する。なお、下記の説明において記載された各部の構成、配置、大きさ、不純物タイプ等は、特段の記載がない限り、本発明の範囲をそれのみに限定する趣旨のものではない。

**【0013】****(第1の実施形態)**

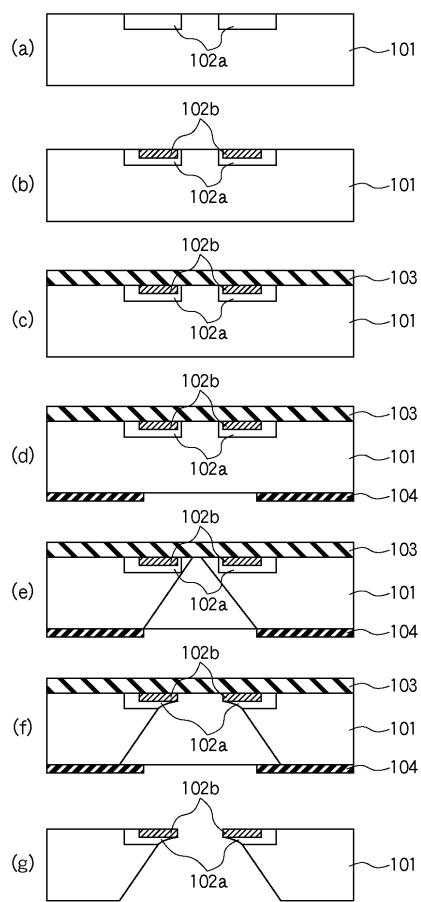

図1は、本発明の好適な第1の実施形態に係るスルーホールの形成方法を説明するための図である。

**【0014】**

図1(a)に示す工程では、<100>の結晶面方位を有するシリコン基板101を準備する。次いで、シリコン基板101の第1の面において、スルーホールの入口孔が形成される領域の周囲にシリコン基板101よりも不純物濃度が高い第1の不純物領域102aを形成する。第1の不純物領域102aは、例えば、周知のフォトリソグラフィ技術によってパターンを形成し、このパターンをマスクとして、イオン注入法を用いてシリコン基板101中に不純物を導入することにより形成されうる。40

**【 0 0 1 5 】**

図1( b )に示す工程では、図1( a )に示す工程で形成された第1の不純物領域102aよりも不純物濃度が高い第2の不純物領域102bを、スルーホールの入口孔が形成される領域の周囲に形成する。第2の不純物領域102bは、シリコン基板101の深さ方向において、第1の不純物領域102aに隣接する位置に形成される。

**【 0 0 1 6 】**

図1( c )に示す工程では、図1( b )に示す工程で形成された第2の不純物領域102bの上(第1の面の上)に、エッティングストップ層103を形成する。

**【 0 0 1 7 】**

図1( d )に示す工程では、シリコン基板101のスルーホールの入口孔が形成される第1の面と対向する第2の面の上に、エッティングマスク層104を形成する。10 エッティングマスク層104の開口部は、スルーホールの出口孔が形成される領域に対応する。

**【 0 0 1 8 】**

図1( e )に示す工程では、シリコン基板101を強アルカリ溶液等のエッティング液に浸漬し、エッティングマスク層104をマスクとして、異方性エッティングにより、スルーホールが形成される。エッティングマスク層104の開口部は、エッティングストップ層103が露出するまでエッティングされたスルーホールが、第1、第2の不純物領域102a、102bの内側に形成されるように配置される。

**【 0 0 1 9 】**

図1( f )に示す工程では、オーバーエッティングを行って、スルーホールがサイドエッティングにより広がり、第1、第2の不純物領域102a、102bに達する。スルーホールのサイドエッティングが、第1、第2の不純物領域102a、102bに達すると、不純物濃度に依存して、サイドエッティング速度が遅くなる。具体的には、サイドエッティングの速度は、約1/2~1/10程度まで遅くなる。ここで、シリコン基板101を貫通した時点におけるスルーホールの大きさが、シリコン基板101の厚さのばらつきや結晶欠陥などで、ばらついていたとする。その場合でも、オーバーエッティングを行って、スルーホールが第1、第2の不純物領域102a、102bまで広がると、その時点からサイドエッティング量が極端に小さくなる。その結果、得られるスルーホールの大きさは、図1( f )に示すようにほぼ一定となる。

**【 0 0 2 0 】**

図1( g )に示す工程では、上述のようにスルーホールの大きさが制御されたシリコン基板101から、エッティングストップ層103及びエッティングマスク層104を適宜除去して、スルーホールが完成する。

**【 0 0 2 1 】**

なお、第1、第2の不純物領域102a、102bは、それぞれエッティング速度が異なる。そのため、不純物濃度とエッティング時間に応じて、第1、第2の不純物領域102a、102bの厚さもそれぞれ異なる。これを図1( e )及び図1( f )を参照して説明する。

**【 0 0 2 2 】**

図1( e )及び図1( f )に示すように、第1の不純物領域102aと第2の不純物領域102bとは、シリコン基板101の深さ方向に対する位置が異なる。具体的には、第2の不純物領域102bは、第1の不純物領域102aよりもシリコン基板101の表面近傍に位置する。また、第1の不純物領域102aは、シリコン基板101よりも不純物濃度が高く、第2の不純物領域102bは、第1の不純物領域102aよりも不純物濃度が高い。そのため、図1( e )及び図1( f )に示す工程では、シリコン基板101のエッティング速度が最も速く、その次に、第1の不純物領域102aのエッティング速度が速く、第2の不純物領域102bのエッティング速度が一番遅くなる。その結果、スルーホールをオーバーエッティングすると、第1の不純物領域102aは、シリコン基板101よりもエッティングされずに残り、スルーホールの出口孔に近づくにつれて厚さが厚くなる。また、第2の不純物領域102bは、ほとんどエッティングされないで残る。これにより、第24050

の不純物領域 102b の機械強度を第 1 の不純物領域 102a で補強するとともに、スルーホールの入口孔から出口孔までの形状をほぼ滑らかにことができる。また、本実施形態によれば、第 1 の不純物領域 102a は、第 2 の不純物領域 102b よりも不純物濃度が低いため、熱拡散やイオン注入により容易に形成することができる。そのため、生産性が高く、コストの低いスルーホール形成方法を実施することができる。

#### 【0023】

これに対し、従来のシリコン基板上に不純物濃度の高い領域のみを配置する方法でも、不純物濃度の高い領域を厚く形成することにより、機械強度を高めることができる。しかしながら、不純物濃度の高い領域を厚く形成するためには、高濃度の不純物を長時間熱拡散させるなど、工程数の増加や処理時間の増大を招く。また、シリコン基板と不純物領域とのエッチング速度の差が大きいため、スルーホールの入口孔から出口孔までの形状が滑らかにならず、段差が生じうる。10

#### 【0024】

また、第 1 の不純物領域 102a の不純物濃度は、 $1 \times 10^{18} \text{ cm}^{-3}$  以上であることが好ましく、 $1 \times 10^{19} \text{ cm}^{-3}$  以上であることが更に好ましい。不純物濃度が $7 \times 10^{19} \text{ cm}^{-3}$  以上になると、通常のシリコン基板のエッチング速度と比べて、1/100 程度までエッチング速度が低下する。本実施形態では、第 1 の不純物領域 102a のサイドエッチングの速度をシリコン基板よりも適度に低下させねばよいため、 $1 \times 10^{18} \text{ cm}^{-3}$  以上の不純物濃度でも効果が認められる。20

#### 【0025】

また、第 2 の不純物領域 102b の不純物濃度は、通常のシリコン基板よりも大きくエッチング速度を低下させるために、 $1 \times 10^{19} \text{ cm}^{-3}$  以上であることが好ましく、 $7 \times 10^{19} \text{ cm}^{-3}$  以上であることが更に好ましい。20

#### 【0026】

また、シリコン基板 101 の濃度は、特に限定されないが、 $1 \times 10^{13} \text{ cm}^{-3} \sim 1 \times 10^{16} \text{ cm}^{-3}$  程度であることが好ましい。

#### 【0027】

また、第 1、第 2 の不純物領域 102a、102b は、幅 $1 \sim 20 \mu\text{m}$ 、深さ $0.2 \sim 3 \mu\text{m}$  程度であることが好ましいが、スルーホールの使用形態に応じて、適宜変更することができる。30

#### 【0028】

また、第 1、第 2 の不純物領域 102a、102b の不純物としては、ホウ素、リン、砒素、アンチモン等を用いることができる。この中では、ホウ素が、KOH 等のアルカリ薬液に対して、低い不純物濃度でエッチング速度が変化するため望ましい。更に、第 1、第 2 の不純物領域 102a、102b の不純物が同一種であれば、エッチング速度の制御性が良くなるため望ましい。

#### 【0029】

また、第 1、第 2 の不純物領域 102a、102b の形成は、通常の半導体素子を形成する際の不純物拡散層形成工程において、同時に実施することも可能である。

#### 【0030】

また、第 2 の不純物領域 102b が第 1 の不純物領域 102a よりもシリコン基板 101 の第 1 の面（スルーホールの入口孔側）に近い位置にある方が、より低加速のイオン注入により容易に形成することができるので好ましい。このような配置により、基板表面での異方性エッチングによるサイドエッチングの進行が抑えられ、加工精度が向上する。しかしながら、第 1 の不純物領域 102a の少なくとも一部が、シリコン基板 101 の深さ方向において第 2 の不純物領域 102b と異なる位置に配置されていれば、第 2 の不純物領域 102b を補強することが可能である。従って、第 1 の不純物領域 102a 及び第 2 の不純物領域 102b のシリコン基板 101 の深さ方向における位置関係については、図 1 に示した配置のみに限定されない。40

#### 【0031】

10

20

30

40

50

また、第2の不純物領域102bがエッティング液に触れても、エッティングはほとんど進行しないが、第2の不純物領域102bの表面荒れが激しくなって、発塵の原因となりうる。そのため、第1の不純物領域102aの少なくとも一部が、第2の不純物領域102bよりも、スルーホールが形成される領域の近くに配置されていることが好ましい。この場合、異方性エッティングによって第1の不純物領域102aが先にエッティングされ、第2の不純物領域102bにエッティング液が触れる時間が短くてすみ、第2の不純物領域102bの表面荒れを抑えることができる。しかしながら、第1の不純物領域102aのシリコン基板101の表面に平行な位置については、図1に示した配置のみに限定されない。

## 【0032】

エッティングストップ層103とシリコン基板101との界面には、界面準位が形成され、また、加工等でダメージ層が形成されると、異方性エッティング時のサイドエッティングの進行が速くなる。この場合、第1、第2の不純物領域102a、102bを形成しても、効果が十分に現れない場合がある。従って、エッティングストップ層103と第1、第2の不純物領域102a、102bとの界面に、熱酸化膜を形成すると、サイドエッティングが抑制されるため好ましい。特に、サイドエッティングを抑える必要性がある第2の不純物領域102bの少なくとも一部が熱酸化膜と接しているとより効果的である。

## 【0033】

エッティングストップ層103は、エッティング液に対するエッティング速度が小さく、シリコン基板との十分な選択性があればよく、例えば、シリコン窒化膜、Ta等の様々な材料を選択することができる。特に、プラズマCVD酸化膜は、LSI製造工程でも一般的に用いられ、スルーホールとLSIで用いられる素子等とを同時に形成する場合に有効である。

## 【0034】

また、本実施形態に係るスルーホールの形成方法は、インク供給口を有するインクジェットヘッドに好適に用いられる。

## 【0035】

## (第2の実施形態)

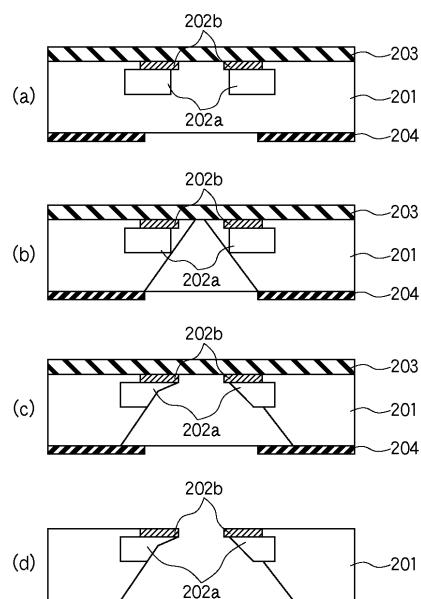

図2は、本発明の好適な第2の実施形態に係るスルーホールの形成方法を説明するための図である。第2の実施形態に係るスルーホールの形成方法は、第1の実施の形態に係るスルーホールの形成方法の一部を変更したものである。即ち、第1の実施形態では、第1の不純物領域102aの一部が第2の不純物領域102bと重なっていたが、第2の実施形態では、第1の不純物領域202aが第2の不純物領域202bと重ならずに配置されている。他の点については、第1の実施形態と同様であるため、図2では、図1(a)~(c)に対応する工程を省略し、図1(d)に対応する図2(a)から示している。

## 【0036】

図2(a)に示す工程では、<100>の結晶面方位を有するシリコン基板201(厚さ $625\mu m$ )に、幅 $4\mu m$ 、深さ $1\mu m$ 、厚さ $0.8\mu m$ の第1の不純物領域202aが内径 $101\mu m$ で形成されている。第1の不純物領域202aよりも基板表面に近い位置には、幅 $3\mu m$ 、深さ $0.2\mu m$ の第2の不純物領域202bが、内径 $100\mu m$ で形成されている。更に、エッティングストップ層203として、LPSiN膜が2500で成膜されている。第1の不純物領域202aの内側かつ基板の第1の面(スルーホールの入口孔側)に近い位置に配置された第2の不純物領域202bの上には、エッティングストップ層203が配置されている。第1の不純物領域202aには、不純物として $1\times 10^{18}cm^{-3}$ の濃度のホウ素(B)が拡散されている。また、第2の不純物領域202bには、不純物として $1\times 10^{19}cm^{-3}$ の濃度のホウ素(B)が拡散されている。シリコン基板201の第2の面(スルーホールの出口孔側)には、異方性エッティングのマスク204(例えば、SiO<sub>2</sub>、4000)が配置されている。

## 【0037】

図2(b)に示す工程では、シリコン基板201が異方性エッティングされる。例えば、基板全体を濃度22%のTMAH水溶液中に浸漬し、温度83で1000分間異方性工

10

20

30

40

50

ッチングが行われる。この条件でのエッチング速度は、約 39 ~ 40 μm / 時である。基板の表面は、TMAH 水溶液が回り込まないように、治具で保護されることが好ましい。異方性エッチングにより、シリコン基板 201 を貫通するスルーホールが形成されると、その形成幅は 80 ~ 95 μm となる。

#### 【0038】

図 2 (c) に示す工程では、シリコン基板 201 を更にオーバーエッチングするために、異方性エッチングを再度行う。例えば、異方性エッチングを 30 分間行うと、スルーホールの片側のサイドエッチング量は、約 5 μm / 時となる。オーバーエッチング時のサイドエッチングによりスルーホールは拡大するが、スルーホールの入口孔付近では、第 2 の不純物領域 202b によりエッチングが停止し、スルーホールの幅は 100 ~ 101 μm となる。10

#### 【0039】

図 2 (d) に示す工程では、エッチングストップ層 203 及びマスク 204 を適宜除去することによって、スルーホールが完成する。

#### 【0040】

なお、本実施形態では、シリコン基板のエッチング液として TMAH を用いたが、これに限定されず、例えば、KOHなどを用いることができる。

#### 【0041】

以上のように、本実施形態では、第 1 の実施形態よりも第 1 の不純物領域を基板深くに配置する。このような構成によって、第 2 の不純物領域の機械強度を第 1 の不純物領域で補強するとともに、スルーホールの入口孔から出口孔までの形状をより滑らかにすることができます。20

#### 【0042】

(第 3 の実施形態)

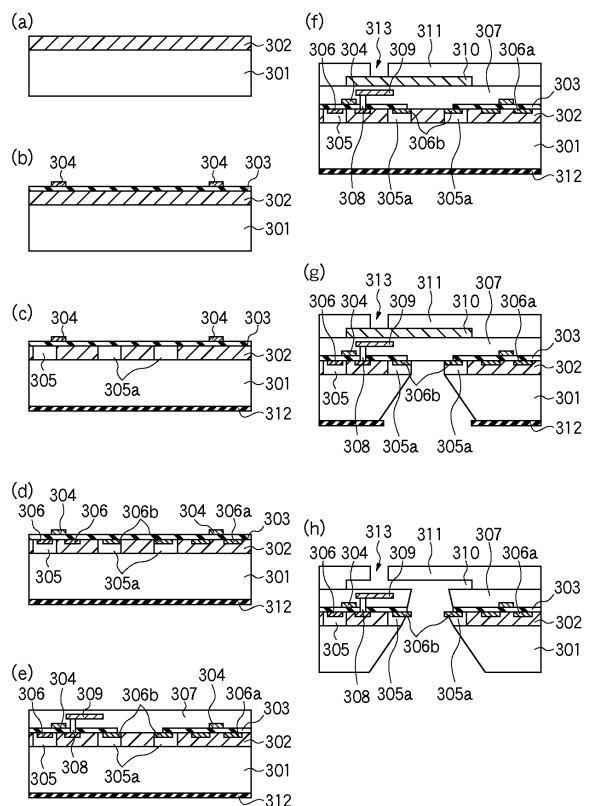

図 3 は、本発明の好適な第 3 の実施形態として、第 1、2 の実施形態に係るスルーホール形成方法をインクジェットヘッドのインク供給口の形成に適用した例を示す図である。図 3 に示すように、本実施形態に係るインクジェットヘッド用の基板には、概略的には、複数の電気熱変換体と、複数の電気熱変換体に電流を流すための複数のスイッチング素子とが集積化される。30

#### 【0043】

図 3 (a) に示す工程では、<100> の結晶面方位を有する p 型シリコン基板 301 (例えば、厚さ 625 μm) を準備し、n 型の不純物を選択的に導入して、p 型シリコン基板 301 の表面に n 型ウエル領域 302 を形成する。n 型ウエル領域 302 は、p 型シリコン基板 301 の全面に形成してもよい。n 型ウエル領域 302 を p 型シリコン基板 301 の全面に形成する場合には、エビタキシャル成長法を用いて n 型ウエル領域 302 を形成することができる。

#### 【0044】

図 3 (b) に示す工程では、厚さ約 50 nm のゲート酸化膜 (ゲート絶縁膜) 303 を形成し、ゲート酸化膜 303 上に、厚さ約 300 nm の多結晶シリコンを堆積させる。多結晶シリコンには、例えば、リンがドーピングされ、所望の配線抵抗値となっている。その後、周知のフォトリソグラフィ技術によってパターンを形成し、多結晶シリコン膜をエッチングする。これによって、MIS 型電界効果トランジスタのゲート電極 304 が形成される。40

#### 【0045】

図 3 (c) に示す工程では、周知のフォトリソグラフィ技術によってパターンを形成し、フォトレジストにより形成されたイオン注入用マスク (不図示) を形成する。また、ゲート電極 304 もイオン注入マスクとして使用し、選択的に p 型の不純物 (例えば、ホウ素) をイオン注入する。次いで、例えば 1100 、 60 分間の熱処理を行い、不純物領域 305 とスルーホールが形成される領域の周囲にある第 1 の不純物領域 305a とを形成する。また、この p 型の不純物のイオン注入の前後に熱酸化を行い、シリコン基板 30

50

1の第2の面(出口孔側)に、異方性エッティング用のマスク312(例えば、SiO<sub>2</sub>、4000)を形成する。不純物領域305は、素子や配線等を電気的に絶縁するための深さ2.2μm程度のベース領域である。このベース領域の濃度は、最表面で $1 \times 10^{-1}$  cm<sup>-3</sup>~ $1 \times 10^{-9}$  cm<sup>-3</sup>程度の範囲内にあることが好ましい。

#### 【0046】

図3(d)に示す工程では、ゲート電極304とフォトレジストとをマスクとして、例えば、ヒ素をイオン注入し、NSD領域306を形成する。また、ゲート電極304とフォトレジストとをマスクとして、例えば、ホウ素をイオン注入し、PSD領域306aとスルーホールの入口孔が形成される領域の周辺に第2の不純物領域306bとを形成する。その後、例えば950、30分の熱処理を行い、NSD領域306とPSD領域306aと不純物領域306bとを活性化する。

10

#### 【0047】

図3(e)に示す工程では、例えば、プラズマCVDにより酸化膜を堆積して、層間絶縁膜307を形成する。層間絶縁膜307は、エッティングトップ層としても機能する。次いで、コンタクト用のコンタクトホール308を開口し、導電体を堆積させて、パターニングすることにより配線を形成する。また、必要に応じて多層配線が行われる。また、電気熱変換素子309が、周知の薄膜形成工程により、p型シリコン基板301上に形成される。電気熱変換素子309としては、例えば、TaSiNを用いることができる。

#### 【0048】

図3(f)に示す工程では、インク流路の型となるポジ型レジスト310をp型シリコン基板301上にパターニングより形成する。次いで、ネガ型レジスト311をインク流路上に塗布し、パターニングによりインク吐出口313を形成する。

20

#### 【0049】

図3(g)に示す工程では、例えば、濃度22%のTMAH水溶液中に基板全体を浸漬し、例えば温度83で990分間、異方性エッティングを行う。基板の表面は、治具によりTMAH水溶液が回り込まないように保護されることが好ましい。図3(g)は、異方性エッティングが終了した時点における基板の断面形状を示している。

#### 【0050】

次いで、図3(h)に示す工程では、基板の表面を保護した状態で、シリコン基板301の第2の面(出口孔側)から、例えばHFを用いて、エッティングトップ層である層間絶縁膜307をエッティングする。これにより、スルーホールが完成する。次いで、インク流路となるポジ型レジスト310を除去する。その後、マスク312を適宜除去することによって、インクジェットヘッドが完成する。

30

#### 【0051】

上記のインクジェットヘッドが形成された全てのチップに対し、スルーホールの周辺のシリコンのクラックや異常を顕微鏡検査したところ、不良は発生していなかった。また、スルーホールの短手方向の幅を計測したところ、102~106μmの範囲内にあり、スルーホールが極めて精度良く形成されていた。

#### 【図面の簡単な説明】

#### 【0052】

【図1】本発明の好適な第1の実施形態に係るスルーホールの形成方法を説明するための図である。

【図2】本発明の好適な第2の実施形態に係るスルーホールの形成方法を説明するための図である。

【図3】本発明の好適な第3の実施形態に係るインクジェットヘッドのインク供給口形成に適用した例を示す図である。

#### 【図4】従来のスルーホールの形成方法を説明するための図である。

#### 【符号の説明】

#### 【0053】

101 シリコン基板

- 1 0 2 a 第1の不純物領域

1 0 2 b 第2の不純物領域

1 0 3 エッチングストップ層

1 0 4 エッチングマスク層

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(72)発明者 佐々木 圭一

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 早川 幸宏

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 数井 賢治

(56)参考文献 特開2004-034533(JP,A)

特開平10-260523(JP,A)

特開2001-205815(JP,A)

特開2003-133581(JP,A)

(58)調査した分野(Int.Cl., DB名)

B 41 J 2 / 16

B 41 J 2 / 05

H 01 L 21 / 306