(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2007년11월21일

(11) 등록번호 10-0777994

(24) 등록일자 2007년11월14일

(51) Int. Cl.

*H05K 3/12* (2006.01)

(21) 출원번호 10-2001-0028568

(22) 출원일자 2001년05월24일

심사청구일자 2006년04월17일

(65) 공개번호 10-2001-0107703

공개일자 2001년12월07일

(30) 우선권주장

09/578,424 2000년05월25일 미국(US)

(56) 선행기술조사문현

EP0955642 A

US5674596 A

전체 청구항 수 : 총 32 항

심사관 : 남정길

(54) 염격한 공차로 매입된 소자를 구비하는 인쇄 회로 기판형성 방법

**(57) 요 약**

본 발명은 임피던스 소자를 구비하고, 절연 지지체상에 소정 패턴의 임피던스 소자와 도체 패턴이 합체되어 있는 인쇄 회로 기판 형성 방법에 관한 것이다. 이 인쇄 회로 기판 형성 방법은 고전도성 재료 시트의 제1 표면에 임피던스 재료층을 성막하는 공정과, 고전도성 재료 시트의 제2 표면을 지지체에 부착하는 공정을 포함한다. 그 후, 임피던스 재료층에 포토레지스트층을 도포하고 화상에 따른 노출 및 현상을 행한다. 포토레지스트 재료의 제거된 비화상 영역 아래의 임피던스 재료층 부분을 에칭해 낸 후에, 고전도성 재료 시트 상에는 소정 패턴의 임피던스 소자가 남는다. 그러므로, 임피던스 소자를 구비하는 인쇄 회로 기판을 고정밀도의 전기적인 공차로서 제조할 수 있다.

**대표도** - 도9

## 특허청구의 범위

### 청구항 1

임피던스 소자를 구비하는 인쇄 회로 기판 형성 방법으로서,

- (a) 전기적으로 높은 전도성의 재료로 구성되는 고전도성 재료 시트의 제1 표면 상에 임피던스 재료층을 성막하고, 상기 고전도성 재료 시트의 제2 표면을 지지체에 부착하는 공정; 또는

- (b) 전기적으로 높은 전도성의 재료로 구성되는 고전도성 재료 시트의 제2 표면을 지지체에 부착하고, 상기 고전도성 재료 시트의 제1 표면 상에 임피던스 재료층을 성막하는 공정 중 어느 한 공정을 포함하고,

- (c) 상기 임피던스 재료층 상에 포토레지스트 재료층을 도포하는 공정과;

- (d) 상기 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

- (e) 포토레지스트 재료의 제거된 비화상 영역 아래에 있는 임피던스 재료층 부분을 에칭한 후에, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여 상기 고전도성 재료 시트 상에 소정 패턴의 임피던스 소자를 남기는 공정과;

- (f) 상기 고전도성 재료 시트를 관통하는 복수 개의 타겟 구멍을 형성하는 공정과;

- (g) 절연 재료 시트와 고전도성 재료 시트 사이에 임피던스 소자가 배치되도록 절연 재료 시트의 한쪽 면을 상기 고전도성 재료 시트에 부착하는 공정과;

- (h) 상기 고전도성 재료 시트로부터 지지체를 제거하는 공정과;

- (i) 상기 고전도성 재료 시트의 제2 표면 상에 추가적인 포토레지스트 재료층을 도포하는 공정과;

- (j) 상기 추가적인 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

- (k) 포토레지스트 재료의 제거된 비화상 영역 아래에 있는 상기 고전도성 재료 시트 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여 고전도성 재료로 구성되는 전도성 라인 중 일부 또는 전부가 임피던스 소자들 중 일부 또는 전부와 접촉하도록 소정 패턴의 전도성 라인을 남기는 공정

을 더 포함하는 것인 인쇄 회로 기판 형성 방법

### 청구항 2

제1항에 있어서,

- (l) 전기적으로 높은 전도성의 재료로 구성되는 제2 고전도성 재료 시트의 제1 표면 상에 제2 임피던스 재료층을 성막하고, 상기 제2 고전도성 재료 시트의 제2 표면을 제2 지지체에 부착하는 공정; 또는

- (m) 전기적으로 높은 전도성의 재료로 구성되는 제2 고전도성 재료 시트의 제2 표면을 제2 지지체에 부착하고, 상기 제2 고전도성 재료 시트의 제1 표면 상에 제2 임피던스 재료층을 성막하는 공정 중 어느 한 공정을 더 포함하고,

- (n) 제2 임피던스 재료층 상에 포토레지스트 재료층을 도포하는 공정과;

- (o) 포토레지스트 재료를 화상을 따라 노출시켜 화상 영역 및 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

- (p) 포토레지스트 재료의 제거된 비화상 영역 아래에 있는 제2 임피던스 재료층 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거함으로써, 제2 고전도성 재료 시트에 소정 패턴의 제2 임피던스 소자를 남기는 공정과;

- (q) 상기 제2 고전도성 재료 시트를 관통하는 복수 개의 타겟 구멍을 형성하는 공정과;

- (r) 절연 재료 시트와 상기 제2 고전도성 재료 시트 사이에 제2 임피던스 소자들이 배치되도록 상기 제2 고전도성 재료 시트를 상기 절연 재료 시트의 다른 쪽 면에 부착하는 공정과;

- (s) 상기 제2 고전도성 재료 시트로부터 제2 지지체를 제거하는 공정과;

- (t) 상기 제2 고전도성 재료 시트의 이면에 추가적인 포토레지스트 재료층을 도포하는 공정과;

- (u) 상기 추가적인 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

- (v) 포토레지스트 재료의 제거된 비화상 영역 아래에 있는 제2 고전도성 재료 시트 부분을 예칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거함으로써, 전기적으로 높은 전도성의 재료로 구성되는 제2 전도성 라인 중 일부 또는 전부가 제2 임피던스 소자 중 일부 또는 전부와 접촉하도록 소정 패턴의 제2 전도성 라인을 남기는 공정

을 더 포함하는 것인 인쇄 회로 기판 형성 방법.

### 청구항 3

제1항에 있어서, 상기 (e) 공정에서 포토레지스트 재료의 화상 영역의 제거를 수행하는 것인 인쇄 회로 기판 형성 방법.

### 청구항 4

제2항에 있어서, 상기 (v) 공정에서 포토레지스트 재료의 화상 영역의 제거를 수행하는 것인 인쇄 회로 기판 형성 방법.

### 청구항 5

제1항에 있어서, 상기 고전도성 재료는 구리, 니켈, 알루미늄, 금, 은, 황동 또는 스테인레스강인 것인 인쇄 회로 기판 형성 방법.

### 청구항 6

제1항에 있어서, 상기 임피던스 재료는 저항성 재료를 포함하는 것인 인쇄 회로 기판 형성 방법.

### 청구항 7

제6항에 있어서, 상기 저항성 재료는 니켈, 니켈 함유 합금, 반도체, 또는 1종 이상의 금속이나 금속 합금과 1종 이상의 절연체의 조합을 포함하는 것인 인쇄 회로 기판 형성 방법.

### 청구항 8

제6항에 있어서, 상기 저항성 재료는 25 내지 1000 오옴/스퀘어의 저항을 갖는 것인 인쇄 회로 기판 형성 방법.

### 청구항 9

제1항에 있어서, 상기 임피던스 재료는 용량성 재료를 포함하는 것인 인쇄 회로 기판 형성 방법.

### 청구항 10

제9항에 있어서, 상기 용량성 재료는 폴리머 재료, 금속 산화물, 반도체 재료 또는 이들의 조합을 포함하는 것인 인쇄 회로 기판 형성 방법.

### 청구항 11

제9항에 있어서, 상기 용량성 재료는  $0.01 \text{ 내지 } 3000 \text{ nF/cm}^2$ 의 용량을 갖는 것인 인쇄 회로 기판 형성 방법.

### 청구항 12

제1항에 있어서, 상기 지지체는 상기 고전도성 재료의 시트에 초음파 접합 가능한 재료를 포함하는 것인 인쇄 회로 기판 형성 방법.

### 청구항 13

제1항에 있어서, 상기 지지체는 상기 고전도성 재료 시트에 초음파 접합되는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 14

제1항에 있어서, 상기 지지체는 금속, 폴리머 또는 이들의 조합을 포함하는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 15

제1항에 있어서, 상기 지지체는 알루미늄을 포함하는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 16

제1항에 있어서, 상기 지지체는 스테인레스강을 포함하는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 17

제1항에 있어서, 상기 포토레지스트 재료는 액체로서 도포되는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 18

제1항에 있어서, 상기 포토레지스트 재료는 건조 박막으로서 도포되는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 19

제1항에 있어서, 상기 절연 재료 시트는 에폭시 또는 폴리이미드를 포함하는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 20

제1항에 있어서, 상기 절연 재료 시트는 열경화성 또는 열가소성 폴리머를 포함하는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 21

제1항에 있어서, 상기 임피던스 소자 중 일부 또는 전부는 이를 임피던스 소자의 다른 접점에서 2개 이상의 전도성 라인과 접촉하며, 상기 접점 사이의 간격은 0.025 mm 내지 100 mm 인 것인 인쇄 회로 기판 형성 방법.

#### 청구항 22

제1항에 있어서, 상기 고전도성 재료는 구리를 포함하고, 상기 임피던스 재료는 니켈 또는 니켈 합금을 포함하며, 상기 지지체는 알루미늄을 포함하는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 23

제1항에 있어서, 상기 고전도성 재료는 구리를 포함하고, 상기 임피던스 재료는 니켈 또는 니켈 합금을 포함하며, 상기 지지체는 알루미늄을 포함하고, 상기 절연 재료는 에폭시를 포함하며, 상기 제2 고전도성 재료는 구리를 포함하고, 상기 제2 임피던스 재료는 니켈 또는 니켈 합금을 포함하며, 상기 제2 지지체는 알루미늄을 포함하는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 24

제2항에 있어서, 상기 고전도성 재료는 구리를 포함하고, 상기 임피던스 재료는 니켈 또는 니켈 합금을 포함하며, 상기 지지체는 알루미늄을 포함하고, 상기 절연 재료는 에폭시를 포함하며, 상기 제2 고전도성 재료는 구리를 포함하고, 상기 제2 임피던스 재료는 니켈 또는 니켈 합금을 포함하며, 상기 제2 지지체는 알루미늄을 포함하는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 25

임피던스 소자를 구비하는 인쇄 회로 기판 형성 방법으로서,

(a) 전기적으로 높은 전도성의 재료로 구성되는 고전도성 재료 시트의 제1 표면 상에 소정 패턴의 임피던스 소자들을 성막하고, 상기 고전도성 재료 시트의 제2 표면을 지지체에 부착하는 공정; 또는

(b) 전기적으로 높은 전도성의 재료로 구성되는 고전도성 재료 시트의 제2 표면을 지지체에 부착하고, 상기 고

전도성 재료 시트의 제1 표면 상에 소정 패턴의 임피던스 소자들을 성막하는 공정 중 어느 한 공정을 포함하고,

- (c) 상기 고전도성 재료 시트를 관통하는 복수 개의 타겟 구멍을 형성하는 공정과;

- (d) 절연 재료 시트와 고전도성 재료 시트 사이에 임피던스 소자가 배치되도록 절연 재료 시트의 한쪽 면을 상기 고전도성 재료 시트에 부착하는 공정과;

- (e) 상기 고전도성 재료 시트로부터 지지체를 제거하는 공정과;

- (f) 상기 고전도성 재료 시트의 제2 표면 상에 포토레지스트 재료층을 도포하는 공정과;

- (g) 상기 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

- (h) 포토레지스트 재료의 제거된 비화상 영역 아래에 있는 고전도성 재료 시트 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여, 전기적으로 높은 전도성의 재료로 구성되는 전도성 라인 중 일부 또는 전부가 임피던스 소자들 중 일부 또는 전부와 접촉하도록 소정 패턴의 전도성 라인을 남기는 공정

을 더 포함하는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 26

제25항에 있어서,

- (i) 전기적으로 높은 전도성의 재료로 구성되는 제2 고전도성 재료 시트의 제1 표면 상에 소정 패턴의 제2 임피던스 소자들을 성막하고, 상기 제2 고전도성 재료 시트의 제2 표면을 제2 지지체에 부착하는 공정; 또는

- (j) 상기 전기적으로 높은 전도성의 재료로 구성되는 제2 고전도성 재료 시트의 제2 표면을 제2 지지체에 부착하고, 상기 제2 고전도성 재료 시트의 제1 표면 상에 소정 패턴의 제2 임피던스 소자들을 성막하는 공정 중 어느 한 공정을 더 포함하고,

- (k) 상기 제2 고전도성 재료 시트를 관통하는 복수 개의 타겟 구멍을 형성하는 공정과;

- (l) 절연 재료층과 제2 고전도성 재료 시트 사이에 제2 임피던스 소자가 배치되도록, 상기 제2 고전도성 재료 시트를 절연 재료 시트의 다른 쪽 면에 부착하는 공정과;

- (m) 상기 제2 고전도성 재료 시트로부터 제2 지지체를 제거하는 공정과;

- (n) 상기 제2 고전도성 재료 시트의 이면에 추가적인 포토레지스트 재료층을 도포하는 공정과;

- (o) 상기 추가적인 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

- (p) 포토레지스트 재료의 제거된 비화상 영역 아래에 있는 제2 고전도성 재료 시트 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여, 전기적으로 높은 전도성의 재료로 구성되는 제2 전도성 라인 중 일부 또는 전부가 제2 임피던스 소자들 중 일부 또는 전부와 접촉하도록 소정 패턴의 제2 전도성 라인을 남기는 공정

- 을 더 포함하는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 27

제25항에 있어서, 상기 임피던스 소자는 폴리머 잉크를 포함하는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 28

제25항에 있어서, 상기 임피던스 소자는 스크린 인쇄 공정에 의하여 성막되는 것인 인쇄 회로 기판 형성 방법.

#### 청구항 29

임피던스 소자를 구비하는 인쇄 회로 기판 형성 방법으로서,

- (a) 전기적으로 높은 전도성의 재료로 구성되는 고전도성 재료 시트의 제1 표면 상에 감광성 임피던스 재료층을 성막하고, 상기 고전도성 재료 시트의 제2 표면을 지지체에 부착하는 공정; 또는

- (b) 전기적으로 높은 전도성의 재료로 구성되는 고전도성 재료 시트의 제2 표면을 지지체에 부착하고, 상기 고전도성 재료 시트의 제1 표면 상에 감광성 임피던스 재료층을 성막하는 공정 중 어느 한 공정을 포함하고,

- (c) 상기 감광성 임피던스 재료를 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거함으로써, 상기 고전도성 재료 시트 상에 소정 패턴의 임피던스 소자를 남기는 공정과;

- (d) 상기 고전도성 재료 시트를 관통하는 복수 개의 타겟 구멍을 형성하는 공정과;

- (e) 절연 재료 시트와 고전도성 재료 시트 사이에 임피던스 소자가 배치되도록 절연 재료 시트의 한쪽 면을 상기 고전도성 재료 시트에 부착하는 공정과;

- (f) 상기 고전도성 재료 시트로부터 지지체를 제거하는 공정과;

- (g) 상기 고전도성 재료 시트의 제2 표면 상에 포토레지스트 재료층을 도포하는 공정과;

- (h) 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과,

- (i) 포토레지스트 재료의 제거된 비화상 영역 아래에 있는 고전도성 재료 시트 부분을 예칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여, 전기적으로 높은 전도성의 재료로 구성되는 전도성 라인 중 일부 또는 전부가 임피던스 소자 중 일부 또는 전부와 접촉하도록 소정 패턴의 전도성 라인을 남기는 공정을 더 포함하는 것인 인쇄 회로 기판 형성 방법.

### 청구항 30

제29항에 있어서,

- (j) 전기적으로 높은 전도성의 재료로 구성되는 제2 고전도성 재료 시트의 제1 표면 상에 제2 감광성 임피던스 재료층을 성막하고, 상기 제2 고전도성 재료 시트의 제2 표면을 제2 지지체에 부착하는 공정; 또는

- (k) 전기적으로 높은 전도성의 재료로 구성되는 제2 고전도성 재료 시트의 제2 표면을 제2 지지체에 부착하고, 상기 제2 고전도성 재료 시트의 제1 표면 상에 제2 감광성 임피던스 재료층을 성막하는 공정 중 어느 한 공정을 포함하고,

- (l) 상기 감광성 임피던스 재료를 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거함으로써, 상기 제2 고전도성 재료 시트 상에 소정 패턴의 제2 임피던스 소자를 남기는 공정과;

- (m) 상기 제2 고전도성 재료 시트를 관통하는 복수 개의 타겟 구멍을 형성하는 공정과;

- (n) 절연 재료층과 제2 고전도성 재료 시트 사이에 제2 임피던스 소자가 배치되도록 제2 고전도성 재료 시트를 절연 재료 시트의 다른 쪽 면에 부착하는 공정과;

- (o) 상기 제2 고전도성 재료 시트로부터 제2 지지체를 제거하는 공정과;

- (p) 상기 제2 고전도성 재료 시트의 이면에 포토레지스트 재료층을 도포하는 공정과;

- (q) 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과,

- (r) 포토레지스트 재료의 제거된 비화상 영역 아래에 있는 제2 고전도성 재료 시트 부분을 예칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여, 전기적으로 높은 전도성의 재료로 구성되는 제2 전도성 라인 중 일부 또는 전부가 제2 임피던스 소자 중 일부 또는 전부와 접촉하도록 소정 패턴의 제2 전도성 라인을 남기는 공정을 더 포함하는 것인 인쇄 회로 기판 형성 방법.

### 청구항 31

임피던스 소자를 구비하는 인쇄 회로 기판 형성 방법으로서,

- (a) 전기적으로 높은 전도성의 재료로 구성되는 고전도성 재료 시트의 제1 표면 상에 임피던스 재료층을 성막하는 공정과;

- (b) 전기적으로 높은 전도성의 재료로 구성되는 고전도성 재료 시트의 제2 표면을 지지체에 부착하는 공정과;

- (c) 상기 임피던스 재료층 상에 포토레지스트 재료층을 도포하는 공정과;

- (d) 상기 포토레지스트 재료를 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

- (e) 포토레지스트 재료의 제거된 비화상 영역 아래에 있는 임피던스 재료층 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여 상기 고전도성 재료 시트 상에 소정 패턴의 임피던스 소자를 남기는 공정

을 포함하고, 상기 (a) 및 (b) 공정은 서로 순서에 관계없이 수행되며,

상기 임피던스 재료는 용량이 0.01 내지 3000 nF/cm<sup>2</sup>인 용량성 재료와, 저항이 25 내지 1000 오옴/스퀘어인 저항성 재료와, 인덕턴스가 0.001 내지 1 헨리인 유도성 재료를 포함하는 것인 인쇄 회로 기판 형성 방법.

## 청구항 32

제1항에 있어서, 상기 절연 재료 시트는 보강된 열경화성 또는 열가소성 폴리머를 포함하는 것인 인쇄 회로 기판 형성 방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

<30>

#### 발명의 분야

<31>

본 발명은 임피던스 소자를 합체하는 인쇄 회로 기판에 관한 것으로서, 보다 구체적으로 말하면 절연 지지체상에 합체된 도체 패턴 및 소정 패턴의 임피던스 소자를 구비하는 인쇄 회로 기판에 관한 것이다. 이러한 방법으로, 임피던스 소자를 구비하는 인쇄 회로 기판을 고정밀도의 공차로 제조할 수 있다.

<32>

#### 관련 기술의 설명

<33>

인쇄 회로 기판을 제조하는 한 가지 종래의 방법에 있어서는, 절연 지지체에는 이 지지체의 전체 표면상에 저항층이 마련되고, 이 저항층상에 고전도성 재료층이 배치된다. 이 종래의 방법을 사용하면, 인쇄 회로 기판, 절연 영역, 저항 영역 및 도체 영역이 부(負) 마스크 에칭법(subtractive mask-etching method)에 의하여 형성된다. 다른 한 가지 종래 기술의 방법에 있어서는, 구리 포일과 같은 고전도성의 재료층을 제거가능한 마스킹 시트로 덮고, 전착에 의하여 상기 고전도성의 재료층의 다른 표면에 저항층을 형성함으로써 인쇄 회로 기판을 제조한다. 그 후, 마스킹 시트를 제거한 후에 절연 지지체를 저항층과 결합시킨다. 그 후, 구리 포일의 표면에 포토레지스트를 덮고, 도체 패턴과 레지스터 패턴을 함께 화상을 따라 노출시키며, 이들 패턴 영역에 포토레지스트가 남도록 현상한다. 포토레지스트가 덮이지 않은 영역의 구리 포일은 에칭에 의하여 제거되고, 노출된 저항층은 에칭 용액을 사용하여 제거하며, 그 결과 절연 지지체의 표면이 노출된다. 그 후, 남은 포토레지스트를 제거 용액을 사용하여 제거한다. 그 후, 기판에 다시 포토레지스트를 덮고, 도체 패턴을 갖는 사진 네거티브를 통해서 노출시키고, 도체 패턴 영역에 포토레지스트가 남도록 기판을 현상한다. 포토레지스트가 덮이지 않은 영역의 구리 포일은 에칭으로 제거되며, 그 결과 레지스터 패턴에 상응하는 저항층의 표면이 노출된다. 그 후, 제거 용액을 사용하여 나머지 포토레지스트를 제거한다. 레지스터 패턴 영역의 저항층에 인쇄에 의하여 납 정지제(solder stop-off) 등을 도포한 후 가열, 경화시켜 저항층을 덮음으로써 레지스터를 구비한 인쇄 회로 기판을 얻는다. 종래 기술의 방법의 문제는 저항층이 얇고 그것의 기계적 강도가 매우 낮다는 것이다. 따라서, 다수 회에 걸친 현상 공정이 시트 저항 및 다양한 다른 특성의 변동을 초래한다.

<34>

이러한 난점을 극복하기 위하여 다른 방법이 제안되었는데, 이 방법에서는, 회로 기판의 도체 패턴 영역을 금

도금 박막으로 보호하고, 최종 공정에서 레지스터 패턴 영역에 상응하는 구성을 갖는 구리 포일을 에칭으로 제거한다. 그러나, 당업자라면, 이러한 방법의 공정은 오히려 복잡하여 상당한 기술을 요한다는 것을 쉽게 이해할 것이다. 인쇄 회로 기판을 형성하는 다른 한 가지 방법이 미국 특허 제4,368,252호에 개시되어 있다. 이 기술은 구리 포일의 두 표면상의 예정된 위치에 레지스터 패턴 박막과 도체 패턴 박막을 형성한다. 절연 지지체를 고전도성 재료층상의 레지스터 패턴 박막과 직접적으로 또는 간접적으로 결합시킨다. 전술한 바로부터 명백한 바와 같이, 종래의 인쇄 회로 기판 처리 기술은 대단한 많은 횟수의 복잡한 처리 공정을 비롯한 여러 가지 단점을 내포하고 있다. 그러므로, 처리에 비교적 긴 시간을 요하고, 제조비가 비싸며, 수율이 제한되고, 부자재가 비싸다. 아울러, 저항성 포일을 사용하여 제조되는 매입 레지스터는 너무 높은, 즉 필요치의 ±10% 정도의 전기적인 공차를 갖는다. 이러한 변동의 상당 부분은 보다 엄격한 공차 내에서의 레지스터 패턴의 분해능 결여에 기인한다.

### 발명이 이루고자 하는 기술적 과제

&lt;35&gt;

본 발명은 전술한 문제점을 해결한다. 본 발명에 따르면, 전기적으로 높은 전도성 재료로 이루어지고 지지체에 부착되는 고전도성 재료 시트상에 미리 임피던스 소자가 형성된 인쇄 회로 기판이 제조된다. 임피던스 소자를 구비한 전도성 재료 시트에는 임피던스 소자 사이에 절연 시트가 적용된다. 전도성 재료 시트로부터 지지체를 제거한 후에, 고전도성 재료 시트를 에칭하여 고전도성 라인 중 적어도 일부가 임피던스 소자들 중 적어도 일부와 접촉하도록 소정의 패턴의 전도성 라인을 형성한다. 선택적으로는, 절연 시트의 대향측 면에 다른 한 가지 패턴의 임피던스 소자와 전도성 라인이 형성된다. 그 결과, 절연 시트상에는 훨씬 개선된 전기적 공차를 갖는 임피던스 소자가 형성된다.

### 발명의 구성 및 작용

&lt;36&gt;

본 발명은 임피던스 소자를 구비한 인쇄 회로 기판 형성 방법으로서,

&lt;37&gt;

(a) 전기적으로 높은 전도성의 재료로 구성된 고전도성 재료 시트의 제1 표면상에 임피던스 재료층을 성막(成膜)하는 공정과;

&lt;38&gt;

(b) 상기 고전도성 재료 시트의 제2 표면을 지지체에 부착하는 공정과;

&lt;39&gt;

(c) 상기 임피던스 재료층상에 포토레지스트 재료층을 도포하는 공정과;

&lt;40&gt;

(d) 상기 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

&lt;41&gt;

(e) 포토레지스트 재료의 제거된 비화상 영역 아래의 임피던스 재료 부분을 에칭한 후에, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여 상기 고전도성 재료 시트상에 소정 패턴의 임피던스 소자를 남기는 공정

&lt;42&gt;

을 포함하며, 상기 (a) 공정과 (b) 공정은 서로 순서에 관계없이 수행하는 인쇄 회로 기판 형성 방법을 제공한다.

&lt;43&gt;

바람직하기로, 상기 인쇄 회로 기판 형성 방법은

&lt;44&gt;

(f) 고전도성 재료 시트를 판통하여 복수 개의 타겟 구멍(target holes)을 형성하는 공정과;

&lt;45&gt;

(g) 절연 재료 시트와 고전도성 재료 시트 사이에 임피던스 소자가 배치되도록 절연 재료 시트의 한 쪽 면을 상기 고전도성 재료 시트에 부착하는 공정과;

&lt;46&gt;

(h) 상기 고전도성 재료 시트로부터 지지체를 제거하는 공정과;

&lt;47&gt;

(i) 상기 고전도성 재료 시트의 제2 표면에 추가적인 포토레지스트 재료층을 도포하는 공정과;

&lt;48&gt;

(j) 상기 추가적인 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

&lt;49&gt;

(k) 포토레지스트 재료의 제거된 비화상 영역 아래의 고전도성 재료 시트 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여 고전도성 재료로 이루어진 전도성 라인 중 적어도 일부가 임피던스 소자들 중 적어도 일부와 접촉하도록 소정 패턴의 전도성 라인을 남기는 공정

&lt;50&gt;

을 더 포함한다.

- <51> 더욱 바람직하기로, 상기 기판 회로 형성 방법은

- <52> (1) 제2 고전도성 재료 시트의 제1 표면에 제2 임피던스 재료층을 성막하는 공정과;

- <53> (m) 상기 제2 고전도성 재료 시트의 제2 표면을 지지체에 부착하는 공정과;

- <54> (n) 상기 제2 임피던스 재료층에 포토레지스트 재료층을 도포하는 공정과;

- <55> (o) 상기 포토레지스트 재료를 화상을 따라 노출시켜 화상 영역 및 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

- <56> (p) 포토레지스트 재료의 제거된 비화상 영역 아래의 제2 임피던스 재료층 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거함으로써, 제2 고전도성 재료 시트에 소정 패턴의 제2 임피던스 소자를 남기는 공정과;

- <57> (q) 상기 제2 고전도성 재료 시트를 관통하여 복수 개의 타겟 구멍을 형성하는 공정과;

- <58> (r) 상기 제2 임피던스 소자들이 상기 절연 재료층과 상기 제2 고전도성 재료 시트 사이에 있도록 상기 제2 고전도성 재료 시트를 상기 절연 재료 시트의 다른 쪽 면에 부착하는 공정과;

- <59> (s) 상기 제2 고전도성 재료 시트로부터 제2 지지체를 제거하는 공정과;

- <60> (t) 상기 제2 고전도성 재료 시트의 이면에 추가적인 포토레지스트 재료층을 도포하는 공정과;

- <61> (u) 상기 추가적인 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

- <62> (v) 포토레지스트 재료의 제거된 비화상 영역 아래의 제2 고전도성 재료 시트 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거함으로써, 고전도성 재료로 이루어지는 제2 전도성 라인 중 적어도 일부가 제2 임피던스 소자 중 적어도 일부와 접촉하도록 소정 패턴의 제2 전도성 라인을 남기는 공정

- <63> 을 더 포함하고, 상기 (1) 공정과 (m) 공정을 서로 순서에 관계없이 행할 수 있다.

- <64> 본 발명의 다른 한 가지 실시예는,

- <65> (a) 전기적으로 고전도성의 재료로 구성된 고전도성 재료 시트의 제1 표면상에 소정 패턴의 임피던스 소자들을 성막하는 공정과;

- <66> (b) 상기 고전도성 재료 시트의 제2 표면을 지지체에 부착하는 공정과;

- <67> (c) 상기 고전도성 재료 시트를 관통하여 복수 개의 타겟 구멍을 형성하는 공정과;

- <68> (d) 절연 재료 시트와 고전도성 재료 시트 사이에 임피던스 소자가 배치되도록 절연 재료 시트의 한 쪽 면을 상기 고전도성 재료 시트에 부착하는 공정과;

- <69> (e) 상기 고전도성 재료 시트로부터 지지체를 제거하는 공정과;

- <70> (f) 상기 고전도성 재료 시트의 제2 표면상에 포토레지스트 재료층을 도포하는 공정과;

- <71> (g) 상기 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

- <72> (h) 포토레지스트 재료의 제거된 비화상 영역 아래의 고전도성 재료 시트 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여 고전도성 재료로 구성되는 전도성 라인 중 적어도 일부가 임피던스 소자들 중 적어도 일부와 접촉하도록 소정 패턴의 전도성 라인을 남기는 공정

- <73> 을 포함하고, 상기 (a) 공정과 (b) 공정은 서로 순서에 관계없이 수행하는 인쇄 회로 기판 형성 방법을 제공한다.

- <74> 바람직하기로, 이 실시예는

- <75> (i) 제2 고전도성 재료 시트의 제1 표면상에 소정 패턴의 제2 임피던스 소자들을 성막하는 공정과;

- <76> (j) 상기 제2 고전도성 재료 시트의 제2 표면을 제2 지지체에 부착하는 공정과;

- <77> (k) 상기 제2 고전도성 재료 시트를 관통하여 복수 개의 타겟 구멍을 형성하는 공정과;

- <78> (l) 절연 재료 시트와 제2 고전도성 재료 시트 사이에 제2 임피던스 소자가 배치되도록, 절연 재료 시트의 다른 쪽 면을 상기 제2 고전도성 재료 시트에 부착하는 공정과;

- <79> (m) 상기 제2 고전도성 재료 시트로부터 제2 지지체를 제거하는 공정과;

- <80> (n) 상기 제2 고전도성 재료 시트의 제2 표면상에 추가적인 포토레지스트 재료층을 도포하는 공정과;

- <81> (o) 상기 추가적인 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

- <82> (p) 포토레지스트 재료의 제거된 비화상 영역 아래의 제2 고전도성 재료 시트 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여, 고전도성 재료로 구성된 제2 전도성 라인 중 적어도 일부가 제2 임피던스 소자들 중 적어도 일부와 접촉하도록 소정 패턴의 제2 전도성 라인을 남기는 공정을 포함하고, 상기 (i) 공정과 (j) 공정은 서로 순서에 관계없이 수행하는 인쇄 회로 기판 형성 방법을 제공한다.

- <84> 본 발명의 제3 실시예는,

- <85> (a) 전기적으로 높은 전도성의 재료로 구성된 고전도성 재료 시트의 제1 표면상에 감광성 임피던스 재료층을 성막하는 공정과;

- <86> (b) 상기 고전도성 재료 시트의 제2 표면을 지지체에 부착하는 공정과;

- <87> (c) 상기 감광성 임피던스 재료를 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거함으로써, 상기 고전도성 재료 시트상에 소정 패턴의 임피던스 소자를 남기는 공정과;

- <88> (d) 상기 고전도성 재료 시트를 관통하여 복수 개의 타겟 구멍을 형성하는 공정과;

- <89> (e) 절연 재료 시트와 고전도성 재료 시트 사이에 임피던스 소자가 배치되도록 절연 재료 시트의 한 쪽 면을 상기 고전도성 재료 시트에 부착하는 공정과;

- <90> (f) 고전도성 재료 시트로부터 지지체를 제거하는 공정과;

- <91> (g) 상기 고전도성 재료 시트의 제2 표면상에 포토레지스트 재료층을 도포하는 공정과;

- <92> (h) 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과,

- <93> (i) 포토레지스트 재료의 제거된 비화상 영역 아래의 고전도성 재료층 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여, 고전도성 재료로 구성되는 전도성 라인 중 적어도 일부가 임피던스 소자 중 적어도 일부와 접촉하도록 소정 패턴의 전도성 라인을 남기는 공정을 포함하며, 상기 (a) 공정과 (b) 공정은 서로 순서에 관계없이 수행하는 인쇄 회로 기판 형성 방법을 제공한다.

- <95> 바람직하기로, 이 실시예는,

- <96> (j) 전기적으로 높은 전도성의 재료로 구성된 제2 고전도성 재료 시트의 제1 표면상에 제2 감광성 임피던스 재료층을 성막하는 공정과;

- <97> (k) 상기 제2 고전도성 재료 시트의 제2 표면을 제2 지지체에 부착하는 공정과;

- <98> (l) 상기 감광성 임피던스 재료를 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거함으로써, 상기 제2 고전도성 재료 시트상에 소정 패턴의 제2 임피던스 소자를 남기는 공정과;

- <99> (m) 상기 제2 고전도성 재료 시트를 관통하여 복수 개의 타겟 구멍을 형성하는 공정과;

- <100> (n) 절연 재료 시트와 제2 고전도성 재료 시트 사이에 제2 임피던스 소자가 배치되도록 절연 재료 시트의 다른 쪽 면을 상기 제2 고전도성 재료 시트에 부착하는 공정과;

- <101> (o) 상기 제2 고전도성 재료 시트로부터 제2 지지체를 제거하는 공정과;

- <102> (p) 상기 제2 고전도성 재료 시트의 이면에 포토레지스트 재료층을 도포하는 공정과;

- <103> (q) 포토레지스트 재료층을 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음, 화상 영역을 유지시키면서 비화상 영역을 제거하는 공정과;

- <104> (r) 포토레지스트 재료의 제거된 비화상 영역 아래의 제2 고전도성 재료층 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 선택적으로 제거하여, 고전도성 재료로 구성되는 제2 전도성 라인 중 적어도 일부가 제2 임피던스 소자 중 적어도 일부와 접촉하도록 소정 패턴의 제2 전도성 라인을 남기는 공정

- <105> 을 더 포함하며, 상기 (j) 공정과 (k) 공정은 서로 순서에 관계없이 수행하는 인쇄 회로 기판 형성 방법을 제공한다.

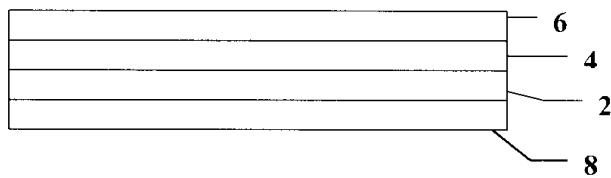

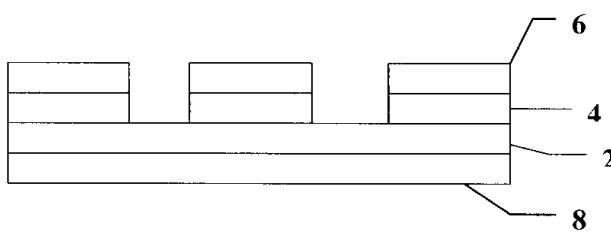

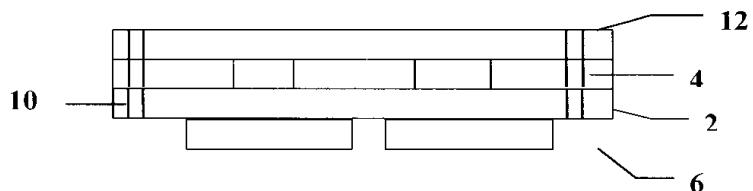

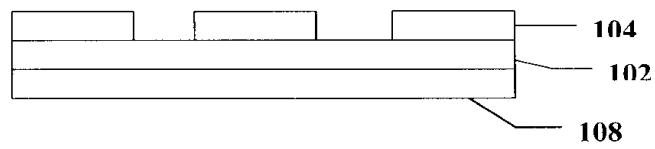

- <106> 도 1은 인쇄 회로 기판을 형성하는 방법의 제1 공정을 보여준다. 이 제1 공정은 고전도성 재료 시트(2)의 제1 표면상에 임피던스 재료층(4)을 성막하고, 다음에 고전도성 재료 시트(2)의 제2 표면을 지지체(8)에 부착하는 것을 포함한다. 그 후, 임피던스 재료층(4)상에 포토레지스트 재료층(6)을 도포한다. 모든 도면은 실제의 치수로 도시한 것은 아니다.

- <107> 한정하는 것은 아니지만, 고전도성 재료로 적합한 재료로는, 구리, 알루미늄, 니켈, 황동, 금, 은, 스테인레스강, 주석, 아연 또는 이들의 조합으로 구성되는 포일이 있다. 이들 재료의 포일은 두께가 약 12  $\mu\text{m}$  내지 35  $\mu\text{m}$ 인 것이 바람직하다.

- <108> 임피던스 재료는 전도성 재료 상에 레지스터를 성막하기 위한 저항성 재료인 것이 바람직하지만, 트랜지스터나 다른 미소 전자 디바이스를 형성하기 위하여 용량성, 유도성 또는 활성 재료를 포함해도 된다. 전형적으로, 이것들은 두께가 약 100 nm 내지 약 1000 nm이다. 저항성 재료는, 니켈, 니켈 함유 합금, 반도체, 적어도 한 종류의 금속 또는 금속 합금과 적어도 한 종류의 절연체의 조합을 포함해도 된다. 저항성 재료는 약 25 내지 1000 옴/스퀘어의 저항을 갖는 것이 바람직하다. 적합한 용량성 재료는 폴리머 재료, 금속 산화물, 반도체 재료, 또는 이들의 조합을 포함한다. 용량성 재료는 약 0.01 내지 3000  $\text{nF}/\text{cm}^2$ 의 용량을 가지는 것이 바람직하며, 약 0.5 내지 2000  $\text{nF}/\text{cm}^2$ 의 용량을 가지는 것이 더욱 바람직하다. 한정하는 것은 아니지만, 적합한 유도성 재료로는, Honeywell Amorphous Metals로부터 제품 2605 SA1로서 입수할 수 있는 철, 붕소 및 실리카의 복합체와 같은 비정질 금속과, 역시 Honeywell Amorphous Metals로부터 입수할 수 있는 코발트, 철, 붕소 및 실리카의 복합체인 제품 2714 A가 있다. 이들 제품은 용해된 금속을 급냉된 드럼에 쏟아 부어 그 재료들을 신속하게 냉각시킴으로써, 결과적으로 비정질 상태로 남게 하여 제조된다. 유도성 재료는 도금, 스터터링 또는 증착과 같은 기술에 의하여 전도성 재료상에 성막된다. 유도성 재료는 약 0.001 내지 1 헨리의 인덕턴스를 갖는 것이 바람직하다.

- <109> 지지체는 금속, 폴리머, 또는 이들의 조합을 포함할 수 있다. 적합한 재료로는, 한정하는 것은 아니지만, 알루미늄 및 스테인레스강이 있다. 그러한 지지체는 두께가 약 0.12 mm 내지 약 0.51 mm인 것이 바람직하다.

- <110> 지지체는 고전도성 재료 시트에 초음파 접합될 수 있는 재료를 포함하는 것이 바람직하다. 가장 바람직하기로, 지지체는 본 명세서에서 참고로 인용되는 미국 특허 제5,942,314호에 개시된 기술에 의하여 고전도성 재료 시트에 초음파 접합 또는 용착된다. 초음파 접합의 이점은 접합시 화학적 또는 열적인 작용에 견디는 능력이다. 이는 임피던스 재료를 적용하고 처리하는 기술을 사용할 수 있게 한다.

- <111> 포토레지스트는 포지티브 작용을 하는 것이거나 또는 네가티브 작용을 하는 것으로서, 액체 또는 건조 박막일 수 있다. 네가티브 작용 포토레지스트 조성물이 화상을 따라 방사광(radiation)에 노출되면, 방사광에 노출된 영역은 현상 용액에 대하여 용해성이 더 낮아지는 반면에, 포토레지스트의 비노출 영역은 현상 용액에 대하여 비교적 용해성으로 유지된다. 그러므로, 노출된 네가티브 작용 포토레지스트를 현상제로 처리하면, 포토레지스트 괴막의 비노출 영역이 제거되어 위에 포토레지스트 조성물이 성막되었던 하부 기판 표면의 필요한 부분을 노출시킨다. 포지티브 작용 조성물이 화상을 따라 방사광에 노출되는 경우, 방사광에 노출된 영역은 현상제 용액에 대하여 더 용해성이 커지는 반면, 노출되지 않은 영역은 현상제 용액에 대하여 비교적 비용해성으로 남는다. 그러므로, 포지티브 작용 포토레지스트를 현상제로 처리하면, 포토레지스트의 노출된 영역이 제거되어 포토레지스트 괴막에 양화(陽畫)를 남긴다. 어떤 경우든, 하부 기판 표면의 필요한 부분은 노출된 채 남는다. 포지티브 작용 포토레지스트 조성물은 네가티브 작용 포토레지스트보다 선호되는데, 그 이유는 전자가 후자보다는 일반적으로 더 양호한 해상도를 갖기 때문이다. 적합한 포토레지스트 조성물은 노볼락(novolak) 또는 폴리(4-히

드록시스티렌)과 같은 수성 알카리 용해성 또는 팽창성 결합제 수지와 o-퀴논 디아지드의 혼합물을 포함할 수 있다. 적합한 포토레지스트는 미국 특허 제4,692,398호, 제4,835,086호, 제4,863,827호 및 제4,892,801호에 개시되어 있다. 적합한 포토레지스트는 뉴저지, 섬버빌에 소재하는 Clariant Corporation으로부터 AZ-4620 및 AZ-111로서 상업적으로 구입할 수 있다.

<112> 본 발명의 방법에 있어서는, 전술한 감광성 조성물을 적합한 기판상에 피복하고 건조시킨다. 준비된 포토레지스트 용액을, 침지, 분사, 롤러 피복, 회전 피복 및 스펀 피복을 비롯한 포토레지스트 기술 분야에서 사용되는 어떤 종래의 방법으로 기판에 도포할 수 있다. 예를 들면, 스펀 피복의 경우, 소정 타입의 스피닝 장치가 사용되고 스피닝 공정을 위한 충분한 시간이 허용된다면, 원하는 두께의 피막을 제공하기 위하여 포토레지스트 용액을 고체 함량과 관련하여 조절할 수 있다. 본 발명의 바람직한 실시예에 있어서, 포토레지스트층은 액체 포토레지스트 조성물을 약 500 내지 6000 rpm, 바람직하게는 약 1500 내지 4000 rpm 범위의 회전 속도의 회전 훌의 상부 표면에, 약 5 내지 60초, 바람직하기로는 약 10 내지 30초 동안 적용하여, 포토레지스트 조성물이 상부 표면을 가로질러 균등하게 퍼지도록 함으로써 형성된다. 포토레지스트 층의 두께는 적용되는 액체 포토레지스트 조성물의 양에 따라 달라질 수 있지만, 그 두께는 대개 약 500 Å 내지 약 50,000 Å 범위, 바람직하기로는 약 2000 Å 내지 약 12,000 Å 범위일 수 있다. 적용되는 포토레지스트 조성물의 양은 기판의 치수에 따라서 약 1 mL 내지 10 mL, 바람직하기로는 약 2 mL 내지 8 mL 까지 변동될 수 있다.

<113> 포토레지스트 조성물 용액이 기판에 피복된 후에는, 기판을 약 20 °C 내지 200 °C 의 온도에서 처리한다. 이러한 온도 처리는 감광제의 열에 의한 실질적인 열화(劣化)를 초래하지 않고 포토레지스트 중의 잔류 용매의 농도를 감소 및 조절하기 위하여 수행된다. 일반적으로, 용매의 농도를 최소화하는 것이 요망되며, 따라서 이러한 온도 처리는 실질적으로 모든 용매가 증발되고 미크론 두께 범위의 얇은 포토레지스트 조성물 피막이 기판에 남을 때까지 수행된다. 바람직한 실시예에 있어서, 온도 처리는 약 50 °C 내지 150 °C에서 행해진다. 보다 바람직한 범위는 약 70 °C 내지 90 °C 이다. 이러한 처리는 용매 제거 변화율이 비교적 미미해 질 때까지 수행된다. 온도 및 시간의 선택은 사용되는 장치 및 상업적으로 필요한 피복 시간은 물론 사용자가 원하는 포토레지스트의 성질에 좌우된다. 핫 플레이트 처리(hot plate treatment)를 위한 상업적으로 허용 가능한 처리 시간은 약 3분, 더 바람직하기로는 약 1분까지이다. 한 가지 예에 있어서, 90 °C에서 30초간의 처리가 유용하다. 처리 시간은 이러한 온도의 컨벡션 오븐(convective oven)에서 수행되는 경우, 약 20 내지 40분까지 연장된다.

<114> 포토레지스트층은 기판상에 성막된 후에, 가령 ArF 레이저를 매개로 또는 에칭 마스크를 통해서 화상을 따라 화학성 방사광(actine radiation)에 노출된다. 이러한 노출은 포토레지스트의 화상 영역과 비화상 영역 사이에 화상에 따른 차이를 초래한다. 비화상 영역은 그 후에 현상 용액중에서 용해된다. 바람직하기로는, 화상을 따라 노출된 포토레지스트층 부분이 현상제중에서 용해가능하도록 하기에 충분한 양의 UV 방사광이 사용된다. UV 노출 선량은 바람직하게는 약 5 mJ/cm<sup>2</sup> 내지 약 300 mJ/cm<sup>2</sup>, 더 바람직하게는 약 5 mJ/cm<sup>2</sup> 내지 약 100 mJ/cm<sup>2</sup>, 더욱 더 바람직하기로는 10 mJ/cm<sup>2</sup> 내지 약 30 mJ/cm<sup>2</sup> 범위이다.

<115> 현상 공정은 적절한 현상 용액에 침지시키는 방법으로 행할 수 있다. 이 용액은 예컨대 질소 방출 교반(nitrogen burst agitation)에 의하여 교반되는 것이 바람직하다. 기판은 모든, 또는 거의 모든 포토레지스트 피막이 방사된 영역으로부터 용해될 때까지 현상제중에 유지될 수 있다. 현상제로서 적합한 수성 알칼라인 용액의 대표적인 예는 수산화나트륨, 수산화테트라메틸암모늄, 또는 수산화칼륨과 같은 주기율표의 I 족 및 II 족에 속하는 금속의 수산화물의 수용액을 포함한다. 수산화테트라알킬암모늄과 같이 금속 이온이 유리된 유기 염기, 예를 들면 수산화 테트라메틸암모늄(TMAH), 수산화테트라에틸암모늄(TEAH) 및 수산화테트라부틸암모늄(TBAH)가 바람직하며, 수산화테트라메틸암모늄(TMAH)이 더 바람직하다. 또한, 필요하다면, 현상제로 사용되는 염기 수용액은 최종 현상 효과를 개선하기 위하여 표면 활성제와 같은 어떤 부가제를 추가로 함유할 수 있다.

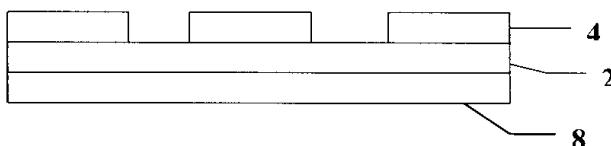

<116> 도 2는 포토레지스트 재료를 화상을 따라 노출시켜 화상 영역과 비화상 영역을 형성한 다음 화상 영역을 유지시키면서 비화상 영역을 제거한 후의 결과를 보여준다. 그 후, 포토레지스트 재료의 제거된 비화상 영역 아래의 임피던스 재료층 부분이 예칭되어, 도 3에 도시된 바와 같이 고전도성 재료 시트(6)상에 소정 패턴의 임피던스 소자를 남긴다. 임피던스 재료의 예칭은 임피던스 재료를 예칭액과 접촉시킴으로써 행할 수 있는데, 이는 수평 또는 수직의 컨베이어화된 스프레이형 장치에 의해 행해질 수 있다. 임피던스 재료를 견식으로 예칭하기 위하여 플라스마 시스템을 사용할 수도 있다. 도 3에서는, 남은 포토레지스트가 제거되었으며, 도 4에서는 남은 포토레지스트가 제거되지 않았다.

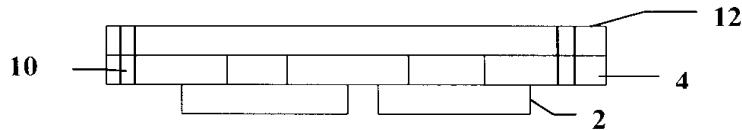

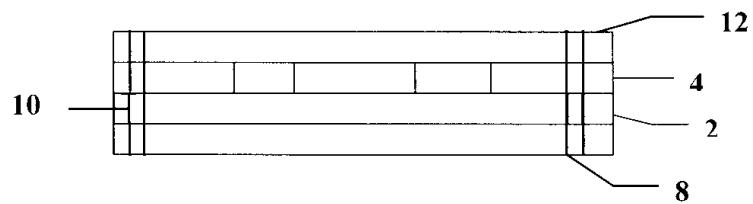

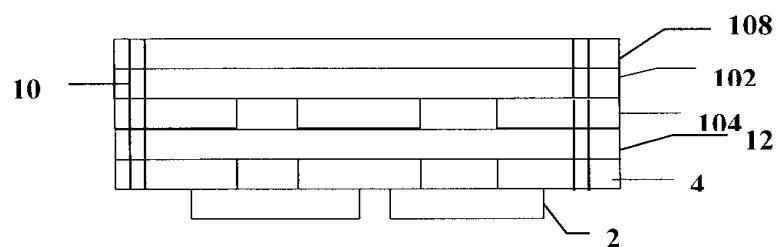

<117> 그 후, 절연 재료 시트(12)의 한 쪽 면을 고전도성 시트에 부착하여, 절연 재료 시트(12)와 고전도성 재료 시트(2) 사이에 임피던스 소자가 위치하게 한다. 도 5에 도시된 바와 같은 본 발명의 바람직한 실시예에 있어서는, 그 후에 고전도성 재료 시트(2), 지지체(8), 절연 재료 시트(12) 및 임의의 몇 개의 임피던스 소자(4)를 관통하여 2개 이상의 타겟 또는 가이드 구멍(10)을 천공하는데, 이 구멍은 임피던스 재료의 패턴을 차후에 형성되는 금속 라인들과 일치시키는 것을 용이하게 하는 작용을 한다.

<118> 절연 재료 시트는 보강이 있거나 또는 없는 열경화성 또는 열가소성 폴리머를 포함할 수 있다. 적합한 절연 재료는 에폭시 수지-유리 적물, 폴리에스터-유리 적물, 폴리이미드-유리 적물, 폴리아미도이미드-유리 적물, 페놀수지-종이 및 에폭시 수지-종이; 폴리이미드; 폴리에스터; 폴리아미도이미드; 그리고 가요성 에폭시 수지-유리 적물 또는 가요성 폴리아미드-종이로 형성된 가요성 절연 시트로 제조되는 적층 구조체이다. 에폭시 수지, 폴리에스터, 폴리우레탄, 폴리아미드이미드, 폴리이미드 및 고무와 같은 수지류 및 고무류가 접착층으로 채용되는 세라믹 판 및 유리 판과 같은 무기 재료도 또한 절연 재료로서 채용될 수 있다. 절연 재료 시트는 에폭시 또는 폴리이미드를 포함하는 것이 바람직하다.

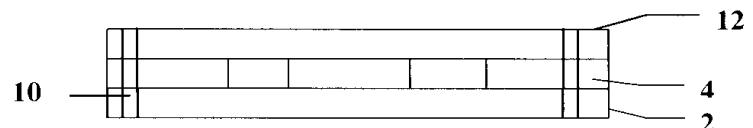

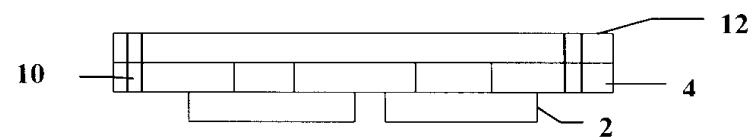

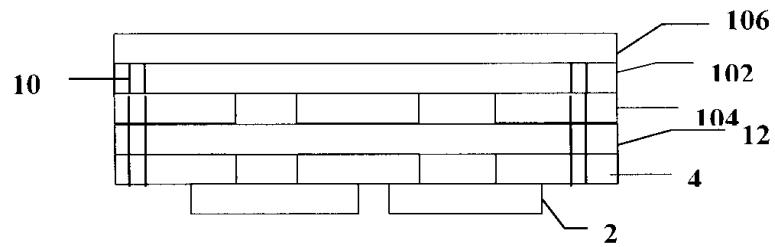

<119> 그 후, 지지체(8)가 제거되어, 결과적으로 도 6에 도시된 구성을 형성한다. 그 후, 고전도성 재료 시트의 이면에는 도 7에 도시되어 있는 바와 같이 다른 한 층의 포토레지스트 재료층(6)이 도포된다. 이 포토레지스트 재료층은 그 후에 전술한 것과 유사한 방법으로 노출 및 현상되어, 도 8에 도시된 구조를 형성한다. 그 후, 포토레지스트 재료의 제거된 비화상 영역 아래의 고전도성 재료 시트 부분을 에칭한 다음, 포토레지스트 재료의 화상 영역을 임의로 제거하여, 도 9에 도시된 바와 같이 고전도성 재료로 구성된 전도성 라인 중 적어도 일부가 임피던스 소자들 중 적어도 일부와 접촉하도록 소정 패턴의 전도성 라인을 남긴다. 고전도성 재료층의 에칭 용액으로는, 잘 알려진 에칭 용액을 사용할 수 있다. 예를 들면, 구리 포일의 경우, 그 에칭 용액은 염화제2철, 과황산화암모늄, 염화구리, 크롬산 황산 혼합물 용액일 수 있으며, 임피던스 재료의 내식성을 고려하여 암모니아 퀄레이트 타입의 다양한 형태의 에칭 용액이 사용된다. 전도성 라인은, 임피던스 소자들 중 적어도 일부가 임피던스 소자의 다른 접점에서 적어도 2개의 전도성 라인과 접촉하고, 접점들 사이의 간격이 액 0.025 mm 내지 100 mm가 되도록 형성된다.

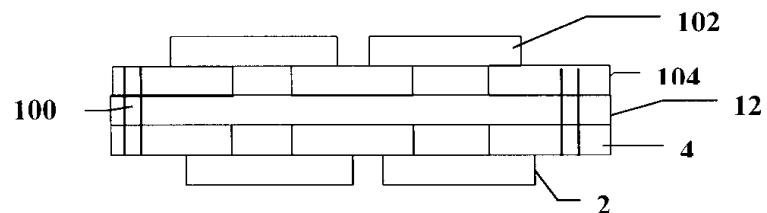

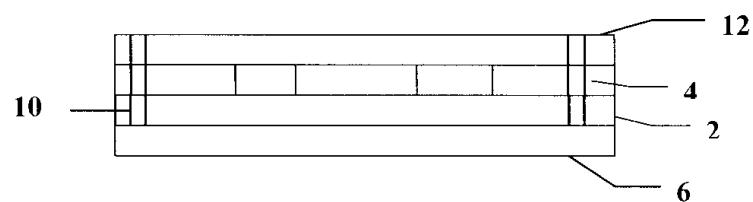

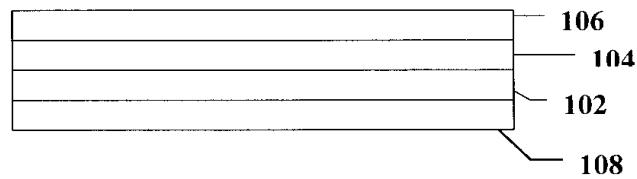

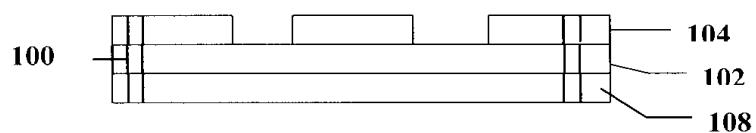

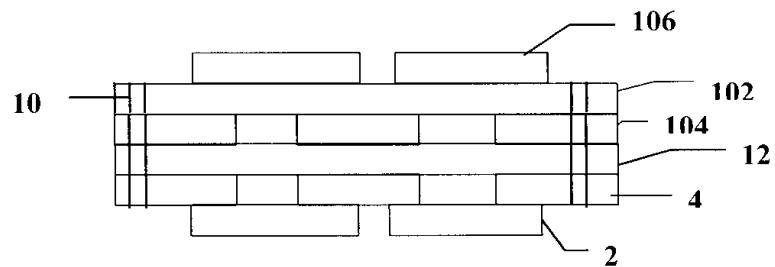

<120> 도 10 내지 도 17은 본 발명의 다른 실시예를 보여주는데, 이 실시예에서는 다른 한 층의 임피던스 소자와 전도성 라인이 절연 재료 시트(12)의 대향측 면에 형성된다. 도 10은 제2 고전도성 재료 시트(102)의 제1 표면에 제2 임피던스 재료층(104)을 성막한 다음, 제2 고전도성 재료 시트(108)를 제2 지지체(108)에 부착한 것을 보여준다. 그 후, 제2 임피던스 재료층(106)상에 다른 한 층의 포토레지스트 재료층(106)을 도포한다.

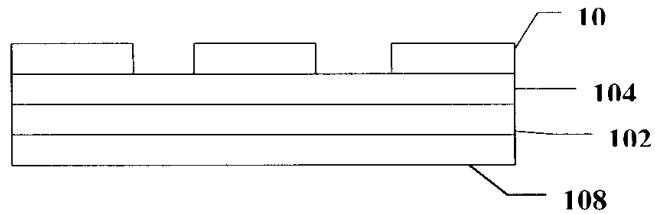

<121> 도 11은 제2 포토레지스트 재료층(106)을 화상을 따라 노출시킨 다음, 화상 영역을 유지시키면서 비화상 영역을 제거한 후의 결과를 보여준다. 도 12는 제2 임피던스 재료층(104)이 포토레지스트 재료층(106)의 제거된 비화상 영역 아래의 임피던스 재료층 영역이 화상을 따라 에칭된 다음 포토레지스트가 제거된 후의 결과를 보여준다. 에칭 및 포토레지스트의 제거는 전술한 공정들과 유사하게 수행된다. 선택적으로 포토레지스트를 남기는 것은 도시되어 있지 않다. 도 13은 고전도성 재료 시트(102), 지지체(108) 및 임의의 몇 개의 임피던스 소자(104)를 관통하여 천공된 타겟 구멍(100)을 보여준다. 도 14는 제2 임피던스 소자(104)가 절연 재료 시트(12)와 제2 고전도성 재료 시트(102) 사이에 있도록 제2 고전도성 재료 시트(102)를 절연 재료 시트(12)의 이면에 부착한 결과를 보여준다. 그 후, 제2 지지체(108)는 제2 고전도성 재료 시트(102)로부터 제거되고 다른 한 층의 포토레지스트 재료층(106)이 도 15에 도시된 바와 같이 제2 고전도성 재료 시트(102)의 이면에 도포된다. 도 16은 포토레지스트 재료층(106)이 화상을 따라 노출된 후 현상된 결과를 보여준다. 도 17은 제2 전도성 재료 시트(102)가 에칭되어 절연 재료 시트(12)의 이면에서 소정 패턴의 제2 임피던스 소자들과 접촉하는 제2 패턴의 전도성 라인들을 형성하는 제품을 보여주고 있다. 하나의 절연 재료 시트만이 양면에 임피던스 소자 및 전도성 라인이 마련된 것으로 도시되어 있지만, 추가적인 임피던스 소자, 전도성 라인 또는 절연 재료 시트 층들을 갖는 구조를 형성할 수 있다는 것도 본 발명이 의도한 범위 내에 있다.

<122> 비록, 전술한 상세한 설명은 완전한 임피던스 재료 시트를 전도성 재료 시트에 적용하고, 이어서 포토레지스트 화상 형성 및 에칭에 의한 패터닝을 행하여 임피던스 소자를 형성하는 과정을 거쳐 임피던스 소자가 형성되는 것으로 설명하고 있지만, 임피던스 소자들이 소정 패턴의 임피던스 소자를 고전도성 재료 시트상에 성막하는 방식으로도 형성될 수 있다고 하는 것은 본 발명이 의도한 범위 내에 있다. 이는, 예컨대 임피던스 소자 패턴으로서, 여러 가지 금속 충전물을 갖는 폴리머 잉크를 직접 성막함으로써 행할 수 있다. 그러한 폴리머 잉크는 미국 캘리포니아주 샌디에고에 소재하는 Ormet, 영국 켄트에 소재하는 Electra Polymers, 미국 뉴저지주 로키힐에 소재하는 Parelec으로부터 구입할 수 있는 것들을 포함한다. 그러한 성막은 잘 알려져 있는 스크린 인쇄법으로 행할 수 있다. 다른 방법으로, 임피던스 재료 자체가 감광성일 수 있다. 한 층의 임피던스 재료를 전

도성 재료 위에 도포하고, 표준 리소그래피 화상 형성 및 현상 기술로 화상을 형성할 수 있다. 적합한 감광성 임피던스 재료는 스위스 바실에 소재하는 Ciba Geigy 및 상기 Electra Polymers로부터 구입할 수 있는 것을 포함한다.

<123> 후술하는 비한정적인 예들로서 본 발명을 설명한다.

### 예 1

<125> 인산니켈로 구성된 저항성층을 전착된 구리 포일 롤에 도금한다. 구리 포일 롤을 지지 요소로서 알루미늄 롤과 함께 초음파 접합기를 통과시킨다. 이에 따라 상기 두 재료는 저항성층이 바깥을 향한 상태로 에지를 따라 함께 용착된다. 이것을 개별적인 시트(이하, "패널"이라 부른다)로 절단한다. 레지스터층에 핫 롤 라미네이터(hot roll laminator)를 사용하여 포토레지스트 박막을 도포하고, 할로겐화은 도판(silver halide artwork) 및 UV 노출 장치를 사용하여 노출시킨다. 노출되지 않는 포토레지스트는 탄산염 용액중에서 현상되어 인산니켈층을 노출시킨다. 이 인산니켈층은 염화제2구리 용액중에서 에칭에 의하여, 제거되어 이제 확정된 레지스터 소자를 남긴다. 그 후, 포토레지스트는 부식성 용액(KOH) 중에서 벗겨진다. 추가로, 패널의 기준 경계 영역에 타겟이 형성된다. 이를 타겟을 사용하여, 설치 구멍(tooling hole)을 패널에 천공한다. 이를 설치 구멍을 기준으로, 즉 다른 쪽의 면에 있는 레지스터에 대하여 상부면으로부터 회로의 화상을 구리에 활상하는 데에 사용된다. 그 후, 패널을 산화시켜 노출된 구리를 부동태화하고, 다음 공정중에 양호한 접착성을 제공한다. 그 후, 패널을 위치맞춤판의 설치 편에 배치하고, 에폭시 프리프레그(epoxy prepreg)를 레지스터층과 대향하게 배치한다. 다른 쪽의 면에는, 알루미늄에 의하여 지지된 구리상에 레지스터층을 갖는 다른 하나의 패널을 배치하거나 또는 구리층을 사용할 수 있다. 수지를 경화시키기에 필요한 열 및 압력을 가하면서 패널을 프레스한다. 프레스 후에, 패널을 트리밍하여 수지 플래시를 제거하고 알루미늄 지지체를 제거한다. 이렇게 하여 형성되는 심부(芯部)를 이제 양면에 포토레지스트층을 도포하고 할로겐화은 도판 및 UV 노출 유닛을 사용하여 노출시킴으로써 마무리 가공을 행한다. 할로겐화은 도판을 미리 형성된 설치 구멍을 사용하여 상기 심부에 정렬시킨다. 노출되지 않은 영역을 현상하고, 아래의 인산니켈 레지스터 재료에 영향을 미치지 않는 암모니아 에칭으로 구리를 에칭한다. 그 후, 포토레지스트를 벗기고 마무리된 심부를 남긴다. 이제, 레지스터 소자의 상부에 전도성 라인을 형성하여 회로를 완성한다.

<126> 심부를 산화시켜 구리를 부동태화하고, 보다 양호한 접착성을 부여하여 다른 심부들과 다층 인쇄 회로 기판으로 적층한다.

### 예 2

<128> 저항 소자의 에칭 후에 포토레지스트를 벗겨내지 않는다는 것을 제외하고는 예 1의 공정을 반복한다.

### 예 3

<130> 초음파 접합기를 사용하여, 구리 포일 롤을 알루미늄 지지체 요소의 롤에 부착한다. 이를 롤을 개별적인 패널로 절단한다. 이들 패널에, 후속 작업을 위한 기준용 설치 구멍을 천공한다. 패널의 구리측 면에(구리 포일은 처리면이 내측 또는 외측을 향하게 알루미늄에 부착된다) 스크린 인쇄법을 사용하여 저항성 잉크를 도포한다. 다른 방법으로, 잉크는 자동화된 디스펜싱 장치를 사용하여 도포될 수 있다. 잉크를 오븐 내에서 건조 경화시킨다. 이로써 저항 소자가 형성된다. 패널을 위치맞춤판의 설치 편상에 배치하고 프리프레그(파이버 글라스상의 반경화 에폭시)를 레지스터 소자와 대향하게 배치한다. 수지 침투 가공재의 다른 측에는 레지스터 소자 또는 오로지 구리 포일 시트(역시 알루미늄에 부착됨)만을 갖는 다른 하나의 패널을 배치한다. 상기 패널을 열 및 압력을 가하면서 적층하여 프리프레그를 경화시킨다. 프레스에서 패널들을 취출하여 트리밍한다. 예 1의 공정에서처럼 알루미늄을 제거하고 구리에 화상을 활상한다.

### 예 4

<132> 저항성 재료가 감광성으로서 전체 구리 표면상에 도포된다는 것을 제외하고는, 예 3의 공정을 반복한다. 그 후, 할로겐화은 도판 및 UV 노출 유닛을 사용하여 저항성 재료에 화상을 활상하고, 비노출 영역을 현상하여 제거한다. 나머지 저항성 재료는 오븐 내에서 충분히 경화된 다음, 예 3에서와 같은 공정 흐름을 따른다.

<133> 본 발명을 바람직한 실시예와 관련하여 구체적으로 도시하고 설명하였으나, 당업자라면 본 발명의 정신 및 범위에서 벗어나지 않고도 여러 가지 변경 및 수정이 행해질 수 있다는 것을 쉽게 인식할 것이다. 특히 청구 범위는 개시된 실시예, 전술한 변형예 및 모든 균등물을 포함하는 것으로 해석되도록 의도되어 있다.

### 발명의 효과

<134> 본 발명에 따르면 매우 단순화된 공정으로, 특히 임피던스 소자들이 염격한 공차로서 매입 형성되는 인쇄 회로 기판 제조 방법이 제공된다.

### 도면의 간단한 설명

- <1> 도 1은 고전도성 재료 시트의 한 쪽 면상의 성막된 임피던스 재료층과, 전도성 재료 시트의 다른 쪽 면상의 지지체와, 임피던스 재료상의 포토레지스트 재료층을 보여주는 도면.

- <2> 도 2는 포토레지스트 재료를 화상을 따라 노출시킨 다음, 화상 영역을 유지시키면서 비화상 영역을 제거한 후의 결과를 보여주는 도면.

- <3> 도 3은 포토레지스트 재료의 제거된 비화상 영역 아래의 임피던스 재료층의 영역에서 임피던스 재료를 화상을 따라 에칭한 다음 포토레지스트를 제거한 후의 결과를 보여주는 도면.

- <4> 도 4는 포토레지스트 재료의 제거된 비화상 영역 아래의 임피던스 재료를 에칭하고, 포토레지스트는 제거하지 않은 결과를 보여주는 도면.

- <5> 도 5는 고전도성 재료 시트 및 이 고전도성 재료 시트에 부착된 절연 재료 시트를 관통하여 천공된 타겟 구멍을 보여주는 도면.

- <6> 도 6은 지지체 제거 후의 결과를 보여주는 도면.

- <7> 도 7은 고전도성 재료 시트의 이면에 도포된 다른 한 층의 포토레지스트를 보여주는 도면.

- <8> 도 8은 노출 및 현상 후의 포토레지스트를 보여주는 도면.

- <9> 도 9는 포토레지스트 재료의 제거된 영역 아래의 고전도성 재료를 에칭하고, 몇 개의 임피던스 소자와 접촉하는 소정 패턴의 전도성 라인을 남긴 후의 결과를 보여주는 도면.

- <10> 도 10은 제2 지지체에 부착되는 제2 고전도성 재료 시트와, 이 고전도성 재료 시트 상의 제2 임피던스 재료층 및 이 제2 임피던스 재료층상의 다른 한 층의 포토레지스트 재료를 보여주는 도면.

- <11> 도 11은 포토레지스트 재료를 화상을 따라 노출시킨 다음 화상 영역을 유지시키면서 비화상 영역을 제거한 후의 결과를 보여주는 도면.

- <12> 도 12는 임피던스 소자를 형성하기 위하여, 포토레지스트 재료의 제거된 비화상 영역 아래의 임피던스 재료층을 화상을 따라 에칭한 다음 포토레지스트를 제거한 후의 결과를 보여주는 도면.

- <13> 도 13은 고전도성 재료 시트를 관통하여 천공된 타겟 구멍을 보여주는 도면.

- <14> 도 14는 절연 재료 시트의 이면에 제2 고전도성 재료 시트를 부착한 결과를 보여주는 도면.

- <15> 도 15는 제2 지지체가 제거되고 이 전도성 재료 시트의 이면에 다른 한 층의 포토레지스트가 도포된 제2 고전도성 재료 시트를 보여주는 도면.

- <16> 도 16은 포토레지스트가 화상을 따라 노출되고 현상된 후의 결과를 보여주는 도면.

- <17> 도 17은 전도성 라인을 형성하기 위하여 제2 고전도성 재료 시트가 에칭되고 포토레지스트가 제거된 후의 결과를 보여주는 도면.

- <18> **도면의 주요 부분에 대한 부호의 설명**

- <19> 2 : 고전도성 재료 시트

- <20> 4 : 임피던스 재료층(임피던스 소자)

- <21> 6 : 포토레지스트 재료층

- <22> 8 : 지지체

- <23> 10 : 타겟 구멍

- <24> 12 : 절연 재료 시트

- <25> 100 : 타겟 구멍

- <26> 102 : 제2 고전도성 재료

- <27> 104 : 임피던스 재료(임피던스 소자)

- <28> 106 : 포토레지스트 재료층

- <29> 108 : 제2 지지체

### 도면

#### 도면1

#### 도면2

#### 도면3

#### 도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17