## (12) 发明专利

(10) 授权公告号 CN 110620124 B

(45) 授权公告日 2023.07.18

(21) 申请号 201910870756.4

H04N 23/84 (2023.01)

(22) 申请日 2014.10.23

H04N 25/40 (2023.01)

(65) 同一申请的已公布的文献号

H04N 25/68 (2023.01)

申请公布号 CN 110620124 A

## (56) 对比文件

US 2012025060 A1, 2012.02.02

(43) 申请公布日 2019.12.27

US 2011049590 A1, 2011.03.03

(30) 优先权数据

CN 102005461 A, 2011.04.06

2013-226299 2013.10.31 JP

US 2009200451 A1, 2009.08.13

(62) 分案原申请数据

US 2006007331 A1, 2006.01.12

201410572947.X 2014.10.23

CN 103209308 A, 2013.07.17

(73) 专利权人 索尼半导体解决方案公司

US 2013182154 A1, 2013.07.18

地址 日本神奈川县

JP 2009206941 A, 2009.09.10

(72) 发明人 山本敦彦

US 2010225795 A1, 2010.09.09

(74) 专利代理机构 北京信慧永光知识产权代理

有限责任公司 11290

US 2007273779 A1, 2007.11.29

专利代理人 卫李贤 曹正建

US 2005264684 A1, 2005.12.01

(51) Int.Cl.

US 2012268632 A1, 2012.10.25

H04N 23/54 (2023.01)

CN 103227897 A, 2013.07.31

CN 103369264 A, 2013.10.23

审查员 王建霞

权利要求书2页 说明书19页 附图24页

## (54) 发明名称

摄像器件、信号处理器件和电子装置

## (57) 摘要

本发明公开了摄像器件、信号处理器件和电子装置。所述摄像器件包括：第一多个像素，所述第一多个像素被构造为仅包含相同颜色的相邻像素；滤色器，所述滤色器是以所述第一多个像素的拜耳排列的形式形成的；和像素共用单元，所述像素共用单元的第一组像素共用第一浮动扩散部且包括所述第一多个像素中的一个或多个像素，其中，使用所述第一多个像素的所述相邻像素中不共用所述第一浮动扩散部的至少一个像素来对所述第一组像素中的所述一个或多个像素中的至少一个像素中产生的缺陷进行校正，其中，所述像素共用单元是共用放大晶体管的 $2 \times 4$ 像素。

B

CN 110620124

1. 一种摄像器件，其包括：

第一多个像素，所述第一多个像素被构造为仅包含相同颜色的相邻像素；

滤色器，所述滤色器是以所述第一多个像素的拜耳排列的形式形成的；和

像素共用单元，其中所述像素共用单元的第一组像素共用第一浮动扩散部且包括所述第一多个像素中的一个或多个像素，

其中，使用所述第一多个像素的所述相邻像素中不共用所述第一浮动扩散部的至少一个像素来对所述第一组像素中的所述一个或多个像素中的至少一个像素中产生的缺陷进行校正，

其中，所述像素共用单元是共用放大晶体管的 $2 \times 4$ 像素，并且所述滤色器的编码单元的四个像素中至少一半不是所述像素共用单元的像素。

2. 根据权利要求1所述的摄像器件，

其中，所述第一多个像素是 $2 \times 2$ 像素。

3. 根据权利要求1所述的摄像器件，

其中，所述第一多个像素包括4个像素。

4. 根据权利要求1所述的摄像器件，

其中，所述相同颜色的相邻像素的颜色编码是原色方格的编码。

5. 根据权利要求1所述的摄像器件，

其中，所述相同颜色的相邻像素的颜色编码是WRGB的编码。

6. 根据权利要求1所述的摄像器件，

其中，所述像素共用单元的第二组像素共用第二浮动扩散部，并且所述第二组像素是 $2 \times 2$ 像素，并且其中，所述相邻像素与所述一个或多个像素中的具有所述缺陷的所述至少一个像素直接相邻。

7. 根据权利要求1所述的摄像器件，

其中，所述第一多个像素中不被包含在所述像素共用单元中的像素与所述像素共用单元中的至少一些像素直接相邻。

8. 根据权利要求1所述的摄像器件，

其中，所述像素共用单元中的像素包括所述第一多个像素中的仅一个像素，并且其中，所述相邻像素与所述像素共用单元中的像素直接相邻。

9. 根据权利要求1所述的摄像器件，

其中，所述像素共用单元中的像素包括所述第一多个像素中的仅两个像素。

10. 根据权利要求2所述的摄像器件，

其中，所述像素共用单元中的像素包括所述第一多个像素中的仅一个像素。

11. 根据权利要求2所述的摄像器件，

其中，所述像素共用单元中的像素包括所述第一多个像素中的仅两个像素。

12. 根据权利要求7所述的摄像器件，

其中，缺陷像素具有相同的颜色。

13. 一种信号处理器件，其包括：

校正处理单元，在从包括第一多个像素和滤色器的摄像器件输出的输出信号中，所述校正处理单元对第一像素共用单元中的至少一个或多个像素中产生的缺陷进行校正，所述

第一多个像素被配置为仅包括相同颜色的相邻像素，所述滤色器是以所述第一多个像素的拜耳排列的形式形成的，其中，所述第一像素共用单元中的像素共用浮动扩散部且包括所述第一多个像素中的一个或多个像素，其中，所述缺陷是使用所述第一多个像素的所述相邻像素中的不共用所述浮动扩散部的至少一个像素来校正的，并且其中，所述第一像素共用单元共用放大晶体管，并且所述滤色器的编码单元的四个像素中至少一半不是所述第一像素共用单元的像素。

14. 根据权利要求13所述的信号处理器件，

其中，所述校正处理单元根据所述第一像素共用单元内产生的缺陷像素的数量使用所述第一多个像素中的像素来校正所述第一像素共用单元内产生的所述缺陷像素。

15. 根据权利要求13所述的信号处理器件，

其中，所述校正处理单元使用所述第一多个像素中的所有像素来校正所述第一像素共用单元内产生的缺陷像素。

16. 根据权利要求13所述的信号处理器件，

其中，所述校正处理单元根据所述第一像素共用单元内产生的缺陷像素的存储时间使用所述第一多个像素中的数据来校正所述第一像素共用单元内产生的所述缺陷像素。

17. 一种电子装置，其包括如权利要求1至12中任一项所述的摄像器件。

## 摄像器件、信号处理器件和电子装置

[0001] 本申请是申请日为2014年10月23日、发明名称为“固态摄像器件、信号处理器件和电子装置”的申请号为201410572947.X的专利申请的分案申请。

### 技术领域

[0002] 本发明涉及固态摄像器件、信号处理器件和电子装置，特别地，涉及能够抑制白点校正中的分辨率劣化的固态摄像器件、信号处理器件和电子装置。

### 背景技术

[0003] 在同一像素共用型固态摄像器件中，当附着相同颜色的四个像素的滤色器时，通过同一像素共用进行相同颜色编码(参照JP 2010-28423A)。

[0004] [引用列表]

[0005] [专利文献]

[0006] [专利文献1]JP 2010-28423A

### 发明内容

[0007] [技术问题]

[0008] 然而，当例如由于像素共用部中的浮动扩散部的泄漏等而产生白点时，使用距白点隔开两个像素的相同颜色的四个像素来校正该白点。在这种情况下，在校正中使用的每个像素的位置与待校正的像素的位置是在空间上是被分隔开的。由于这个原因，校正后的分辨率通常会被劣化。

[0009] 期望抑制白点校正中的分辨率劣化。

[0010] [解决该技术问题的技术方案]

[0011] 本发明的第一方面的固态摄像器件包括：被构造为包括相同颜色编码且彼此之间无像素共用的像素的多个像素构成的组；和以所述多个像素构成的组的拜耳(Bayer)阵列的形式形成的滤色器。

[0012] 所述多个像素构成的组是由彼此之间无像素共用的像素形成的。

[0013] 所述像素共用的单元是 $2 \times 2$ 像素。

[0014] 所述多个像素构成的组的至少一半是彼此之间无像素共用的像素。

[0015] 所述像素共用的单元是 $2 \times 4$ 像素。

[0016] 所述像素共用的单元是 $1 \times 4$ 像素。

[0017] 使用所述多个像素构成的组内的像素来校正所述像素共用的单元内产生的缺陷像素。

[0018] 所述多个像素构成的组包括四个像素。

[0019] 所述颜色编码是原色(primary color)方格的编码。

[0020] 所述颜色编码是WRGB的编码。

[0021] 本发明的第二方面的信号处理器件包括：校正处理单元，在从包括被构造为包含

相同颜色编码且彼此之间无像素共用的像素的多个像素构成的组和以所述多个像素构成的组的拜耳阵列的形式形成的滤色器的固态摄像器件输出的输出信号中,所述校正处理单元使用所述多个像素构成的组内的像素来校正像素共用单元内产生的缺陷像素。

[0022] 所述校正处理单元可以根据所述像素共用单元内产生的缺陷像素的数量使用所述多个像素构成的组内的像素来校正所述像素共用单元内产生的所述缺陷像素。

[0023] 所述校正处理单元可以使用所述多个像素构成的组内的所有像素来校正所述像素共用单元内产生的缺陷像素。

[0024] 所述校正处理单元可以根据所述像素共用单元内产生的缺陷像素的存储时间使用所述多个像素构成的组内的数据来校正所述像素共用单元内产生的所述缺陷像素。

[0025] 本发明的第三方面的电子装置包括:固态摄像器件,所述固态摄像器件包括被构造为包含相同颜色编码且彼此之间无像素共用的像素的多个像素构成的组和由所述多个像素构成的组的拜耳阵列形成的滤色器;光学系统,所述光学系统使入射光入射至所述固态摄像器件;和信号处理电路,所述信号处理电路处理从所述固态摄像器件输出的输出信号。

[0026] 根据本发明的第一方面,所述固态摄像器件包括被构造为包含相同颜色编码且彼此之间无像素共用的像素的多个像素构成的组和以所述多个像素构成的组的拜耳阵列的形式形成的滤色器。

[0027] 根据本发明的第二方面,在从包括被构造为包含相同颜色编码且彼此之间无像素共用的像素的多个像素构成的组和以所述多个像素构成的组的拜耳阵列的形式形成的滤色器的固态摄像器件输出的输出信号中,使用所述多个像素构成的组内的像素来校正像素共用单元内产生的缺陷像素。

[0028] 根据本发明的第三方面,所述固态摄像器件包括被构造为包含相同颜色编码且彼此之间无像素共用的像素的多个像素构成的组和以所述多个像素构成的组的拜耳阵列的形式形成的滤色器。此外,入射光入射至所述固态摄像器件,并且对从所述固态摄像器件输出的输出信号进行处理。

[0029] [本发明的有益效果]

[0030] 根据本发明的实施例,能够进行白点校正。此外,根据本发明的实施例,能够抑制白点校正中的分辨率劣化。

[0031] 本说明书所述的效果是为了说明的目的,且本发明的效果不限于本说明书所述的效果,也可能存在附加的效果。

## 附图说明

[0032] [图1]图1是示出了应用了本发明的固态摄像器件的示意性构造的示例的框图。

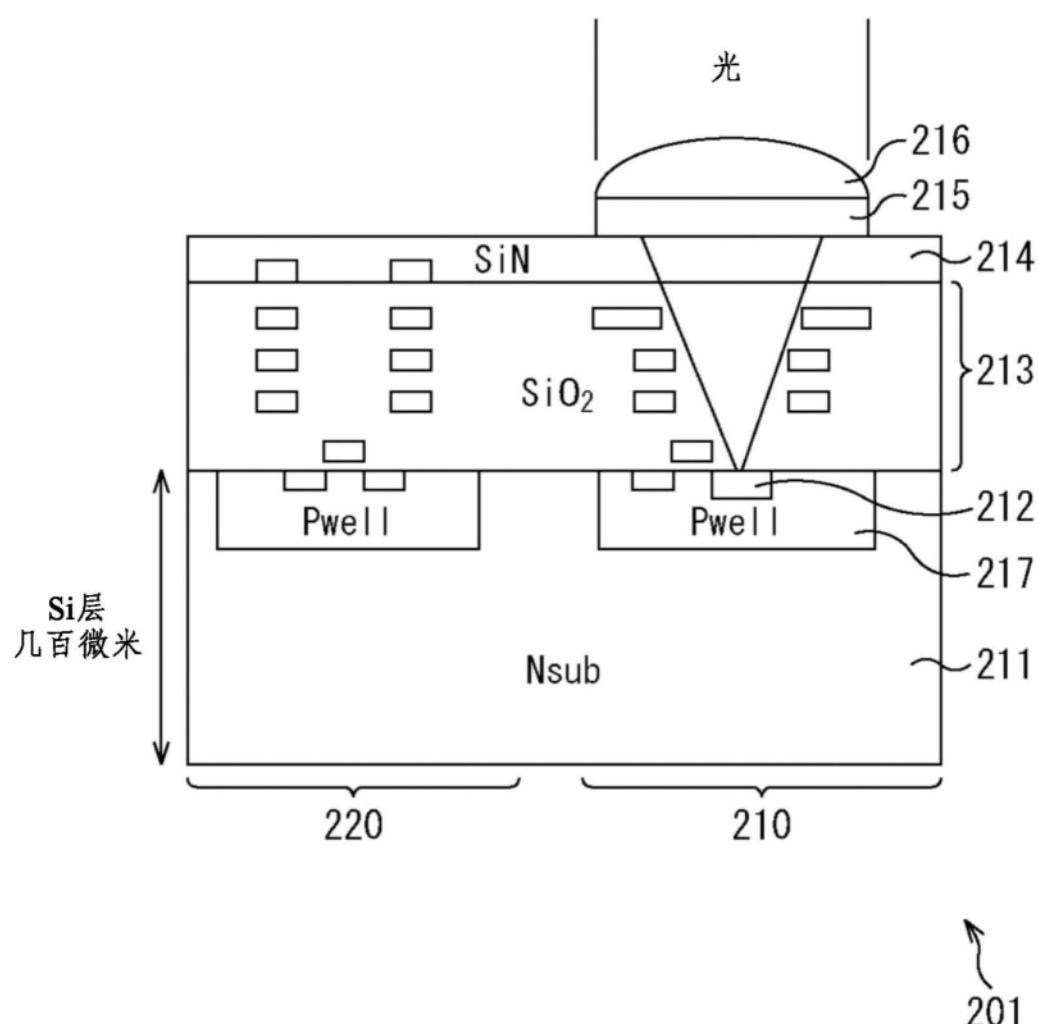

[0033] [图2]图2是根据本发明实施例的固态摄像器件的横截面图。

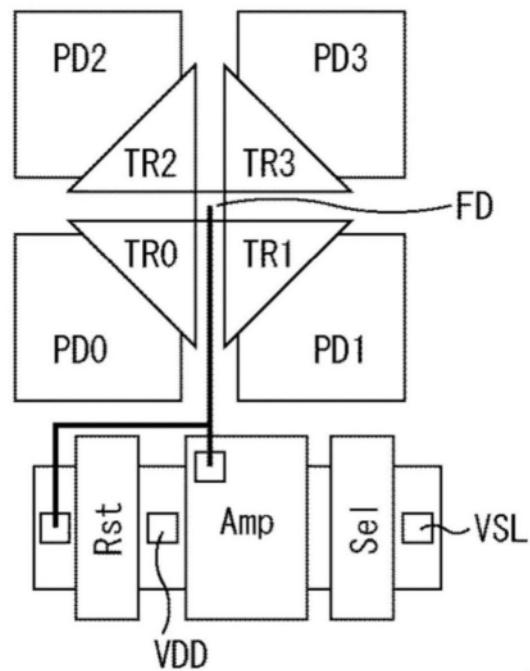

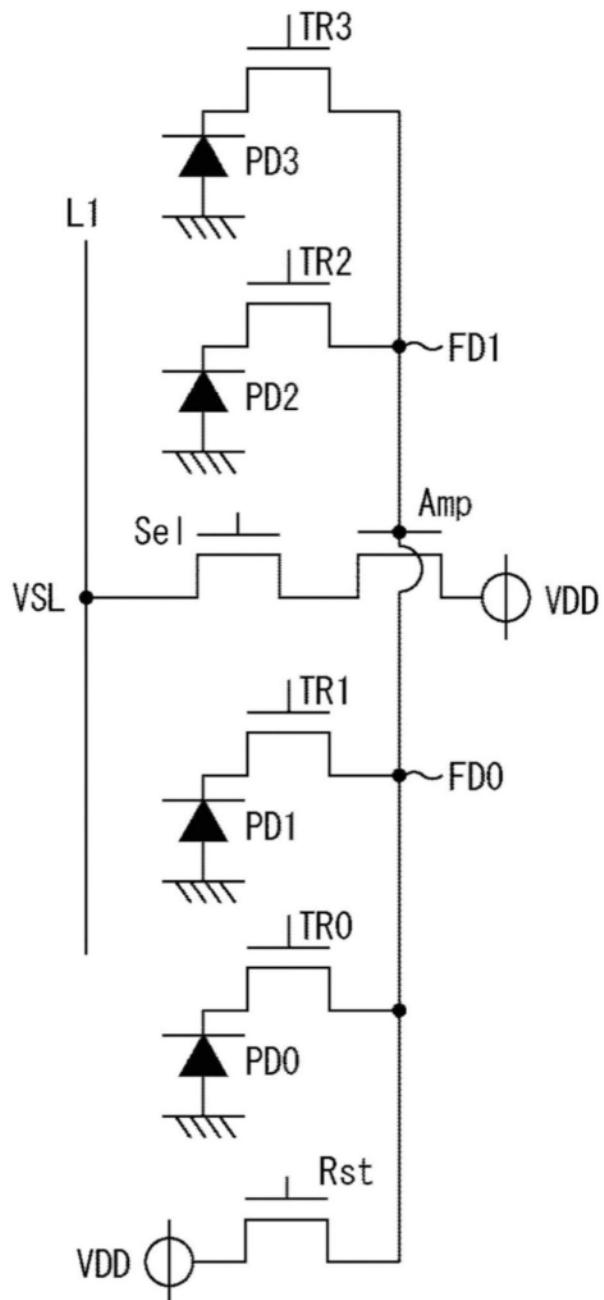

[0034] [图3]图3是示出了 $2 \times 2$ 像素共用单元的电路构造的示例的电路图。

[0035] [图4]图4是示出了 $2 \times 2$ 像素共用单元的电路构造的示例的平面图。

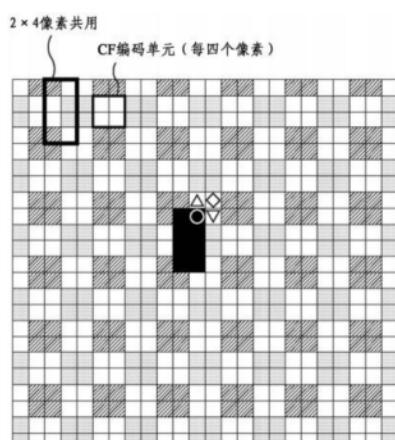

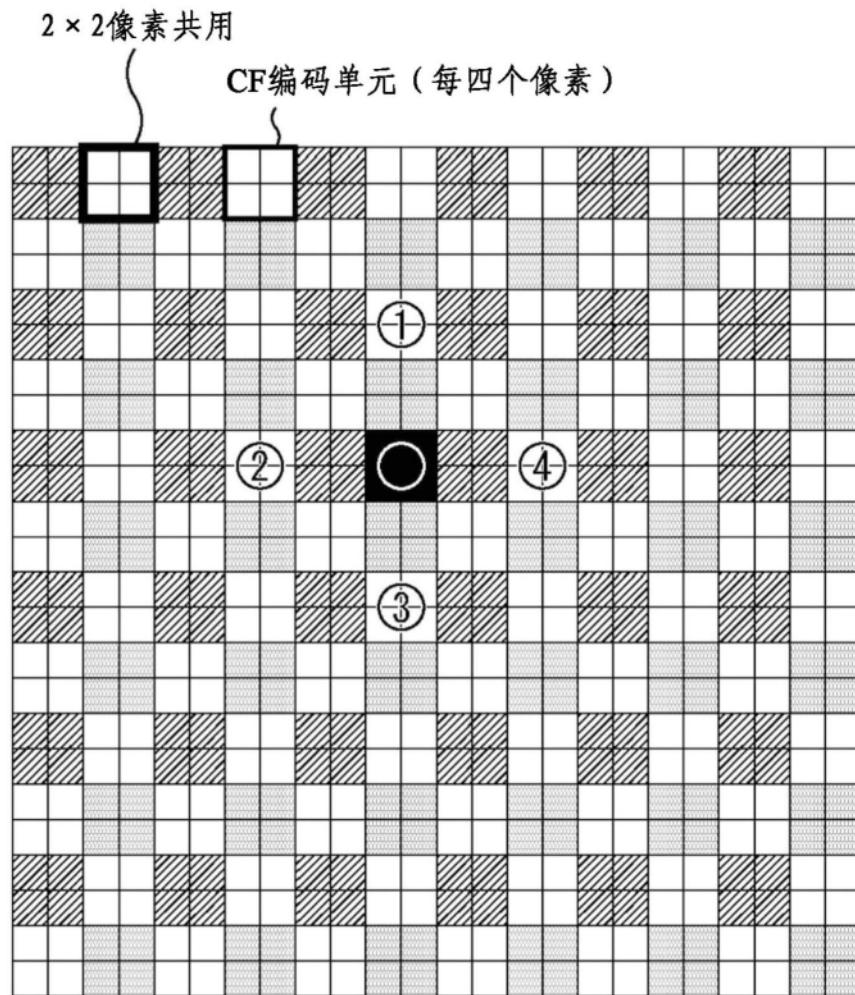

[0036] [图5]图5示出了 $2 \times 2$ 像素共用单元与滤色器的编码单元之间的关系的示例。

[0037] [图6]图6示出了根据本发明实施例的 $2 \times 2$ 像素共用单元与滤色器的编码单元之间的关系。

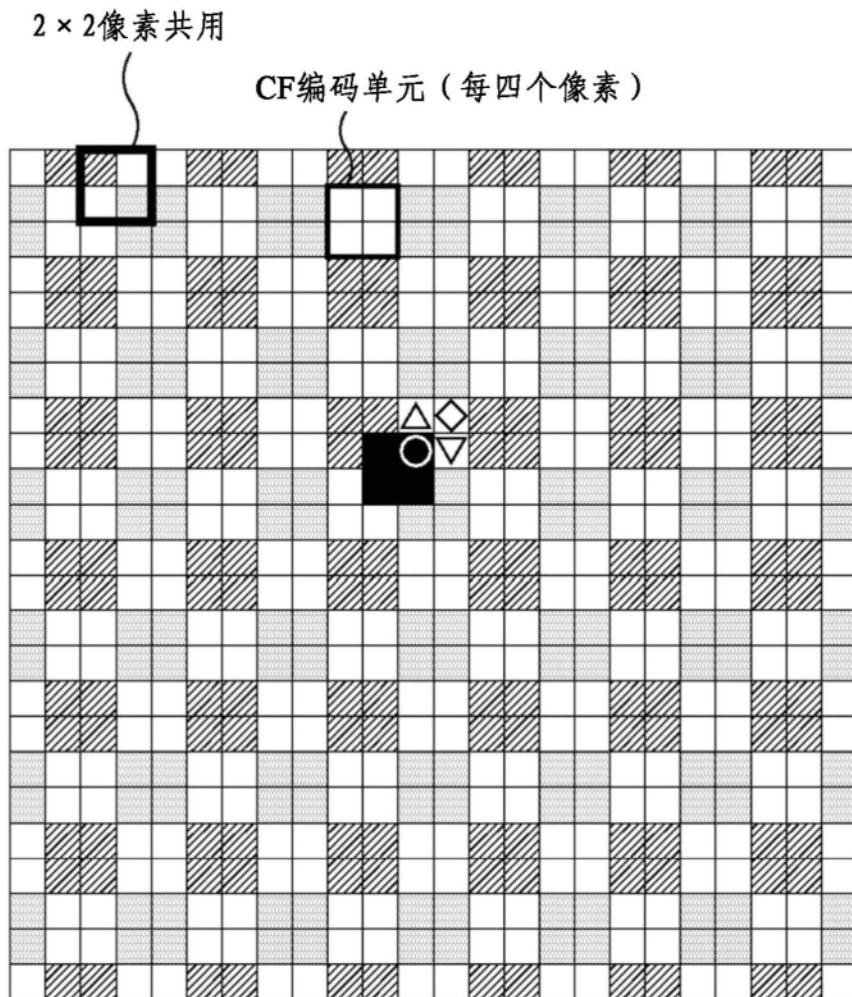

- [0038] [图7]图7是示出了根据本发明实施例的电子装置的构造的示例的框图。

- [0039] [图8]图8示出了DSP电路的构造的示例。

- [0040] [图9]图9是用于说明图8所示的DSP电路的信号处理的示例的流程图。

- [0041] [图10]图10示出了DSP电路的构造的示例。

- [0042] [图11]图11是用于说明图10所示的DSP电路的信号处理的示例的流程图。

- [0043] [图12]图12示出了DSP电路的构造的示例。

- [0044] [图13]图13是用于说明图12所示的DSP电路的信号处理的示例的流程图。

- [0045] [图14]图14示出了每个像素的方格(checker)RGB拜耳阵列的示例。

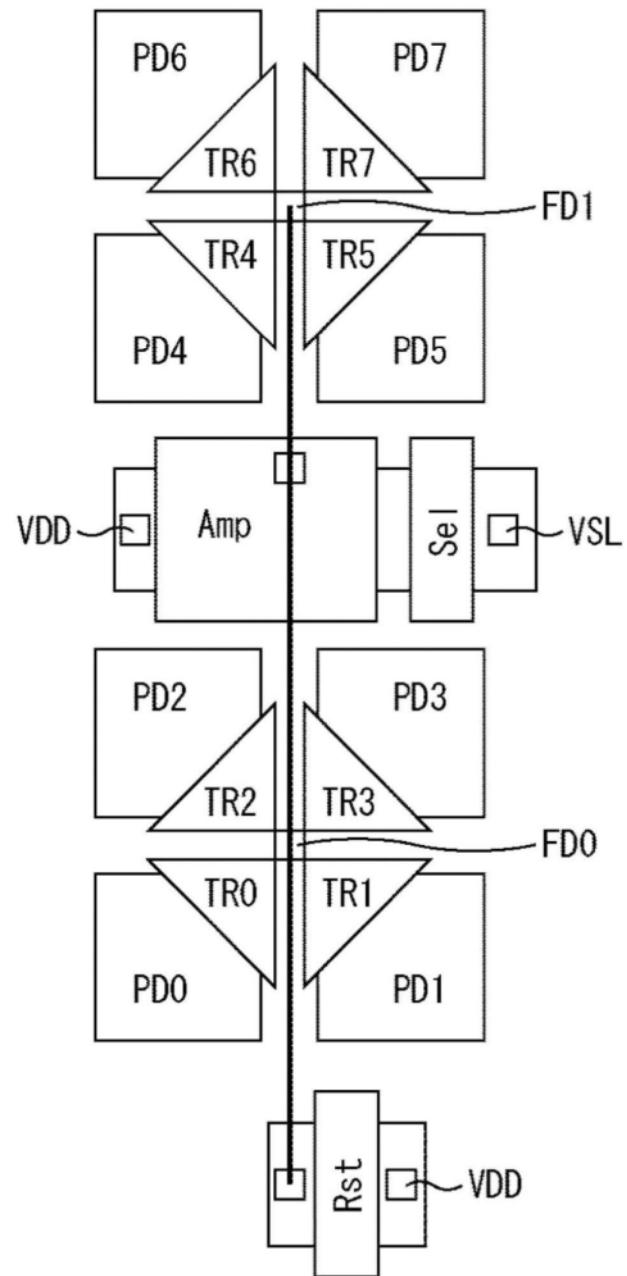

- [0046] [图15]图15是示出了 $2 \times 4$ 像素共用单元的电路构造的示例的电路图。

- [0047] [图16]图16是示出了 $2 \times 4$ 像素共用单元的电路构造的示例的平面图。

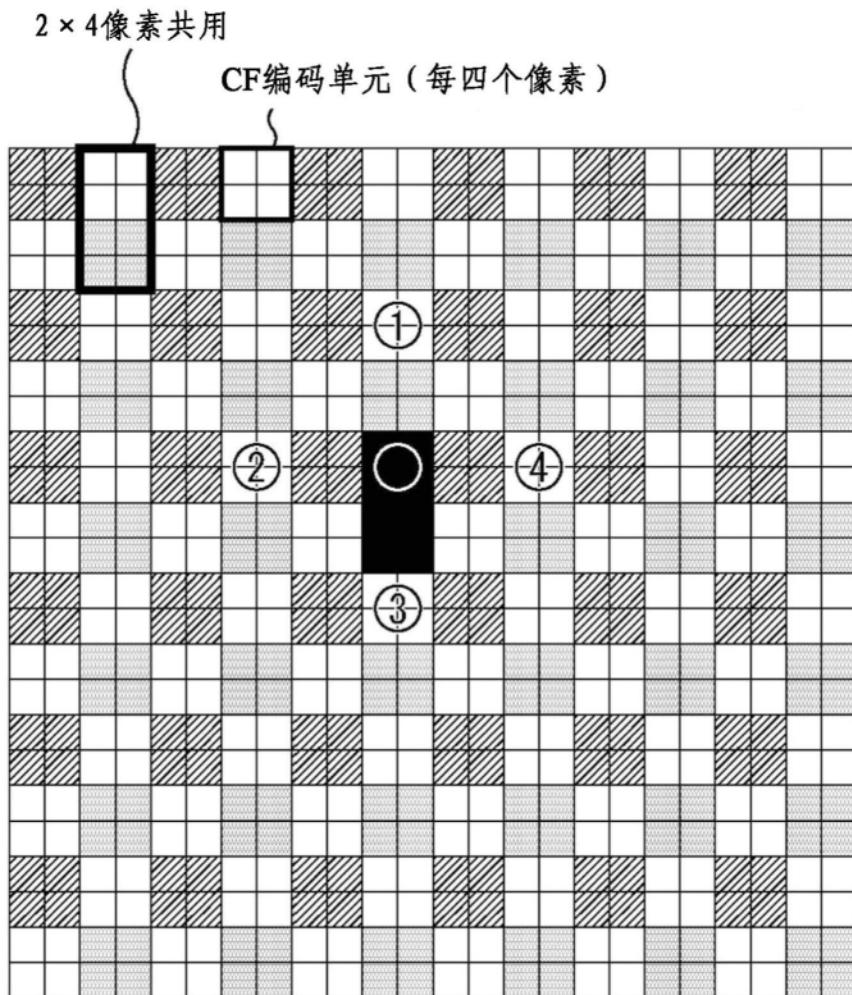

- [0048] [图17]图17示出了 $2 \times 4$ 像素共用单元与滤色器的编码单元之间的关系的示例。

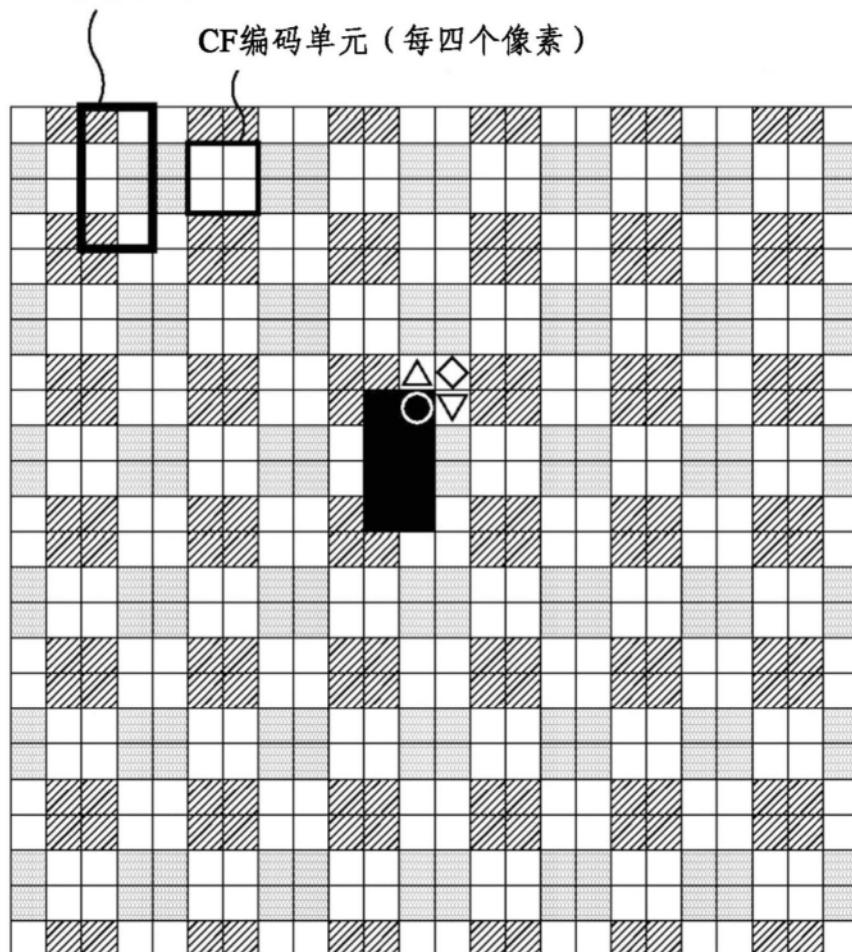

- [0049] [图18]图18示出了根据本发明实施例的 $2 \times 4$ 像素共用单元与滤色器的编码单元之间的关系。

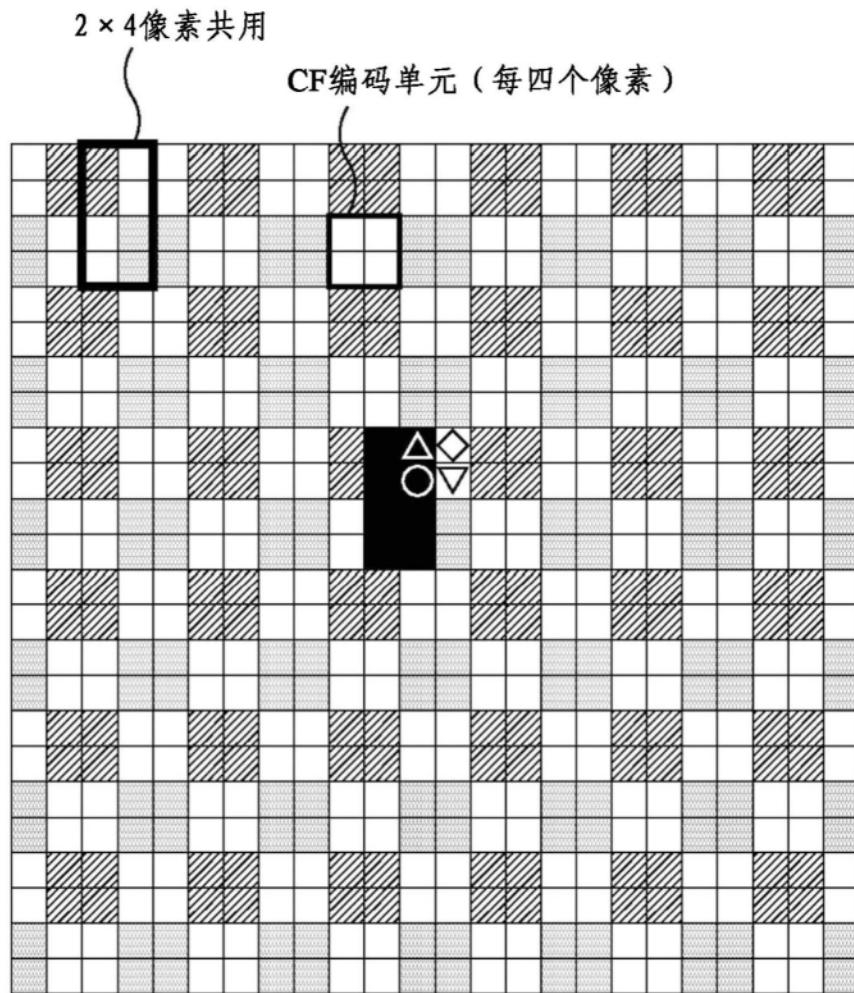

- [0050] [图19]图19示出了根据本发明实施例的 $2 \times 4$ 像素共用单元与滤色器的编码单元之间的关系。

- [0051] [图20]图20是示出了 $1 \times 4$ 像素共用单元的电路构造的示例的电路图。

- [0052] [图21]图21是示出了 $1 \times 4$ 像素共用单元的电路构造的示例的平面图。

- [0053] [图22]图22示出了根据本发明实施例的 $1 \times 4$ 像素共用单元与滤色器的编码单元之间的关系。

- [0054] [图23]图23示出了根据本发明实施例的 $1 \times 4$ 像素共用单元与滤色器的编码单元之间的关系。

- [0055] [图24]图24是根据本发明另一个实施例的固态摄像器件的横截面图。

- [0056] [图25]图25是示出了计算机的构造的示例的框图。

## 具体实施方式

[0057] 以下,将说明用于实施本发明的方式(在下文中,被称为实施例)。此外,将以下面的顺序给出说明。

- [0058] 0. 固态摄像器件的示意性构造的示例

- [0059] 1. 第一实施例( $2 \times 2$ 像素共用的示例)

- [0060] 2. 第二实施例( $2 \times 4$ 像素共用的示例)

- [0061] 3. 第三实施例( $1 \times 4$ 像素共用的示例)

- [0062] 4. 第四实施例(固态摄像器件的构造的另一个示例)

- [0063] 5. 第五实施例(计算机)

- [0064] 0. 固态摄像器件的示意性构造的示例

(固态摄像器件的示意性构造的示例)

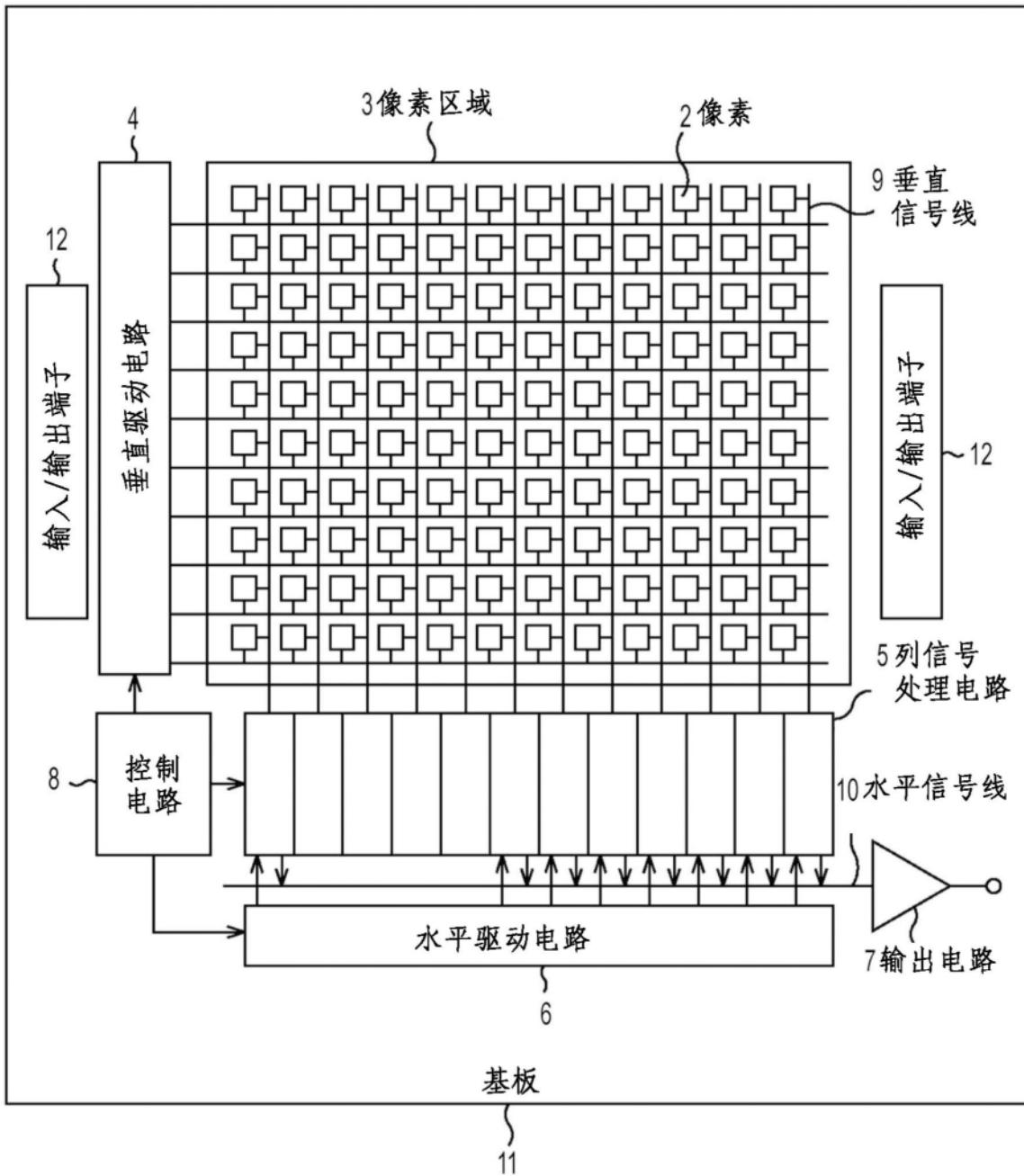

- [0065] 图1示出了应用于本发明每个实施例的CMOS(互补金属氧化物半导体)固态摄像器件的示意性构造的示例。

- [0066] 如图1所示,固态摄像器件(元件芯片)1包括像素区域(所谓的摄像区域)3和周边电路部,在像素区域3内,含有光电转换元件的多个像素2以二维的方式有规则地排列在半

导体基板11(例如,硅基板)上。

[0068] 像素2包括光电转换元件(例如,光电二极管)和多个像素晶体管(所谓的MOS晶体管)。例如,多个像素晶体管可能是传输晶体管、复位晶体管和放大晶体管这三个晶体管,或者可能是添加了选择晶体管的四个晶体管。因为每个像素2(单元像素)的等效电路与典型像素的等效电路相同,所以这里将省略该等效电路的详细说明。

[0069] 像素2能够被形成为具有像素共用结构。如后面将参照图3所述,像素共用结构例如包括多个光电二极管、多个传输晶体管、被共用的一个浮动扩散部和被共用的所有其它像素晶体管。

[0070] 周边电路部包括垂直驱动电路4、列信号处理电路5、水平驱动电路6、输出电路7和控制电路8。

[0071] 控制电路8接收用来指定操作方式等的输入时钟或数据,并且输出诸如固态摄像器件1的内部信息等数据。具体地,控制电路8根据垂直同步信号、水平同步信号和主时钟产生作为垂直驱动电路4、列信号处理电路5和水平驱动电路6的操作基准的控制信号或时钟信号。然后,控制电路8将这些信号输入到垂直驱动电路4、列信号处理电路5和水平驱动电路6。

[0072] 垂直驱动电路4例如由移位寄存器形成,并且选择像素驱动配线且将用于驱动像素2的脉冲供给至所选的像素驱动配线,从而以行为单位驱动像素2。具体地,垂直驱动电路4以行为单位在垂直方向上按顺序选择和扫描像素区域3的每个像素2,并且通过垂直信号线9将基于信号电荷(信号电荷是根据每个像素2的光电转换元件中接收的光量而产生的)的像素信号供给至列信号处理电路5。

[0073] 列信号处理电路5例如是针对像素2的各列而布置的,并且对从各像素列的一行的像素2输出的信号进行诸如去噪等信号处理。具体地,列信号处理电路5进行诸如去除像素2固有的固定模式噪声的CDS(相关双采样)、信号放大或A/D(模拟/数字)转换等信号处理。在列信号处理电路5的输出端与水平信号线10之间设置有水平选择开关(未示出)。

[0074] 水平驱动电路6例如由移位寄存器形成,并且通过按顺序输出水平扫描脉冲来依次选择列信号处理电路5并将从每个列信号处理电路5输出的像素信号输出到水平信号线10。

[0075] 输出电路7对通过水平信号线10从列信号处理电路5按顺序供给来的信号进行信号处理,并且输出处理结果。例如,输出电路7可以仅进行缓冲,或可以进行黑电平调整、列差异校正和各种数字信号处理等等。

[0076] 输入/输出端子12被设置用来将信号发送至外部并且接收来自外部的信号。

[0077] (固态摄像器件的横截面的示例)

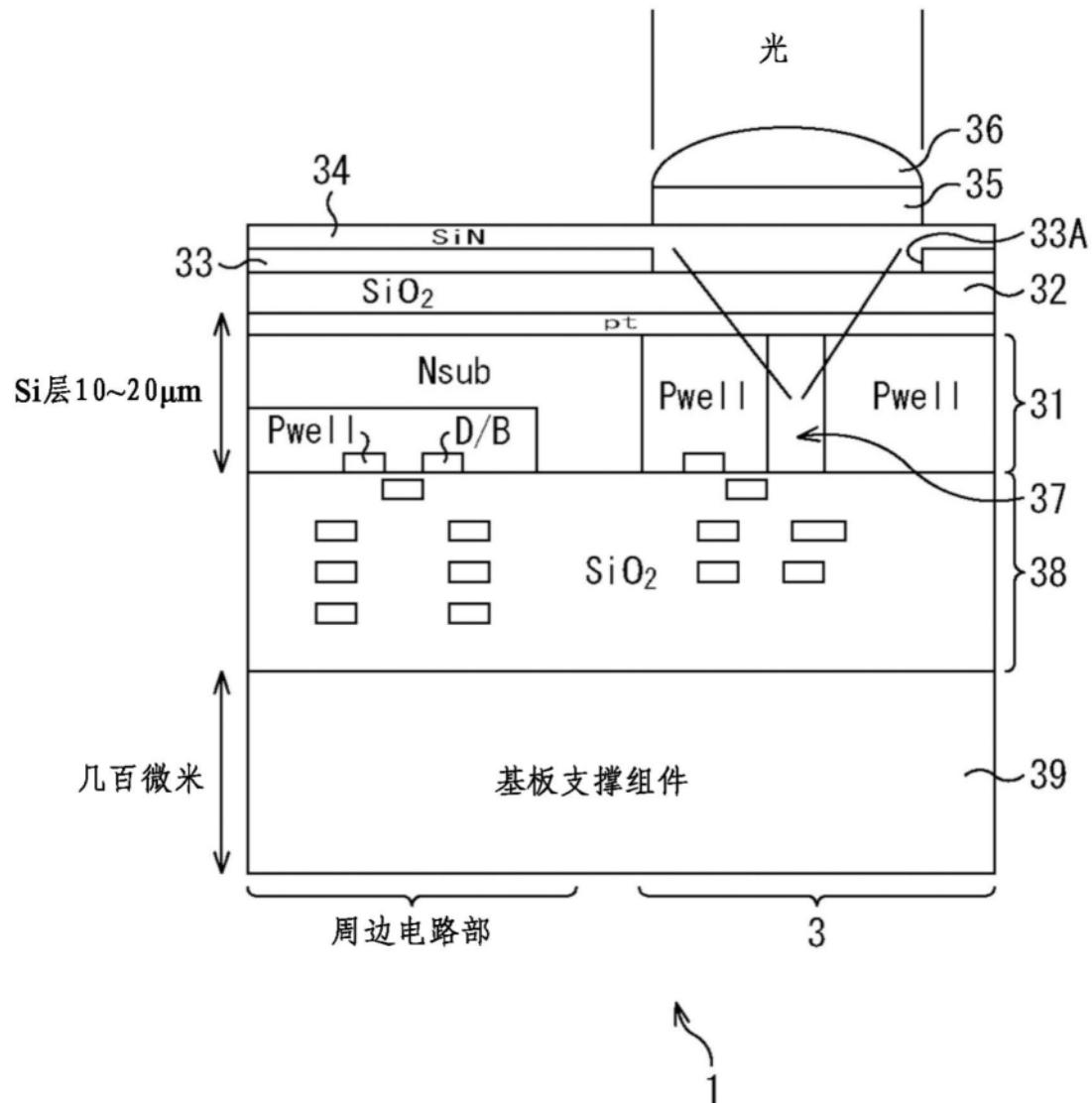

[0078] 图2是示出了固态摄像器件的像素区域3和周边电路部的结构的示例的横截面图。在图2所示的示例中,示出了底面发光型固态摄像器件的示例。

[0079] 在图2所示的示例性的固态摄像器件1中,通过以CMP(化学机械研磨)对晶圆进行研磨形成有具有约10μm至20μm厚度的Si(硅)层(元件层)31。在可见光情况下该厚度的优选范围是5μm至15μm,在红外光情况下该厚度的优选范围是5μm至50μm且在紫外光情况下该厚度的优选范围是3μm至7μm。在Si层31的一个表面上形成有遮光层33并且在Si层31与遮光层33之间设置有SiO<sub>2</sub>层32。

[0080] 与配线不同,遮光层33是仅考虑光学元件来布局的。遮光层33中形成有开口33A。在遮光层33上形成有作为钝化层的氮化硅层(SiN)34,且在开口33A的上方还形成有滤色器35和OCL(片上透镜)36。

[0081] 也即是,上述的是这样的像素结构:其中,从Si层31的一个表面侧入射的光透过OCL 36和滤色器35被引导至形成于Si层31内的光电二极管37的受光面。形成有晶体管或金属配线线路的配线层38形成在Si层31的另一个表面上,且基板支撑组件39被接合至配线层38。

[0082] 1. 第一实施例(2×2像素共用的示例)

[0083] (像素共用单元的构造的示例)

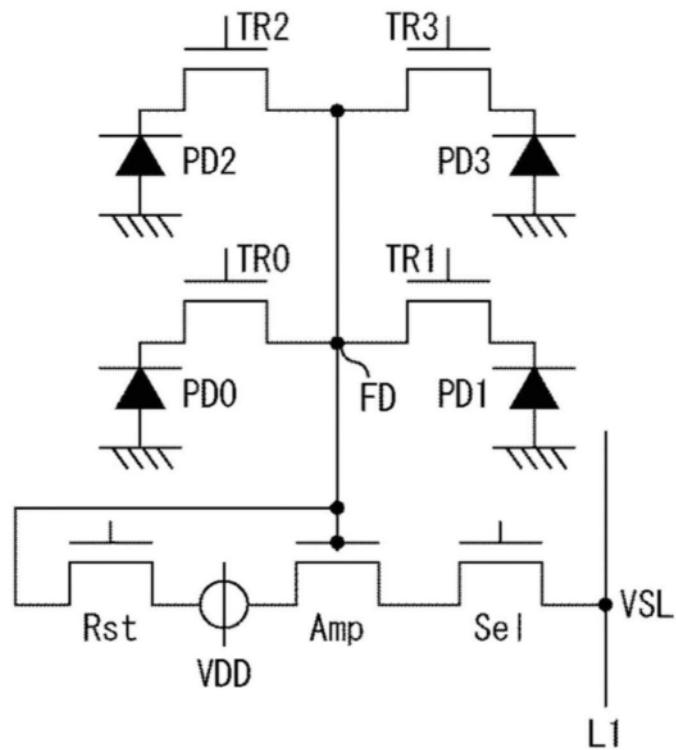

[0084] 首先,将参照图3和图4说明2×2像素共用单元的电路构造的示例。图3是示出了2×2像素共用单元的电路构造的示例的电路图。图4是示出了2×2像素共用单元的电路构造的示例的平面图。

[0085] 如图3和图4所示,2×2像素共用单元被构造为包括四个光电转换元件(例如,光电二极管PD0至PD3)、与光电二极管PD0至PD3相对应的四个传输晶体管TR0至TR3以及复位晶体管Rst、放大晶体管Amp和选择晶体管Sel这三个晶体管。

[0086] 光电二极管PD0至PD3具有连接至负电源(例如,地)的阳极电极,并且进行将接收的光转换成电荷量与接收的光量相对应的光电荷(在这里,光电子)的光电转换。光电二极管PD0至PD3的阴极电极通过对应的传输晶体管TR0至TR3电连接至放大晶体管Amp的栅极电极。放大晶体管Amp的栅极电极电连接至四个传输晶体管TR0至TR3的节点被称为浮动扩散部FD。

[0087] 传输晶体管TR0至TR3连接在相应光电二极管PD0至PD3的阴极电极与浮动扩散部FD之间。高电平(例如,VDD电平)有效(以下,被称为“高有效”)传输脉冲 $\phi_{TRF}$ 通过传输线(未示出)被施加于传输晶体管TR0至TR3的栅极电极。通过施加传输脉冲 $\phi_{TRF}$ ,传输晶体管TR0至TR3导通,且由光电二极管PD0至PD3内的光电转换产生的光电荷被传输至浮动扩散部FD。

[0088] 复位晶体管Rst具有连接至像素电源VDD的漏极电极和连接至浮动扩散部FD的源极电极。在信号电荷从光电二极管PD0至PD3传输至浮动扩散部FD之前,高有效复位脉冲 $\phi_{RST}$ 通过复位线(未示出)被施加于复位晶体管Rst的栅极电极。通过施加复位脉冲 $\phi_{RST}$ 使复位晶体管Rst导通,且通过将浮动扩散部FD的电荷排出至像素电源VDD而使浮动扩散部FD复位。

[0089] 放大晶体管Amp具有连接至浮动扩散部FD的栅极电极和连接至像素电源VDD的漏极电极。此外,放大晶体管Amp输出经过复位晶体管Rst的复位后的浮动扩散部FD的电位作为复位信号(复位电平)Vreset。另外,放大晶体管Amp输出经过传输晶体管TR0至TR3传输信号电荷后的浮动扩散部FD的电位作为光累积信号(信号电平)Vsig。

[0090] 选择晶体管Sel具有连接至放大晶体管Amp的源极电极的漏极电极和连接至例如垂直信号线L1的源极电极。高有效选择脉冲 $\phi_{SEL}$ 通过选择线(未示出)而被施加于选择晶体管Sel的栅极电极。通过施加选择脉冲 $\phi_{SEL}$ ,选择晶体管Sel导通以选择单元像素,且从放大晶体管Amp输出的信号被转发至垂直信号线L1。

[0091] 此外,选择晶体管Sel也可以连接在放大晶体管Amp的漏极与像素电源VDD之间。

[0092] (像素共用单元与CF编码单元之间的关系)

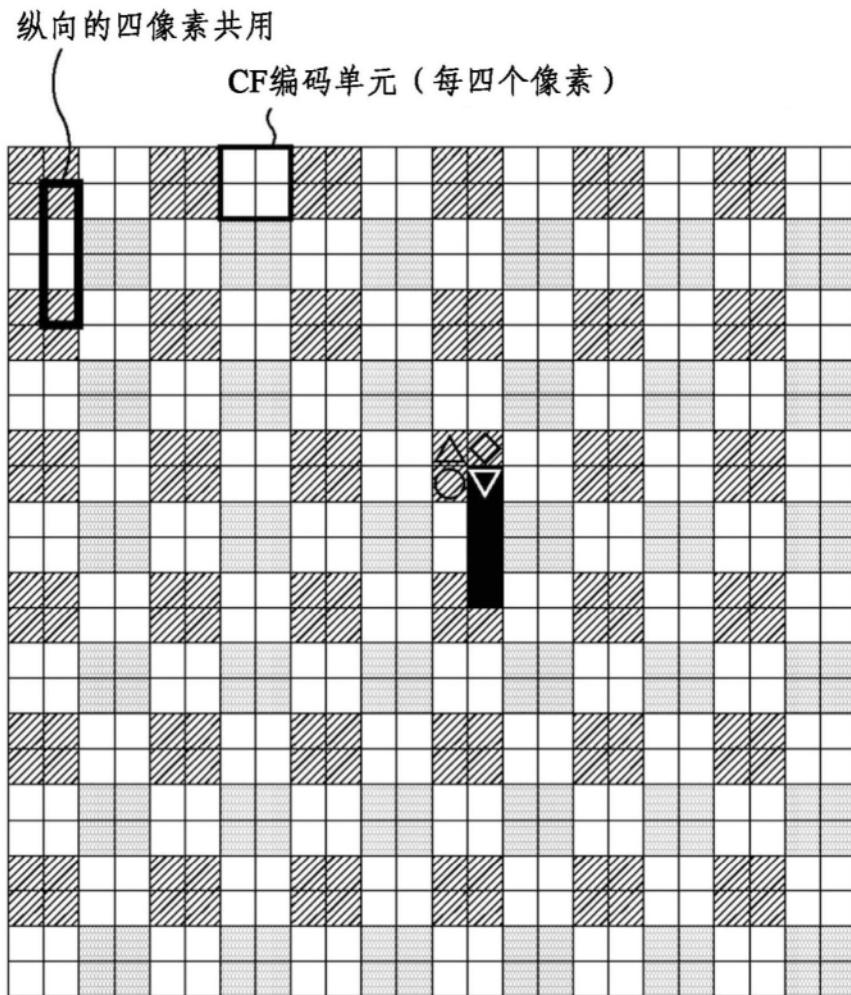

[0093] 图5示出了 $2 \times 2$ 像素共用单元与滤色器(CF)编码单元之间的关系。在图5所示的示例中,没有阴影的方格表示绿色(green)像素、斜线阴影的方格表示红色(red)像素且其余阴影的方格表示蓝色(blue)像素。这同样适于下面的其它附图。在图5所示的示例中,用粗实线示出了 $2 \times 2$ 像素共用的示例,并且用实线示出了每四个像素进行相同滤色器的RGB方格编码(拜耳阵列)的示例。

[0094] 即,在图5所示的示例中,像素共用单元与相同滤色器的编码单元以一对一的方式彼此对应,且用相同的滤色器对像素共用单元的 $2 \times 2$ 像素之中的各个像素进行编码。

[0095] 因此,当由于浮动扩散部的泄漏等而造成在中央的黑的 $2 \times 2$ 像素部中产生白点时,能够考虑使用图5中的由数字1至4所示的布置于最周边位置的绿色像素来校正上述绿色像素。即,在图5所示的示例中,在单元像素中,使用在空间上分隔开两个像素的数据来校正上述绿色像素。

[0096] (本发明的像素共用单元与CF编码单元之间的关系)

[0097] 图6示出了应用了本发明的像素共用单元与滤色器(CF)编码单元之间的关系。在图6所示的示例中, $2 \times 2$ 像素共用的示例由粗实线示出,且每四个像素地进行了相同滤色器的RGB方格编码(拜耳阵列)的示例由实线示出。

[0098] 在图6所示的示例中,如粗实线所示,用不同的滤色器对像素共用单元的 $2 \times 2$ 像素之中的各个像素进行编码。换言之,同一滤色器的编码单元的四个像素由不同像素共用单元的像素形成。即,同一滤色器的编码单元的四个像素(以下,被适当地称为同色的四个相邻像素)是由彼此间无像素共用的像素形成的。

[0099] 此外,图6所示的滤色器35例如是通过使图5所示的滤色器向上移动一个像素并向右移动一个像素而形成的。

[0100] 因此,当由于浮动扩散部的泄漏等而造成在中央的黑的像素部内产生白点时,使用同一绿色滤色器的编码单元的由三角形、菱形和倒三角形表示的绿色像素中的至少一个绿色像素来进行黑的像素部内的例如由圆形表示的绿色像素的校正。关于所述校正,可以使用由三角形、菱形和倒三角形表示的绿色像素中的任何一个绿色像素,或者可以使用这些绿色像素中的两个或所有的绿色像素。

[0101] 即,在图6所示的示例中,用于校正的像素是相邻像素。因此,由于能够使用空间上靠近的数据进行校正,所以能够比图5所示的示例更好地抑制分辨率劣化。

[0102] 下文中将具体说明当产生白点时的像素校正方法。

[0103] (电子装置的构造的示例)

[0104] 图7是示出了作为应用了本发明的电子装置的相机装置的构造的示例的框图。在图7所示的电子装置中,当产生白点时进行上述校正。

[0105] 图7所示的相机装置100包括含有透镜组等的光学单元101、采用图1所示的各像素2的构造的固态摄像器件(摄像器件)1和作为相机信号处理电路的DSP(数字信号处理器)电路103。此外,相机装置100包括帧存储器104、显示单元105、记录单元106、操作单元107和电源单元108。DSP电路103、帧存储器104、显示单元105、记录单元106、操作单元107和电源单元108通过总线109彼此连接。

[0106] 光学单元101接收来自被摄物的入射光(图像光)并将图像形成在固态摄像器件1

的成像面上。固态摄像器件1以像素为单元将由光学单元101形成在成像面上的入射光的光量转换成电信号，并将电信号输出作为像素信号。当产生上述因浮动扩散部的泄漏而造成的白点时，DSP电路103校正从图1所示的输出电路7输出的信号。DSP电路103例如将校正过的信号存储在帧存储器104中。

[0107] 显示单元105由面板型显示器件(例如，液晶面板或有机EL(电致发光)面板)形成，并且显示由固态摄像器件1摄取的动态图像或静态图像。记录单元106将固态摄像器件1摄取的动态图像或静态图像记录在诸如录像带或DVD(数字通用光盘)等记录媒介上。

[0108] 操作单元107在用户的操作下发出用于相机装置100的各种功能的操作指令。电源单元108将作为DSP电路103、帧存储器104、显示单元105、记录单元106和操作单元107的操作电源的各种电力适当地供给至上述部件。

[0109] (DSP电路的构造的示例)

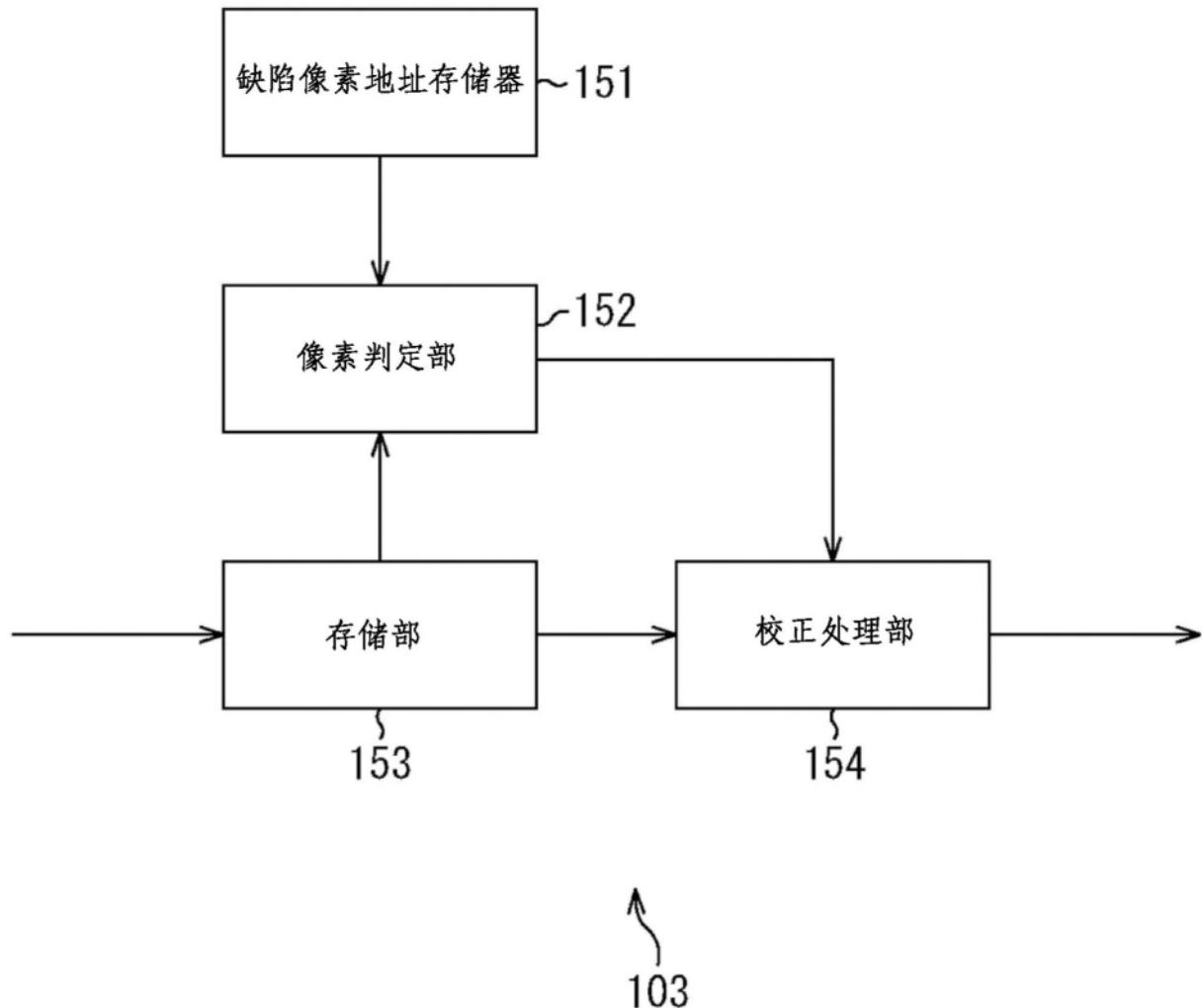

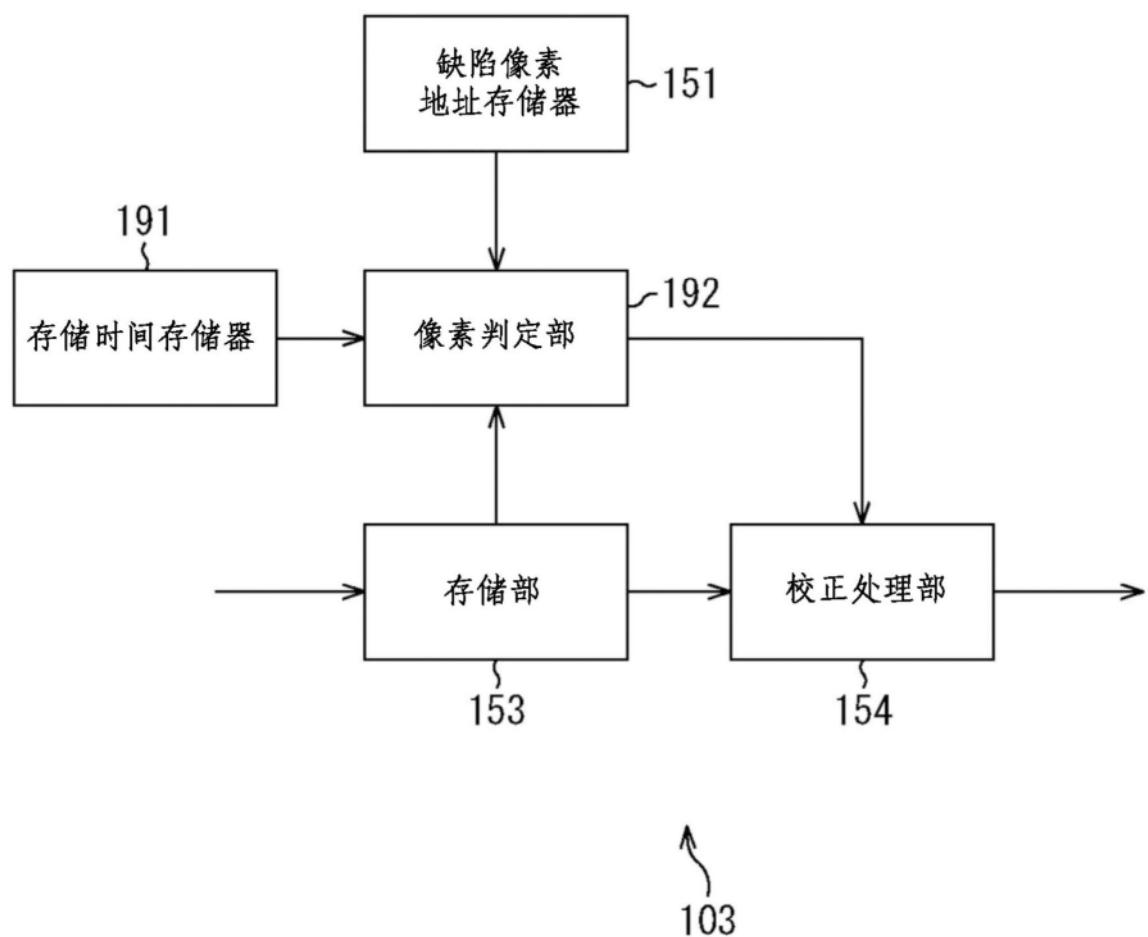

[0110] 图8是示出了当产生白点时进行像素校正的DSP电路的构造的第一示例的框图。

[0111] 在图8所示的示例中，DSP电路103被构造为包括缺陷像素地址存储器151、像素判定部152、存储部153和校正处理部154。

[0112] 缺陷像素地址存储器151存储在工厂中被判定为缺陷像素的缺陷像素的地址。如下地进行缺陷像素的判定。例如，对于白点，在工厂中将输出等于或高于工厂中OPB基准的暗状态的输出的像素判定为白点。另一方面，在HL点缺陷的情况下，在工厂中将这样的像素确定为缺陷像素：其该像素中，同色的输出与一定量的输入光的比率等于或高于某一比率(缺失滤色器(CF))或者等于或小于某一比率(污物)。如上所述判定的缺陷像素的地址被写入缺陷像素地址存储器151。

[0113] 像素判定部152参照存储于缺陷像素地址存储器151内的缺陷像素地址来判断缺陷像素是否被包含在存储于存储部153的图像中的同色的四个相邻像素的单元(CF的编码单元)中。像素判定部152根据判断结果(即，同色的四个相邻像素单元中的缺陷像素的数量(百分比))来控制校正处理部154的校正处理。

[0114] 存储部153例如是帧存储器。存储部153暂时存储从固态摄像器件1的输出电路7输出的信号(图像)。

[0115] 校正处理部154以每同色的四个相邻像素为单位从存储部153读取像素数据，根据来自像素判定部152的控制对像素数据进行校正处理并且输出结果。

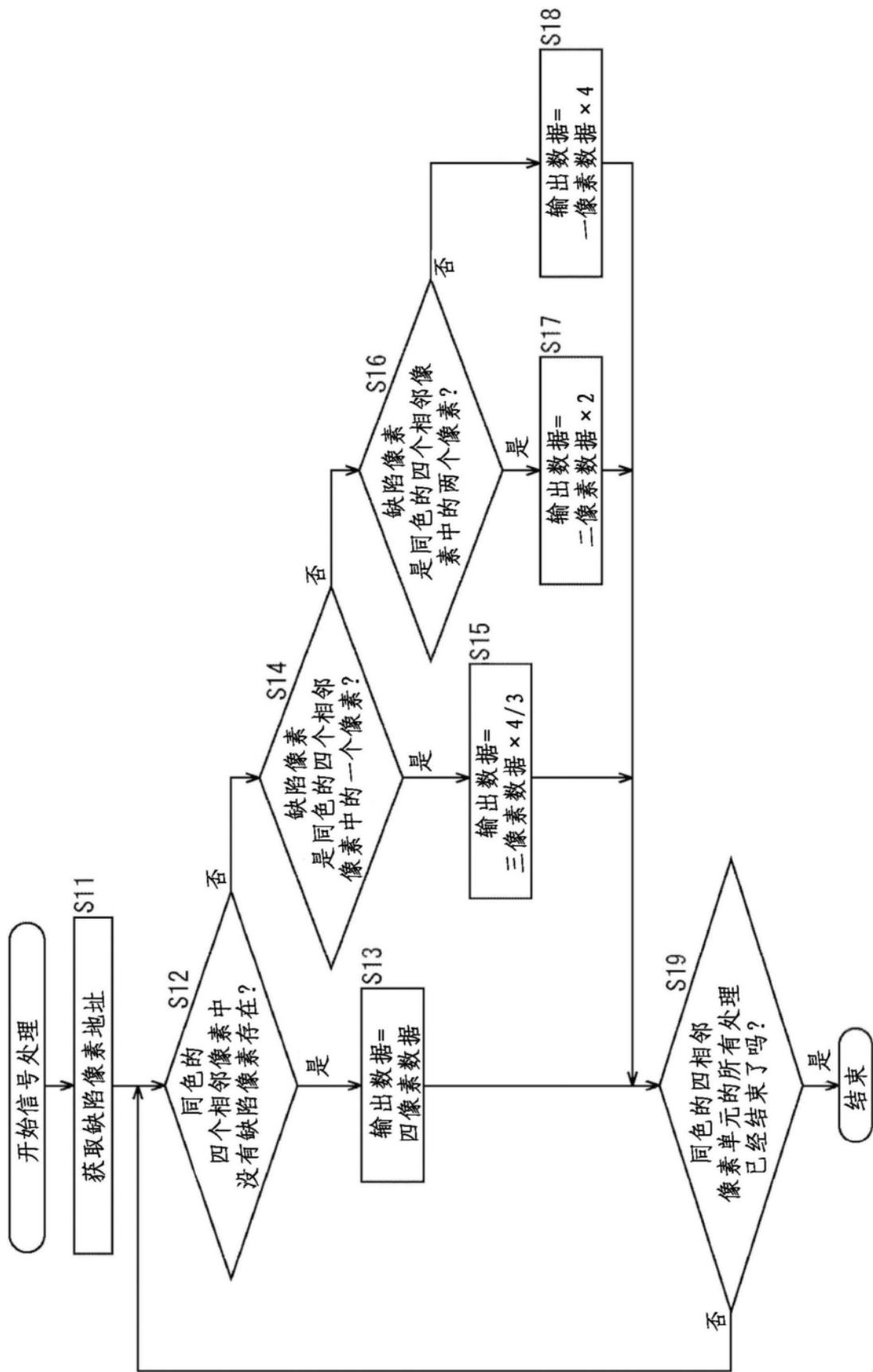

[0116] (信号处理的示例)

[0117] 接着，将参照图9所示的流程图说明由图8所示的DSP电路103进行的信号处理的示例。以作为CF的编码单元的同色的四个相邻像素为单位进行上述信号处理。例如，所述信号处理是输出同色的四个相邻像素的单元的像素数据作为加运算数据(added data)的处理。此外，将适当地参照图6说明 $2 \times 2$ 像素共用单元作为示例。

[0118] 从固态摄像器件1的输出电路7输出的信号(图像)被存储在存储部153中。校正处理部154从存储部153读取待处理的同色的四个相邻像素(CF的编码单元)。

[0119] 在步骤S11中，像素判定部152从缺陷像素地址存储器151获取图像的缺陷像素地址。此外，也能够以每四个待处理的同色的相邻像素地方式获取缺陷像素地址。

[0120] 在步骤S12中，像素判定部152参照在步骤S11中获取的缺陷像素地址来判断在待处理的同色的四个相邻像素中是否存在缺陷像素。当步骤S12中判定没有缺陷像素存在

时,处理前进至步骤S13。

[0121] 在步骤S13中,在像素判定部152的控制下,校正处理部154不进行校正而将从存储部153读取的同色的四个相邻像素的四像素数据(four-pixel data)作为输出数据输出至例如帧存储器104。

[0122] 当步骤S12中判定缺陷像素存在时,处理前进至步骤S14。在步骤S14中,像素判定部152参照在步骤S11中获取的缺陷像素地址来判断同色的四个相邻像素中的一个像素是否是缺陷像素。

[0123] 当步骤S14中判定同色的四个相邻像素中的一个像素是缺陷像素时,处理前进至步骤S15。在步骤S15中,在像素判定部152的控制下,校正处理部154将通过把同色的四个相邻像素之中除了缺陷像素以外的三像素数据(three-pixel data)乘以4/3而获得的结果作为输出数据输出至帧存储器104。

[0124] 例如,当由图6中的圆形表示的绿色像素是缺陷像素时,使用同一绿色滤色器的编码单元的由三角形、菱形和倒三角形表示的绿色像素的数据。具体地,将由三角形、菱形和倒三角形表示的绿色像素的数据的和乘以4/3,并将结果输出作为同色的四个相邻像素的输出数据。

[0125] 当在步骤S14中判定同色的四个相邻像素之中的缺陷像素不是一个像素时,处理前进至步骤S16。在步骤S16中,像素判定部152参照在步骤S11中获取的缺陷像素地址来判断同色的四个相邻像素之中的两个像素是否是缺陷像素。

[0126] 当在步骤S16中判定同色的四个相邻像素之中的两个像素是缺陷像素时,处理前进至步骤S17。在步骤S17中,在像素判定部152的控制下,校正处理部154将通过把同色的四个相邻像素之中的除了缺陷像素之外的二像素数据(two-pixel data)乘以2而获得的结果作为输出数据输出至帧存储器104。

[0127] 例如,当由图6中的圆形和三角形表示的绿色像素是缺陷像素时,使用同一绿色滤色器的编码单元的由菱形和倒三角形表示的绿色像素的数据。具体地,将由菱形和倒三角形表示的绿色像素的数据的和乘以2,并输出结果作为同色的四个相邻像素的输出数据。

[0128] 当步骤S16中判定同色的四个相邻像素之中的缺陷像素不是两个像素时,即,当在步骤S16中同色的四个相邻像素之中的三个像素是缺陷像素时,处理前进至步骤S18。在步骤S18中,在像素判定部152的控制下,校正处理部154将通过把同色的四个相邻像素之中除了缺陷像素以外的一像素数据(one-pixel data)乘以4而获得的结果作为输出数据输出至帧存储器104。与这个示例有关,同色的四个相邻像素都是缺陷像素的情况非常罕见。在这样的情况下,在CMOS图像传感器发货之前进行分类拣选,以使得上述情况的CMOS图像传感器不被发送。

[0129] 例如,当由图6中的圆形、三角形和菱形表示的绿色像素是缺陷像素时,使用同一绿色滤色器的编码单元的由倒三角形表示的绿色像素的数据。具体地,将由倒三角形表示的绿色像素的数据乘以4,并输出结果作为同色的四个相邻像素的输出数据。

[0130] 在步骤S19中,像素判定部152判断图像中的同色的四相邻像素单元的所有处理是否已经结束。当步骤S19中判定对同色的四相邻像素单元的处理还没有结束时,处理返回至步骤S12以重复用于接下来待处理的同色的四相邻像素单元的处理。当步骤S19中判定对同色的四相邻像素单元的处理已经结束时,这个信号处理结束。

[0131] 如上所述,当同色的四个相邻像素中存在缺陷像素时,与缺陷像素同一滤色器的编码单元的像素数据被用于缺陷像素数据的校正。

[0132] 根据装置,图8所示的缺陷像素地址存储器151的容量可能不足。下面将说明与这样的装置相对应的处理的示例。

[0133] (DSP电路的构造的示例)

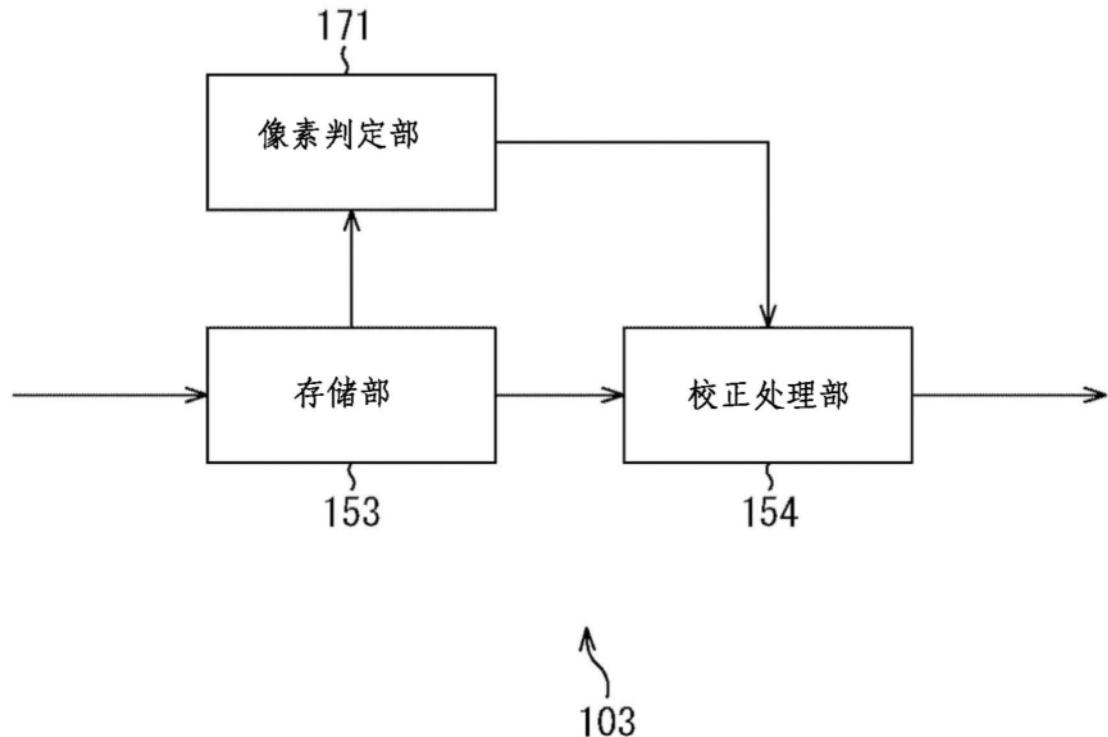

[0134] 图10是示出了当产生白点时进行像素校正的DSP电路的构造的第二示例的框图。

[0135] 图10所示的DSP电路103与图8所示的DSP电路103的不同之处在于:去除了缺陷像素地址存储器151且像素判定部152被像素判定部171替代。图10所示的DSP电路103与图8所示的DSP电路103的相同之处在于设置有存储部153和校正处理部154。

[0136] 即,像素判定部171使校正处理部154对同色的所有四个相邻像素进行中值处理以使点缺陷能够被动态地校正。此外,在加运算输出的情况下,优选进行所有像素的中值处理,并且在乘以所有像素的数量后将结果输出作为输出数据。

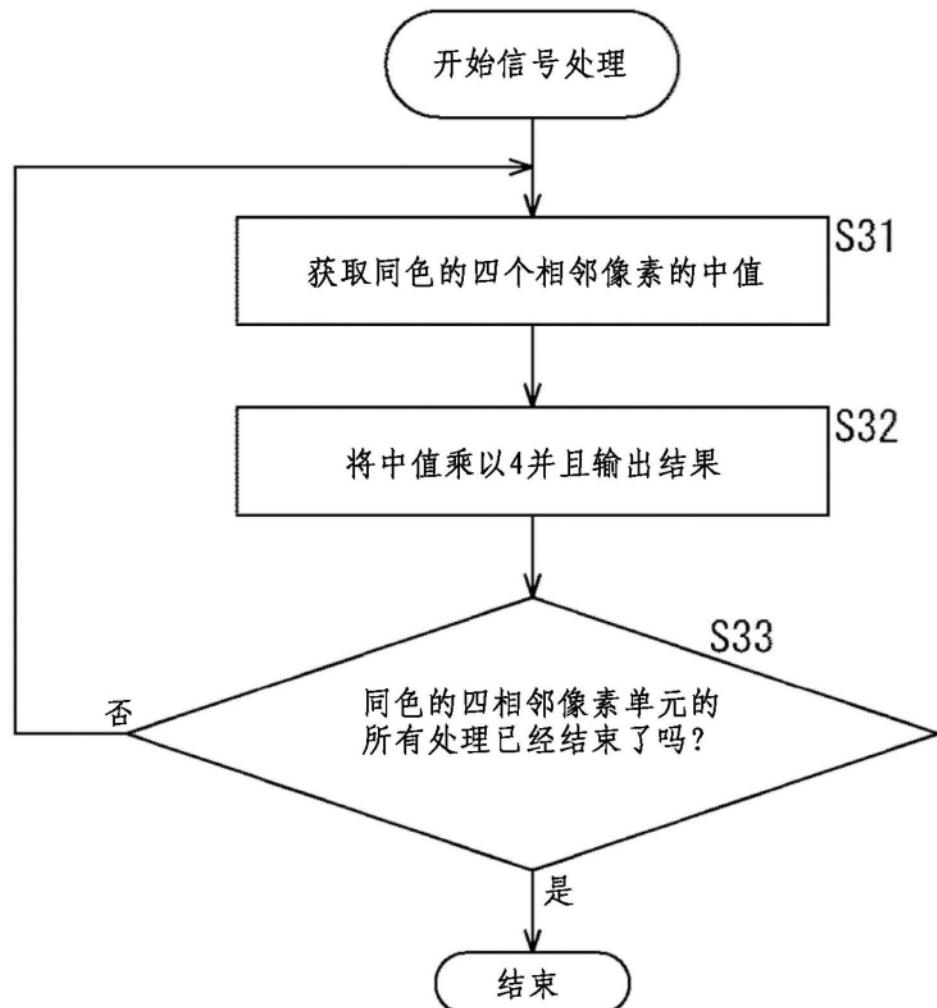

[0137] (信号处理的示例)

[0138] 接着,将参照图11所示的流程图说明由图10所示的DSP电路103进行的信号处理的示例。这个信号处理是在同色的四相邻像素单元中进行的。例如,这个信号处理是这样的处理:将同色的四个相邻像素的像素数据作为加运算数据输出至后续级。此外,将适当地参照图6说明 $2 \times 2$ 像素共用单元作为示例。

[0139] 从固态摄像器件1的输出电路7输出的信号(图像)被存储于存储部153。校正处理部154从存储部153读取待处理的同色的四个相邻像素。

[0140] 在步骤S31中,校正处理部154在像素判定部171的控制下获得从存储部153读取的同色的四个相邻像素的像素中值。在步骤S32中,在像素判定部171的控制下,校正处理部154将上述中值乘以4并输出结果作为输出数据。此外,在没有输出作为加运算数据的处理的情况下,省去步骤S32的处理,且将中值输出至后续级。

[0141] 在步骤S33中,像素判定部171判断图像中的同色的四相邻像素单元的所有处理是否已经结束。当步骤S33中确定对同色的四相邻像素单元的处理还没有结束时,处理返回至步骤S31以重复对于接下来待处理的同色的四相邻像素单元的处理。当步骤S33中确定对同色的四相邻像素单元的处理已经结束时,这个信号处理结束。

[0142] 如上所述,通过在作为CF的编码单元的同色的四个相邻像素中进行中值处理能够容易地校正白点。此外,还能够校正HL点缺陷。因此,即使在难以充分保证缺陷像素地址存储器151的容量的装置中,也能够抑制白点校正中的分辨率劣化。

[0143] 接着,为了确保高的动态范围,将说明当改变存储时间以进行图像处理时的示例。

[0144] (DSP电路的构造的示例)

[0145] 图12是示出了当产生白点时进行像素校正的DSP电路的构造的第三示例的框图。

[0146] 图12所示的DSP电路103与图8所示的DSP电路103的不同之处在于:增加了存储时间存储器191且像素判定部152被像素判定部192替代。图12所示的DSP电路103与图8所示的DSP电路103的相同之处设置有缺陷像素地址存储器151、存储部153和校正处理部154。

[0147] 在固态摄像器件1中,通过改变每个像素的光(电荷)的存储时间能够获得高的动态范围。例如,在图12所示的示例中,设定有两类存储时间A和B,且存储时间存储器191存储每个像素的存储时间(A或B)。此外,存储时间存储器191可以置于像素判定部192内。

[0148] 像素判定部192参照存储于缺陷像素地址存储器151内的缺陷像素地址来判断存储于存储部153的图像中的同色的四个相邻像素之中是否包含缺陷像素。当包含有缺陷像素时,像素判定部192参照存储时间存储器191来判定缺陷像素和同色的四个相邻像素之中的相同存储时间内的像素,并且根据判定结果(存储时间)来控制校正处理部154的校正处理。

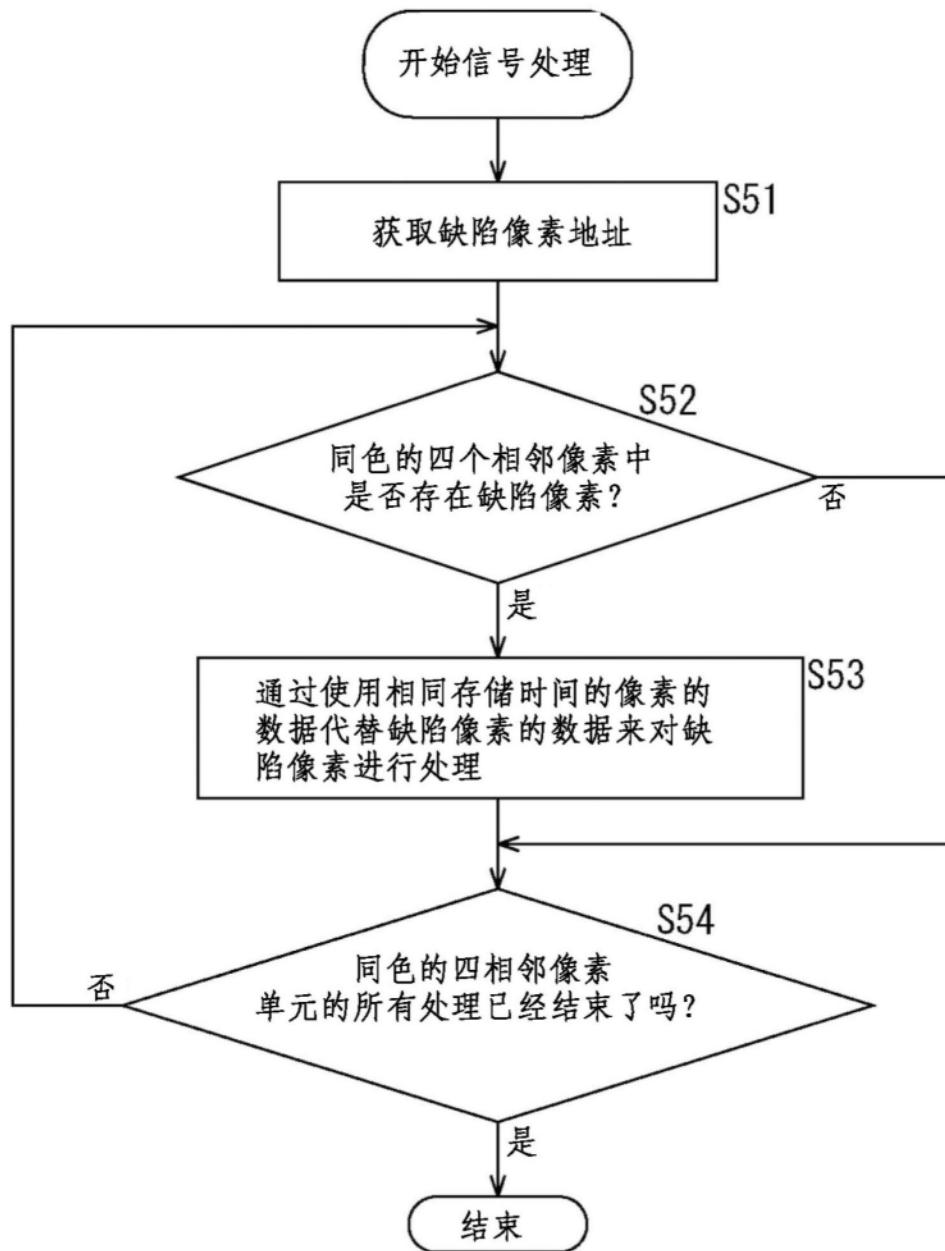

[0149] (信号处理的示例)

[0150] 接着,将参照图13所示的流程图说明由图12所示的DSP电路103进行的信号处理的示例。这个信号处理是在同色的四相邻像素单元中进行的。例如,这个信号处理是这样的处理:将同色的四个相邻像素的像素数据输出至后续级。此外,将适当地参照图6说明 $2 \times 2$ 像素共用单元作为示例。

[0151] 从固态摄像器件1的输出电路7输出的信号(图像)被存储于存储部153。校正处理部154从存储部153读取待处理的同色的四相邻像素单元。

[0152] 在步骤S51中,像素判定部192从缺陷像素地址存储器151获取图像的缺陷像素地址。此外,还能够以每四个待处理的同色的相邻像素的方式获取缺陷像素地址。

[0153] 在步骤S52中,像素判定部192参照步骤S51中获取的缺陷像素地址来判断待处理的同色的四个相邻像素中是否存在缺陷像素。当在步骤S52中判定存在缺陷像素时,处理前进至步骤S53。

[0154] 在步骤S53中,在像素判定部192的控制下,校正处理部154通过使用相同存储时间的像素的数据代替缺陷像素的数据来对缺陷像素进行处理。

[0155] 即,像素判定部192确定缺陷像素和同色的四个相邻像素之中的相同存储时间内的像素,并通过使用相同存储时间的图像的数据代替缺陷像素的数据来对缺陷像素进行处理。

[0156] 在图6所示的示例中,假设由圆形和倒三角形表示的绿色像素被设定为存储时间A且由三角形和菱形表示的绿色像素被设定为存储时间B,那么当由圆形表示的绿色像素是缺陷像素时,通过使用由倒三角形表示的像素的数据代替缺陷像素的数据来进行用于由圆形表示的绿色像素的处理。例如,在图6所示的示例中,假设通过交换存储时间使得由圆形和菱形表示的绿色像素被设定为存储时间A且由三角形和倒三角形表示的绿色像素被设定为存储时间B,那么当由圆形表示的绿色像素是缺陷像素时,通过使用由菱形表示的像素的数据代替缺陷像素的数据来进行用于由圆形表示的绿色像素的处理。

[0157] 此外,作为步骤S53中进行的处理的示例,例如在一像素输出(one-pixel output)的情况下,输出替代数据作为输出数据。在加运算数据输出的情况下,使用替代数据,并且将输出数据相加以输出。

[0158] 如上所述,即使当确保高的动态范围时,也能够抑制白点校正中的分辨率劣化。

[0159] (效果的说明)

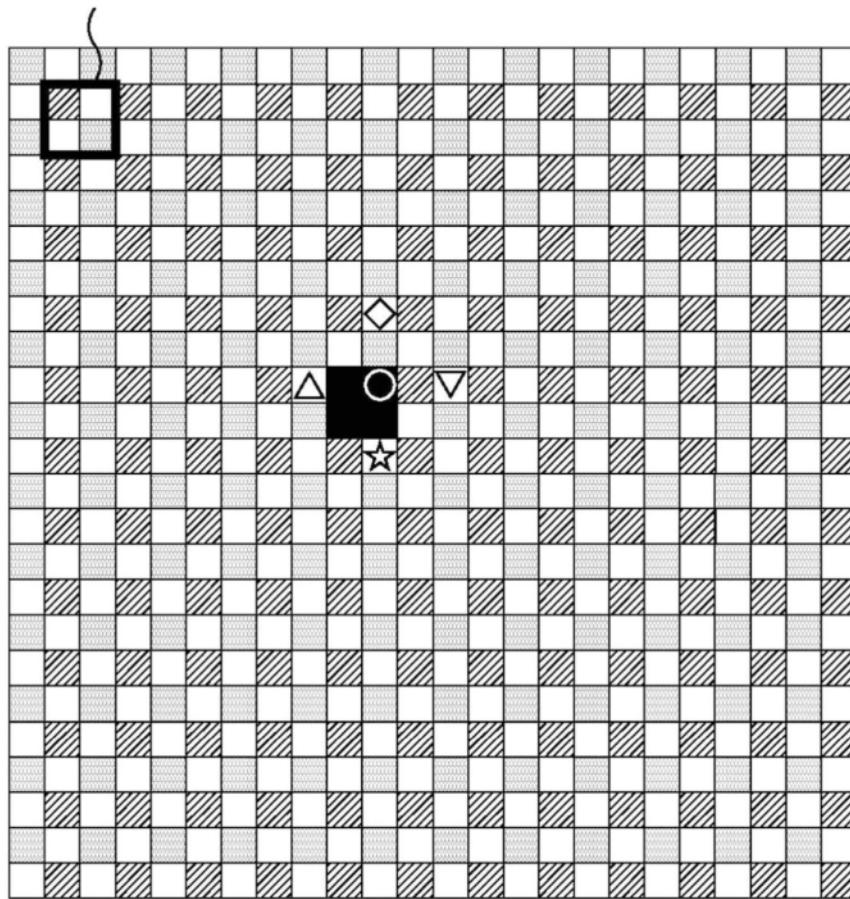

[0160] 在图6所示的示例中,仅 $2 \times 2$ 像素共用单元中的 $2 \times 2$ 像素的滤色器排列与图14的示例所示的普通方格RGB拜耳阵列(即,各像素的方格RGB拜耳阵列)相同。当仅观察 $2 \times 2$ 像素共用单元时,分别从存储器读取这些像素。

[0161] 然而,在图14所示的拜耳阵列中,当包含由圆形表示的绿色像素的共用单元中存在缺陷像素时,使用由三角形、菱形、倒三角形和星形表示的与由圆形表示的绿色像素相隔

一个像素的邻近绿色像素的数据(所述数据是被分别读取的)来替代由圆形表示的绿色像素的数据。或者,需要使用由三角形、菱形、倒三角形和星形表示的与由圆形表示的绿色像素相隔一个像素的邻近绿色像素的数据的平均值来进行缺陷校正。

[0162] 与此相比,在图6所示的示例中,因为从存储器中读取同色的四相邻像素单元(CF的编码单元)的数据,所以能够立刻进行同色的四相邻像素单元的校正。如上所述,图14所示的示例中的信号处理不同于图6所示的示例中的信号处理。

[0163] 如上所述,即使因像素共用单元内的浮动扩散部的泄漏等而产生白点,也能够使用不同像素共用单元的同色的像素进行白点校正。因为上述像素在空间上靠近缺陷像素,所以相比于上述像素在空间上远离缺陷像素的情况能够更好地抑制图像劣化。

[0164] 此外,尽管上面已经说明了像素共用单元是 $2 \times 2$ 像素的情况,但是像素共用单元不限于 $2 \times 2$ 像素,且也可以使用 $2 \times 2$ 像素以外的像素共用单元。以下,将说明其它的像素共用单元。

[0165] 2. 第二实施例( $2 \times 4$ 像素共用的示例)

[0166] (像素共用单元的构造的示例)

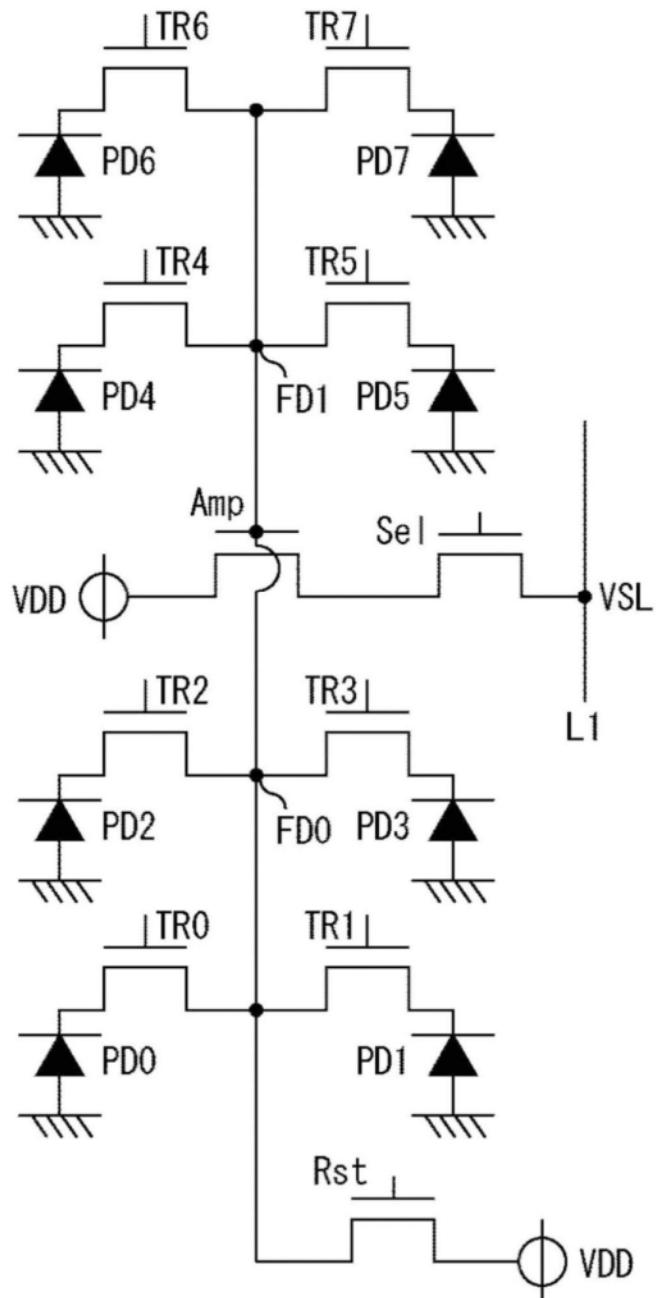

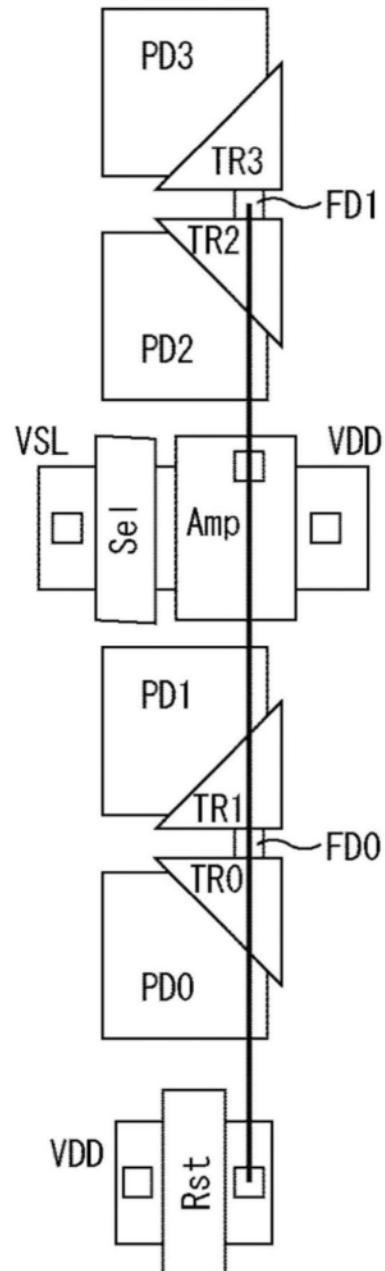

[0167] 首先,将参照图15和图16说明 $2 \times 4$ 像素共用单元的电路构造的示例。图15是示出了 $2 \times 4$ 像素共用单元的电路构造的示例的电路图。图16是示出了 $2 \times 4$ 像素共用单元的电路构造的示例的平面图。此外,参照图15和图16所述的 $2 \times 4$ 像素共用单元与参照图3和图4所述的 $2 \times 2$ 像素共用单元仅在像素的数量上不同,且各晶体管等的基本功能均相同。

[0168] 如图15和图16所示, $2 \times 4$ 像素共用单元被构造为包括八个光电转换元件(例如,光电二极管PD0至PD7)、与光电二极管PD0至PD7相对应的八个传输晶体管TR0至TR7以及复位晶体管Rst、放大晶体管Amp和选择晶体管Sel这三个晶体管。

[0169] 光电二极管PD0至PD7具有连接至负电源(例如,地)的阳极电极,并且进行将接收的光转换为电荷量与接收的光量相对应的光电荷(在这里,光电子)的光电转换。光电二极管PD0至PD7的阴极电极通过对应的传输晶体管TR0至TR7电连接至放大晶体管Amp的栅极电极。放大晶体管Amp的栅极电极电连接至四个传输晶体管TR0至TR3的节点被称为浮动扩散部FD0。放大晶体管Amp的栅极电极电连接至四个传输晶体管TR4至TR7的节点被称为浮动扩散部FD1。

[0170] 传输晶体管TR0至TR3连接在相应的光电二极管PD0至PD3的阴极电极与浮动扩散部FD0之间。此外,传输晶体管TR4至TR7连接在相应的光电二极管PD4至PD7的阴极电极与浮动扩散部FD1之间。

[0171] 高电平(例如,VDD电平)有效(以下,被称为“高有效”)传输脉冲 $\phi_{TRF}$ 经由传输线(未示出)被施加至传输晶体管TR0至TR7的栅极电极。通过施加传输脉冲 $\phi_{TRF}$ ,传输晶体管TR0至TR3导通,且由光电二极管PD0至PD3内的光电转换产生的光电荷被传输至浮动扩散部FD0。同样,通过施加传输脉冲 $\phi_{TRF}$ ,传输晶体管TR4至TR7导通,且由光电二极管PD4至PD7内的光电转换产生的光电荷被传输至浮动扩散部FD1。

[0172] 复位晶体管Rst具有连接至像素电源VDD的漏极电极和连接至浮动扩散部FD0的源极电极。在信号电荷从光电二极管PD0至PD3传输至浮动扩散部FD0以及从光电二极管PD4至PD7传输至浮动扩散部FD1之前,高有效复位脉冲 $\phi_{RST}$ 经由复位线(未示出)被施加至复位晶体管Rst的栅极电极。通过施加复位脉冲 $\phi_{RST}$ 使复位晶体管Rst导通,且通过将浮动扩散

部FD0和FD1的电荷排出至像素电源VDD来使浮动扩散部FD0和FD1复位。

[0173] 放大晶体管Amp具有连接至浮动扩散部FD0和FD1的栅极电极和连接至像素电源VDD的漏极电极。此外,放大晶体管Amp将经过复位晶体管Rst的复位后的浮动扩散部FD0和FD1的电位输出作为复位信号(复位电平)Vreset。此外,放大晶体管Amp将经过传输晶体管TR0至TR3传输信号电荷后的浮动扩散部FD0的电位和经过传输晶体管TR4至TR7传输信号电荷后的浮动扩散部FD1的电位输出作为光累积信号(信号电平)Vsig。

[0174] 选择晶体管Sel具有例如连接至放大晶体管Amp的源极电极的漏极电极和连接至垂直信号线L1的源极电极。高电平有效选择脉冲 $\phi_{SEL}$ 经由选择线(未示出)被施加至选择晶体管Sel的栅极电极。通过施加选择脉冲 $\phi_{SEL}$ ,选择晶体管Sel导通以选择单元像素,且从放大晶体管Amp输出的信号被转发至垂直信号线L1。

[0175] 此外,选择晶体管Sel也可以连接在放大晶体管Amp的漏极与像素电源VDD之间。

[0176] (像素共用单元与CF编码单元之间的关系)

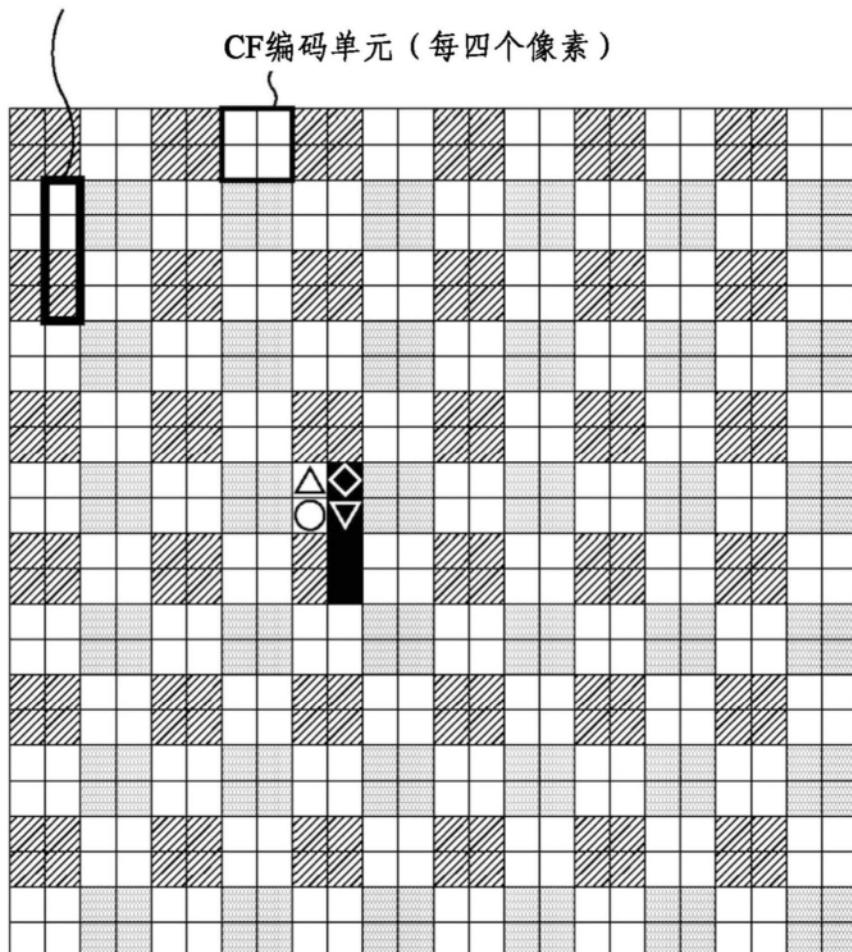

[0177] 图17示出了 $2 \times 4$ 像素共用单元与滤色器(CF)编码单元之间的关系。在图17所示的示例中, $2 \times 4$ 像素共用的示例由粗实线示出,且以每四个像素的方式进行相同滤色器的RGB方格编码(拜耳阵列)的示例由实线示出。

[0178] 即,在图17所示的示例中,像素共用单元的 $2 \times 4$ 像素的上半部分的四个像素使用相同的滤色器进行编码并且下半部分的四个像素使用相同的滤色器进行编码。

[0179] 因此,当由于浮动扩散部的泄漏等而造成中央的黑色的 $2 \times 4$ 像素部内产生白点时,能够考虑使用由图中的数字1至4所示的布置于最周边位置处的绿色像素来校正以圆形表示的绿色像素。即,在图17所示的示例中,使用单元像素中的在空间上分隔了两个像素的数据来校正圆形表示的绿色像素。

[0180] (本发明的像素共用单元与CF编码单元之间的关系)

[0181] 图18示出了应用了本发明的像素共用单元与滤色器(CF)的编码单元之间的关系。在图18所示的示例中, $2 \times 4$ 像素共用的示例由粗实线示出,且以每四个像素的方式进行了相同滤色器的RGB方格编码(拜耳阵列)的示例由实线示出。

[0182] 在图18所示的示例中,如图18中的粗实线所示,像素共用单元的 $2 \times 4$ 像素的两个上部像素用不同的滤色器进行编码,两个下部像素也用不同的滤色器进行编码。如图18中的粗实线所示,像素共用单元的 $2 \times 4$ 像素的中央的四个像素中每两个像素使用相同的滤色器进行编码。换言之,同一滤色器的编码单元的四个像素被构造为包括彼此之间无像素共用的像素。即,同一滤色器的编码单元的四个像素被构造为使得至少该构造的一半是不同的像素共用单元的像素。

[0183] 此外,图18中所示的滤色器35例如是通过使图17所示的滤色器向上移动一个像素并向右移动一个像素形成的。

[0184] 因此,当由于浮动扩散部的泄漏等而造成中央的黑色的像素部内产生白点时,使用同一绿色滤色器的编码单元的由三角形、菱形和倒三角形表示的绿色像素中的至少一个绿色像素来进行黑色的像素部内的由圆形表示的绿色像素的校正。

[0185] 即,在图18所示的示例中,用于校正的像素是相邻像素。因此,由于能够使用空间上靠近的数据进行校正,所以能够比图17所示的示例更好地抑制分辨率劣化。

[0186] 此外,因为当产生白点时进行像素校正的电子装置的构造基本上与上文中参照图

7说明的图6的示例中的电子装置的构造相同,所以将省去该构造的说明。此外,因为当产生白点时用于进行像素校正的信号处理的示例基本上与参照图9、11和13说明的信号处理相同,所以将省去该信号处理的说明。

[0187] 即,对于像素共用单元的 $2 \times 4$ 像素的两个上部像素和两个下部像素,以与图6所示的示例中的方式基本上相同的方式进行图9和图13所示的示例中的信号处理。另一方面,对于像素共用单元的 $2 \times 4$ 像素的中心的四个像素,因为同一像素共用单元中包括各滤色器的两个像素,所以以与将在后面说明的图19所示的情况中的方式进行图9和图13所示的示例中的信号处理。

[0188] 此外, $2 \times 4$ 像素共用单元与CF编码单元之间的关系可以如下。

[0189] (本发明的像素共用单元与CF编码单元之间的关系)

[0190] 图19示出了应用了本发明的像素共用单元与滤色器(CF)的编码单元之间的关系。在图19所示的示例中, $2 \times 4$ 像素共用的示例由粗实线示出,且以每四个像素的方式进行了相同滤色器的RGB方格编码(拜耳阵列)的示例由实线示出。

[0191] 在图19所示的示例中,与图18所示的像素共用单元的中心的四个像素的情况类似,如图19中的粗实线所示,像素共用单元的 $2 \times 4$ 像素的各个像素中每两个像素使用相同的滤色器进行编码。换言之,同一滤色器的编码单元的四个像素被构造为包括彼此之间无像素共用的像素。即,同一滤色器的编码单元的四个像素被构造为使得至少该构造的一半是不同的像素共用单元的像素。

[0192] 此外,图19所示的滤色器35例如是通过使图17所示的滤色器向右移动一个像素形成的。

[0193] 因此,当由于浮动扩散部的泄漏等而造成中心的黑色像素部内产生白点时,使用同一绿色滤色器的编码单元的由菱形和倒三角形表示的绿色像素来进行黑色的像素部内的由三角形和圆形表示的绿色像素的校正。

[0194] 即,在图19所示的示例中,用于校正的像素是相邻像素。因此,因为能够使用空间上靠近的数据进行校正,所以能够比图17所示的示例更好地抑制分辨率劣化。

[0195] 此外,因为当产生白点时进行像素校正的电子装置的构造基本上与上文中参照图7说明的图6的示例中的电子装置的构造相同,所以将省去该构造的说明。此外,因为当产生白点时用于进行像素校正的信号处理的示例基本上与参照图9、11和13说明的信号处理相同,所以将省去该信号处理的说明。

[0196] 即,在像素共用单元的 $2 \times 4$ 像素中,各滤色器的两个像素(例如,图19中的由三角形和圆形表示的像素)包含于同一像素共用单元。因此,特别地,在图19所示的示例中,与上述步骤S17的处理类似地进行当像素共用单元的两个像素是缺陷像素时的信号处理。

[0197] 此外,在图13所示的示例中,假设由圆形表示的像素和由倒三角表示的像素被设定为存储时间A且由三角形表示的像素和由菱形表示的像素被设定为存储时间B(假设存在两类存储时间),那么能够使用由倒三角形表示的像素的数据来替代由圆形表示的缺陷像素的数据。此外,能够使用由菱形表示的像素的数据来替代由三角形表示的缺陷像素的数据。

[0198] 如上所述,即使当像素共用单元是 $2 \times 4$ 像素,也能够抑制白点校正中的分辨率劣化。

[0199] 3. 第三实施例( $1 \times 4$ 像素共用的示例)

[0200] (像素共用单元的构造的示例)

[0201] 首先,将参照图20和图21说明 $1 \times 4$ 像素共用单元的电路构造的示例。图20是示出了 $1 \times 4$ 像素共用单元的电路构造的示例的电路图。图21是示出了 $1 \times 4$ 像素共用单元的电路构造的示例的平面图。此外,参照图20和图21所述的 $2 \times 4$ 像素共用单元与参照图3和图4所述的 $2 \times 2$ 像素共用单元仅在像素的数量上不同,且晶体管等的基本功能相同。

[0202] 如图20和图21所示, $1 \times 4$ 像素共用单元被构造为包括四个光电转换元件(例如,光电二极管PD0至PD3)、与光电二极管PD0至PD3相对应的四个传输晶体管TR0至TR3以及复位晶体管Rst、放大晶体管Amp和选择晶体管Sel这三个晶体管。

[0203] 光电二极管PD0至PD3具有连接至负电源(例如,地)的阳极电极,并且进行将接收的光转换成电荷量与接收的光量相对应的光电荷(在这里,光电子)的光电转换。光电二极管PD0至PD3的阴极电极通过对应的传输晶体管TR0至TR3电连接至放大晶体管Amp的栅极电极。放大晶体管Amp的栅极电极电连接至两个传输晶体管TR0至TR1的节点被称为浮动扩散部FD0。放大晶体管Amp的栅极电极电连接至两个传输晶体管TR2至TR3的节点被称为浮动扩散部FD1。

[0204] 传输晶体管TR0至TR3连接在相应的光电二极管PD0至PD3的阴极电极与浮动扩散部FD0或FD1之间。高电平(例如,VDD电平)有效(以下,被称为“高有效”)传输脉冲 $\phi_{TRF}$ 经由传输线路(未示出)被施加至传输晶体管TR0至TR3的栅极电极。通过施加传输脉冲 $\phi_{TRF}$ ,传输晶体管TR0至TR3导通,且由光电二极管PD0至PD3内的光电转换产生的光电荷被传输至浮动扩散部FD0或FD1。

[0205] 复位晶体管Rst具有连接至像素电源VDD的漏极电极和连接至浮动扩散部FD0和FD1的源极电极。在信号电荷从光电二极管PD0和PD1传输至浮动扩散部FD0以及从光电二极管PD2和PD3传输至浮动扩散部FD1之前,高有效复位脉冲 $\phi_{RST}$ 经由复位线(未示出)被施加至复位晶体管Rst的栅极电极。通过施加复位脉冲 $\phi_{RST}$ 使复位晶体管Rst导通,且通过将浮动扩散部FD0和FD1的电荷排出至像素电源VDD来复位浮动扩散部FD0和FD1。

[0206] 放大晶体管Amp具有连接至浮动扩散部FD0和FD1的栅极电极和连接至像素电源VDD的漏极电极。此外,放大晶体管Amp将经过复位晶体管Rst的复位后的浮动扩散部FD0和FD1的电位输出作为复位信号(复位电平)Vreset。此外,放大晶体管Amp将经过传输晶体管TR0和TR1传输信号电荷后的浮动扩散部FD0的电位和经过传输晶体管TR2和TR3传输信号电荷后的浮动扩散部FD1的电位输出作为光累积信号(信号电平)Vsig。

[0207] 选择晶体管Sel具有例如连接至放大晶体管Amp的源极电极的漏极电极和连接至垂直信号线L1的源极电极。高电平有效选择脉冲 $\phi_{SEL}$ 通过选择线(未示出)被施加至选择晶体管Sel的栅极电极。通过施加选择脉冲 $\phi_{SEL}$ ,选择晶体管Sel导通以选择单元像素,且从放大晶体管Amp输出的信号被转发至垂直信号线L1。

[0208] 此外,选择晶体管Sel也可以连接在放大晶体管Amp的漏极与像素电源VDD之间。

[0209] (本发明的像素共用单元与CF编码单元之间的关系)

[0210] 图22示出了应用了本发明的像素共用单元与滤色器(CF)的编码单元之间的关系。在图22所示的示例中, $1 \times 4$ 像素共用的示例由粗实线示出,且以每四个像素的方式进行了相同滤色器的RGB方格编码(拜耳阵列)的示例由实线示出。

[0211] 在图22所示的示例中,如图22中的粗实线所示,像素共用单元的 $1 \times 4$ 像素的一个上部像素、一个下部像素用不同的滤色器进行编码。如图22中的粗实线所示,像素共用单元的 $1 \times 4$ 像素的中心的两个像素用相同的滤色器进行编码。换言之,同一滤色器的编码单元的四个像素被构造为包括彼此之间无像素共用的像素。即,同一滤色器的编码单元的四个像素被构造为使得该构造的至少一半是不同的像素共用单元的像素。

[0212] 因此,当由于浮动扩散部的泄漏等而造成中央的黑色的像素部内产生白点时,使用同一红色滤色器的编码单元的由三角形、菱形和圆形表示的红色像素来进行黑色的像素部内的由倒三角形表示的红色像素的校正。

[0213] 即,因为用于校正的像素是相邻像素,所以能够使用空间上靠近的数据进行校正。因此,能够抑制分辨率劣化。

[0214] 此外, $1 \times 4$ 像素共用单元与CF编码单元之间的关系可以如下。

[0215] (本发明的像素共用单元与CF编码单元之间的关系)

[0216] 图23示出了应用了本发明的像素共用单元与滤色器(CF)的编码单元之间的关系。在图23所示的示例中, $1 \times 4$ 像素共用的示例由粗实线示出,且以每四个像素的方式进行了相同滤色器的RGB方格编码(拜耳阵列)的示例由实线示出。

[0217] 在图23所示的示例中,与图22所示的像素共用单元的中心的四个像素的情况类似,如图23中的粗实线所示,像素共用单元的 $1 \times 4$ 像素的各像素以每两个像素使用同一滤色器的方式进行编码。换言之,同一滤色器的编码单元的四个像素被构造为包括彼此之间无像素共用的像素。即,同一滤色器的编码单元的四个像素被构造为使得该构造的至少一半是不同的像素共用单元的像素。

[0218] 因此,当由于浮动扩散部的泄漏等而造成中心的黑色的像素部内产生白点时,使用同一绿色滤色器的编码单元的由三角形和圆形表示的绿色像素来进行黑色的像素部内的由菱形和倒三角形表示的绿色像素的校正。

[0219] 即,因为用于校正的像素是相邻像素,所以能够使用空间上靠近的数据进行校正。因此,能够抑制分辨率劣化。

[0220] 如上所述,即使当像素共用单元是 $1 \times 4$ 像素时,也能够抑制白点校正中的分辨率劣化。

[0221] 此外,尽管上面已经说明了当像素共用单元是 $2 \times 2$ 像素、 $2 \times 4$ 像素和 $1 \times 4$ 像素时的情况,但是本发明也能够同样适用于其它的像素共用单元。

[0222] 此外,尽管上面已经说明了RGB方格颜色编码,但是本发明也能够适用于含有W的RGBW,只要相同颜色编码用于四个像素即可。此外,本发明也能够适用于RGBW以外的多颜色编码。

[0223] 此外,尽管上面已经说明了底面发光型固态摄像器件,但是本发明也能够适用于顶面发光型固态摄像器件。

[0224] 4. 第四实施例

[0225] (固态摄像器件的横截面的示例)

[0226] 图24是示出了本发明的固态摄像器件的像素区域和周边电路部的结构的示例的横截面图。在图24所示的示例中,示出了顶面发光型固态摄像器件的示例。

[0227] 图24的示例中的固态摄像器件201具有这样的构造:其中,像素区域210和周边电

路部220集成在同一芯片(基板)上,像素区域210进行入射光的光电转换,周边电路部220驱动像素以读取信号,对读取的信号进行信号处理并且输出结果。此外,形成像素区域210的晶体管和形成周边电路部220的晶体管共用一些它们的配线线路。图1所示的像素区域3被应用为像素区域210。

[0228] 像素区域210具有这样的结构:其中,光电二极管212形成在具有约几百微米厚度的N型硅基板211的顶面侧,且滤色器215和OCL(片上透镜)216布置于光电二极管212上方并且在滤色器215和OCL 216与光电二极管212之间布置有配线层213和钝化层214。滤色器215被设置用来获得彩色信号。此外,图2所示的滤色器35被应用为滤色器215。

[0229] 在像素区域210中,晶体管或配线线路存在于光电二极管212与滤色器215之间。因此,为了增加入射光电二极管212的光与入射像素区域210的光的比率,即,孔径比,入射光穿过配线线路后被OCL 216会聚至光电二极管212。

[0230] 与固态摄像器件1类似,固态摄像器件201具有上述滤色器215的编码单元和像素共用单元的关系。因此,因为能够使用空间上靠近的数据进行白点校正,所以能够抑制分辨率劣化。

[0231] 此外,本发明不限于被应用至例如图像传感器等固态摄像器件。即,本发明能够被应用于使用固态摄像器件作为摄像单元(光电转换单元)的各种电子装置,诸如包含数码相机和摄像机在内的摄像装置、具有摄像功能的便携式终端装置以及使用固态摄像器件作为图像读取单元的复印机等。

[0232] 5.第五实施例

[0233] (计算机的构造的示例)

[0234] 可以由硬件执行或可以由软件执行上述的一系列处理。当使用软件执行一系列处理时,将该软件的程序安装在计算机上。在这里,计算机的示例包括置于专用硬件内的计算机和通过安装各种程序能够执行各种功能的通用个人计算机。

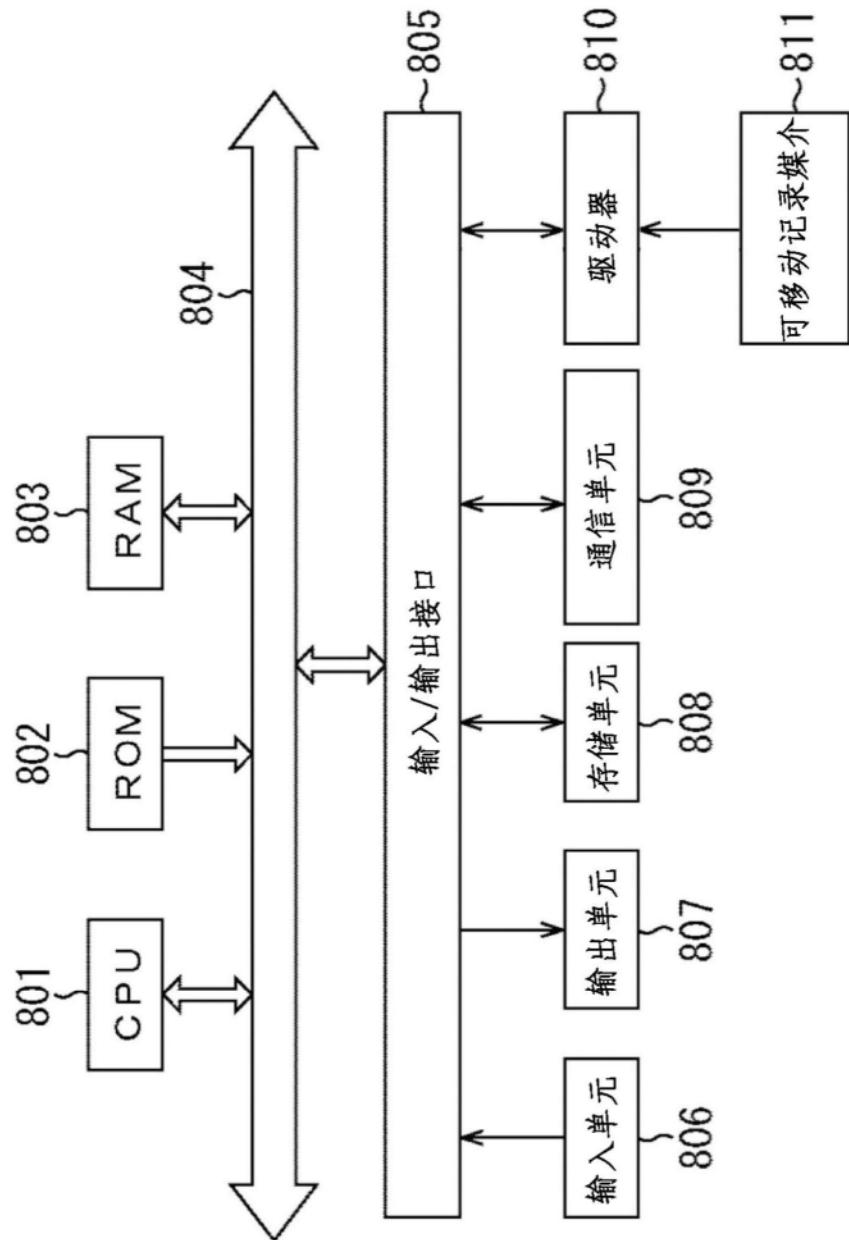

[0235] 图25是示出了使用程序执行上述的一系列处理的计算机的硬件构造的示例的框图。

[0236] 在计算机800中,CPU(中央处理单元)801、ROM(只读存储器)802和RAM(随机存取存储器)803通过总线804彼此连接。

[0237] 输入/输出接口805连接至总线804。输入单元806、输出单元807、存储单元808、通信单元809和驱动器810连接至输入/输出接口805。

[0238] 输入单元806被构造为包括键盘、鼠标和麦克风等等。输出单元807被构造为包括显示器和扬声器等等。存储单元808被构造为包括硬盘和非易失性存储器等等。通信单元809被构造为包括网络接口等。驱动器810驱动诸如磁盘、光盘、磁光盘或半导体存储器等等可移动记录媒介811。

[0239] 在如上所述的构造的计算机中,例如,CPU 801通过输入/输出接口805和总线804将存储于存储单元808内的程序加载至RAM 803并且执行该程序,从而执行上述的一系列处理。

[0240] 由计算机800(CPU 801)执行的程序能够通过例如被记录在作为包媒介等的可移动记录媒介811上而被提供。此外,程序能够通过诸如局域网、因特网或数字卫星广播等等有线或无线传输媒介而被提供。

[0241] 通过将可移动记录媒介811安装在驱动器810中,计算机能够经由输入/输出接口805将程序安装在存储单元808中。此外,能够在通信单元809经由有线或无线传输媒介接收程序后,将程序安装在存储单元808中。此外,能够预先将程序安装在ROM 802或存储单元808中。

[0242] 此外,由计算机执行的程序可以是用于按照本说明书所述的顺序以时序方式进行处理的程序,或可以是用于并行地或在诸如进行调用时等的必要时刻进行处理的程序。

[0243] 此外,在本说明书中,用于描述记录于记录媒介上的程序的步骤不仅包括根据上述顺序以时序方式进行的处理,而且还包括不必以时序方式进行的并行进行或单独进行的处理。

[0244] 此外,在本说明书中,系统表示由多个器件形成的整个装置。

[0245] 此外,本发明的实施例不限于上述的实施例,且也能够在不脱离本发明的主旨和范围的情况下作出各种修改。

[0246] 此外,上面流程图中所述的每个步骤可以由一个器件执行或可以被执行为由多个器件共用。

[0247] 此外,当一个步骤中包含多个处理时,包含于一个步骤中的多个处理可以由一个器件执行或可以被执行为由多个器件共用。

[0248] 此外,作为一个器件(或一个处理单元)的上述组件可以被分成多个器件(或多个处理单元)。可替代地,作为多个器件(或多个处理单元)的上述组件可以被集成为一个器件(或一个处理单元)。此外,每个器件(或每个处理单元)当然可以被构造为包括上述组件以外的组件。此外,只要作为整个系统的构造或操作本质上相同,某器件(或某处理单元)的一部分构造可以包含于另一个器件(或另一个处理单元)的构造中。即,本发明不限于上述实施例,且能够在不脱离本发明的范围的情况下作出各种变化。

[0249] 虽然已经参照附图详细地说明了本发明的优选实施例,但是本发明不限于这样的示例。本领域技术人员显然知晓在随附的权利要求书所披露的技术理念的范围内能够作出各种变化和修改;且本领域技术人员应当毫无疑义地理解的是,这些变化和修改也属于本发明的技术范围。

[0250] 此外,本发明能够采用下面的构造。

[0251] (1)一种固态摄像器件,其包括:

[0252] 多个像素构成的组,所述多个像素构成的组被构造为包含相同颜色编码并且彼此之间无像素共用的像素;和

[0253] 滤色器,所述滤色器是以所述多个像素构成的组的拜耳排列形式形成的。

[0254] (2)根据(1)所述的固态摄像器件,

[0255] 其中,所述多个像素构成的组是由彼此之间无像素共用的像素形成的。

[0256] (3)根据(1)或(2)所述的固态摄像器件,

[0257] 其中,所述像素共用的单元是 $2 \times 2$ 像素。

[0258] (4)根据(1)所述的固态摄像器件,

[0259] 其中,所述多个像素构成的组的至少一半是彼此之间无像素共用的像素。

[0260] (5)根据(1)或(4)所述的固态摄像器件,

[0261] 其中,所述像素共用的单元是 $2 \times 4$ 像素。

- [0262] (6) 根据(1)或(4)所述的固态摄像器件，

[0263] 其中，所述像素共用的单元是 $1 \times 4$ 像素。

[0264] (7) 根据(1)至(6)中任一项所述的固态摄像器件，

[0265] 其中，使用所述多个像素构成的组内的像素来校正所述像素共用的单元内产生的缺陷像素。

[0266] (8) 根据(1)至(7)中任一项所述的固态摄像器件，

[0267] 其中，所述多个像素构成的组包括四个像素。

[0268] (9) 根据(1)至(8)中任一项所述的固态摄像器件，

[0269] 其中，所述颜色编码是原色方格的编码。

[0270] (10) 根据(1)至(8)中任一项所述的固态摄像器件，

[0271] 其中，所述颜色编码是WRGB的编码。

[0272] (11) 一种信号处理器件，其包括：

[0273] 校正处理单元，在从包括被构造为包含相同颜色编码且彼此之间无像素共用的像素的多个像素构成的组和以所述多个像素构成的组的拜耳排列形式形成的滤色器的固态摄像器件输出的输出信号中，所述校正处理单元使用所述多个像素构成的组内的像素来校正像素共用单元内产生的缺陷像素。

[0274] (12) 根据(11)所述的信号处理器件，

[0275] 其中，所述校正处理单元根据所述像素共用单元内产生的所述缺陷像素的数量使用所述多个像素构成的组内的像素来校正所述像素共用单元内产生的所述缺陷像素。

[0276] (13) 根据(11)所述的信号处理器件，

[0277] 其中，所述校正处理单元使用所述多个像素构成的组内的所有像素来校正所述像素共用单元内产生的所述缺陷像素。

[0278] (14) 根据(11)所述的信号处理器件，

[0279] 其中，所述校正处理单元根据所述像素共用单元内产生的所述缺陷像素的存储时间使用所述多个像素构成的组内的数据来校正所述像素共用单元内产生的所述缺陷像素。

[0280] (15) 一种电子装置，其包括：

[0281] 固态摄像器件，所述固态摄像器件包括被构造为包含相同颜色编码且彼此之间无像素共用的像素的多个像素构成的组和以所述多个像素构成的组的拜耳排列形式形成的滤色器；

[0282] 光学系统，所述光学系统使入射光入射到所述固态摄像器件；和

[0283] 信号处理电路，所述信号处理电路处理从所述固态摄像器件输出的输出信号。

[0284] [参考符号列表]

[0285] 1 固态摄像器件

[0286] 2 像素

[0287] 3 像素区域

[0288] 100 相机装置

[0289] 101 光学单元

[0290] 103 DSP电路

[0291] 104 帧存储器

- [0292] 151 缺陷像素地址存储器

- [0293] 152 像素判定部

- [0294] 153 存储部

- [0295] 154 校正处理部

- [0296] 171 像素判定部

- [0297] 191 存储时间存储器

- [0298] 192 像素判定部

- [0299] 201 固态摄像器件

- [0300] 相关申请的交叉参考

- [0301] 本申请主张享有于2013年10月31日提交的日本优先权专利申请JP 2013-226299的权益，并将该日本优先权申请的全部内容以引用的方式并入本文。

图1

图2

图3

图4

35

图6

图7

图8

图10

图11

图12

图13

2 × 2 像素共用

图14

图15

图16

图17

2 × 4像素共用

35

图18

35

图19

图20

图21

35

图22

纵向的四像素共用

35

图23

图24

图25