# (19) World Intellectual Property Organization

International Bureau

(43) International Publication Date 27 September 2007 (27.09.2007) (10) International Publication Number WO 2007/109046 A2

(51) International Patent Classification: H01L 27/24 (2006.01) G11C 16/02 (2006.01)

(21) International Application Number:

PCT/US2007/006425

(22) International Filing Date: 14 March 2007 (14.03.2007)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

60/782,379 15 March 2006 (15.03.2006) US 11/637.967 13 December 2006 (13.12.2006) US

(63) Related by continuation (CON) or continuation-in-part (CIP) to earlier application:

US 11/637.967 (CON) Filed on 13 December 2006 (13.12.2006)

- (71) Applicant (for all designated States except US): MAR-VELL WORLD TRADE LTD. [BB/BB]; L'Horizon Gunsight Road, Brittons Hill, St. Michael, BB 14027 (BB).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): SUTARDJA, Pantas [US/US]; 18690 Blythswood Drive, Los Gatos, California 95030 (US). WU, Albert [US/US]; 3801 Nathan Way, Palo Alto, California 94303 (US).

- (74) Agents: WIGGINS, Michael D. et al.; Harness, Dickey & Pierce, P.l.c., P.O. Box 828, Bloomfield Hills, Michigan 48303 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, MT, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### **Published:**

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: CROSS-POINT MEMORY ARRAY

(57) Abstract: A phase-change memory (PCM) system comprises a PCM cell array that comprises a plurality of PCM cells. Each of the PCM cells includes diode arranged adjacent to a metallization layer; a heater element arranged adjacent to the diode, and a phase-change material arranged adjacent to the heater element.

## CROSS-POINT MEMORY ARRAY

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application claims the benefit of U.S. Provisional Application No. 60/782,379, filed on 15 March 2006, and U.S. Application Number 11/637,967, filed 13 December 2006. The disclosure of the above application is incorporated herein by reference in its entirety.

5

15

20

25

30

#### **FIELD**

10 **[0002]** The present disclosure relates to memory and, more particularly, to memory arrays including phase-change materials.

#### **BACKGROUND**

[0003] The Background description provided herein is for the purpose of generally presenting the context of the disclosure. Work of the presently named inventors, to the extent it is described in this background section, as well as aspects of the description which may not otherwise qualify as prior art at the time of filing, are neither expressly or impliedly admitted as prior art against the present disclosure.

[0004] Phase-change materials have been proposed for use in memory devices. Phase-change materials may be electrically programmed between various states. These states range from fully amorphous to fully crystalline. In a fully crystalline state, the phase-change material exhibits a low resistance. In a fully amorphous state, the phase-change material exhibits a high resistance. Phase-change materials may be used as binary memories by varying the resistance of the phase-change material.

[0005] Random access memory (RAM) utilizing phase-change materials has competed unfavorably against other memory technologies, such as flash memory. This is because flash memory typically has a density that is 2-4 times greater than the densest phase-change memory.

#### **SUMMARY**

[0006] A phase-change memory (PCM) system comprises a PCM cell array that comprises a plurality of PCM cells. Each of the PCM cells includes a diode arranged adjacent to a metallization layer. A heater element is arranged adjacent to the diode, and a phase-change material is arranged adjacent to the heater element. The diode includes an amorphous silicon layer that is deposited over the metallization layer. The amorphous silicon layer is crystallized using a seeding metal. The diode includes a Schottky diode or a junction diode. The diode thermally communicates with the metallization layer.

5

10

15

20

25

30

[0007] In other features, a system comprises the PCM system and further comprises a non-memory circuit that includes the metallization layer. The PCM system is integrated with the non-memory circuit. The diode thermally communicates with the metallization layer. In other features, a system comprises the PCM system and further comprises a memory circuit that includes the metallization layer. The PCM system is integrated with the memory circuit. The diode thermally communicates with the metallization layer. N bits of user data are stored in each of the plurality of PCM cells, where N is an integer greater than one.

[0008] In other features, a portable electronic device comprises an integrated circuit comprising a metallization layer. A block-based mass storage device comprises a PCM array integrated with the integrated circuit and arranged adjacent to the metallization layer. The PCM array comprises a plurality of PCM cells each including a diode arranged adjacent to the metallization layer, a heater element arranged adjacent to the diode, and a phase-change material arranged adjacent to the heater element. The portable electronic device is selected from a group consisting of: cell phones, laptop computers, personal digital assistants, hand-held gaming devices, and media players. N bits of user data are stored in each of the plurality of PCM cells, where N is an integer greater than one.

[0009] In other features, for the portable device, the diode includes an amorphous silicon layer that is deposited over the metallization layer. The amorphous silicon layer is crystallized using a seeding metal. The diode

includes a Schottky diode or a junction diode. The diode thermally communicates with the metallization layer.

[0010] In other features, a PCM cell fabrication method comprises arranging a diode adjacent to a metallization layer and arranging a heater element adjacent to the diode. The method further comprises arranging a phase-change material adjacent to the heater element. An amorphous silicon layer is deposited over the metallization layer and crystallized using a seeding metal to form the diode. The diode includes a Schottky diode or a junction diode.

5

10

15

20

25

30

[0011] In other features, a phase-change data storage system comprises phase-change storing means for storing data. The phase-change storing means comprises a plurality of memory cells. Each of the memory cells includes current restricting means for selectively restricting current flow, and the current restricting means are arranged adjacent to a metallization layer. The memory cells further comprise heating means for heating arranged adjacent to the current restricting means. The memory cells still further comprise phase change material arranged adjacent to the heating means.

[0012] In other features, the current restricting means includes an amorphous silicon layer that is deposited over the metallization layer. The amorphous silicon layer is crystallized using a seeding material. The current restricting means includes a Schottky diode or a junction diode. The current restricting means thermally communicates with the metallization layer.

[0013] In still other features, a system comprises the phase-change data storage system and further comprises a non-memory circuit that includes the metallization layer. The phase-change data storage system is integrated with the non-memory circuit. The current restricting means thermally communicates with the metallization layer.

[0014] In other features, a system comprises the phase-change data storage system and further comprises storing means for storing data. The system includes the metallization layer. The phase-change data storage system is integrated with the storing means. The current restricting means thermally

communicates with the metallization layer. N bits of user data are stored in each of the plurality of the memory cells, where N is an integer greater than one.

[0015] In other features, a portable electronic device comprises an integrated circuit that comprises a metallization layer. The integrated circuit further comprises a storage device that comprises the PCM system. The portable electronic device is selected from a group consisting of: cell phones, laptop computers, personal digital assistants, hand-held gaming devices, and media players. N bits of user data are stored in each of the plurality of cells, where N is an integer greater than one.

5

10

15

20

25

30

[0016] In other features, the current restricting means includes an amorphous silicon layer that is deposited over the metallization layer. The amorphous silicon layer is crystallized using a seeding material. The current restricting means includes a Schottky diode or a junction diode. The current restricting means thermally communicates with the metallization layer.

[0017] In still other features, a circuit comprises the PCM system and a bulk silicon transistor that communicates with the metallization layer. The bulk silicon transistor comprises a complimentary metal-oxide semiconductor (CMOS) transistor.

[0018] Further areas of applicability of the present disclosure will become apparent from the detailed description provided hereinafter. It should be understood that the detailed description and specific examples, while indicating the preferred embodiment of the disclosure, are intended for purposes of illustration only and are not intended to limit the scope of the disclosure

# **BRIEF DESCRIPTION OF THE DRAWINGS**

[0019] The present disclosure will become more fully understood from the detailed description and the accompanying drawings, wherein:

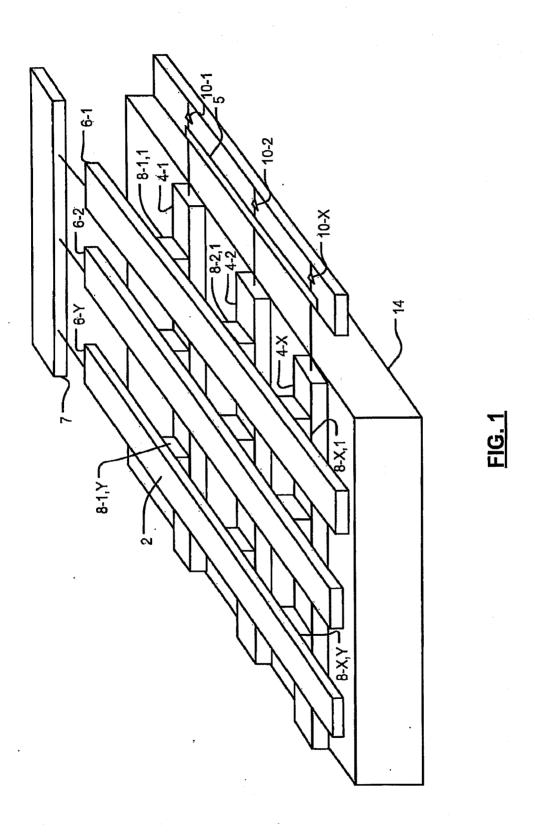

[0020] FIG. 1 is a perspective diagram of a cross-point memory array;

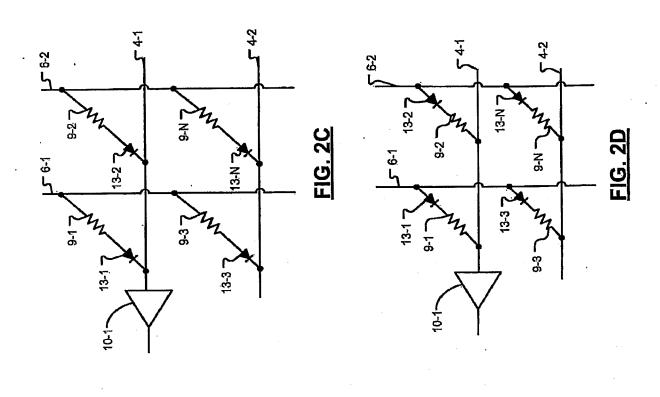

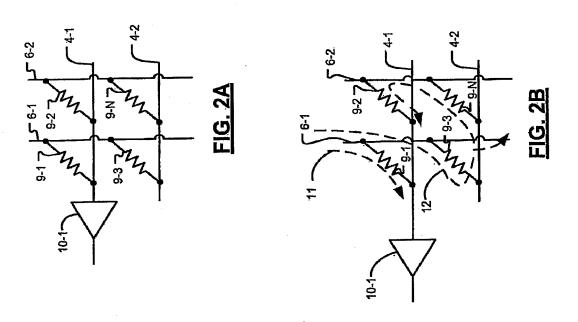

[0021] FIG. 2A is a simplified partial circuit diagram of a cross-point memory array;

[0022] FIG. 2B is a simplified partial circuit diagram of a cross-point memory array;

[0023] FIG. 2C is a simplified partial circuit diagram of a cross-point memory array including diodes;

[0024] FIG. 2D is a simplified partial circuit diagram of a cross-point memory array including diodes;

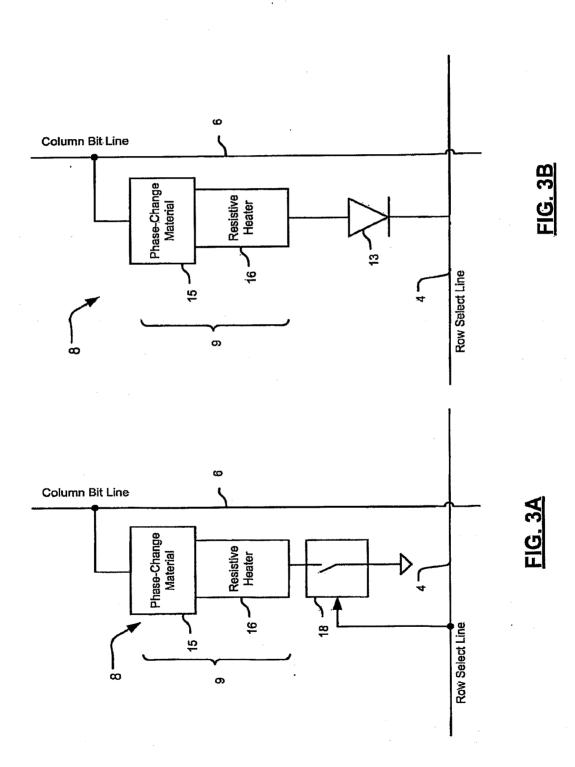

[0025] FIG. 3A is a functional block diagram of a phase-change memory cell;

5

15

20

25

30

[0026] FIG. 3B is a functional block diagram of a phase-change memory cell;

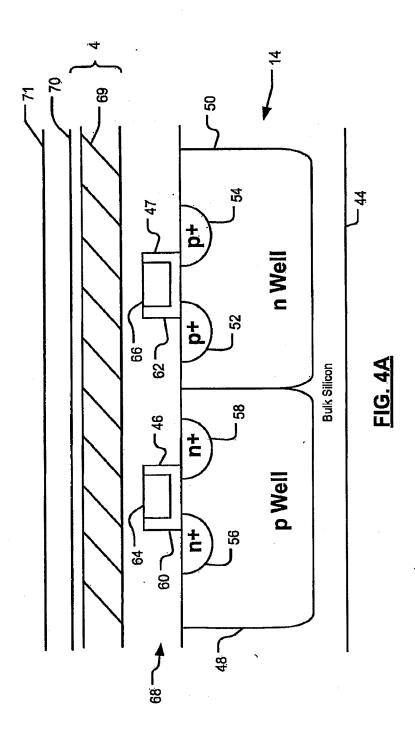

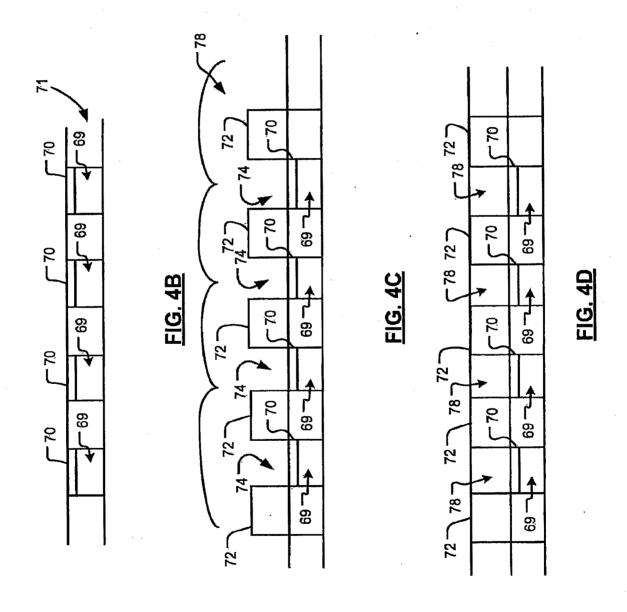

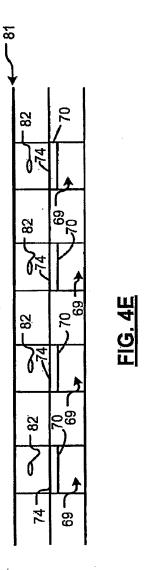

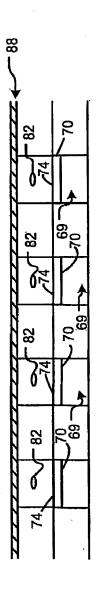

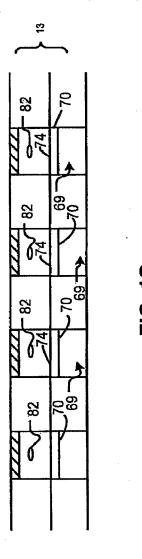

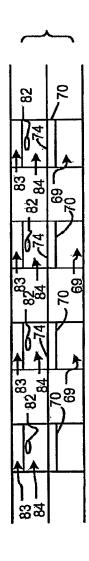

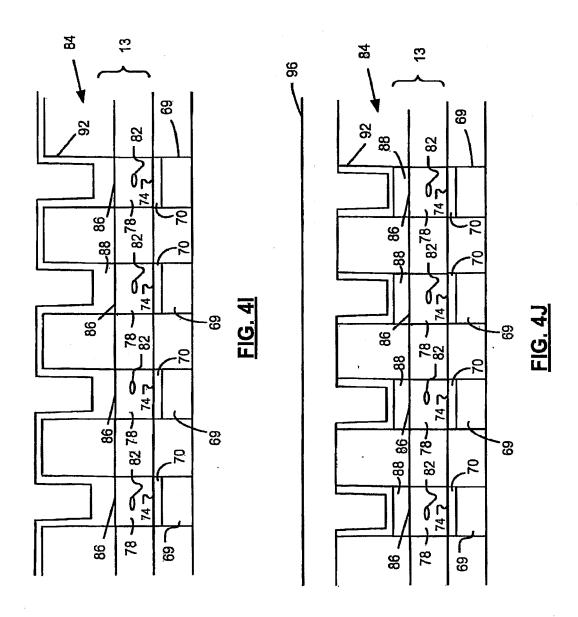

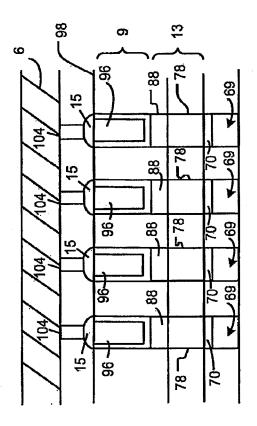

[0027] FIG. 4A-4K are partial cross sections of a cross-point memory array;

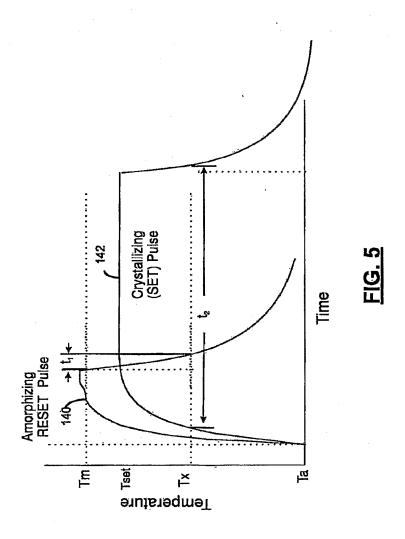

[0028] FIG. 5 is graph of a temperature profile for formation of an amorphous and crystalline state;

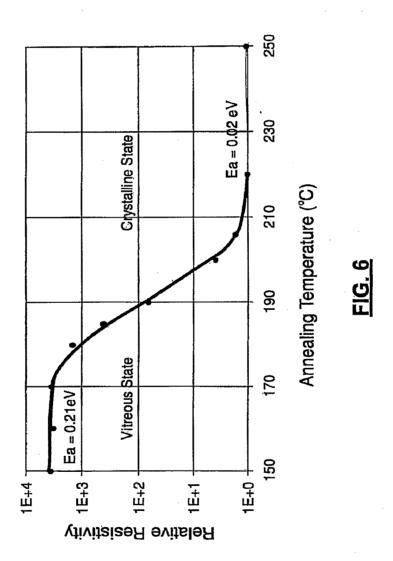

[0029] FIG. 6 is a graph of a resistivity change when an amorphous state phase-change material is annealed;

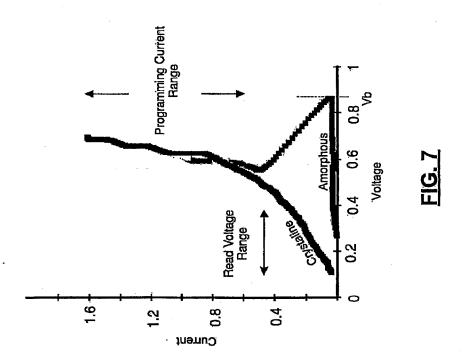

[0030] FIG. 7 is a graph of current and voltage characteristics of a phase-change material;

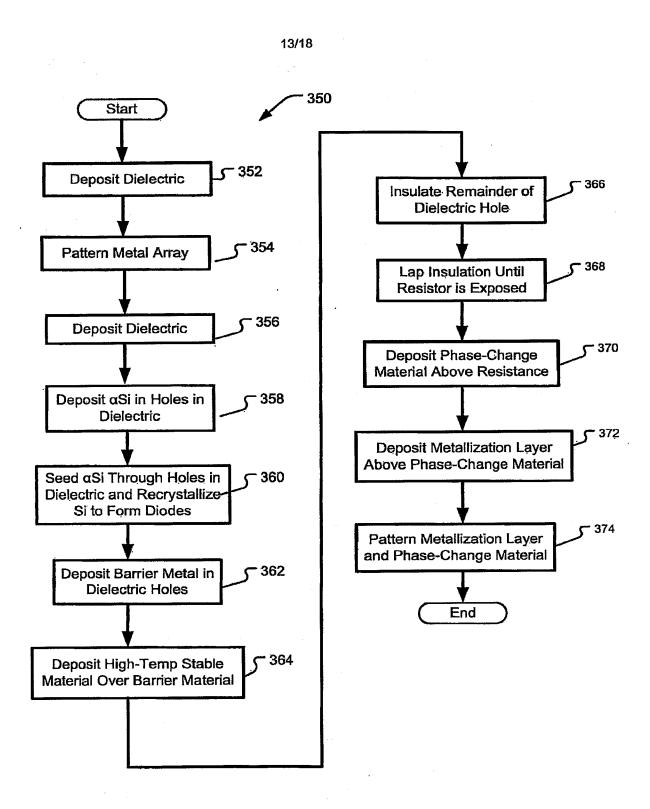

[0031] FIG. 8 illustrates a flowchart of a method for fabricating a cross-point phase-change memory array with crystalline diodes;

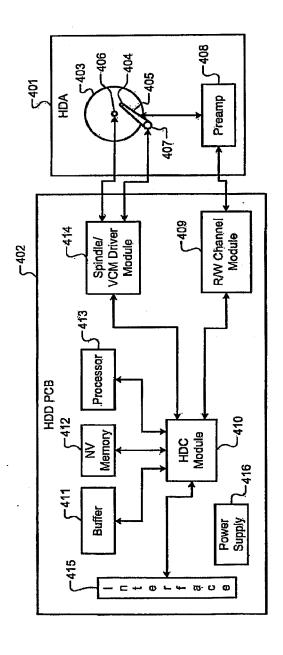

[0032] FIG. 9A is a functional block diagram of a hard disk drive;

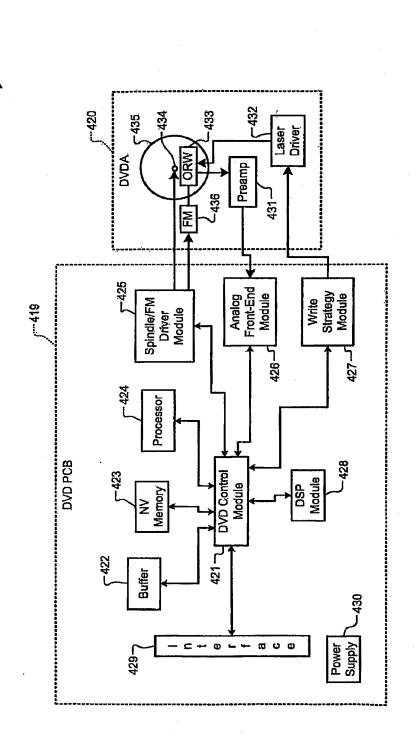

[0033] FIG. 9B is a functional block diagram of a DVD drive;

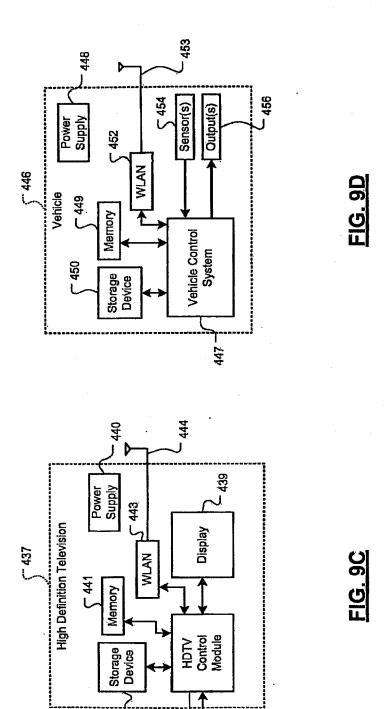

[0034] FIG. 9C is a functional block diagram of a high definition television:

[0035] FIG. 9D is a functional block diagram of a vehicle control system;

[0036] FIG. 9E is a functional block diagram of a cellular phone;

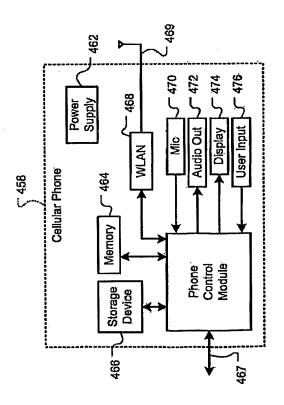

[0037] FIG. 9F is a functional block diagram of a set top box; and

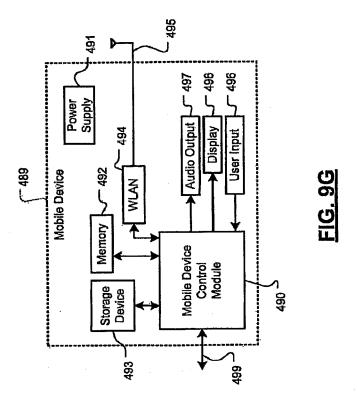

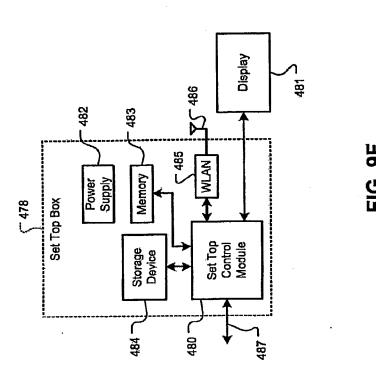

[0038] FIG. 9G is a functional block diagram of a mobile device.

#### **DETAILED DESCRIPTION**

[0039] The following description is merely exemplary in nature and is in no way intended to limit the disclosure, its application, or uses. For purposes

of clarity, the same reference numbers will be used in the drawings to identify similar elements. As used herein, the term module, circuit and/or device refers to an Application Specific Integrated Circuit (ASIC), an electronic circuit, a processor (shared, dedicated, or group) and memory that execute one or more software or firmware programs, a combinational logic circuit, and/or other suitable components that provide the described functionality. It should be understood that steps within a method may be executed in different order without altering the principles of the present disclosure.

5

10

15

20

25

30

[0040] The present disclosure describes a cross-point memory array arranged over a metallization layer of an integrated circuit. While the present disclosure will be described in conjunction with phase change memory, the present disclosure may be applicable to other memory types, such as Magnetic RAM (MRAM). Multiple cross point memory arrays may be stacked over memory or other types of circuits and tend to increase storage density and/or increase the number of memory functions.

[0041] Referring now to FIGs. 1 and 2A-2D, a cross-point memory array 2 may include row select lines 4-1, 4-2, ..., 4-X (collectively row select lines 4) that are connected to a row decoder 5. Column bit lines 6-1, 6-2, ..., 6-Y (collectively column bit lines 6) are connected to a column decoder 7. Phase-change memory cells 8-1,1, 8-1,2, ..., 8-X,Y (collectively phase change memory cells 8) are illustrated between the row and column lines 4, 6. The phase change memory cells 8 may provide variable resistances 9-1, 9-2, ..., 9-N (collectively resistances 9) that represent data. X, Y and N are integers greater than one.

[0042] Sense amplifiers 10-1, 10-2, ..., 10-X (collectively sense amplifiers 10) may read current 11 from resistance 9-1 through the row decoder 5 during a read operation. Current 12 flowing through other resistances, for example, resistances 9-2, 9-3, ..., and 9-N, may adversely affect the current 11, which may cause an error in the sensing of the data stored by the resistance 9-1. To reduce this impact, diodes 13-1, 13-2, ..., 13-N (collectively diodes 13) may be connected in series to one or both ends of the resistances 9 to reduce interference.

[0043] The cross-point memory array 2 may be constructed on a bulk silicon integrated circuit (IC) 14. One or more additional cross-point memory arrays 2 may be stacked over the first cross-point memory array 2 as will be described below.

5

10

15

20

25

30

[0044] Referring now to FIGs. 3A and 3B, a phase-change memory cell 8 may include a phase-change material 15, a resistive heater 16, and a select switch 18. The phase-change material 15 may be connected to a column bit line 6 and the resistive heater 16. The row select line 4 may control the select switch 18, which may be connected to the resistive heater 16. A controlled current may be used to program the phase-change memory cell 8 via the row select line 4 and the column bit line 6. In FIG. 3B, the phase-change memory cell 8 includes a diode 13.

[0045] Referring now to FIGs. 1 and 4A, the bulk silicon IC 14 may include a bulk silicon substrate 44 and semiconductor components 46, 47. For example only, the semiconductor components 46, 47 may include complementary metal-oxide semiconductor (CMOS) transistors 46, 47. n and p type wells 48, 50 may be formed in the bulk silicon substrate 44 using one or more patterning, ion implantation and/or diffusion steps. The bulk silicon substrate 44 may be heated to anneal damage from the ion implantation and/or to drive diffused dopants sufficiently within the n and p type wells 48, 50.

[0046] After the n and p wells 48, 50 are formed, additional patterning and implanting steps may be used to define hole dense (p+) regions 52, 54 and/or electron dense (n+) regions 56, 58. Once the bulk silicon substrate 44 is doped, an oxide layer may be grown on the bulk silicon substrate 44. The oxide layer may be patterned in selected areas to create first gate oxide areas 60, 62. A layer of polysilicon may be deposited over the oxide layer and patterned to create gates 64, 66 in selected areas. Ions may also be implanted in the polysilicon to lower a resistance of the gates 64, 66. A first interlayer dielectric (ILD) 68 may be deposited over the bulk silicon IC 14.

[0047] Referring now to FIGs. 4A and 4B, the row select lines 4 (illustrated in a direction perpendicular to a plane of FIG. 4A) may include a metallization layer 69. For example, the metallization layer 69 may include

copper. A barrier material 70 may be arranged adjacent to the metallization layer 69 and may include titanium nitride (TiN). A second ILD 71 may be deposited on the row select lines 4. The metallization layer 69 may be connected to the bulk silicon IC 14.

5

10

15

20

25

30

[0048] Referring now to FIG. 4C and 4D, a third ILD 72 may be deposited over the row select lines 4 and may include openings 74. The openings 74 may terminate at the top of the barrier material 70. A layer of amorphous silicon ( $\alpha$ -Si) 78 may be deposited in the openings 74. The  $\alpha$ -Si 78 may be inactive and/or doped with ions. In FIG. 4D, chemical mechanical polishing (CMP) may be used to polish the  $\alpha$ -Si 78, which leaves  $\alpha$ -Si in the openings 74.

[0049] Referring now to FIG. 4E, a seeding metal layer 81, for example nickel (Ni), is deposited on the structure, then low temperature solid phase epitaxy may be used to anneal/crystallize the  $\alpha$ -Si into crystal silicon islands 82 inside the openings 74. The remaining seeding metal layer 81 may be etched.

[0050] Referring now to FIGs. 4F and 4G, a metal layer 88 (for example only, titanium (Ti), tungsten (W), or titanium tungsten (TiW)) may be deposited on the structure, followed by thermal activation to form Schottky diodes on the surface of recrystallized Si islands 82. Un-reacted metal can then be removed by chemical etching. After this stage, the structure is depicted in FIG. 4G.

[0051] Referring now to FIG. 4H, an alternative embodiment is illustrated. If Schottky diode is not the desired diode structure a P/N junction may instead be formed. After the recrystallization to form the Si islands 82, an ion implantation step can be used to introduce dopant to the surface of the Si islands 82, followed by thermal activation to form the P/N junction (for example, P-Si 83 and N-Si 84).

[0052] Referring now to FIG. 4I, another dielectric isolation layer 84 may then be deposited over the structure. Openings 86 may be etched above the recrystallized Si islands 82, stopping at the Si island 82, which contains either a Schottky diode, or a P/N diode.

[0053] Generally, a significant amount of energy may be dissipated across the diode 13 during programming of the phase-change memory cell 8. The metallization layer 69 may act as a heat sink for the diode 13 to prevent heat-related structural damage to the diode.

5

10

15

20

25

30

[0054] Referring now to FIG. 4J, a relatively high-resistivity, high temperature-stable material 92 (for example, titanium (Ti), titanium nitride (TiN), titanium tungsten (TiW), and tungsten (W)) may be deposited on the surface of the structure. CMP may be used to remove the material 92 that is not in the openings 86. The resistive heater 16 may include the material 92. The material 92 may cover the sidewalls of the openings 86 and/or may fill the openings 86 completely. Remaining space in each of the openings 86 may be filled with an ILD 96.

[0055] Referring now to FIG. 4K, the upper surface 98 may be cleaned to remove remaining conducting layers, and a phase-change material 15 may be deposited. For example only, the phase change material can include chalcogenide alloy. The phase-change material 15 may be connected to a metallization layer that may be patterned into column bit lines 6. Contact holes and/or plugs 104 may be formed adjacent or within the metallization layer.

[0056] Referring now to FIG. 5, a phase-change memory cell can be programmed using temperature profiles 140 and 142. A RESET pulse of profile 140 heats the phase-change material above the melting temperature (Tm) and allows the material to rapidly quench during t<sub>1</sub>. The quench freezes an unstructured or molten state of the material. The freezing of the unstructured state results in an amorphous or vitreous (glassy) state.

[0057] In temperature profile 142, a SET pulse heats the phase-change material to a set temperature (Tset), which is below the molten state, but above a crystallization temperature (Tx). A prolonged period (t<sub>2</sub>) allows the phase-change material to re-order/anneal to a crystalline state. An alternative temperature profile may initially melt (raise to Tm) the phase-change material.

[0058] Referring now to FIG. 6, as higher set temperatures are used, relative resistivity of the phase-change material decreases in a predictable manner.

[0059] Referring now to FIG. 7, a voltage difference across the phase-change material may be non-linear and may exhibit break-down characteristics. A current-voltage characteristic curve may illustrate the phase-change material in a particular resistance state. A substantial amount of current may be conducted through the phase-change material by applying a voltage exceeding the breakdown voltage (Vb) using the resistive heater.

5

10

15

20

25

30

[0060] Referring now to FIG. 8, a flowchart 350 of steps for fabricating a cross-point phase-change memory array with diodes is illustrated. In step 352, a dielectric layer may be deposited. In step 354, a row metal array is patterned, which may include patterning barrier metal on copper rows within a dielectric. In step 356, a dielectric may be deposited above the row metal array. In step 358, openings are formed in the dielectric deposited in step 356 and filled with aSi.

[0061] In step 360, openings are formed in the dielectric, and a seeding metal is used to crystallize the  $\alpha Si$  of step 358. Step 360 may create single crystal silicon islands (through the seeding process) from the top and/or the bottom of the  $\alpha Si$ . When seeded from the bottom, the seeding material may be placed under the  $\alpha Si$  and may not be removed after the  $\alpha Si$  deposition. The seeding material generally should not interfere with the normal operation of a host device.

[0062] In step 362, un-reacted seeding metal may be removed using a suitable approach. Subsequently, a Schottky barrier metal or other barrier metal is deposited above the now seeded αSi in the openings of step 360. As previously mentioned, junction diodes may be formed instead of Schottky diodes by adding p+ doping. When junction diodes are used, the diode polarity may be more easily reversed than with a Schottky diode. Alternately, a phase-change material array may be built with SOI (silicon-on-insulator) transistor switches formed using a similar crystal seeding process.

[0063] In step 364, a high-temperature stable material is deposited having a high resistivity (resistance) within the openings of step 360 above the Schottky barrier metal. In step 366, insulation fills a remainder of space within the openings of step 360. In step 368, insulation of step 366 may be removed to expose an area of the high-temperature stable material. In step 370, a phase-

change material is deposited above the high-temperature stable material. In step 372, a metallization layer is deposited above the phase-change material of step 370. In step 374, the metallization layer and the phase-change material of step 372 may be patterned.

[0064] The phase-change memory cell arrays may be organized into rows and columns of phase-change memory cells, each of which may store multiple bits of data. The larger the number of levels programmable within a phase-change memory cell of an array, the more effective number of bits each cell may be able to store.

5

10

15

20

25

30

[0065] Referring now to FIGs. 9A-9G, various exemplary implementations incorporating the teachings of the present disclosure are shown.

[0066] Referring now to FIG. 9A, the teachings of the disclosure can be implemented in a memory of a hard disk drive (HDD) 400. The HDD 400 includes a hard disk assembly (HDA) 401 and a HDD PCB 402. The HDA 401 may include a magnetic medium 403, such as one or more platters that store data, and a read/write device 404. The read/write device 404 may be arranged on an actuator arm 405 and may read and write data on the magnetic medium 403. Additionally, the HDA 401 includes a spindle motor 406 that rotates the magnetic medium 403 and a voice-coil motor (VCM) 407 that actuates the actuator arm 405. A preamplifier device 408 amplifies signals generated by the read/write device 404 during read operations and provides signals to the read/write device 404 during write operations.

[0067] The HDD PCB 402 includes a read/write channel module (hereinafter, "read channel") 409, a hard disk controller (HDC) module 410, a buffer 411, nonvolatile memory 412, a processor 413, and a spindle/VCM driver module 414. The read channel 409 processes data received from and transmitted to the preamplifier device 408. The HDC module 410 controls components of the HDA 401 and communicates with an external device (not shown) via an I/O interface 415. The external device may include a computer, a multimedia device, a mobile computing device, etc. The I/O interface 415 may include wireline and/or wireless communication links.

[0068] The HDC module 410 may receive data from the HDA 401, the read channel 409, the buffer 411, nonvolatile memory 412, the processor 413, the spindle/VCM driver module 414, and/or the I/O interface 415. The processor 413 may process the data, including encoding, decoding, filtering, and/or formatting. The processed data may be output to the HDA 401, the read channel 409, the buffer 411, nonvolatile memory 412, the processor 413, the spindle/VCM driver module 414, and/or the I/O interface 415.

5

10

15

20

25

30

[0069] The HDC module 410 may use the buffer 411 and/or nonvolatile memory 412 to store data related to the control and operation of the HDD 400. The buffer 411 may include DRAM, SDRAM, etc. The nonvolatile memory 412 may include flash memory (including NAND and NOR flash memory), phase change memory, magnetic RAM, or multi-state memory, in which each memory cell has more than two states. The spindle/VCM driver module 414 controls the spindle motor 406 and the VCM 407. The HDD PCB 402 includes a power supply 416 that provides power to the components of the HDD 400.

[0070] Referring now to FIG. 9B, the teachings of the disclosure can be implemented in a memory of a DVD drive 418 or of a CD drive (not shown). The DVD drive 418 includes a DVD PCB 419 and a DVD assembly (DVDA) 420. The DVD PCB 419 includes a DVD control module 421, a buffer 422, nonvolatile memory 423, a processor 424, a spindle/FM (feed motor) driver module 425, an analog front-end module 426, a write strategy module 427, and a DSP module 428.

[0071] The DVD control module 421 controls components of the DVDA 420 and communicates with an external device (not shown) via an I/O interface 429. The external device may include a computer, a multimedia device, a mobile computing device, etc. The I/O interface 429 may include wireline and/or wireless communication links.

[0072] The DVD control module 421 may receive data from the buffer 422, nonvolatile memory 423, the processor 424, the spindle/FM driver module 425, the analog front-end module 426, the write strategy module 427, the DSP module 428, and/or the I/O interface 429. The processor 424 may process the

data, including encoding, decoding, filtering, and/or formatting. The DSP module 428 performs signal processing, such as video and/or audio coding/decoding. The processed data may be output to the buffer 422, nonvolatile memory 423, the processor 424, the spindle/FM driver module 425, the analog front-end module 426, the write strategy module 427, the DSP module 428, and/or the I/O interface 429.

5

10

15

20

25

30

[0073] The DVD control module 421 may use the buffer 422 and/or nonvolatile memory 423 to store data related to the control and operation of the DVD drive 418. The buffer 422 may include DRAM, SDRAM, etc. The nonvolatile memory 423 may include flash memory (including NAND and NOR flash memory), phase change memory, magnetic RAM, or multi-state memory, in which each memory cell has more than two states. The DVD PCB 419 includes a power supply 430 that provides power to the components of the DVD drive 418.

[0074] The DVDA 420 may include a preamplifier device 431, a laser driver 432, and an optical device 433, which may be an optical read/write (ORW) device or an optical read-only (OR) device. A spindle motor 434 rotates an optical storage medium 435, and a feed motor 436 actuates the optical device 433 relative to the optical storage medium 435.

[0075] When reading data from the optical storage medium 435, the laser driver provides a read power to the optical device 433. The optical device 433 detects data from the optical storage medium 435, and transmits the data to the preamplifier device 431. The analog front-end module 426 receives data from the preamplifier device 431 and performs such functions as filtering and A/D conversion. To write to the optical storage medium 435, the write strategy module 427 transmits power level and timing information to the laser driver 432. The laser driver 432 controls the optical device 433 to write data to the optical storage medium 435.

[0076] Referring now to FIG. 9C, the teachings of the disclosure can be implemented in memory of a high definition television (HDTV) 437. The HDTV 437 includes a HDTV control module 438, a display 439, a power supply

440, memory 441, a storage device 442, a WLAN interface 443 and associated antenna 444, and an external interface 445.

[0077] The HDTV 437 can receive input signals from the WLAN interface 443 and/or the external interface 445, which sends and receives information via cable, broadband Internet, and/or satellite. The HDTV control module 438 may process the input signals, including encoding, decoding, filtering, and/or formatting, and generate output signals. The output signals may be communicated to one or more of the display 439, memory 441, the storage device 442, the WLAN interface 443, and the external interface 445.

5

10

15

20

25

30

[0078] Memory 441 may include random access memory (RAM) and/or nonvolatile memory such as flash memory, phase change memory, or multi-state memory, in which each memory cell has more than two states. The storage device 442 may include an optical storage drive, such as a DVD drive, and/or a hard disk drive (HDD). The HDTV control module 438 communicates externally via the WLAN interface 443 and/or the external interface 445. The power supply 440 provides power to the components of the HDTV 437.

[0079] Referring now to FIG. 9D, the teachings of the disclosure may be implemented in a memory of a vehicle 446. The vehicle 446 may include a vehicle control system 447, a power supply 448, memory 449, a storage device 450, and a WLAN interface 452 and associated antenna 453. The vehicle control system 447 may be a powertrain control system, a body control system, an entertainment control system, an anti-lock braking system (ABS), a navigation system, a telematics system, a lane departure system, an adaptive cruise control system, etc.

[0080] The vehicle control system 447 may communicate with one or more sensors 454 and generate one or more output signals 456. The sensors 454 may include temperature sensors, acceleration sensors, pressure sensors, rotational sensors, airflow sensors, etc. The output signals 456 may control engine operating parameters, transmission operating parameters, suspension parameters, etc.

[0081] The power supply 448 provides power to the components of the vehicle 446. The vehicle control system 447 may store data in memory 449

and/or the storage device 450. Memory 449 may include random access memory (RAM) and/or nonvolatile memory such as flash memory, phase change memory, or multi-state memory, in which each memory cell has more than two states. The storage device 450 may include an optical storage drive, such as a DVD drive, and/or a hard disk drive (HDD). The vehicle control system 447 may communicate externally using the WLAN interface 452.

5

10

15

20

25

30

[0082] Referring now to FIG. 9E, the teachings of the disclosure can be implemented in memory of a cellular phone 458. The cellular phone 458 includes a phone control module 460, a power supply 462, memory 464, a storage device 466, and a cellular network interface 467. The cellular phone 458 may include a WLAN interface 468 and associated antenna 469, a microphone 470, an audio output 472 such as a speaker and/or output jack, a display 474, and a user input device 476 such as a keypad and/or pointing device.

[0083] The phone control module 460 may receive input signals from the cellular network interface 467, the WLAN interface 468, the microphone 470, and/or the user input device 476. The phone control module 460 may process signals, including encoding, decoding, filtering, and/or formatting, and generate output signals. The output signals may be communicated to one or more of memory 464, the storage device 466, the cellular network interface 467, the WLAN interface 468, and the audio output 472.

[0084] Memory 464 may include random access memory (RAM) and/or nonvolatile memory such as flash memory, phase change memory, or multi-state memory, in which each memory cell has more than two states. The storage device 466 may include an optical storage drive, such as a DVD drive, and/or a hard disk drive (HDD). The power supply 462 provides power to the components of the cellular phone 458.

[0085] Referring now to FIG. 9F, the teachings of the disclosure can be implemented in memory of a set top box 478. The set top box 478 includes a set top control module 480, a display 481, a power supply 482, memory 483, a storage device 484, and a WLAN interface 485 and associated antenna 486.

[0086] The set top control module 480 may receive input signals from the WLAN interface 485 and an external interface 487, which can send and

receive information via cable, broadband Internet, and/or satellite. The set top control module 480 may process signals, including encoding, decoding, filtering, and/or formatting, and generate output signals. The output signals may include audio and/or video signals in standard and/or high definition formats. The output signals may be communicated to the WLAN interface 485 and/or to the display 481. The display 481 may include a television, a projector, and/or a monitor.

5

10

15

20

25

30

[0087] The power supply 482 provides power to the components of the set top box 478. Memory 483 may include random access memory (RAM) and/or nonvolatile memory such as flash memory, phase change memory, or multi-state memory, in which each memory cell has more than two states. The storage device 484 may include an optical storage drive, such as a DVD drive, and/or a hard disk drive (HDD).

[0088] Referring now to FIG. 9G, the teachings of the disclosure can be implemented in memory of a mobile device 489. The mobile device 489 may include a mobile device control module 490, a power supply 491, memory 492, a storage device 493, a WLAN interface 494 and associated antenna 495, and an external interface 499.

[0089] The mobile device control module 490 may receive input signals from the WLAN interface 494 and/or the external interface 499. The external interface 499 may include USB, infrared, and/or Ethernet. The input signals may include compressed audio and/or video, and may be compliant with the MP3 format. Additionally, the mobile device control module 490 may receive input from a user input 496 such as a keypad, touchpad, or individual buttons. The mobile device control module 490 may process input signals, including encoding, decoding, filtering, and/or formatting, and generate output signals.

[0090] The mobile device control module 490 may output audio signals to an audio output 497 and video signals to a display 498. The audio output 497 may include a speaker and/or an output jack. The display 498 may present a graphical user interface, which may include menus, icons, etc. The power supply 491 provides power to the components of the mobile device 489. Memory 492 may include random access memory (RAM) and/or nonvolatile memory such as flash memory, phase change memory, or multi-state memory,

in which each memory cell has more than two states. The storage device 493 may include an optical storage drive, such as a DVD drive, and/or a hard disk drive (HDD). The mobile device may include a personal digital assistant, a media player, a laptop computer, a gaming console or other mobile computing device.

5

10

[0091] Those skilled in the art can now appreciate from the foregoing description that the broad teachings of the disclosure can be implemented as a variety of forms. Therefore, while this disclosure includes particular examples, the true scope of the disclosure should not be so limited since other modifications will become apparent to the skilled practitioner upon a study of the drawings, the specification and the following claims.

# **CLAIMS**

## What is claimed is:

25

- 1. A phase-change memory (PCM) system, comprising:

- a PCM cell array that comprises a plurality of PCM cells, wherein each of said PCM cells includes:

- a diode arranged adjacent to a metallization layer;

- a heater element arranged adjacent to said diode; and

- a phase-change material arranged adjacent to said heater element.

- 10 2. The PCM system of Claim 1 wherein said diode includes an amorphous silicon layer that is deposited over said metallization layer, wherein said amorphous silicon layer is crystallized using a seeding metal.

- 3. The PCM system of Claim 1 wherein said diode includes a Schottky diode.

- 4. The PCM system of Claim 1 wherein said diode includes a junction diode.

- The PCM system of Claim 1 wherein said diode thermally communicates

with said metallization layer.

- 6. A system comprising said PCM system of Claim 1 and further comprising a non-memory circuit that includes said metallization layer, wherein said PCM system is integrated with said non-memory circuit, and wherein said diode thermally communicates with said metallization layer.

- 7. A system comprising said PCM system of Claim 1 and further comprising a memory circuit that includes said metallization layer, wherein said PCM system is integrated with said memory circuit, and wherein said diode thermally communicates with said metallization layer.

8. The PCM system of Claim 1 wherein N bits of user data are stored in each of said plurality of PCM cells, where N is an integer greater than one.

- A portable electronic device comprising:

- an integrated circuit comprising:

5

15

- a metallization layer; and

- a storage device comprising the PCM system of Claim 1.

- 10. The portable electronic device of Claim 9 wherein said portable electronic device is selected from a group consisting of: cell phones, laptop computers, personal digital assistants, hand-held gaming devices, and media players.

- 11. The portable electronic device of Claim 9 wherein N bits of user data are stored in each of said plurality of PCM cells, where N is an integer greater than one.

- 12. The portable electronic device of Claim 9 wherein said diode includes an amorphous silicon layer that is deposited over said metallization layer, wherein said amorphous silicon layer is crystallized using a seeding metal.

- 13. The portable electronic device of Claim 9 wherein said diode includes a Schottky diode.

- 14. The portable electronic device of Claim 9 wherein said diode includes a25 junction diode.

- 15. The portable electronic device of Claim 9 wherein said diode thermally communicates with said metallization layer.

- 30 16. A method for fabricating a phase-change memory (PCM) cell, comprising: arranging a diode adjacent to a metallization layer; arranging a heater element adjacent to said diode; and

arranging a phase-change material adjacent to said heater element.

17. The method of Claim 16 further comprising:

depositing an amorphous silicon layer over said metallization layer; and crystallizing said amorphous silicon layer using a seeding metal to form said diode.

- 18. The method of Claim 16 wherein said diode includes a Schottky diode.

- 10 19. The method of Claim 16 wherein said diode includes a junction diode.

- 20. A phase-change data storage system, comprising:

phase-change storing means for storing data that comprises a plurality of memory cells, wherein each of said memory cells includes:

current restricting means for selectively restricting current flow and that is arranged adjacent to a metallization layer;

heating means for heating arranged adjacent to said current restricting means; and

a phase change material arranged adjacent to said heating means.

20

15

5

21. The phase-change data storage system of Claim 20 wherein said current restricting means includes an amorphous silicon layer that is deposited over said metallization layer, wherein said amorphous silicon layer is crystallized using a seeding material.

- 22. The phase-change data storage system of Claim 20 wherein said current restricting means includes a Schottky diode.

- 23. The phase-change data storage system of Claim 20 wherein said current restricting means includes a junction diode.

24. The phase-change data storage system of Claim 20 wherein said current restricting means thermally communicates with said metallization layer.

- 25. A system comprising the phase-change data storage system of Claim 20 and further comprising a non-memory circuit that includes said metallization layer, wherein said phase-change data storage system is integrated with said non-memory circuit, and wherein said current restricting means thermally communicates with said metallization layer.

- 10 26. A system comprising said phase-change data storage system of Claim 20 and further comprising storing means for storing data that includes said metallization layer, wherein said phase-change data storage system is integrated with said storing means, and wherein said current restricting means thermally communicates with said metallization layer.

- 27. The phase-change data storage system of Claim 20 wherein N bits of user data are stored in each of said plurality of said memory cells, where N is an integer greater than one.

- 20 28. A portable electronic device comprising:

an integrated circuit comprising:

a metallization layer; and

a storage device comprising the PCM system of Claim 1.

- 25 29. The portable electronic device of Claim 28 wherein said portable electronic device is selected from a group consisting of: cell phones, laptop computers, personal digital assistants, hand-held gaming devices, and media players.

- 30. The portable electronic device of Claim 28 wherein N bits of user data are stored in each of said plurality of cells, where N is an integer greater than one.

31. The portable electronic device of Claim 28 wherein said current restricting means includes an amorphous silicon layer that is deposited over said metallization layer, wherein said amorphous silicon layer is crystallized using a seeding material.

5

- 32. The portable electronic device of Claim 28 wherein said current restricting means includes a Schottky diode.

- 33. The portable electronic device of Claim 28 wherein said current restrictingmeans includes a junction diode.

- 34. The portable electronic device of Claim 28 wherein said current restricting means thermally communicates with said metallization layer.

- 15 35. A circuit comprising:

the PCM system of Claim 1; and

a bulk silicon transistor that communicates with said metallization layer.

36. The circuit of Claim 35 wherein said bulk silicon transistor comprises a complimentary metal-oxide semiconductor (CMOS) transistor.

20

- 37. A circuit comprising:

- a bulk silicon integrated circuit (IC);

- a first metallization layer that is arranged adjacent to said bulk silicon IC; and

phase change memory (PCM) that is arranged adjacent to said first metallization layer and that comprises a plurality of PCM cells each including:

a phase-change material;

a heater that selectively heats said phase-change material; and a diode in series with said phase-change material.

38. The circuit of Claim 37 wherein said diode includes an amorphous silicon layer that is deposited over said first metallization layer, wherein said amorphous silicon layer is crystallized using a seeding metal layer.

- 5 39. The circuit of Claim 37 further comprising a conductive barrier material arranged between said first metallization layer and said diode.

- 40. The circuit of Claim 37 wherein said first metallization layer comprises copper.

- 41. The circuit of Claim 39 wherein said barrier material comprises titanium nitride.

10

25

- 42. The circuit of Claim 37 wherein said diode includes one of a Schottky diode and a junction diode.

- 43. The circuit of Claim 37 wherein said first metallization layer thermally communicates with said diode.

- 20 44. The circuit of Claim 37 wherein said diode comprises an n-type amorphous silicon layer.

- 45. The circuit of Claim 37 further comprising a seeding metal layer that crystallizes said n-type amorphous silicon layer.

- 46. The circuit of Claim 45 wherein said seeding metal layer comprises nickel.

- 47. The circuit of Claim 45 wherein said diode comprises a metal layer arranged adjacent to said n-type amorphous silicon layer.

- 48. The circuit of Claim 47 wherein said metal layer comprises titanium.

49. The circuit of Claim 37 further comprising an interlayer dielectric arranged adjacent to said diode.

- 50. The circuit of Claim 37 wherein said heater comprises at least one of titanium, titanium nitride, titanium tungsten, and tungsten.

- 51. The circuit of Claim 37 further comprising a second metallization layer arranged adjacent to said phase-change material.

- 10 52. The circuit of Claim 51 wherein said first metallization layer includes a row select line and said second metallization layer includes a column bit line.

- 53. The circuit of Claim 37 wherein said bulk silicon IC comprises complimentary metal-oxide semiconductor (CMOS) transistors.

- 54. A system comprising the circuit of Claim 37 and further comprising a non-memory circuit that includes said first metallization layer, wherein said PCM is integrated with said non-memory circuit, and wherein said diode thermally communicates with said first metallization layer.

20

- 55. A system comprising the circuit of Claim 37 and further comprising a memory circuit that includes said first metallization layer, wherein said PCM is integrated with said memory circuit, and wherein said diode thermally communicates with said first metallization layer.

- 56. The circuit of Claim 37 wherein N bits of user data are stored in each of said plurality of PCM cells, where N is an integer greater than one.

IG. 4F

FIG. 4H

FIG. 4K

12/18

**FIG. 8**

FIG. 9A

FIG. 9B

-1G. 9E