(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6641135号

(P6641135)

(45) 発行日 令和2年2月5日(2020.2.5)

(24) 登録日 令和2年1月7日(2020.1.7)

|              |           |

|--------------|-----------|

| (51) Int.Cl. | F 1       |

| HO4N 5/378   | (2011.01) |

| HO4N 5/374   | (2011.01) |

| HO4N 5/232   | (2006.01) |

| GO2B 7/34    | (2006.01) |

| GO3B 13/36   | (2006.01) |

| HO4N         | 5/378     |

| HO4N         | 5/374     |

| HO4N         | 5/232     |

| GO2B         | 7/34      |

| GO3B         | 13/36     |

請求項の数 20 (全 18 頁)

(21) 出願番号 特願2015-183246 (P2015-183246)

(22) 出願日 平成27年9月16日 (2015.9.16)

(65) 公開番号 特開2017-60000 (P2017-60000A)

(43) 公開日 平成29年3月23日 (2017.3.23)

審査請求日 平成30年9月6日 (2018.9.6)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】撮像素子及び撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

1つのマイクロレンズと複数の光電変換部とを有する単位画素が行列状に複数配列された画素部と、

前記画素部全体の単位画素から出力された信号を保持する信号保持部と、

前記信号保持部により保持された信号を処理する信号処理部であって、前記信号保持部により保持された信号に撮像画像を生成するための信号処理を行う撮像画像用信号処理部と、前記信号保持部により保持された信号に焦点検出のための信号処理を行う焦点検出用信号処理部とを有する信号処理部と、

前記信号処理部で処理された信号を出力する出力部と、

を備えることを特徴とする撮像素子。

## 【請求項 2】

前記焦点検出用信号処理部は、前記信号保持部により保持された前記画素部全体の信号から、前記画素部における目的とする領域の前記単位画素の信号を選択し、選択された単位画素それぞれの複数の光電変換部の信号のうち少なくとも1つの光電変換部の信号を出力することを特徴とする請求項1に記載の撮像素子。

## 【請求項 3】

前記焦点検出用信号処理部は、前記選択された単位画素それぞれの複数の光電変換部の信号をそれぞれ出力することを特徴とする請求項2に記載の撮像素子。

## 【請求項 4】

10

20

前記焦点検出用信号処理部は、前記選択された単位画素それぞれの複数の光電変換部の信号を選択的に混合して出力することを特徴とする請求項2に記載の撮像素子。

**【請求項5】**

前記焦点検出用信号処理部は、前記信号保持部により保持された前記画素部全体の信号から、前記画素部における目的とする領域の前記単位画素の信号を選択し、前記選択された単位画素それぞれの複数の光電変換部の信号に対して相関演算を行い、該相関演算により算出された値を出力することを特徴とする請求項1に記載の撮像素子。

**【請求項6】**

前記信号保持部は、それぞれの単位画素の前記光電変換部から出力された信号をそれぞれ保持する複数の保持回路を有することを特徴とする請求項1乃至5のいずれか1項に記載の撮像素子。10

**【請求項7】**

前記信号保持部は、それぞれの単位画素の前記光電変換部から列ごとに出力された信号をそれぞれ保持するための複数の保持回路を有することを特徴とする請求項1乃至5のいずれか1項に記載の撮像素子。

**【請求項8】**

前記撮像画像用信号処理部は、それぞれの単位画素の前記複数の光電変換部の信号を圧縮して出力する圧縮処理手段を有することを特徴とする請求項1乃至7のいずれか1項に記載の撮像素子。20

**【請求項9】**

前記圧縮処理手段は、それぞれの単位画素の前記複数の光電変換部の信号を混合平均化することを特徴とする請求項8に記載の撮像素子。

**【請求項10】**

複数の半導体基板から形成される多層構造を備え、前記画素部と前記信号処理部は互いに異なる基板に形成されていることを特徴とする請求項1乃至9のいずれか1項に記載の撮像素子。

**【請求項11】**

撮像素子と、該撮像素子から読み出された信号を処理して画像を生成する画像処理手段と、前記読み出された信号を処理して焦点検出を行う焦点検出手段とを備え、

前記撮像素子が、30

1つのマイクロレンズと複数の光電変換部とを有する単位画素が行列状に複数配列された画素部と、

前記画素部全体の単位画素から出力された信号を保持する信号保持部と、

前記信号保持部により保持された信号を処理する信号処理部であって、前記信号保持部により保持された信号に撮像画像を生成するための信号処理を行う撮像画像用信号処理部と、前記信号保持部により保持された信号に焦点検出のための信号処理を行う焦点検出用信号処理部とを有する信号処理部と、

前記信号処理部で処理された信号を出力する出力部と、

を有することを特徴とする撮像装置。

**【請求項12】**

前記焦点検出用信号処理部は、前記信号保持部により保持された前記画素部全体の信号から、前記画素部における目的とする領域の前記単位画素の信号を選択し、選択された単位画素それぞれの複数の光電変換部の信号のうち少なくとも1つの光電変換部の信号を出力することを特徴とする請求項11に記載の撮像装置。40

**【請求項13】**

前記焦点検出用信号処理部は、前記選択された単位画素それぞれの複数の光電変換部の信号をそれぞれ出力することを特徴とする請求項12に記載の撮像装置。

**【請求項14】**

前記焦点検出用信号処理部は、前記選択された単位画素それぞれの複数の光電変換部の信号を選択的に混合して出力することを特徴とする請求項12に記載の撮像装置。50

**【請求項 15】**

前記焦点検出用信号処理部は、前記信号保持部により保持された前記画素部全体の信号から、前記画素部における目的とする領域の前記単位画素の信号を選択し、前記選択された単位画素それぞれの複数の光電変換部の信号に対して相関演算を行い、該相関演算により算出された値を出力することを特徴とする請求項 11 に記載の撮像装置。

**【請求項 16】**

前記信号保持部は、それぞれの単位画素の前記光電変換部から出力された信号をそれぞれ保持する複数の保持回路を有することを特徴とする請求項 11 乃至 15 のいずれか 1 項に記載の撮像装置。

**【請求項 17】**

10

前記信号保持部は、それぞれの単位画素の前記光電変換部から列ごとに出力された信号をそれぞれ保持するための複数の保持回路を有することを特徴とする請求項 11 乃至 15 のいずれか 1 項に記載の撮像装置。

**【請求項 18】**

前記撮像画像用信号処理部は、それぞれの単位画素の前記複数の光電変換部の信号を圧縮して出力する圧縮処理手段を有することを特徴とする請求項 11 乃至 17 のいずれか 1 項に記載の撮像装置。

**【請求項 19】**

前記圧縮処理手段は、それぞれの単位画素の前記複数の光電変換部の信号を混合平均化することを特徴とする請求項 18 に記載の撮像装置。

20

**【請求項 20】**

前記撮像素子は、複数の半導体基板から形成される多層構造を備え、前記画素部と前記信号処理部は互いに異なる基板に形成されていることを特徴とする請求項 11 乃至 19 のいずれか 1 項に記載の撮像装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、撮像素子及び撮像装置に関するものである。

**【背景技術】****【0002】**

30

近年、CMOS 撮像素子などを用いた撮像装置において、様々なニーズに対応するべく高機能化、多機能化が進んでいる。CMOS 撮像素子は、多画素化、高速撮像化が進み、より高速に画素信号を読み出せる方式への要求が高まっている。

**【0003】**

例えば、高速読み出しを行う方式としては、特許文献 1 に記載されているように、列毎にアナログ / デジタル変換回路（以下、列 ADC）を配置し、デジタル出力を行う方式が近年普及している。列 ADC を導入することで、撮像素子の外部への画素信号の伝送をデジタルで行うことが可能となり、デジタル信号伝送の技術向上に伴い、高速読み出しが可能となる。

**【0004】**

40

一方、多機能化の例としては、例えば光の強度分布のみならず、光の入射方向や距離情報をも取得可能な撮像装置が提案されている。特許文献 2 では、撮像素子から得られた信号を用いて焦点検出が可能な撮像素子について開示されている。1 つのマイクロレンズに対応するフォトダイオード（以下、PD）を 2 つに分割することによって、各 PD が撮影レンズの異なる瞳面の光を受光するように構成されている。そして、2 つの PD の出力を比較することによって、焦点検出を行っている。また、単位画素を構成する 2 つの PD からの出力信号を加算することで、通常の撮像画像を得ることもできる。

**【先行技術文献】****【特許文献】****【0005】**

50

【特許文献 1】特開 2005 - 278135 号公報

【特許文献 2】特許第 3774597 号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0006】**

しかし、特許文献 2 に開示されているような撮像素子において焦点検出を行う場合、全ての P D の信号を読み出す必要があるため、P D の信号を読み出すのに必要な時間が長くなり、フレームレートが下がってしまうという課題がある。特許文献 1 のように列 A D C を用いた読み出し方式により信号読み出し時間を高速化しても、今後更なる多画素化、高フレームレート化が進むことが予想され、信号読み出し時間の更なる短縮が望まれる。

10

**【0007】**

本発明は上述した課題に鑑みてなされたものであり、その目的は、1 フレーム内で、撮影画像データと焦点検出情報の両方の取得を高速に行うことが可能な撮像素子を提供することである。

**【課題を解決するための手段】**

**【0008】**

本発明に係わる撮像素子は、1 つのマイクロレンズと複数の光電変換部とを有する単位画素が行列状に複数配列された画素部と、前記画素部全体の単位画素から出力された信号を保持する信号保持部と、前記信号保持部により保持された信号を処理する信号処理部であって、前記信号保持部により保持された信号に撮像画像を生成するための信号処理を行う撮像画像用信号処理部と、前記信号保持部により保持された信号に焦点検出のための信号処理を行う焦点検出用信号処理部とを有する信号処理部と、前記信号処理部で処理された信号を出力する出力部と、を備えることを特徴とする。

20

また、本発明に係わる撮像装置は、撮像素子と、該撮像素子から読み出された信号を処理して画像を生成する画像処理手段と、前記読み出された信号を処理して焦点検出を行う焦点検出手段とを備え、前記撮像素子が、1 つのマイクロレンズと複数の光電変換部とを有する単位画素が行列状に複数配列された画素部と、前記画素部全体の単位画素から出力された信号を保持する信号保持部と、前記信号保持部により保持された信号を処理する信号処理部であって、前記信号保持部により保持された信号に撮像画像を生成するための信号処理を行う撮像画像用信号処理部と、前記信号保持部により保持された信号に焦点検出のための信号処理を行う焦点検出用信号処理部とを有する信号処理部と、前記信号処理部で処理された信号を出力する出力部と、を有することを特徴とする。

30

**【発明の効果】**

**【0009】**

本発明によれば、撮像画像データと焦点検出情報の両方を撮像素子内で高速に取得して出力することができる。

**【図面の簡単な説明】**

**【0010】**

【図 1】本発明の第 1 の実施形態に係わる撮像装置の構成を示すブロック図。

【図 2】第 1 の実施形態の撮像素子の構成を説明する図。

40

【図 3】撮影レンズの射出瞳から出射された光束が単位画素に入射する概念図。

【図 4】第 1 の実施形態の撮像素子の構成を示すブロック図。

【図 5】第 1 の実施形態の撮像素子の画素回路及び読み出し回路を説明する図。

【図 6】第 1 の実施形態の撮像素子の信号読み出し動作を示すタイミングチャート。

【図 7】第 1 の実施形態の撮像素子における信号処理部の構成を説明する図。

【図 8】第 2 の実施形態の画素領域における焦点検出用信号出力領域を示した図。

【図 9】第 3 の実施形態の撮像素子の構成を説明する図。

【図 10】第 3 の実施形態の撮像素子の画素回路及び読み出し回路を説明する図。

【図 11】第 4 の実施形態の撮像素子の全体構成図。

【図 12】第 4 の実施形態の撮像素子の全体構成図。

50

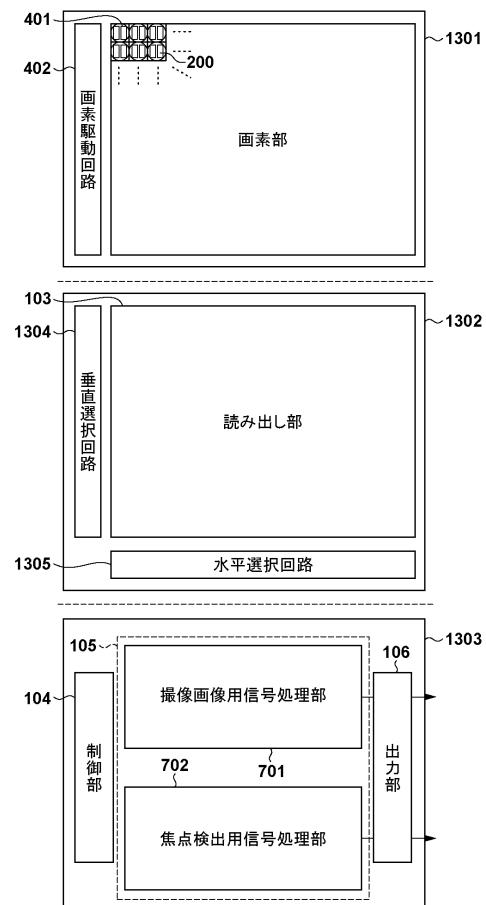

【図13】第5の実施形態の撮像素子の全体構成図。

【発明を実施するための形態】

【0011】

以下、本発明の実施形態について、添付図面を参照して詳細に説明する。

【0012】

(第1の実施形態)

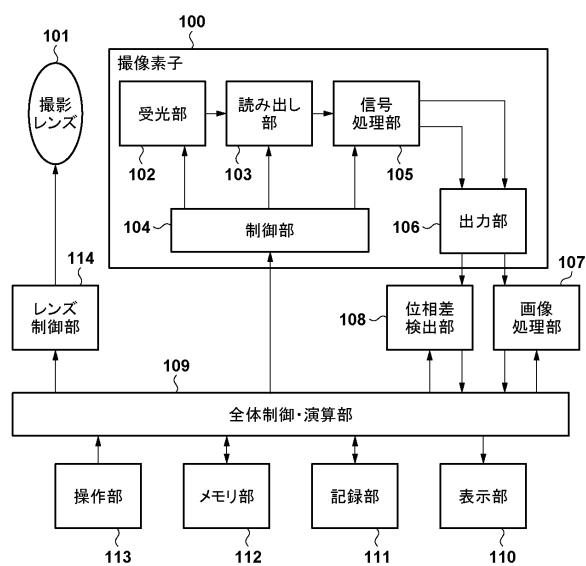

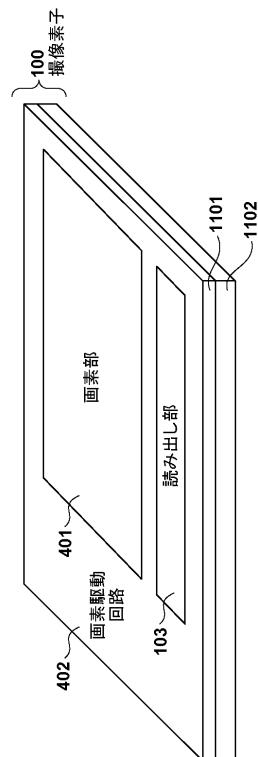

図1は、本発明の第1の実施形態の撮像素子を有する撮像装置の構成を示すブロック図である。撮像素子100は、受光部102、読み出し部103、制御部104、信号処理部105、出力部106を備えて構成される。受光部102は、複数の単位画素が行列状に配置されており、撮影レンズ101により結像された光学像を受光する。受光部102の構成については後述する。読み出し部103は、制御部104の制御信号を受けて、受光部102から出力される画素信号をA/D変換し、信号処理部105に送る。

10

【0013】

信号処理部105は、A/D変換された画像信号に対して、信号の加算、減算、乗算等の演算処理や、出力部106を介して撮像素子100から外部に出力する信号の選択処理などを行う。また、信号処理部105では、基準レベル調整等の各種補正やデータの並べ替えなども行う。これらの処理は、制御部104からの制御信号を受けて実行される。信号処理部105の詳細は後述するが、信号処理部105においては、受光部102から得られた画素信号に対して、撮像画像用の信号処理と焦点検出用の信号処理を行い、それらを出力部106に送る。出力部106は、信号処理部105により処理された画素信号を撮像素子100の外部に出力する。

20

【0014】

画像処理部107は、撮像素子100の出力部106から撮像画像用の信号を受け取り、欠陥画素の補正、ノイズリダクション、色変換、ホワイトバランス補正、画像補正等の画像処理や、解像度変換処理、画像圧縮処理などを行い、静止画像や動画像を生成する。位相差検出部108は、出力部106からの焦点検出用の信号を受けて、焦点検出を行うための位相差評価値を算出する。

【0015】

全体制御・演算部109は、撮像素子100や撮像装置全体の統括的な駆動及び制御を行う。表示部110は撮影後の画像やライブビュー画像、各種設定画面等を表示する。記録部111及びメモリ部112は、全体制御・演算部109から出力された画像信号等を記録保持する不揮発性メモリあるいはメモリカード等の記録媒体である。操作部113は撮像装置に備え付けられた操作部材によりユーザーの命令を受け付け、全体制御・演算回路106にその命令を入力する。レンズ制御部114は、位相差検出部108で算出された位相差評価値に基づいて光学系駆動情報を算出し、撮影レンズ101のフォーカスレンズ位置を制御する。

30

【0016】

次に、本実施形態の撮像装置における撮影レンズ101、マイクロレンズアレイ、撮像素子100の受光部102の関係と、画素の定義、及び瞳分割方式による焦点検出の原理について説明する。

40

【0017】

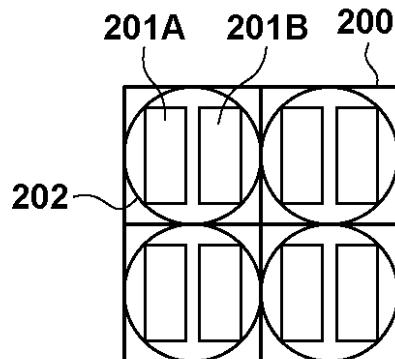

図2は、撮像素子100の受光部102とマイクロレンズアレイを光軸方向(Z方向)から観察した図である。本実施形態では、マイクロレンズアレイを形成する個々のマイクロレンズ202を1つの画素と定義し、これを単位画素200とする。また、1つのマイクロレンズ202に対してフォトダイオード(PD)からなる2つの光電変換部がX軸方向に並んで配置されており、それぞれ光電変換部201A, 201Bと定義する。

【0018】

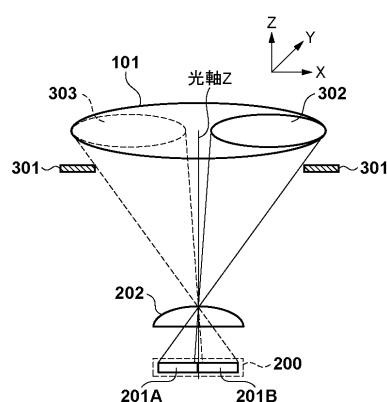

図3は、撮影レンズ101を通過した光が1つのマイクロレンズ202を通過して撮像素子100の受光部102の単位画素200で受光される様子を光軸(Z軸)に対して垂直な方向(Y軸方向)から観察した図である。302, 303は撮影レンズの射出瞳を表

50

す。301はレンズ絞りである。射出瞳を通過した光は、光軸を中心として単位画素200に入射する。図3に示すように瞳領域302を通過する光束はマイクロレンズ202を通して光電変換部201Aで受光され、瞳領域303を通過する光束はマイクロレンズ202を通して光電変換部201Bで受光される。したがって、光電変換部201A, 201Bはそれぞれ撮影レンズの射出瞳の異なる領域の光を受光する。

#### 【0019】

撮影レンズ101からの光を瞳分割する光電変換部201Aの信号をX軸方向に並ぶ複数の単位画素200から取得し、これらの出力信号群で構成した被写体像をA像とする。同様に瞳分割する光電変換部201Bの信号をX軸方向に並ぶ複数の単位画素200から取得し、これらの出力信号群で構成した被写体像をB像とする。

10

#### 【0020】

A像とB像に対して相関演算を実施し、像のずれ量（瞳分割位相差）を検出する。さらに像のずれ量に対して撮影レンズ101の焦点位置と光学系から決まる変換係数を乗じることで、画面内の任意の被写体位置に対応した焦点位置を算出することができる。ここで算出された焦点位置情報に基づいて撮影レンズ101のフォーカス位置を制御することで撮像面位相差AF（オートフォーカス）が可能となる。また、A像信号とB像信号との足し合わせをA+B像信号として、このA+B像信号を通常の撮影画像に用いることができる。

#### 【0021】

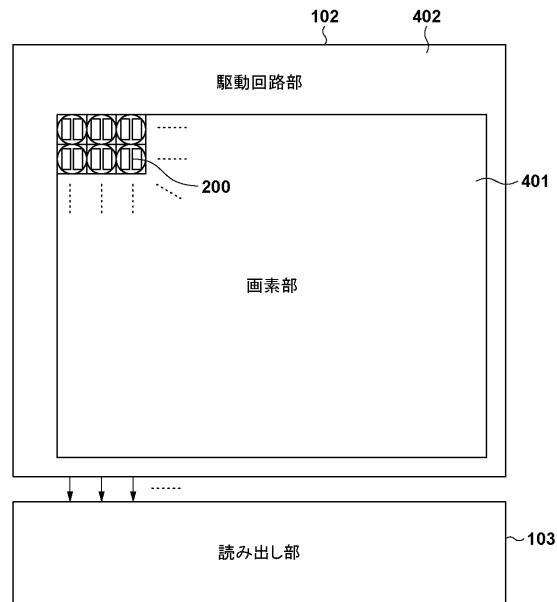

次に、撮像素子100の受光部102と読み出し部103の構成を図4、図5を用いて説明する。図4は、撮像素子100の受光部102と読み出し部103の構成例を示すブロツク図である。

20

#### 【0022】

受光部102は、画素部401と駆動回路部402とを有する。画素部401には複数の単位画素200が、水平方向（行方向）および垂直方向（列方向）に行列状に複数配列されている。図4においては単位画素200を2行3列の計6個図示しているが、実際は数百万、数千万の単位画素200が配置されている。駆動回路部402は画素部401を駆動するための電源回路、TG、走査回路などを含む。駆動回路部402によって駆動されて読み出された画素信号は、読み出し部103へ出力される。駆動回路部402は、図1の制御部104からの制御を受けて駆動される。読み出し部103には、画素部401からの画素信号が入力され、アナログデジタル変換（A/D変換）が行われる。なお、読み出し部103は複数の読み出し回路、例えば1列に1つの読み出し回路を備えて構成される。

30

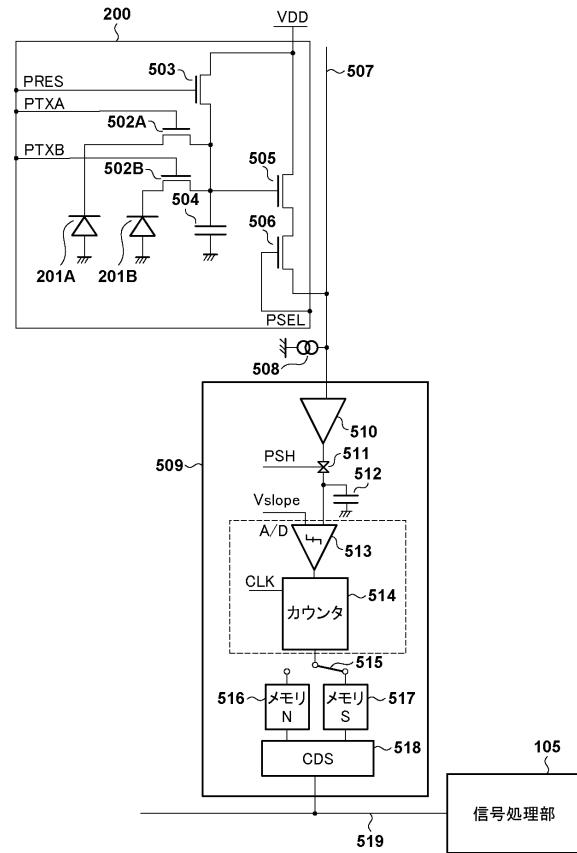

#### 【0023】

図5は、撮像素子100の単位画素200、及び読み出し部103を構成する読み出し回路509の一例を示す図である。単位画素200において、フォトダイオード（PD）からなる光電変換部201Aには転送スイッチ502Aが接続され、光電変換部201Bには転送スイッチ502Bが接続される。光電変換部201A, 201Bで発生した電荷は、それぞれ転送スイッチ502A, 502Bを介して共通のフローティングディフュージョン部（FD）504に転送され、一時的に保存される。FD504に転送された電荷は、選択スイッチ506がオンされると、ソースフォロワアンプを形成する増幅MOSトランジスタ（SF）505を介して電荷に対応した電圧として列出線507に出力される。列出線507には電流源508が接続されている。

40

#### 【0024】

リセットスイッチ503は、FD504の電位、及び転送スイッチ502A, 502Bを介して光電変換部201A, 201Bの電位をVDDにリセットする。転送スイッチ502A, 502B、リセットスイッチ503、選択スイッチ506は、それぞれ周辺の駆動回路部402に接続されている信号線を介して、制御信号PTXA, PTXB, PRE, PSELにより制御される。

#### 【0025】

50

次に、読み出し回路 509 の回路構成について説明する。アンプ 510 は、列出力線 507 に現れた信号を増幅し、容量 512 は信号電圧を保持するために用いられる。容量 512 への書き込みは、制御信号 PSH によりオン、オフされるスイッチ 511 により制御される。比較器 513 の一方の入力には、不図示のスロープ電圧発生回路から供給された参照電圧である Vslope が入力され、他方の入力には、容量 512 に書き込まれたアンプ 510 の出力が入力される。比較器 513 はアンプ 510 の出力と参照電圧 Vslope を比較し、その大小関係によってローレベル、ハイレベルの 2 値のいずれかを出力する。具体的には、Vslope がアンプ 510 の出力に対して小さい時にはローレベル、大きい時にはハイレベルを出力する。参照電圧 Vslope の遷移開始と共に CLK (クロック) が動き出し、カウンタ 514 は比較器 513 の出力がハイレベルの時に CLK に対応してカウントアップし、比較器 513 の出力がローレベルに反転すると同時にカウントの信号を停止する。

10

#### 【0026】

メモリ 516 には、FD504 のリセットレベルの信号（以下、「N 信号」）を A/D 変換したデジタル信号が保持され、メモリ 517 には、光電変換部 201A や光電変換部 201B の信号を FD504 の N 信号に重畠した信号（以下「S 信号」）を A/D 変換したデジタル信号が保持される。メモリ 516, 517 のどちらに書き込まれるかはスイッチ 515 により振り分けられる。メモリ 516, 517 に保持された信号は CDS 回路 518 にて S 信号から N 信号を差し引いた差分が算出される。そして、駆動回路部 402 の制御により、デジタル信号出力線 519 を介して信号処理部 105 へ出力される。

20

#### 【0027】

なお、読み出し回路 509 は画素の各列に対して 1 つ配置され、画素信号は行単位で読み出される。この場合、選択スイッチ 506 は行単位で制御され、選択された行の画素信号が一括して列出力線 507 に出力される。この読み出し回路 509 の数が多いほど、画素部 401 の画素信号を高速に信号処理部 105 に読み出すことができる。

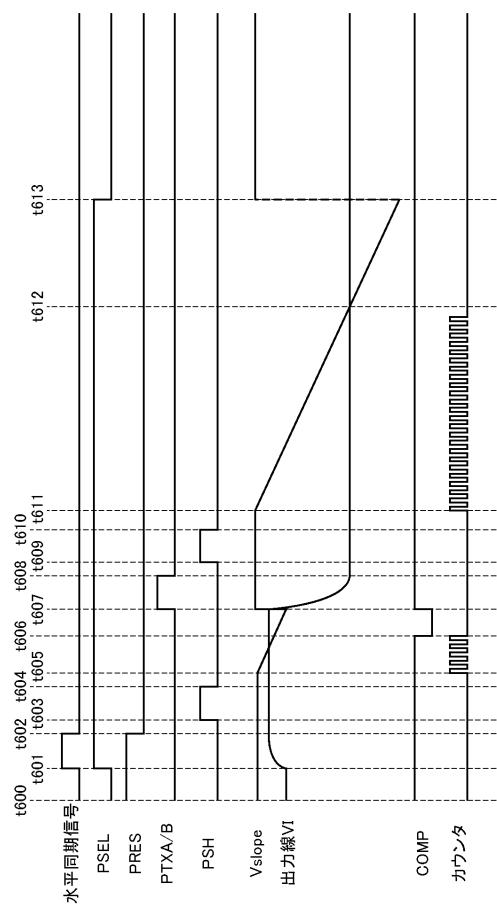

#### 【0028】

図 6 は、図 5 に示す回路構成を有する撮像素子 100 の単位画素 200 からの電荷読み出し動作の一例を示すタイミングチャートである。各駆動パルスのタイミング、参照電圧 Vslope、CLK、水平走査信号を模式的に示している。また、各タイミングにおける列出力線の電位 V1 も併せて示している。

30

#### 【0029】

光電変換部 201A からの信号の読み出しに先立って、リセットスイッチ 503 の信号線 PRES が Hi となる (t600)。これによって、SF (ソースフォロワアンプ) 505 のゲートがリセット電源電圧にリセットされる。時刻 t601 で制御信号 PSEL を Hi とし、SF505 を動作状態とする。そして、t602 で制御信号 PRES を Lo とすることで FD504 のリセットを解除する。このときの FD504 の電位を列出力線 507 にリセット信号レベル (N 信号) として読み出し、読み出し回路 509 に入力する。

#### 【0030】

時刻 t603、t604 で制御信号 PSH を Hi、Lo としてスイッチ 511 をオン、オフすることで、列出力線 507 に読み出された N 信号はアンプ 510 で所望のゲインで増幅されたのち容量 512 に保持される。容量 512 に保持された N 信号の電位は比較器 513 の一方に入力される。時刻 t604 でスイッチ 511 がオフされた後、時刻 t605 から t607 まで、不図示のスロープ電圧発生回路により、参照電圧 Vslope を時刻と共に初期値から減少させていく。参照電圧 Vslope の遷移開始と共に、CLK (クロック) をカウンタ 514 に供給する。CLK の数に応じてカウンタ 514 の値は増加していく。そして、比較器 513 に入力した参照電圧 Vslope が N 信号と同じレベルになると、比較器 513 の出力 COMP はローレベルとなり、同時にカウンタ 514 の動作も停止する (時刻 t606)。この、カウンタ 514 の動作が停止した時の値が、N 信号が A/D 変換された値となり、スイッチ 515 により、カウンタ 514 とメモリ 516 が接続され、N 信号のデジタル値が N 信号用メモリ 516 に保持される。

40

50

## 【0031】

次に、デジタル化されたN信号をN信号メモリ516に保持した後の時刻t607、t608で制御信号PTXAを順次Hi、Loとして光電変換部201Aに蓄積された光電荷をFD504に転送する。すると、電荷量に応じたFD504の電位変動が列出力線507に信号レベル(光成分+リセットノイズ成分(N信号))として読み出され、読み出し回路509に入力される。入力された信号(S(A)+N)はアンプ510で所望のゲインで増幅されたのち、時刻t609、t610で制御信号PSHを順次Hi、Loとしてスイッチ511をオン、オフするタイミングで容量512に保持される。容量512に保持された電位は比較器513の一方に入力される。時刻t610でスイッチ511がオフされた後、時刻t611からt613まで、スロープ電圧発生回路により、参照電圧Vslopeを時刻と共に初期値から減少させていく。参照電圧Vslopeの遷移開始と共に、CLKをカウンタ514に供給する。CLKの数に応じてカウンタ514の値は増加していく。そして、比較器513に入力した参照電圧VslopeがS信号と同じレベルになると、比較器513の出力COMPはローレベルとなり、同時にカウンタ514の動作も停止する(時刻t612)。この、カウンタ514の動作が停止した時の値が、S(A)+N信号がAD変換された値となる。そして、スイッチ515により、カウンタ514とメモリ517が接続され、S(A)+N信号のデジタル値がS信号用メモリ517に保持される。メモリ516及びメモリ517に保持された信号からCDS回路518により差動信号レベル(光成分)が算出され、リセットノイズ成分が除去されたS(A)信号が得られる。S(A)信号は、制御部104の制御により順次信号処理部105に送られる。

## 【0032】

以上が、単位画素200の光電変換部201Aからの信号を読み出す動作である。単位画素200のもう一方の光電変換部201Bからの信号を読み出す場合も同様に図6のタイミングチャートに従って駆動すればよい。ただし、この場合はt607、t608において制御信号PTXAの代わりにPTXBを順次Hi、Loする。すなわち、図6のt600からt613の駆動を1回目に制御信号PTXAをHi、Loして画素信号S(A)を読み出し、続いて2回目に制御信号PTXBをHi、Loして画素信号S(B)を読み出すことで、1行の読み出しが完了する。これを全行分繰り返すことで、全画素の画素信号S(A)、S(B)の読み出しが完了する。

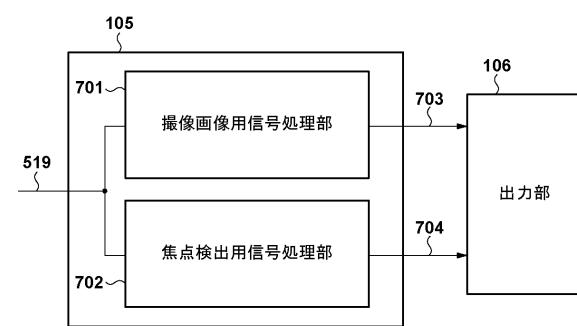

## 【0033】

図7は、撮像素子100の信号処理部105及び出力部106の構成例を示す図である。信号処理部105は撮像画像用信号処理部701と焦点検出用信号処理部702を有する。読み出し部103から出力された画素信号はデジタル信号出力線519を介して信号処理部105に入力される。入力された信号は制御部104からの制御に従って処理される。なお、撮像画像用信号処理部701と焦点検出用信号処理部702は、それぞれ不図示のメモリを備えるものとする。

## 【0034】

撮像画像用信号処理部701では、読み出された信号から、撮像画像用信号を算出する。すなわち、単位画素200の光電変換部201A、及び光電変換部201Bの画素信号S(A)、S(B)を受けて、混合処理を行い、S(A+B)信号を算出する。そして、画素信号S(A+B)を撮像画像用信号出力線703を介して出力部106に送る。撮像画像用信号処理部701において、2つの光電変換部の画素信号S(A)、S(B)を混合処理して出力部106から撮像素子100の外部に出力することで、撮像素子100の外部への信号伝送量を減らすことができる。なお、画素信号S(A)とS(B)の演算は、単位画素の両方の信号がそろった段階で可能となる。先に読み出された画素信号S(A)はメモリで保持しておき、画素信号S(B)が読み出され、撮像画像用信号処理部701に入力されると、順次S(A)+S(B)が演算され、出力部106から出力される。

## 【0035】

なお、撮像画像用信号処理部では更に単位画素200同士の信号を混合、平均化処理し

てもよい。例えば、赤( R )、緑( G )、青( B )のペイヤ配列のカラーフィルタが設けられた一般的な構成の画素部において、隣接する同色画素の信号を混合平均化演算して出力部 106 に送れば、更に信号伝送量を減らすことができる。また、画素部全ての信号を出力部 106 に出力するのではなく、必要な領域のみの信号を出力してもよい。これらの処理は制御部 104 により制御される。

#### 【 0036 】

続いて、焦点検出用信号処理部 702 の処理について説明する。焦点検出用信号処理部 702 では、読み出された信号から、焦点検出用信号を算出して出力する。位相差検出を行うためには、前述した通り、画素信号 S(A) と S(B) がそれぞれ必要である。しかし、画素部 401 の全ての画素の画素信号 S(A) と S(B) を出力部 106 から撮像素子 100 の外部に出力するとなると信号伝送量が膨大になり、高速読み出しに望ましくない。

10

#### 【 0037 】

そこで、焦点検出用信号処理部 702 において演算処理を行い、信号量を減らして出力部 106 から出力する。例えば、画素信号 S(A)、S(B) をそれぞれペイヤ加算して輝度値 Y 値を算出して、輝度信号 Y(A)、Y(B) を出力する。焦点検出演算は、信号を Y 値に変換してから演算することもあり、撮像素子 100 から出力する前に Y 値を演算することで、信号伝送量を 1/4 に減らすことができる。なお、Y 値の演算にはペイヤ単位の信号が必要になるため、演算に必要な信号が揃うまで、焦点検出用信号処理部 702 に入力された画素信号をメモリに保持しておく。つまり、R・G 行の信号が読み出された後、G・B 行の信号が読み出されるので、R・G 行の画素信号 S(A) と S(B) はメモリに保持しておき、G・B 行の信号が読み出されたら順次輝度信号 Y(A)、Y(B) を演算し、信号線 704 を介して出力部 106 から出力する。

20

#### 【 0038 】

また、更に焦点検出用信号処理部 702 において相関演算を行い、その演算値を信号線 704 から出力部 106 に出力してもよい。なお、相関演算を用いた位相差検出は公知の手法により実施可能である。相関演算値のみの出力であれば、その演算時の領域分割数に依存するものの、出力する信号量は大幅に減らすことができる。

#### 【 0039 】

以上のように、撮像画像用信号処理部 701 と焦点検出用信号処理部 702 を備える撮像素子 100 において、必要な信号のみを撮像素子 100 の外部に出力する信号処理を行う。これにより、信号伝送量を減らすことができ、撮像画像データと焦点検出情報を共に高速に得ることができる。

30

#### 【 0040 】

なお、本実施形態においては、撮像画像用信号処理部 701 と焦点検出用信号処理部 702 それぞれにメモリを備える構成とした。しかし、これらの前段にメモリを備えて、各処理部における演算に必要な信号が揃った段階で、撮像画像用信号処理部 701 と焦点検出用信号処理部 702 に信号を送る構成であってもよい。

#### 【 0041 】

また、本実施形態の説明において、焦点検出用信号として、輝度信号 Y(A)、及び Y(B) を出力したが、出力部 106 からは輝度信号 Y(A) のみを出力してもよい。具体的には、撮像画像用信号処理部 701 からは、撮像画像用信号、すなわち画素信号 S(A+B) が output されている。そのため、撮像素子 100 の外部に出力された後、位相差検出部 108 などで画素信号 S(A+B) から輝度信号 Y(A+B) を演算し、輝度信号 Y(A) の減算処理を行い、輝度信号 Y(B) を算出することで、焦点検出用信号を得てもよい。このように、焦点検出用信号処理部 702 からは輝度信号 Y(A) のみを出力することによって、信号伝送量を更に減らすことができる。

40

#### 【 0042 】

例えば、画素数が 2000 万画素であった場合、信号処理部を備えない場合は全画素分の画素信号 S(A)、S(B)、すなわち 4000 万個のデータを出力する必要がある。

50

一方、本実施形態の信号処理部を備える撮像素子により焦点検出用信号としてY値を演算して出力する場合、撮像画像用の2000万個のデータと焦点検出用の2000万 / 4 = 500万個のデータを出力することになり、信号伝送量が減ることがわかる。その結果、高速読み出しが可能となる。また、焦点検出用信号が相関演算値である場合、更に信号伝送量が減ることは明らかである。

#### 【0043】

また、図6のタイミングチャートにおいて、t607、t608で制御信号PTXA、PTXBを同時に制御して光電変換部201Aと光電変換部201Bの電荷が混合された単位画素200の信号を得ることも可能である。具体的には、図6のタイミングチャートに従って、光電変換部201Aの信号を読み出した後、制御信号PTXA、PTXBを同時にHi、Lo制御して信号を読み出せば画素信号S(A+B)を得ることが可能である。この場合、リセット信号の読み出しが1回減るため、更に高速読み出しが可能となる。10

#### 【0044】

画素から画素信号S(A)とS(A+B)が読み出された場合には、焦点検出用信号処理部702において、画素信号S(A+B)から画素信号S(A)を減算する処理を行えば、画素信号S(B)を得ることができる。もしくは、焦点検出処理部702においては、画素信号S(A)のみ処理して出力し、位相差検出部108で画素信号S(B)あるいは輝度信号Y(B)の算出を行ってもよい。

#### 【0045】

##### (第2の実施形態)

20

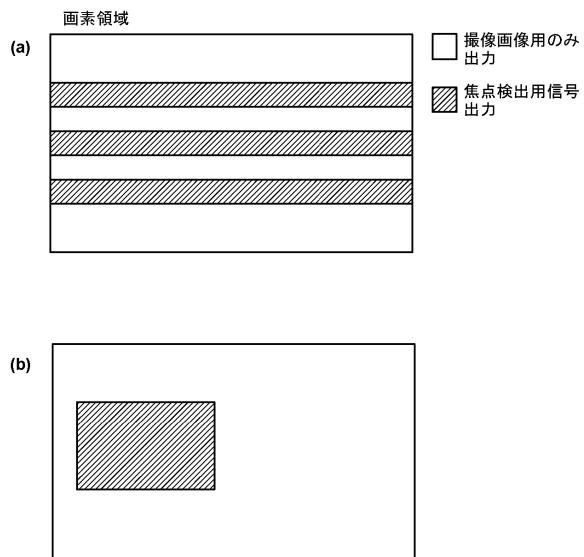

次に、本発明の第2の実施形態について説明する。第1の実施形態においては、画素部の全領域において焦点検出用信号の出力を行ったが、焦点検出用信号については必要な領域のみの信号を選択して出力すれば、更に高速化を実現することができる。

#### 【0046】

図8は、画素領域における、焦点検出用信号の出力領域の例を示した図である。斜線で示した領域は、焦点検出用信号と撮像画像用信号を出力し、それ以外の領域は撮像画像用信号のみを出力する。例えば、図8(a)に示した例のように、画素の広範囲において目的とする領域のみの焦点検出用信号を離散的に(選択的に)出力する。これによって、画素領域全体の焦点検出情報を得ることが可能となる一方で、撮像素子100の外部に出力する信号量を抑制することが可能となる。また、図8(b)に示した例の場合、一部の領域について詳細な焦点検出情報を得ることが可能となり、また撮像素子100の外部に出力する信号量を抑制することが可能となる。これらの出力する領域の選択は制御部104により制御される。焦点検出用信号処理部702において、出力対象領域の信号のみをメモリから読み出して演算する。30

#### 【0047】

なお、図8に示したような一部の領域における焦点検出用信号の出力は、Y値信号や相関演算結果でもよいが、画素信号S(A)であってもよい。Y値信号や相関演算結果に比べて伝送する信号量は多くなるが、必要領域のみ出力するため、信号伝送量の抑制は達成される。また、比較的小規模な信号処理回路でも実現可能である。

#### 【0048】

40

なお、焦点検出用信号処理部702においても、焦点検出用信号を混合、平均化処理してもよい。この場合、画素信号S(A)同士、画素信号S(B)同士について混合、平均化処理を行う。

#### 【0049】

以上のように、撮像画像用信号処理部701と焦点検出用信号処理部702を備える撮像素子100において、必要な信号のみを撮像素子100の外部に出力する信号処理を行う。これにより、焦点検出用信号の伝送量を減らすことができ、撮像画像データと焦点検出情報を共に高速かつ効率的に得ることができる。

#### 【0050】

なお、このように焦点検出に使用する画素を限定することによって、1フレームの読み

50

出し時間を短縮する方法がある。通常は、焦点検出処理に使用する行のみ単位画素内の2つの光電変換部の信号をそれぞれ読み出し、焦点検出処理に使用しない行は2つの光電変換部の信号を混合して画像生成用の信号のみを読み出すことで読み出し時間の増大を抑制する。この場合、焦点検出用として読み出された2つの光電変換部の個々の出力信号は混合して撮像画像用の画素信号として使用することが可能である。しかし、信号の読み出し方法や2つの光電変換部の出力信号の混合方法が焦点検出処理に使用する行としない行とで異なることにより、ノイズレベル等に差が生じてしまい、その結果得られる撮像画像が劣化するという問題が生じる。しかし、本実施形態のように焦点検出用信号処理部を備えることによって、画素部からの信号は全て同様の読み出しタイミングで読み出し、焦点検出用信号処理部702で出力する画素を選択できる。そのため、撮像画像に用いる画素信号 $S(A+B)$ のノイズ量が領域によって異なることもなく、高品質の撮像画像を得ることができる。

10

#### 【0051】

##### (第3の実施形態)

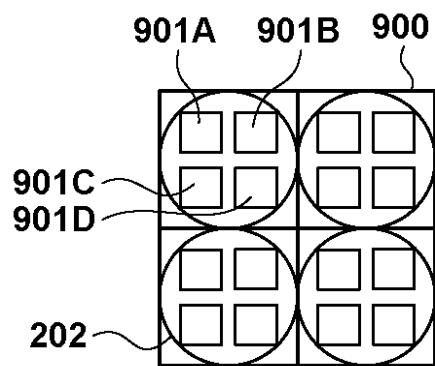

次に、本発明の第3の実施形態について説明する。第3の実施形態では、画素部402の単位画素200の構成が異なる。図9は、撮像素子100の受光部102及びマイクロレンズアレイを光軸方向(Z方向)から観察した図である。1つのマイクロレンズ202に対して、4つの光電変換部901A、901B、901C、901Dが配置されている。このように、X軸方向及びY軸方向それぞれ2つの合計4つの光電変換部を有することで、4つに分割された射出瞳領域の光をそれぞれ受光することができる。このような単位画素がそれぞれ4つの光電変換部を備えている画素部401により構成される撮像素子100における、信号読み出し方法、及び信号処理部105の処理について説明する。

20

#### 【0052】

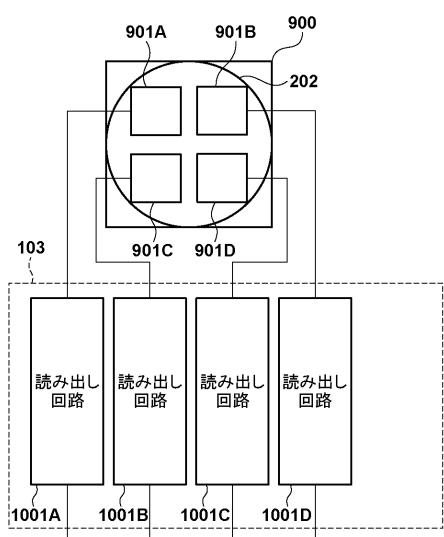

図10は、単位画素900及び読み出し部103の構成の一例を示す模式図である。図10の構成では、各光電変換部のそれぞれに読み出し回路を備えている。すなわち、光電変換部901Aの画素信号は読み出し回路1001Aにより読み出される。以下同様に、光電変換部901Bは読み出し回路1001B、光電変換部901Cは読み出し回路1001C、光電変換部901Dは読み出し回路1001Dにより読み出される。光電変換部からの信号読み出し動作については、図5、図6で説明した駆動方法とほぼ同様の方法で実施可能であるため、説明は省略する。

30

#### 【0053】

各光電変換部から読み出された信号に対する信号処理部105の処理について説明する。撮像画像用信号処理部701では、読み出された信号から、撮像画像用信号を算出する。すなわち、単位画素900の複数の光電変換部901A、901B、901C、901Dの画素信号 $S(A)$ 、 $S(B)$ 、 $S(C)$ 、 $S(D)$ を受けて、混合処理を行い、画素信号 $S(A+B+C+D)$ を算出する。そして、画素信号 $S(A+B+C+D)$ を撮像画像用信号出力線703を介して出力部106に送る。撮像画像用信号処理部701において、複数の光電変換部の信号を混合処理して出力部106から撮像素子100の外部に出力することで、撮像素子100の外部への信号伝送量を減らすことができる。単位画素900のように4つの光電変換部を備えるような撮像素子においては、その効果はより大きくなる。

40

#### 【0054】

続いて、焦点検出用信号処理部702の処理について説明する。図9に示した様な単位画素900当たり4つの光電変換部を備える撮像素子の場合、焦点検出のためには4つの光電変換部の信号を個別に読み出す必要があり、信号伝送量が膨大になり、高速読み出しに望ましくない。第1の実施形態で説明したように、Y値を演算して出力したり、相關演算結果のみを出力することが好適である。必要な領域のみの信号を出力すれば、更に信号伝送量を減らすことができる。

#### 【0055】

また、図9のように単位画素900が $2 \times 2$ の光電変換部を備える構成の場合、左右方

50

向に加え、上下方向の位相差検出も行うことができる。例えば、画素信号 S ( A ) と S ( C ) を混合処理し、画素信号 S ( B ) と S ( D ) を混合処理してそれぞれ出力する。この場合、得られた焦点検出用信号からは左右方向に瞳分割された位相差方式の焦点検出が可能となる。また、画素信号 S ( A ) と S ( B ) を混合処理し、画素信号 S ( C ) と S ( D ) を混合処理してそれぞれ出力した場合は、得られた焦点検出用信号からは上下方向に瞳分割された位相差方式の焦点検出が可能となる。これらは、被写体に応じて切り替えて出力することで、縦縞、横縞それぞれの被写体に対して精度良く焦点検出することができる。また、画素の領域によって出力パターンを変えてよい。

#### 【 0 0 5 6 】

更に、焦点検出用信号処理部 702において、得られた混合信号（例えば、S ( A + C ) と S ( B + D ) ）を用いて相関演算を行い、その結果のみを出力してもよい。焦点検出用信号処理部 702で相関演算処理をすれば撮像素子 100 から出力する信号伝送量を減らすことができる。また、同一領域において左右方向と上下方向両方の相関演算を行って出力しても信号伝送量を抑えることができる。

10

#### 【 0 0 5 7 】

このように、多分割画素を備えた撮像素子において、撮像素子内に焦点検出用信号処理部 702を備えることで、撮像素子から出力する信号量の増加を抑制し、高速に撮像画像データと焦点検出情報を得ることができる。更に、左右方向と上下方向の位相差情報を取得できるため、精度良く焦点検出を行うことができる。本実施形態では、単位画素当たり 4つの光電変換部を有する撮像素子を例に説明したが、更に多くの光電変換部を有する構成であってもよい。より視差を付けるために、必要な P D の信号のみを出力したり、斜め方向に信号を加算して出力してもよい。

20

#### 【 0 0 5 8 】

##### （第 4 の実施形態）

第 1 および第 2 の実施形態で説明したような撮像素子 100 の信号処理部 105 は大規模な回路となるため、撮像素子 100 は全体として大面積なものとなる可能性が高い。そこで、本実施形態においては、面積の増大を抑制する撮像素子 100 の構成について説明する。

#### 【 0 0 5 9 】

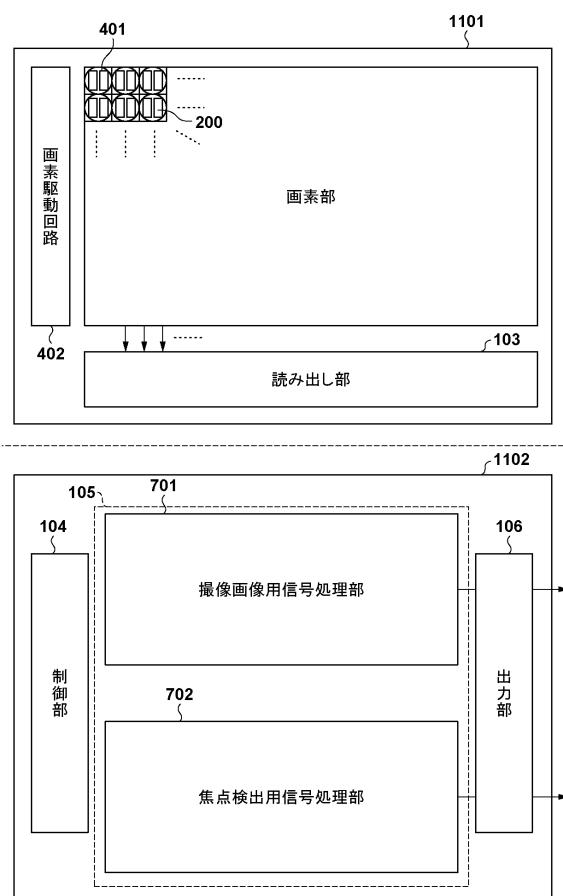

図 11、図 12 は、第 3 の実施形態における撮像素子 100 の構成図である。本実施形態の撮像素子は画素領域チップ 1101、信号処理チップ 1102 を積層させた構成（多層構造）を有する。各チップ間の配線は、公知の基板積層技術により、マイクロバンプ等を用いて電気的に接続される。

30

#### 【 0 0 6 0 】

画素領域チップ 1101 は、複数の光電変換部を備えた単位画素 200 が行列状に配置された画素部 401 と、駆動回路部 402 と、読み出し部 103 とを備える。駆動回路部 402 は、画素部 401 の画素に対して駆動信号を送る。なお、図 11 では、単位画素 200 は、2 つの光電変換部を有するが、光電変換部の数はこれに限定されるものではない。

#### 【 0 0 6 1 】

40

読み出し部 103 は多数の、例えば画素 1 列当たり 1 つの読み出し回路 509 を備えて構成され、画素部 401 の画素信号を読み出す。読み出された画素信号は駆動回路部 402 の制御により、垂直・水平選択がなされ、順次、信号処理部 105 に転送される。

#### 【 0 0 6 2 】

信号処理チップ 1102 は、制御部 104、信号処理部 105、出力部 106 を備える。信号処理部 105 は、撮像画像用信号処理部 701 と焦点検出用信号処理部 702 を有し、読み出し部 103 から読み出された画素信号を処理して、出力部 106 を介して撮像素子 100 の外部に出力する。信号処理部 105 における信号処理については、第 1 および第 2 の実施形態で説明した処理と同様であるため説明を省略する。撮像素子 100 は、図 12 に示したように、画素領域チップ 1101、信号処理チップ 1102 が積層されて

50

一体となった構成を有する。

#### 【0063】

以上のように、撮像素子が積層構造となることにより、信号処理部105に十分な面積を取ることができ、大規模な回路を実装することが可能となる。信号処理部105において、必要な信号のみを撮像素子100の外部に出力する信号処理を行うことにより信号伝送量を減らすことができ、撮像画像データと焦点検出情報を共に高速に得ることが可能となる。

#### 【0064】

##### (第5の実施形態)

第1および第2の実施形態で説明したような単位画素当たり複数の光電変換部を備える画素部から構成される撮像素子においては、読み出し回路509が多い方が好ましい。例えば、単位画素当たり1つの読み出し回路を備える構成や、更に、1つの光電変換部当たり1つの読み出し回路を備える構成であれば、全画素同時に画素信号を読み出してA/D変換することができるため、より高速な読み出しが可能となる。この場合、読み出し回路を配するのに面積が必要であり、積層構造の撮像素子であることが望ましい。

10

#### 【0065】

図13は、第5の実施形態における撮像素子100の構成を示す図である。本実施形態の撮像素子は画素領域チップ1301、読み出し回路チップ1302、信号処理チップ1303を積層させた構成を有する。各チップ間の配線は、公知の基板積層技術により、マイクロバンプ等を用いて電気的に接続される。

20

#### 【0066】

画素領域チップ1301は、複数の光電変換部を備えた単位画素200が行列状に配置された画素部401と駆動回路部402を備える。駆動回路部402は、画素部401の画素に対して駆動信号を送る。なお、図13では、単位画素200は2つの光電変換部を備えるが、光電変換部の数は2つに限定されるものではない。

#### 【0067】

読み出し回路チップ1302は、読み出し部103、垂直選択回路1304、水平選択回路1305を備える。読み出し部103は多数の読み出し回路509を有し、画素部401の画素信号を読み出す。読み出された画素信号は垂直選択回路1304、水平選択回路1305の制御により、順次信号処理部105に転送される。

30

#### 【0068】

信号処理チップ1303は、制御部104、信号処理部105、出力部106を備える。信号処理部105は、撮像画像用信号処理部701と焦点検出用信号処理部702を有し、読み出し部103により読み出された画素信号を信号処理部105で処理して、出力部106を介して撮像素子100の外部に出力する。信号処理部105における信号処理については、第1および第2の実施形態で説明した処理と同様であるため、説明を省略する。

#### 【0069】

撮像素子100は、画素領域チップ1301、読み出し回路チップ1302、信号処理チップ1303が積層されて一体となった構成を有する。ところで、本実施形態の構成のように、例えば1つの光電変換部当たり1つの読み出し回路を備える構成の場合、画素信号が信号処理部105に読み出される時間は飛躍的に速くなる。例えば、1つの光電変換部の読み出しにかかる時間を<sup>1</sup>とすると、1列当たり1つの読み出し回路を備える撮像素子の場合、1フレーム分の画素信号を読み出すには<sup>1</sup>×行数分の時間がかかる。一方、1つの光電変換部当たり1つの読み出し回路を備える場合は、<sup>1</sup>の時間で1フレーム分の画素信号が読み出される。ただしこの場合は、画素信号を受け取る信号処理部105での信号の受け取り、及び信号処理が律速することが懸念される。しかし、本実施形態のように、積層構造からなる撮像素子100の信号処理部105は面積を大きく配することができるため、読み出し回路チップ1302からの信号の伝送ラインを多数設けることができ、高速に画素信号を信号処理部105に送ることができる。また、信号処理部105には信

40

50

号処理回路を多数実装することができるため、並列処理が可能となり、信号処理時間も高速化される。

### 【 0 0 7 0 】

以上のように、撮像素子が積層構造となることにより、読み出し部、信号処理部に十分な面積を取ることができる。本実施形態の撮像素子は、画素部からの信号読み出しも高速になり、更に信号処理部 105において、必要な信号のみを撮像素子の外部に出力する信号処理を行うことにより、信号伝送量を減らすことができ、撮像画像データと焦点検出情報と共に高速に得ることができる。

### 【 0 0 7 1 】

(その他の実施形態)

10

本発明は、上述の実施形態の 1 以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける 1 つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1 以上の機能を実現する回路(例えば、ASIC)によっても実現可能である。

### 【 符号の説明 】

### 【 0 0 7 2 】

100 : 撮像素子、101 : 撮影レンズ、102 : 受光部、103 : 読み出し部、104 : 制御部、105 : 信号処理部、106 : 出力部、107 : 位相差検出部、108 : 画像処理部、109 : 全体制御・演算部、110 : 表示部、111 : 記録部、112 : メモリ部、113 : 操作部、114 : レンズ制御部、200 : 201A、201B、202 : 撮像素子構造、300 : 光軸 Z、301 : 302 : 303 : 撮影レンズ

【 図 1 】

【 図 2 】

【 図 3 】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図12】

【図13】

---

フロントページの続き

(72)発明者 石井 美絵

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 鈴木 明

(56)参考文献 特開2007-324985(JP,A)

特開2014-146023(JP,A)

特開2014-72541(JP,A)

特開2014-179911(JP,A)

特開2015-2531(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H04N 5/222 - 5/257

G02B 7/34

G03B 13/36