(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5629329号

(P5629329)

(45) 発行日 平成26年11月19日(2014.11.19)

(24) 登録日 平成26年10月10日(2014.10.10)

(51) Int.Cl.

H03K 5/04 (2006.01)

F 1

H03K 5/04

請求項の数 19 (全 20 頁)

(21) 出願番号 特願2012-549162 (P2012-549162)

(86) (22) 出願日 平成23年1月19日 (2011.1.19)

(65) 公表番号 特表2013-517711 (P2013-517711A)

(43) 公表日 平成25年5月16日 (2013.5.16)

(86) 國際出願番号 PCT/US2011/021762

(87) 國際公開番号 WO2011/091073

(87) 國際公開日 平成23年7月28日 (2011.7.28)

審査請求日 平成25年11月18日 (2013.11.18)

(31) 優先権主張番号 12/690,064

(32) 優先日 平成22年1月19日 (2010.1.19)

(33) 優先権主張国 米国(US)

早期審査対象出願

前置審査

(73) 特許権者 597154922

アルテラ コーポレイション

Altera Corporation

アメリカ合衆国 95134 カリフォルニア州 サンホセ イノベーション ドライブ 101

(74) 代理人 100078282

弁理士 山本 秀策

(74) 代理人 100113413

弁理士 森下 夏樹

(72) 発明者 チョン, ヤン

アメリカ合衆国 カリフォルニア 95134, サンノゼ, イノベーション ドライブ 101

最終頁に続く

(54) 【発明の名称】集積回路のメモリインターフェースのためのデューティサイクル補正器回路

## (57) 【特許請求の範囲】

## 【請求項 1】

集積回路(I C)であって、該I Cは、

第1のクロック信号を受信するように連結されたスプリッタ回路であって、該スプリッタ回路は、該第1のクロック信号に基づいて第2のクロック信号および第3のクロック信号を発生させ、該スプリッタは、該第1のクロック信号を受信するように連結されたバスゲートを備え、該バスゲートは、該第2のクロック信号を発生させる、スプリッタ回路と、

該第2のクロック信号を受信するように連結された第1の遅延回路であって、該第1の遅延回路は、該第2のクロック信号を遅延させて、第2の遅延したクロック信号を発生させる、第1の遅延回路と、

該第3のクロック信号を受信するように連結された第2の遅延回路であって、該第2の遅延回路は、該第3のクロック信号を遅延させて、第3の遅延したクロック信号を発生させる、第2の遅延回路と、

該第2の遅延したクロック信号および該第3の遅延したクロック信号を受信するように連結された補正器回路であって、該補正器回路は、該第1のクロック信号に対して50%のデューティサイクルを有するクロック出力信号を発生させる、補正器回路と

を備える、I C。

## 【請求項 2】

複数の前記補正器回路の各々から前記クロック出力信号を受信するように連結された第

1のセレクタ回路であって、該第1のセレクタ回路は、該複数の補正器回路のうちの1つから、第1の補正されたクロック出力信号を選択および出力する、第1のセレクタ回路と、

該複数の補正器回路の各々から該クロック出力信号を受信するように連結された第2のセレクタ回路であって、該第2のセレクタ回路は、該複数の補正器回路のうちの別の1つから、第2の補正されたクロック出力信号を選択および出力する、第2のセレクタ回路とをさらに備える、請求項1に記載のIC。

#### 【請求項3】

前記第2の補正されたクロック出力信号は、前記出力された第1の補正されたクロック出力信号に対して位相シフトしている、請求項2に記載のIC。 10

#### 【請求項4】

前記第1の補正されたクロック出力信号および前記第2の補正されたクロック出力信号は、位相整列から実質的に90度外れている、請求項2に記載のIC。

#### 【請求項5】

前記第1および第2の補正されたクロック出力信号を受信するように連結された複数のストレージ回路をさらに備え、該複数のストレージ回路は、該第1および第2の補正されたクロック出力信号のエッジを遷移させることによってトリガされる、請求項2に記載のIC。

#### 【請求項6】

前記補正器回路は、SRラッチを備える、請求項1に記載のIC。 20

#### 【請求項7】

前記スプリッタ回路は、前記第1のクロック信号を受信するように連結されたインバータを備え、該インバータは、前記第3のクロック信号を発生させ、該第3のクロック信号は、前記第2のクロック信号の反転信号である、請求項1に記載のIC。

#### 【請求項8】

前記第1および第2の遅延回路は各々、直列に連結された複数のバッファを含む、請求項1に記載のIC。

#### 【請求項9】

デューティサイクル補正器回路であって、該デューティサイクル補正器回路は、

第1のクロック信号を受信するように連結された第1のパルス発生器回路であって、該第1のパルス発生器回路は、該第1のクロック信号に基づいて第1のパルス信号を発生させる、第1のパルス発生器回路と、 30

第2のクロック信号を受信するように連結された第2のパルス発生器回路であって、該第2のパルス発生器回路は、該第2のクロック信号に基づいて第2のパルス信号を発生させる、第2のパルス発生器回路と、

該第1および第2のパルス信号を受信するように連結されたラッチであって、該ラッチは、クロック入力信号に対して50%のデューティサイクルを有するクロック出力信号を発生させる、ラッチと

を備え、

該第1および第2のパルス発生器回路は各々、

該第1または第2のクロック信号のうちの1つを受信するように連結された設定可能遅延連鎖回路と、

該設定可能遅延連鎖の出力に連結されたインバータと、

該インバータの出力、および該第1または第2のクロック信号のうちの1つに連結された論理ゲートと

を備え、それにより、該第1および第2のパルス発生器の各々は、該クロック入力信号のパルスよりも小さい幅を有するパルスを発生させる、デューティサイクル補正器回路。

#### 【請求項10】

デューティサイクル補正器回路であって、該デューティサイクル補正器回路は、

第1のクロック信号を受信するように連結された第1のパルス発生器回路であって、該

10

20

30

40

50

第1のパルス発生器回路は、該第1のクロック信号に基づいて第1のパルス信号を発生させる、第1のパルス発生器回路と、

第2のクロック信号を受信するように連結された第2のパルス発生器回路であって、該第2のパルス発生器回路は、該第2のクロック信号に基づいて第2のパルス信号を発生させる、第2のパルス発生器回路と、

該第1および第2のパルス信号を受信するように連結されたラッチであって、該ラッチは、クロック入力信号に対して50%のデューティサイクルを有するクロック出力信号を発生させる、ラッチと

該クロック入力信号を受信するように連結されたスプリッタ回路であって、該スプリッタ回路は、該クロック入力信号を第3のクロック信号と第4のクロック信号とに分割する、スプリッタ回路と、10

該第3および第4のクロック信号の各々を受信するように連結された遅延連鎖回路であって、該遅延連鎖回路は、該第3および第4のクロック信号を遅延させて、第3および第4の遅延したクロック信号を該第1および第2のクロック信号としてそれぞれ発生させる、遅延連鎖回路と

を備える、デューティサイクル補正器回路。

**【請求項11】**

前記遅延回路は、直列に連結された複数のバッファと、該複数のバッファの各々から出力を受信するように連結されたセレクタ回路とを備える、請求項10に記載のデューティサイクル補正器回路。20

**【請求項12】**

前記第2のクロック信号は、前記第1のクロック信号の反転信号である、請求項9に記載のデューティサイクル補正器回路。

**【請求項13】**

前記第1のパルス信号は、前記ラッチをセットし、前記第2のパルス信号は、該ラッチをリセットする、請求項9に記載のデューティサイクル補正器回路。

**【請求項14】**

前記設定可能遅延連鎖回路は、前記第1および第2のパルス信号の幅を制御する、請求項9に記載のデューティサイクル補正器回路。30

**【請求項15】**

スプリッタ回路と遅延回路と第1のパルス発生器回路と第2のパルス発生器回路とラッチとを備える集積回路(I C)の作動方法であって、該方法は、

該スプリッタ回路が、第1のクロック信号を分割することにより、第2および第3のクロック信号を発させることと、

該遅延回路が、該第2および第3のクロック信号に遅延を適用することにより、該第2および第3のクロック信号から第2および第3の遅延したクロック信号を発させることと、

該第1のパルス発生器回路が、該第2の遅延したクロック信号に基づいて第1のパルス信号を発せることであって、該第1のパルス信号は、該第2のクロック信号の遷移に従って第1の論理レベルから第2の論理レベルまで遷移することと、40

該第2のパルス発生器回路が、該第3の遅延したクロック信号に基づいて第2のパルス信号を発せることであって、該第2のパルス信号は、該第3のクロック信号の遷移に従って該第1の論理レベルから該第2の論理レベルまで遷移することと、

該ラッチが、該第1のクロック信号に対して50%のデューティサイクルを有するクロック出力信号を発せることであって、該クロック出力信号は、該第1のクロック信号に対して位相シフトしていることと

を含む、方法。

**【請求項16】**

前記第1のパルス信号の幅は、前記第2のクロック信号の幅の半分未満である、請求項15に記載の方法。50

**【請求項 17】**

前記クロック出力信号の立ち上がりエッジは、前記第1のパルス信号の立ち上がりエッジと実質的に同時に生じ、該出力クロック信号の立ち下がりエッジは、前記第2のパルス信号の立ち上がりエッジと実質的に同時に生じる、請求項15に記載の方法。

**【請求項 18】**

前記第3のクロック信号は、前記第2のクロック信号の反転信号である、請求項15に記載の方法。

**【請求項 19】**

前記第1および第2のパルス信号を発生させることは、前記第2のクロック信号が、前記第1の論理レベルから前記第2の論理レベルまで遷移するときに、前記ラッチをセットすることと、前記第3のクロック信号が、該第1の論理レベルから該第2の論理レベルまで遷移するときに、該ラッチをリセットすることとを含む、請求項15に記載の方法。10

**【発明の詳細な説明】****【背景技術】****【0001】**

デジタル回路において、クロック信号は、回路内の異なる部品の間および異なる回路の間での通信を同期させる。クロック信号と協働するように設計された回路は、クロック信号の立ち上がりまたは立ち下がりエッジにおいて応答し得る。單一データレート（S D R）メモリインターフェースは、通常、立ち上がりまたは立ち下がりエッジのいずれかのみを利用してデータを転送する。一方、ダブルデータレート（D D R）メモリインターフェースは、クロック信号の立ち上がりエッジおよび立ち下がりエッジの両方においてデータを転送する。したがって、D D Rメモリインターフェースにおけるデータ転送レートは、通常のS D Rメモリインターフェースの転送レートの2倍の速さである。20

**【0002】**

データレートの増加に伴って、有効データが捕捉され得るウインドウのサイズが縮小され、潜在的にデータの損失につながり得るので、デューティサイクルの歪みが問題となる場合がある。デューティサイクルは、クロックまたはシステムが、「アクティブ」状態にある時間の一部である。非対称デューティサイクルは、システム内のすべてのクロックの同期をより困難にするだろうため、実質的に対称であるデューティサイクルが、最高速度用途に対して要求される。対称デューティサイクルまたは50%のデューティサイクルとは、各クロック周期が等しい高い周期と低い周期とを有することを意味する。言い換えると、50%のデューティサイクルを有するクロック信号は、論理1においてクロック周期の半分を費やし、論理0において残りの半分を費やす。30

**【0003】**

種々のデューティサイクル補正技法は、通常、デューティサイクルの歪みを補正するために採用される。クロック信号の立ち上がりおよび立ち下がりエッジを遅延させることができるので、静的遅延連鎖が一般に使用される。しかしながら、デューティサイクルの歪みは、通常、デバイス毎に異なるので、1つの静的遅延セットを使用して異なるデバイスにおけるデューティサイクルの歪みを補正することは困難である。また、異なるプロセス、電圧、および温度（P V T）の条件下において動作するデバイスに対する正確なセットを見つけることは困難であり、何故なら、デューティサイクルの歪みも異なるP V T条件下において変動するからである。40

特許文献1は、入力クロック信号を受信し、遅延が入力クロックにロックされた出力クロック信号を生成する遅延ロックループ回路であって、電圧制御遅延ライン（V C D L）、マルチブレクサ、位相検出制御ループ、位相選択制御ループを含む遅延ロックループ回路を開示する。V C D Lは、一セットのマルチ位相遅延クロック信号を生成する。マルチブレクサは、選択信号に基づいて、出力クロック信号として、遅延クロック信号のうちの1つを選択する。位相検出制御ループは、入力および出力クロック信号間の位相差を測定し、V C D Lを駆動するための制御電圧を生成する。位相選択制御ループは、制御電圧を測定し、制御電圧に基づいて選択信号を生成し、マルチブレクサに、現在選択されている50

遅延クロック信号に対して位相遅延量を増大あるいは低減した遅延クロック信号を選択させるか、現在選択されている遅延クロック信号をホールドさせる。

特許文献2は、D L Lクロック信号の位相を制御して、立ち上がりクロック信号および立ち下りクロック信号を生成するように構成される位相スプリッタと、制御信号に応答して立ち上がりクロック信号および立ち下りクロック信号を遅延させて、遅延した立ち上がりクロック信号および遅延した立ち下りクロック信号を生成するように構成されるクロック遅延ユニットと、遅延した立ち上がりクロック信号および遅延した立ち下りクロック信号のエッジタイミングに応答してトグルする補正立ち上がりクロック信号および補正立ち下りクロック信号を生成するように構成されるデューティ比補正ユニットと、補正立ち上がりクロック信号および補正立ち下りクロック信号のデューティサイクルを検出して、上記制御信号を生成するように構成される遅延制御ユニットとを含んでいるデューティサイクル補正回路を開示する。10

特許文献3は、半導体メモリ装置内の高められた動作周波数をサポートする遅延ロップループを開示する。遅延ロップループにおいて使用される出力ドライバーは、遅延ロップループからの出力を受信して、読み出しコマンドに対応する読み出しデータを出力するための第1のD L Lクロックを生成する第1のドライビングブロックと、遅延ロップループからの出力を受信して、書き込み動作中の電流消費を低減するための第2のD L Lクロックを生成する第2のドライビングブロックとを備え、第1のドライビングブロックは、第2のドライビングブロックよりも大きな遅延量を有する。

特許文献4は、第1および第2の遅延クロックデューティ比のデューティ比を補正して第1および第2の補正クロックを生成するデューティ比補正ユニットを含むD L L回路を開示する。デューティ比検出ユニットは、第1および第2の補正クロックのデューティ比を検出し、それにより、第1および第2の検出信号を生成する。電圧比較ユニットは、第1および第2の検出信号のレベルを比較し、それにより、第1のファイン制御信号を生成する。動作モード設定ユニットは、ロック完了信号および第2のファイン制御信号を生成する。スイッチングユニットは、ロック完了信号がイネーブルされているか否かに従って、第1のファイン制御信号または第2のファイン制御信号を選択的に遅延制御ユニットに送信する。20

#### 【先行技術文献】

##### 【特許文献】

【特許文献1】 米国特許第7,236,028号明細書

【特許文献2】 米国特許出願公開第2009/0231006号明細書

【特許文献3】 米国特許第7,365,583号明細書

【特許文献4】 米国特許出願公開第2008/0164920号明細書

#### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0004】

したがって、異なるP V T条件下において動作する異なるデバイスにおけるデューティサイクルの歪みを自動的に補正することができるデューティサイクル補正器回路を有することが望ましい。このことは、本発明が生じることの背景にある。40

##### 【課題を解決するための手段】

##### 【0005】

本発明の実施形態は、集積回路(I C)内のデューティサイクルの歪みを補正するための回路および方法を含む。

##### 【0006】

本発明は、プロセス、装置、システム、デバイス、またはコンピュータ可読媒体上の方法等、数多くの方法で実現することができることを理解されたい。以下、本発明のいくつかの発明的実施形態を説明する。

##### 【0007】

一実施形態において、補正器回路を有するI Cが開示される。I Cは、クロック信号を50

受信し、クロック信号を2つの異なるクロック信号に分割するスプリッタ回路を含む。一実施形態において、クロック信号のうちの一方は、他方の反転したバージョンである。クロック信号はそれぞれ遅延回路に連結される。遅延回路はそれぞれ対応するクロック信号の遅延したバージョンを発生させる。補正器回路は、クロック信号の遅延したバージョンの両方に連結され、クロック信号の遅延したバージョンに基づいてクロック出力信号を発生させる。発生させられたクロック出力信号は、補正されたデューティサイクルを有する。

#### 【0008】

本発明によるさらに別の実施形態において、デューティサイクル補正器回路が提供される。回路は、ラッチと、パルス発生器回路とを含む。パルス発生器回路の1つは、第1のクロック信号を受信するように連結される。第1のパルス信号は、第1のクロック信号に基づいて、パルス発生器回路によって発生させられる。別のパルス発生器回路は、第2のクロック信号を受信するように連結される。第2のパルス信号は、第2のクロック信号に基づいてパルス発生器回路によって発生させられる。ラッチは、2つのパルス信号を受信し、2つのパルス信号に基づいて補正されたデューティサイクルを有するクロック出力信号を発生させる。

#### 【0009】

本発明による代替実施形態において、I Cを動作させる方法が提供される。方法は、クロック信号を2つの異なるクロック信号に分割するステップを含む。遅延が、2つのクロック信号の各々に適用されることにより、2つのクロック信号の遅延したバージョンを発生させる。2つのパルス信号は、2つのクロック信号の遅延したバージョンのそれぞれに基づいて発生させられる。発生させられたパルス信号は、対応するクロック信号の遅延したバージョンの遷移に基づいて、1つの論理レベルから別の論理レベルまで遷移する。補正されたデューティサイクルを有するクロック出力は、第1および第2のパルス信号に基づいて発生させられる。

#### 【0010】

本発明の他の側面は、本発明の原理の一例として示される添付図面に関連してなされる、以下の発明を実施するための形態から明らかになるであろう。

本願明細書は、例えば、以下の項目も提供する。

##### (項目1)

集積回路(I C)であって、該I Cは、

第1のクロック信号を受信するように連結されるスプリッタ回路であって、該スプリッタ回路は、該第1のクロック信号に基づいて第2のクロック信号および第3のクロック信号を発生させる、スプリッタ回路と、

該第2のクロック信号を受信するように連結される第1の遅延回路であって、該第1の遅延回路は、該第2のクロック信号の遅延したバージョンを発生させる、第1の遅延回路と、

該第3のクロック信号を受信するように連結される第2の遅延回路であって、該第2の遅延回路は、該第3のクロック信号の遅延したバージョンを発生させる、第2の遅延回路と、

該第2および第3のクロック信号の該遅延したバージョンを受信するように連結される補正器回路であって、該補正器回路は、該第1のクロック信号に対して修正されたデューティサイクルを有するクロック出力信号を発生させる、補正器回路と

を備える、I C。

##### (項目2)

複数の前記補正器回路の各々から前記クロック出力信号を受信するように連結される第1のセレクタ回路であって、該第1のセレクタ回路は、該複数の補正器回路のうちの1つから、第1の補正されたクロック出力信号を選択および出力する、第1のセレクタ回路と、

該複数の補正器回路の各々から該クロック出力信号を受信するように連結される第2の

10

20

30

40

50

セレクタ回路であって、該第2のセレクタ回路は、該複数の補正器回路のうちの別の1つから、第2の補正されたクロック出力信号を選択および出力する、第2のセレクタ回路とをさらに備える、項目1に記載のIC。

(項目3)

前記第2の補正されたクロック出力信号は、前記出力された第1の補正されたクロック出力信号の位相シフトしたバージョンである、項目2に記載のIC。

(項目4)

前記第1の補正されたクロック出力信号および前記第2の補正されたクロック出力信号は、位相整列から実質的に90度外れている、項目2に記載のIC。

(項目5)

前記第1および第2の補正されたクロック出力信号を受信するように連結される複数のストレージ回路をさらに備え、該複数のストレージ回路は、該第1および第2の補正されたクロック出力信号のエッジを遷移させることによってトリガされる、項目2に記載のIC。

(項目6)

前記補正器回路は、SRラッチを備える、項目1に記載のIC。

(項目7)

前記スプリッタ回路は、

前記第1のクロック信号を受信するように連結されるバスゲートであって、該バスゲートは、前記第2のクロック信号を発生させる、バスゲートと、

該第1のクロック信号を受信するように連結されるインバータであって、該インバータは、前記第3のクロック信号を発生させ、該第3のクロック信号は、該第2のクロック信号の反転したバージョンである、インバータと

を備える、項目1に記載のIC。

(項目8)

前記第1および第2の遅延回路は各々、直列に接続された複数のバッファを含む、項目1に記載のIC。

(項目9)

デューティサイクル補正器回路であって、該回路は、

第1のクロック信号を受信するように連結される第1のパルス発生器回路であって、該第1のパルス発生器回路は、該第1のクロック信号に基づいて第1のパルス信号を発生させる、第1のパルス発生器回路と、

第2のクロック信号を受信するように連結される第2のパルス発生器回路であって、該第2のパルス発生器回路は、該第2のクロック信号に基づいて第2のパルス信号を発生させる、第2のパルス発生器回路と、

該第1および第2のパルス信号を受信するように連結されるラッチであって、該ラッチは、クロック入力信号に対して修正されたデューティサイクルを有するクロック出力信号を発生させる、ラッチと

を備える、回路。

(項目10)

前記クロック入力信号を受信するように連結されるスプリッタ回路であって、該スプリッタ回路は、該クロック入力信号を第3のクロック信号と第4のクロック信号とに分割する、スプリッタ回路と、

該第3および第4のクロック信号の各々を受信するように連結される遅延連鎖回路であって、該遅延連鎖回路は、該第3および第4のクロック信号の各々に対して遅延したバージョンを前記第1および第2のクロック信号としてそれぞれ発生させる、遅延連鎖回路とをさらに備える、項目9に記載のIC。

(項目11)

前記遅延回路は、直列に連結された複数のバッファと、該複数のバッファの各々から出力を受信するように連結されるセレクタ回路とを備える、項目10に記載のIC。

10

20

30

40

50

(項目12)

前記第2のクロック信号は、前記第1のクロック信号の反転したバージョンである、項目9に記載のIC。

(項目13)

前記第1のパルス信号は、前記ラッチをセットし、前記第2のパルス信号は、該ラッチをリセットする、項目9に記載のIC。

(項目14)

前記第1および第2のパルス発生器回路は各々、

前記第1または第2のクロック信号のうちの1つを受信するように連結される設定可能遅延連鎖回路と、

10

該設定可能遅延連鎖の出力に連結されるインバータと、

該インバータの出力、および該第1または第2のクロック信号のうちの1つに連結される論理ゲートと

を備え、それにより、前記第1および第2のパルス発生器の各々は、前記クロック入力信号のパルスよりも小さい幅を有するパルスを発生させる、項目9に記載のIC。

(項目15)

前記設定可能遅延連鎖回路は、前記第1および第2のパルス信号の幅を制御する、項目14に記載のIC。

(項目16)

集積回路(IC)を動作させる方法であって、該方法は、

20

第1のクロック信号を分割することであって、それにより、第2および第3のクロック信号を発生させる、ことと、

該第2および第3のクロック信号に遅延を適用することであって、それにより、該第2および第3のクロック信号の遅延したバージョンを発生させる、ことと、

該第2のクロック信号の該遅延したバージョンに基づいて第1のパルス信号を発生させることであって、該第1のパルス信号は、該第2のクロック信号の遷移に従って第1の論理レベルから第2の論理レベルまで遷移する、ことと、

該第3のクロック信号の該遅延したバージョンに基づいて第2のパルス信号を発生させることであって、該第2のパルス信号は、該第3のクロック信号の遷移に従って該第1の論理レベルから該第2の論理レベルまで遷移する、ことと、

30

該第1のクロック信号に対して修正されたデューティサイクルを有するクロック出力信号を発生させることと

を含む、方法。

(項目17)

前記第1のパルス信号の幅は、前記第2のクロック信号の幅の半分未満である、項目16に記載の方法。

(項目18)

前記クロック出力信号の立ち上がりエッジは、前記第1のパルス信号の立ち上がりエッジと実質的に同時に生じ、該出力クロック信号の立ち下がりエッジは、前記第2のパルス信号の立ち上がりエッジと実質的に同時に生じる、項目16に記載の方法。

40

(項目19)

前記クロック出力信号は、前記第1のクロック信号の位相シフトしたバージョンである、項目16に記載の方法。

(項目20)

前記第3のクロック信号は、前記第2のクロック信号の反転したバージョンである、項目16に記載の方法。

(項目21)

前記第1および第2のパルス信号を発生させることは、前記第2のクロック信号が、前記第1の論理レベルから前記第2の論理レベルまで遷移するときに、ラッチをセットすることと、前記第3のクロック信号が、該第1の論理レベルから該第2の論理レベルまで遷

50

移するときに、該ラッチをリセットすることとを含む、項目 16 に記載の方法。

#### 【0011】

本発明は、添付図面に関連してなされる以下の説明を参照することによって最良に理解することができる。

#### 【図面の簡単な説明】

##### 【0012】

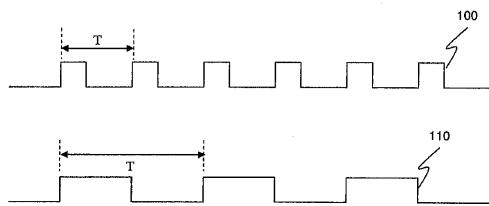

【図1】図1は、イーブンでないデューティサイクルを有するクロック信号の例示的波形と、イーブンなデューティサイクルを有するクロック信号の例示的波形を示す。

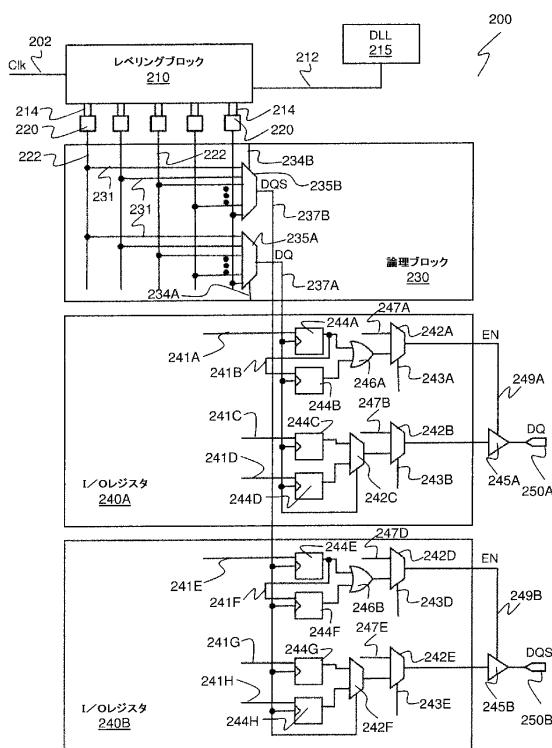

【図2A】図2Aは、限定ではなく、例示として意図されるが、本発明による、一実施形態として、I C内のメモリインターフェースのためのデューティサイクル補正器回路を有する例示的回路を示す。

10

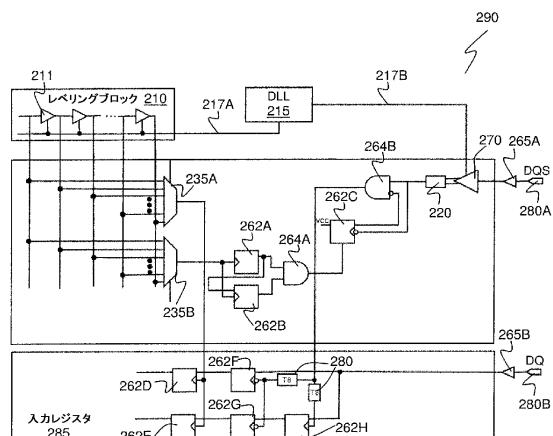

【図2B】図2Bは、限定ではなく、例示として意図されるが、本発明による、一実施形態として、メモリインターフェース読み出しバス回路を示す。

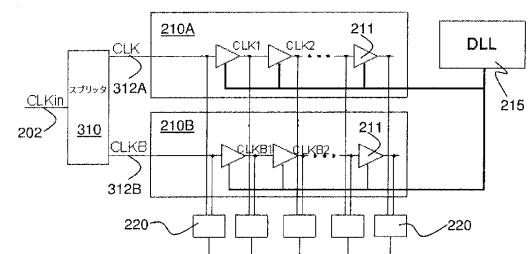

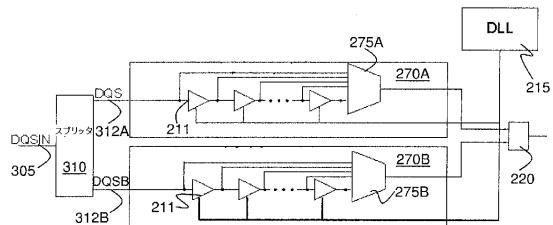

【図3】図3Aは、限定ではなく、例示として意図されるが、本発明による、一実施形態として、レベリングブロックのより詳細な表現を示す。図3Bは、限定ではなく、例示として意図されるが、本発明による、一実施形態として、遅延連鎖のより詳細な表現を示す。

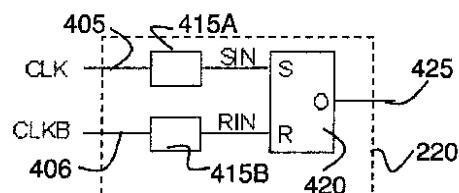

【図4】図4は、限定ではなく、例示として意図されるが、本発明による、一実施形態として、補正器回路のより詳細な表現を示す。

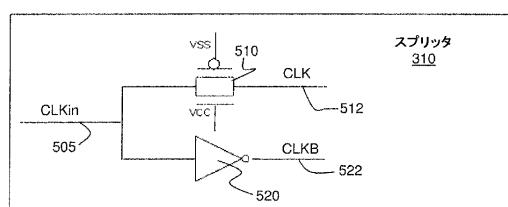

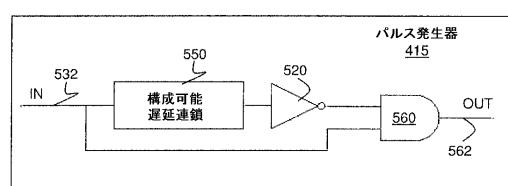

【図5】図5Aは、限定ではなく、例示として意図されるが、本発明による、一実施形態として、スプリッタ回路のより詳細な表現を示す。図5Bは、限定ではなく、例示として意図されるが、パルス発生器回路のより詳細な表現を示す。図5Cは、限定ではなく、例示として意図されるが、本発明における一実施形態として、ラッチの詳細な表現を示す。

20

【図6】図6は、限定ではなく、例示として意図されるが、クロック信号、クロック信号の反転したバージョン、セットパルス信号、リセットパルス信号、およびクロック出力信号間の関係を説明する、例示的波形を示す。

【図7】図7は、限定ではなく、例示として意図されるが、本発明による、別の実施形態として、I Cを動作させるための方法フローを示す簡略化されたフロー図である。

#### 【発明を実施するための形態】

##### 【0013】

本発明の実施形態は、集積回路(I C)内のデューティサイクルの歪みを補正するための回路および方法を含む。

##### 【0014】

しかしながら、本発明が、これらの特定の詳細のうちの一部または全てを伴わずに実施され得ることは、当業者に明らかになるであろう。他の例では、本発明が不必要に不明瞭になることを避けるために、周知のプロセス動作は詳細に説明されていない。

##### 【0015】

本明細書において説明される実施形態は、I C内のデューティサイクルの歪みを補正し、全PVTの範囲にわたって、約50%のデューティサイクルを有するクロック信号を発生させるための回路および技法を提供する。高速用途、例えば、DDR3等の高速メモリインターフェースにおいて、50%または略50%のデューティサイクルは、伝送ウィンドウが、データが適切に捕捉されることを保証するために十分に広いことが確実であるように要求されることを理解されたい。高速用途において、非対称デューティサイクルを有するクロック信号は、データ同期をより困難にし得る。開示される実施形態は、I Cデバイス内のクロック信号におけるデューティサイクルの歪みを容易に補正することができる動的デューティサイクル補正器回路を提供する。一実施形態は、クロック信号を2つの異なるクロック信号に分割し、2つのクロック信号を使用して、対称または実質的に対称である出力クロック信号を発生させる、I C内のデューティサイクル補正器回路を説明する。別の実施形態は、2つの信号パルスおよびラッチを使用して、実質的に対称であるクロ

40

ック信号を発生させるデューティサイクル補正器回路を説明する。

#### 【0016】

図1は、非対称クロック信号の例示的波形100および対称クロック信号の波形110を示す。波形100は、各クロック周期の間、不均一な高周期と低周期とを有する。波形100上に示される間隔Tは、クロック信号のクロック周期である。当業者は、1つのクロック周期が、ある立ち上がり／立ち下がりエッジから次の立ち上がり／立ち下がりエッジまでの周期を指すことを理解する。デューティサイクルパラメータは、各クロック周期の間の論理高出力の相対的持続時間を規定する。図1の波形100に示されるように、各クロック周期Tは、その論理低の持続時間と比較して、比較的に短い論理高の持続時間と有する。前述のように、対称クロック信号は、実質的に、50%のデューティサイクルを有する。言い換えると、各クロック周期Tは、等しいかまたは略等しい論理高と論理低との出力の持続時間と有するべきである。図1の例示的波形110は、対称クロック信号を示す。波形110上の各クロック周期Tは、高出力と低出力との等しい持続時間と有する。したがって、波形110は、50%のデューティサイクルを有する対称クロック信号の波形である。10

#### 【0017】

図2Aは、限定ではなく、例示として意図されるが、本発明による一実施形態として、IC内のメモリインターフェースのためのデューティサイクル補正器回路を有する例示的回路200を示す。当業者は、図2Aの実施形態が、IC内のメモリインターフェースの書き込みパスを示し、出力ピン250Aおよび250Bが、外部メモリモジュールに接続されてもよいことを理解されたい。当業者はまた、出力ピン250Aおよび250Bが、それぞれ、データ(DQ)ピンおよびデータストローブ(DQS)ピンを表し得ることを理解されたい。図2Aの実施形態は、論理ブロック230を通して、I/Oレジスタ240Aおよび240Bに連結されるレベリングブロック210を示す。クロック信号202は、レベリングブロック210に連結される。一実施形態において、レベリングブロック210は、クロック信号202を受信するように連結される遅延連鎖を含む。例示的実施形態において、遅延連鎖は、クロック信号202の複数の遅延したバージョンを発生させる、直列に接続された複数のバッファである。遅延ロックループ(DLL)215の出力212は、レベリングブロック210に連結される。図2Aの実施形態において、DLL215は、レベリングブロック210内の複数のバッファのそれぞれのイネーブル入力に連結されるが、その詳細は、後の段落において説明される。一実施形態において、レベリングブロック210は、電流不足遅延連鎖である。DLL215は、レベリングブロック210に遅延セットを出力および送信し、各レベリング段階の遅延を制御し、遅延セットは、異なるPVT条件にわたって維持される。レベリングブロック210は、出力214として、クロック信号202の複数の遅延したバージョンを発生させる。2030

#### 【0018】

依然として図2Aを参照すると、出力214は、補正器回路220に接続される。一実施形態において、補正器回路220の各々は、セット/リセット(SR)ラッチを含む。補正器回路220のそれぞれの出力は、セレクタ回路235Aおよび235Bに連結される。それぞれ、セレクタ回路235Aおよび235Bの選択入力234Aおよび234Bは、セレクタ回路235Aおよび235Bのための出力として、複数の入力231のいずれが選択されるかを制御する。出力237Aおよび237Bは、それぞれ、I/Oレジスタ240Aおよび240Bに連結される。I/Oレジスタ240Aおよび240Bは、種々の論理要素に接続される複数のストレージ回路またはレジスタを含む。出力237Aおよび237Bは、それぞれ、I/Oレジスタ240Aおよび240B内のレジスタ244A-244Hのクロック端子に接続される。一実施形態において、I/Oレジスタ244A-244Hは、補正器回路220からのクロック出力信号のエッジによってトリガされる。図2Aの実施形態において、出力237Aは、レジスタ244A-244Dのクロック端子に接続され、I/Oレジスタ240A内のセレクタ回路242Cの入力243Cを選択する。レジスタ244Aおよび244Bは、論理ゲート246Aおよびセレクタ回路4050

242Aに連結され、出力バッファ245Aのイネーブル端子249Aを制御する。出力バッファ245Aは、出力ピンDQ250Aに連結される。レジスタ244Cおよび244Dは、セレクタ回路242Cおよび242Bを通して、出力バッファ245Aに連結される。レジスタ244Bの入力端子241Bは、レジスタ244Aの出力に連結される。当業者は、入力端子241A、241C、および241Dが、論理高または論理低レベルのいずれかを提供し得る、ICのコアに接続されてもよいことを理解されたい。当業者はまた、セレクタ回路242Aおよび242Bが、レジスタ244A - 244D、論理ゲート246A、およびセレクタ回路242Cを迂回するために使用されることができることを理解されたい。一実施形態において、選択入力243Aおよび243Bは、静的値または構成ランダムアクセスメモリ(CRAM)ビットに接続され、それぞれ、セレクタ回路242Aおよび242Bの出力を制御する。図2Aの実施形態において、入力端子247Aおよび247Bは、ICのコアに連結される。当業者は、入力端子247Aおよび247Bが、ICのコア内のレジスタに接続されてもよいことを理解されたい。セレクタ回路242Aの出力は、出力バッファ245Aを有効および無効にし、セレクタ回路242Bの出力は、出力バッファ245Aを介してI/Oレジスタ240Aから出力ピンDQ250Aに出力データを搬送する。

#### 【0019】

依然として、図2Aを参照すると、I/Oレジスタ240Bは、I/Oレジスタ240Aと類似性を共有する。簡潔にするために、I/Oレジスタ240A内に図示され、前述された要素、例えば、レジスタ244E - 244F、入力端子241E - 241H、入力端子247Dおよび247E、選択入力243Dおよび243E、セレクタ回路242D - 242Fおよび論理ゲート246Bは、ここでは反復または詳述されない。論理ブロック230のセレクタ回路235Bは、出力信号として、レベリングブロック210から、クロック信号の遅延したバージョンのうちの1つを選択する。一実施形態において、選択入力234Bは、IC内のコア論理ブロックに連結される。コア論理ブロックは、クロック信号202のための好適な位相を決定するために、較正プロセスの間、選択入力234Bを制御し、異なる位相を選択する。別の実施形態において、セレクタ回路235Aの選択入力234Aは、セレクタ回路235Bの選択に従って、出力237Aとして、入力信号231のうちの1つを選択する。例えば、セレクタ回路235Aは、セレクタ回路235Bの出力237Bとして選択される入力信号231の位相シフトしたバージョンを選択してもよい。例示的実施形態において、出力237Aおよび237Bは、実質的に90°位相が外れた状態で整列させられる。出力237Bは、I/Oレジスタ240B内のレジスタ244E - 244Hのクロック端子に連結される。I/Oレジスタ240B内のセレクタ回路242Dおよび242Eの出力は、それぞれ、イネーブル端子249Bおよび出力バッファ245Bに接続される。出力バッファ245Bは、出力ピン250Bに接続される。一実施形態において、出力ピン250Aおよび250Bは、それぞれ、DQおよびDQSピンであって、DQおよびDQSピンは両方とも、外部メモリモジュールに接続される。当業者は、DQおよびDQS信号が、DDRメモリインターフェース内で使用されることを理解されたい。当業者はまた、IC内のメモリインターフェースが、メモリモジュールに書き込むとき、DQSが、DQピンがデータをメモリモジュールに書き込まれたことをアサートすることを理解されたい。

#### 【0020】

図2Bは、限定ではなく、例示として意図されるが、本発明による一実施形態として回路290を示す。簡潔にするために、図2Aに既に図示され、前述された要素、例えば、レベリングブロック210、DLLブロック215、補正器回路220、ならびにセレクタ回路235Aおよび235Bは、ここでは詳述されない。当業者は、回路290は、IC内のメモリインターフェース回路の読み出しバスを表すことを理解されたい。したがって、周知の要素は、本発明を曖昧にしないように、詳述されない。一実施形態において、ピン280Aおよび280Bは、外部メモリモジュールに接続され、ピン280Aおよび280Bは、メモリモジュールからICにデータを読み出す入力ピンである。そのような

10

20

30

40

50

実施形態の1つでは、ピン280Aは、DQSピンであってもよく、ピン280Bは、DQピンであってもよい。ピン280Aは、ピン280Aから伝送された信号を受信する入力バッファ265Aに連結される。入力バッファ265Aからの信号は、遅延連鎖270に伝送される。一実施形態において、遅延連鎖270は、いくつかの直列に接続されたバッファを含み、入力信号の遅延したバージョンまたは位相シフトしたバージョンを生成する。補正器回路220は、位相シフトされたクロック信号内の歪みを補正し、実質的に50%のデューティサイクルを有するクロック信号を生成する。遅延連鎖270からの出力は、補正器回路220に接続される。一実施形態において、遅延連鎖270からの出力は、入力信号の遅延したバージョン、および同じ信号の遅延したバージョンの反転したバージョンを含む。遅延連鎖270および補正器回路220の詳細は、それぞれ、図3Bおよび4に示され、後の段落で説明される。補正器回路220の出力は、論理ゲート264Bの入力端子およびレジスタ262Cのクロック端子のうちの1つに連結される。当業者は、レジスタ262Cのクロック端子が、一実施形態において、アクティブ低端子であることを理解されたい。言い換えると、図2Bの実施形態において、レジスタ262Cは、受信したクロック信号の立ち下がりエッジによってトリガされる。

### 【0021】

図2Bの実施形態において、レジスタ262Cは、論理高信号を出力し、論理ゲート264Bの他の入力端子のうちの1つに接続される。セレクタ回路235Bは、DQSイネーブル信号を選択し、レジスタ262Aおよび262Bを制御する。一実施形態において、DQSイネーブル信号はまた、ポストアンプルクロック信号として知られている。ポストアンプルクロック信号は、DQSイネーブル信号のための正確なタイミングを達成するように較正されているクロック信号であることを理解されたい。セレクタ回路235Bの出力は、セレクタ回路262Aおよび262Bのクロック端子に接続される。セレクタ回路262Aおよび262Bは、論理ゲート264Aに連結され、レジスタ262Cのクリア端子を制御する。レジスタ262Cは、レジスタ262Aおよび262Bが有効になると、クリアされる。一実施形態において、レジスタ262Aおよび262Bは、論理ゲート264Aとともに、回路290が、メモリモジュールから読み出しているとき、回路内のグリッチを防止するために、回路290が、メモリモジュールから読み出しているときだけ、有効にされる。別の実施形態において、セレクタ回路235Bからのポストアンプル信号は、ピン280Aをゲートし、クロック信号内のグリッチまたは擬似エッジを防止する。

### 【0022】

依然として、図2Bを参照すると、ピン280Bは、入力バッファ265Bに接続される。一実施形態において、ピン280Bは、外部メモリモジュールからデータを読み出し、そのデータを入力レジスタ285に伝送するDQピンである。図2Bの実施形態において、入力レジスタ285は、例示されるように、相互に接続されるいくつかのストレージ要素またはレジスタ262D-262Hを含む。ピン280Bで受信したデータまたは信号は、入力バッファ265Bを介してレジスタ262D-262Hに伝送される。レジスタ262F、262G、および262Hは、論理ゲート264Bからの補正されたクロック出力信号によって、制御される。クロック出力信号は、遅延回路280に接続されてもよい。当業者は、遅延回路280が、単純遅延連鎖、例えば、回路内のクロックスキューを補正または低減させるために使用される、直列に連結された2つのインバータであることを理解されたい。したがって、遅延回路280は、スキューが、実質的に低いとき、バイパスされてもよい。回路290は、異なるクロックドメインと協働する外部メモリモジュールに接続されてもよいことを理解されたい。したがって、一実施形態において、レジスタ262Dおよび262Eは、外部メモリモジュールからのクロック信号を、本実施形態において、システム内のクロック信号と再同期させるために使用される。

### 【0023】

図3Aは、限定ではなく、例示として意図されるが、本発明による一実施形態として、レベリングブロック210のより詳細な表現を示す。クロック信号202は、スプリッタ

10

20

30

40

50

回路 310 に接続される。スプリッタ回路 310 は、クロック入力信号 202 を分割し、2つの異なるクロック信号 312A および 312B を発生させる。一実施形態において、クロック信号 312B は、クロック信号 312A の反転したバージョンである。2つのクロック信号、すなわち、312A および 312B は、レベリング遅延ブロック 210A および 210B に連結される。レベリング遅延ブロック 210A および 210B はそれぞれ、直列に接続された複数の遅延バッファ 211 を含む。バッファ 211 はそれぞれ、対応するクロック信号の遅延したバージョン 312A および 312B を発生させる。バッファ 211 のそれからの出力は、補正器回路 220 に接続される。D L L ブロック 215 は、レベリング遅延ブロック 210A および 210B 内のバッファ 211 のそれぞれに接続される。補正器回路 220 はそれぞれ、レベリング遅延ブロック 210A および 210B からの対応する遅延されたクロック信号に基づいて、補正されたデューティサイクルを有するクロック信号を出力する。10 図 2A の実施形態において、補正器回路 220 のそれによって発生させられるクロック信号は、セレクタ回路 235A および 235B に連結される。

#### 【 0024 】

図 3B は、限定ではなく、例示として意図されるが、本発明による一実施形態として、図 2B の遅延連鎖 270 のより詳細な表現を示す。D L L ブロック 215 は、遅延連鎖 270A および 270B のそれぞれに接続される。端子 D Q S I N 305 は、図 2B の入力バッファ 265A に接続される。スプリッタ回路 310 は、端子 D Q S I N 305 で受信したクロック信号をクロック信号 312A および 312B に分割する。図 3B の実施形態において、クロック信号 312B は、クロック信号 312A の反転したバージョンである。20 遅延連鎖 270A および 270B はそれぞれ、直列に接続された複数のバッファ 211 を含む。遅延連鎖 270A および 270B 内のバッファ 211 のそれからの出力は、それぞれ、セレクタ回路 275A および 275B に接続される。遅延連鎖 270A および 270B のそれからの出力は、補正器回路 220 に接続される。図 3B の実施形態において、補正器回路 220 は、遅延連鎖 270A および 270B からのクロック信号に基づいて、補正されたデューティサイクルを有するクロック信号を発生させる。補正されたデューティサイクルを有するクロック信号は、図 2B の実施形態において、論理ゲート 264B および レジスタ 262C に接続される。30 3つだけのバッファ 211 が、図 3A のレベリングブロック 210A および 210B、ならびに図 3B の遅延連鎖 270A および 270B 内に示されているが、当業者は、要求されるバッファの数が、異なる用途に対して、異なる回路にわたって変動し得ることを理解されたい。したがって、より多いまたはより少ないバッファ 211 を、レベリングブロック 210A および 210B ならびに遅延連鎖 270A および 270B 内で使用することができる。

#### 【 0025 】

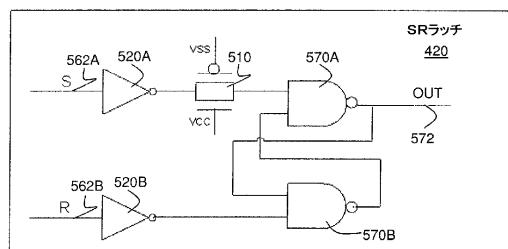

図 4 は、限定ではなく、例示として意図されるが、本発明による一実施形態として、補正器回路 220 のより詳細な表現を示す。補正器回路 220 は、ラッチ 420 に接続される2つのパルス発生器回路 415A および 415B を含む。クロック信号 405A および 405B は、図 3A および 3B の実施形態において、レベリングブロック 210A、210B ならびに遅延連鎖 270A および 270B からの出力信号に類似する。クロック信号 405A および 405B は、それぞれ、パルス発生器回路 415A および 415B に接続される。40 パルス発生器回路 415A および 415B は、それぞれ、クロック信号 405A および 405B に基づいて比較的に小さいパルスを発生させる。パルスがどのように発生させられるかについての詳細は、図 5B および図 6 を参照して論じられる。図 4 の実施形態において、ラッチ 420 は S R ラッチであって、パルス発生器 415A は、ラッチ 420 のセット探知に接続される一方、パルス発生器 415B は、ラッチ 420 のリセット端子に接続される。一実施形態において、パルス発生器 415A および 415B は、それぞれ、非重複セットおよびリセット信号を発生させる。例示的実施形態において、S R ラッチ 420 の出力 425 は、パルス発生器 415A および 415B からのパルスに基づいて発生させられる補正されたデューティサイクルを有するクロック信号である。50

**【0026】**

図5Aは、限定ではなく、例示として意図されるが、本発明による一実施形態として、スプリッタ回路310のより詳細な表現を示す。スプリッタ回路310は、パスゲート510と、インバータ520とを含む。図5Aの実施形態において、パスゲート510は、相補型金属酸化膜半導体(CMOS)パスゲートである。スプリッタ回路310は、クロック信号、CLKin信号505を受信し、信号をCLK512とCLKB522信号とに分割する。CLKin信号505は、パスゲート510およびインバータ520を介して伝送される。インバータ520は、CLKin信号505を反転させて、CLKB信号522を発生させる。図5Aの実施形態において、クロック信号CLKB522は、クロック信号CLK512の反転したバージョンである。クロック信号CLK512およびCLKB522の各々は、それぞれ図3Aおよび3Bの実施形態に示されるように、レベリング遅延ブロックまたは遅延連鎖に接続されてもよい。10

**【0027】**

図5Bは、限定ではなく、例示として意図されるが、パルス発生器回路415のより詳細な表現を示す。入力信号IN532は、パルス発生器回路415内の設定可能遅延連鎖回路550に接続される。図5Bの実施形態において、入力信号IN532は、図5Aに示されるように、クロック信号CLK512またはクロック信号CLKB522のいずれかに接続されてもよい。設定可能遅延連鎖回路550は、パルス発生器回路415によって発生させられるパルスの幅を制御する。設定可能遅延連鎖回路550からの信号は、インバータ520によって反転され、論理ゲート560に接続される。図5Bの実施形態において、論理ゲート560は、設定可能遅延連鎖回路550および入力信号IN532からの反転された信号を受信するANDゲートである。出力信号OUT562は、入力信号IN532の論理状態および設定可能遅延連鎖回路550から反転された信号に基づいて発生させられる。例示的実施形態において、出力信号OUT562は、比較的に小さいパルスを有する信号である。出力信号OUT562は、ラッチに接続されてもよい。図4の例示的実施形態において、パルス発生器415Aおよび415Bからの出力信号は、それぞれ、ラッチ420のセットおよびリセット端子に接続される。20

**【0028】**

図5Cは、限定ではなく、例示として意図されるが、本発明における一実施形態として、ラッチ420の詳細な表現を示す。一実施形態において、ラッチ420は、SRラッチであって、したがって、そのようなラッチの周知の要素は、本発明を必要に曖昧にしないように詳述されないことを理解されたい。ラッチ420は、2つのインバータ520Aおよび520Bと、2つのNANDゲート570Aおよび570Bとを含む。パスゲート510は、インバータ520Aの出力およびNANDゲート570Aの入力に連結される。一実施形態において、パスゲート510は、入力信号S562Aからの出力OUT572および入力信号R562Bからの出力OUT572の信号バスを均等にするために使用される。入力信号S562Aおよび入力信号R562Bは、パルス発生器回路によって発生させられる。図4の例示的実施形態において、入力信号S562Aは、パルス発生器415Aによって発生させられる一方、入力信号R562Bは、パルス発生器415Bによって発生させられる。一実施形態において、ラッチ420の出力OUT572は、入力信号S562Aおよび入力信号R562Bからのパルスに基づいて発生させられる、実質的に50%のデューティサイクルを有するクロック信号である。この実施形態において、ラッチが使用されるが、当業者は、類似の機能を果たす類似の論理またはストレージ要素が、この背景におけるラッチの代わりに使用できることを理解されたい。3040

**【0029】**

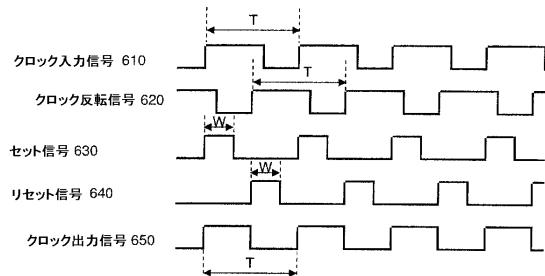

図6は、限定ではなく、例示として意図されるが、本発明の一実施形態によるクロック入力信号、クロック信号の反転したバージョン、セットパルス信号、リセットパルス信号、およびクロック出力信号間の関係を説明する例示的波形610、620、630、640、および650を示す。波形610は、クロック入力信号の例示的波形であって、波形620は、クロック入力信号の反転したバージョンの例示的波形である。一実施形態にお50

いて、クロック入力信号は、遅延を有する位相シフトされたクロック信号であって、クロック入力信号の反転したバージョンは、遅延を有する位相シフトされたクロック信号の反転したバージョンである。一実施形態において、クロック入力信号は、レベリングブロック 210A 内のバッファ 211 のうちの 1 つからのクロック出力信号および図 3A のレベリングブロック 210B 内のバッファ 211 のうちの 1 つからのクロック出力信号の反転したバージョンである。図 6 に示されるように、各クロック周期 T は、等しい周期の論理高と論理低レベルとを有していないので、波形 610 によって表されるクロック入力信号は、50% のデューティサイクルを有していない。図 6 の例示的実施形態において、クロック入力信号は、各クロック周期 T において、実質的に長い論理高周期を有する。したがって、波形 620 によって表されるクロック信号の反転したバージョンもまた 50% のデューティサイクルを有していないことを理解されたい。10

### 【0030】

依然として図 6 を参照すると、波形 630 は、発生させられたセット信号を示す。図 6 の例示的実施形態において、波形 630 によって表されるようなセット信号は、実質的に短いアクティブパルスを有するアクティブ高信号である。当業者は、アクティブ高信号が、論理高レベル、すなわち、論理 1 にあるとき、「アクティブ」と見なされることを理解されたい。この事例では、波形 630 によって表されるセット信号は、波形 630 が論理高状態にあるとき、アクティブである。波形 640 は、比較的に短いパルスを有する発生させられたりセット信号を示す。図 6 の例示的実施形態において、セット信号 630 は、クロック入力信号 610 が論理低レベルから論理高レベルまで遷移するとき、論理低レベルから論理高レベルまで変化する。リセット信号 640 は、クロック入力信号 620 の反転したバージョンが論理低レベルから論理高レベルまで遷移するとき、論理低レベルから論理高レベルまで変化する。例示的実施形態において、それぞれ波形 630 および 640 によって表されるセット信号およびリセット信号内のパルスの幅 W を調節することができる。図 5B の実施形態において、設定可能遅延連鎖回路 550 は、セット 630 およびリセット 640 パルスのそれぞれの幅 W を調節するために使用される。一実施形態において、セット 630 およびリセット 640 パルスのそれぞれの幅 W は、クロック入力信号 610 の 1/2 周期 (1/2T) 未満である。20

### 【0031】

依然として図 6 を参照すると、波形 650 は、実質的に 50% のデューティサイクル、すなわち、等しい周期の高と低論理レベルとを有する発生させられたクロック出力信号を示す。図 6 の実施形態において、クロック出力信号 650 は、セット 630 およびリセット 640 信号に基づいて発生させられる。クロック出力信号 650 は、セット信号 630 が論理低レベルから論理高レベルまで変化するとき、論理低レベルから論理高レベルまで変化する。リセット信号 640 が論理低レベルから論理高レベルまで変化するとき、クロック出力信号 650 は、論理高レベルから論理低レベルまで遷移し、実質的に 50% のデューティサイクルを達成する。図 5C の例示的実施形態において、それぞれ、波形 630 および 640 によって表されるセットおよびリセットパルスは、図 5C のラッチ 420 をセットおよびリセットするために使用される。図 5C における出力 OUT 572 は、波形 650 に示されるクロック出力信号を表す。図 6 の実施形態におけるクロック出力信号の各クロック周期 T は、実質的に、50% のデューティサイクルを有する。例示的実施形態において、クロック出力信号は、45/55 より悪くないデューティサイクルを有する。3040

### 【0032】

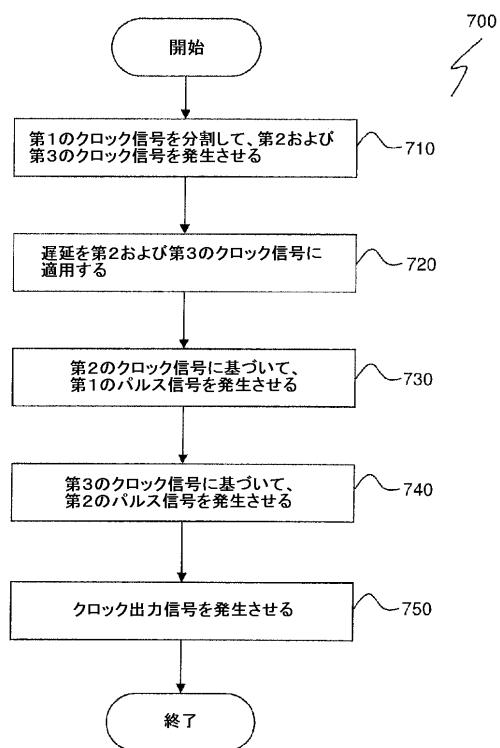

図 7 は、限定ではなく、例示として意図されるが、本発明による、別の実施形態として、I C を動作させるための方法フロー 700 を示す、簡略化されたフロー図である。第 1 のクロック信号は、動作 710 において分割され、第 2 および第 3 のクロック信号を発生させる。図 3A の例示的実施形態において、CLKin 信号 202 は、スプリッタ回路 310 によって、CLK 信号 312A および CLK 信号 312B に分割される。第 3 のクロック信号は、一実施形態において、第 2 のクロック信号の反転したバージョンであってもよい。遅延が、動作 720 において、第 2 および第 3 のクロック信号に適用され、第 250

および第3のクロック信号の遅延したバージョンを発生させる。例示的実施形態において、第2および第3のクロック信号の遅延したバージョンは、第2および第3のクロック信号の位相シフトしたバージョンである。図2Aの例示的実施形態において、クロック信号の遅延したバージョンは、レベリングブロック210によって発生させられる。パルス信号は、動作730において、第2のクロック信号の遅延したバージョンに基づいて発生させられる。一実施形態において、パルス信号は、比較的に小さいパルスの論理高レベルを有し、パルスのそれぞれの幅は、第2のクロック信号の論理高パルスの幅の半分未満である。設定可能遅延連鎖回路、例えば、図5Bの設定可能遅延550は、パルスのそれぞれの幅を調節するために使用されてもよい。別の実施形態において、パルス信号は、図5Cに示されるように、SRラッチ420等のラッチをセットするために使用されるセットパルス信号である。パルス信号は、第2のクロック信号が、論理低レベルから論理高レベルまで遷移するとき、論理低レベルから論理高レベルまで遷移する。図6の例示的実施形態において、波形630は、パルス信号の表現を示す。

#### 【0033】

依然として、図7を参照すると、別のパルス信号が、動作740において発生させられる。このパルス信号は、第3のクロック信号に基づいて発生させられる。例示的実施形態において、動作740において発生させられたパルス信号は、第3のクロック信号が、論理低レベルから論理高レベルまで遷移するとき、論理低レベルから論理高レベルまで遷移するリセットパルス信号である。リセットパルス信号は、図6の例示的実施形態において、波形640によって表される。リセットパルス信号は、図5Cの実施形態において、ラッチ420をリセットするために使用される。クロック出力信号は、動作750において発生させられる。クロック出力信号は、動作730および740において発生させられた2つのパルス信号に基づいて発生させられ、補正されたデューティサイクルを有する。図6の例示的実施形態において、クロック出力信号は、波形650によって表される。一実施形態において、クロック出力信号の立ち上がりエッジは、動作730において発生させられたパルス信号の立ち上がりエッジと実質的に同時に生じる一方、クロック出力信号の立ち下がりエッジは、実質的に、動作740において発生させられたパルス信号の立ち上がりエッジと同時に生じる。別の実施形態において、クロック出力信号は、実質的に対称である、すなわち、略50%のデューティサイクルを有するクロック信号である。

#### 【0034】

実施形態は、これまで、集積回路に関して説明された。本明細書に説明される方法および装置は、任意の好適な回路に組み込まれてもよい。例えば、方法および装置は、マイクロプロセッサまたはプログラム可能論理デバイス等、多数の種類のデバイスに組み込まれてもよい。例示的プログラム可能論理デバイスは、いくつかを挙げると、プログラム可能アレイ論理(PAL)、プログラム可能論理アレイ(PLA)、フィールドプログラム可能論理アレイ(FPLA)、電気的にプログラム可能論理デバイス(EPLD)、電気的に消去可能プログラム可能論理デバイス(EEPROM)、論理細胞アレイ(LCA)、フィールドプログラム可能ゲートアレイ(FPGA)、特定用途用標準品(ASSP)、特定用途向け集積回路(ASIC)を含む。

#### 【0035】

本明細書において説明されるプログラム可能論理デバイスは、以下の構成要素；プロセッサ、メモリ、I/O回路、および周辺デバイスのうちの1つ以上を含むデータ処理システムの一部であってもよい。データ処理システムは、コンピュータネットワーキング、データネットワーキング、計装、ビデオ処理、デジタル信号処理、またはプログラム可能または再プログラム可能な論理を使用する利点が望ましい、あらゆる好適な他のアプリケーション等の種々のアプリケーションで使用することができる。プログラマブル論理デバイスは、種々の異なる論理機能を実施するために使用することができる。例えば、プログラマブル論理デバイスは、プロセッサとして、またはシステムプロセッサと協働するコントローラとして構成することができる。プログラマブル論理デバイスはまた、データ処理システムの中の共有リソースへのアクセスをアービトレートするためのアービタとして使用

10

20

30

40

50

されてもよい。さらに別の実施例では、プログラマブル論理デバイスは、システムの中のプロセッサと他の構成要素のうちの1つとの間のインターフェースとして構成することができる。一実施形態において、プログラム可能論理デバイスは、譲受人によって所有されるデバイスのうちの1つであってもよい。

### 【0036】

方法動作は、具体的な順番において説明されたが、他の動作が、説明された動作の間ににおいて行われてもよく、説明された動作が若干異なる時間において生じるよう調節されてもよく、または説明された動作が、オーバレイ動作の処理が所望の方法で行われる限り、処理と関連付けられた種々の間隔において、処理動作の発生を可能にするシステム内に分散されてもよいことを理解されたい。

10

### 【0037】

上述の本発明は、理解を明確にする目的である程度詳細に記載されているが、添付の特許請求の範囲内において、特定の変更および修正を行うことができる事が明らかになるであろう。故に、本実施形態は、限定的なものではなく例示的なものであるとみなされるべきであり、また本発明は、本明細書に与えられる詳細に限定されるものではなく、添付の特許請求の範囲およびその同等物の範囲内で変更され得るものである。

【図1】

Fig. 1

【図2A】

Fig. 2A

【図2B】

Fig. 2B

【図3】

Fig. 3A

Fig. 3B

【図4】

Fig. 4

【図5】

Fig. 5A

Fig. 5B

Fig. 5C

【図6】

Fig. 6

【図7】

Fig. 7

---

フロントページの続き

(72)発明者 ホアン , ジョセフ

アメリカ合衆国 カリフォルニア 95134 , サンノゼ , イノベーション ドライブ 1

01

(72)発明者 ナガラジヤン , プラディープ

アメリカ合衆国 カリフォルニア 95134 , サンノゼ , イノベーション ドライブ 1

01

(72)発明者 サン , チアカン

アメリカ合衆国 カリフォルニア 95134 , サンノゼ , イノベーション ドライブ 1

01

審査官 宮島 郁美

(56)参考文献 特開平03-258015(JP,A)

特開平11-112485(JP,A)

特開平06-188698(JP,A)

特開昭57-210718(JP,A)

特開2001-326564(JP,A)

特開2007-295562(JP,A)

特開2000-013205(JP,A)

米国特許出願公開第2008/0164920(US,A1)

特開平06-013857(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K5/00-5/26