(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4867028号

(P4867028)

(45) 発行日 平成24年2月1日(2012.2.1)

(24) 登録日 平成23年11月25日(2011.11.25)

|                              |                |

|------------------------------|----------------|

| (51) Int.Cl.                 | F 1            |

| <b>H04N 5/374 (2011.01)</b>  | H04N 5/335 740 |

| <b>H04N 5/378 (2011.01)</b>  | H04N 5/335 780 |

| <b>H01L 27/146 (2006.01)</b> | H01L 27/14 A   |

請求項の数 10 (全 8 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2001-15150 (P2001-15150)    |

| (22) 出願日     | 平成13年1月24日 (2001.1.24)        |

| (65) 公開番号    | 特開2001-245210 (P2001-245210A) |

| (43) 公開日     | 平成13年9月7日 (2001.9.7)          |

| 審査請求日        | 平成20年1月21日 (2008.1.21)        |

| (31) 優先権主張番号 | 490238                        |

| (32) 優先日     | 平成12年1月24日 (2000.1.24)        |

| (33) 優先権主張国  | 米国(US)                        |

## 前置審査

|           |                                                                |

|-----------|----------------------------------------------------------------|

| (73) 特許権者 | 511077731<br>インテレクチュアル ベンチャーズ セカ<br>ンド エルエルシー                  |

|           | アメリカ合衆国 ワシントン州 9800<br>5 ベルビュー ビルディング4 第13<br>9アベニュー エスイー 3150 |

| (74) 代理人  | 100147485<br>弁理士 杉村 慎司                                         |

| (74) 代理人  | 100153017<br>弁理士 大倉 昭人                                         |

| (74) 代理人  | 100158148<br>弁理士 荒木 淳                                          |

| (72) 発明者  | アンドレア・ニーダーコーン<br>アメリカ合衆国アリゾナ州テンペ、サウス<br>・スタンレー・プレース7317        |

最終頁に続く

(54) 【発明の名称】画素読み出しスイッチ・コンデンサ・バッファ回路およびその方法

## (57) 【特許請求の範囲】

## 【請求項1】

画素信号增幅回路(200)であって：

第1および第2入力ならびに第1および第2出力(R, S)を有する増幅器(OP1)；

前記増幅器の第1入力および第1出力間に結合された第1コンデンサ(C2)；

前記増幅器の第2入力および第2出力間に結合された第2コンデンサ(C4)；

画素信号(PIXIN)を受信するように結合された第1端子と、前記増幅器の第1入力に結合された第2端子とを有する第3コンデンサ(C1)；

前記画素信号を受信するように結合された第1端子と、前記増幅器の第2入力に結合された第2端子を有する第4コンデンサ(C3)；および

前記第1コンデンサ(C2)の第1および第2端子のそれぞれに結合された第1導通端子を有する第1および第2トランジスタ(225c, 225d)；

を備え。

前記第1および第2トランジスタ(225c, 225d)がバイアスされると、前記第1コンデンサ(C2)の両端子における電荷が等化されることを特徴とする画素信号增幅回路(200)。

## 【請求項2】

前記画素信号を受信するように結合された第1導通端子と、前記第3コンデンサの第1端子に結合された第2導通端子を有する第1トランジスタ(225a)であって、前記画

素信号のリセット値を導通するために前記第1トランジスタを選択する信号を受信する制御端子とを有する第1トランジスタ(225a)；および

前記画素信号を受信するように結合された第1導通端子と、前記第4コンデンサの第1端子に結合された第2導通端子を有する第2トランジスタ(235a)であって、サンプル画素信号値を導通するために前記第2トランジスタを選択する信号を受信する制御端子とを有する第2トランジスタ(235a)；

を更に備えることを特徴とする請求項1記載の画素信号増幅回路。

#### 【請求項3】

前記第3コンデンサの第2端子に結合された第1導通端子と、前記増幅器の第1入力に結合された第2導通端子と、信号を受信する制御端子とを有する第3トランジスタ(245a)；および

10

前記第4コンデンサの第2端子に結合された第1導通端子と、前記増幅器の第2入力に結合された第2導通端子と、信号を受信する制御端子とを有する第4トランジスタ(245d)；

を更に備えることを特徴とする請求項2記載の画素信号増幅回路。

#### 【請求項4】

画素検出回路(200)であって：

第1および第2入力を有し、該第1および第2入力における信号間の差分値を発生する増幅器(OP1)；

20

前記増幅器の前記第1入力および第1出力間に結合された第1コンデンサ(C2)であって、画素リセット値を格納する第1コンデンサ；

前記増幅器の第2入力および第2出力間に結合され、サンプル画素信号値を格納する、第2コンデンサ(C4)；および

前記第1コンデンサ(C2)の第1および第2端子のそれぞれに結合された第1導通端子を有する第1および第2トランジスタ(225c, 225d)；

を備え、

前記第1および第2トランジスタ(225c, 225d)がバイアスされると、前記第1コンデンサ(C2)の両端子における電荷が等化される

ことを特徴とする画素検出回路(200)。

#### 【請求項5】

30

画素信号(PIXIN)を受信するように結合された第1端子と、前記増幅器の第1入力に結合された第2端子とを有する第3コンデンサ(C1)；および

前記画素信号を受信するように結合された第1端子と、前記増幅器の第2入力に結合された第2端子を有する第4コンデンサ(C3)；

を更に備えることを特徴とする請求項4記載の画素検出回路。

#### 【請求項6】

画素信号を検出する方法であって：

第1および第2コンデンサの端子上の電荷を基準電圧に等しくする段階；

第3コンデンサ上に画素リセット値を格納する段階；

40

第4コンデンサ上にサンプル画素信号値を格納する段階；

前記第3コンデンサ上に格納された画素リセット値を前記第1コンデンサに転送する段階；および

前記第4コンデンサ上に格納されたサンプル画素信号値を前記第2コンデンサに転送する段階；

を備えることを特徴とする方法。

#### 【請求項7】

さらに、前記第1コンデンサ上に格納された画素リセット値と前記第2コンデンサ上に格納されたサンプル画素信号値との間の差を増幅する段階を備えることを特徴とする請求項6記載の方法。

#### 【請求項8】

50

前記第2コンデンサの第1および第2端子のそれぞれに結合された第1導通端子を有する第1および第2トランジスタを更に備えることを特徴とする請求項1記載の画素信号増幅器。

**【請求項9】**

前記第2コンデンサの第1および第2端子のそれぞれに結合された第1導通端子を有する第1および第2トランジスタを更に備えることを特徴とする請求項4記載の画素信号増幅器。

**【請求項10】**

第1および第2トランジスタを第2コンデンサに結合する段階を更に備えることを特徴とする請求項6記載の方法。

10

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

本発明は、一般的に、半導体撮像回路に関し、更に特定すれば、スイッチ・コンデンサを利用して信号対ノイズ比の向上および信号利得の増大を図った画素読み出し回路およびバッファ回路に関するものである。

**【0002】**

**【従来の技術】**

半導体撮像素子の主要な機能は、光子の検出、およびそのエネルギーの測定可能な電圧信号への変換である。典型的に、画素エレメント内においてフォトダイオードから容量性ノードに電荷を移動させることによって発生する電圧を検出する。各画素エレメントをリセットし、画素エレメント・アレイ内にある各ダイオードの基準レベルを決定する。画素リセット動作に続いて、再度画素エレメントを連続的に動作させ、サンプルした画素信号を読み取る。サンプルした画素信号と基準レベルとの差が、アレイ内の各画素エレメントに対して決定される。

20

**【0003】**

アクティブ画素センサ(active pixel sensor)の主な性能パラメータは、荷電粒子分光測定(charged particle spectrometry)の用途または撮像の用途であるかに係らず、信号対ノイズ比である。ノイズは、空間、時間および検出成分に分けられる。空間即ち固定パターン・ノイズ(FPN: Fixed Pattern Noise)は、一般に最も大きなノイズ源であり、本発明における重要な課題である。

30

**【0004】**

**【発明が解決しようとする課題】**

捕獲した電子電荷(electron charge)の電圧への変換(e<sup>-</sup>からV)の間、その結果得られるサンプル信号レベルの強度は非常に小さい。したがって、認知可能なダイナミック・レンジを有する電圧振幅を得るために、得られたサンプル信号レベルの増幅、即ち、利得作用が必要となる。このためには、信号源において最大利得を与えることにより、下流のノイズ注入源(downstream noise injecting source)からのノイズの増幅を回避することが望ましい。

40

**【0005】**

**【発明の実施の形態】**

本発明が提案する方法は、CMOS撮像素子の列アーキテクチャにおけるスイッチ・コンデンサ回路の適用によって、列読み出し回路におけるソース・フォロワ(source follower)の殆どを排除する。スイッチ・コンデンサは、従来技術において用いられているソース・フォロワ・バッファの使用に伴う利得損失を受けることはない。

**【0006】**

コンデンサ比を適正に選択することによって、1よりも大きな利得が得られ、スイッチ・コンデンサ回路を画素信号源に接近して接続することができ、これによって全体の信号対ノイズ比が更に向上する。画素サンプル信号の利得向上は、二次元フォト・アレイ撮像素子には非常に望ましい。この種の素子における画素信号レベルは、局部的な光レベルに左

50

右され、信号の振幅が 100 ミリボルト未満となる場合もあり、信号対ノイズ比の低下を招く。したがって、いずれの下流ノイズ注入源による処理にも先立って、画素信号利得を与えることが非常に望ましい。

#### 【 0 0 0 7 】

加えて、一定のコンデンサ比を維持することは、アレイにおける個々のソース・フォロワに一定の利得を維持するよりも簡単である。ソース・フォロワ内における利得の不整合が大きくなると、列間のノイズ比較において現れ、ノイズの増大に至る。図 2 に示すように、回路にスイッチ・コンデンサを用いることにより、従来技術が示すノイズ性能よりも約 30 パーセント低い、列間ノイズ性能を達成する。

#### 【 0 0 0 8 】

本発明に用いるスイッチ・コンデンサは、アクティブ画素検出エレメントを有するその他の半導体撮像素子にも適用可能である。本発明の構成は、例えば、CMOS リニア・センサ、電荷結合素子 (CCD)、または列毎に読み出し検出を行なうその他の CMOS センサに有効である。かかる画像検出素子は、指紋認証器、カメラ、網膜スキャナ、ならびにディジタルおよびビデオ・カメラに含まれる。

#### 【 0 0 0 9 】

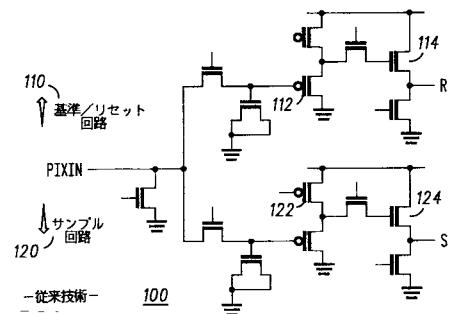

図 1 を参照すると、複数のソース・フォロワ・バッファを有する従来技術の画像センサおよびバッファ回路の簡略構成図が示されている（以下、「従来技術回路 100」と呼ぶ）。従来技術回路 100 は、基準リセット回路部 110 およびサンプル回路部 120 を有する。基準リセット回路部 110 は、2 つの共通モード・ソース・フォロワ・スイッチ、即ち、トランジスタ 112, 114 を有する。また、サンプル回路部 120 も 2 つの共通モード・ソース・フォロワ・スイッチ、即ち、トランジスタ 122, 124 を有する。2 つの回路部 110, 120 は互いに接続され、更に図 3 に示す画素エレメントの出力にも接続することができる。図 3 は、画素入力源の一例を示す。従来技術回路 100 は、相関二重サンプリング (correlated double sampling) を用いた従来技術の CCD 撮像方法の一例である。

#### 【 0 0 1 0 】

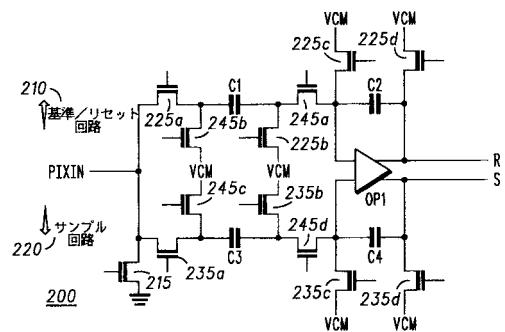

図 2 は、本発明の一実施例による画素検出回路または画素信号增幅回路 200 である。回路 200 は、従来技術回路 100 (図 1) の 2 つの回路部分 110, 120 の代わりに、スイッチ・コンデンサを用いた回路を有する。

#### 【 0 0 1 1 】

回路 200 は、リセット回路 210 およびサンプル信号回路 220 を含む。回路 210, 220 は互いに接続され、更に図 3 に示す画素エレメントの出力にも接続されている。リセット回路 210 は、リセット信号トランジスタ・スイッチ 225a を含む。リセット回路 210 は、信号 PIXIN (図 3) を受信し、トランジスタ 225a を介してこの信号をコンデンサ C1 の端子に転送する。コンデンサ C1 の他方の端子は、トランジスタ・スイッチ 245a を介してコンデンサ C2 の第 1 端子に、更に差動演算增幅器 OP1 の第 1 入力に接続されている。

基準リセット回路 210 は、トランジスタ・スイッチ 225c, 225d を含み、電圧 VCM を受信するようコンデンサ C2 の双方の端子を接続する。トランジスタ・スイッチ 225b, 245b は、コンデンサ C1 の端子を接続し、電圧 VCM を受信する。OP1 の出力 R は、コンデンサ C2 の第 2 端子に共通に接続されている。

#### 【 0 0 1 2 】

サンプル信号回路 220 は、更に、トランジスタ・スイッチ 235a を含み、信号 PIXIN を受信し、この信号をコンデンサ C3 の端子に転送する。コンデンサ C3 の他方の端子は、トランジスタ・スイッチ 245d を介してコンデンサ C4 の第 1 端子に接続され、更に差動演算增幅器 OP1 の第 2 入力にも接続されている。更に、サンプル信号回路 220 は、トランジスタ・スイッチ 235c, 235d を含み、電圧 VCM を受信するようコンデンサ C4 の端子を接続する。トランジスタ・スイッチ 235b, 245c は、コンデンサ C3 の端子を接続し、電圧 VCM を受信する。OP1 の出力 S は、コンデンサ C4

10

20

30

40

50

の第2端子およびトランジスタ・スイッチ235dの端子に共通に接続されている。負荷トランジスタ215が画素に負荷を与える、PIXINソースに接続されている。

#### 【0013】

差動演算増幅器（以下「オペアンプ」と呼ぶ）の使用は有効である。何故なら、完全に差動的なオペアンプは、回路200内で用いる場合、シングル・エンド・ソース・フォロワ回路よりもノイズが少ないからである。つまり、共通モード・ノイズを受けないのである。加えて、以下で更に詳細に説明するが、回路200にOP1を使用することにより、電圧の利得が得られる。

#### 【0014】

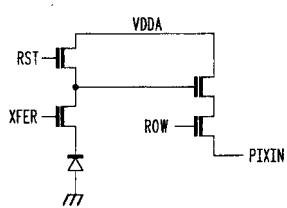

図3は、画素エレメント回路の一例の簡略構成図である。信号RSTはリセット動作を行なわせ、画素エレメント内にあるフォトダイオード間に基準電圧をセットする。信号XFERは、転送動作を行なわせ、光が画素エレメント回路を照明する際、フォトダイオード間に発生する電荷、即ち、サンプル値を転送させる。10

#### 【0015】

動作において、最初に基準リセット動作が選択された画素上で行われる。信号RST（図3）が、信号PIXINに対する電圧値をセットする。基準リセット動作の間、トランジスタ・スイッチ225a, 225bはオンとなっており、信号PIXINは回路200によって処理される。トランジスタ・スイッチ225aは、信号PIXINをコンデンサC1の端子に転送する。トランジスタ・スイッチ225bは、コンデンサC1の他方の端子におけるVCMの電圧値をセットする。したがって、画素エレメントからの信号PIXI20Nのリセット値はコンデンサC1を充電する。導通モードにあるトランジスタ・スイッチ225a, 225bに伴い、トランジスタ・スイッチ225c, 225dはバイアスされ、コンデンサC2の両端子を接続して電圧VCMを受信し、コンデンサC3の端子における電荷を等化する。

#### 【0016】

次いで、選択した画素エレメント（図3）から信号RSTを除去し、信号XFERをアサートする。画素エレメントを照明する光の強度に応答してフォトダイオードによって発生した電圧、即ち、サンプル画素信号値が、画素エレメントの出力における信号PIXINに転送される。トランジスタ・スイッチ235a, 235bは、回路220（図2）内においてオンとなる。トランジスタ・スイッチ235aは、信号PIXINをコンデンサC3の端子に転送する。トランジスタ・スイッチ235bは、コンデンサC3の他方の端子におけるVCMの電圧値を設定する。トランジスタ・スイッチ235a, 235bが導通モードにある場合、トランジスタ・スイッチ235c, 235dもバイアスされ、コンデンサC4の両端子を接続して、電圧VCMを受信し、コンデンサC4の端子における電荷を等化する。30

#### 【0017】

回路200が画素エレメントからリセット値を受信してコンデンサC1上に蓄積した後、電荷は更にトランジスタ・スイッチ245aを介して転送され、コンデンサC2上に蓄積される。電荷転送は、トランジスタ・スイッチ245a, 245bをオンにすることによって開始される。コンデンサ間の電圧は瞬時に変化することができないので、トランジスタ・スイッチ245bによってコンデンサC1の端子に供給される電圧VCMは、コンデンサC1上に格納されているリセット値も、コンデンサC2上に格納されている電圧にする。40

#### 【0018】

加えて、画素エレメント内のフォトダイオードを照明した光の強度に応答してコンデンサC3上に蓄積された電荷は、トランジスタ・スイッチ245dを介してコンデンサC4に転送される。コンデンサC3からコンデンサC4への電荷転送は、トランジスタ・スイッチ245c, 245dを導通モードに切り替えることによって開始される。

#### 【0019】

ここで、画素エレメント・リセット値は、コンデンサC2上に格納され、画素エレメント50

のダイオードを照明した光によって発生した電圧は、コンデンサC4上に格納される。コンデンサC2,C4上に蓄積された電荷間の電圧差は、差動オペアンプOP1によって増幅され、増幅出力信号R,SがOP1の出力に現れる。信号R,Sは、次段(図示せず)において得られ、必要に応じて更に処理される。オペアンプOP1は、スイッチ・コンデンサと共に動作し、電圧利得を与える。

【0020】

以上の説明から、本発明はリセット値および光が画素エレメントを照明した結果生ずるサンプル信号レベル間の電圧を増幅することが認められよう。演算増幅器による電圧差の検出により、認知可能なダイナミック・レンジを有する電圧振幅が得られる。

【図面の簡単な説明】

10

【図1】従来技術の撮像センサおよびバッファの簡略構成図。

【図2】本発明の一実施例による画素信号増幅回路。

【図3】画素エレメント回路の一例の簡略構成図。

【符号の説明】

|                                          |                   |    |

|------------------------------------------|-------------------|----|

| 100                                      | 従来技術回路            |    |

| 110                                      | 基準リセット回路部         |    |

| 112, 114, 122, 124                       | トランジスタ            |    |

| 120                                      | サンプル回路部           |    |

| 200                                      | 画素検出回路 / 画素信号増幅回路 |    |

| 210                                      | リセット回路            | 20 |

| 220                                      | サンプル信号回路          |    |

| 225a                                     | リセット信号トランジスタ・スイッチ |    |

| 225c, 225d, 235a, 235c, 235d, 245a, 245d | トランジスタ・スイッチ       |    |

| C1, C2, C3, C4                           | コンデンサ             |    |

| OP1                                      | 差動演算増幅器           |    |

【図1】

【図2】

【図3】

---

フロントページの続き

(72)発明者 スハイル・アグワニ

アメリカ合衆国アリゾナ州チャンドラー、イースト・サン・タン・ストリート2880

(72)発明者 デビット・ロカスチオ

アメリカ合衆国アリゾナ州チャンドラー、ウェスト・ゲリー・ドライブ2590

審査官 若林 治男

(56)参考文献 特表2002-507863(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/374

H01L 27/146

H04N 5/378