(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6266892号

(P6266892)

(45) 発行日 平成30年1月24日(2018.1.24)

(24) 登録日 平成30年1月5日(2018.1.5)

(51) Int.Cl.

F 1

|      |       |           |      |       |      |

|------|-------|-----------|------|-------|------|

| G06F | 3/041 | (2006.01) | G06F | 3/041 | 512  |

| G06F | 3/044 | (2006.01) | G06F | 3/044 | 120  |

| G09G | 3/20  | (2006.01) | G09G | 3/20  | 611A |

| G09G | 3/36  | (2006.01) | G09G | 3/20  | 621A |

| G09F | 9/00  | (2006.01) | G09G | 3/20  | 631B |

請求項の数 16 (全 25 頁) 最終頁に続く

(21) 出願番号

特願2013-75835(P2013-75835)

(22) 出願日

平成25年4月1日(2013.4.1)

(65) 公開番号

特開2014-203102(P2014-203102A)

(43) 公開日

平成26年10月27日(2014.10.27)

審査請求日

平成28年3月2日(2016.3.2)

(73) 特許権者 308017571

シナプティクス・ジャパン合同会社

東京都中野区中野四丁目10番2号

(74) 代理人 100205350

弁理士 狩野 芳正

(74) 代理人 100102864

弁理士 工藤 実

(74) 代理人 100117617

弁理士 中尾 圭策

(72) 発明者 棟近 功

東京都小平市上水本町五丁目20番1号

株式会社ルネサスエスピードライバ内

審査官 原 秀人

最終頁に続く

(54) 【発明の名称】 ドライバIC及び表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

表示パネルの駆動制御とタッチパネルの検出タイミング制御を行うドライバICであつて、

表示駆動期間に前記表示パネルを駆動する駆動回路と、

前記駆動回路の動作を停止する非表示駆動期間に前記タッチパネルの検出タイミングを生成すると共に前記表示駆動期間と前記非表示駆動期間とを生成する制御回路と、

表示データを1表示フレームに満たない複数表示ライン分保持するデータRAMと、を有し、

前記制御回路は、1表示フレームの期間に、外部から供給される表示データを前記データRAMに書込むと共に書込まれた表示データを書き込みよりも速い速度で前記データRAMから読み出して駆動回路に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返すことにより、前記表示駆動期間と前記非表示駆動期間とを交互に生成する制御を行い、 10

前記制御回路は前記ラップアラウンドに繰返すメモリアドレッシング操作のアドレッシング範囲を前記データRAMの最大記憶容量以下の表示ライン数相当のライン数の範囲で制御するタッチインターバル期間データを書き換え可能に保持するためのレジスタ回路を有し、

前記タッチインターバル期間データは、前後の前記非表示駆動期間の間に前記表示ライン数相当のライン数の範囲で可変期間を形成するために計数される表示ライン数を制御す 20

る制御データである、ドライバＩＣ。

【請求項 2】

請求項 1において、前記制御回路は、前記データRAMの最大記憶容量以下の表示ライン数分のデータサイズを1ページとし、外部からの第1フレーム同期信号の周期単位でページ単位のページ書込みアドレスを生成すると共にページ単位でページ内のライン書込みアドレスを生成する書込みアドレスカウンタ回路と、表示動作のための第2フレーム同期信号の周期単位で前記ページ単位のページ読出しアドレスを生成すると共にページ単位でページ内のライン読出しアドレスを生成する読出しアドレスカウンタ回路とを有し、ページ読出しアドレス毎に前記表示駆動期間と前記非表示駆動期間とを交互に生成し、表示駆動期間においてライン読出しアドレスを生成し、非表示駆動期間においてライン読出しアドレスの生成を停止する、ドライバＩＣ。10

【請求項 3】

請求項 2において、前記制御回路は、前記ページ書込みアドレス毎に前記データRAMに表示データの書込みを開始するタイミングから所定時間遅延したタイミングで前記データRAMから表示データの読出しを開始し、開始した読出しの終了は当該ページ書込みアドレス単位での書込みの終了後とする、ドライバＩＣ。

【請求項 4】

請求項 3において、前記レジスタ回路は更に、ページ内の先頭の書込みアドレスへの書き込み開始からタッチ検出開始までの表示ライン数を制御するためのタッチ検出開始ライン数データ、及びタッチ検出開始ライン数データで決定される表示ライン数の位置からタッチ検出を行って表示リードを開始するまでの表示ライン数を制御するための表示リード開始ライン数データを書き換え可能に保持し、20

前記所定時間は、前記タッチ検出開始ライン数データと表示リード開始ライン数データとの和で決まる期間である、ドライバＩＣ。

【請求項 5】

請求項 4において、前記制御回路は、表示フレーム単位で、先頭ページの先頭の書込みアドレスへの書き込み開始から表示ライン周期毎に表示ラインのカウントを行うラインカウンタを有し、前記ラインカウンタのカウント値に基づいて前記タッチ検出開始ライン数データによるライン数と前記表示リード開始ライン数データによるライン数とを判別する、30 ドライバＩＣ。

【請求項 6】

請求項 3において、前記データRAMに対する読み出し要求のデータアクセス単位は書き込み要求のデータアクセス単位に比べて大きくされ、

前記制御回路は書き込み要求と読み出し要求が競合したとき書き込み要求を優先させる調停回路を有する、ドライバＩＣ。

【請求項 7】

請求項 6において、前記読み出し要求のアクセス単位は1表示ライン分の並列データ数を単位とし、前記書き込み要求のアクセス単位はバスアクセスの並列データ数を単位とする、ドライバＩＣ。40

【請求項 8】

請求項 1において、前記データRAMは複数のメモリバンクを有し、前記制御回路は、相互にいずれか一方のメモリバンクに対する書き込み中に他方のメモリバンクに対する読み出しを行い、書き込み対象とするメモリバンクと読み出し対象とするメモリバンクを交互に切替える、ドライバＩＣ。

【請求項 9】

請求項 8において、前記制御回路は、表示フレーム単位で最初の非表示駆動期間に何れか一方のメモリバンクを書き込み対象メモリバンクとし、最初の表示駆動期間に他方のメモリバンクを読み出し対象メモリバンクとし、夫々のページ切替え毎に、書き込み対象メモリバンクと読み出し対象メモリバンクの切替えを行う、ドライバＩＣ。

【請求項 10】

50

請求項 2において、前記レジスタ回路は更に、駆動する表示ラインの切替え周期である表示パネルの表示ライン周期を制御するための表示ライン周期データ、及び駆動する表示パネルの表示ライン数を制御するための表示ライン数データを書き換え可能に保持する、ドライバＩＣ。

**【請求項 1 1】**

請求項 1 0において、前記制御回路は、前記データRAMの最大記憶容量以下の表示ライン数分のデータサイズを1ページとし、外部からの第1フレーム同期信号の周期単位でページ単位のページ書き込みアドレスを生成すると共にページ単位でページ内のライン書き込みアドレスを生成する書き込みアドレスカウンタ回路と、表示動作のための第2フレーム同期信号の周期単位で前記ページ単位のページ読み出しアドレスを生成すると共にページ単位でページ内のライン読み出しアドレスを生成する読み出しアドレスカウンタ回路とを有し、ページ読み出しアドレス毎に前記表示駆動期間と前記非表示駆動期間とを交互に生成し、表示駆動期間においてライン読み出しアドレスを生成し、非表示駆動期間においてライン読み出しアドレスの生成を停止し、10

前記レジスタ回路は更に、ページ内の先頭の書き込みアドレスへの書き込み開始からタッチ検出開始までの表示ライン数を制御するためのタッチ検出開始ライン数データ、及びタッチ検出開始ライン数データで決定される表示ライン数の位置からタッチ検出を行って表示リードを開始するまでの表示ライン数を制御するための表示リード開始ライン数データを書き換え可能に保持するドライバＩＣ。

**【請求項 1 2】**

請求項 1 0において、前記データRAMは複数のメモリバンクを有し、20

前記制御回路は、相互にいずれか一方のメモリバンクに対する書き込み中に他方のメモリバンクに対する読み出しを行い、書き込み対象とするメモリバンクと読み出し対象とするメモリバンクを交互に切替え、

前記レジスタ回路は更に、ページ内の先頭の書き込みアドレスへの書き込み開始からのオフセットを表示ライン数で制御するためのオフセットライン数データ、及びオフセットライン数データで決定される表示ライン数の位置から前記タッチインターバル期間データで指定される表示ライン数に達した表示ラインからタッチ検出を行って次の表示リードを開始するまでの表示ライン数を制御するための表示リード開始ライン数データを書き換え可能に保持する、ドライバＩＣ。30

**【請求項 1 3】**

請求項 1 1 又は 1 2において、前記制御回路は、表示フレーム単位で、先頭ページの先頭の書き込みアドレスへの書き込み開始から表示ライン周期毎に表示ラインのカウントを行うラインカウンタを有し、前記ラインカウンタのカウント値に基づいて前記タッチインターバル期間データによるタッチインターバル期間のライン数、前記タッチ検出開始ライン数データによるライン数、及び前記表示リード開始ライン数データによるライン数、を判別する、ドライバＩＣ。

**【請求項 1 4】**

表示パネルにタッチパネルが組み込まれたパネルモジュールと、40

前記パネルモジュールに搭載され、前記表示パネルの駆動制御と前記タッチパネルの検出制御を行うドライバＩＣとを有する表示装置であって、

前記ドライバＩＣは、表示駆動期間に前記表示パネルを駆動する駆動回路と、

前記駆動回路の動作を停止する非表示駆動期間に前記タッチパネルの検出制御を行なうタッチパネルコントローラと、

表示データを1表示フレームに満たない複数表示ライン分保持するデータRAMと、

1表示フレームの期間に、外部から供給される表示データを前記データRAMに書き込むと共に書き込まれた表示データを書き込みよりも速い速度で前記データRAMから読み出して駆動回路に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返すことにより、前記表示駆動期間と前記非表示駆動期間とを交互に生成する制御を行う制御回路を有し、50

前記制御回路は、前記データRAMの最大記憶容量以下の表示ライン数相当のライン数の範囲で前記表示駆動期間及び前記非表示駆動期間が指定される制御回路とを有し、

タッチインターバル期間データは、前後の前記非表示駆動期間の間に前記表示ライン数相当のライン数の範囲で可変期間を形成するために計数される表示ライン数を制御する制御データである、表示装置。

#### 【請求項 15】

請求項14において、前記制御回路は、前記データRAMの最大記憶容量以下の表示ライン数分のデータサイズを1ページとし、外部からの第1フレーム同期信号の周期単位でページ単位のページ書込みアドレスを生成すると共にページ単位でページ内のライン書込みアドレスを生成する書込みアドレスカウンタ回路と、表示動作のための第2フレーム同期信号の周期単位で前記ページ単位のページ読み出しアドレスを生成すると共にページ単位でページ内のライン読み出しアドレスを生成する読み出しアドレスカウンタ回路とを有し、ページ読み出しアドレス毎に前記表示駆動期間と前記非表示駆動期間とを交互に生成し、表示駆動期間においてライン読み出しアドレスを生成し、非表示駆動期間においてライン読み出しアドレスの生成を停止する、表示装置。

10

#### 【請求項 16】

請求項14において、前記データRAMは複数のメモリバンクを有し、前記制御回路は、相互にいずれか一方のメモリバンクに対する書込み中に他方のメモリバンクに対する読み出しを行い、書込み対象とするメモリバンクと読み出し対象とするメモリバンクを交互に切替える、表示装置。

20

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、表示駆動期間と非表示駆動期間を交互に生成して表示パネルを駆動するドライバIC関し、例えば表示パネルにタッチパネルを組み込んだパネルモジュールの駆動制御に適用して有効な技術に関する。

#### 【背景技術】

#### 【0002】

表示パネルを駆動するドライバICは1フレーム分の画像データを一時的に保持することが可能な表示のデータRAMを搭載するものがある。静止画を表示する場合には既にデータRAMに蓄積した1フレーム分の画像データを読み出しながら表示することにより、ホストプロセッサによる画像データの逐次的な送信を停止することができ、表示パネルの低消費電力化並びに画像データの送信に要するホストプロセッサの負荷低減を実現することができる。

30

#### 【0003】

そのような考慮を全く必要としなければ、ドライバICに占める面積の大きなデータRAMを持たなくとも済む。

#### 【0004】

また、データRAMのチップ占有面積を減らしながら少しでもホストプロセッサの負担を低減しようとする場合には1フレームに満たない数表示ライン分の記憶容量しか持たない表示用のデータRAM(パーシャルRAM)を搭載し、更新頻度の高い表示領域の画像データについては常にホストプロセッサに表示データを送信させるが、更新頻度の低い表示領域の画像データはパーシャルRAMのデータを読み出しながら表示させることができ。これにより、携帯電話等における受信状況、ステータス欄など表示の更新頻度が低い部分の表示に対してホストプロセッサのデータ送信量を低減することができる。

40

#### 【0005】

このとき、表示パネルにタッチパネルを組み込んだパネルモジュールが多用されている現状に鑑みれば、表示駆動時に発生する動作ノイズがタッチ検出精度を低下させるため、タッチ検出は表示駆動を停止している期間に行うのが好ましい。

50

**【0006】**

例えばこの観点に立った特許文献1においては、1フレーム分のデータRAMを持ち、画像表示を数ライン毎のブロック単位で断続的に行い、駆動回路からの表示駆動出力が停止している期間にタッチセンスを行うことで高いタッチ検出精度を実現する。このように、表示パネルを複数のブロック単位で時分割して駆動するために、1フレーム分のデータRAMにブロック単位で画像データを格納する。

**【先行技術文献】****【特許文献】****【0007】**

【特許文献1】特開2012-59265号公報

10

**【発明の概要】****【発明が解決しようとする課題】****【0008】**

本発明者は、パーシャルRAMのようなデータRAMを備えたドライバICにおいて、表示駆動期間に対する非表示駆動期間にタッチ検出を行ってタッチ検出精度を向上させることについて検討した。

**【0009】**

これによれば、特許文献1では表示パネルを複数のブロック単位で時分割駆動するためにはメモリにブロック単位で画像データを格納するとあるが、メモリは1フレーム分のメモリと考えられている。パーシャルメモリを用いる場合にはブロック単位でメモリアドレスをラップアラウンドに生成する制御などが必須でありこれについて全く考慮されていない。したがって、特許文1では1フレーム分のデータRAMを用いて表示駆動と非表示駆動を行う域を脱しておらず、1フレーム分のデータRAMを搭載する必要からドライバICの回路規模若しくはチップサイズを低減することができない。

20

**【0010】**

一方、表示用のデータRAMを持たない場合には、ドライバICは、ホストプロセッサプロセッサに表示データを断続的に送信させて、表示駆動を行わない期間を生成し、この非表示駆動期間にタッチセンスを行う。例えば、表示ライン周期毎にホストプロセッサからワード単位などで送信されてラインラッチにラッチされた表示データは直ちに次の表示ライン周期で駆動回路による駆動に用いられることになる。このように、非表示駆動期間を生成するには、ホストプロセッサに表示データを断続的に送信させる必要があり、そのようなタイミング制御の点で更にホストプロセッサへの負担が大きくなるので、そのような負担増を許容できない場合にはデータRAMを持つことを考えなくてはならなくなる。結果として、チップサイズの小型化とホストプロセッサに対する負担軽減の双方を満足することはできない。

30

**【0011】**

本発明の目的は、チップサイズの小型化とホストプロセッサに対する負担軽減との双方を満足させながら、タッチ検出精度を向上させることにある。

**【0012】**

上記並びにその他の課題と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

40

**【課題を解決するための手段】****【0013】**

本願において開示される実施の形態のうち代表的なものの概要を簡単に説明すれば下記の通りである。

**【0014】**

すなわち、駆動回路の動作を停止する非表示駆動期間にタッチパネルによる検出タイミングを生成すると共に、前記駆動回路で前記表示パネルを駆動する表示駆動期間と前記非表示駆動期間とを生成する制御を行う制御回路と、表示データを1表示フレームに満たない複数表示ライン分保持するデータRAMとを有する。前記制御回路は、1表示フレーム

50

の期間に、外部から供給される表示データを前記データRAMに書込むと共に書込まれた表示データを書き込みよりも速い速度で前記データRAMから読み出して駆動回路に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返すことにより、前記表示駆動期間と前記非表示駆動期間とを交互に生成する制御を行う。

#### 【0015】

これによれば、1フレーム分のデータRAMを搭載することを要しないからチップサイズが小さくなる。1表示フレームに満たない複数表示ライン分保持するデータRAMを搭載する表示駆動期間と非表示駆動期間においてホストプロセッサとの間で表示データの転送と転送停止との同期制御を行うことを要せず、ホストプロセッサの負担を軽減することができる。1表示フレームの期間に、データRAMへの表示データの書き込みと書き込まれた表示データを読み出して駆動回路に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返すから、1表示フレームに満たないデータRAMを用いる場合でも表示駆動期間と非表示駆動期間とを交互に生成することができる。10

#### 【発明の効果】

#### 【0016】

本願において開示される実施の形態のうち代表的なものによって得られる効果を簡単に説明すれば下記のとおりである。

#### 【0017】

すなわち、チップサイズの小型化とホストプロセッサに対する負担軽減との双方を満足させながら、タッチ検出精度を向上させることができる。20

#### 【図面の簡単な説明】

#### 【0018】

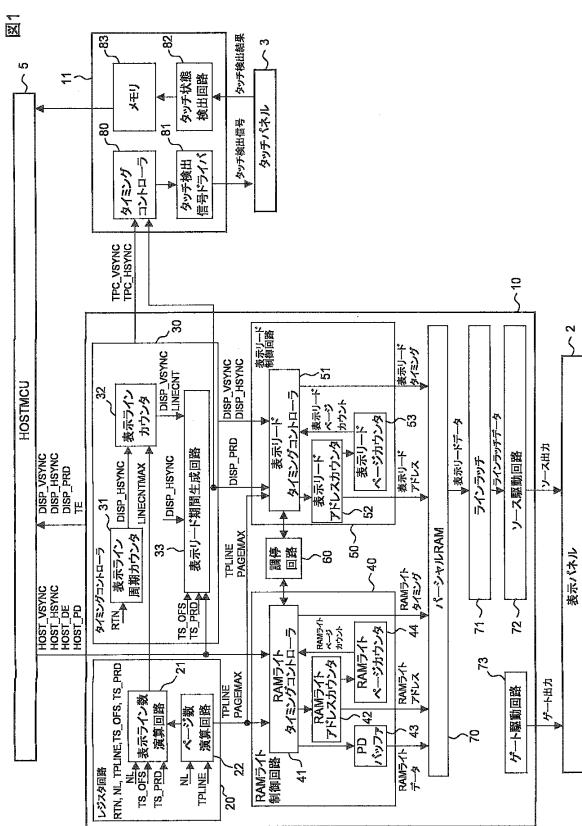

【図1】図1は表示ドライバの構成を例示するブロック図である。

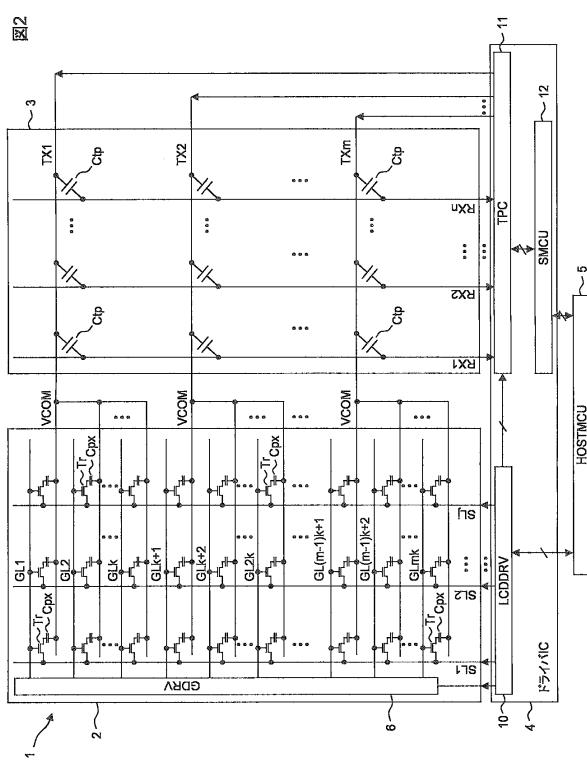

【図2】図2はパネルモジュールとこれを駆動するドライバICを備えた表示装置を例示するブロック図である。

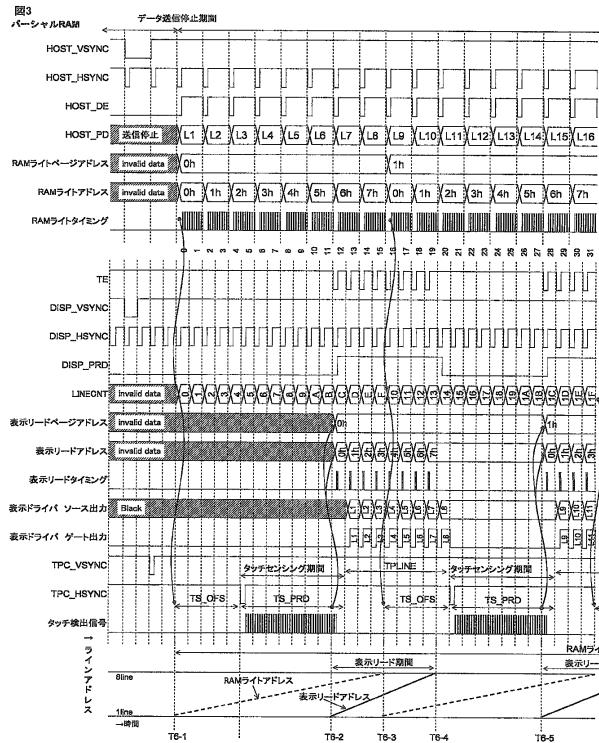

【図3】図3は図1の表示ドライバによる動作制御タイミングの前半を例示するタイミングチャートである。

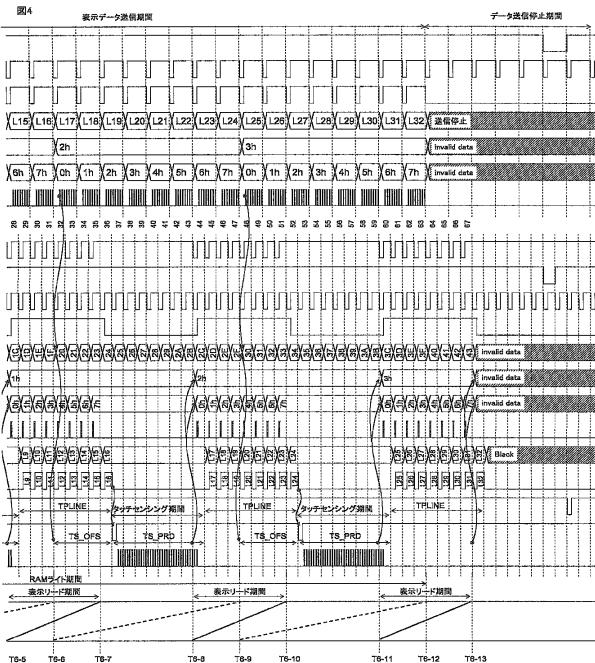

【図4】図4は図1の表示ドライバによる動作制御タイミングの後半を例示するタイミングチャートである。

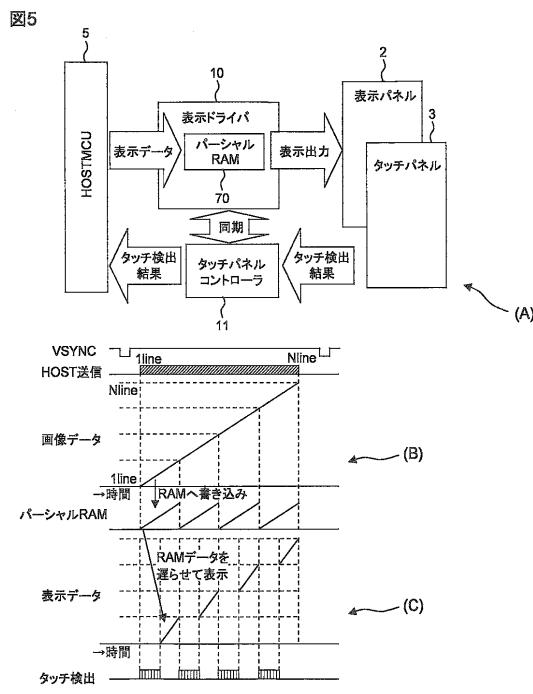

【図5】図5の(A)乃至(C)は図1の表示ドライバの構成及び機能を凝縮して示した説明図である。30

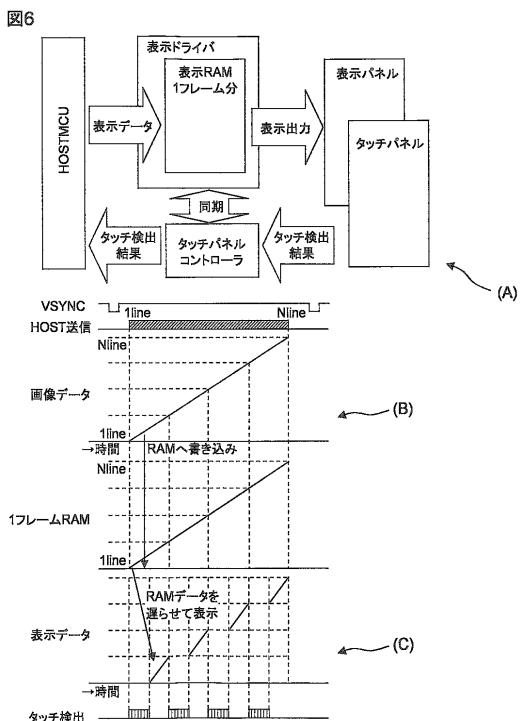

【図6】図6の(A)乃至(C)は1フレーム分のRAMを用いて表示駆動期間と前記非表示駆動期間とを交互に生成する駆動形態を概略的に示した説明図である。

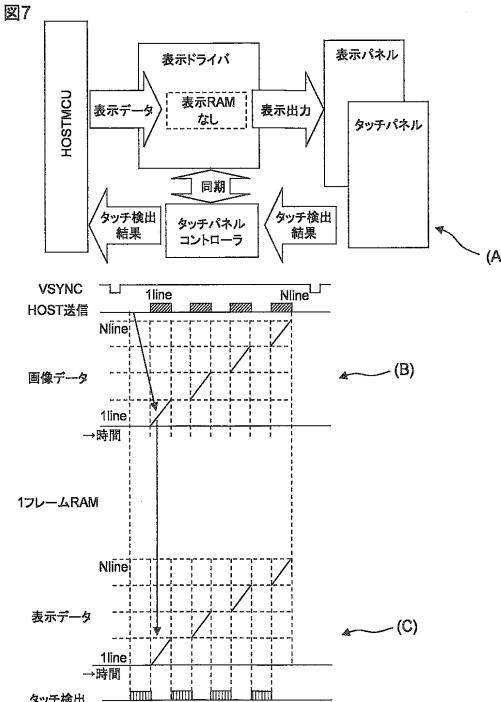

【図7】図7の(A)乃至(C)はRAMを搭載しない代わりにホストプロセッサ5との間で表示データの転送と転送停止との同期制御を行うことによって表示駆動期間と前記非表示駆動期間とを交互に生成する駆動形態を概略的に示した説明図である。

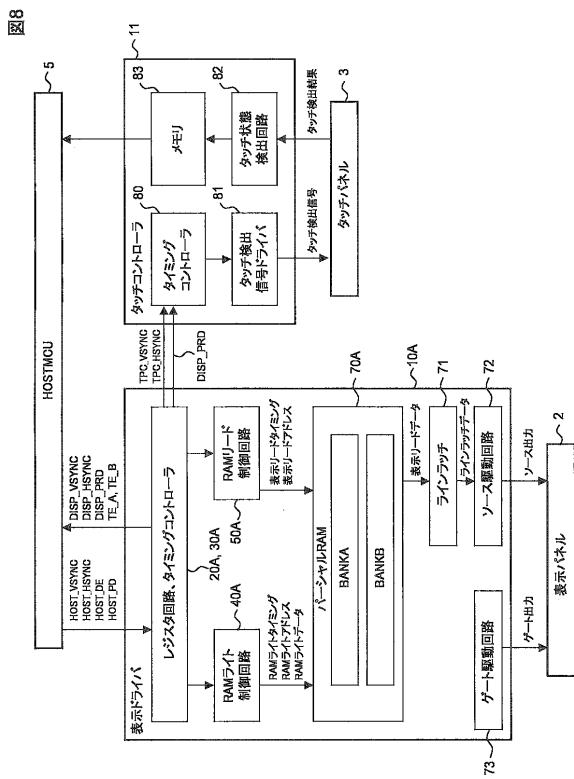

【図8】図8は表示ドライバの別の例を示すブロック図である。

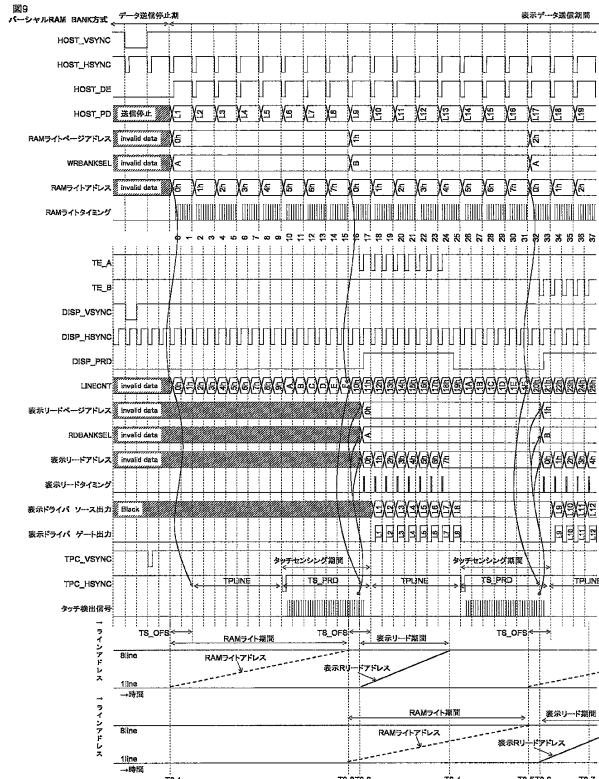

【図9】図9は図8の表示ドライバによる動作制御タイミングの前半を示すタイミングチャートである。

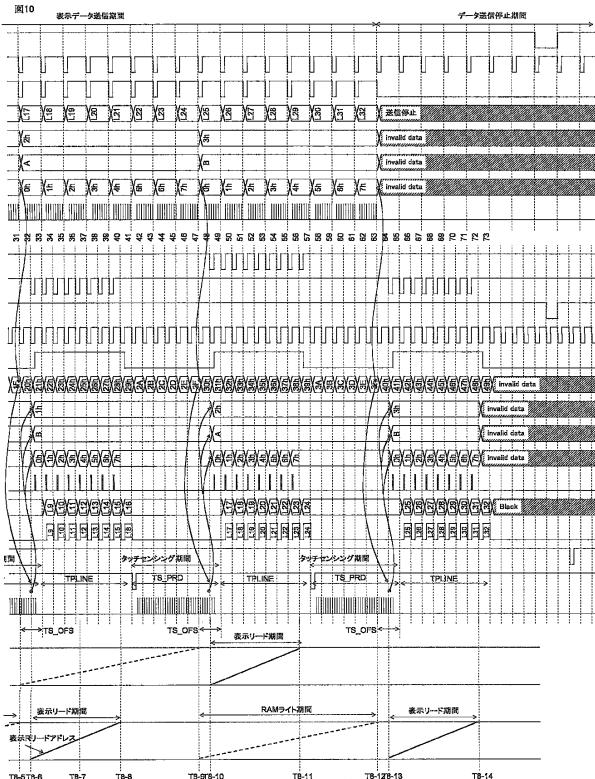

【図10】図10は図8の表示ドライバによる動作制御タイミングの後半を示すタイミングチャートである。40

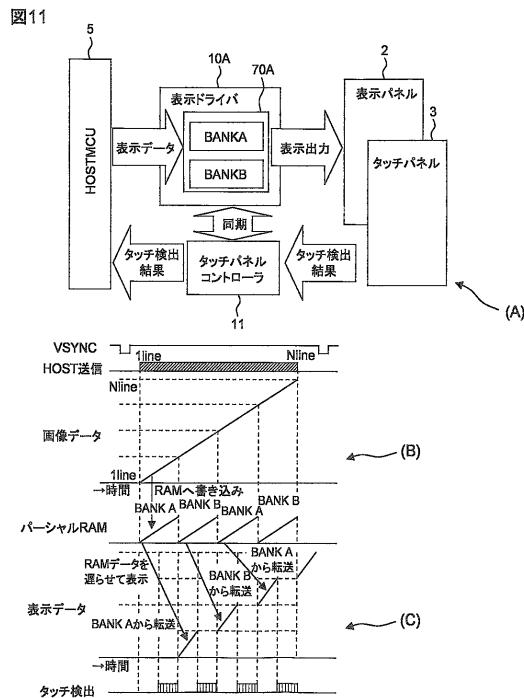

【図11】図11の(A)乃至(C)は図8の表示ドライバの構成及び機能を凝縮して示した説明図である。

#### 【発明を実施するための形態】

#### 【0019】

#### 1. 実施の形態の概要

先ず、本願において開示される実施の形態について概要を説明する。実施の形態についての概要説明で括弧を付して参照する図面中の参照符号はそれが付された構成要素の概念に含まれるものを見示すに過ぎない。

#### 【0020】

[ 1 ] < 表示データを書き込みよりも速く読み出して表示駆動期間と非表示駆動期間を交互に生成 >

表示パネル(2)の駆動制御とタッチパネル(3)の検出タイミング制御を行うドライバI C(4)は、表示駆動期間に前記表示パネルを駆動する駆動回路(72)と、前記駆動回路の動作を停止する非表示駆動期間に前記タッチパネルの検出タイミングを生成すると共に前記表示駆動期間と前記非表示駆動期間とを生成する制御回路(20～60、20A～50A)と、表示データを1表示フレームに満たない複数表示ライン分保持するデータRAM(70, 70A)と、を有する。前記制御回路は、1表示フレームの期間に、外部から供給される表示データを前記データRAMに書き込むと共に書き込まれた表示データを書き込みよりも速い速度で前記データRAMから読み出して駆動回路に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返すことにより、前記表示駆動期間と前記非表示駆動期間とを交互に生成する制御を行う。

#### 【 0 0 2 1 】

これによれば、1フレーム分のデータRAMを搭載することを要しないからチップサイズが小さくなる。1表示フレームに満たない複数表示ライン分保持するデータRAMを搭載する表示駆動期間と非表示駆動期間においてホストプロセッサとの間で表示データの転送と転送停止との同期制御を行うことを要せず、ホストプロセッサの負担を軽減することができる。1表示フレームの期間に、データRAMへの表示データの書き込みと書き込まれた表示データを読み出して駆動回路に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返すから、1表示フレームに満たないデータRAMを用いる場合でも表示駆動期間と非表示駆動期間とを交互に生成することができる。したがって、チップサイズの小型化とホストプロセッサに対する負担軽減との双方を満足させながら、タッチ検出精度を向上させることができる。

#### 【 0 0 2 2 】

##### [ 2 ] < 前記表示駆動期間及び前記非表示駆動期間の指定 >

項1において、前記制御回路は前記ラップアラウンドに繰返すメモリアドレッシング操作のアドレッシング範囲を前記データRAMの最大記憶容量以下の表示ライン数相当のライン数の範囲で制御するタッチインターバル期間データ(TPLINE)を書き換え可能に保持するためのレジスタ回路(20, 20A)を有する。

#### 【 0 0 2 3 】

これによれば表示パネルの表示解像度及びタッチパネルの検出解像度の種々の構成に柔軟に対応することが可能になる。

#### 【 0 0 2 4 】

##### [ 3 ] < ページ単位で前記表示駆動期間と前記非表示駆動期間とを交互に生成 >

項2において、前記制御回路は、前記データRAMの最大記憶容量以下の表示ライン数分のデータサイズを1ページとし、外部からの第1フレーム同期信号の周期単位でページ単位のページ書き込みアドレスを生成すると共にページ単位でページ内のライン書き込みアドレスを生成する書き込みアドレスカウンタ回路(40, 40A)と、表示動作のための第2フレーム同期信号の周期単位で前記ページ単位のページ読み出しアドレスを生成すると共にページ単位でページ内のライン読み出しアドレスを生成する読み出しアドレスカウンタ回路(50, 50A)とを有し、ページ読み出しアドレス毎に前記表示駆動期間と前記非表示駆動期間とを交互に生成し、表示駆動期間においてライン読み出しアドレスを生成し、非表示駆動期間においてライン読み出しアドレスの生成を停止する。

#### 【 0 0 2 5 】

これによれば、1表示フレームの期間に、データRAMへの表示データの書き込みと書き込まれた表示データを読み出して駆動回路に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返す構成を比較的簡単に実現する事ができる。

#### 【 0 0 2 6 】

[ 4 ] < 表示データの書き込み開始から遅延させて読み出し開始し、書き込み終了後に読み出し終了 >

10

20

30

40

50

項3において、前記制御回路は、前記ページ書込みアドレス毎に前記データRAMに表示データの書き込みを開始するタイミングから所定時間(TS\_OF\_S + TS\_PRD)遅延したタイミングで前記データRAMから表示データの読み出しを開始し、開始した読み出しの終了は当該ページ書込みアドレス単位での書き込みの終了後とする。

#### 【0027】

これによれば、ページ毎にデータRAMへの書き込みに対してアクセスアドレスが重なることなく円滑に読み出しを行うことができる。

#### 【0028】

[5] <タッチ検出開始ライン数データ(TS\_OF\_S)、及び表示リード開始ライン数データ(TS\_PRD)>

項4において、前記レジスタ回路は更に、ページ内の先頭の書き込みアドレスへの書き込み開始からタッチ検出開始までの表示ライン数を制御するためのタッチ検出開始ライン数データ(TS\_OF\_S)、及びタッチ検出開始ライン数データで決定される表示ライン数の位置からタッチ検出を行って表示リードを開始するまでの表示ライン数を制御するための表示リード開始ライン数データ(TS\_PRD)を書き換え可能に保持する。前記所定時間は、前記タッチ検出開始ライン数データと表示リード開始ライン数データとの和で決まる期間である。

#### 【0029】

これによれば、データRAMに対するページ単位の書き込み開始を基準にタッチ検出期間(非表示駆動期間)及び表示駆動期間を可変に定義することができる。

#### 【0030】

[6] <表示ラインのラインカウンタ>

項5において、前記制御回路は、表示フレーム単位で、先頭ページの先頭の書き込みアドレスへの書き込み開始から表示ライン周期毎に表示ラインのカウントを行うラインカウンタ(32)を有し、前記ラインカウンタのカウント値に基づいて前記タッチ検出ライン数データによるライン数と前記表示リード開始ライン数データによるライン数とを判別する。

#### 【0031】

これによれば、項4において説明したページ毎にデータRAMへの書き込みと読み出しのアクセスアドレスが重ならないこと、項5で説明したデータRAMに対するページ単位の書き込み開始を基準にタッチ検出期間を可変に定義することを、ラインカウンタのカウント値を用いることによって比較的簡単に実現することができる。

#### 【0032】

[7] <書き込み要求と読み出し要求が競合するとき書き込み要求を優先させる>

項4において、前記データRAMに対する読み出し要求のデータアクセス単位は書き込み要求のデータアクセス単位に比べて大きくされる。このとき、前記制御回路は書き込み要求と読み出し要求が競合したとき書き込み要求を優先させる調停回路(60)を有する。

#### 【0033】

これによれば、ホストプロセッサからの書き込みを一時停止させたりするような同期制御を一切必要としない。データRAMが完全なデュアルポートを持つ場合にはそのような調停は必要ないが、その場合にはデータRAMの回路規模が倍増するので現実的ではない。

#### 【0034】

[8] <書き込みと読み出しのアクセス単位>

項7において、前記読み出し要求のアクセス単位は1表示ライン分の並列データ数を単位とし、前記書き込み要求のアクセス単位はバスアクセスの並列データ数を単位とする。

#### 【0035】

これによれば、書き込みと読み出しが競合して書き込みが優先されても、バスアクセス単位の書き込みの後に表示ライン単位の読み出しが行われるので、ページ単位で既に書き込まれた表示データの読み溢しの虞は全くない。

#### 【0036】

[9] <複数のメモリバンクに対する表示データの書き込みと読み出しを交互に切替え>

10

20

30

40

50

項2において、前記データRAM(70A)は複数のメモリバンク(BANK A, BANK B)を有する。前記制御回路は、相互にいずれか一方のメモリバンクに対する書き込み中に他方のメモリバンクに対する読み出しを行い、書き込み対象とするメモリバンクと読み出し対象とするメモリバンクを交互に切替える。

#### 【0037】

これによれば、書き込みと読み出しのメモリバンクの切り換えによって一つのメモリバンクに対する書き込みと読み出しの競合を排除する事が容易である。

#### 【0038】

##### [10] <書き込みと読み出しの調停回路不要>

項9において、前記制御回路(20A~50A)は、表示フレーム単位で最初の非表示駆動期間に何れか一方のメモリバンクを書き込み対象メモリバンクとし、最初の表示駆動期間に他方のメモリバンクを読み出し対象メモリバンクとし、夫々のページ切替え毎に、書き込み対象メモリバンクと読み出し対象メモリバンクの切替えを行う。

10

#### 【0039】

これによれば、一つのメモリバンクに対して書き込みと読み出しが競合することはないので、項7で説明したような調停回路を一切必要としない。

#### 【0040】

##### [11] <表示ライン周期データ(RTN)、及び表示ライン数データ(NL)>

項3において、前記レジスタ回路は更に、駆動する表示ラインの切替え周期である表示パネルの表示ライン周期を制御するための表示ライン周期データ(RTN)、及び駆動する表示パネルの表示ライン数を制御するための表示ライン数データ(NL)を書き換え可能に保持する。

20

#### 【0041】

これによれば、表示ライン周期及び表示ライン数の異なる種々の表示パネルに容易に対応することができる。

#### 【0042】

##### [12] <ページ単位で表示駆動期間と前記非表示駆動期間とを交互に生成する場合におけるタッチ検出回路ライン数データ(TS\_OF\_S)、及び表示リード開始ライン数データ(TS\_PRD)>

項11において、前記制御回路(20~60)は、前記データRAMの最大記憶容量以下の表示ライン数分のデータサイズを1ページとし、外部からの第1フレーム同期信号の周期単位でページ単位のページ書き込みアドレスを生成すると共にページ単位でページ内のライン書き込みアドレスを生成する書き込みアドレスカウンタ回路(40)と、表示動作のための第2フレーム同期信号の周期単位で前記ページ単位のページ読み出しアドレスを生成すると共にページ単位でページ内のライン読み出しアドレスを生成する読み出しアドレスカウンタ回路(50)とを有し、ページ読み出しアドレス毎に前記表示駆動期間と前記非表示駆動期間とを交互に生成し、表示駆動期間においてライン読み出しアドレスを生成し、非表示駆動期間においてライン読み出しアドレスの生成を停止する。前記レジスタ回路(20)は更に、ページ内の先頭の書き込みアドレスへの書き込み開始からタッチ検出開始までの表示ライン数を制御するためのタッチ検出開始ライン数データ(TS\_OF\_S)、及びタッチ検出開始ライン数データで決定される表示ライン数の位置からタッチ検出を行って表示リードを開始するまでの表示ライン数を制御するための表示リード開始ライン数データ(TS\_PRD)を書き換え可能に保持する。

30

#### 【0043】

これによれば、1表示フレームの期間に、データRAMへの表示データの書き込みと書き込まれた表示データを読み出して駆動回路に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返す構成を比較的簡単に実現する事ができる。そして、データRAMに対するページ単位の書き込み開始を基準にタッチ検出期間(非表示駆動期間)及び表示駆動期間を可変に定義することができる。

#### 【0044】

40

50

[ 1 3 ] <複数のメモリバンクを用いる場合におけるオフセットライン数データ ( T S \_ O F S )、及び表示リード開始ライン数データ ( T S \_ P R D ) >

項 1 1において、前記データ R A M ( 7 0 A )は複数のメモリバンク ( B A N K A , B A N K B )を有する。前記制御回路 ( 2 0 A ~ 5 0 A )は、相互にいずれか一方のメモリバンクに対する書き込み中に他方のメモリバンクに対する読み出しを行い、書き込み対象とするメモリバンクと読み出し対象とするメモリバンクを交互に切替える。このいとき、前記レジスタ回路 ( 2 0 A )は更に、ページ内の先頭の書き込みアドレスへの書き込み開始からのオフセットを表示ライン数で制御するためのオフセットライン数データ ( T S \_ O F S )、及びオフセットライン数データで決定される表示ライン数の位置から前記タッチインターバル期間データで指定される表示ライン数に達した表示ラインからタッチ検出を行って次の表示リードを開始するまでの表示ライン数を制御するための表示リード開始ライン数データ ( T S \_ P R D )を書き換え可能に保持する。

#### 【 0 0 4 5 】

これによれば、書き込みと読み出しのメモリバンクの切り換えによって一つのメモリバンクに対する書き込みと読み出しの競合が排除される。また、データ R A Mに対するページ先頭の書き込みを基準に非表示駆動期間 ( タッチ検出期間 ) と表示駆動期間を可変に設定できる。

#### 【 0 0 4 6 】

##### [ 1 4 ] <表示ラインのラインカウンタ >

項 1 2 又は 1 3において、前記制御回路は、表示フレーム単位で、先頭ページの先頭の書き込みアドレスへの書き込み開始から表示ライン周期毎に表示ラインのカウントを行うラインカウンタ ( 3 2 )を有し、前記ラインカウンタのカウント値に基づいて前記タッチインターバル期間データによるタッチインターバル期間のライン数、前記タッチ検出ライン数データによるライン数、及び前記表示リード開始ライン数データによるライン数、を判別する。

#### 【 0 0 4 7 】

これによれば、項 1 2 で説明したデータ R A Mに対するページ単位の書き込み開始を基準にタッチ検出期間を可変に定義すること、また、項 1 3 で説明したデータ R A Mに対するページ先頭の書き込みを基準に非表示駆動期間 ( タッチ検出期間 ) を可変に設定でき、データ R A Mに対するページ先頭の読み出しを基準に表示駆動期間を可変に設定できることを、ラインカウンタのカウント値を用いることによって比較的簡単に実現することができる。

#### 【 0 0 4 8 】

[ 1 5 ] <表示データを書き込みよりも速く読み出して表示駆動期間と非表示駆動期間を交互に生成 >

表示装置は表示パネル ( 2 )にタッチパネル ( 3 )が組み込まれたパネルモジュール ( 1 )と、前記パネルモジュールに搭載され、前記表示パネルの駆動制御と前記タッチパネルの検出制御を行うドライバ I C ( 4 )とを有する。前記ドライバ I Cは、表示駆動期間に前記表示パネルを駆動する駆動回路 ( 7 2 )と、前記駆動回路の動作を停止する非表示駆動期間に前記タッチパネルの検出制御を行なうタッチパネルコントローラ ( 1 1 )と、表示データを 1 表示フレームに満たない複数表示ライン分保持するデータ R A M ( 7 0 , 7 0 A )と、1 表示フレームの期間に、外部から供給される表示データを前記データ R A Mに書き込むと共に書き込まれた表示データを書き込みよりも速い速度で前記データ R A Mから読み出して駆動回路に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰り返すことにより、前記表示駆動期間と前記非表示駆動期間とを交互に生成する制御を行う制御回路 ( 2 0 ~ 6 0 , 2 0 A ~ 5 0 A )とを有する。

#### 【 0 0 4 9 】

これによれば、1 フレーム分のデータ R A Mを搭載することを要しないからドライバ I Cのチップサイズが小さくなり、パネルモジュールの小型化に寄与する。1 表示フレームに満たない複数表示ライン分保持するデータ R A Mを搭載する表示駆動期間と非表示駆動期間においてホストプロセッサとの間で表示データの転送と転送停止との同期制御を行う

10

20

30

40

50

ことを要せず、ホストプロセッサの負担を軽減することができる。1表示フレームの期間に、データRAMへの表示データの書き込みと書き込まれた表示データを読み出して駆動回路に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返すから、1表示フレームに満たないデータRAMを用いる場合でも表示駆動期間と非表示駆動期間とを交互に生成することができる。したがって、チップサイズの小型化とホストプロセッサに対する負担軽減との双方を満足させながら、タッチ検出精度を向上させることができる。

#### 【0050】

〔16〕<ページ単位で前記表示駆動期間と前記非表示駆動期間とを交互に生成>

項15において、前記制御回路は、前記データRAM(70, 70A)の最大記憶容量以下の表示ライン数分のデータサイズを1ページとし、外部からの第1フレーム同期信号の周期単位でページ単位のページ書き込みアドレスを生成すると共にページ単位でページ内のライン書き込みアドレスを生成する書き込みアドレスカウンタ回路(40, 40A)と、表示動作のための第2フレーム同期信号の周期単位で前記ページ単位のページ読み出しアドレスを生成すると共にページ単位でページ内のライン読み出しアドレスを生成する読み出しアドレスカウンタ回路(50, 50A)とを有し、ページ読み出しアドレス毎に前記表示駆動期間と前記非表示駆動期間とを交互に生成し、表示駆動期間においてライン読み出しアドレスを生成し、非表示駆動期間においてライン読み出しアドレスの生成を停止する。10

#### 【0051】

これによれば、1表示フレームの期間に、データRAMへの表示データの書き込みと書き込まれた表示データを読み出して駆動回路に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返す構成を比較的簡単に実現する事ができる。20

#### 【0052】

〔17〕<複数のメモリバンクに対する表示データの書き込みと読み出しを交互に切替え>

項15において、前記データRAM(70A)は複数のメモリバンク(BANK A, BANK B)を有する。前記制御回路(20A~50A)は、相互にいずれか一方のメモリバンクに対する書き込み中に他方のメモリバンクに対する読み出しを行い、書き込み対象とするメモリバンクと読み出し対象とするメモリバンクを交互に切替える。

#### 【0053】

これによれば、書き込みと読み出しのメモリバンクの切り換えによって一つのメモリバンクに対する書き込みと読み出しの競合を排除する事が容易である。30

#### 【0054】

##### 2. 実施の形態の詳細

実施の形態について更に詳述する。

#### 【0055】

##### 《表示装置》

図2にはパネルモジュール1とこれを駆動するドライバIC4を備えた表示装置が例示される。パネルモジュール1は表示パネル2にタッチパネル3が組み込まれた所謂インセル形態で構成され、例えばガラス基板上にTFTと画素電極をマトリクス状に配置したTFTアレイ基板を有し、その上に、液晶層、画素電極に対するコモン電極層、カラーフィルタ、及びタッチ検出容量、タッチ検出電極、及び表面ガラスなどが積層されて構成される。図2では便宜上、表示パネル2とタッチパネル3を左右に分離して図示しているが、実際には両者は重ねられている。40

#### 【0056】

図2に従えば、表示パネル2は、例えば、交差配置された走査電極GL1~GLmk(m、kは正の整数)と信号電極SL1~SLj(jは正の整数)の各交点にTFTと呼ばれる薄膜トランジスタTrが配置され、薄膜トランジスタTrのゲートに対応する走査電極GL1~GLmk、薄膜トランジスタTrのソースに対応する信号電極SL1~SLjが設けられ、そして薄膜トランジスタTrのドレインにはコモン電極VCOMとの間にサブピクセルとなる液晶素子及び蓄積コンデンサ(図では液晶素子及び蓄積コンデンサを1個のコンデンサCpxで代表する)が形成されて、各画素が形成される。走査電極GL150

～G L m k の夫々に沿った画素のラインを表示ラインと称する。表示制御では順次走査電極 G L 1 ～ G L m k が駆動され、走査電極単位で薄膜トランジスタ T r がオン状態にされることで、ソースとドレイン間に電流が流れ、そのとき信号電極 S L 1 ～ S L j を介してソースに加えられている各々の信号電圧が液晶素子 C p x に印加されることによって液晶の状態が制御される。

#### 【0057】

タッチパネル 3 は、静電容量方式とされ、例えば、交差配置された駆動電極 T X 1 ～ T X m と検出電極 R X 1 ～ R X n の交差位置に多数のタッチ検出容量 C t p がマトリクス状に形成されている。特に制限されないが、図 2 では k 本の表示ライン単位でコモン電極を m 個に分割し、対応する駆動電極 T X 1 ～ T X m と共に通化して、パネルモジュール 1 の薄型化を図っている。駆動電極 T X 1 ～ T X m を順次駆動したときタッチ検出容量 C t p を介して検出電極 R X 1 ～ R X n に電位変化が現れ、この電位変化を検出電極 R X 1 ～ R X n 毎に積分することによって検出信号を形成することができる。検出容量の近傍に指があるとその浮遊容量によって検出容量 C t p との合成容量値が小さくなり、この容量値の変化に応じた検出信号の相違によってタッチと非タッチを区別するようになっている。表示パネル 2 に重ねられたタッチパネル 3 を用いることによって、液晶パネル 2 の画面表示に応じてタッチパネル 3 で行われるタッチ操作によるタッチ座標からその操作を判別可能になる。

#### 【0058】

ドライバ I C 4 は、表示パネル 2 に対する駆動制御及びタッチパネル 3 に対する検出制御を行なうコントローラデバイスもしくはドライバデバイスとして機能される。このドライバ I C 4 は上記パネルモジュールの TFT 基板に COG (Chip on Glass) などの形態で実装されている。ドライバ I C 4 は、例えばパネルモジュール 1 をユーザインタフェースとして搭載するスマートフォンなどの情報端末装置のホストプロセッサ (HSTM C U ) 5 に接続され、ホストプロセッサ 5 との間で、動作コマンド、表示データ、タッチ検出座標データなどの入出力が行なわれる。

#### 【0059】

ドライバ I C 4 は、特に制限されないが、表示ドライバ (LCDDRV) 10、及びタッチパネルコントローラ (TPC) 11 を搭載して半導体集積回路化されている。半導体集積回路化されたドライバ I C 4 は、例えば、CMOS 集積回路製造技術などによって単結晶シリコンなどの半導体基板に形成されている。特に制限されないが、図 2 の例では、走査電極 G L 1 ～ G L m k を駆動する回路はゲートドライバ (GDRV) 6 として液晶パネル 2 に搭載される。ドライバ I C 4 は垂直同期信号などのフレーム同期信号に同期して信号電極 S L 1 ～ S L j を駆動すると共に、ゲートドライバ I C 6 に走査電極 G L 1 ～ G L m k の駆動タイミングなどを与える。ゲートドライバ I C 6 はドライバ I C 4 から与えられたタイミングにしたがって走査電極 G L 1 ～ G L m k の駆動を行う。

#### 【0060】

表示ドライバ 10 は、一つの表示フレーム期間の中を、表示駆動期間及び非表示駆動期間に分けて表示パネル 2 を制御する。例えば走査電極 G L 1 ～ G L m k を k × i (i は正の整数) 本単位で m / i 個のブロックに分割して m / i 個の表示駆動期間に分割し、分割された表示駆動期間毎に対応するブロックの k × i 本の走査電極を順番に駆動し、各走査電極の駆動タイミングに合わせて対応する表示ラインの表示データで信号電極 S L 1 ～ S L j を駆動する。表示ドライバ 10 は表示駆動期間に対応するブロックの走査電極に対する駆動タイミングをゲートドライバ 6 に与える。また、表示ドライバ 10 は非表示駆動期間において信号電極 S L 1 ～ S L j の駆動を停止し、タッチパネルコントローラ 11 にタッチ検出動作可能であることを通知する。タッチパネルコントローラ 11 は非表示駆動期間毎に、駆動電極 T X 1 ～ T X m の内の所定範囲を順次駆動してタッチ検出容量 C t p を介して検出電極 R X 1 ～ R X n に現れる電位変化を積分することによって検出信号を形成し、取得した検出信号をホストプロセッサ 5 に与える。

#### 【0061】

10

20

30

40

50

ここで、表示ドライバ10は信号電極S L 1～S L jの駆動に用いる表示データを一時的に保持するメモリとして1表示フレームに満たない記憶容量のRAMを利用し、1表示フレームの期間に、ホストプロセッサから供給される表示データをそのRAMに書き込むと共に書き込まれた表示データを書き込みよりも速い速度でRAMから読み出すためのメモリアドレッシング操作をラップアラウンドに複数回繰返すことにより、前記表示駆動期間と前記非表示駆動期間とを交互に生成する制御を行う。以下その制御機能の詳細について説明する。

#### 【0062】

##### 表示ドライバの第1の例

図1には表示ドライバ10の構成が例示される。表示ドライバ10は、レジスタ回路20、タイミングコントローラ30、RAMライト制御回路40、表示リード制御回路50、調停回路60、パーシャルRAM70、ラインラッチ71、ソース駆動回路72、及びゲートドライバIC6にゲート駆動タイミング信号などを供給するゲート駆動回路73を有する。

#### 【0063】

パーシャルRAM70は表示データを1表示フレームに満たない複数表示ライン分保持するデータRAMの一例である。

#### 【0064】

レジスタ回路20、タイミングコントローラ30、RAMライト制御回路40、表示リード制御回路50、及び調停回路60は、1表示フレームの期間に、ホストプロセッサ5から供給される表示データをパーシャルRAM70に書き込むと共に書き込まれた表示データを書き込みよりも速い速度でパーシャルRAM70から読み出してソース駆動回路72に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返すことにより、前記表示駆動期間と前記非表示駆動期間とを交互に生成する制御を行う制御回路の一例である。

#### 【0065】

タッチパネルコントローラ11はタイミングコントローラ80、タッチ検出信号ドライバ81、タッチ状態検出回路82、及びメモリ83を有する。タッチ検出信号ドライバ81は駆動電極TX1～TXmを順次駆動する。タッチ状態検出回路82はタッチ検出信号ドライバ81で駆動電極TX1～TXmを順次駆動したときタッチ検出容量Ctpを介して検出電極RX1～RXnに現れる電位変化を検出電極RX1～RXn毎に積分して検出データを生成する回路である。メモリ83は前記検出データを蓄積し、蓄積した検出データはホストプロセッサ5によるタッチ座標の演算に供される。

#### 【0066】

図3及び図4には表示ドライバによる動作制御タイミングが例示される。両図のタイミングは時刻T6-5の前後で接続するように部分的に重複するように作図されている。図3及び図4においてカウント値L1NECNT及び表示リードアドレスに代表されるカウント値及びアドレス値は0から始まるディジタル値を想定してその値を図示している。これに対し、転送データ及びドライバ出力に付された番号は1から始まる表示ラインを想定してその値を図示してある。

#### 【0067】

図1、図3及び図4に基づいて表示ドライバ10を詳細に説明する。ここでは、表示ライン(単にラインとも記す)が32ラインの表示パネル2において、表示ドライバ10に8ライン分のパーシャルRAM70を搭載した場合を例に挙げて説明する。

#### 【0068】

8ライン分のパーシャルRAM70に対する書き込みと読み出しは8ライン分のページ単位で行う。RAMライト制御回路40及び表示リード制御回路50はページ単位でパーシャルRAMのアクセスアドレスを生成する。

#### 【0069】

RAMライト制御回路40はRAMライトタイミングコントローラ41、RAMライト

10

20

30

40

50

アドレスカウンタ42、P Dバッファ43、及びR A Mライトページカウンタ44を有する。R A Mライトタイミングコントローラ41はホストプロセッサ5から垂直同期信号H O S T \_ V S Y N C , 水平同期信号H O S T \_ H S Y N C , データイネーブル信号H O S T \_ D E , 及び表示データH O S T \_ P D を入力してパーシャルR A M70の書き込み制御を行う。R A Mライトアドレス(パーシャルR A M70のライトアクセスアドレス)の上位側アドレスはR A Mライトページカウンタ44のカウント値( R A Mライトページアドレス; ページ書き込みアドレス)であり、その下位側アドレスはR A Mライトアドレスカウンタ42のカウント値( R A Mライトアドレス)である。

#### 【0070】

表示リード制御回路50は表示リードタイミングコントローラ51、表示リードアドレスカウンタ52、表示リードページカウンタ53を有する。表示リードタイミングコントローラ51はタイミングコントローラ30から垂直同期信号D I S P \_ V S Y N C , 水平同期信号D I S P \_ H S Y N C , ラインカウント値L I N E C N T , 及び表示駆動期間信号D I S P \_ P R D を入力してパーシャルR A M70の読み出し制御を行う。R A Mリードアドレス(パーシャルR A M70のリードアクセスアドレス)の上位側アドレスは表示リードページカウンタ53のカウント値(表示リードページアドレス; ページ読み出しがアドレス)であり、その下位側アドレスは表示リードアドレスカウンタ52のカウント値(表示リードアドレス)である。

#### 【0071】

R A Mライトと表示リードは非同期であり、調停回路60はパーシャルR A M70に対するライトアクセス要求とリードアクセス要求の競合を調停する。例えば、調停回路60はR A Mライトタイミングコントローラコントローラ41からの書き込み要求を、表示リードタイミングコントローラ51からの読み出し要求よりも優先して許可する。調停回路60によるタイミング調整は書き込み、読み出しの何れに対してもキャンセルするものではない。

#### 【0072】

レジスタ回路20はタッチ検出開始ライン数データ(T S \_ O F S )、表示リード開始ライン数データ(T S \_ P R D )、表示ライン周期データ(R T N )、表示ライン数データ(N L )、及びタッチインターバル期間データ(T P L I N E )を書き換え可能に保持する。その書き換えは例えばホストプロセッサ5によって行われる。

#### 【0073】

タッチ検出開始ライン数データ(T S \_ O F S )はページ内の先頭の書き込みアドレスへの書き込み開始からタッチ検出開始までの表示ライン数を制御するための制御データである。表示リード開始ライン数データ(T S \_ P R D )はタッチ検出開始ライン数データで決定される表示ライン数の位置からタッチ検出を行って表示リードを開始するまでの表示ライン数を制御するための制御データである。図3及び図4から明らかのように、前記R A Mライトページアドレス(ページ書き込みアドレス)毎に前記パーシャルR A M70に表示データの書き込みを開始するタイミングから所定時間(T S \_ O F S + T S \_ P R D )遅延したタイミングでパーシャルR A M70から表示データの読み出しを開始する。開始した読み出しの終了は当該ページ書き込みアドレス単位での書き込みの終了後とする。

#### 【0074】

表示ライン周期データ(R T N )は駆動する表示ラインの切替え周期である表示パネルの表示ライン周期を制御するための制御データである。

#### 【0075】

表示ライン数データ(N L )は駆動する表示パネルの表示ライン数を制御するための制御データである。

#### 【0076】

タッチインターバル期間データ(T P L I N E )は幾つの表示ライン毎にタッチ期間を挿入するかを制御するための制御データである。

#### 【0077】

10

20

30

40

50

ページ数演算回路 22 は RAM ライトページ数 (= 表示リードページ数) PAGE MAX X を演算する。NL / TPLINE に余りがある場合、1 ページ追加して最終ページに余りを割り当てる。また、複数のページに数ラインずつ余りを割り当ててもよい。すなわち、“ PAGE MAX = (NL / TPLINE) + { (NL / TPLINE) に余りがあれば + 1 } ”とする。

#### 【0078】

表示ライン数演算回路 21 は 1 フレームにおいて表示ライン周期カウンタ 32 でカウントする LINECNT の最大カウント値 LINECNTMAX を演算する。すなわち、“ LINECNTMAX = NL + (TS\_OF\_S + TS\_PRD) × PAGE MAX + TPLINE ”とする。

10

#### 【0079】

表示ライン周期カウンタ 31 は周期データ (RTN) による周期の水平同期信号 DISP\_HSYNC を出力する。表示ラインカウンタ 32 は 1 フレーム単位でパーシャル RAM 70 の書き込み開始後に水平同期信号 DISP\_HSYNC のクロック数を LINECNTMAX までカウントして表示ラインカウント値 LINECNT を生成する。表示リード期間生成回路 33 は TS\_OF\_S, TS\_PRD, DISP\_HSYNC, LINECNT に基づいて表示駆動期間信号 DISP\_PRD を生成する。

#### 【0080】

表示リードタイミングコントローラ 51 は、パーシャル RAM 70 に保持したデータを、パーシャル RAM 70 の各ページの先頭ラインのデータ書き込みが始まってから、TS\_OF\_S + TS\_PRD の後に表示出力開始し、TPLINE の期間だけ表示リードしてから再び TS\_OF\_S + TS\_PRD の期間だけ表示リードを停止する動作を + PAGE MAX による回数だけ繰り返す。この表示リードタイミングコントローラ 51 は、ホストプロセッサ 5 の表示データ書き込み速度より十分速い速度でパーシャル RAM 70 から表示データを読み出して表示駆動を可能にする。RAM ライト速度に対して表示リード速度が早ければ早いほど、タッチセンシング期間 TS\_PRD を確保できるが、遅れてアドレスカウントされる表示リードアドレスは RAM ライトアドレスを追い越してはならない。表示データの読み出しは、図 3 及び図 4 に示す表示リードアドレスと表示ライトアドレスが交わらないように表示リード停止期間と表示リード期間を交互に繰り返しながら断続的に表示動作が行われる。

20

#### 【0081】

表示データ書き込み、表示リードが可能な 1 フレームの画像サイズに満たないパーシャル RAM で、RAM ライト用のカウンタ 42, 44 と表示リード用のカウンタ 52, 53 により、1 フレーム内に複数回メモリ全面を書き込み、読み出しを行うことができる 1 ページで使用するパーシャル RAM 70 のライン数は TGPLINE の設定値で調整することができる。

30

#### 【0082】

図 3 及び図 4 において、ホストプロセッサ 5 から図の T6-1 ~ T6-12 の間に連続的に送信される表示データは、順に表示ドライバ 10 内のパーシャル RAM 70 に蓄積される。パーシャル RAM 70 の RAM ライトアドレスが 0 h から最大値の 7 h までインクリメントした後は、RAM ライトアドレスはリセットされ、再び 0 h からインクリメントされる。RAM ライト用のカウンタ 42, 44 は垂直同期信号 HOST\_VSYNC でリセットされる。パーシャル RAM 70 の書き込みは、PAGE MAX の最終頁におけるパーシャル RAM 70 のライン数 (TPLINE が示すライン数に等しい) まで継続され、フレームを跨がずにさらに表示データ書き込みが発生した場合は、書き込みデータを無視する。

40

#### 【0083】

図 3 及び図 4 において、1 フレームごとにパーシャル RAM 70 に対して複数回表示リード停止期間、表示リード期間の順に断続的なデータを読み出しが行われる。表示リード停止期間は、図 3 及び位図 4 における時刻 T6-1 ~ T6-2, T6-4 ~ T6-5, T

50

6 - 7 ~ T 6 - 8 , T 6 - 10 ~ T 6 - 11 である。表示リード期間は、時刻 T 6 - 2 ~ T 6 - 4 , T 6 - 5 ~ T 6 - 7 , T 6 - 8 ~ T 6 - 10 , T 6 - 11 ~ T 6 - 13 である。表示リード停止期間は非表示駆動期間に対応される。すなわち、パーシャルRAM70から読み出された表示リードデータは1ラインだけラインラッチ71で同期を取った後にソース駆動回路72に供給されて表示パネル2を駆動する。パーシャルRAM70の読み出し開始からソース駆動回路72の駆動開始までにDISP\_HSYNCの1サイクル分の動作遅延がある。したがって、表示リード停止期間と非表示駆動期間との開始タイミングにはDISP\_HSYNCの1サイクル分の動作遅延がある。ちなみに表示駆動期間はTLINEの期間に対応される。このようにして、表示ドライバ10は非表示駆動、表示駆動を交互に繰り返しながらソース駆動回路72で表示パネル2の信号電極SL1~SLjを駆動し、信号電極SL1~SLjの駆動、駆動停止に合わせてゲート駆動回路73にゲートドライバに対する動作、停止を交互に繰り返す。

#### 【0084】

表示ドライバ10は表示フレーム、表示ラインを示すDISP\_VSYNC, DISP\_HSYNC、表示期間を示すDISP\_PRD、及びパーシャルRAM70の表示リードタイミングでトグルするタイミング信号TEをホストプロセッサ5へ返す。ホストプロセッサ5はこれらの信号を必要に応じて参照することにより表示ドライバ10の表示リードタイミングを確認しながら表示データを送信することができる。

#### 【0085】

図1のドライバIC10によれば以下の作用効果を得る。

#### 【0086】

(1) 1表示フレームの期間に、表示データをパーシャルRAM70に書込むと共に書き込まれた表示データを書き込みよりも速い速度でパーシャルRAM70から読み出してソース駆動回路72に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返すことにより、表示駆動期間と前記非表示駆動期間とを交互に生成する。図5の(A)乃至(C)にはこの駆動形態を凝縮して示してある。

#### 【0087】

これにより、1フレーム分のRAMを搭載することを要しないからチップサイズが小さくなる。図6の(A)乃至(C)には1フレーム分のRAMを用いて表示駆動期間と前記非表示駆動期間とを交互に生成する駆動形態を概略的に示してある。

#### 【0088】

1表示フレームに満たない複数表示ライン分保持するパーシャルRAM70を搭載する表示駆動期間と非表示駆動期間においてホストプロセッサ5との間で表示データの転送と転送停止との同期制御を行うことを要せず、ホストプロセッサ5の負担を軽減することができる。図7の(A)乃至(C)にはRAMを搭載しない代わりにホストプロセッサ5との間で表示データの転送と転送停止との同期制御を行うことによって表示駆動期間と前記非表示駆動期間とを交互に生成する駆動形態を概略的に示してある。

#### 【0089】

1表示フレームの期間に、パーシャルRAM70への表示データの書き込みと書き込まれた表示データを読み出してソース駆動回路72に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返すから、1表示フレームに満たないパーシャルRAM70を用いる場合でも表示駆動期間と非表示駆動期間とを交互に生成することができる。したがって、チップサイズの小型化とホストプロセッサ5に対する負担軽減との双方を満足させながら、タッチ検出精度を向上させることができる。

#### 【0090】

(2) 前記ラップアラウンドに繰返すメモリアクセス操作のアドレッシング範囲をパーシャルRAM70の最大記憶容量以下の表示ライン数相当のライン数の範囲で制御する制御データTGPLINEの設定値で調整することができる。換言すれば、1フレーム内に複数回メモリ全面を書き込み、読み出しを行うことができる1ページで使用するパーシャルRAM70のライン数は制御データTGPLINEの設定値で調整することができる。

10

20

30

40

50

したがって、表示パネルの表示解像度及びタッチパネルの検出解像度の種々の構成に柔軟に対応することが可能になる。

#### 【0091】

(3) RAMライト用のアドレスカウンタ42, 44と表示リード用のカウンタ52, 53を用いて、ページ単位で前記表示駆動期間と前記非表示駆動期間とを交互に生成するから、1表示フレームの間に、データRAMへの表示データの書き込みと書き込まれた表示データを読み出して駆動回路に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返す構成を比較的簡単に実現する事ができる。

#### 【0092】

(4) ページ書き込みアドレス毎に前記パーシャルRAM70に表示データの書き込みを開始するタイミングから所定時間(TS\_OF S + TS\_PR D)遅延したタイミングでパーシャルRAM70から表示データの読み出しを開始し、開始した読み出しの終了は当該ページ書き込みアドレス単位での書き込みの終了後とするから、ページ毎にパーシャルRAM70への書き込みに対してアクセスアドレスが重なることなく円滑に読み出しを行うことができる。上記所定期間は、夫々可変可能なタッチ検出開始ライン数データ(TS\_OF S)、及び表示リード開始ライン数データ(TS\_PR D)によって決定するから、パーシャルRAM70に対するページ単位の書き込み開始を基準にタッチ検出期間(非表示駆動期間)及び表示駆動期間を可変に定義することができる。10

#### 【0093】

(5) パーシャルRAM70に対する書き込み要求と読み出し要求が競合するとき調停回路60によって書き込み要求を優先させるから、ホストプロセッサ5からの書き込みを一時停止させたりするような同期制御を一切必要としない。パーシャルRAM70が完全なデュアルポートを持つ場合にはそのような調停は必要ないが、その場合にはパーシャルRAMの回路規模が倍増するので現実的ではない。20

#### 【0094】

(6) パーシャルRAM70に対する読み出し要求のアクセス単位を1表示ライン分の並列データ数を単位とし、書き込み要求のアクセス単位をバスアクセスの並列データ数を単位とするから、書き込み期間に比べて表示リード期間が短い上に書き込みと読み出しが競合したとき書き込みを優先させても、バスアクセス単位の書き込みの後に表示ライン単位の読み出しが行われるので、ページ単位で既に書き込まれた表示データの読み出しの虞は全くない。30

#### 【0095】

(7) 可変可能な表示ライン周期データ(RTN)、及び表示ライン数データ(NL)によって表示ラインの切替え周期と表示パネルの表示ライン数を制御するから、表示ライン周期及び表示ライン数の異なる種々の表示パネルに容易に対応することができる。

#### 【0096】

##### 《表示ドライバの第2の例》

図8には表示ドライバの別の例が示される。ここに示される表示ドライバ10Aは、パーシャルRAM70Aが第1のメモリバンクBANK Aと第2のメモリバンクBANK Bとを備え、ホストプロセッサ5からのデータ書き込み用と表示パネルへの読み出し用に第1のメモリバンクBANK Aと第2のメモリバンクBANK Bとを切替えて相互に書き込みと読み出しを排他的に行うように構成した点が図1の表示ドライバ10と相違される。図9及び図10には表示ドライバ10Aによる動作制御タイミングが例示される。両図のタイミングは時刻T8-7の前後で接続するように部分的に重複するように作図されている。図8、図9及び図10に基づいて表示ドライバ10Aが図1の表示ドライバと相違する点について詳細に説明する。ここでは、表示ラインが32ラインの表示パネル2において、表示ドライバ10に夫々8ライン分のメモリバンクBANK A, BANK Bを持つパーシャルRAM70Aを搭載した場合を例に挙げて説明する。40

#### 【0097】

パーシャルRAM70Aは1フレーム内に複数回メモリ全面を書き込み、読み出しができることは図1の場合と同様である。パーシャルRAM70Aの第1のメモリバ50

ンクBANKAと第2のメモリバンクBANKBはライトと表示リードを同時発生できないため、BANKAとBANKBにおいて、書き込みアクセス期間と読み出しアクセス期間を交互に繰り返しながら書き込み、読み出しを行う。1ページで使用するパーシャルRAMのライン数、即ち各メモリバンクBANKA、BANKBのライン数は制御データTLINEで調整することができる。

#### 【0098】

レジスタ回路20Aはオフセットライン数データ(TS\_OF\_S)による制御の意義が異なる。即ち、オフセットライン数データ(TS\_OF\_S)はページ内の先頭の書き込みアドレスへの書き込み開始からのオフセットを表示ライン数で制御するための制御データである。表示リード開始ライン数データ(TS\_PRD)はオフセットライン数データで決定される表示ライン数の位置から前記タッチインターバル期間データで指定される表示ライン数に達した表示ラインからタッチ検出を行って次の表示リードを開始するまでの表示ライン数を制御するための制御データである。その他の制御データの意義は図1の場合と変わりない。これに伴って、1フレームにおいて表示ライン周期カウント32でカウントするLINECNTの最大カウント値LINECNTMAXの演算内容が、“LINECNTMAX = TS\_OF\_S + (TLINE + TS\_PRD) × PAGEMAX”に変更される。

10

#### 【0099】

タイミングコントローラ30Aはオフセットライン数データ(TS\_OF\_S)及び表示リード開始ライン数データ(TS\_PRD)の意義の相違により、図9及び図10に例示されるようにDISP\_VSYNC, DISP\_PRDの生成タイミングが図1とは相違される。即ち、ページ書き込みが開始されるとTS\_OF\_S + TLINEで指定されるライン数を経過するタイミングでタッチ検出が開始され、ページ読出しが開始されるとTS\_OF\_Sで指定されるライン数を経過するタイミングで表示駆動が開始される。

20

#### 【0100】

RAMライト制御回路40Aはライトバンク選択信号WRBANKSELを生成し、RAMライトページアドレスの初期値0hを基点にBANKAを選択し、RAMライトページアドレスの+1インクリメント毎にメモリバンクの選択を切替えていく。RAMリード制御回路50Aはリードバンク選択信号RDBANKSELを生成し、RAMリードページアドレスの初期値0hを基点にBANKAを選択し、RAMリードページアドレスの+1インクリメント毎にメモリバンクの選択を切替えていく。RAMリード頁の切替えはRAMライトページの切替えに対して1ページ分遅延される。即ち、信号DISP\_PRDの最初のイネーブルタイミングは先頭ページに対するRAMライト期間経過後になる。したがって、書き込みと読出しに割り当たられるメモリバンクはページ毎に第1メモリバンクBANKAと第2メモリバンクBANKBとの間で交互に切替えられる。RAMライト制御回路40A及びRAMリード制御回路50Aのその他の構成は図1と同様である。

30

#### 【0101】

図9及び図10において、ホストプロセッサ5から図のT8-1～T8-12の間に連続的に送信される表示データを、順に表示ドライバ10A内のパーシャルRAM70AのメモリバンクBANKA、BANKBに蓄積する。メモリバンクBANKAが書き込み状態のとき、メモリバンクBANKBは読み出し可能な状態となり、メモリバンクBANKBが書き込み状態のとき、メモリバンクBANKAは読み出し可能な状態となる。パーシャルRAM70AのRAMライトアドレスが0hから最大の7hまでインクリメントした後は、RAMライトアドレスはリセットされ、再び0hからインクリメントする。このとき、ライトバンク選択信号WRBANKSELの選択指示をBANKAからBANKB、またはBANKBからBANKAに切り替え、連続して同じメモリバンクに書き込みアクセスしないように制御される。

40

#### 【0102】

図9及び図10において、表示リード停止期間と表示リード期間が順に繰返される。表示リード停止期間は、図の時刻T8-1～T8-3、T8-4～T8-6、T8-8～T

50

8 - 10 で示され、表示リード期間は、図の時刻 T 8 - 3 ~ T 8 - 4、T 8 - 6 ~ T 8 - 8、T 8 - 10 ~ T 8 - 11 で示され、表示リード停止期間が非表示駆動期間に対応される。パーシャル RAM 70A の表示リードアドレスが 0h から最大値の 7h までインクリメントした後は、表示リードアドレスはリセットされ、再び 0h からインクリメントする。このとき、リードバンク選択信号 R D B A N K S E L の選択指示を BANK A から BANK B、または BANK B から BANK A に切り替え、連続して同じメモリバンクに読み出しアクセスしないように制御される。

#### 【 0103 】

ライインラッチ 71、ソース駆動回路 72、ゲート駆動回路 73 は図 1 と同様である。ホストプロセッサ 5 が表示ドライバ 10A の表示リードタイミングを確認するため信号は図 1 の TE に対して、パーシャル RAM 70A の BANK A の表示リードタイミングでトグルする TE\_A と BANK B の表示リードタイミングでトグルする TE\_B に分けた点が相違される。10

#### 【 0104 】

その他の構成については図 1 の場合と同様であるからそれと同一の参照符号を付してその詳細な説明を省略する。

#### 【 0105 】

図 9 のドライバ I C 10A によれば以下の作用効果を得る。

#### 【 0106 】

(1) 1 表示フレームの期間に、表示データを 2 メモリバンク構成のパーシャル RAM 70A に書込むと共に書き込まれた表示データを書き込みよりも速い速度でパーシャル RAM 70A から読み出してソース駆動回路 72 に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返すことにより、表示駆動期間と前記非表示駆動期間とを交互に生成する。図 11 の (A) 乃至 (C) にはこの駆動形態を凝縮して示してある。これにより図 1 と同様に、1 フレーム分の RAM を搭載することを要しないからチップサイズが小さくなる。また、1 表示フレームに満たない複数表示ライン分保持するパーシャル RAM 70 を搭載する表示駆動期間と非表示駆動期間においてホストプロセッサ 5 との間で表示データの転送と転送停止との同期制御を行うことを要せず、ホストプロセッサ 5 の負担を軽減することができる。さらに、1 表示フレームの期間に、パーシャル RAM 70A への表示データの書き込みと書き込まれた表示データを読み出してソース駆動回路 72 に与えるためのメモリアドレッシング操作をラップアラウンドに複数回繰返すから、1 表示フレームに満たないパーシャル RAM 70A を用いる場合でも表示駆動期間と非表示駆動期間とを交互に生成することができる。したがって、チップサイズの小型化とホストプロセッサ 5 に対する負担軽減との双方を満足させながら、タッチ検出精度を向上させることができる。2030

#### 【 0107 】

(2) パーシャル RAM 70A に複数のメモリバンク BANK A, BANK B を用意し、双方に対する表示データの書き込みと読み出しを交互に切替えて行う。これによれば、書き込みと読み出しのメモリバンクの切り換えによって一つのメモリバンクに対する書き込みと読み出しの競合を排除する事が容易である。したがって、一つのメモリバンクに対して書き込みと読み出しが競合することはないので、図 1 の例のような調停回路 60 を一切必要としない。40

#### 【 0108 】

(3) 複数のメモリバンク BANK A, BANK B を用いる場合においてオフセットライン数データ (TS\_OF\_S)、表示リード開始ライン数データ (TS\_PRD)、及びタッチインターバル期間データ (TPLINE) が可変可能であるから、パーシャル RAM 70A に対するページ先頭の書き込みを基準に非表示駆動期間 (タッチ検出期間) と表示駆動期間を可変に設定できる。

#### 【 0109 】

その他の主な作用効果は図 1 の場合と同様である

本発明は上記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは言うまでもない。

#### 【0110】

例えば、表示パネルは液晶を用いるものに限定されず、エレクトロルミネッセンスを応用した表示パネルなどの別の表示パネルであってよい。タッチパネルは相互容量検出方式に限定されず表示パネルの駆動ノイズを問題視する構造であれば何でも良い。また、パネルモジュールはインセル形態に限定されず表示パネルにタッチパネルを重ね構造など他の構造であってよい。

#### 【0111】

ドライバICは図2で説明したように表示ドライバ(LCDDRV)、及びタッチパネルコントローラ(TPC)から成る構成に限定されず、タッチ座標演算に特化してホストプロセッサの負担軽減に資するサブプロセッサなどの他の回路モジュールを含んでも良い。また、タッチパネルコントローラを含ます、そのタイミング制御信号を外付けのタッチパネルコントローラに出力可能な構成であってもよい。また、ドライバICを用いる表示装置は携帯型であるか非携帯型であるかを問わない。10

#### 【0112】

データRAMはシングルポートに限定されず、擬似マルチポート型であってもよい。

#### 【0113】

レジスタ回路は必ずしもホストプロセッサによって書き換え可能であることに限定されない。例えば不揮発性レジスタの場合には、テスト端子を介して書き換え可能であってもよい。20

#### 【0114】

書込みアドレスカウンタ回路と、読み出しアドレスカウンタ回路とはそれぞれページカウンタとアドレスカウンタを別々に持つことに限定されず、一つのカウンタの上位側と下位側で構成できることは言うまでもない。

#### 【0115】

パーシャルRAMに対する読み出し単位はバスアクセスの並列データ数に限定されず、書込み要求のデータアクセス単位は1表示ライン分の並列データ数に限定されず、適宜変更可能である。

#### 【0116】

パーシャルRAMのメモリバンクは2バンクに限定せず、それ以上であってもよい。30

#### 【符号の説明】

#### 【0117】

- 1 パネルモジュール

- 2 表示パネル

- 3 タッチパネル

- 4 ドライバIC

G L 1 ~ G L m k 走査電極

S L 1 ~ S L j 信号電極

T r 薄膜トランジスタ

C p x 画素コンデンサ

T X 1 ~ T X m 駆動電極

R X 1 ~ R X n 検出電極

5 ホストプロセッサ

6 ゲートドライバ

10, 10A 表示ドライバ(LCDDRV)

11 タッチパネルコントローラ(TPC)

20, 20A レジスタ回路

30, 30A タイミングコントローラ

40, 40A RAMライト制御回路

40

50

- 4 1 RAMライトタイミングコントローラ

- 4 2 RAMライトアドレスカウンタ

- 4 3 PDバッファ

- 4 4 RAMライトページカウンタ

- 5 0 , 50A 表示リード制御回路

- 5 1 表示リードタイミングコントローラ

- 5 2 表示リードアドレスカウンタ

- 5 3 表示リードページカウンタ

- 6 0 調停回路

- 7 0 パーシャルRAM70

- 7 1 ラインラッチ

- 7 2 ソース駆動回路

- 7 3 ゲート駆動回路

- 8 0 タイミングコントローラ

- 8 1 タッチ検出信号ドライバ

- 8 2 タッチ状態検出回路

- 8 3 メモリ

10

【 义 1 】

【 义 2 】

【図3】

【図4】

【図5】

【図6】

【図7】

【 义 8 】

【図9】

【図10】

【図11】

---

フロントページの続き

| (51)Int.Cl. |       | F I       |         |              |

|-------------|-------|-----------|---------|--------------|

| G 0 2 F     | 1/133 | (2006.01) | G 0 9 G | 3/20 6 5 0 J |

|             |       |           | G 0 9 G | 3/20 6 9 1 D |

|             |       |           | G 0 9 G | 3/36         |

|             |       |           | G 0 9 G | 3/20 6 3 1 R |

|             |       |           | G 0 9 F | 9/00 3 4 6 A |

|             |       |           | G 0 9 F | 9/00 3 6 6 A |

|             |       |           | G 0 2 F | 1/133 5 3 0  |

|             |       |           | G 0 2 F | 1/133 5 5 0  |

(56)参考文献 特開平09-073367(JP,A)

特開2012-059265(JP,A)

特開2013-076795(JP,A)

## (58)調査した分野(Int.Cl., DB名)

|         |           |

|---------|-----------|

| G 0 6 F | 3 / 0 4 1 |

| G 0 6 F | 3 / 0 4 4 |

| G 0 2 F | 1 / 1 3 3 |

| G 0 9 F | 9 / 0 0   |

| G 0 9 G | 3 / 2 0   |

| G 0 9 G | 3 / 3 6   |