(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第5096483号

(P5096483)

(45) 発行日 平成24年12月12日(2012.12.12)

(24) 登録日 平成24年9月28日(2012.9.28)

(51) Int.Cl.

H01L 27/146 (2006.01)

H04N 5/374 (2011.01)

F 1

H01L 27/14

H04N 5/335 740

A

請求項の数 3 (全 15 頁)

(21) 出願番号 特願2009-539352 (P2009-539352)

(86) (22) 出願日 平成19年11月30日 (2007.11.30)

(65) 公表番号 特表2010-512004 (P2010-512004A)

(43) 公表日 平成22年4月15日 (2010.4.15)

(86) 國際出願番号 PCT/US2007/024684

(87) 國際公開番号 WO2008/069994

(87) 國際公開日 平成20年6月12日 (2008.6.12)

審査請求日 平成22年11月26日 (2010.11.26)

(31) 優先権主張番号 11/565,801

(32) 優先日 平成18年12月1日 (2006.12.1)

(33) 優先権主張国 米国(US)

(73) 特許権者 510188975

オムニビジョン テクノロジーズ、 イン

コーポレイテッド

アメリカ合衆国 カリフォルニア, サン

タ クララ, バートン ドライブ 42

75

(73) 特許権者 390009531

インターナショナル・ビジネス・マシーン

ズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPO

RATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

最終頁に続く

(54) 【発明の名称】撮像素子トランスファゲートデバイスにおけるシリサイドストラップ

## (57) 【特許請求の範囲】

## 【請求項 1】

第1導電性タイプ材料から成る基板；

該基板上に形成されたゲート誘電体層と、該ゲート誘電体層上に形成されたデュアル仕事関数ゲート導体層とを含むトランスファゲートデバイス、

該デュアル仕事関数ゲート導体層は、第1導電性タイプ材料から成る第1ドープ領域及び第2導電性タイプ材料から成る第2ドープ領域を含む；

入射する光に応答して電荷キャリヤを捕集するための、前記トランスファゲートデバイスの前記第1ドープ領域に隣接する基板表面に又は該基板表面の下側に形成されたフォトセンシングデバイス；

前記トランスファゲートデバイスの前記第2ドープ領域に隣接する前記基板表面に形成された、第2導電性タイプ材料から成る拡散領域、

該トランスファゲートデバイスは、前記フォトセンシングデバイスと前記拡散領域との間の電荷移動を可能にするチャネル領域を形成している；及び

前記トランスファゲートデバイスの第1導電性タイプ材料から成る前記第1ドープ領域と、前記トランスファゲートデバイスの第2導電性タイプ材料から成る前記第2ドープ領域とを電気的にカップリングするための、前記デュアル仕事関数ゲート導体層の最上部に形成されたシリサイド構造

を含んで成るアクティピクセルセンサ(A.P.S.)セル構造であって、

前記シリサイド構造が、面積寸法で、前記デュアル仕事関数ゲート導体層の面積寸法よ

りも小さいアクティブピクセルセンサ(APS)セル構造。

**【請求項2】**

前記APSセル構造が、アクティブピクセルセンサ(APS)セル構造をそれぞれ含んでいる各ピクセルを有するCMOS画像センサのピクセルアレイに含まれ、そして当該CMOS画像センサが、画像捕獲装置に含まれる、請求項1に記載のAPSセル構造。

**【請求項3】**

第1導電性タイプ材料から成る基板を用意すること；

該基板上に形成されたゲート誘電体層及び該ゲート誘電体層上に形成されたデュアル仕事関数ゲート導体層を含むトランスマネーティングゲートデバイスを形成すること、

該デュアル仕事関数ゲート導体層は、第1導電性タイプ材料から成る第1ドープ領域及び第2導電性タイプ材料から成る第2ドープ領域を含む；

前記トランスマネーティングゲートデバイスの前記第1ドープ領域に隣接する基板表面に又は該基板表面の下側に形成された、入射する光に応答して電荷キャリヤを捕集するための、フォトセンシングデバイスを形成すること；

前記トランスマネーティングゲートデバイスの前記第2ドープ領域に隣接する前記基板表面とともに、第2導電性タイプ材料から成る拡散領域を形成すること、

前記トランスマネーティングゲートデバイスは、前記フォトセンシングデバイスと前記拡散領域との間の電荷移動を可能にするチャネル領域を形成する；そして

前記トランスマネーティングゲートデバイスの第1導電性タイプ材料から成る前記第1ドープ領域と、前記トランスマネーティングゲートデバイスの第2導電性タイプ材料から成る前記第2ドープ領域とを電気的にカップリングするための、前記デュアル仕事関数ゲート導体層の最上部にシリサイド構造を形成すること

を含んで成るアクティブピクセルセンサ(APS)セル構造を形成する方法であって、

前記シリサイド構造が、面積寸法で、前記デュアル仕事関数ゲート導体層の面積寸法よりも小さいアクティブピクセルセンサ(APS)セル構造を形成する方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体光学画像センサに関し、特に、低減されたラグ、より高い容量、及びより低い暗電流を示す新規のCMOS(相補型金属酸化膜半導体)画像センサ・セル構造に関する。 30

**【背景技術】**

**【0002】**

CMOS画像センサは、デジタルカメラ、携帯電話機、広範囲なデジタルデバイス、例えばPDA(パーソナル・デジタル・アシスタント)、パーソナル・コンピュータ、医療機器などのような撮像を必要とする用途に対して、コンベンショナルなCCDセンサに取って代わり始めている。CMOS画像センサは、半導体デバイス、例えばフォトダイオードなどのための現行のCMOS製造プロセスを適用することにより、低いコストで製作されるので有利である。さらに、CMOS画像センサは、単一電源によって操作することができるので、そのための消費電力を、CCDセンサよりも低く抑えることができ、そしてさらに、CMOS論理回路及び同様の論理処理デバイスはセンサ・チップ内に容易に集積され、従ってCMOS画像センサを小型化することができる。 40

**【0003】**

現在のCMOS画像センサは、CMOSアクティブピクセルセンサ(Active Pixel Sensor(APS))セル・アレイを含んでおり、これらのセルは、光エネルギーを捕集し、そしてこれを読み取り可能な電気信号に変換するために使用される。各APSセルは、光生成電荷を下側部分に蓄積するための基板のドープされた領域の上に位置する感光性素子、例えばフォトダイオード、フォトゲート、又は光伝導体を含む。各ピクセルセルには読み取り回路が接続されており、この回路はしばしば、読み取り時に感光性素子からの電荷を受容するための拡散領域を含む。典型的には、このことは、浮動拡散領域に電気的に接続

10

20

30

40

50

されたゲートを有するトランジスタデバイスによって達成される。撮像素子は、感光性素子からチャネルを横切って浮動拡散領域へ電荷を移動するための、トランスマッピングゲートを有するトランジスタと、電荷移動前に浮動拡散領域を所定の電荷レベルにリセットするためのトランジスタとを含んでいてもよい。

#### 【0004】

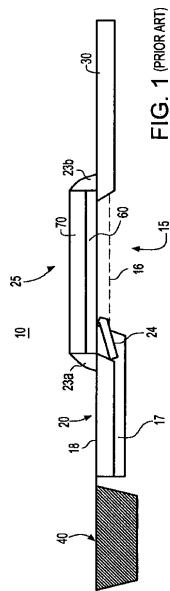

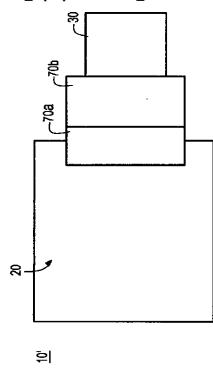

図1に示されているように、典型的なCMOS APSセル10は、ドープp型ピニング層18と、下側の軽度ドープn型領域17とを有するピンド・フォトダイオード20を含む。典型的には、ピンド・ダイオード20は、ダイオード・ピニング層18よりもp型濃度が低いp型基板15又はp型エピタキシャル層又はpウェル表面層の最上部に形成されている。図から明らかなように、表面ドープp型ピニング層18は基板15（又はp型エピタキシャル層又はpウェル表面層）と電気的に接触している。フォトダイオード20はこうして、n型ドープ領域17がピニング電圧（Vp）で完全消耗するように、同じ電位を有する2つのp型領域18及び15を備えている。すなわち、表面ピニング層18は、基板と電気的な接触状態になる。ピンド・フォトダイオードは、フォトダイオードが完全消耗した時にフォトダイオード中の電位が一定の値Vpにピン固定されるので「ピンド（pinned）」と呼ばれる。このピンド・フォトダイオードの形態は、暗電流（暗環境においてピクセルによって出力される電流）を減少させることにより、デバイス性能を改善する。しかし、ピンド・フォトダイオードの形態は、フォトダイオードから浮動ノードへの電荷の不完全な移動による画像ラグを招くおそれがある。

#### 【0005】

図1にさらに示されているように、フォトダイオード20のn型ドープ領域17及びp領域18は、絶縁領域、すなわちシャロートレンチ分離（STI）領域40と、薄型スペーサ構造23a, bによって取り囲まれた電荷移動トランジスタ・ゲート25との間に、所定の間隔を置いて設けられている。シャロートレンチ分離（STI）領域40は、セルを隣接ピクセルセルから分離するために、ピクセル画像セルの近くに配置されている。動作中、ピクセルから来た光は、ダイオードを通じてフォトダイオード上に集束され、ここで、電子がn型領域17に集まる。トランスマッピングゲート25が操作されると、すなわち、例えば薄型誘電体層60上のn型ドープ・ポリシリコン層70を含むトランスマッピングゲート70に電圧を印加することによりオンにされると、光生成電荷24は、電荷を蓄積するドープn型領域17から、トランスマッピングゲート・チャネル16を介して、浮動拡散領域30、例えば浮動「ノード」ドープn+型に移動される。

#### 【0006】

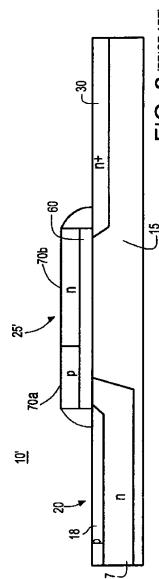

図2はさらに、p型材料部分70aと、n型部分70bとを有するゲート25'が内蔵された別の従来技術CMOS APSセル10'を示している。ゲートのn型部分70bは、より低いVtを有しており、ゲートのp型部分70aはより高いVtを有している。同時にゲート内に存在する両方を有することにより、トランスマッピングゲートは、フォトダイオードから浮動拡散領域へ電子を引き付ける、組み込まれた場を有する。加えて、CMOS APSセル10'の構成において、アレイ内で浮動ノード拡散領域上に形成されたシリサイド（silicide）コンタクト領域（図示せず）の存在が、輝点欠陥漏れの問題を引き起こすことが示されている。すなわち、これらの拡散領域上に形成されたシリサイドコンタクトの追加の存在によって、偶発的なピクセルが、そのピクセルを使用不能にするのに十分な高さのレベルで電流を漏らすシリサイド「スパイク」を被ることが判っている。その結果として、シリサイドは、輝点収率のために、CMOS撮像素子のアレイから除去されている。

#### 【0007】

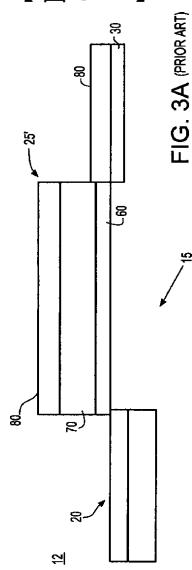

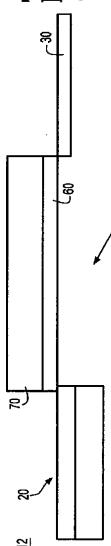

図3Aはシリサイドが光を遮断するため、シリサイド層をフォトダイオード表面から遮断された状態で有するCMOS撮像素子12を示しているが、トランスマッピングゲートポリシリコン及び浮動拡散領域上に形成されたシリサイド層80はそのまま残っている。図3Bは、図3AのCMOS撮像素子12を、漏れ挙動をさらに低くするために、シリサイド層80をゲートポリ及び浮動拡散領域から除去した状態で示している。

10

20

30

40

50

**【0008】**

図3Cは、図2のCMOS撮像素子10'を、シリサイド表面層をフォトダイオード20、ゲートポリ領域70a, 70b及び浮動拡散ノード30から除去した状態で示す頂面図である。

**【0009】**

しかし、残念ながら、n領域及びp領域を有するトランスマッピングゲートを備えた撮像素子からシリサイドを除去すると、ゲート内部の内蔵型ダイオードを有するように形成された各CMOS APSセル・ゲート・ポリシリコンは、ゲート全体がコンタクト形成されるのを妨げる。すなわち、ポリシリコンゲートのn型又はp型にだけ接続するコンタクトは、ゲートポリ層の他方の極性に十分に接続されることはない。このことは、ゲートのコンタクト形成されていない部分に時間依存性の電圧をもたらす。すなわち、ゲートのn型部分に対するコンタクトが形成されると、p型部分が浮動し、同様に、ゲートのp型部分に対するコンタクトが形成されると、n型部分が浮動する。コンタクトが境界エッジ上に直接形成されると、コンタクト・オーバーレイは、コンタクトが統計的に見て一方の側だけに接触することしか許さない。10

**【発明の概要】****【発明が解決しようとする課題】****【0010】**

従って、低減された(低)ラグ及び暗電流を示す新規のAPSセル構造、並びに輝点スパイク漏れ現象を排除する新規のAPSセル構造を含む、CMOS画像センサ・セル構造を提供することが強く望まれる。20

**【課題を解決するための手段】****【0011】**

本発明は概ね、改善された半導体撮像素子に関し、そして具体的には、標準的なCMOS法を用いて製造することができる撮像素子に関する。

**【0012】**

本発明は、CMOS画像センサであって、センサが、光検出領域(例えばフォトダイオード)；浮動拡散領域；光検出領域と浮動拡散領域との間に配置されたトランスマッピングゲート、該トランスマッピングゲートはダイオードを形成するためにn型ドープ領域とp型ドープ領域とを含む；トランスマッピングゲートのn型ドープ領域とp型ドープ領域と電気的にカップリングする相互接続層(例えばシリサイド構造)を含んで成るCMOS画像センサに関する。30

**【0013】**

本発明の1つの態様の場合、相互接続層はシリサイドを含む、ポリシリコントランスマッピングゲートのp型領域の少なくとも一部と、n型領域の少なくとも一部と物理的に接続状態にあるように形成されている。シリサイド層は、ポリゲート幅全体にわたって又はその一部だけに形成されていてよく、またシリサイドは、拡散領域(すなわちフォトダイオード及び浮動拡散領域)上には形成されない。

**【0014】**

好ましくは、2つの仕事関数(n型及びp型ゲートポリ)を有するトランスマッピングゲートデバイスとシリサイドストラップとを含む本発明のCMOS撮像素子は協働して、暗電流に対しては、フォトダイオードに高いバリアを示すのに対して、低いラグ・パフォーマンスに対しては浮動拡散領域に低いバリアが提供される。シリサイドストラップは、ダイオード挙動が、ゲートの一方又は他方の側が不確定電圧に浮動するのを許すのを防止する。40

**【0015】**

このように、本発明の1つの観点によれば、アクティブピクセルセンサ(APS)セル構造、及び製造方法が提供される。アクティブピクセルセンサ(APS)セル構造は、第1導電性タイプ材料から成る基板；

該基板上に形成されたゲート誘電体層と、該ゲート誘電体層上に形成されたデュアル仕事関数ゲート導体層とを含むトランスマッピングゲートデバイス、50

該デュアル仕事関数ゲート導体層は、第1導電性タイプ材料から成る第1ドープ領域及び第2導電性タイプ材料から成る第2ドープ領域を含む；

入射する光に応答して電荷キャリヤを捕集するための、前記トランスマニアゲートデバイスの前記第1ドープ領域に隣接する基板表面に又は該基板表面の下側に形成されたフォトセンシングデバイス；

前記トランスマニアゲートデバイスの前記第2ドープ領域に隣接する前記基板表面に形成された、第2導電性タイプ材料から成る拡散領域、

該トランスマニアゲートデバイスは、前記フォトセンシングデバイスと前記拡散領域との間の電荷移動を可能にするチャネル領域を形成している；及び

前記トランスマニアゲートデバイスの第1導電性タイプ材料から成る前記第1ドープ領域と、前記トランスマニアゲートデバイスの第2導電性タイプ材料から成る前記第2ドープ領域とを電気的にカップリングするための、前記デュアル仕事関数ゲート導体層の最上部に形成されたシリサイド構造

を含んで成る。

#### 【0016】

1つの態様の場合、フォトセンシングデバイスは、基板表面の下側に形成された第2導電性タイプ材料から成る捕集ウェル；及び基板表面に捕集ウェルの最上部に形成された第1導電性タイプ材料から成るピニング層を含むフォトダイオードを含む。

#### 【0017】

1つの態様の場合、基板、第1導電性タイプ材料から成るピニング層、及びトランスマニアゲートデバイスのデュアル仕事関数ゲート導体層の第1ドープ領域が、p型ドーパント材料、例えばホウ素又はインジウムを含む。第2導電性タイプ材料から成る捕集ウェル、第2導電性タイプ材料から成る拡散領域、及びトランスマニアゲートのデュアル仕事関数ゲート導体層の第2ドープ領域が、n型ドーパント材料、例えばリン、ヒ素、又はアンチモンを含む。

#### 【0018】

さらに、シリサイド構造は、Ti、Ta、W、Co、Ni、Pt、Pd、又はこれらの合金のシリサイドを含む。

#### 【0019】

1つの態様の場合、トランスマニアゲートデバイスの第1導電性タイプ材料から成る第1ドープ領域と、第2導電性タイプ材料から成る第2ドープ領域とを電気的にカップリングするための、デュアル仕事関数ゲート導体層の上に形成された前記シリサイド構造は、面積寸法で、デュアル仕事関数ゲート導体層の面積寸法よりも小さい。

#### 【0020】

或いは、トランスマニアゲートデバイスの第1導電性タイプ材料から成る第1ドープ領域と、第2導電性タイプ材料から成る第2ドープ領域とを電気的にカップリングするための、デュアル仕事関数ゲート導体層の上に形成されたシリサイド構造は、長さ寸法で、デュアル仕事関数ゲート導体層の長さ寸法よりも小さい。

#### 【0021】

トランスマニアゲートデバイスが、トランスマニアゲートデバイスの下側の捕集ウェルと浮動拡散領域との間で電荷移動が可能にされる導電チャネル領域を画定する状況において、さらに別の態様では、シリサイド構造は、導電チャネル領域を画定する領域の外側で、トランスマニアゲートデバイスの第1導電性タイプ材料から成る第1ドープ領域と、第2導電性タイプ材料から成る第2ドープ領域とを電気的にカップリングするために、デュアル仕事関数ゲート導体層の最上部に形成されている。

#### 【0022】

有利には、本発明の教示内容は、両極性のデバイス、すなわちn型フォトダイオード及びp型ピニング層及びnFET、並びにp型フォトダイオード、及びpFETを有するn型ピニング層に適用することができる。

#### 【0023】

10

20

30

40

50

本発明の目的、特徴、及び利点は、添付の図面と組み合わせて下記詳細な説明を参照すれば当業者に明らかである。

**【図面の簡単な説明】**

**【0024】**

【図1】図1は、従来技術による画像センサのためのCMOSアクティピクセルセンサ(APS)セル10を示す図である。

【図2】図2は、内蔵型ダイオード、例えばpn接合を備えたゲートポリシリコン層を有する、従来技術によるCMOSアクティピクセルセンサ(APS)セル10'を示す断面図である。

【図3A】図3Aは、従来技術によるCMOSアクティピクセルセンサ(APS)セル12を、シリサイドコンタクト領域をフォトダイオードから除去した状態で示す断面図である。

10

【図3B】図3Bは、従来技術によるCMOSアクティピクセルセンサ(APS)セル12を、シリサイド表面層コンタクト領域をゲートポリ層及び浮動拡散層から除去した状態で示す断面図である。

【図3C】図3Cは、図2のCMOS撮像素子10'を、シリサイド表面層を、フォトダイオード20、ゲートポリ領域70a, 70b、及び浮動拡散ノード30から除去した状態で示す頂面図である。

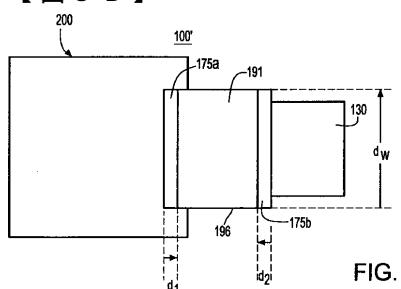

【図4】図4は、シリサイドコンタクト領域をフォトダイオード及び浮動ノード拡散領域から除去し、そしてゲート・バリアac特性を改善するためにゲートポリシリコン上に部分導電性ストラップを形成する、本発明の第1の態様によるCMOS APSセル100を示す断面図である。

20

【図5A】図5Aは、図4に示された本発明の態様に従って形成されたCMOS APSセル100を示す頂面図である。

【図5B】図5Bは、図4に示された本発明の態様の第1変更形に従って形成されたCMOS APSセル100'を示す頂面図である。

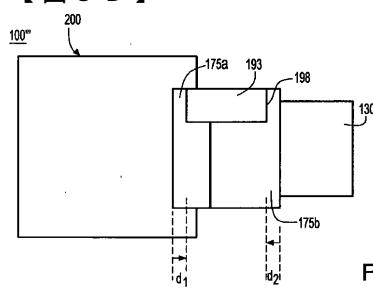

【図5C】図5Cは、図4に示された本発明の態様の第2変更形に従って形成されたCMOS APSセル100''を示す頂面図である。

【図5D】図5Dは、図4に示された本発明の態様の第3変更形に従って形成されたCMOS APSセル100'''を示す頂面図である。

30

【図6】図6は、本発明に従って形成されたCMOSアクティピクセルセンサ(APS)セルを有する画像センサを実現するカメラデバイスを示す側面図である。

**【発明を実施するための形態】**

**【0025】**

本発明を詳細に説明する前に、念のために述べておきたいのは、本発明は、好ましくは、CMOSアクティピクセルセンサに使用されるが、しかしこれには限定されないことがある。アクティピクセルセンサ(APS)は、スイッチとして機能するトランジスタ以外の、ピクセル内部のアクティピ電気素子を意味する。例えば浮動拡散領域又は増幅器は、アクティピ素子である。CMOSは、相補型金属酸化膜シリコン・タイプの電気素子、例えばトランジスタを意味する。これらのトランジスタは、ピクセルと連携するが、しかし典型的にはピクセル内にはなく、またトランジスタのソース/ドレインが1つのドーパント・タイプを有し、且つその相手となるトランジスタが対向ドーパント・タイプを有すると形成される。CMOSデバイスはいくつかの利点を有しており、そのうちの1つは消費電力が少ないとある。

**【0026】**

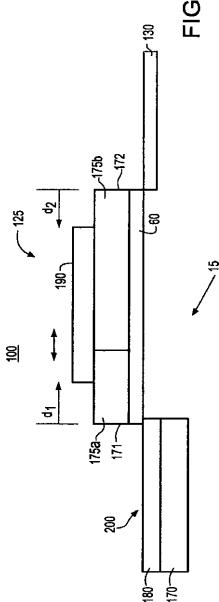

図4は、フォトセンシングデバイス、例えばフォトダイオード200、及びシリコン含有トランスマニッシュゲート、例えばポリシリコントランスマニッシュゲート125を含む、本発明の第1態様によるラインCMOS撮像素子APS100の後端部を示す断面図である。ポリシリコントランスマニッシュゲート125は、ダイオードを形成する、アノード(p型ドープ)領域と、隣接するカソード領域(n型ドープ)領域とを含んでいる。1つの非限定的な例

40

50

において、ポリシリコントラ ns ファゲート 125 はショットキーダイオードを含む。さらに、図 4 に示されているように、本明細書中で以下により詳細に説明するようなゲート・バリア a c 特性を改善するために、p 型部分 175a と n 型部分 175b とを有するポリゲートの表面上に、導電性構造、例えば部分シリサイド「ストラップ」190 が形成されている。

#### 【0027】

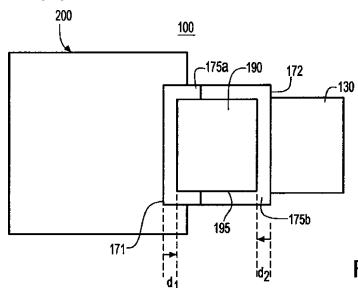

図 4 に示されているように、部分シリサイドストラップ層 190 は、ポリシリコンゲート 125 の p 型ドープ部分 175a と n 型ドープ部分 175b とを電気的に接続する。さらに、図 4 に示されているように、部分シリサイド「ストラップ」190 は、ゲートの境界から所定の距離を置いて形成されたエッジを有している。すなわち、シリサイドストラップ 190 は、ポリゲート層の各エッジ 171, 172 から所定の距離、例えば距離  $d_1$  及び  $d_2$  だけ内方に設けられている。形成される部分シリサイドストラップの、内方へ引き込まれた距離  $d_1$  及び  $d_2$  は、等しい必要はない。すなわち、シリサイドストラップ 190 が p 型部分 175a から n 型部分 175b へ電気的に短絡する限り、ストラップは、ポリ幅の一部だけに被さるように形成される。こうして、図 5A の頂面図に示すように、シリサイドストラップ 190 は、ポリ幅の一部の最上部に形成されている。好ましい態様では、シリサイドストラップ 190 は、拡散領域 130 から離れた状態で形成されることは明らかである。

#### 【0028】

図示はしていないが、図 4 に示された CMOS 撮像素子 APS100 構造の製造方法の一例をここで説明する。言うまでもなく、ダイオード構造、当業者に知られているような隣接する p 型及び n 型のゲートポリシリコン領域を有するトランスマゲートを形成するために、他の技術を用いることもできる。デバイス 100 は基板 15 上に形成され、基板 15 は、例えば Si、SiGe、SiC、SiGeC、GaAs、InP、InAs 及びその他の半導体を含むバルク半導体であってよく、或いは、層状半導体、例えばシリコン・オン・インシュレータ (SOI)、SiC・オン・インシュレータ (SiCOI)、又はシリコンゲルマニウム・オン・インシュレータ (SGOI) であってもよい。説明のため、基板 15 は、例えばホウ素又はインジウム (III-V 半導体の場合にはベリリウム又はマグネシウム) のような p 型ドーパント材料で、例えば  $1 \times 10^{14} \sim 1 \times 10^{16} \text{ cm}^{-3}$  まで軽度ドープされた第 1 導電性タイプの Si 含有半導体基板である。次いで、基板 15 上に、標準的な堆積 / 成長技術によって誘電体材料層 60 を形成し、これは最終的なトランスマゲート誘電体を形成することになる。誘電体層は、例えば厚さ 40 ~ 100

に形成されてよく、好適なゲート誘電体材料、例えば酸化物 (例えば  $\text{SiO}_2$ )、窒化物 (例えば窒化ケイ素)、酸窒化物 (例えば酸窒化 Si)、 $\text{N}_2\text{O}$ 、NO、 $\text{ZrO}_2$ 、又はその他の同様の材料を含んでよい。1つの態様において、ゲート誘電体 60 は、酸化物、例えば  $\text{SiO}_2$ 、 $\text{HfO}_2$ 、 $\text{ZrO}_2$ 、 $\text{Al}_2\text{O}_3$ 、 $\text{TiO}_2$ 、 $\text{La}_2\text{O}_3$ 、 $\text{SrTiO}_3$ 、 $\text{LaAlO}_3$ 、及びこれらの混合物から成る。誘電体層 60 は、コンベンショナルな熱酸化を用いて、又は好適な堆積法、例えば化学蒸着、プラズマ支援化学蒸着、原子層堆積 (ALD)、蒸発、反応性スパッタリング、化学溶液堆積、及びその他の同様の堆積法によって、Si 含有半導体基板 15 の表面上に形成される。ゲート誘電体 16 は、上記方法の任意の組み合わせを利用して形成されてもよい。図示はしないが、誘電体層は、誘電体材料のスタックを含んでもよいことは明らかである。

#### 【0029】

次いで、コンベンショナルな堆積法、例えば CVD、プラズマ支援 CVD、スパッタリング、めっき、蒸発、及びその他の同様の堆積法 (例えば低圧 CVD) を用いて、誘電体層 60 上に、シリコン含有層、例えば多結晶シリコンを形成する。ポリシリコン層は、約 1k ~ 2k の厚さに形成されてよいが、しかしこの範囲から外れていてもよい。或いは、シリコン含有層は、ポリシリコン層のスタックを含んでもよい。次いで、フォトリソグラフィ法、例えばマスク、例えばフォトレジスト層をポリシリコン層上に適用し、そして例えば、形成されるべきトランスマゲートの有効チャネル長を決定する長さにわたつ

10

20

30

40

50

て、ゲート領域を画定するようにパターン化されたマスクを適用し、次いでレジストを現像し、そしてエッチング法を実施することにより、トランスマスク内に形成する。基本的には、エッチング窓がレジストマスク内に設けられており、そのサイズ及び形状が、形成されるべきゲート領域の横方向のサイズ及び形状をほぼ画定する。次いで、ポリシリコン層及び誘電体層 60 又は誘電体層スタックの適正なエッチングを保証するように最適化された 1 種又は 2 種以上のエッチング法、例えば反応性イオン・エッチング (RIE) 法を実施することにより、トランスマスク構造をもたらす。

#### 【 0030 】

ゲート誘電体層上に固有のポリシリコン層を含むトランスマスク構造を形成した後、トランスマスク構造の一部を覆う後続のマスク堆積法、及びイオン注入法を実施することにより、第 2 導電性タイプから成るドーパント材料、例えば n 型ドーパント材料（例えばリン、ヒ素又はアンチモン）をポリシリコン層内に注入することにより、n 型ドープ・ゲート・ポリシリコン部分 175b を形成する。n 型ドーパント材料は、 $1 \times 10^{17} \text{ cm}^{-3}$  ~  $1 \times 10^{20} \text{ cm}^{-3}$  の添加濃度を達成するように注入されてよい。同様に、残りの部分、すなわちトランスマスク構造の他方の側を覆う後続のマスク堆積法を用いて、イオン注入法を実施することにより、第 1 導電性タイプから成るドーパント材料、例えば p 型ドーパント材料（例えばホウ素又はガリウム又はインジウム）をポリシリコン層内に注入することにより、図 4 に示された p 型ドープ・ゲート・ポリシリコン部分 175a を形成する。p 型ドーパント材料は、ゲートボリ中、 $1 \times 10^{17} \text{ cm}^{-3}$  ~  $1 \times 10^{20} \text{ cm}^{-3}$  の添加濃度を達成するように注入されてよい。或いは、ポリシリコンのドープは、プロセス中に既に存在する注入物を使用して、これらの注入物マスクを適正に使用することによって達成することもでき、同時に、これらの注入はチップ内の他の場所で実施される（一例としてソース・ドレイン注入物及びマスクが挙げられるが、他のものの可能である）。 10

#### 【 0031 】

なお、上記方法の変更形において、現場でドーピングされた n 型、p 型、又は n 型及び p 型両方のポリシリコン材料を、現場ドーピング堆積法又は堆積（例えば CVD、プラズマ支援など）に従って、ゲート誘電体層 60 の最上部に堆積することができる。現場ドープ堆積法は、例えば、ゲート誘電体が後続の高温アニーリングに耐えられないときに採用することができるのに対して、イオン注入及びアニールは、ゲート誘電体がこのような高温アニーリングに耐えられる材料であるときに採用することができる。 20

#### 【 0032 】

追加の任意選択の工程において、当業者によく知られているコンベンショナルな堆積法によって、トランスマスクのいずれかの側にゲート側壁スペース（図示せず）を形成することでき、ゲート側壁スペースは、任意のコンベンショナルな酸化物又は窒化物（例えば Si<sub>3</sub>N<sub>4</sub>）又は酸化物 / 窒化物を含んでよく、これらは次いで、RIE 又は別の同様のエッチング法によってエッチングされる。スペースの厚さは種々様々であってよいが、しかし典型的にはこれらの厚さは約 5 nm ~ 約 150 nm である。 30

#### 【 0033 】

トランスマスク側壁スペースを任意選択的に形成した後、フォトダイオード・ピニング領域 180 を提供するために、次の工程を実施する。この工程は、フォトレジスト層（図示せず）パターンを形成し、そしてゲートエッジとほぼ一致する、又はできる限り精密な整合許容誤差が与えられるマスク・エッジを形成するための当業者に知られた技術に従ってイオン注入マスクを作成することにより、ゲートのエッジと、形成された絶縁領域、例えば STI 領域（図示せず）との間の区域に開口を設ける。この開口に、フォトダイオードの電荷蓄積領域が形成されるようになっている。この開口は、図 4 に示された p 型ドーパント・ピニング領域 180 を形成するのに十分な濃度で、p 型ドーパント材料、例えばホウ素から成るイオンを注入するのを可能にする。このピニング領域 180 は、スペース（図示せず）のエッジまで形成されてよい。活性 p 型ドーパント材料は、次いで  $1 \times 10^{17}$  ~  $1 \times 10^{19} \text{ cm}^{-3}$  の添加濃度でイオン注入される。或いは言うまでもなく、p 型ピニング・フォトダイオード表面層 180 は、他の良く知られている技術によって形成す 40

ることもできる。例えば p 型表面層 180 は、ガス源プラズマ・ドープ法によって、フォトダイオードが形成されるべき領域全体にわたって堆積された現場ドープ層又はドープ酸化物層から p 型ドーパントを拡散することにより形成されてよい。

#### 【 0034 】

フォトダイオード素子 200 の基板表面の p 型ドープ領域 180 の下側に、n 型ドーパントをイオン注入するために、更なる工程を実施する。潜在的には、ピニング領域を形成するために p 型材料を注入したときと同じイオン注入マスクを使用することもでき、第 2 導電性タイプから成るドーパント材料、例えば n 型ドーパント材料（例えばリン、ヒ素又はアンチモン）を注入するために、イオン注入法を実施することにより、イオン注入された p 型ピニング層 180 の下側に電荷捕集層を形成する。図 4 に示されたフォトダイオード 190 の n 型ドープ領域 170 を形成するために、n 型ドーパント材料は、より高いエネルギーレベルで注入される。活性 n 型ドーパント材料は、 $1 \times 10^{16} \sim 1 \times 10^{18} \text{ cm}^{-3}$  の添加濃度でイオン注入されてよい。図 4 に示されているように、光生成電子を捕集するための感光性電荷貯蔵領域 170 は、n 型領域 170 のプロフィールを調整するために複数の注入物によって形成されてよい。10

#### 【 0035 】

フォトダイオード 200 の形成に加えて、トランスマスクの他方の側に n 型浮動拡散領域 130 を形成する追加の工程が行われる。この工程は、フォトレジスト層を形成し、そしてゲートエッジとほぼ一致する、又はできる限り精密な整合許容誤差が与えられるマスク・エッジを形成するための当業者に知られた技術に従ってイオン注入マスクをパターン化してエッチングすることにより、図 4 に示されているような、又はゲート側壁スペーサ（図示せず）のエッジまでの n+ 型ドープ浮動拡散領域を形成するのに十分な濃度で、n 型ドーパント材料、例えばリン、ヒ素又はアンチモンの注入を可能にする開口を提供することを含む。活性 n+ 型ドーパント材料は、次いで  $1 \times 10^{18} \sim 1 \times 10^{20}$  の添加濃度で、浮動拡散領域にイオン注入される。このイオン注入工程の結果として、n 型ドーパント材料は加えて、ドープトランスマスクゲートポリシリコン層 175b 部分にも注入されてもよい。20

#### 【 0036 】

図 5A ~ 5D に示すように、ポリシリコンゲート 125 を消費することにより、本発明による金属シリサイドストラップ 190 を形成するために、シリサイド法を実施する。30

#### 【 0037 】

シリサイド法の第 1 工程は、よく知られた堆積技術を用いて、p 型ドープ・ポリシリコン・ゲート層 175a 及び n 型ドープ・ポリシリコン・ゲート層 175b 上に、プランケット絶縁キャップを先ず形成することを含む。例えば、ポリシリコンゲート層 175a, b 上に、堆積法、物理蒸着又は化学蒸着を利用して、誘電体キャップ層を形成する。誘電キャップ層は、酸化物、窒化物、酸窒化物又はこれらの任意の組み合わせであってよい。1 つの態様の場合、窒化物、例えば Si<sub>3</sub>N<sub>4</sub> が、誘電体キャップ層として採用される。誘電体キャップ層の厚さ、すなわち高さは約 20 nm ~ 約 180 nm であってよい。

#### 【 0038 】

次いで、典型的なリソグラフィ工程、すなわち、キャップ（例えば窒化物）誘電体層上にパターン化レジストマスクを形成する工程を用いて、形成されるべきシリサイドストラップの輪郭となる領域をエッチングする。リソグラフィ工程は、誘電体キャップ層の上面にフォトレジストを適用し、このフォトレジストを、所望のパターンの輻射線に当て、そしてコンベンショナルなレジスト現像剤を利用して露光されたフォトレジストを現像することを含む。フォトレジスト内のパターンは、1 つ又は 2 つ以上の乾式エッチング工程を利用して、誘電体キャップ層に転写され、下に位置するポリシリコンゲート層を露出したままにし、そして特に、露出された下に位置するポリシリコン層内の両ドープ領域 175a, b の隣接部分を露出させるように、誘電体キャップ層に窓を開ける。本発明によれば、所望されるパターンは、図 5A ~ 5D に示すように、形成されるべきシリサイドストラップの面積及び寸法である。こうして、例えば図 5A に示された本発明の頂面図に示すよ4050

うに、上に位置するキャップ誘電体（窒化物）層（図示せず）に適用されるフォトグラフィ・マスク、現像及びエッチング法は結果として、ゲートの長さに沿って各ゲートエッジ 171, 172 のそれぞれから距離  $d_1$  及び  $d_2$  だけ内方に設けられた下に位置するポリシリコン層の露出領域 195 が生じる。この露出領域には、シリサイドコンタクトが形成されることになる。いくつかの態様の場合、パターン化フォトレジストは、パターンが誘電体キャップ層が誘電体キャップ層内に転写された後、除去されてよい。

#### 【0039】

パターン化ゲートを形成する際に本発明において用いることができる好適な乾式乾燥エッチング法の一例としては、反応性イオン・エッチング、イオンビーム・エッチング、プラズマ・エッチング又はレーザーアブレーションが挙げられる。

10

#### 【0040】

次いで、エッチングによりパターン化された窒化物層内に金属シリサイド（図示せず）を堆積する工程が実施されるので、露出された下に位置するポリシリコン層には、金属シリサイドが充填されるようになる。シリサイドストラップを形成する上で使用される金属は、金属シリサイドを形成するようにシリコンと反応することができる任意の金属を含む。このような金属の一例としては、Ti、Ta、W、Co、Mo、Ni、Pt、Pd 又はこれらの金属が挙げられる。金属は、例えばスパッタリング、化学蒸着、シリサイド蒸発の物理蒸着（PVD）、化学溶液堆積、及びめっきなどを含む任意のコンベンショナルな堆積法を用いて堆積されてよい。

#### 【0041】

20

シリサイドストラップ 190 の寸法を定義する露出ポリシリコン領域上に金属シリサイドを堆積した後、構造内にシリサイド相、好ましくは金属シリサイドの最低抵抗率相を示すシリサイドを形成するために、熱アニール法が採用される。アニールは、図 4 に示された金属シリサイド層 190 を形成するために金属シリサイドが下に位置するポリシリコンと反応するようにする、当業者によく知られた環境及び温度を利用して実施される。1つの態様の場合、金属シリサイドは Co、特に当業者に良く知られた2工程アニール法を用いる CoSi<sub>2</sub> 形態を含んでよい。本発明の別の態様の場合、金属シリサイドは Ni 又は Pt であり、NiSi 及び PtSi は單一アニール工程を用いて形成される。次いで、構造から非反応性金属シリサイドを除去するために、選択的な湿式エッチング工程を採用することができる。

30

#### 【0042】

1つの態様において、ウエハーを次いで、ポリシリコン層部分 175a, b と反応するための窒素環境中でほぼ 30 秒にわたって約 500 ~ 約 800 でアニールすることにより、導電性シリサイドストラップ 190 を形成する。

#### 【0043】

上述の本発明による金属シリサイドゲート処理が完了した後、トランジスタ間、及びトランジスタと外部コンタクトとの相互接続構造を形成するためのコンベンショナルな処置を採用することができる。

#### 【0044】

図 5B は、図 5A に示した本発明の態様の第 1 変更形に従って形成された CMOS A PS セル 100' を示す頂面図である。ここでは、本明細書中に記載された方法を用いてシリサイドストラップ 191 が形成され、このシリサイドストラップ 191 は、境界ゲートのエッジから距離  $d_1$  及び  $d_2$  だけ内方に形成されたエッジを有しているが、しかしポリシリコンのほぼ全幅にわたって延びるように形成されている。このように、例えば、図 5A に関して本明細書中に説明したサリサイド法を参照すると、図 5B に示すように、上に位置するキャップ誘電体（窒化物）層（図示せず）に適用されるフォトグラフィ・マスク、現像及びエッチング法は結果として、例えば、ゲートの長さに沿って各ゲートエッジ 171, 172 のそれぞれから距離  $d_1$  及び  $d_2$  だけ内方に設けられるが、しかしポリ層の両エッジまでほぼ全幅にわたって距離  $d_w$  だけ延びる下に位置するポリシリコン層の露出領域 196 が形成されることになる。

40

50

## 【0045】

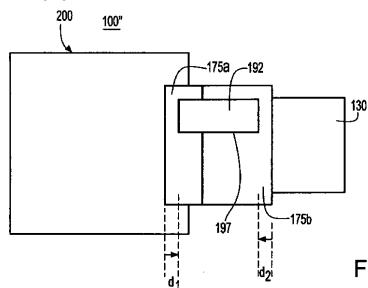

図5Cは、図5Aに示した本発明の態様の第2変更形に従って形成されたCMOSAPSセル100''を示す頂面図である。ここでは、本明細書中に記載された方法を用いてシリサイドストラップ192が形成され、このシリサイドストラップ192は、境界ゲートのエッジから距離d<sub>1</sub>及びd<sub>2</sub>だけ内方に形成されたエッジを有しているが、しかしポリゲートの短い距離にわたって延びるように形成されている。このように、例えば、図5Aに関して本明細書中に説明したシリサイド法を参照すると、図5Cに示すように、上に位置するキャップ誘電体(窒化物)層(図示せず)に適用されるフォトグラフィ・マスク、現像及びエッチング法は結果として、例えば、ゲートの長さに沿って各ゲートエッジ171, 172のそれから距離d<sub>1</sub>及びd<sub>2</sub>だけ内方に設けられるが、しかしポリゲートの短い距離だけにわたって延びる下に位置するポリシリコン層の露出領域197が形成されることになる。10

## 【0046】

本発明の更なる態様によれば、CMOS撮像素子APSトランスマゲートのためのシリサイドストラップは、導電チャネル上に直接には位置していないポリシリコンゲート部分上に形成することができる(すなわちn領域とn領域とが、或る場所のストラップによって短絡される限り)。図5Dは、図5Aに示した本発明の態様の第3変更形に従って形成されたCMOSAPSセル100'''を示す頂面図である。ここでは、本明細書中に記載された方法を用いてシリサイドストラップ193が形成され、このシリサイドストラップ193は、境界ゲートのエッジから所定の距離だけ内方に形成されたエッジを有しており、しかもポリゲートの短い距離にわたって延びるように形成されている。しかしながら、このストラップ193は、トランスマデバイスのためのチャネル領域を画定するそのゲート部分175a, bから、ずらされている。すなわち、シリサイドストラップ193は、導電チャネル上に直接には位置していないポリシリコンゲート部分上に形成することができる。このように、例えば、図5Aに関して本明細書中に説明したシリサイド法を参考すると、図5Dに示すように、上に位置するキャップ誘電体(窒化物)層(図示せず)に適用されるフォトグラフィ・マスク、現像及びエッチング法は結果として、ゲートの長さに沿って各ゲートエッジ171, 172のそれから所定の距離だけ内方に設けられ、しかも、例えばデバイスのチャネル領域に直接には被さらない領域内で、ポリゲートの短い距離だけにわたって延びる下に位置するポリシリコン層の露出領域198が形成されることになる。2030

## 【0047】

言うまでもなく、上記シリサイドコンタクト構造以外に、トランスマゲートポリのアノード部分175aとカソード部分175bとを電気的に短絡するためのいずれの導電性構造をも実現することもできる。しかし、光検出領域と浮動拡散領域とがシリサイド非含有であることは必須である。

## 【0048】

図5A～5Dに示し、これらの図面に関して説明した構造の利点は、暗電流漏れを低減するために、フォトダイオードに高いバリアが存在すること、及び、より低いラグのために、浮動拡散領域に低いバリアが存在することである。シリサイドストラップは、ダイオード拳動が、ゲートの一方又は他方の側が中間電圧まで浮動するのを許すのを防止する。40

## 【0049】

図6を参照すると、図5A～5Dに示された本発明のそれぞれの態様に従って形成されたCMOSアクティブピクセルセンサ(APS)セル100～100'''を有する画像センサ302を実現するカメラデバイス300の側面図が示されている。

## 【0050】

本発明の好ましい態様と考えられるものを図示して説明してきたが、もちろん、本発明の思想を逸脱することなしに、形態又は詳細の種々の改変及び変更を容易に加え得ることは明らかである。例えば、本明細書中に記載された好ましい態様は、n型フォトダイオード及びp型ピニング層及びnFETに向けられているが、本発明の原理をp型フォトダイ50

オード、及びpFETを有するn型ピニング層に適用することができる。従って、本発明は、記述・例示された形態そのままのものに限定されるものではなく、添付の特許請求の範囲の中に含まれる全ての改変形に及ぶものと解釈されるべきである。

【図1】

FIG. 1 (PRIOR ART)

【図2】

FIG. 2 (PRIOR ART)

【図3A】

FIG. 3A (PRIOR ART)

【図3B】

FIG. 3B (PRIOR ART)

【図3C】

FIG. 3C

(PRIOR ART)

【図4】

FIG. 4

【図 5 A】

FIG. 5A

【図 5 C】

FIG. 5C

【図 5 B】

FIG. 5B

【図 5 D】

FIG. 5D

【図 6】

FIG. 6

---

フロントページの続き

(74)代理人 100099759

弁理士 青木 篤

(74)代理人 100077517

弁理士 石田 敬

(74)代理人 100087413

弁理士 古賀 哲次

(74)代理人 100102990

弁理士 小林 良博

(74)代理人 100128495

弁理士 出野 知

(74)代理人 100093665

弁理士 蛭谷 厚志

(72)発明者 アドキッソン, ジェイムズ ダブリュ .

アメリカ合衆国, バーモント 05465, ジェリコ, フィールズ レーン 55

(72)発明者 エリス-モナハン, ジョン ジエイ .

アメリカ合衆国, バーモント 05458, グランド アイル, メイナード コート シックス

(72)発明者 ガイダシュ, ロバート マイケル

アメリカ合衆国, ニューヨーク 14618, ロチェスター, アントラーズ ドライブ 460

(72)発明者 ジャッフェ, マーク ディー .

アメリカ合衆国, バーモント 05482, シエルバーン, ガバナーズ レーン 447

(72)発明者 ネルソン, エドワード ティー .

アメリカ合衆国, ニューヨーク 14534, ピッツフォード, ブルック ロード 59

(72)発明者 ラッセル, リチャード ジエイ .

アメリカ合衆国, バーモント 05446, コルチェスター, グラニット クリーク ロード 2

25

(72)発明者 スタンキャンピアーノ, チャールズ ブイ .

アメリカ合衆国, ニューヨーク 14618, ロチェスター, オークデール ドライブ 175

審査官 橋 均憲

(56)参考文献 米国特許出願公開第2006/0118835(US, A1)

米国特許出願公開第2006/0124976(US, A1)

国際公開第2005/004240(WO, A1)

特開平11-274320(JP, A)

特開平5-183117(JP, A)

特開2005-260077(JP, A)

特開2008-78489(JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H04N 5/374

H01L 21/8238

H01L 27/092