#### US00RE46013E

## (19) United States

## (12) Reissued Patent

Selinger et al.

### (10) Patent Number: US RE46,013 E

(45) Date of Reissued Patent: May 24, 2016

# (54) METHOD AND CONTROLLER FOR PERFORMING A COPY-BACK OPERATION

(71) Applicant: SanDisk Technologies Inc., Plano, TX

(US)

(72) Inventors: Robert D Selinger, San Jose, CA (US);

Gary Lin, San Jose, CA (US); Paul Lassa, Cupertino, CA (US); Chaoyang Wang, Cupertino, CA (US)

(73) Assignee: SanDisk Technologies Inc., Plano, TX

(US)

(21) Appl. No.: 14/243,637

(22) Filed: Apr. 2, 2014

### Related U.S. Patent Documents

### Reissue of:

(64) Patent No.: **8,443,263**Issued: **May 14, 2013**Appl. No.: **12/650,263**Filed: **Dec. 30, 2009**

(51) Int. Cl.

G06F 11/00

(2006.01)

G06F 11/10

(2006.01)

G06F 7/00

(2006.01)

(52) U.S. Cl.

CPC ...... *G06F 11/1068* (2013.01); *G06F 11/1016* (2013.01)

### (58) Field of Classification Search

### (56) References Cited

### U.S. PATENT DOCUMENTS

### FOREIGN PATENT DOCUMENTS

EP 1 146 428 10/2001 WO WO 2005/066773 7/2005 (Continued)

### OTHER PUBLICATIONS

Arya, P., "A Survey of 3D Nand Flash Memory", *EECS Int'l Graduate Program, National Chiao Tung University*, 2012, pp. 1-11. (Continued)

Primary Examiner — Samuel Rimell (74) Attorney, Agent, or Firm — Brinks Gilson & Lione

### (57) ABSTRACT

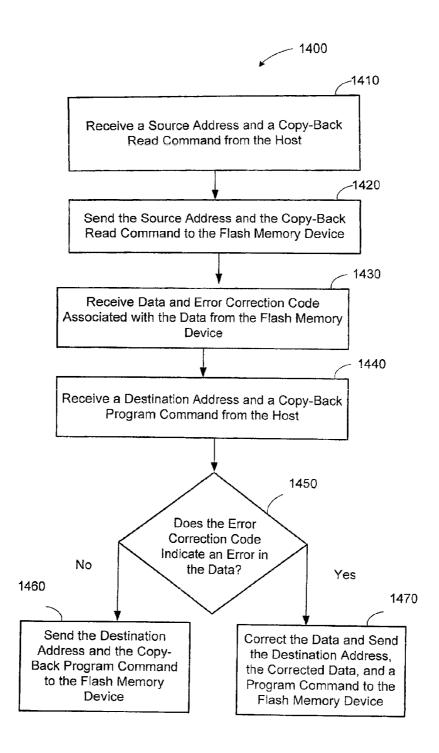

The embodiments described herein provide a method and controller for performing a copy-back command. In one embodiment, a controller receives the data and error correction code associated with a copy-back operation from at least one flash memory device. The controller determines if the error correction code indicates there is an error in the data. If the error correction code does not indicate there is an error in the data, the controller sends a destination address and copyback program command received from a host to the at least one flash memory device. If the error correction code indicates there is an error in the data, the controller corrects the data and sends the destination address, the corrected data, and a program command to the at least one flash memory device. Additional embodiments relate to modifying data during the copy-back operation.

### 37 Claims, 19 Drawing Sheets

### US RE46,013 E

Page 2

| (56) | References Cited     |    |                  |                                      |                                                                    | ,429,330                                                                                                                               |         |                             | Wan et al.                                                   |  |

|------|----------------------|----|------------------|--------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------|--------------------------------------------------------------|--|

|      | U.S. PATENT          |    |                  | DOCUMENTS                            | 8,                                                                 | ,443,263<br>,595,411<br>,732,553                                                                                                       | B2      | 5/2013<br>11/2013<br>5/2014 | Selinger et al.<br>Selinger et al.<br>Nagadomi et al 714/768 |  |

| 5.   | ,937,425             | Α  | 8/1999           | Ban                                  |                                                                    | 0028523                                                                                                                                |         |                             | Moro et al.                                                  |  |

|      | ,943,283             |    |                  | Wong et al.                          |                                                                    | 0028704                                                                                                                                |         |                             | Mukaida et al.                                               |  |

|      | ,034,882             |    |                  | Johnson et al.                       |                                                                    | 0051118<br>0065899                                                                                                                     |         |                             | Wu et al.<br>Gorobets                                        |  |

|      | ,119,245             |    |                  | Hiratsuka<br>Gangwar                 |                                                                    | 0079077                                                                                                                                |         |                             | Piau et al.                                                  |  |

|      | ,181,599<br>,185,122 |    |                  | Gongwer Johnson et al.               |                                                                    | 0097520                                                                                                                                |         |                             | Lai et al.                                                   |  |

|      | ,230,233             |    |                  | Lofgren et al.                       |                                                                    | 0099134                                                                                                                                |         |                             | Lasser et al.                                                |  |

|      | ,266,273             |    |                  | Conley et al.                        |                                                                    | 0135688                                                                                                                                |         | 7/2003                      | Tai<br>Tang et al.                                           |  |

|      | ,317,799             |    |                  | Futral et al.                        |                                                                    | 0206442<br>0229645                                                                                                                     |         |                             | Mogi et al.                                                  |  |

|      | ,420,215<br>,426,893 |    |                  | Knall et al.<br>Conley et al.        |                                                                    | 0103234                                                                                                                                |         |                             | Zer et al.                                                   |  |

|      | ,498,851             |    | 12/2002          |                                      |                                                                    |                                                                                                                                        |         |                             | Sakaue et al 714/52                                          |  |

| 6,   | ,591,330             | B2 | 7/2003           | Lasser                               |                                                                    | 0005055                                                                                                                                |         |                             | Pasotti et al.                                               |  |

|      | ,594,183             |    |                  | Lofgren et al.                       |                                                                    | 0050235<br>0055479                                                                                                                     |         | 3/2005                      | Zer et al.                                                   |  |

|      | ,624,773<br>,631,085 |    | 9/2003           | Wong<br>Kleveland et al.             |                                                                    | 0092846                                                                                                                                |         |                             | Lai et al.                                                   |  |

|      | ,683,817             |    |                  | Wei et al.                           |                                                                    | 0125630                                                                                                                                |         |                             | Liao et al 712/5                                             |  |

| 6,   | ,694,415             | B2 |                  | March et al.                         |                                                                    | 0172065                                                                                                                                |         | 8/2005                      |                                                              |  |

|      | ,715,044             |    |                  | Lofgren et al.                       |                                                                    | 0180209<br>0207231                                                                                                                     |         | 8/2005<br>9/2005            |                                                              |  |

|      | ,721,820<br>,760,805 |    | 7/2004           | Zilberman et al.                     |                                                                    | 0237814                                                                                                                                |         |                             | Li et al.                                                    |  |

|      | ,988,175             |    | 1/2004           |                                      |                                                                    |                                                                                                                                        |         |                             | Kim 713/1                                                    |  |

| 7,   | ,012,835             | B2 |                  | Gonzalez et al.                      |                                                                    | 0286306                                                                                                                                |         |                             | Srinivasan et al.                                            |  |

|      | ,081,377             |    |                  | Cleeves                              |                                                                    | 0289314<br>0184709                                                                                                                     |         |                             | Adusumilli et al 711/168<br>Sukegawa et al.                  |  |

|      | ,120,729             |    | 10/2006          | Gonzalez et al.                      |                                                                    | 0239450                                                                                                                                |         |                             | Holtzman et al.                                              |  |

|      | ,149,119             |    | 12/2006          |                                      |                                                                    | 0047306                                                                                                                                |         | 3/2007                      | Roohparvar                                                   |  |

|      | ,159,069             |    | 1/2007           | Adusumilli et al 711/103             |                                                                    | 0074093                                                                                                                                |         |                             | Lasser et al.                                                |  |

|      | ,170,788             |    |                  | Wan et al.                           |                                                                    | 0088940<br>0101237                                                                                                                     |         |                             | Conley<br>Tamura et al.                                      |  |

|      | ,171,536<br>,177,191 |    | 1/2007<br>2/2007 | Chang et al.                         |                                                                    | 0170268                                                                                                                                |         | 7/2007                      |                                                              |  |

|      | ,177,977             |    |                  | Chen et al.                          |                                                                    | 0263440                                                                                                                                |         |                             | Cornwell et al.                                              |  |

|      | ,187,583             |    |                  | Yang et al.                          |                                                                    | 0276987                                                                                                                                |         |                             | Luo et al.                                                   |  |

|      | ,218,552             |    |                  | Wan et al.                           |                                                                    | 0046630<br>0046641                                                                                                                     |         | 2/2008<br>2/2008            |                                                              |  |

|      | ,224,607             |    |                  | Gonzalez et al.<br>Choi et al.       |                                                                    | 0052449                                                                                                                                |         |                             | Kim et al.                                                   |  |

|      | ,239,556             |    |                  | Abe et al.                           |                                                                    | 0151618                                                                                                                                |         | 6/2008                      | Sharon et al.                                                |  |

| 7,   | ,262,994             | B2 |                  | Fong et al.                          |                                                                    | 0158948                                                                                                                                |         |                             | Sharon et al.                                                |  |

|      | ,295,473             |    |                  | Fong et al.                          |                                                                    | 0222491<br>0229000                                                                                                                     |         | 9/2008                      | Lee et al.                                                   |  |

|      | ,345,907             |    |                  | Scheuerlein<br>Fong et al.           |                                                                    | 0243954                                                                                                                                |         |                             | Augenstein et al.                                            |  |

|      | ,350,044             |    |                  | Keays 711/165                        | 2009/0                                                             | 0031072                                                                                                                                | A1      | 1/2009                      | Sartore                                                      |  |

| 7,   | ,355,888             | B2 | 4/2008           | Hemink et al.                        |                                                                    | 0049229                                                                                                                                |         |                             | Honda et al.                                                 |  |

|      | ,355,889             |    |                  | Hemink et al.                        |                                                                    | 0132760<br>0023676                                                                                                                     |         |                             | Flynn et al 711/103                                          |  |

|      | ,362,604             |    |                  | Scheuerlein<br>Yano et al 365/189.05 |                                                                    | 0023800                                                                                                                                |         |                             | Harari et al.                                                |  |

|      | ,366,029             |    | 4/2008           |                                      |                                                                    | 0031270                                                                                                                                |         |                             | Wu et al.                                                    |  |

| 7,   | ,379,330             | B2 | 5/2008           | Conley et al.                        |                                                                    | 0082882                                                                                                                                |         |                             | Im et al                                                     |  |

|      | ,379,334             |    |                  | Murakami et al.                      |                                                                    | 0161932<br>0040924                                                                                                                     |         | 2/2011                      | Stern et al                                                  |  |

|      | ,392,343             |    |                  | Oshima<br>Nguyen                     |                                                                    | 0041005                                                                                                                                |         | 2/2011                      | Selinger                                                     |  |

|      | ,426,137             |    |                  | Hemink                               |                                                                    | 0041039                                                                                                                                |         |                             | Harari et al.                                                |  |

|      | ,433,241             |    |                  | Dong et al.                          | 2011/0                                                             | 0131383                                                                                                                                | Al*     | 6/2011                      | Kim et al 711/148                                            |  |

|      | ,436,713             |    | 10/2008          |                                      |                                                                    | EC                                                                                                                                     | DEIG    | NI DATE                     | NT DOCUMENTS                                                 |  |

|      | ,440,318             |    |                  | Fong et al.<br>Lutze et al.          |                                                                    | rc                                                                                                                                     | KEIO    | IN FAIL.                    | NI DOCOMENTS                                                 |  |

|      | ,443,736             |    |                  | Samachisa                            | WO                                                                 | WO 20                                                                                                                                  | 09/032  | 945                         | 3/2009                                                       |  |

|      | ,447,065             |    |                  | Fong et al.                          | WO                                                                 | WO 20                                                                                                                                  |         |                             | 7/2009                                                       |  |

|      | ,447,066<br>,450,430 |    |                  | Conley et al.<br>Hemink et al.       | WO                                                                 | WO 20                                                                                                                                  |         |                             | 11/2009                                                      |  |

|      | ,463,531             |    |                  | Hemink et al.                        | WO                                                                 | WO 20                                                                                                                                  | 117090  | 343                         | 7/2011                                                       |  |

| 7,   | ,464,259             | B2 |                  | Sukegawa et al.                      |                                                                    |                                                                                                                                        | OTE     | HER PU                      | BLICATIONS                                                   |  |

|      | ,468,911             |    |                  | Lutze et al.                         |                                                                    |                                                                                                                                        |         |                             |                                                              |  |

|      | ,468,918<br>,475,184 |    | 1/2008           | Dong et al.                          | Nowak, E. et al., "Intrinsic Fluctuations in Vertical NAND Flash   |                                                                                                                                        |         |                             |                                                              |  |

|      | ,477,547             |    | 1/2009           |                                      | Memories", 2012 Symposium on VLSI Technology Digest of Techni-     |                                                                                                                                        |         |                             |                                                              |  |

| 7.   | 495,956              | B2 | 2/2009           | Fong et al.                          | -                                                                  | cal Papers, 2012, pp. 21-22.  Natification of the First Office Action (with translation) for Chinese                                   |         |                             |                                                              |  |

|      | ,499,326             |    |                  | Hemink                               |                                                                    | Notification of the First Office Action (with translation) for Chinese patent application No. 200680035631.0, 14 pages, Jul. 13, 2010. |         |                             |                                                              |  |

|      | ,818,525<br>,890,732 |    |                  | Frost et al 711/165<br>Sukegawa      | Cooke, J., Powerpoint Presentation, Flash Memory Summit, "NAND     |                                                                                                                                        |         |                             |                                                              |  |

|      | ,941,586             |    |                  | Kim 711/103                          | 101, An Introduction to NAND Flash and How to Design It in to Your |                                                                                                                                        |         |                             |                                                              |  |

|      | ,059,455             |    |                  | Stern et al.                         | Next Product", Aug. 8, 2006, p. 1-68.                              |                                                                                                                                        |         |                             |                                                              |  |

|      | ,154,918             |    |                  | Sharon et al.                        | EE Times Asia, "Toshiba Mixes LBA to NAND Flash Memory",           |                                                                                                                                        |         |                             |                                                              |  |

|      | ,187,936             |    |                  | Alsmeier et al.                      | -                                                                  | http://www.eetasia.com/ARTP_8800428816_499486.HTM, posted on Aug. 9, 2006, 1 page.                                                     |         |                             |                                                              |  |

| 8,   | ,281,062             | DΖ | 10/2012          | Hahn et al.                          | posted                                                             | on Aug. S                                                                                                                              | >, ∠∪∪0 | , 1 page.                   |                                                              |  |

#### (56)References Cited

### OTHER PUBLICATIONS

Grimsrud, K., Powerpoint Presentation, "Intel Developer Forum", 2007, pp. 1-30.

Heye, R., Powerpoint Presentation, "Microsoft WinHec 2008 Advancing the Platform—MLC NAND in the PC, Planning for Success". 2008, pp. 1-34.

"Innovation, Simplify Embedded NAND Flash Design", Advertisement, 1 page

Inoue, A. et al., "NAMD Flash Applications Design Guide, System Solutions from Toshiba America Electronic Components, Inc.", Revision 1.0, Apr. 2003, pp. 1-29

Toshiba LBA-NAND Simplifies Integration, http://www.toshiba. com/taec/adinfo/embeddednand/images/LBAblockDiagram.ip-g, retrieved on Aug. 4, 2009, 1 page.

Office Action for U.S. Appl. No. 11/806,702 dated Jun. 18, 2009, 14 pages.

Schwaderer, W. et al., "Understanding I/O Subsystems, First Edition", Adaptec Press, 1996 pp. ii-iii, 82-87, 176-191.

Supplemental European Search Report and Opinion for European Patent Application No. 06796108.6, May 7, 2009, 8 pages

Wikipedla, "Southbridge (Computing)", http://en.wikipedia.org/ wiki/Southbridge\_(computing), Retrieved on Aug. 4, 2009, pp. 1-2. MT29F4G0BAAA, NAND Flash Memory: MT29F8G08BAA, MT29F8GO8DAA, MT29F16G08FAA," http:// download.micron.com/pdf/datasheets/flash/nand/4gb\_nand\_ m40a.pdf, 1 page, 2006.

"SanDisk Flash Memo Cards Wear Leveling", Oct. 2003, pp. 1-6. International Search Report and Written Opinion for PCT/US2010/ 057386, dated Feb. 28 2012, 19 pages.

Restriction Requirement for U.S. Appl. No. 12/544,529, dated May 10, 2011, 22 pages.

U.S. Appl. No. 14/133,979, filed Dec. 19, 2013, 121 pages.

U.S. Appl. No. 14/136,103, filed Dec. 20, 2013, 56 pages.

Jang et al., "Vertical Cell Array using TCAT(Terabit Cell Array Transistor) Technology for Ultra High Density NAND Flash Memory," 2009 Symposium on VLSI Technology Digest of Technical Papers, pp. 192-193, 2009

English translation of Office Action for Chinese Patent Application Serial No. 2010800649962 dated Sep. 19, 2014, 2 pages.

English translation of Office Action for Chinese Patent Application Serial No. 2010800649962 dated Jun. 3, 2014, 9 pages

English Translation of Office Action for Taiwanese Application No. 099143836 dated May 16, 2015, 4 pages.

Search Report for Taiwanese Application No. 099143836 dated May 16, 2015, 1 page.

Cooke, J., Microsoft WinHec 2007, "Flash Memory Technology Direction", Apr. 30, 2007, pp. 1-11.

Denali Software, "Spectra<sup>TM</sup> NAND Flash File System", http://www. denali.com/en/products/spectra\_ffs.jsp, copyright 1994-2009, retrieved on Aug. 6, 2009, pp. 1-3.

Roohparvar, F., Powerpoint Presentation, Flash Memory Summit, "The Future of Wireless Flash", Aug. 2006, pp. 1-29.

"Simplify MLC NAND Design with Toshiba Embedded NAND Solutions", http://www.toshiba.com/taec/adinfo/embeddednand/, retrieved on Aug. 4, 2009, 2 pages

Cooke, "Micron e-MMC Embedded Memory Simplifies High Capacity Storage for Mobile and Embedded Solutions," 2007, 7 pages.

Abraham, "Flash Standards for Embedded Systems," Aug. 2008, 22 pages.

Ex Parte Quayle Action for U.S. Appl. No. 11/326,336, dated Jul. 30, 2009, 13 pages

Office Action for U.S. Appl. No. 11/806,701 dated Jun. 22, 2009, 35

"Open NAND Flash Interface Specification", Revision 2.1, Jan. 14,

2009, pp. 1-201. "Samsung Electronics Develops World's First Eight-Die Multi-Chip

Package for Multimedia Cell Phones", http://www.samsung.com/us/ business/seimconductor/newsView.do?news\_id=628.0, Jan. 10, 2005.

Serial ATA, "High Speed Serialized AT Attachment", Revision 1.0a, Jan. 7, 2003, 2 pages (title page and p. 144).

Toshiba TC58NVG1S3BFT00/TC58NVG1S8BFT000 Tentative, Toshiba MOS Digital Integrated Circuit Silicon Gate CMOS, Oct. 30, 2003, pp. 1-37.

Toshiba TC58NVG2D4BFT00/TC58NVG2D9BFT000 Tentative, Toshiba MOS Digital Integrated Circuit Silicon Gate CMOS, Oct. 30, 2003, pp. 1-37.

U.S. Appl. No. 12/165,141 entitled, "Partial Scrambling to Reduce Correlation," filed Jun. 30, 2008, inventors: Ori Stern, Tal Heller, and Menahem Lasser.

U.S. Appl. No. 12/199,023 entitled, "A Portable Storage Device With an Accelerated Access Speed", filed Aug. 27, 2008, inventors: Judah Gamliel and Donald Ray Bryant-Rich.

U.S. Appl. No. 12/209,697 entitled, "Method for Scrambling Data in which Scrambling Data and Scrambled Data are Stored in Corresponding Non-Volatile Memory Locations," filed Sep. 12, 2008, inventors: Jun Wan, Yupin K. Fong, and Man L. Mui.

U.S. Appl. No. 12/251,820 entitled, "Method for Page- and Block Based Scrambling in Non-Volatile Memory," filed Oct. 15, 2008, inventors: Eran Sharon and Idan Alrod.

U.S. Appl. No. 12/539,394 entitled, "Controller and Method for Interfacing Between a Host Controller in a Host and a Flash Memory Device", filed Aug. 11, 2009, inventors: Eliyahou Harari, Richard R. Heye and Robert D. Selinger.

U.S. Appl. No. 12/539,407, entitled, "Controller and Method for Detecting a Transmission Error Over a NAND Interface Using Error Detection Code", filed Aug. 11, 2009, inventor: Robert D. Selinger. U.S. Appl. No. 12/539,417 entitled, "NAND Flash Memory Controller Exporting a NAND Interface", filed Aug. 11, 2009, inventors: Eliyahou Harari, Richard R. Heye, Robert D. Selinger and Menahem Lasser

U.S. Appl. No. 12/539,379 entitled, "Controller and Method for Providing Read Status and Spare Block Management Information in a Flash Memory System," filed Aug. 11, 2009, inventor: Robert D. Selinger.

"USB 2.0 High-Speed Flash Drive Controller, ST72681", Revision Feb. 6, 2009 (previous revisions May 2005-Jan. 2009), pp. 1-34.

Extended European Search Report and Opinion for European Patent Application No. 09009022.6-1233, Sep. 21, 2009, 9 pages

"ONFI Working on Next-Generation NAND Specifications: ONFI 3.0 and EZNAND," 1 page, Jan. 6, 2010.

"Siemens Internal Flash Data Management," 2 pages, Siemens AG

Examination Report for EP Application No. 09009022.6-1233, 6 pages, May 4, 2010.

Examination Report for EP Application No. 06796108.6-1233, 5 pages, Feb. 17, 2010.

Notice of Ground for Refusal for Korean Patent Application No. 10-2008-7007225, 5 pages, May 11, 2010.

Office Action directed against U.S. Appl. No. 11/806,701, 27 pages, Feb. 25, 2010

Office Action directed against U.S. Appl. No. 11/806,702, 9 pages, Feb. 25, 2010.

U.S. Appl. No. 12/650,255 entitled, "Method and Controller for Performing a Sequence of Commands," filed Dec. 30, 2009, inventors: Robert D. Selinger, Gary Lin, and Chaoyang Wang.

Brown, "White Paper: Flash Memory", Oct. 2007, pp. 70-71

Chang, "On Efficient Wear Leveling for Large-Scale Flash-Memory Storage Systems", Mar. 15, 2007, pp. 1127-1130.

Clause 8.2.3 and other sections of Clause 8, SCSI-2 Specification, 1994, 73 pages.

Open NAND Flash Interface (ONFI) Specification, Revision 2.0, Feb. 27, 2008, 174 pages.

"SanDisk Flash Memory Cards Wear Leveling", Oct. 2003, pp. 1-6. Solomon, "Microsoft Windows Internals: Microsoft Windows Server tm 2003, Windows XP and Windows 2000, Fourth Edition", Dec. 8, 2004, pp. xi, 280, 373, 564.

Invitation to Pay Additional Fees for PCT/US2010/057386, dated Sep. 12, 2011, 5 pages.

International Search Report and Written Opinion for PCT/US2010/ 057386, dated Feb. 28, 2012, 19 pages.

### **US RE46,013 E**

Page 4

#### **References Cited** (56)

### OTHER PUBLICATIONS

Office Action for U.S. Appl. No. 12/338,378, dated May 4, 2011, 23

Office Action for U.S. Appl. No. 12/338,378, dated Apr. 26, 2012, 15 pages.

Office Action for U.S. Appl. No. 12/544,529, dated Mar. 23,2012,12

pages.

U.S. Appl. No. 12/338,378 etntitled, Methods for Writing Data from a Source Location in a Memory Device, filed Dec. 18, 2008, inventors: Ori Stern, Micha Rave, Robert Selinger, and Sandra Almog Goldschmidt.

\* cited by examiner

FIG. .

FIG. 3

FIG. 5

FIG. 6

FIG. 7

FIG. 8A

FIG. 8B

FIG. 9

FIG. 10

FIG. 11

FIG. 14

FIG. 15

# METHOD AND CONTROLLER FOR PERFORMING A COPY-BACK OPERATION

Matter enclosed in heavy brackets [] appears in the original patent but forms no part of this reissue specification; matter printed in italics indicates the additions made by reissue; a claim printed with strikethrough indicates that the claim was canceled, disclaimed, or held invalid by a prior post-patent action or proceeding.

### BACKGROUND

NAND flash memory devices are commonly used to store data by a host, such as a personal computer. A host can 15 communicate with a NAND flash memory device using a NAND interface, such as Open NAND Flash Interface (ONFI), for example. One example of a command that a host can send to a NAND flash memory device is a "copy-back" command. In operation, the host sends a source address and a 20 copy-back read command to the NAND flash memory device, in response to which the NAND flash memory device reads data from the source address in its non-volatile memory and writes the data in a register internal to the NAND flash memory device. Next, the host sends a destination address 25 and a copy-back program command to the NAND flash memory device, in response to which the NAND flash memory device reads the data out of the register and writes it to the destination address in its non-volatile memory. Because the data is not sent back to the host, a copy-back operation 30 avoids occupying the communication bus between the host and the NAND flash memory device and avoids requiring the host to allocate processing power and overhead to perform standard read and program operations to move the data. However, although any error correction code (ECC) bits stored 35 FIG. 7. with the data are also moved, the NAND flash memory device does not perform ECC checking and error correction on the data. Accordingly, any errors existing in the data would be propagated.

### SUMMARY

The present invention is defined by the claims, and nothing in this section should be taken as a limitation on those claims.

By way of introduction, the embodiments described below 45 provide a method and controller for performing a copy-back operation. In one embodiment, a controller in communication with a host and at least one flash memory device receives a source address and a copy-back read command from the host. The controller sends the source address and the copy-back 50 read command to the at least one flash memory device, in response to which the at least one flash memory device reads data from the source address and writes the data in a register in the at least one flash memory device. The controller receives the data and error correction code associated with the 55 data from the at least one flash memory device and receives a destination address and a copy-back program command from the host. The controller determines if the error correction code indicates there is an error in the data. If the error correction code does not indicate there is an error in the data, the 60 controller sends the destination address and the copy-back program command to the at least one flash memory device, in response to which the at least one flash memory device reads the data out of the register and writes the data to the destination address in the at least one flash memory device. If the 65 error correction code indicates there is an error in the data, the controller corrects the data and sends the destination address,

2

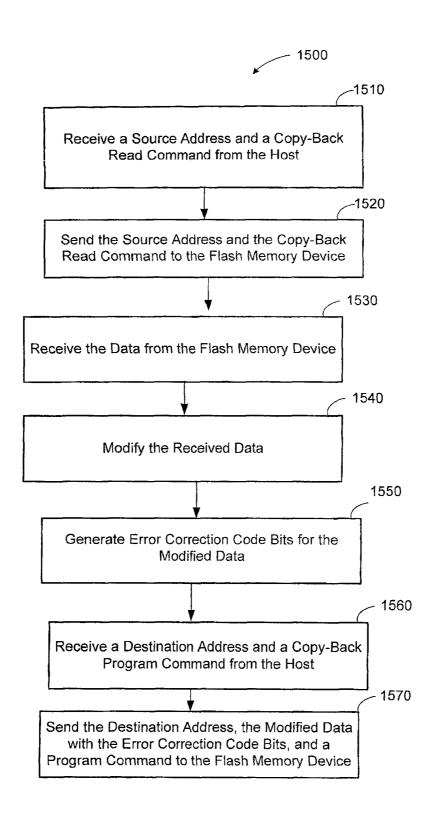

the corrected data, and a program command to the at least one flash memory device. Additional embodiments relate to modifying data during the copy-back operation.

Other embodiments are disclosed, and each of the embodiments can be used alone or together in combination. The embodiments will now be described with reference to the attached drawings.

### BRIEF DESCRIPTION OF THE DRAWINGS

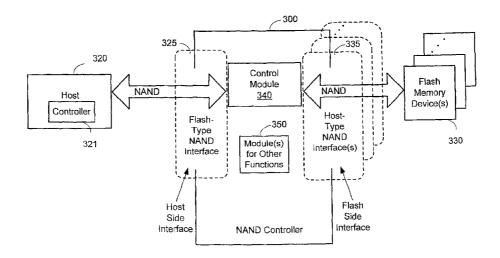

FIG. 1 is a block diagram of a system of an embodiment comprising a controller, a host, and one or more flash memory devices.

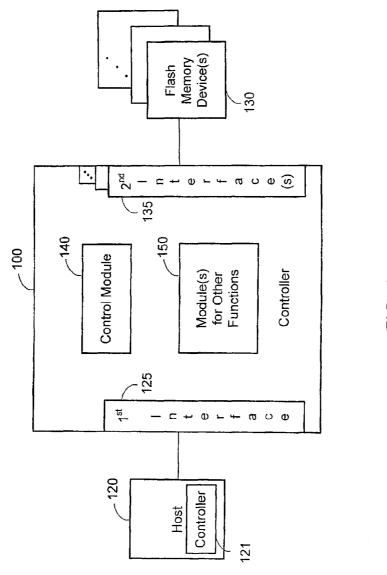

FIGS. 2A, 2B, and 2C are block diagrams illustrating different arrangements of a controller and flash memory device(s) of an embodiment.

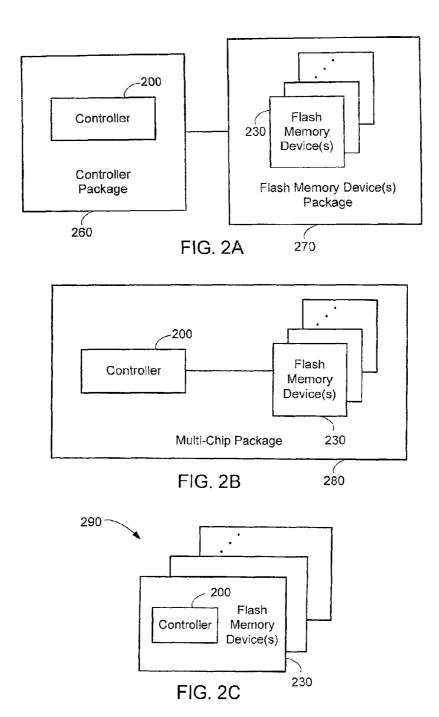

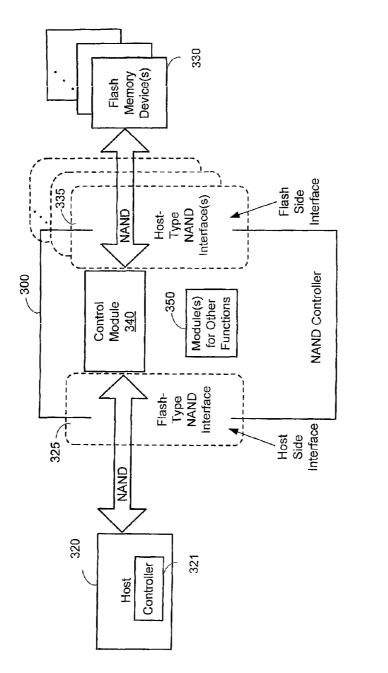

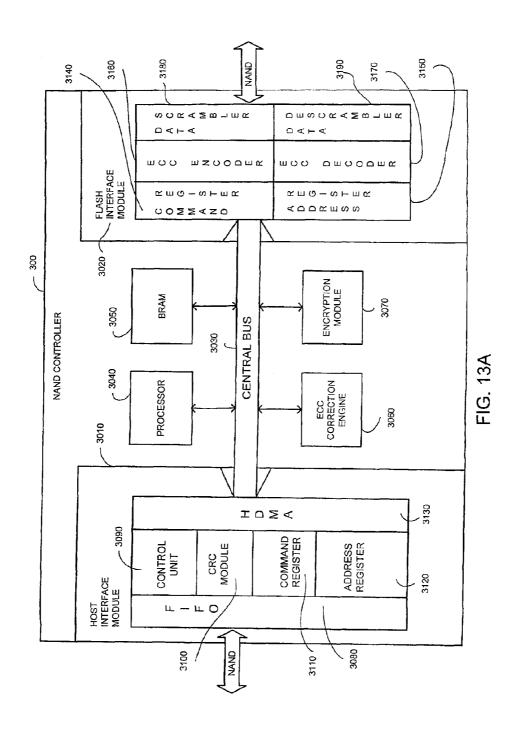

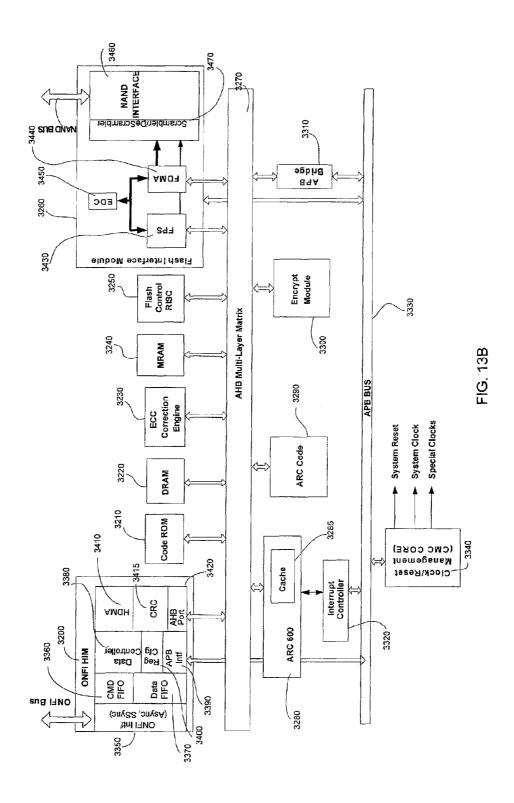

FIG. 3 is a block diagram of an exemplary controller of an embodiment.

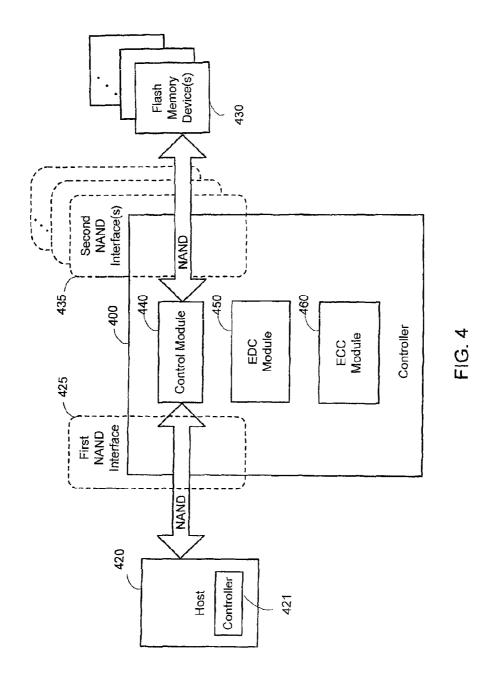

FIG. 4 is a block diagram of a controller of an embodiment for writing data to and reading data from flash memory device(s).

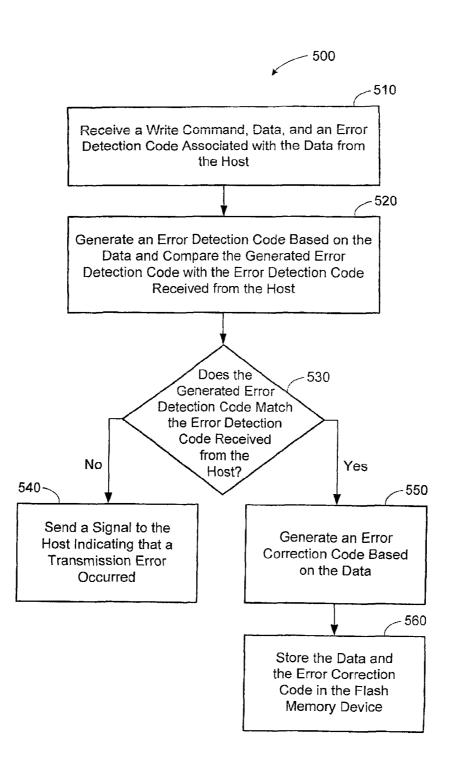

FIG. 5 is a flow chart of a method for writing data in a flash memory device using a controller of an embodiment.

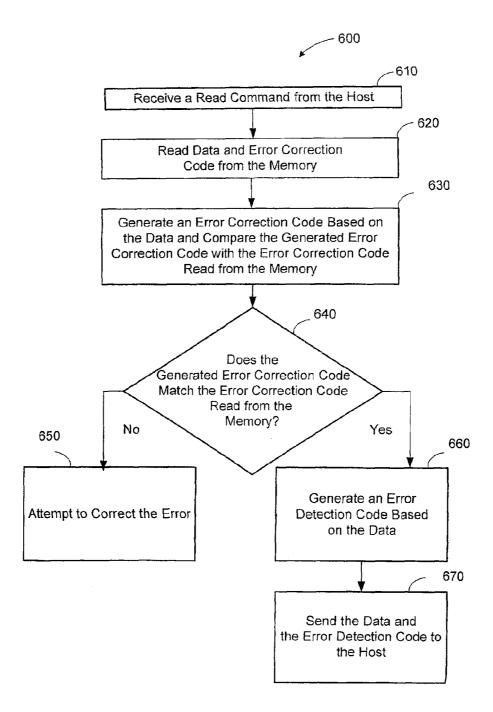

FIG. **6** is a flow chart of a method for reading data from a flash memory device using a controller of an embodiment.

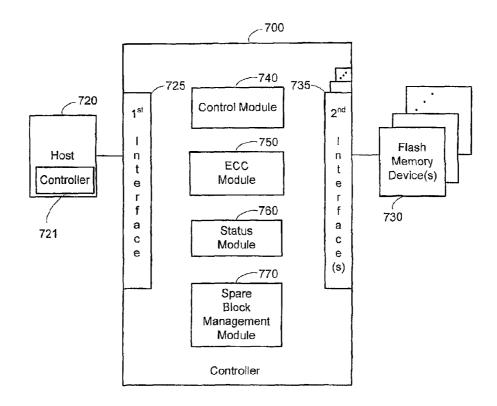

FIG. 7 illustrates a controller arrangement of an embodiment configured for providing read status and spare block management control.

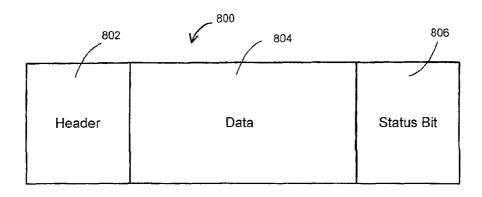

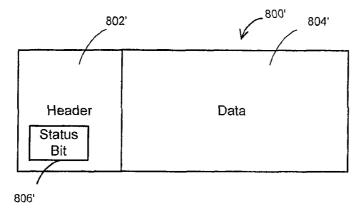

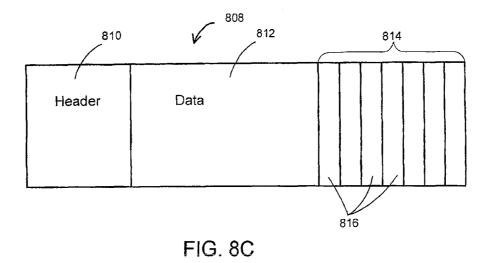

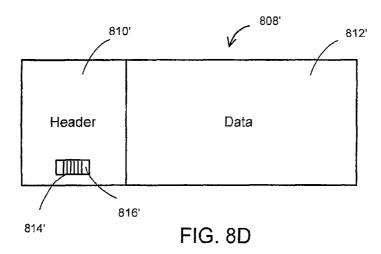

FIGS. 8A, 8B, 8C, and 8D are examples of data message formats that may be generated by the controller of FIG. 7.

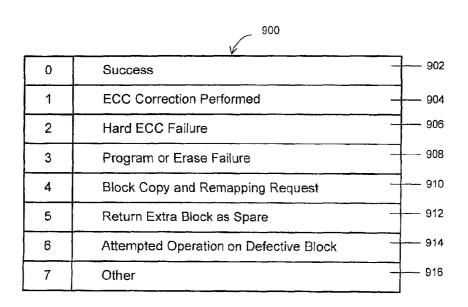

FIG. 9 is an embodiment of data fields available for use in the data message format of FIG. 8C.

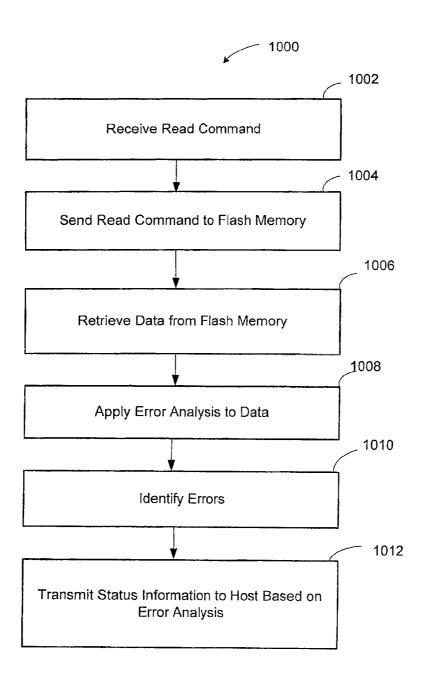

FIG. 10 is a flow chart of a method of an embodiment for providing status information to a host using the controller of FIG. 7.

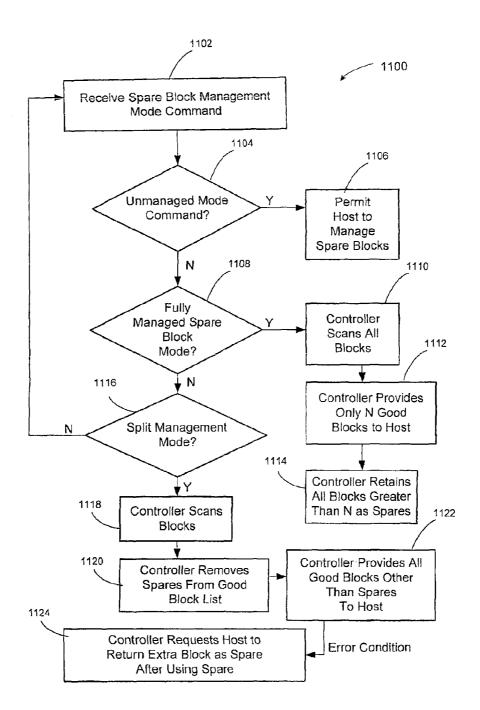

FIG. 11 is a flow chart illustrating one embodiment of managing spare blocks using the controller of FIG. 7.

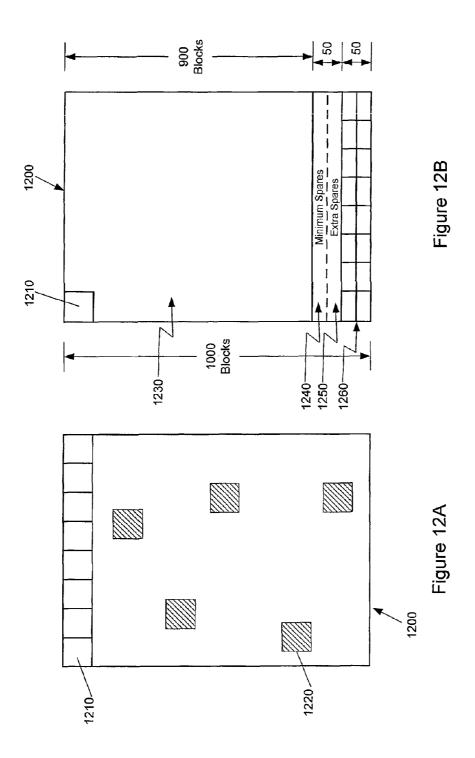

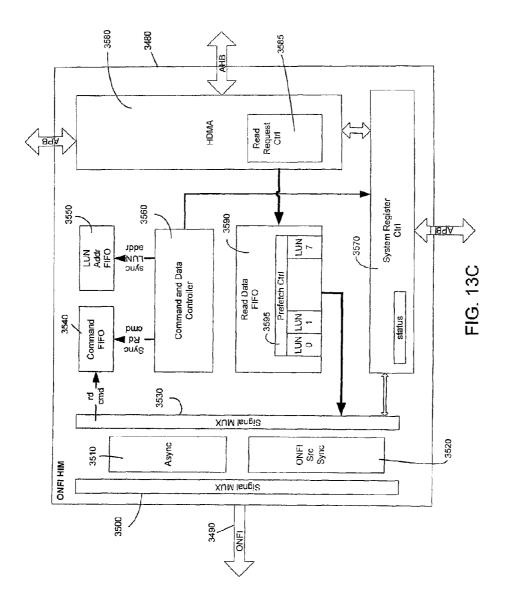

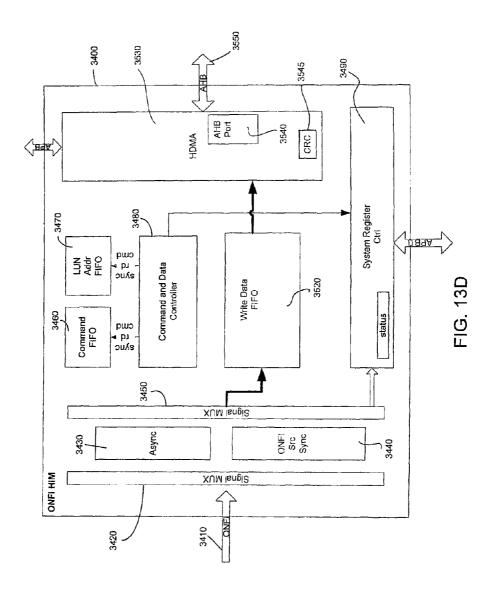

FIGS. **12**A and **12**B are illustrations of good, bad, and spare block areas within an exemplary flash memory device. FIGS. **13**A-**13**D are block diagrams of exemplary control-

lers of an embodiment.

FIG. **14** is a flowchart of a method of an embodiment for performing a copy-back operation.

FIG. 15 is a flowchart of a method of an embodiment for performing a copy-back operation in which data is modified.

# DETAILED DESCRIPTION OF THE PRESENTLY PREFERRED EMBODIMENTS

Introduction

The following embodiments are directed to flash memory controllers and methods for use therewith. In one embodiment, a controller and method are provided for performing a copy-back command. Before turning to this and other embodiments, a general overview of exemplary controller architectures and a discussion of NAND interfaces and NAND interface protocols are provided.

**Exemplary Controller Architectures**

Turning now to the drawings, FIG. 1 is a system of an embodiment in which a controller 100 is in communication with a host 120 (having a host controller 121) through a first interface 125 and is in communication with one or more flash memory device(s) 130 through one or more second interface(s) 135. (The number of second interface(s) 135 can match the number of flash memory device(s) 130, or the number of second interface(s) 135 can be greater than or less than the number of flash memory device(s) 130 (e.g., a single

•

second interface 135 can support multiple flash memory device(s)).) As used herein, the phrase "in communication with" means directly in communication with or indirectly in communication with through one or more components, which may or may not be shown or described herein.

3

A "host" is any entity that is capable of accessing the one or more flash memory device(s) 130 through the controller 100, either directly or indirectly through one or more components named or unnamed herein. A host can take any suitable form, such as, but not limited to, a personal computer, a mobile 10 phone, a game device, a personal digital assistant (PDA), an email/text messaging device, a digital camera, a digital media (e.g., MP3) player, a GPS navigation device, a personal navigation system (PND), a mobile Internet device (MID), and a TV system. Depending on the application, the host 120 can 15 take the form of a hardware device, a software application, or a combination of hardware and software.

"Flash memory device(s)" refer to device(s) containing a to plurality of flash memory cells and any necessary control circuitry for storing data within the flash memory cells. In one 20 embodiment, the flash memory cells are NAND memory cells, although other memory technologies, such as passive element arrays, including one-time programmable memory elements and/or rewritable memory elements, can be used. (It should be noted that, in these embodiments, a non-NAND- 25 type flash memory device can still use a NAND interface and/or NAND commands and protocols.) One example of a passive element array is a three-dimensional memory array. As used herein, a three-dimensional memory array refers to a memory array comprising a plurality of layers of memory 30 cells stacked vertically above one another above a single silicon substrate. In this way, a three-dimensional memory array is a monolithic integrated circuit structure, rather than a plurality of integrated circuit devices packaged or die-bonded in close proximity to one another. Although a three-dimen- 35 sional memory array is preferred, the memory array can instead take the form of a two-dimensional (planar) array. The following patent documents, which are hereby incorporated by reference, describe suitable configurations for three-dimensional memory arrays, in which the three-dimensional 40 memory array is configured as a plurality of levels, with word lines and/or bit lines shared between levels: U.S. Pat. Nos. 6,034,882; 6,185,122; 6,420,215; 6,631,085; and 7,081,377. Also, the flash memory device(s) 130 can be a single memory die or multiple memory dies. Accordingly, the phrase "a flash 45 memory device" used in the claims can refer to only one flash memory device or more than one flash memory device.

As shown in FIG. 1, the controller 100 also comprises a control module 140 for controlling the operation of the controller 100 and performing a memory operation based on a 50 command (e.g., read, write, erase, etc.) and an address received from the host 120. As used herein, a "module" can include hardware, software, firmware, or any combination thereof. Examples of forms that a "module" can take include, but are not limited to, one or more of a microprocessor or 55 processor and a computer-readable medium that stores computer-readable program code (e.g., software or firmware) executable by the (micro)processor, logic gates, switches, an application specific integrated circuit (ASIC), a programmable logic controller, and an embedded microcontroller, for 60 example. (The following sections provide examples of the various forms a "module" can take.) As shown in FIG. 1, the controller 100 can include one or more additional modules 150 for providing other functionality, including, but not limited to, data scrambling, column replacement, handling write 65 aborts and/or program failures (via safe zones), read scrubbing, wear leveling, bad block and/or spare block manage-

ment, error correction code (ECC) functionality, error detection code (EDC) functionality, status functionality, encryption functionality, error recovery, and address mapping (e.g., mapping of logical to physical blocks). The following sections provide more details on these functions, as

well as additional examples of other functions.

While the controller 100 and flash memory device(s) 130 are shown as two separate boxes in FIG. 1, it should be understood that the controller 100 and flash memory device(s) 130 can be arranged in any suitable manner. FIGS. 2A, 2B, and 2C are block diagrams illustrating different arrangements of the controller and flash memory device(s). In FIG. 2A, the controller 200 and the flash memory device(s) 230 are packaged in different packages 260, 270. In this embodiment, an inter-die interface can interface between the controller 200 and the flash memory device(s) 230. As used herein, an "inter-die interface" (e.g., an inter-die NAND interface) is operative to interface between two distinct units of electronic circuitry residing on distinct dies (e.g., to provide the necessary physical and logical infrastructure for the distinct units of electronic circuitry to communicate with each other, for example, using one or more specific protocols). Thus, the inter-die interface includes the necessary physical elements (e.g., pads, output, input drivers, etc.) for interfacing between the two distinct units of electronic circuitry residing on separate dies.

In FIG. 2B, the controller 200 and the flash memory device(s) 230 both reside within a common multi-chip package 280. In this embodiment, an inter-die interface can interface between the controller 200 and the flash memory device(s) 230 fabricated on two distinct dies that are packaged in the common multi-chip package 280. In FIG. 2C, the controller 200 and the flash memory device(s) 230 are integrated on a same die 290. As another alternative, the controller 200 and/or flash memory device(s) 230 can be fabricated on two distinct dies, where one or both of these dies has no package at all. For example, in many applications, due to a need to conserve space, memory dies are mounted on circuit boards with no packaging at all.

It should be noted that in each of these arrangements, the controller 200 is physically located separately from the host. This allows the controller 200 and flash memory device(s) 230 to be considered a separate circuitry unit, which can be used in a wide variety of hosts.

As noted above with reference to FIG. 1, the controller 100 communicates with the host 120 using a first interface 125 and communicates with the flash memory device(s) 130 using second interface(s) 135. In general, the first and second interfaces 125, 135 can take any suitable form. However, in a presently preferred embodiment, which will be described below in conjunction with FIG. 3, the first and second interfaces 125, 135 are both NAND interfaces that use NAND interface protocols. Before turning to FIG. 3, the following section provides a general discussion of NAND interfaces and NAND interface protocols.

NAND Interfaces and NAND Interface Protocols

A NAND interface protocol is used to coordinate commands and data transfers between a NAND flash device and a host using, for example, data lines and control signals, such as ALE (Address Latch Enable), CLE (Command Latch Enable), and WE#(Write Enable). Even though the term "NAND interface protocol" has not, to date, been formally standardized by a standardization body, the manufacturers of NAND flash devices all follow very similar protocols for supporting the basic subset of NAND flash functionality. This is done so that customers using NAND devices within their electronic products could use NAND devices from any manu-

facturer without having to tailor their hardware or software for operating with the devices of a specific vendor. It is noted that even NAND vendors that provide extra functionality beyond this basic subset of functionality ensure that the basic functionality is provided in order to provide compatibility with the protocol used by the other vendors, at least to some extent

5

A given device (e.g., a controller, a flash memory device, a host, etc.) is said to comprise, include, or have a "NAND interface" if the given device includes elements (e.g., hardware, software, firmware, or any combination thereof) necessary for supporting the NAND interface protocol (e.g., for interacting with another device using a NAND interface protocol). (As used herein, the term "interface(s)" can refer to a 15 single interface or multiple interfaces. Accordingly, the term "interface" in the claims can refer to only one interface or more than one interface.) In this application, the term "NAND Interface protocol" (or "NAND interface" in short) refers to an interface protocol between an initiating device and a 20 responding device that, in general, follows the protocol between a host and a NAND flash device for the basic read, write, and erase operations, even if it is not fully compatible with all timing parameters, not fully compatible with respect to other commands supported by NAND devices, or contains 25 additional commands not supported by NAND devices. One suitable example of a NAND interface protocol is an interface protocol that uses sequences of transferred bytes equivalent in functionality to the sequences of bytes used when interfacing with a Toshiba TC58NVG1S3B NAND device (or a Toshiba 30 TC58NVG2D4B NAND device) for reading (opcode 00H), writing (opcode 80H), and erasing (opcode 60H), and also uses control signals equivalent in functionality to the CLE, ALE, CE, WE, and RE signals of the above NAND device.

It is noted that a NAND interface protocol is not symmetric in that the host—not the flash device—initiates the interaction over a NAND interface. Further, an interface (e.g., a NAND interface or an interface associated with another protocol) of a given device (e.g., a controller) may be a "host-side interface" (e.g., the given device is adapted to interact with a host using the host-side interface), or the interface of the given device may be a "flash memory device-side interface" (e.g., the given device is adapted to interact with a flash memory device using the flash memory device-side interface). The terms "flash memory device-side interface," "flash device-side interface," and "flash-side interface" are used interchangeably herein.

These terms (i.e., "host-side interface" and "flash deviceside interface") should not be confused with the terms "hosttype interface" and "flash-type interface," which are termi- 50 nology used herein to differentiate between the two sides of a NAND interface protocol, as this protocol is not symmetric. Furthermore, because it is the host that initiates the interaction, we note that a given device is said to have a "host-type interface" if the device includes the necessary hardware and/ 55 or software for implementing the host side of the NAND interface protocol (i.e., for presenting a NAND host and initiating the NAND protocol interaction). Similarly, because the flash device does not initiate the interaction, we note that a given device is said to have a "flash-type interface" if the 60 device includes the necessary hardware and/or software for implementing the flash side of the NAND protocol (i.e., for presenting a NAND flash device).

Typically, "host-type interfaces" (i.e., those which play the role of the host) are "flash device-side interfaces" (i.e., they interact with flash devices or with hardware emulating a flash device) while "flash device-type interfaces" (i.e., those which

6

play the role of the flash device) are typically "host-side interfaces" (i.e., they interact with hosts or with hardware emulating a host).

Because of the complexities of NAND devices, a "NAND controller" can be used for controlling the use of a NAND device in an electronic system. It is possible to operate and use a NAND device directly by a host with no intervening NAND controller; however, such architecture suffers from many disadvantages. First, the host has to individually manipulate each one of the NAND device's control signals (e.g., CLE or ALE), which is cumbersome and time-consuming for the host. Second, the support of error correction code (ECC) puts a burden on the host. For at least these reasons, "no controller" architectures are usually relatively slow and inefficient.

In some conventional controller architectures, a NAND controller interacts with a flash memory device using a NAND interface and interacts with a host using a standard, non-NAND interface, such as USB or SATA. That is, in these conventional controller architectures, the NAND controller does not export a NAND interface to the host. Indeed, this is reasonable to expect, as a host processor that does not have built-in NAND support and requires an external controller for that purpose typically does not have a NAND interface and cannot directly connect to a device exporting a NAND interface and, therefore, has no use of a controller with a host-side NAND interface. On the other hand, a host processor that has built-in NAND support typically also includes a built-in NAND controller and can connect directly to a NAND device, and, therefore, has no need for an external NAND controller.

"NAND Flash Memory Controller Exporting a NAND Interface," U.S. Pat. No. 7,631,245, which is hereby incorporated by reference, discloses a new type of NAND controller, characterized by the fact that the interface it exports to the host side is a NAND interface. In this way, the NAND controller exports to the host the same type of interface that is exported by a standard NAND flash memory device. The controller also preferably has a NAND interface on the flash memory device side as well, where the controller plays the role of a host towards the NAND flash memory device and plays the role of a NAND device towards the host.

Exemplary NAND Flash Memory Controller Exporting a NAND Interface

Returning to the drawings, FIG. 3 is a block diagram of an exemplary controller 300 of an embodiment. As shown in FIG. 3, the controller 300 includes a control module 340 for controlling the operation of the controller 300 and, optionally, one or more additional modules 350 for providing other functions. Examples of other functions include, but are not limited to, data scrambling, column replacement, handling write aborts and/or program failures (via safe zones), read scrubbing, wear leveling, bad block and/or spare block management, error correction code (ECC) functionality, error detection code (EDC) functionality, status functionality, encryption functionality, error recovery, and address mapping (e.g., mapping of logical to physical blocks). The following paragraphs describe some of these functions, and sections later in this document describe others of these functions.

"Data scrambling" or "scrambling" is an invertible transformation of an input bit sequence to an output bit sequence, such that each bit of the output bit sequence is a function of several bits of the input bit sequence and of an auxiliary bit sequence. The data stored in a flash memory device may be scrambled in order to reduce data pattern-dependent sensitivities, disturbance effects, or errors by creating more randomized data patterns. More information about data scrambling can be found in the following patent documents: U.S.

patent application Ser. Nos. 11/808,906, 12/209,697, 12/251, 820, 12/165,141, and 11/876,789, as well as PCT application no. PCT/US08/88625.

"Column replacement" refers to various implementations of mapping or replacing entirely bad columns, portions of 5 columns, or even individual cells. Suitable types of column replacement techniques can be found in U.S. Pat. Nos. 7,379, 330 and 7,447,066.

There are several potential problems in writing to flash memory devices where logically or physically adjacent data 10 may be corrupted outside of the location where the data is attempted to be written. One example is when a write to one area (e.g., a cell, page, or block) of memory fails, and the contents of some surrounding memory may be corrupted. This is referred to as a "program failure" or "program disturb." A similar effect known as "write abort" is when a write (or program) operation is terminated prematurely, for example when power is removed unexpectedly. In both cases, there are algorithms which may be used to pro-actively copy data from a "risk zone" to a "safe zone" to handle write aborts 20 and program failures, as described in U.S. Pat. No. 6,988,175.

"Read scrubbing" or, more generally, "scrubbing" refers to the techniques of refreshing and correcting data stored in a flash memory device to compensate for disturbs. A scrub operation entails reading data in areas that may have received 25 exposure to potentially disturbing signals and performing some corrective action if this data is determined to have been disturbed. Read scrubbing is further described in U.S. Pat. Nos. 7.012.835, 7.224.607, and 7.477.547.

Flash memory devices may be written unevenly, and "wear 30 leveling" refers to techniques that attempt to even out the number of times memory cells are written over their lifetime. Exemplary wear leveling techniques are described in U.S. Pat. Nos. 6,230,233 and 6,594,183.

In general, flash memory devices are manufactured with an excess number of blocks (greater than the defined minimum capacity). Either during factory testing or during use of the device, certain blocks may be discovered as "bad" or "defective," meaning that they are unable to correctly store data and need to be replaced. Similarly, there may be an excess of "good" blocks (greater than the defined minimum capacity) which may be used as "spares" until another block fails or becomes defective. Keeping track of these extra blocks is known as bad block management and spare block management, respectively. More information about bad block and spare block management can be found in U.S. Pat. No. 7,171, 536.

As mentioned above, additional information about these different functional modules and how they are used in exemplary controller architectures is provided later in this document.

Returning to the drawings, as also shown in FIG. 3, the controller 300 includes one or more flash memory device-side NAND interface(s) 335 for interfacing with one or more NAND flash device(s) 330 (e.g., 1-8 memory dies). Further- 55 more, it is noted that the flash memory device-side NAND interface 335 is also a host-type NAND interface (i.e., that it is adapted to initiate the interaction over the NAND interface and to present a host to a NAND flash device(s) 330). The controller 300 also includes a host side NAND interface 325 60 for interfacing to a host 320 (having a host controller 321) that supports a NAND interface protocol. This host side NAND interface 325 is also a flash memory-type NAND interface (e.g., the controller 300 is adapted to present to the host 320 a NAND flash memory storage device). Examples of NAND 65 interfaces include, but are not limited to, Open NAND Flash Interface (ONFI), toggle mode (TM), and a high-perfor8

mance flash memory interface, such as the one described in U.S. Pat. No. 7,366,029, which is hereby incorporated by reference. The controller 300 may optionally include one or more additional host-side interfaces, for interfacing the controller 300 to hosts using non-NAND interfaces, such as SD, USB, SATA, or MMC interfaces. Also, the interfaces 325, 335 can use the same or different NAND interface protocols.

It should be noted that the controller 300 and flash memory device(s) 330 can be used in any desired system environment. For example, in one implementation, a product manufactured with one or more controller 300/flash memory device(s) 330 units is used in a solid-state drive (SSD). As another example, the controller 300 can be used in OEM designs that use a Southbridge controller to interface to flash memory devices.

There are several advantages of using a NAND flash memory controller that exports a NAND interface to a host. To appreciate these advantages, first consider the realities of current controller architectures. Today, there are two types of NAND interfaces: a "raw" interface and a "managed" interface. With a raw interface, the basic memory is exposed with primitive commands like read, program, and erase, and the external controller is expected to provide memory management functions, such as ECC, defect management, and flash translation. With a managed interface, through some higher level interface, logical items such as sectors/pages/blocks or files are managed, and the controller manages memory management functions.

However, the set of firmware required to "manage" the NAND can be divided into two categories. The first category is generic flash software that mostly manages the host interface, objects (and read/modify/write sequences), and caching. This is referred to as the "host management" layer. The second category is flash-specific management functionality that does, for example, the ECC, data scrambling, and specific error recovery and error prevention techniques like pro-active read scrubbing and copying lower-page blocks to prevent data loss due to write aborts, power failures, and write errors. This is referred to as the "device management" layer.

The first category of software is relatively constant and dors, chipset and controller vendors, and embedded device vendors. In general, let's assume there are M specific systems/OSes/ASICs that may want to use flash in their designs. The second set is potentially proprietary to individual companies and even specific to certain memory designs and generations. In general, let's assume there are N different memory specific design points. Today, this is an all-or-nothing approach to flash management—either buy raw NAND or managed NAND. This also means that a solution must incorporate one of the M system and host management environments with one of the N memory device management environments. In general, this means that either (1) a flash vendor with the second kind of knowledge must provide all layers of a solution, including ASIC controller and host interface software, and do M different designs for the M different host opportunities, or (2) any independent ASIC and firmware company has little opportunity to customize their solutions to specific memory designs without doing N different designs, or (3) two companies have to work together, potentially exposing valuable trade secrets and IP and/or implement different solutions for each memory design. This can also produce a time-to-market delay if M different host solutions have to be modified to accept any new memory design or vice versa.

By using a NAND flash memory controller that exports a NAND interface to a host, a new logical interface is provided that uses existing physical NAND interfaces and commands,

such as legacy asynchronous, ONFI, or TM, to create a new logical interface above raw or physical NAND and below logical or managed NAND, create "virtual" raw NAND memory with no ECC required in the host controller, and disable host ECC (since 0 ECC is required from the host to 5 protect the NAND memory). This new logical interface also can provide, for example, data scrambling, scrubbing, disturbs, safe zone handling, wear leveling, and bad block management (to only expose the good blocks) "beneath" this interface level.

This different logical interface provides several advantages over standard flash interfaces or managed NAND interfaces, including ONFI Block Abstraction (BA) or Toshiba LBA. For example, separation of the memory-specific functions that may vary from memory type and generation (e.g., NAND vs. 15 3D (or NOR) and 5×nm vs. 4×nm vs. 3×nm) allows for different amounts of ECC, vendor-unique and memoryunique schemes for error prevention and correction schemes, such as handling disturbs and safe zones, and allows vendorunique algorithms to remain "secret" within the controller 20 and firmware. Additionally, there is greater commonality between technology (and vendors) at this logical interface level, which enables quicker time to market. Further, this allows much closer to 1:1 command operation, meaning improved and more-predictable performance versus man- 25 aged NAND or other higher level interfaces.

There are additional advantages associated with this controller architecture. For example, it allows for independent development, test, and evolution of memory technology from the host and other parts of the system. It can also allow for 30 easier and faster deployment of next generation memories, since changes to support those memories are more localized. Further, it allows memory manufactures to protect secret algorithms used to manage the raw flash. Also, page management can be integrated with the file system and/or other 35 logical mapping. Thus, combined with standard external interfaces (electrical and command sets), this architecture makes it easier to design in raw flash that is more transparent from generation to generation.

There is at least one other secondary benefit from the use of 40 this architecture—the controller 300 only presents a single electrical load on the external interface and drives the raw flash internal to the MCP. This allows for potentially greater system capacity without increasing the number of flash channels, higher speed external interfaces (since fewer loads), and 45 higher-speed internal interfaces to the raw flash devices (since very tightly-controlled internal design (substrate connection) is possible).

Another advantage associated with the controller of this embodiment is that is can be used to provide a "split bus" 50 architecture through the use of different host and memory buses, potentially at different speeds (i.e., the bus between the host and the controller can be different from the bus between the controller and the flash memory device(s)). (As used herein, a "bus" is an electrical connection of multiple devices 55 (e.g., chips or dies) that have the same interface. For example, a point-to-point connection is a bus between two devices, but most interface standards support having multiple devices connected to the same electrical bus.) This architecture is especially desired in solid-state drives (SSDs) that can poten- 60 tially have hundreds of flash memory devices. In conventional SSD architectures, the current solution is to package N normal flash memory devices in a multi-chip package (MCP), but this still creates N loads on a bus, creating N times the capacitance and inductance. The more loads on a bus, the slower it 65 operates. For example, one current architecture can support a 80 MHz operation with 1-4 devices but can support only a 40

10

MHz operation with 8-16 devices. This is the opposite of what is desired—higher speeds if more devices are used. Furthermore, more devices imply the need for greater physical separation between the host and the memory MCPs. For example, if 16 packages were used, they will be spread over a relatively large physical distance (e.g., several inches) in an arbitrary topology (e.g., a bus or star-shaped (or arbitrary stub) topology). This also reduces the potential performance of any electrical interface. So, to obtain, for example, 300 MHz of transfers (ignoring bus widths), either four fast buses or eight slow buses can be used. But, the fast buses could only support four flash memory devices each, or 16 total devices, which is not enough for most SSDs today. If the buses run faster, the number of interface connections (pins and analog interfaces) can be reduced, as well as potentially the amount of registers and logic in the host.

Because the controller 300 in this embodiment splits the interconnection between the host and the raw flash memory device(s) into a separate host side interface and a flash side interface with a buffer in between, the host bus has fewer loads and can run two to four times faster. Further, since the memory bus is internal to the MCP, it can have lower power, higher speed, and lower voltage because of the short distance and finite loads involved. Further, the two buses can run at different frequencies and different widths (e.g., one side could use an 8-bit bus, and the other side can use a 16-bit bus).

While some architectures may insert standard transceivers to decouple these buses, the controller 300 of this embodiment can use buffering and can run these interfaces at different speeds. This allows the controller 300 to also match two different speed buses, for example, a flash side interface bus running at 140 MB/sec and an ONFI bus that runs at either 132 or 166 MB/sec. A conventional bus transceiver design would have to pick the lower of the two buses and run at 132 MB/sec in this example, while the controller 300 of this embodiment can achieve 140 MB/sec by running the ONFI bus at 166 MB/sec and essentially have idle periods. Accordingly, the controller 300 of this embodiment provides higher performance at potentially lower cost and/or lower power and interface flexibility between different products (e.g., different speed and width host and memory buses, fewer loads on the host in a typical system (which enables faster operation and aggregation of the memory bus bandwidth to the host interface), and different interfaces on the host and memory side with interface translation)

As mentioned above, a single controller can also have multiple flash side interface(s) 335 to the flash memory device(s), which also enables further parallelism between raw flash memory devices and transfers into the controller, which allows the flash side interface to run slower (as well as faster) than the host side interface 325. A single controller can also have multiple host side interfaces that may be connected to different host controller interfaces to allow for greater parallelism in accessing the flash memory device(s), to share the controller, or to better match the speed of the flash side interface (which could be faster than the host side interface for the reasons described above).

Another advantage of importing a NAND interface to a host relates to the use of a distributed controller architecture. Today, flash memory devices are typically implemented with a single level of controller. In large solid-state drives (SSDs), there may be tens or even hundreds of flash devices. In high-performance devices, it may be desirable to have parallel operations going on in as many of these flash devices as possible, which may be power constrained. There are interface specs today at 600 MB/sec, and these are still increasing. To reach this level of performance requires very fast control-

lers, memories, and ECC modules. Today, high performance controllers are built with either one or a small number of ECC modules and one or two microprocessors to handle memory device management. Since some of the functions are very localized to the memory devices themselves, such as ECC, 5 with the controller 300 of this embodiment, a two-tiered network of devices can be utilized. Specifically, the host 320 can manage the host interface and high-level mapping of logical contents, and one or more controllers 300 can manage one or more raw NAND flash memory devices to provide 10 local management of memory device functions (e.g., ECC) and parallelism in the execution of these functions due to parallel execution of the controller 300 and the host 320 and parallel execution of multiple controllers 300 handling different operations in parallel on different memories 320. In 15 contrast to conventional controllers in SSDs, which perform memory device management functions in one place, by splitting these functions into two layers, this architecture can take advantage of parallel performance in two ways (e.g., between host and slave, and between many slaves). This enables to 20 higher total performance levels (e.g., 600 MB/sec) without having to design a single ECC module or microprocessor that can handle that rate.

Yet another advantage of this architecture is that a higherlevel abstraction of the raw memory can be developed, such 25 that system developers do not need to know about error recovery or the low-level details of the memory, such as ECC and data scrambling, since the controller 300 can be used to perform those functions in addition to handling memoryspecific functions such as read, erase, and program disturbs, 30 and safe zones. This level of support is referred to herein as "corrected" flash," which is logically in between raw flash and managed NAND. On the other hand, this architecture is not fully managed memory in the sense of page or block management at a logical level and may require the host to 35 provide for logical-to-physical mapping of pages and blocks. However, the controller 300 can still present some flash memory management restrictions to the host and its firmware, such as: only full pages can be programmed, pages must be written in order within a block, and pages can only be written 40 once before the entire block must be erased. Wear leveling of physical blocks to ensure that they are used approximately evenly can also be performed by the controller 300; however, the host 320 can be responsible for providing this function. Also, the controller 300 preferably presents the host 320 with 45 full page read and write operations into pages and blocks of NAND. The characteristics of logical page size and block size will likely be the same as the underlying NAND (unless partial page operations are supported). The majority of the spare area in each physical page in the raw NAND will be 50 used by the controller 300 for ECC and its metadata. The controller 300 can provide for a smaller number of spare bytes that the using system can utilize for metadata management.

Embodiments Relating to Detecting a Transmission Error Over a NAND Interface

With reference to FIG. 3, transmission errors may occur as data is being sent from the host 320 to the controller 300 over a NAND interface bus to the host-side NAND interface 325. Since ECC is generated and checked within the controller 300, there is no ECC protecting the data transmitted over the 60 host-side NAND interface 325. This problem and a proposed solution will now be discussed in conjunction with FIG. 4.

FIG. 4 is a block diagram of a controller 400 of an embodiment for writing data to and reading data from one or more flash memory device(s) 430. As shown in FIG. 4, the controller 400 in this embodiment comprises a first NAND interface 425 configured to transfer data between the controller 400

and a host 420 (having a host controller 421) using a NAND interface protocol, as well as second NAND interface(s) 435 configured to transfer data between the controller 400 and one or more flash memory device(s) 430 using a NAND interface protocol. As discussed above, the NAND interface protocol used by each interface 425, 435 can be the same protocol or can be different protocols. As also discussed above, the controller 400 and the flash memory device(s) 430 can be packaged in different packages, can both reside within a common multi-chip package, or can be integrated on the same die. Also, in one embodiment, the host 420 performs logical-to-physical address mapping, so the host 420 provides the controller 400 with a physical address over the first NAND interface 425 along with a command to write or read to that physical address.