(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5838256号

(P5838256)

(45) 発行日 平成28年1月6日(2016.1.6)

(24) 登録日 平成27年11月13日(2015.11.13)

(51) Int.Cl.

G06F 3/00 (2006.01)

F 1

G06F 3/00

G06F 3/00A

V

請求項の数 9 (全 11 頁)

(21) 出願番号 特願2014-503697 (P2014-503697)

(86) (22) 出願日 平成24年3月30日 (2012.3.30)

(65) 公表番号 特表2014-510356 (P2014-510356A)

(43) 公表日 平成26年4月24日 (2014.4.24)

(86) 國際出願番号 PCT/US2012/031350

(87) 國際公開番号 WO2012/138550

(87) 國際公開日 平成24年10月11日 (2012.10.11)

審査請求日 平成26年12月24日 (2014.12.24)

(31) 優先権主張番号 13/079,912

(32) 優先日 平成23年4月5日 (2011.4.5)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVICES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンノイベイル、ビィ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・ブレイス、メイル・ストップ

・68(番地なし)

(74) 代理人 100108833

弁理士 早川 裕司

(74) 代理人 100111615

弁理士 佐野 良太

最終頁に続く

(54) 【発明の名称】柔軟且つ拡張可能なシステムアーキテクチャのためのスロット設計

## (57) 【特許請求の範囲】

## 【請求項 1】

プリント回路基板とコネクタとを備える装置であって、

前記プリント回路基板は、

前記プリント回路基板の第1の表面上の電気接点のパターンであって、第1のコネクタ部を受け入れるように作用する第1の部分と、第2のコネクタ部を受け入れるように作用する第2の部分とを備えるパターンであって、前記第1の部分は第1の通信リンク型に対応しており、前記第1及び第2の部分は共同して第2の通信リンク型に対応している、パターンと、

前記第1の部分及び第1のデバイスフットプリントに結合された第1の導電性トレースであって、前記第1及び第2の通信リンク型のうち選択された通信リンク型に応じて選択的に構成可能な第1の導電性トレースと、

前記第2の部分及び前記第1のデバイスフットプリントに結合された第2の導電性トレースと、を備え、

前記コネクタは、

前記パターンに結合されており、第1のコネクタ部と第2のコネクタ部とを備えており、前記第1の通信リンク型に応じて、前記第1のコネクタ部を、第1の数の端子を有する第1のデバイスに結合することが可能であり、前記第2の通信リンク型に応じて、前記第1のコネクタ部及び前記第2のコネクタ部を、第2の数の端子を有する第2のデバイスに結合することが可能であり、

10

20

前記第1の数は前記第2の数未満である、

装置。

【請求項2】

前記第1の通信リンク型はA C結合であつて、前記第2の通信リンク型はD C結合である、請求項1に記載の装置。

【請求項3】

前記第1の導電性トレースは、前記第1の部分及び前記第1のデバイスフットプリントをA C結合するように構成されており、前記第2の導電性トレースは、浮動状態にある、請求項1に記載の装置。

【請求項4】

前記第1の導電性トレースの個別のトレースの第1及び第2の接続点に結合された第1のスイッチを更に備える、請求項1に記載の装置。

【請求項5】

コンデンサと直列に結合された第2のスイッチを更に備え、

前記第2のスイッチ及び前記コンデンサは、前記第1のスイッチと並列に結合されており、前記第1及び第2の接続点に結合されている、請求項4に記載の装置。

【請求項6】

前記第1のデバイスフットプリントは、前記第1の通信リンク型の第1のインターフェースと、前記第2の通信リンク型の第2のインターフェースとを含むプロセッサを受け入れ可能である、請求項1に記載の装置。

10

【請求項7】

前記第1の通信リンク型は、ペリフェラルコンポーネントインターフェクトエクスプレス（PCI-E）であり、前記第2の通信リンク型は、ハイパートランスポート（HT）である、請求項1に記載の装置。

【請求項8】

前記第1の通信リンク型の通信リンク及び前記第2の通信リンク型の通信リンクは、シリアルバス通信リンクである、請求項1に記載の装置。

【請求項9】

前記第1の通信リンク型は第1の数の信号に関連付けられており、前記第2の通信リンク型は第2の数の信号に関連付けられており、前記信号の第1の数は前記信号の第2の数未満である、請求項1に記載の装置。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、計算システム、より具体的には、計算システムにおける接続に関する。

【背景技術】

【0002】

一般に、計算システムにおけるデバイスは、相互接続又はリンクと呼ばれる論理的な接続を介して通信する。例示的なリンクプロトコルに対応する典型的なリンクは、1つ以上のレーンを含む2つのポート間のポイントトゥポイントの通信チャネルである。個別のレーンは、送信及び受信の対のラインから構成される。ラインは、シングルエンドライン又は差動ラインであつてもよい。リンクの少なくとも一実施形態において、それぞれのレーンは、送信及び受信の対の差動ラインを含み、すなわち、それぞれのレーンは、完全な二重通信に対応するために、リンクのエンドポイント間に4つの信号経路を含む。例示的な低速デバイスは、単一のレーンリンクを使用する一方で、例示的な高速デバイス（例えばグラフィックアダプタ）は、遙かに広域の複数のレーンリンクを使用する。

40

【0003】

少なくとも1つの実施形態では、リンクは、シリアル通信を実装する。シリアルリンクは、データの特定の語のビットが目的地に同時に到着することを必要としないため、シリアル通信は、並列の通信リンクと比較して、タイミングスキュームによってあまり影響され

50

ない。シリアル通信の技術は、通信リンクを介して、1度に1ビットのデータを順次送信する。例示的なシリアル通信リンクとしては、ペリフェラルコンポーネントインターフェクトエクスプレス（P C I E）、ハイパートランスポート（以前はライトニングデータトランスポートとして知られていた）、シリアルアドバンストテクノロジーアタッチメント（シリアルA T A）、ユニバーサルシリアルバス（U S B）、I E E E 1 3 9 4 インタフェース、シリアルラピッドI O及びシリアルアタッチドスマールコンピュータシステムインターフェース（S A S）が挙げられる。処理システムの少なくとも1つの実施形態では、2つ以上のタイプのシリアル通信リンクが使用される（例えば、P C I E及びハイパートランスポート）。ハイパートランスポートは、双方向、シリアル、広帯域幅、低レイテンシ、ポイントトゥポイントのリンクを使用する、コンピュータプロセッサの相互接続のためのプロトコルである。典型的なハイパートランスポートリンクは、2～32ビットの範囲のビット幅に対応する。しかし、ハイパートランスポートリンクは、側波帯制御とコマンド信号とを必要とする。加えて、ハイパートランスポートは、D C 結合リンクである。ペリフェラルコンポーネントインターフェクトエクスプレス（P C I E）は、典型的に、基板レベルの相互接続（例えば、マザーボード実装された周辺機器へのリンク用）として使用され、アドインボードのための拡張カードインターフェースとして使用される、コンピュータ拡張カード標準である。典型的なP C I Eスロットは、1～16のレーンを含み、A C 結合される。それぞれのレーンは、典型的に、1対の送信差動信号と、1対の受信差動信号とを含む。一般に、ハイパートランスポート及びP C I Eリンクは、実質的に同じデータレートに対応する。

10

20

#### 【0004】

例示的な処理システムは、機能性を処理システムに付加するための拡張スロット（すなわちスロット）を有するプリント回路基板アセンブリ（例えば、マザーボード、バックプレーン又は他のプリント回路基板アセンブリ）を含む。例示的な拡張ボード（すなわち、拡張カード、アダプタカード又はアクセサリカード）は、デバイス（例えば、プロセッサ又は周辺デバイス）を含む。少なくとも1つの実施形態では、拡張スロットは、プリント回路基板アセンブリ上のプロセッサ又はデバイスによって使用され、且つ、コンポーネント（例えば、デバイス又は拡張ボード）によって使用される通信リンクプロトコルに対応するコネクタを使用して、コンポーネントをプリント回路基板に結合する。

30

#### 【0005】

少なくとも1つの実施形態では、処理システム及びコネクタは、ブレードサーバに含まれる。本明細書で呼ばれるように、ブレードサーバ（すなわちブレード）は、プロセッサ、メモリ、I / O 及び不揮発性記憶要素を含む、プリント回路基板アセンブリである。典型的なブレードサーバは、他のサーバシステムと比較して、物理的空間とエネルギーとの使用を低減するモジュール式設計を有する。典型的なブレード筐体は、ブレードシステムを形成し、システム用の電力、冷却、ネットワーク化、相互接続及び管理のうち1つ以上を提供するために、複数のブレードを含む。製造者は、単一のブレードにオペレーティングシステム及びアプリケーションを有する完全なサーバをパッケージ化する。ブレードは、複数のブレードに共通のシャシー内で独立して作動し得る。

40

#### 【発明の概要】

#### 【0006】

本発明の少なくとも1つの実施形態において、装置は、プリント回路基板を含む。プリント回路基板は、第1のコネクタ部を受け入れるように作用する第1のフットプリント部と、第2のコネクタ部を受け入れるように作用する第2のフットプリント部とを備えるコネクタフットプリントを含む。第1のフットプリント部分は、第1の通信リンク型に対応し、第1及び第2のフットプリント部は共同して、第2の通信リンク型に対応する。プリント回路基板は、第1のフットプリント部及び第1のデバイスフットプリントに結合された第1の導電性トレースを含む。第1の導電性トレースは、第1及び第2の通信リンク型のうち選択された1つの通信リンク型に応じて、選択的に構成可能である。プリント回路基板は、第2のフットプリント部及び第1のデバイスフットプリントに結合された第2の

50

導電性トレースを含む。装置の少なくとも 1 つの実施形態では、第 1 の通信リンク型は A C 結合されており、第 2 の通信リンク型は D C 結合されている。第 1 の導電性トレースは、第 1 のフットプリント及びデバイスフットプリントを A C 結合するように構成されてもよく、第 2 の導電性トレースは浮動状態にあってもよい。装置は、第 1 の導電性トレースの個別のトレースの第 1 及び第 2 の接続点に結合された、第 1 のスイッチを含んでもよい。装置は、第 1 及び第 2 の接続点に結合されたゼロオーム抵抗器、ジャンパ線、ワイヤ及びコンデンサのうち 1 つを含んでもよい。装置は、コンデンサと直列に結合された第 2 のスイッチを含んでもよく、第 2 のスイッチ及びコンデンサは、第 1 のスイッチに並列に結合され、且つ、第 1 及び第 2 の接続点に結合されてもよい。装置は、コネクタフットプリントに結合されたコネクタを含んでもよい。コネクタは、第 1 のコネクタ部及び第 2 のコネクタ部を含んでもよい。コネクタは、第 1 の通信リンク型に応じて、第 1 のコネクタ部を、第 1 の数の端子を有する第 1 のデバイスに結合することができてもよく、第 2 の通信リンク型に応じて、第 1 のコネクタ部及び第 2 のコネクタ部を、第 2 の数の端子を有する第 2 のデバイスに結合することができてもよく、端子の第 1 の数は、端子の第 2 の数未満である。装置は、コネクタに接続されたプロセッサを含んでもよい。装置は、コネクタに接続された周辺デバイスを含んでもよい。第 1 のデバイスフットプリントは、第 1 の通信リンク型の第 1 のインターフェースと、第 2 の通信リンク型の第 2 のインターフェースとを含むプロセッサを受け入れてもよい。第 1 の通信リンク型は、ペリフェラルコンポーネントインターフェクトエクスプレス (PCI-E) であってもよく、第 2 の通信リンク型は、ハイパートランスポート (HT) である。第 1 の通信リンク型の通信リンク及び第 2 の通信リンク型の通信リンクは、シリアルバス通信リンクであってもよい。第 1 の通信リンク型は、第 1 の数の信号と関連付けられてもよく、第 2 の通信リンク型は、第 2 の数の信号と関連付けられてもよい。信号の第 1 の数は、信号の第 2 の数未満であってもよい。10

#### 【0007】

本発明の少なくとも 1 つの実施形態では、プリント回路基板アセンブリの製造方法は、コネクタが受け入れたデバイスと関連付けられた通信リンク型に応じて、プリント回路基板上のコネクタフットプリント及びデバイスフットプリントに結合された導電性トレースを構成するステップを含む。導電性トレースは、第 1 の通信リンク型に応じて、デバイスフットプリントをコネクタフットプリントに結合するように構成され得るとともに、第 2 の通信リンク型に応じて、デバイスフットプリントをコネクタに結合するように構成され得る。方法の少なくとも 1 つの実施形態では、第 1 の通信リンク型は、ペリフェラルコンポーネントインターフェクトエクスプレス (PCI-E) であって、第 2 の通信リンク型は、ハイパートランスポート (HT) である。第 1 の通信リンク型は A C 結合されてもよく、第 2 の通信リンク型は D C 結合されてもよい。構成するステップは、デバイスフットプリントに結合されたデバイスと関連付けられた通信リンクに応じて、導電性トレースを選択的に構成するステップを含んでもよい。構成するステップは、導電性トレースをコネクタフットプリントに D C 結合するステップを含んでもよい。構成するステップは、導電性トレースの一部をコネクタフットプリントに A C 結合するステップを含んでもよい。導電性トレースの第 2 の部分は浮動状態にあってもよい。30

#### 【0008】

本発明は、添付の図面を参照することによってより良く理解され、多くの目的、特徴及び利点が、当業者に明らかにされ得る。

#### 【図面の簡単な説明】

#### 【0009】

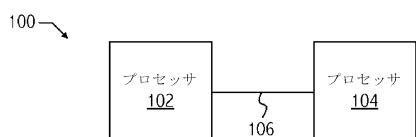

【図 1】例示的な多重プロセッサ処理システムを示す図である。

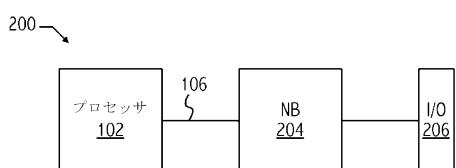

【図 2】周辺デバイスを含む、例示的な処理システムを示す図である。

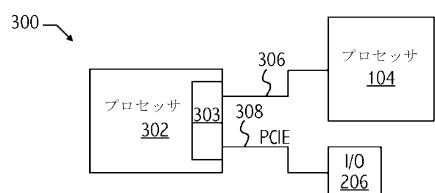

【図 3】周辺デバイスを含む、例示的な多重プロセッサ処理システムを示す図である。

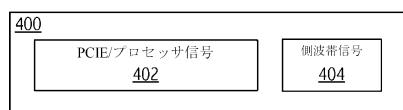

【図 4】本発明の少なくとも 1 つの実施形態と一致するコネクタを示す図である。

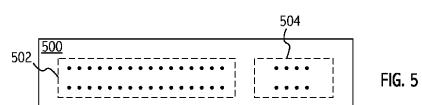

【図 5】本発明の少なくとも 1 つの実施形態と一致するコネクタフットプリントを示す図である。50

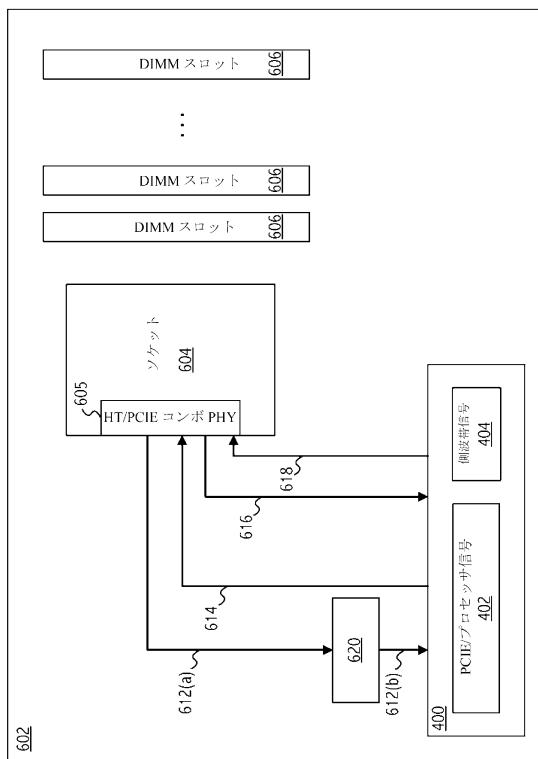

【図6】本発明の少なくとも1つの実施形態と一致する図4のコネクタを含む、例示的な処理システムを示す図である。

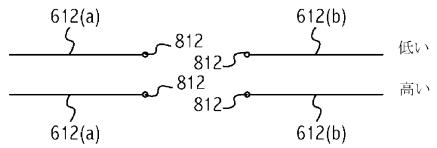

【図7】本発明の少なくとも1つの一実施形態と一致する、プリント回路基板上のリンクの例示的な導電性トレースを示す図である。

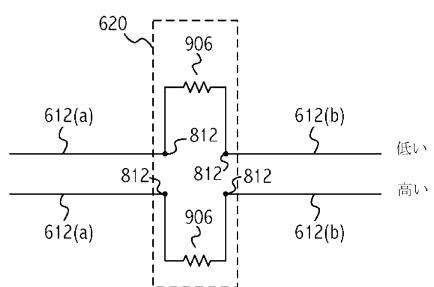

【図8A】本発明の少なくとも1つの実施形態と一致する、図7の導電性トレースの例示的な構成を示す図である。

【図8B】本発明の少なくとも1つの実施形態と一致する、図7の導電性トレースの例示的な構成を示す図である。

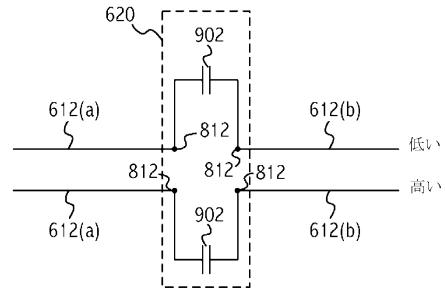

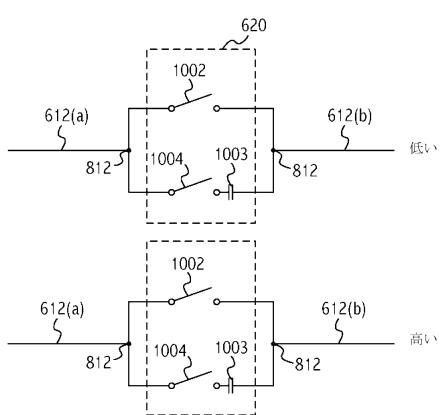

【図9】本発明の少なくとも1つの実施形態と一致する、図7の導電性トレースの例示的な構成を示す図である。

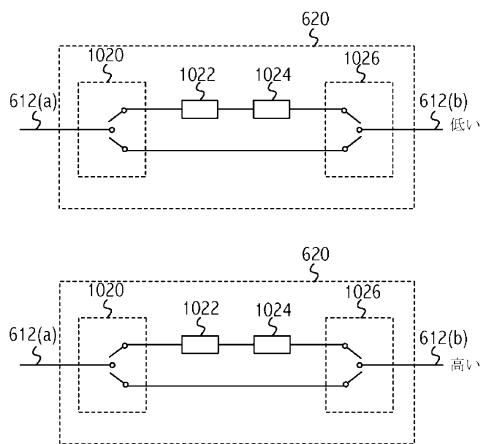

【図10】本発明の少なくとも1つの実施形態と一致する、図7の導電性トレースの例示的な構成を示す図である。

【0010】

異なる図面における同様の参照符号の使用は、類似又は同一の項目を示す。

【発明を実施するための形態】

【0011】

図1を参照すると、例示的な処理システム（例えば、処理システム100）において、プロセッサ（例えば、中央処理ユニット、コア及び／又はハードウェアアクセラレータ、例えばプロセッサ102，104）は、リンク（例えば、リンク106）を使用して互いに結合されている。システム100の少なくとも1つの実施形態において、リンク106は、ハイパートランスポートリンクである。図2を参照すると、例示の処理システム200において、リンク106は、プロセッサ102を他のプロセッサに結合するよりもむしろ、プロセッサ102を、プロセッサ102と1つ以上の周辺デバイス又は他の集積回路（例えば、I/O206）との間の通信を取り扱う集積回路（例えば、集積回路204）に結合する。少なくとも1つの実施形態において、集積回路204は、ノースブリッジ回路である。図3を参照すると、システム300は、ノースブリッジの機能性をプロセッサに統合するインターフェース回路（例えば、ノースブリッジ303）を有するプロセッサ（例えば、プロセッサ302）を含む。

【0012】

例示的なシステムにおいて、プロセッサ（例えば、プロセッサ102）は、プロセッサに結合するコンポーネント（すなわち、拡張プリント回路基板又はデバイス）用の所定数のスロットを有するプリント回路基板に接続されている。例えば、プリント回路基板は、別のプロセッサを含むコンポーネントをプロセッサ102に結合するためのm個のスロットと、I/Oデバイスを含むコンポーネントをプロセッサ102に結合するためのn個のスロットとを含む。本明細書で参照されるように、プリント回路基板上のスロットは、コネクタと、コネクタのフットプリントと一致するパターンで構成されたコネクタに電気的に結合するための1つ以上のパッド又は孔と、パッド又は孔のパターンに結合されたプリント回路基板上の導電性トレースとを含む。コネクタと、パッド又は孔と、プリント回路基板上の導電性トレースとは、任意の好適な生産技術によって形成されてもよい。一般に、コネクタは、あるコンポーネントと別のコンポーネントとの間の機械的及び電気的接続を提供する機械的コンポーネントである。デバイスを受け入れるためのコネクタは、ソケットとしてみなされてもよく、デバイスをコネクタ内に物理的に固定するためのレバー又はラッチを含んでもよい。典型的なコネクタは、コンポーネントの電気リード線、ピン又はランド部の各々のためのプラスチック及び金属接点を含む。各スロットが通信リンクの特定の型に対して構成されることに留意されたい。すなわち、第1のリンク型を使用するコンポーネントと通信するように構成されたスロットは、第2のリンク型を使用するコンポーネントと通信するように構成されていない。同様に、第2のリンク型を使用するコンポーネントと通信するように構成されたスロットは、第1のリンク型を使用するコンポーネントと通信するように構成されていない。例えば、少なくとも1つの実施形態において、プロセッサ302は、第1の型のリンク（例えば、PCI Eリンク308）を介して周

10

20

30

40

50

辺デバイス（例えば、I/O 206）と通信するインターフェースと、第2の型のリンク（例えば、ハイパートランスポートリンク306）を介してプロセッサ（例えば、プロセッサ104）と通信するインターフェースとを含む。しかし、プロセッサ302を含むプリント回路基板アセンブリは、特定の型のリンク専用の1つ以上のスロットを含む。

#### 【0013】

プリント回路基板アセンブリの少なくとも1つの実施形態では、プリント回路基板は、1つ又は別の異なるリンク型に対応し得る別のデバイスにプロセッサを結合するための異なるリンク型に対応する複数のバスをプリント回路基板上に含むよりもむしろ、何れかのリンク型で使用され得るフレキシブルバス（flexible bus）を含む。プリント回路基板アセンブリの少なくとも1つの実施形態では、フレキシブルコネクタ（flexible connector）は、プリント回路基板上で、そのフレキシブルバスに結合されている。図4を参照すると、フレキシブルコネクタは、2つのリンク型（例えば、例示のハイパートランスポートリンク用の20レーン）のうち最も広いものに対して十分な電気接点及びリード線を含む。例えば、電気的コネクタ400は、2つのコネクタ部を含む。第1のコネクタ部（例えば、コネクタ部402）は、PCI Eスロット（例えば、16レーン）を支持するための接点を含む。第2のコネクタ部（例えば、コネクタ部404）は、ハイパートランスポートスロットによって必要とされる、付加的信号用の付加的接点（例えば、ハイパートランスポート及び側波帯信号用の4つのレーン）を含む。PCI Eコンポーネントは、第1のコネクタ部にプラグ接続することができ、第2のコネクタ部は使用されない。ハイパートランスポートリンクに対応するコンポーネントは、両方のコネクタ部にプラグ接続することができる。したがって、同じソケットは、何れかの型のリンクに対応するコンポーネントを結合するように使用されてもよく、これにより、例示的なプリント回路基板アセンブリによって実装されるシステムアーキテクチャを拡張するための柔軟性を提供する。

10

20

#### 【0014】

図5を参照すると、少なくとも1つの実施形態では、プリント回路基板は、上述したように、フレキシブルコネクタのフットプリントと一致するランドパターン（例えば、ランドパターン500）を含む。少なくとも1つの実施形態では、ランドパターンは、フレキシブルコネクタの対応する電気リード線を受け入れるように配置された電気接点（例えば、パッド又は孔）を含む。少なくとも1つの実施形態では、ランドパターン500は、コネクタ部402, 404にそれぞれ対応する、第1のランドパターン部（例えば、ランドパターン部502）及び第2のランドパターン部（例えば、ランドパターン部分504）を含む。ランドパターン500は、対応するコネクタの電気リード線をプリント回路基板上の導体に電気的に結合するのに好適な任意の幾何学的形状及び構成を有してもよいことに留意されたい。

30

#### 【0015】

図6を参照すると、プリント回路基板アセンブリ（例えば、プリント回路基板アセンブリ600）は、統合されたPCI E / ハイパートランスポートインターフェースを含むプロセッサ用のソケット（例えば、インターフェース（例えば、インターフェース605）を含むソケット604）と、メモリスロット（例えば、デュアルインラインメモリモジュールスロット606）と、フレキシブルバス（例えば、導電性トレース612, 614, 616, 618）及びフレキシブルコネクタ（例えば、コネクタ400）を含むフレキシブルな拡張スロットとが装着されたプリント回路基板（例えば、プリント回路基板602）を含む。少なくとも1つの実施形態では、プリント回路基板アセンブリ600には、さらに、ソケット604内のプロセッサと、コネクタ400に接続されたコンポーネントとが装着されている。少なくとも1つの実施形態では、導電性トレース（例えば、トレース612）は、インターフェース605からコネクタ400への信号を通信するインターフェースのレーンを結合し、導電性トレース（例えば、トレース614）は、コネクタ400からインターフェース605への信号を通信するインターフェースのレーンを結合する。回路（例えば、回路620）は、プリント回路基板アセンブリ600の特定の実施形態によって必要と

40

50

される型のインターフェースに応じて選択的に設定及び／又は装着されたコンポーネントを含む。少なくとも1つの実施形態では、回路620は、導電性トレース部612(a)と導電性トレース部612(b)との間で結合されており、回路620には、PCI Eリンク用のAC結合又はハイパートransportリンク用のDC結合を実装するように構成されたスイッチ、コンデンサ、抵抗器及び／又はジャンパ線が装着されている。プリント回路基板602の少なくとも1つの実施形態では、導電性トレース616, 618は、コネクタ400とソケット604との間のハイパートransportリンクの側波帯信号を結合するために含まれている。したがって、プリント回路基板アセンブリ600のフレキシブルスロットは、PCI Eリンク又はハイパートransportリンクと一致するコンポーネントを受け入れるように構成されている。すなわち、プリント回路基板アセンブリ600のフレキシブルスロットは、PCI E又はハイパートransportプロトコルの何れかと一致する通信インターフェースに対応するコネクタを受け入れるように構成されている。10

#### 【0016】

図6及び図7を参照すると、プリント回路基板602の少なくとも1つの実施形態では、導電性トレース部612(a), 612(b)は、1つ以上の回路要素を導電性トレース612に結合するための接続点812を含む。少なくとも1つの実施形態では、特定の導電性トレース612の接続点812は、回路要素を導電性トレース部612(a), 612(b)にシリアル結合するための間隙によって分離されている。プリント回路基板アセンブリ600を製造するための技術は、プリント回路基板アセンブリの用の対象通信リンクに応じて、回路(例えば、回路620)を導電性トレース部612(a), 612(b)に結合することを含む。20

#### 【0017】

図6及び図8Aを参照すると、少なくとも1つの実施形態では、回路620は、導電性トレース612と直列に結合するための少なくとも1つのコンデンサを含む。少なくとも1つの実施形態では、回路620はコンデンサ902を含んでおり、回路620は接続点812に結合されており、これらによって導電性トレース部612(a), 612(b)が静電容量結合されている(すなわち、AC結合されている)。図8Bを参照すると、回路620の少なくとも1つの実施形態では、インターフェース605はコネクタ400にDC結合されており、導電性トレース部612(a), 612(b)はDC結合されており、抵抗性導体(例えば、ゼロオーム抵抗器906)がコンデンサ902の代わりに使用されている。30

#### 【0018】

図6及び図9を参照すると、少なくとも1つの実施形態では、回路620は、導電性トレース612と直列に結合するための1つ以上のアナログスイッチを含む。少なくとも1つの実施形態では、プリント回路基板アセンブリを製造するための技術は、特定のリンク型に応じて導電性トレース部612(a), 612(b)を選択的に結合するために、アナログスイッチを使用することを含む。例えば、DC結合されたリンク用のプリント回路基板602を構成するために、スイッチ1002が閉じられ、スイッチ1004が開かれ、回路部612(a), 612(b)が互いに効果的に抵抗結合される。AC結合されたリンク用のプリント回路基板602を構成するために、スイッチ1002が開かれ、スイッチ1004が閉じられ、コンデンサ1003を使用して、回路部612(a), 612(b)が互いに効果的に静電容量結合される。図9の実施形態は例示的のみであって、他の回路要素が、AC結合及びDC結合されたリンク(例えば、ジャンパ線、ゼロオーム抵抗器、リドライバ又は他の好適な回路要素)のために導電性トレース部612(a), 612(b)を結合するように使用されてもよいことに留意されたい。例えば、図10を参照すると、少なくとも1つの実施形態では、回路620は、1つの経路でマザーボードコンデンサ(例えば、コンデンサ1024)に接続され、且つ、別の経路で直接接続されている、アナログのデマルチプレクサ/マルチプレクサ回路(例えば、スイッチ1020, 1026)を含む。少なくとも1つの実施形態では、回路620は、信号反射を低減又は除去するために、少なくとも1つのリドライバ回路(例えば、リドライバ1022)を含4050

む。

#### 【0019】

プリント回路基板アセンブリ 600 の少なくとも 1 つの実施形態では、ソケット 604 内のプロセッサは、PCI E 又はハイパートransport によって通信し得る。プロセッサは、任意の好適な技術を使用して、どの型の通信リンクがコネクタ 400 に結合されたコンポーネントによって必要とされているかを特定し、それに応じて、プリント回路基板 602 を構成する。例えば、プロセッサは、1 つの型のリンクを想定し、そのリンク型用にプリント回路基板 602 を構成してもよい。プロセッサは、予期されない応答（例えば、予期されない電圧レベル）を受信すると、他のリンク型用にプリント回路基板 602 を再構成し、当該他のリンク型を使用してトレーニングする。プリント回路基板アセンブリ 600 の少なくとも 1 つの実施形態では、トレース 616, 618 は、トレース 612, 614 内の 8 つのデータレーンの各々の組のためのクロック信号及び制御信号を含む。少なくとも 1 つの実施形態では、ソケット 604 内のプロセッサは、ハイパートransport モードで出力を上げる。プロセッサは、DC 電圧レベルを検知するために、シングルエンジンの制御レーン受信器を使用する。プロセッサは、DC 電圧レベルで駆動されるクロック信号又は制御信号を含む任意のリンクをハイパートransport リンクとして初期化する。プロセッサは、クロックレーン及び浮動する制御レーンの両方との任意のリンクを PCI E リンクとして初期化する。10

#### 【0020】

少なくとも 1 つの実施形態では、コネクタ 400 は、PCI E の現在のピン及び / 又はハイパートransport の現在のピンを含み、これはコネクタ 400 に結合されたコンポーネントによって設定され、システムを適切に構成するためのシステムロジックによって検知される。プリント回路基板アセンブリ 600 の少なくとも 1 つの実施形態では、コネクタ 400 にプラグ接続されたカードは、コネクタ 400 に結合されたコンポーネントによって必要とされる通信リンクの型に基づいてスイッチ 1002 及びスイッチ 1004 を閉じるために使用される、制御信号（例えば、導電性トレース部 612 (a), 612 (b) に含まれない制御信号）を発生させる。20

#### 【0021】

コネクタ 400 及び当該コネクタの対応するフットプリントは、任意の好適なプロファイル及び配置（例えば、通常の密度又は高密度）を有してもよいことに留意されたい。コネクタ 400 は、第 1 のコンポーネントを第 2 のコンポーネントに連結するものとして記載されているが、他の実施形態では、コネクタ 400 は、第 1 のコンポーネントを複数のコンポーネントに結合する。例えば、少なくとも 1 つの実施形態では、コネクタ 400 は、第 1 のコンポーネントを 2 つのハイパートransport デバイスに結合し、各々が二分の一のバス幅のモードで作動する。少なくとも 1 つの実施形態では、コネクタ 400 は、I/O 拡張のための複数の I/O スロットを提供するトンネルカード又は処理能力拡張若しくはメモリ拡張を提供するための別のプロセッサカードに対して、第 1 の HT コンポーネントを結合する。30

#### 【0022】

回路及び物理的構造が本発明の実施形態を記載する際に概ね推定されている一方で、現代の半導体設計及び製造において、物理的構造及び回路がその後の設計、シミュレーション、試験又は製作段階で使用されるために好適なコンピュータ読取り可能な記述形態で実施されてもよいことがよく理解される。例示的な構成においてディスクリートのコンポーネントとして提示された構造及び機能性は、組み合わされた構造又はコンポーネントとして実装されてもよい。本発明の様々な実施形態は、回路と、回路システムと、関連する方法と、上記の回路、システム及び方法の符号化データ（例えば、VHSIC ハードウェア記述言語（VHDL）、ヴェリログ、GDSII データ、電子設計交換フォーマット（EDIF）及び / 又はガーバーファイル）を有する有形のコンピュータ可読媒体との全てを、本明細書に記載され、且つ、添付された特許請求の範囲に定義されるものとして含むことが想到される。加えて、コンピュータ可読媒体は、本発明を実装するために使用され得4050

る指示及びデータを格納してもよい。指示／データは、ハードウェア、ソフトウェア、ファームウェア又はそれらの組合せに關してもよい。

【0023】

本明細書に述べられた本発明の記載は例示的であり、以下の特許請求の範囲に記載された本発明の範囲を限定することを意図しない。例えば、本発明は、PCI-E及びハイパートランスポートリンクを含む実施形態において記載されているが、当業者は、本明細書での教示が異なる通信リンク標準に対応する他の型のインターフェースと共に利用され得ることを理解するであろう。本明細書に開示された実施形態の変形態様及び改変形態は、本明細書で述べられた記載に基づき、以下の特許請求の範囲に述べられるものとして本発明の範囲及び趣旨から逸脱することなく行われ得る。

10

【図1】

【図5】

【図2】

【図3】

【図4】

【図 6】

【図 7】

【図 8 A】

【図 8 B】

【図 10】

【図 9】

---

フロントページの続き

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 ラビ ピー . ピンギ

アメリカ合衆国 78739 テキサス州、オースティン、ティエラ リンダ レーン 8108

(72)発明者 ランジェ エイチ . ラム

アメリカ合衆国 78749 テキサス州、オースティン、ポンシャ パス 6813

(72)発明者 ジェイソン アール . タルパート

アメリカ合衆国 78741 テキサス州、オースティン、サンリッジ ドライブ 2900 #

1210

(72)発明者 プラビン ケイ . ハリー

アメリカ合衆国 78727 テキサス州、オースティン、ウィル ロジャース レーン 135

21

(72)発明者 ブライアン イー . ロンヘンリー

アメリカ合衆国 78738 テキサス州、オースティン、ワインズウェプト ドライブ 221

4

(72)発明者 アンドルー ダブリュー . シュタインバッハ

アメリカ合衆国 78746 テキサス州、オースティン、ワインター パーク ロード 190

0

(72)発明者 ジェフ エイチ . グリューガー

アメリカ合衆国 78733 テキサス州、オースティン、エルダー サークル 805

審査官 宮久保 博幸

(56)参考文献 米国特許第07815469(US, B1)

米国特許出願公開第2011/0063790(US, A1)

米国特許出願公開第2009/0006709(US, A1)

特表2013-505600(JP, A)

(58)調査した分野(Int.Cl. , DB名)

G 06 F 3 / 00