(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2015년10월22일

(11) 등록번호 10-1561802

(24) 등록일자 2015년10월13일

(51) 국제특허분류(Int. Cl.)

*H01L 27/32* (2006.01) *H01L 29/786* (2006.01)

(52) CPC특허분류

*H01L 27/3262* (2013.01)*H01L 29/786* (2013.01)

(21) 출원번호 10-2015-0025174

(22) 출원일자 2015년02월23일

심사청구일자 2015년02월23일

(65) 공개번호 10-2015-0101395

(43) 공개일자 2015년09월03일

(30) 우선권주장

1020140021500 2014년02월24일 대한민국(KR)

(56) 선행기술조사문헌

KR101065407 B1

KR1020130099693 A

KR1020040026005 A

(73) 특허권자

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

조성필

경기 고양시 일산서구 후곡로 10, 908동 1403호

(일산동, 후곡마을9단지아파트)

김용일

충남 당진시 송악읍 여망길 19-4

(74) 대리인

특허법인로얄

전체 청구항 수 : 총 19 항

심사관 : 김한수

(54) 발명의 명칭 박막 트랜지스터 기판 및 이를 이용한 표시장치

**(57) 요 약**

본 발명은 서로 다른 유형의 박막 트랜지스터들이 동일 기판 위에 배치된 박막 트랜지스터 기판 및 이를 이용한 표시장치에 관한 것이다. 본 발명에 의한 박막 트랜지스터 기판은, 기판, 제1 박막 트랜지스터 및 제2 박막 트랜지스터를 포함한다. 제1 박막 트랜지스터는 기판 위에 배치되며, 다결정 반도체 층, 제1 게이트 전극, 제1 소

(뒷면에 계속)

**대 표 도** - 도1a

스 전극 및 제1 드레인 전극을 포함한다. 제2 박막 트랜지스터는 기판 위에 배치되며, 산화물 반도체 층, 제2 게이트 전극, 제2 소스 전극 및 제2 드레인 전극을 포함한다. 제1 게이트 전극은 게이트 절연막을 사이에 두고 다결정 반도체 층과 중첩한다. 제1 게이트 전극의 상부에는, 질화막을 포함하는 중간 절연막이 배치된다. 제2 게이트 전극은, 제1 게이트 전극을 덮는 중간 절연막 위에 배치된다. 중간 절연막 위에는 제2 게이트 전극을 덮는 산화막이 배치된다. 산화물 반도체 층은, 산화막 위에서 제2 게이트 전극과 중첩하도록 배치된다. 제1 소스 전극 및 제1 드레인 전극은 중간 절연막과 산화막 사이에 배치된다. 제2 소스 전극 및 제2 드레인 전극은 산화물 반도체 층 위에 배치된다.

(52) CPC특허분류

*H01L 29/78618* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

다결정 반도체 층, 상기 다결정 반도체 층 위에 배치된 제1 게이트 전극, 제1 소스 전극 및 제1 드레인 전극을 포함하는 제1 박막 트랜지스터;

상기 다결정 반도체 층을 덮는 게이트 절연막;

제2 게이트 전극, 상기 제2 게이트 전극 위에 배치된 산화물 반도체 층, 제2 소스 전극 및 제2 드레인 전극을 포함하는 제2 박막 트랜지스터;

상기 제1 게이트 전극의 상부에 배치되며, 질화막을 포함하는 중간 절연막; 그리고

상기 중간 절연막 위에 배치되며, 상기 제2 게이트 전극을 덮는 산화막을 포함하며,

상기 제1 게이트 전극은 상기 게이트 절연막 위에 배치되며, 상기 다결정 반도체 층과 중첩하고,

상기 산화물 반도체 층은, 상기 산화막 위에서 상기 제2 게이트 전극과 중첩하도록 배치되며,

상기 제1 소스 전극, 상기 제1 드레인 전극 및 상기 제2 게이트 전극은, 서로 동일한 물질을 포함하며, 상기 중간 절연막과 상기 산화막 사이에 배치되고,

상기 제2 소스 전극 및 상기 제2 드레인 전극은 상기 산화물 반도체 층 위에 배치되는 표시장치.

#### 청구항 2

제 1 항에 있어서,

구동 회로를 더 포함하며,

상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터 중 적어도 어느 하나는 화소에 포함되며,

상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터 중 적어도 어느 하나는 상기 구동 회로에 포함되는 표시장치.

#### 청구항 3

삭제

#### 청구항 4

제 1 항에 있어서,

상기 제2 박막 트랜지스터는 화소를 선택하는 스위치 소자이고,

상기 제1 박막 트랜지스터는 상기 제2 박막 트랜지스터에 의해 선택된 상기 화소의 유기발광 다이오드를 구동하는 구동 소자인 표시장치.

#### 청구항 5

제 2 항에 있어서,

상기 구동 회로는,

데이터 전압을 출력하는 데이터 구동부;

상기 데이터 구동부로부터의 데이터 전압을 데이터 배선으로 분배하는 멀티플렉서; 그리고

스캔 월스를 게이트 배선으로 출력하는 게이트 구동부를 포함하고,

상기 제1 박막 트랜지스터와 상기 제2 박막 트랜지스터 중 적어도 어느 하나는 상기 멀티플렉서 및 상기 게이트

구동부 중 어느 하나에 포함되는 표시장치.

#### 청구항 6

제 1 항에 있어서,

상기 제1 소스 전극은, 상기 중간 절연막 및 상기 게이트 절연막을 관통하는 소스 콘택홀을 통해 상기 다결정

반도체 층의 일측부와 연결되고,

상기 제1 드레인 전극은, 상기 중간 절연막 및 상기 게이트 절연막을 관통하는 드레인 콘택홀을 통해 상기 다결

정 반도체 층의 타측부와 연결되고,

상기 제2 소스 전극은, 상기 산화물 반도체 층의 일측부와 접촉되고,

상기 제2 드레인 전극은, 상기 산화물 반도체 층의 타측부와 접촉되는 표시장치.

#### 청구항 7

삭제

#### 청구항 8

제 1 항에 있어서,

상기 제2 게이트 전극은, 상기 중간 절연막을 관통하는 게이트 콘택홀을 통해, 상기 제1 게이트 전극과 동일한

물질을 포함하는 게이트 배선과 연결되는 표시장치.

#### 청구항 9

제 1 항에 있어서,

상기 제2 소스 전극은, 상기 산화막을 관통하는 데이터 콘택홀을 통해, 상기 제2 게이트 전극과 동일한 물질을

포함하는 데이터 배선과 연결되는 표시장치.

#### 청구항 10

제 1 항에 있어서,

상기 중간 절연막은 하부 산화막을 더 포함하는 표시장치.

#### 청구항 11

제 10 항에 있어서,

상기 질화막은, 상기 하부 산화막 위에 배치된 표시장치.

#### 청구항 12

다결정 반도체 물질을 포함하는 제1 반도체 층;

상기 제1 반도체 층을 덮는 게이트 절연막;

상기 게이트 절연막 위에서 상기 제1 반도체 층과 중첩하는 제1 게이트 전극;

상기 제1 게이트 전극을 덮으며, 질화막을 포함하는 중간 절연막;

상기 중간 절연막 위에 배치되며, 동일한 물질을 포함하는, 제2 게이트 전극, 제1 소스 전극 및 제1 드레인 전극;

제2 게이트 전극, 상기 제1 소스 전극 및 상기 제1 드레인 전극을 덮는 산화막;

상기 산화막 위에서, 상기 제2 게이트 전극과 중첩하도록 배치되며, 산화물 반도체 물질을 포함하는 제2 반도체 층; 그리고

상기 제2 반도체 층 위에 배치된 제2 소스 전극 및 제2 드레인 전극을 포함하는 표시장치.

### 청구항 13

제 12 항에 있어서,

상기 제1 반도체 층, 상기 제1 게이트 전극, 상기 제1 소스 전극 및 상기 제1 드레인 전극은 제1 박막 트랜지스터에 포함되고,

상기 제2 반도체 층, 상기 제2 게이트 전극, 상기 제2 소스 전극 및 상기 제2 드레인 전극은 제2 박막 트랜지스터에 포함되는 표시장치.

### 청구항 14

제 13 항에 있어서,

구동 회로를 더 포함하며,

상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터 중 적어도 어느 하나는 화소에 포함되고,

상기 제1 박막 트랜지스터 및 상기 제2 박막 트랜지스터 중 적어도 어느 하나는 상기 구동 회로에 포함되는 표시장치.

### 청구항 15

제 13 항에 있어서,

상기 제2 박막 트랜지스터는 화소를 선택하는 스위치 소자이고,

상기 제1 박막 트랜지스터는 상기 제2 박막 트랜지스터에 의해 선택된 상기 화소의 유기발광 다이오드를 구동하는 구동 소자인 표시장치.

### 청구항 16

제 14 항에 있어서,

상기 구동 회로는,

데이터 전압을 출력하는 데이터 구동부;

상기 데이터 구동부로부터의 데이터 전압을 데이터 배선으로 분배하는 멀티플렉서;

스캔 필스를 게이트 배선으로 출력하는 게이트 구동부를 포함하고,

상기 제1 박막 트랜지스터와 상기 제2 박막 트랜지스터 중 적어도 어느 하나는 상기 멀티플렉서 및 상기 게이트

구동부 중 어느 하나에 포함되는 표시장치.

### 청구항 17

제 12 항에 있어서,

상기 제1 소스 전극은, 상기 중간 절연막 및 상기 게이트 절연막을 관통하는 소스 콘택홀을 통해 상기 제1 반도체 층의 일측부와 연결되고,

상기 제1 드레인 전극은, 상기 중간 절연막 및 상기 게이트 절연막을 관통하는 드레인 콘택홀을 통해 상기 제1 반도체 층의 타측부와 연결되고,

상기 제2 소스 전극은, 상기 제2 반도체 층의 일측부와 접촉되고,

상기 제2 드레인 전극은, 상기 제2 반도체 층의 타측부와 접촉되는 표시장치.

### 청구항 18

삭제

### 청구항 19

제 12 항에 있어서,

상기 제2 게이트 전극은, 상기 중간 절연막을 관통하는 게이트 콘택홀을 통해 상기 게이트 절연막 위에 배치된 상기 제1 게이트 전극과 동일한 물질을 포함하는 게이트 배선과 연결되는 표시장치.

### 청구항 20

제 12 항에 있어서,

상기 제2 소스 전극은, 상기 산화막을 관통하는 데이터 콘택홀을 통해 상기 중간 절연막 위에 배치된 상기 제2 게이트 전극과 동일한 물질을 포함하는 데이터 배선과 연결되는 표시장치.

### 청구항 21

제 12 항에 있어서,

상기 중간 절연막은, 하부 산화막을 더 포함하는 표시장치.

### 청구항 22

제 21 항에 있어서,

상기 질화막은, 상기 하부 산화막 위에 배치된 표시장치.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 서로 다른 유형의 박막 트랜지스터들이 동일 기판 위에 배치된 박막 트랜지스터 기판 및 이를 이용한 표시장치에 관한 것이다.

### 배경 기술

[0002] 정보화 사회가 발전함에 따라 화상을 표시하기 위한 표시장치에 대한 요구가 다양한 형태로 증가하고 있다. 표시장치 분야는 부피가 큰 음극선관(Cathode Ray Tube: CRT)을 대체하는, 얇고 가벼우며 대면적이 가능한 평판 표시장치(Flat Panel Display Device: FPD)로 급속히 변화해 왔다. 평판 표시장치에는 액정 표시장치(Liquid Crystal Display Device: LCD), 플라즈마 디스플레이 패널(Plasma Display Panel: PDP), 유기발광 표시장치(Organic Light Emitting Display Device: OLED), 그리고 전기영동 표시장치(Electrophoretic Display Device: ED) 등이 있다.

[0003] 능동형으로 구동하는 액정 표시장치, 유기발광 표시장치 및 전기영동 표시장치의 경우, 매트릭스 방식으로 배열된 화소 영역 내에 할당된 박막 트랜지스터가 배치된 박막 트랜지스터 기판을 포함한다. 액정 표시장치(Liquid Crystal Display Device: LCD)는 전계를 이용하여 액정의 광 투과율을 조절함으로써 화상을 표시한다. 유기발광 표시장치는 매트릭스 방식으로 배열된 화소 자체에 유기발광 소자를 형성함으로써, 화상을 표시한다.

[0004] 유기발광 다이오드 표시장치는 스스로 발광하는 자발광 소자로서 응답속도가 빠르고 발광효율, 휘도 및 시야각이 큰 장점이 있다. 특히, 에너지 효율이 우수한 유기발광 다이오드의 특징을 이용한 유기발광 다이오드 표시장치(Organic Light Emitting Diode display: OLEDD)에는 패시브 매트릭스 타입의 유기발광 다이오드 표시장치(Passive Matrix type Organic Light Emitting Diode display, PMOLED)와 액티브 매트릭스 타입의 유기발광 다이오드 표시장치(Active Matrix type Organic Light Emitting Diode display, AMOLED)로 대별된다.

[0005] 개인용 전자기기의 개발이 활발해짐에 따라, 표시장치도 휴대성 및/또는 착용성이 우수한 제품으로 개발이되고 있다. 이와 같이, 휴대용 혹은 웨어러블 장치에 적용하기 위해서는 저 소비 전력을 구현한 표시장치가 필요하다. 현재까지 개발된 표시장치에 관련된 기술로는 저 소비 전력을 구현하는 데 한계가 있다.

## 발명의 내용

### 해결하려는 과제

[0006] 본 발명의 목적은 상기 종래 기술의 문제점을 해결하고자 안출 된 발명으로써, 동일한 기판 위에 두 종류 이상의 박막 트랜지스터들을 구비한 박막 트랜지스터 기판 및 이를 이용한 표시장치를 제공하는 데 있다. 본 발명의 다른 목적은, 두 종류 이상의 박막 트랜지스터들을 최적화된 제조 공정 및 최소화된 마스크 공정을 통해 형성한 박막 트랜지스터 기판 및 이를 이용한 표시장치를 제공하는 데 있다.

### 과제의 해결 수단

[0007] 상기 목적을 달성하기 위하여, 본 발명에 의한 표시장치는, 제1 박막 트랜지스터, 제2 박막 트랜지스터, 중간 절연막 및 산화막을 포함한다. 제1 박막 트랜지스터는 다결정 반도체 층, 다결정 반도체 층 위에 배치된 제1 게이트 전극, 제1 소스 전극 및 제1 드레인 전극을 포함한다. 제2 박막 트랜지스터는 제2 게이트 전극, 제2 게이트 전극 위에 배치된 산화물 반도체 층, 제2 소스 전극 및 제2 드레인 전극을 포함한다. 중간 절연막은 제1 게이트 전극의 상부에 배치되며, 질화막을 포함한다. 산화막은 중간 절연막 위에 배치되며, 제2 게이트 전극을 덮는다. 산화물 반도체 층은, 산화막 위에서 제2 게이트 전극과 중첩하도록 배치된다. 제1 소스 전극, 제1 드레인 전극 및 제2 게이트 전극은 중간 절연막과 산화막 사이에 배치된다. 제2 소스 전극 및 제2 드레인 전극은 산화물 반도체 층 위에 배치된다.

[0008] 일례로, 구동 회로를 더 포함한다. 제1 박막 트랜지스터 및 제2 박막 트랜지스터 중 적어도 어느 하나는 화소에 포함된다. 제1 박막 트랜지스터 및 제2 박막 트랜지스터 중 적어도 어느 하나는 구동 회로에 포함된다.

[0009] 일례로, 다결정 반도체 층을 덮는 게이트 절연막을 더 포함한다. 제1 게이트 전극은 게이트 절연막 위에 배치되며, 다결정 반도체 층과 중첩한다.

[0010] 일례로, 제2 박막 트랜지스터는 화소를 선택하는 스위치 소자이다. 제1 박막 트랜지스터는 제2 박막 트랜지스터에 의해 선택된 화소의 유기발광 다이오드를 구동하는 구동 소자이다.

[0011] 일례로, 구동 회로는 데이터 구동부, 멀티플렉서 및 게이트 구동부를 포함한다. 데이터 구동부는 데이터 전압을 출력한다. 멀티플렉서는 데이터 구동부로부터의 데이터 전압을 데이터 배선으로 분배한다. 게이트 구동부는 스캔 웨尔斯를 게이트 배선으로 출력한다. 제1 박막 트랜지스터와 제2 박막 트랜지스터 중 어느 하나는 멀티플렉서 및 게이트 구동부 중 어느 하나에 포함된다.

[0012] 일례로, 제1 소스 전극은, 중간 절연막 및 게이트 절연막을 관통하는 소스 콘택홀을 통해 다결정 반도체 층의

일측부와 연결된다. 제1 드레인 전극은, 중간 절연막 및 게이트 절연막을 관통하는 드레인 콘택홀을 통해 다결정 반도체 층의 타측부와 연결된다. 제2 소스 전극은, 산화물 반도체 층의 일측부와 접촉된다. 제2 드레인 전극은, 산화물 반도체 층의 타측부와 접촉된다.

[0013] 일례로, 제1 소스 전극 및 제1 드레인 전극은, 제2 게이트 전극과 동일한 물질을 포함한다.

[0014] 일례로, 제2 게이트 전극은, 중간 절연막을 관통하는 게이트 콘택홀을 통해, 제1 게이트 전극과 동일한 물질을 포함하는 게이트 배선과 연결된다.

[0015] 일례로, 제2 소스 전극은, 산화막을 관통하는 데이터 콘택홀을 통해, 제2 게이트 전극과 동일한 물질을 포함하는 데이터 배선과 연결된다.

[0016] 일례로, 중간 절연막은 하부 산화막을 더 포함한다.

[0017] 일례로, 질화막은, 상기 하부 산화막 위에 배치된다.

[0018] 또한, 본 발명에 의한 표시장치는, 제1 반도체 층, 게이트 절연막, 제1 게이트 전극, 중간 절연막, 제2 게이트 전극, 제1 소스 전극, 제1 드레인 전극, 산화막, 제2 반도체 층, 제2 소스 전극 및 제2 드레인 전극을 포함한다. 제1 반도체 층은, 다결정 반도체 물질을 포함한다. 게이트 절연막은 제1 반도체 층을 덮는다. 제1 게이트 전극은 게이트 절연막 위에서 제1 반도체 층과 중첩한다. 중간 절연막은 제1 게이트 전극을 덮으며 질화막을 포함한다. 제2 게이트 전극, 제1 소스 전극 및 제1 드레인 전극은 중간 절연막 위에 배치된다. 산화막은 제2 게이트 전극, 제1 소스 전극 및 제1 드레인 전극을 덮는다. 제2 반도체 층은 산화막 위에서, 제2 게이트 전극과 중첩하도록 배치되며, 산화물 반도체 물질을 포함한다. 제2 소스 전극 및 제2 드레인 전극은 제2 반도체 층 위에 배치된다.

[0019] 일례로, 1 반도체 층, 제1 게이트 전극, 제1 소스 전극 및 제1 드레인 전극은 제1 박막 트랜지스터에 포함된다. 제2 반도체 층, 제2 게이트 전극, 제2 소스 전극 및 제2 드레인 전극은 제2 박막 트랜지스터에 포함된다.

[0020] 일례로, 구동 회로를 더 포함한다. 제1 박막 트랜지스터 및 제2 박막 트랜지스터 중 적어도 어느 하나는 화소에 포함된다. 제1 박막 트랜지스터 및 제2 박막 트랜지스터 중 적어도 어느 하나는 구동 회로에 포함된다.

[0021] 일례로, 제2 박막 트랜지스터는 화소를 선택하는 스위치 소자이다. 제1 박막 트랜지스터는 제2 박막 트랜지스터에 의해 선택된 화소의 유기발광 다이오드를 구동하는 구동 소자이다.

[0022] 일례로, 구동 회로는 데이터 구동부, 멀티플렉서 및 게이트 구동부를 포함한다. 데이터 구동부는 데이터 전압을 출력한다. 멀티플렉서는 데이터 구동부로부터의 데이터 전압을 데이터 배선으로 분배한다. 게이트 구동부는 스캔 웨尔斯를 게이트 배선으로 출력한다. 제1 박막 트랜지스터와 제2 박막 트랜지스터 중 어느 하나는 멀티플렉서 및 게이트 구동부 중 어느 하나에 포함된다.

[0023] 일례로, 제1 소스 전극은, 중간 절연막 및 게이트 절연막을 관통하는 소스 콘택홀을 통해 제1 반도체 층의 일측부와 연결된다. 제1 드레인 전극은, 중간 절연막 및 게이트 절연막을 관통하는 드레인 콘택홀을 통해 제1 반도체 층의 타측부와 연결된다. 제2 소스 전극은, 제2 반도체 층의 일측부와 접촉된다. 제2 드레인 전극은, 제2 반도체 층의 타측부와 접촉된다.

[0024] 일례로, 제1 소스 전극 및 제1 드레인 전극은, 제2 게이트 전극과 동일한 물질을 포함한다.

[0025] 일례로, 제2 게이트 전극은, 중간 절연막을 관통하는 게이트 콘택홀을 통해 게이트 절연막 위에 배치된 제1 게이트 전극과 동일한 물질을 포함하는 게이트 배선과 연결된다.

[0026] 일례로, 제2 소스 전극은, 산화막을 관통하는 데이터 콘택홀을 통해 중간 절연막 위에 배치된 제2 게이트 전극과 동일한 물질을 포함하는 데이터 배선과 연결된다.

[0027] 일례로, 중간 절연막은, 하부 산화막을 더 포함한다.

[0028] 일례로, 질화막은, 상기 하부 산화막 위에 배치된다.

### 발명의 효과

[0029] 본 발명에 의한 박막 트랜지스터 기판 및 이를 이용한 표시장치는, 서로 다른 두 종류의 박막 트랜지스터를 동일 기판 위에 형성하여, 어느 한 박막 트랜지스터의 단점을 다른 박막 트랜지스터가 보완하는 특징을 가질 수 있다. 특히, 저속 구동 특성을 갖는 박막 트랜지스터를 구비함으로써, 소비 전력을 저감함으로써, 휴대용 및/

또는 웨어러블 기기에 적합한 표시장치를 제공할 수 있다.

### 도면의 간단한 설명

[0030]

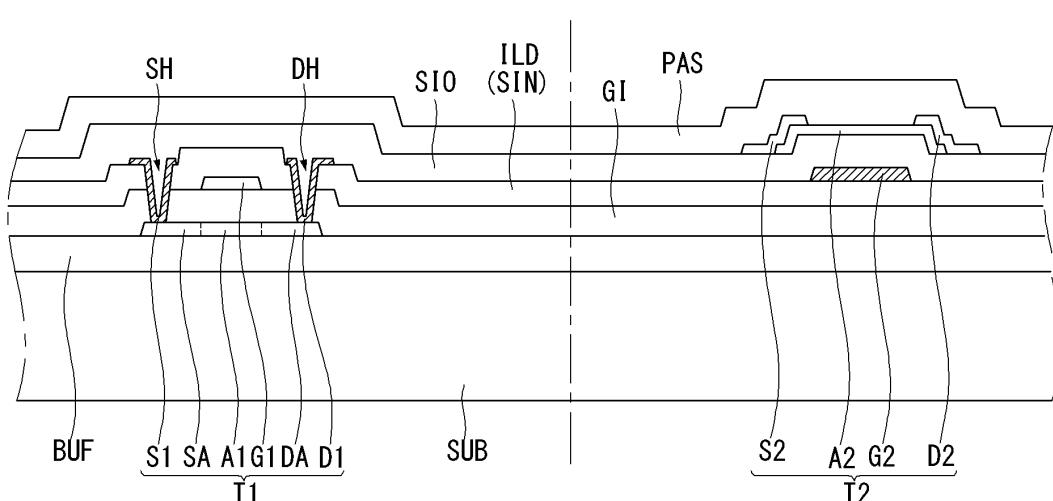

도 1a은 본 발명의 제1 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판을 나타내는 단면도.

도 1b는 도 1a에서 데이터 배선과 소스 전극 그리고 게이트 배선과 게이트 전극과의 연결 구조를 나타낸 단면도.

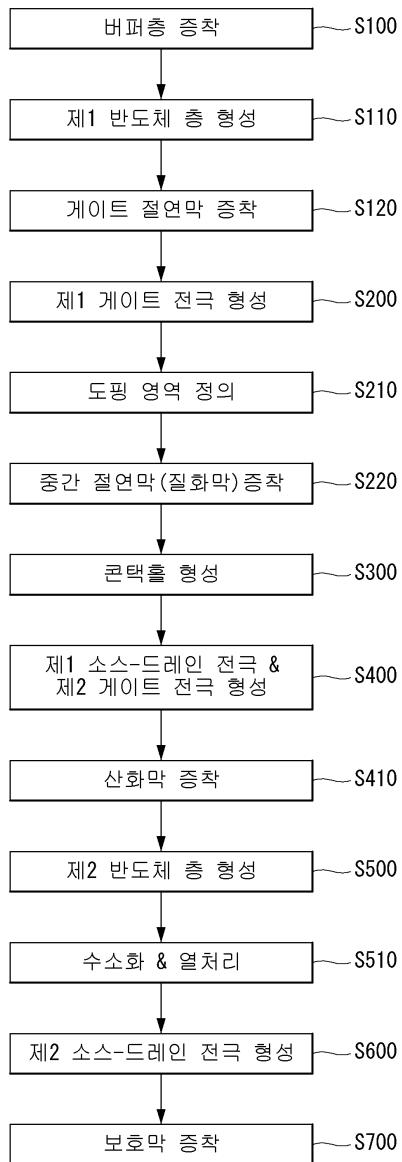

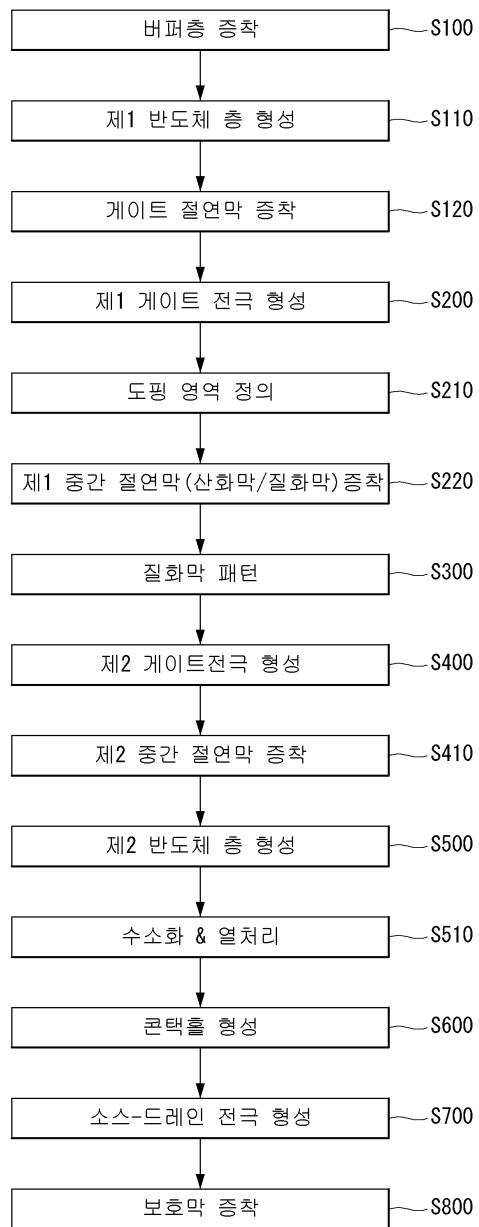

도 2는 본 발명의 제1 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판을 제조하는 과정을 나타내는 순서도.

도 3은 본 발명의 제2 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판을 나타내는 단면도.

도 4는 본 발명의 제2 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판을 제조하는 과정을 나타내는 순서도.

도 5는 본 발명의 제3 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판을 나타내는 단면도.

도 6은 본 발명의 제3 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판을 제조하는 과정을 나타내는 순서도.

도 7은 본 발명의 제1 응용 예에 따른 표시장치의 구성을 개략적으로 보여 주는 블록도.

도 8은 본 발명의 제2 응용 예에 의한 수평 전계형의 일종인 프린지 필드 방식의 액정 표시장치에 포함된 산화물 반도체 층을 갖는 박막 트랜지스터 기판을 나타내는 평면도.

도 9는 도 8에 도시한 박막 트랜지스터 기판을 절취선 I-I' 선을 따라 자른 단면도.

도 10은 본 발명의 제3 응용 예에 의한 액티브 매트릭스 유기발광 다이오드 표시장치에서 한 화소의 구조를 나타내는 평면도.

도 11은 도 10에서 절취선 II-II'로 자른 액티브 매트릭스 유기발광 다이오드 표시장치의 구조를 나타내는 단면도.

도 12는 본 발명의 제4 응용 예에 의한 유기발광 다이오드 표시장치의 개략적인 구조를 나타내는 평면 확대도.

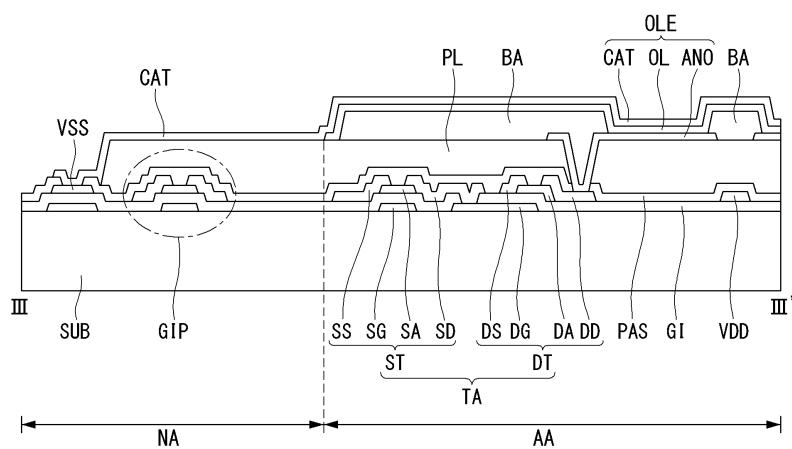

도 13은 도 12에서 절취선 III-III'으로 자른 도면으로 종래 기술에 의한 유기발광 다이오드 표시장치의 구조를 나타내는 단면도.

### 발명을 실시하기 위한 구체적인 내용

[0031]

이하, 첨부한 도면을 참조하여, 본 발명의 바람직한 실시 예들을 설명한다. 명세서 전체에 걸쳐서 동일한 참조 번호들은 실질적으로 동일한 구성 요소들을 의미한다. 이하의 설명에서, 본 발명과 관련된 공지 기술 혹은 구성에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우, 그 상세한 설명을 생략한다. 또한, 이하의 설명에서 사용되는 구성요소 명칭은 명세서 작성의 용이함을 고려하여 선택된 것일 수 있는 것으로서, 실제 제품의 부품 명칭과는 상이할 수 있다.

[0032]

본 발명에 의한 평판 표시장치용 박막 트랜지스터 기판은, 유리 기판 위에서 제1 영역에 배치된 제1 박막 트랜지스터와 제2 영역에 배치된 제2 박막 트랜지스터를 포함한다. 기판은 표시 영역과 비 표시 영역을 포함할 수 있다. 표시 영역에는 다수 개의 화소 영역들이 매트릭스 방식으로 배열된다. 화소 영역에는 표시 기능을 위한 표시 소자들이 배치된다. 비 표시 영역은 표시 영역의 주변에 배치되며, 화소 영역에 형성된 표시 소자들을 구동하기 위한 구동 소자들이 배치될 수 있다.

[0033]

여기서, 제1 영역은 비 표시 영역의 일 부분일 수 있고, 제2 영역은 표시 영역의 일 부분일 수 있다. 이 경우, 제1 박막 트랜지스터와 제2 박막 트랜지스터는 멀리 떨어져 배치될 수 있다. 또는, 제1 영역과 제2 영역 모두가 표시 영역에 포함될 수 있다. 특히, 단일 화소 영역 내에 다수 개의 박막 트랜지스터를 포함하는 경우, 제1

박막 트랜지스터와 제2 박막 트랜지스터는 서로 인접하여 배치될 수 있다.

[0034] 다결정 반도체 물질은 이동도가 높아( $100\text{cm}^2/\text{Vs}$  이상), 에너지 소비 전력이 낮고 신뢰성이 우수하므로, 표시 소자용 박막 트랜지스터들을 구동하는 구동 소자용 게이트 드라이버 및/또는 멀티플렉서(MUX)에 적용할 수 있다. 또는 유기발광 다이오드 표시장치에서 화소 내 구동 박막 트랜지스터로 적용하는 것이 좋다. 산화물 반도체 물질은 오프-전류가 낮으므로, 온(On) 시간이 짧고 오프(Off) 시간을 길게 유지하는 스위칭 박막 트랜지스터에 적합하다. 또한, 오프 전류가 작으므로 화소의 전압 유지 기간이 길어서 저속 구동 및/또는 저 소비 전력을 요구하는 표시 장치에 적합하다. 이와 같이, 서로 다른 두 종류의 박막 트랜지스터를 동일 기판 위에 동시에 배치함으로써, 최적의 효과를 나타내는 박막 트랜지스터 기판을 얻을 수 있다.

[0035] 다결정 반도체 물질로 반도체 층을 형성하는 경우, 불순물 주입공정 및 고온 열처리 공정을 필요로 한다. 반면에, 산화물 반도체 물질로 반도체 층을 형성하는 경우에는 상대적으로 낮은 온도에서 공정을 수행한다. 따라서, 가혹한 조건에서 공정을 수행하는 다결정 반도체 층을 먼저 형성한 후, 산화물 반도체 층을 나중에 형성하는 것이 바람직하다. 이를 위해, 다결정 반도체 물질을 포함하는 제1 박막 트랜지스터는 탑-게이트 구조를 갖고, 산화물 반도체 물질을 포함하는 제2 박막 트랜지스터는 바텀-게이트 구조를 갖는 것이 바람직하다.

[0036] 또한, 제조 공정상, 다결정 반도체 물질은 공극(vacancy)이 존재할 경우 특성이 저하되므로, 수소화 공정을 통해 공극을 수소로 채워주는 공정이 필요하다. 반면에, 산화물 반도체 물질은 공유 결합이 안된 공극이 캐리어(carrier)로써 역할을 할 수 있으므로, 공극을 어느 정도 보유한 상태로 안정화해주는 공정이 필요하다. 이 두 공정은,  $350^\circ\text{C} \sim 380^\circ\text{C}$  하에서 후속 열처리 공정을 통해 수행할 수 있다.

[0037] 수소화 공정을 수행하기 위해, 다결정 반도체 물질 위에 수소 입자를 다량 포함하는 질화막을 개재한다. 질화막은 제조시 사용하는 물질에 수소를 다량 포함하기 때문에, 적층된 질화막 자체에도 상당량의 수소가 포함되어 있다. 열처리 공정으로, 수소들이 다결정 반도체 물질로 확산된다. 그 결과, 다결정 반도체 층은 안정화를 이룰 수 있다. 열처리 공정 중에, 수소들이 산화물 반도체 물질로 지나치게 많은 양이 확산되어서는 안된다. 따라서, 질화막과 산화물 반도체 물질 사이에는 산화막을 개재하는 것이 바람직하다. 열처리 공정을 수행한 후, 산화물 반도체 물질은 수소에 의해 너무 많은 영향을 받지 않은 상태를 유지하여, 소자 안정화를 이룰 수 있다.

[0038] 이하의 설명에서는, 편의상, 제1 박막 트랜지스터가 비 표시 영역에 형성된 구동 소자용 박막 트랜지스터이고, 제2 박막 트랜지스터가 표시 영역의 화소 영역 내에 배치된 표시 소자용 박막 트랜지스터인 경우로 설명한다. 하지만, 이에 국한하는 것은 아니며, 유기발광 다이오드 표시장치의 경우, 제1 박막 트랜지스터와 제2 박막 트랜지스터 모두 표시 영역의 화소 영역 내에 배치될 수 있다. 특히, 다결정 반도체 물질을 포함하는 제1 박막 트랜지스터는 구동 박막 트랜지스터에, 산화물 반도체 물질을 포함하는 제2 박막 트랜지스터는 스위칭 박막 트랜지스터에 적용할 수 있다.

[0039] < 제1 실시 예 >

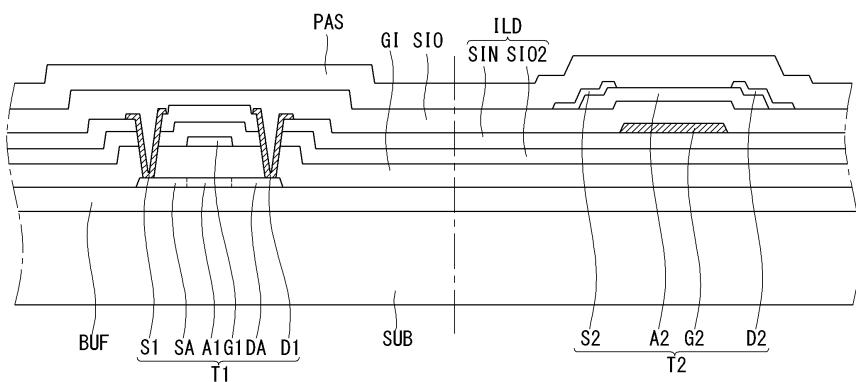

[0040] 도 1a 및 1b를 참조하여 본 발명의 제1 실시 예에 대하여 설명한다. 도 1a는 본 발명의 제1 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판을 나타내는 단면도이다. 도 1b는 도 1a에서 데이터 배선과 소스 전극 그리고 게이트 배선과 게이트 전극과의 연결 구조를 나타낸 단면도이다. 여기서, 발명의 특징을 확실하게 나타낼 수 있는 단면도를 중심으로 설명하며, 편의상 평면도 구조에 대해서는 도면으로 나타내지 않았다.

[0041] 도 1a를 참조하면, 본 발명의 제1 실시 예에 의한 평판 표시장치용 박막 트랜지스터 기판은, 기판(SUB) 위에 배치된 제1 박막 트랜지스터(T1)와 제2 박막 트랜지스터(T2)를 포함한다. 제1 및 제2 박막 트랜지스터들(T1, T2)은 이격되어 배치될 수도 있고, 인접하여 배치될 수도 있다. 혹은 두 개의 박막 트랜지스터들이 중첩되어 배치될 수도 있다.

[0042] 기판(SUB)의 전체 표면 위에는 버퍼 층(BUF)이 적층되어 있다. 경우에 따라서, 버퍼 층(BUF)은 생략될 수도 있다. 또는, 버퍼 층(BUF)은 복수 개의 박막층이 적층된 구조를 가질 수도 있다. 여기서는 편의상 단일층으로 설명한다. 또한, 버퍼 층(BUF)과 기판(SUB) 사이에서 필요한 부분에만 선택적으로 차광층을 더 구비할 수도 있다. 차광층은 그 위에 배치된 박막 트랜지스터의 반도체 층으로 외부의 빛이 유입되는 것을 방지할 목적으로 형성할 수 있다.

[0043] 버퍼 층(BUF) 위에는 제1 반도체 층(A1)이 배치되어 있다. 제1 반도체 층(A1)은 제1 박막 트랜지스터(T1)의 채널 영역을 포함한다. 채널 영역은 제1 게이트 전극(G1)과 제1 반도체 층(A1)이 중첩되는 영역으로 정의된다. 제1 게이트 전극(G1)이 제1 박막 트랜지스터(T1)의 중앙부와 중첩하므로, 제1 박막 트랜지스터(T1)의 중앙부가

채널 영역이 된다. 채널 영역의 양측면부는 불순물이 도핑된 영역으로서, 소스 영역(SA)과 드레인 영역(DA)으로 정의된다.

[0044] 제1 박막 트랜지스터(T1)가 구동 소자용 박막 트랜지스터인 경우, 고속 구동 처리를 수행하는 데 적합한 특성을 갖는 것이 바람직하다. 예를 들어, P-MOS 혹은 N-MOS 형의 박막 트랜지스터를 이용하거나, 이 두 개를 모두 포함하는 C-MOS 형의 박막 트랜지스터를 구비할 수 있다. P-MOS, N-MOS 및/또는 C-MOS 형의 박막 트랜지스터들은 다결정 실리콘(Poly-Silicon)과 같은 다결정 반도체 물질을 포함하는 것이 바람직하다. 또한, 제1 박막 트랜지스터(T1)의 경우 탑-게이트(Top-Gate) 구조를 갖는 것이 바람직하다.

[0045] 제1 반도체 층(A1)이 배치된 기판(SUB)의 전체 표면 위에는 게이트 절연막(GI)이 적층되어 있다. 게이트 절연막(GI)은 질화 실리콘(SiNx) 혹은 산화 실리콘(SiOx)으로 형성할 수 있다. 게이트 절연막(GI)의 경우, 소자의 안정성 및 특성을 고려하여 1,000Å ~ 1,500Å 정도의 두께를 갖는 것이 바람직하다. 게이트 절연막(GI)을 질화 실리콘(SiNx)으로 형성할 경우, 제조 공정상 게이트 절연막(GI) 내에 수소를 다량 포함할 수 있다. 이러한 수소들은 후속 공정에서 게이트 절연막(GI) 외부로 확산될 수 있어, 게이트 절연막(GI)을 산화 실리콘 물질로 형성하는 것이 바람직하다.

[0046] 다결정 실리콘 물질을 포함하는 제1 반도체 층(A1)은, 수소 확산이 긍정적인 효과를 나타낼 수 있다. 하지만, 제1 박막 트랜지스터(T1)와 다른 성질을 갖는 제2 박막 트랜지스터(T2)에는 부정적인 효과를 줄 수 있다. 따라서, 본 발명과 같이 서로 다른 물질을 사용하는 박막 트랜지스터들이 동일 기판 위에 형성되는 경우, 소자에 특별한 영향을 주지 않는 산화 실리콘(SiOx)을 사용하는 것이 더 바람직하다. 경우에 따라서, 게이트 절연막(GI)을 제1 실시 예에서 설명하는 경우와 달리, 2,000Å ~ 4,000Å 정도로 두껍게 형성할 경우가 있다. 이 경우, 게이트 절연막(GI)을 질화 실리콘(SiNx)으로 형성할 경우에는 수소의 확산 정도가 심할 수 있다. 따라서, 여러 경우를 고려했을 때, 게이트 절연막(GI)은 산화 실리콘(SiOx)으로 형성하는 것이 바람직하다.

[0047] 게이트 절연막(GI) 위에는 제1 게이트 전극(G1)이 배치되어 있다. 제1 게이트 전극(G1)은 제1 반도체 층(A1)의 중앙부와 중첩하도록 배치되어 있다. 제1 게이트 전극(G1)과 중첩하는 제1 반도체 층(A1)의 중앙부는 채널 영역으로 정의된다.

[0048] 제1 게이트 전극(G1)이 형성된 기판(SUB) 전체 표면 위에는 중간 절연막(ILD)이 적층되어 있다. 중간 절연막(ILD)은 질화 실리콘(SiNx)과 같은 무기 질화물질을 포함하는 질화막(SIN)으로 형성하는 것이 바람직하다. 질화막(SIN)은, 후속 열처리 공정을 통해 내부에 포함된 수소를 확산하여 다결정 실리콘을 포함하는 제1 반도체 층(A1)을 수소화 처리를 수행하기 위해 증착한다.

[0049] 중간 절연막(ILD) 위에는, 제1 소스 전극(S1) 및 제1 드레인 전극(D1) 그리고 제2 게이트 전극(G2)이 배치되어 있다. 제1 소스 전극(S1)은 중간 절연막(ILD)과 게이트 절연막(GI)을 관통하는 소스 콘택홀(SH)을 통해 제1 반도체 층(A1)의 일측부인 소스 영역(SA)과 접촉한다. 제1 드레인 전극(D1)은 중간 절연막(ILD)과 게이트 절연막(GI)을 관통하는 드레인 콘택홀(DH)을 통해 제1 반도체 층(A1)의 타측부인 드레인 영역(DA)과 접촉한다. 한편, 제2 게이트 전극(G2)은 제2 박막 트랜지스터(T2)의 영역에 배치한다. 제1 소스 전극(S1) 및 제1 드레인 전극(D1) 그리고 제2 게이트 전극(G2)은 동일한 층 상에 동일한 물질로 동일한 마스크로 형성함으로써, 제조 공정을 단순화할 수 있다.

[0050] 제1 소스 전극(S1) 및 제1 드레인 전극(D1) 그리고 제2 게이트 전극(G2)이 형성된 중간 절연막(ILD) 위에 산화막(SIO)이 적층되어 있다. 산화막(SIO)은 산화 실리콘(SiOx)과 같은 무기 산화물질을 포함하는 것이 바람직하다. 산화막(SIO)은 질화막(SIN) 위에 적층된 구조를 가짐으로써, 후속 열처리 공정에 의해 질화막(SIN)에서 방출되는 수소가 제2 박막 트랜지스터의 반도체 물질로 지나치게 많이 확산되는 것을 방지한다.

[0051] 질화막(SIN)으로 이루어진 중간 절연막(ILD)에서 방출되는 수소는 그 아래에 게이트 절연막(GI)을 사이에 두고 배치된 제1 반도체 층(A1)으로 확산되는 것이 바람직하다. 반면에, 질화막(SIN)에서 방출되는 수소는 그 위에 형성되는 제2 박막 트랜지스터(T2)의 반도체 물질로는 확산되는 것을 방지하는 것이 바람직하다. 따라서, 질화막(SIN)은 게이트 절연막(GI) 위에서 제1 반도체 층(A1)과 가깝게 적층되는 것이 바람직하다. 경우에 따라서, 질화막(SIN)은 제1 반도체 층(A1)을 포함하는 제1 박막 트랜지스터(T1)를 선택적으로 덮고, 제2 박막 트랜지스터(T2)가 배치되는 영역에는 배치되지 않는 것이 바람직하다.

[0052] 또한, 제조 공정 및 수소 확산 효율을 고려하여, 질화막(SIN)으로 이루어진 중간 절연막(ILD)은 1,000Å ~ 3,000Å의 두께로 적층하는 것이 바람직하다. 또한, 질화막(SIN) 내의 수소가 제1 반도체 층(A1)으로 다량 확산되는 반면, 제2 반도체 층(A2)으로는 가급적 적게 영향을 주도록 하기 위해서는, 산화막(SIO)의 두께는 게이

트 절연막(GI)보다 더 두꺼운 것이 바람직하다. 특히, 산화막(SIO)은 질화막(SIN)에서 방출되는 수소의 확산 정도를 조절하기 위한 것으로서, 산화막(SIO)의 두께는 질화막(SIN)보다 두꺼운 것이 바람직하다. 또한, 산화막(SIO)은 제2 박막 트랜지스터(T2)에서 게이트 절연막의 기능을 하여야 한다. 이러한 상황을 고려했을 때, 산화막(SIO)은 1,000Å ~ 3,000Å 정도의 두께로 적충하는 것이 바람직하다.

[0053] 산화막(SIO) 상부 표면에는, 제2 게이트 전극(G2)과 중첩하는 제2 반도체 층(A2)이 배치되어 있다. 제2 반도체 층(A2)은 제2 박막 트랜지스터(T2)의 채널 영역을 포함한다. 제2 박막 트랜지스터(T2)가 표시 소자용 박막 트랜지스터인 경우, 표시 기능 처리를 수행하는 데 적합한 특성을 갖는 것이 바람직하다. 예를 들어, 인듐-갈륨-아연 산화물(Indium Gallium Zinc Oxide: IGZO), 인듐-갈륨 산화물(Indium Gallium Oxide: IGO) 및 인듐-아연 산화물(Indium Zinc Oxide: IZO)와 같은 산화물 반도체 물질을 포함하는 것이 바람직하다. 산화물 반도체 물질은, Off-전류(Off-Current)가 낮은 특성이 있어 낮은 주파수에서 구동이 가능하다. 이러한 특성으로 인해, 낮은 보조 용량의 크기로도 충분히 구동할 수 있으므로, 보조 용량이 차지하는 면적을 줄일 수 있다. 따라서, 단위 화소 영역의 크기가 작은 초고 해상도 표시장치를 구현하는 데 유리하다. 산화물 반도체 물질을 포함하는 경우, 소자의 안정성을 좀 더 효과적으로 확보할 수 있는 바텀-게이트 (Bottom-Gate) 구조를 갖는 것이 바람직하다.

[0054] 제2 반도체 층(A2)과 산화막(SIO) 위에, 제2 소스 전극(S2)과 제2 드레인 전극(D2)들이 배치되어 있다. 제2 소스 전극(S2)과 제2 드레인 전극(D2)은 각각 제2 반도체 층(A2)의 일측부와 타측부의 상부 표면과 접촉하며 일정 거리 이격하여 배치되어 있다. 제2 소스 전극(S2)은 산화막(SIO)의 상부 표면 및 제2 반도체 층(A2)의 일측부 상부 표면과 접촉하도록 배치되어 있다. 제2 드레인 전극(D2)은 산화막(SIO)의 상부 표면 및 제2 반도체 층(A2)의 타측부 상부 표면과 접촉하도록 배치되어 있다.

[0055] 제1 박막 트랜지스터(T1)와 제2 박막 트랜지스터(T2) 위에는 보호막(PAS)이 덮고 있다. 이후, 보호막(PAS)을 폐던하여 제1 드레인 전극(D1) 및/또는 제2 드레인 전극(D2)을 노출하는 콘택홀이 더 형성될 수 있다. 또한, 보호막(PAS) 위에는 콘택홀을 통해 제1 드레인 전극(D1) 및/또는 제2 드레인 전극(D2)과 접촉하는 화소 전극을 더 포함할 수 있다. 여기서는, 편의상, 본 발명의 주요 특징을 나타내는 박막 트랜지스터들의 구조를 나타내는 부분들만 도시하고 설명하였다.

[0056] 이와 같이, 본 발명의 제1 실시 예에 의한 평판 표시장치용 박막 트랜지스터 기판은, 다결정 반도체 물질을 포함하는 제1 박막 트랜지스터(T1)와 산화물 반도체 물질을 포함하는 제2 박막 트랜지스터(T2)가 동일 기판(SUB) 위에 형성된 구조를 갖는다. 특히, 제1 박막 트랜지스터(T1)의 다결정 반도체 물질을 포함하는 제1 반도체 층(A1)은 제1 게이트 전극(G1) 아래에 배치되고, 제2 박막 트랜지스터(T2)의 산화물 반도체 물질을 포함하는 제2 반도체 층(A2)은 제2 게이트 전극(G2) 상부에 배치된다. 또한, 제2 게이트 전극(G2)은 제1 게이트 전극(G1)을 덮는 중간 절연막(ILD) 위에 배치된다. 따라서, 상대적으로 고온에서 형성되는 제1 반도체 층(A1)을 먼저 형성한 후에, 상대적으로 저온에서 형성되는 제2 반도체 층(A2)을 나중에 형성함으로써, 제조 공정 중에 산화물 반도체 물질이 고온 상태에 노출되는 상황을 회피할 수 있는 구조를 갖는다. 따라서, 제1 박막 트랜지스터는, 제1 게이트 전극(G1)보다 제1 반도체 층(A1)을 먼저 형성하여야 하므로 탑-게이트 구조를 갖는다. 제2 박막 트랜지스터는, 제2 게이트 전극(G2)보다 제2 반도체 층(A2)을 나중에 형성하여야 하므로 바텀-게이트 구조를 갖는다.

[0057] 또한, 산화물 반도체 물질을 포함하는 제2 반도체 층(A2)을 열처리하는 과정에서 다결정 반도체 물질을 포함하는 제1 반도체 층(A1)에 수소 처리 공정을 동시에 수행할 수 있다. 이를 위해, 중간 절연막(ILD)은 질화막(SIN)으로 이루어지며, 중간 절연막(ILD) 위에는 산화막(SIO)이 적층된 구조를 갖는다. 제조 공정상의 특징으로 질화막(SIN) 내부에 포함된 수소를 열처리 공정에 의해 제1 반도체 층(A1)으로 확산시키는 수소화 공정이 필요하다. 또한, 산화물 반도체 물질을 포함하는 제2 반도체 층(A2)의 안정화를 위한 열처리 공정도 필요하다. 수소화 공정은 제1 반도체 층(A1) 위에 중간 절연막(ILD)을 적층한 후에 실시하고, 열 처리 공정은 제2 반도체 층(A2)을 형성한 후에 실시할 수 있다. 본 발명의 제1 실시 예에 의하면, 제2 반도체 층(A2) 아래에서 질화막(SIN) 위에 증착된 산화막(SIO)에 의해 질화막(SIN)에 내포된 수소가 산화물 반도체 물질을 포함하는 제2 반도체 층(A2)으로 과도하게 확산되는 것을 방지할 수 있는 구조를 갖는다. 따라서, 본 발명의 제1 실시 예에 의한 구조에서는, 산화물 반도체 물질의 안정화를 위한 열처리 공정에서 수소화 공정을 동시에 수행할 수도 있다.

[0058] 한편, 질화막(SIN)은 수소 처리가 필요한 제1 반도체 층(A1)과 가깝게 배치되도록 하기 위해 제1 게이트 전극(G1) 위에 적층된다. 또한, 산화물 반도체 물질을 포함하는 제2 박막 트랜지스터(T2)는 질화막(SIN)으로부터 상당히 멀리 이격되어 배치되도록 하기 위해, 질화막(SIN)과 그 위에 형성된 제2 게이트 전극(G2)을 덮는 산화

막(SIO)의 위에 적층되어 있다. 그 결과, 후속 열처리 공정에서 질화막(SIN)에 내포된 수소가 제2 반도체 층(A2)으로 지나치게 많이 확산되는 것을 방지할 수 있다.

[0059] 이상, 도 1a를 참조한 설명은, 제1 박막 트랜지스터와 제2 박막 트랜지스터의 기본 구조에 대해서만 설명한 것이다. 실제로, 제2 박막 트랜지스터를 화소 영역에 배치되는 표시 소자로 사용하는 경우, 게이트 배선과 데이터 배선이 화소 영역 주변에 배치된다. 그리고, 이들 게이트 배선과 데이터 배선은 제1 박막 트랜지스터의 게이트 배선 및 데이터 배선과 동일한 층에 형성되는 것이 바람직하다. 이하, 도 1b를 참조하여, 제2 박막 트랜지스터를 구성하는 게이트 전극과 소스 전극 각각이 게이트 배선과 데이터 배선에 어떻게 연결할 수 있는지에 대해 추가로 설명한다.

[0060] 도 1b를 참조하면, 기본적인 박막 트랜지스터들의 구조는 앞에서 설명한 것과 동일하다. 따라서, 중복되는 설명은 생략한다. 제1 박막 트랜지스터(T1)를 구성하는 제1 게이트 전극(G1)을 형성할 때, 동일한 물질로 동일한 층에, 제2 박막 트랜지스터(T2)의 주변에는 게이트 배선(GL)을 배치한다. 즉, 게이트 배선(GL)은 제1 게이트 전극(G1)과 같이 중간 절연막(ILD)에 의해 덮이는 구조를 갖는다.

[0061] 중간 절연막(ILD)에는 제1 반도체 층(A1)의 소스 영역(SA)을 개방하는 소스 콘택홀(SH)과 드레인 영역(DA)을 노출하는 드레인 콘택홀(DH)이 형성되어 있다. 이와 동시에, 중간 절연막(ILD)에는 게이트 배선(GL)의 일부를 노출하는 게이트 배선 콘택홀(GLH)이 더 형성되어 있다.

[0062] 중간 절연막(ILD) 위에는 제1 소스 전극(S1), 제1 드레인 전극(D1), 제2 게이트 전극(G2) 그리고 데이터 배선(DL)이 배치되어 있다. 제1 소스 전극(S1)은 소스 콘택홀(SH)을 통해 소스 영역(SA)과 접촉한다. 제1 드레인 전극(D1)은 드레인 콘택홀(DH)을 통해 드레인 영역(DA)과 접촉한다. 또한, 제2 게이트 전극(G2)은 게이트 배선 콘택홀(GLH)을 통해 게이트 배선(GL)과 연결된다. 데이터 배선(DL)은 제2 박막 트랜지스터(T2) 주변에서, 중간 절연막(ILD)을 사이에 두고 게이트 배선(GL)과 교차하도록 배치된다.

[0063] 제1 소스 전극(S1)과 제1 드레인 전극(D1) 그리고 제2 게이트 전극(G2)은 산화막(SIO)에 의해 덮여 있다. 산화막(SIO) 위에는 제2 게이트 전극(G2)과 중첩하는 제2 반도체 층(A2)이 배치되어 있다. 또한, 산화막(SIO)에는 데이터 배선(DL)의 일부를 노출하는 데이터 배선 콘택홀(DLH)이 더 형성되어 있다.

[0064] 제2 반도체 층(A2)과 산화막(SIO) 위에는 제2 소스 전극(S2)과 제2 드레인 전극(D2)이 배치되어 있다. 제2 소스 전극(S2)은 제2 반도체 층(A2)의 일측면 상부 표면과 접촉하며, 데이터 배선 콘택홀(DLH)을 통해 데이터 배선(DL)과 연결된다. 제2 드레인 전극(D2)은 제2 반도체 층(A2)의 타측면 상부 표면과 접촉한다.

[0065] 이하, 도 2를 더 참조하여 본 발명의 제1 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판의 제조 방법을 설명한다. 도 2는 본 발명의 제1 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판을 제조하는 과정을 나타내는 순서도이다.

[0066] 기판(SUB) 위에 버퍼 층(BUF)을 증착한다. 도면으로 설명하지 않았지만, 버퍼 층(BUF)을 증착하기 전에, 필요한 부분에 차광층을 형성할 수도 있다. (S100)

[0067] 버퍼 층(BUF) 위에 아몰퍼스 실리콘(a-Si) 물질을 증착하고, 결정화를 수행하여 다결정 실리콘(poly-silicon)으로 만든다. 다결정 실리콘 물질을 제1 마스크 공정으로 패턴하여 제1 반도체 층(A1)을 형성한다. (S110)

[0068] 제1 반도체 층(A1)이 형성된 기판(SUB) 전체 표면 위에 산화 실리콘과 같은 절연 물질을 증착하여 게이트 절연막(GI)을 형성한다. 게이트 절연막(GI)은 산화 실리콘으로 형성하는 것이 바람직하다. 게이트 절연막(GI)의 두께는 1,000Å ~ 1,500Å인 것이 바람직하다. (S120)

[0069] 게이트 절연막(GI) 상부에 게이트 금속 물질을 증착하고, 제2 마스크 공정으로 패턴하여 제1 게이트 전극(G1)을 형성한다. 제1 게이트 전극(G1)은 제1 반도체 층(A1)의 중심부와 중첩하도록 배치한다. (S200)

[0070] 제1 게이트 전극(G1)을 마스크로 하여, 하부에 배치된 제1 반도체 층(A1)에 불순물을 주입하여 소스 영역(SA) 및 드레인 영역(DA)을 포함하는 도핑 영역을 정의한다. 도핑 영역의 정의 과정은 P-MOS, N-MOS 또는 C-MOS에 따라 약간씩 상이할 수 있다. 예를 들어, N-MOS 형 박막 트랜지스터의 경우, 고 농도 도핑 영역을 먼저 형성하고 난 후, 저 농도 도핑 영역을 나중에 형성할 수 있다. 제1 게이트 전극(G1)보다 좀 더 큰 크기를 갖는 제1 게이트 전극(G1)의 포토레지스트 패턴을 이용하여 고농도 도핑 영역을 정의 할 수 있다. 포토레지스트를 제거하고 제1 게이트 전극(G1)을 마스크로 하여, 고농도 도핑 영역과 제1 게이트 전극(G1) 사이에, 저농도 도핑 영역(Low Density Doping area; LDD)을 정의할 수 있다. 불순물 도핑 영역에 대해서는 편의상 도면으로 나타내지

는 않았다. (S210)

[0071] 제1 게이트 전극(G1)이 형성된 기판(SUB) 전체 표면 위에 질화 실리콘(SiNx)과 같은 질화 무기물질을 이용하여 질화막(SIN)으로 이루어진 중간 절연막(ILD)을 증착한다. 질화막(SIN)은 제조 공정상 내부에 수소를 다량 내포 할 수 있다. 제조 공정 및 수소 확산을 고려했을 때, 중간 절연막(ILD)은 1,000Å ~ 3,000Å의 두께로 증착한다. (S220)

[0072] 제3 마스크 공정으로 중간 절연막(ILD)을 패턴하여, 제1 반도체 층(A1)의 일측부를 노출하는 소스 콘택홀(SH)과 타측부를 노출하는 드레인 콘택홀(DH)을 형성한다. 이는 이후에 형성될 소스-드레인 전극을 제1 반도체 층(A1)과 연결하기 위한 것이다. (S300)

[0073] 중간 절연막(ILD) 위에 금속 물질을 증착한다. 제4 마스크 공정으로 금속 물질을 패턴하여, 제1 소스 전극(S1) 및 제1 드레인 전극(D1) 그리고 제2 게이트 전극(G2)을 형성한다. 제1 소스 전극(S1)은 소스 콘택홀(SH)을 통해 제1 반도체 층(A1)의 일측변과 접촉한다. 제1 드레인 전극(D1)은 드레인 콘택홀(DH)을 통해 제1 반도체 층(A1)의 타측변과 접촉한다. 제2 게이트 전극(G2)은 제2 박막 트랜지스터(T2)가 형성될 위치에 배치된다. (S400)

[0074] 제1 소스 전극(S1) 및 제1 드레인 전극(D1) 그리고 제2 게이트 전극(G2)들이 형성된 기판(SUB)의 전체 표면 위에 산화 실리콘(SiOx)과 같은 산화 무기물질을 이용하여 산화막(SIO)을 증착한다. 제2 박막 트랜지스터(T2)의 구조적인 측면에서 보면, 산화막(SIO)은 제2 게이트 전극(G2)을 덮는 게이트 절연막의 기능을 한다. 또한, 산화막(SIO)은 질화막(SIN)에서 방출되는 수소 입자들이 상부에 배치될 반도체 물질로 확산되는 것을 방지할 수 있도록 1,000Å ~ 3,000Å의 두께로 증착하는 것이 바람직하다. 수소 확산 정도나 소자 특성을 고려하여, 산화막(SIO)과 중간 절연막(ILD)인 질화막(SIN)의 두께를 적절히 선택할 수 있다. 예를 들어, 수소의 과도한 확산을 방지하기 위해서는, 질화막(SIN)은 산화막(SIO)보다 얇은 것이 바람직하다. (S410)

[0075] 산화막(SIO) 위에 산화물 반도체 물질을 증착한다. 산화물 반도체 물질은 인듐-갈륨-아연 산화물(Indium Gallium Zinc Oxide: IGZO), 인듐-갈륨 산화물(Indium Gallium Oxide: IGO) 및 인듐 -아연 산화물(Indium Zinc Oxide: IZO) 중 적어도 어느 하나를 포함한다. 제5 마스크 공정으로 산화물 반도체 물질을 패턴하여 제2 반도체 층(A2)을 형성한다. 제2 반도체 층(A2)은 제2 게이트 전극(G2)과 중첩하도록 배치한다. (S500)

[0076] 제2 반도체 층(A2)이 형성된 기판(SUB)을 후속 열처리하여, 다결정 실리콘을 포함하는 제1 반도체 층(A1)의 수소화 처리와 산화물 반도체 물질을 포함하는 제2 반도체 층(A2)의 열처리를 동시에 수행한다. 후속 열처리 공정은, 350? 내지 380?의 온도 상태에서 수행한다. 이때, 질화막(SIN)에 포함된 수소는 제1 반도체 층(A1)으로 다량 확산되는 반면, 산화막(SIO)에 의해 제2 반도체 층(A2)으로 확산되는 양이 제한된다. 경우에 따라, 제1 반도체 층(A1)의 수소화 공정과 제2 반도체 층(A2)의 열처리 공정을 분리하여 수행할 수도 있다. 이 경우, 수소화 공정은 중간 절연막(ILD)을 증착하는 S220 과정 후에 먼저 수행하고, 이번 후속 열처리 공정을 통해 제2 반도체 층(A2)의 열처리를 수행한다. (S510)

[0077] 제2 반도체 층(A2)이 형성된 기판(SUB)의 전체 표면 위에 소스-드레인 금속 물질을 증착한다. 제6 마스크 공정으로 소스-드레인 금속 물질을 패턴하여 제2 소스 전극(S2) 및 제2 드레인 전극(D2)을 형성한다. 제2 소스 전극(S2)은 제2 반도체 층(A2)의 일측면 상부 면과 제2 중간 절연막(ILD2)의 상부 면에 걸쳐 접촉되도록 배치된다. 마찬가지로, 제2 드레인 전극(D2)은 제2 반도체 층(A2)의 타측면 상부 면과 산화막(SIO)의 상부 면에 걸쳐 접촉되도록 배치된다. (S600)

[0078] 제1 및 제2 박막 트랜지스터(T1, T2)들이 형성된 기판(SUB) 전체 표면 위에 보호막(PAS)을 증착한다. 도면으로 도시하지 않았지만, 이후에 보호막(PAS)을 패턴하여 제1 및/또는 제2 드레인 전극(D1, D2) 일부를 노출하는 콘택홀을 더 형성할 수 있다. (S700)

[0079] < 제2 실시 예 >

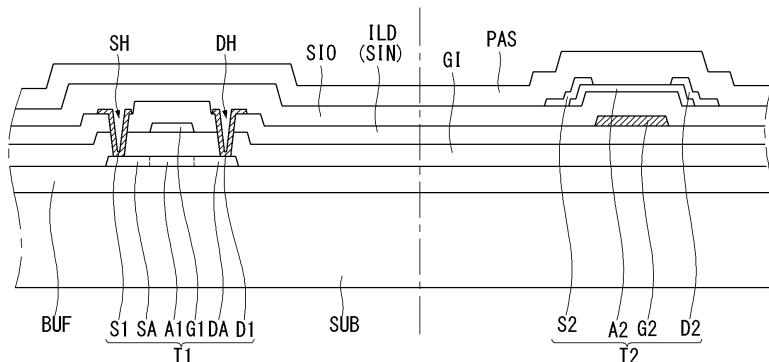

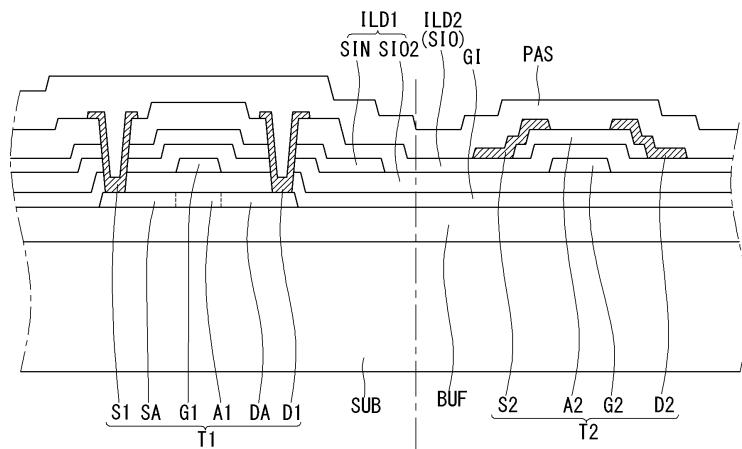

[0080] 이하, 도 3을 참조하여, 본 발명의 제2 실시 예에 대하여 설명한다. 도 3은 본 발명의 제2 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판을 나타내는 단면도이다.

[0081] 본 발명의 제2 실시 예는, 기본적인 구성은 제1 실시 예와 동일하다. 차이가 있다면, 중간 절연막(ILD)이 이중 층으로 구성된다. 하부 산화막(SI02)과 질화막(SIN)이 적층된 구조를 가질 수 있다. 예를 들어, 하부 산화막(SI02) 위에 질화막(SIN)이 적층된 구조를 가질 수 있다. 또는 질화막(SIN) 위에 하부 산화막(SI02)이 적층된 구조를 가질 수 있다. 여기서, 하부 산화막(SI02)이라함은, 산화막(SIO)보다 아래에 위치하므로 명명한 이름이

며, 질화막 아래에 배치되는 것을 한정하는 용어는 아니다.

[0082] 후속 열처리 공정을 통해, 제조 공정상 수소를 다량 함유한 질화막(SIN)에서 수소를 제1 반도체 층(A1)으로 확산하여야 한다. 확산 효율을 고려했을 때, 중간 절연막(ILD)의 질화막(SIN)의 두께는 1,000Å ~ 3,000Å의 두께를 갖는 것이 바람직하다. 하부 산화막(SIO2)은, (질화막(SIN) 하부에 배치되어) 제1 게이트 전극(G1)을 형성하는 과정에서 손상된 게이트 절연막(GI)의 표면을 보상하거나, (질화막(SIN) 상부에 배치되어) 질화막(SIN)을 안정화하기 위한 것으로 500Å ~ 1,000Å 정도의 두께를 갖는 것이 바람직하다.

[0083] 하부 산화막(SIO2)과 질화막(SIN)이 적층된 중간 절연막(ILD) 위에는 산화막(SIO)이 적층되어 있다. 산화막(SIO)은 제2 박막 트랜지스터(T2)에서는 게이트 절연막의 기능을 한다. 따라서, 산화막(SIO)이 너무 두꺼우면 제2 반도체 층(A2)에 게이트 전압이 정상적으로 전달되지 않을 수 있다. 따라서, 산화막(SIO)의 두께는 1,000Å ~ 3,000Å의 두께를 갖는 것이 바람직하다. 또한, 게이트 절연막(GI)은 1,000Å ~ 1,500Å 정도의 두께를 갖는 것이 바람직하다.

[0084] 도 3에서, 중간 절연막(ILD)이 하부 산화막(SIO2) 위에 질화막(SIN)이 적층된 구조로 도시하고, 이를 중심으로 설명하였다. 하지만, 필요하다면, 중간 절연막(ILD)은 질화막(SIN)을 하부에 하부 산화막(SIO2)을 상부에 적층한 구조를 가질 수 있다. 이 경우, 질화막(SIN)은 하부의 제1 반도체 층(A1)과 더 가까이 배치되는 반면, 상부의 제2 반도체 층(A2)과는 하부 산화막(SIO2) 두께만큼 더 이격되는 구조를 가질 수 있다. 따라서, 제1 반도체 층(A1)으로의 수소 확산은 더 잘 이루어지며, 제2 반도체 층(A2)로의 수소 확산을 더 잘 방지할 수 있다.

[0085] 제조 공정을 고려했을 때, 중간 절연막(ILD)의 두께가 2,000Å ~ 6,000Å인 것이 바람직하므로, 질화막(SIN) 및 하부 산화막(SIO2) 각각의 두께를 모두 1,000Å ~ 3,000Å의 두께로 형성하는 것이 바람직하다. 또한, 산화막(SIO)은 제2 박막 트랜지스터(T2)에서 게이트 절연막인 것을 고려하여, 1,000Å ~ 3,000Å의 두께로 형성하는 것이 바람직하다.

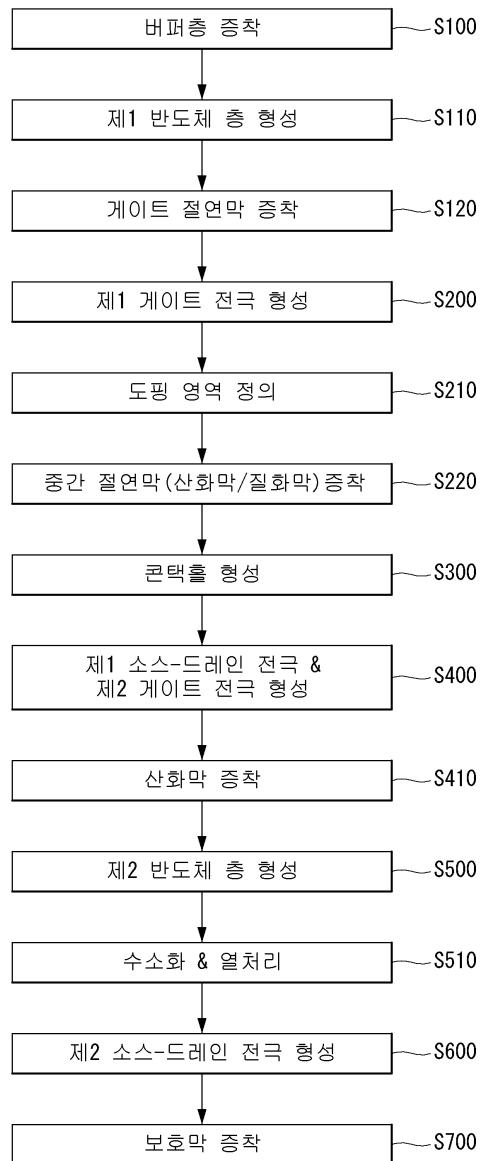

[0086] 그 외의 다른 구성 요소들은 제1 실시 예의 것과 동일하므로, 상세한 설명은 생략한다. 이후, 제2 실시 예에 의한 평판 표시장치용 박막 트랜지스터 기판을 제조하는 과정을 설명한다. 여기서도, 제1 실시 예의 것과 거의 동일하므로, 중요한 의미가 없는 동일한 설명은 생략한다. 도 4는 본 발명의 제2 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판을 제조하는 과정을 나타내는 순서도이다.

[0087] 기판(SUB) 위에 베퍼 층(BUF)을 증착한다. (S100)

[0088] 베퍼 층(BUF) 위에 아몰퍼스 실리콘(a-Si) 물질을 증착하고, 결정화를 수행하여 다결정 실리콘(poly-silicon)으로 만든다. 다결정 실리콘 물질을 제1 마스크 공정으로 패턴하여 제1 반도체 층(A1)을 형성한다. (S110)

[0089] 제1 반도체 층(A1)이 형성된 기판(SUB) 전체 표면 위에 산화 실리콘과 같은 절연 물질을 증착하여 게이트 절연막(GI)을 형성한다. 게이트 절연막(GI)은 약 1,000Å ~ 1,500Å의 두께를 갖는 산화 실리콘으로 형성하는 것이 바람직하다. (S120)

[0090] 게이트 절연막(GI) 상부에 게이트 금속 물질을 증착하고, 제2 마스크 공정으로 패턴하여 제1 게이트 전극(G1)을 형성한다. 제1 게이트 전극(G1)은 제1 반도체 층(A1)의 중심부와 중첩하도록 배치한다. (S200)

[0091] 제1 게이트 전극(G1)을 마스크로 하여, 하부에 배치된 제1 반도체 층(A1)에 불순물을 주입하여 소스 영역(SA) 및 드레인 영역(DA)을 포함하는 도핑 영역을 정의한다. (S210)

[0092] 제1 게이트 전극(G1)이 형성된 기판(SUB) 전체 표면 위에 중간 절연막(ILD)을 증착한다. 특히, 하부 산화막(SIO2)과 질화막(SIN)이 적층된 이중층 구조로 증착한다. 중간 절연막(ILD)은 하부 산화막(SIO2)이 아래에, 질화막(SIN)이 위에 적층될 수도 있고, 그 반대의 구조로 적층될 수도 있다. 아래에 하부 산화막(SIO2)이 적층되는 경우, 하부 산화막(SIO2)은 500Å ~ 1,000Å의 두께로, 질화막(SIN)은 1,000Å ~ 3,000Å의 두께를 갖도록 연속으로 적층하는 것이 바람직하다. 아래에 질화막(SIN)이 적층되는 경우, 하부 산화막(SIO2)도 1,000Å ~ 3,000Å 정도로 적층하여 제2 반도체 층(A2)으로 수소가 지나치게 확산하는 것을 더 효과적으로 방지할 수 있다. (S220)

[0093] 제3 마스크 공정으로 중간 절연막(ILD)을 패턴하여, 제1 반도체 층(A1)의 일측부 및 타측부를 각각 노출하는 소스 콘택홀(SH)과 드레인 콘택홀(DH)을 형성한다. (S300)

[0094] 중간 절연막(ILD) 위에 금속 물질을 증착한다. 제4 마스크 공정으로 금속 물질을 패턴하여, 제1 소스 전극(S1)

및 제1 드레인 전극(D1) 그리고 제2 게이트 전극(G2)을 형성한다. 제1 소스 전극(S1)은 소스 콘택홀(SH)을 통해 제1 반도체 층(A1)의 일측변과 접촉한다. 제1 드레인 전극(D1)은 드레인 콘택홀(DH)을 통해 제1 반도체 층(A1)의 타측변과 접촉한다. 제2 게이트 전극(G2)은 제2 박막 트랜지스터(T2)가 형성될 위치에 배치한다. (S400)

[0095] 제1 소스 전극(S1) 및 제1 드레인 전극(D1) 그리고 제2 게이트 전극(G2)들이 형성된 기판(SUB)의 전체 표면 위에 산화 실리콘(SiO<sub>x</sub>)과 같은 산화 무기물질을 이용하여 산화막(SIO)을 증착한다. 산화막(SIO)은 제2 박막 트랜지스터(T2)에서 게이트 절연막의 기능을 하면서, 수소 확산을 방지하는 기능을 한다. 따라서, 1,000Å ~ 3,000Å의 두께로 적층하는 것이 바람직하다. (S410)

[0096] 산화막(SIO) 위에 산화물 반도체 물질을 증착하고, 제5 마스크 공정으로 패턴하여 제2 반도체 층(A2)을 형성한다. 제2 반도체 층(A2)은 제2 게이트 전극(G2)과 중첩하도록 배치한다. (S500)

[0097] 제2 반도체 층(A2)이 형성된 기판(SUB)을 후속 열처리하여, 다결정 실리콘을 포함하는 제1 반도체 층(A1)의 수소화 처리와 산화물 반도체 물질을 포함하는 제2 반도체 층(A2)의 열처리를 동시에 수행한다. 후속 열처리 공정은, 350°C 내지 380°C의 온도 상태에서 수행한다. 이때, 질화막(SIN)에 포함된 수소는 제1 반도체 층(A1)으로 다양 확산되는 반면, 산화막(SIO)에 의해 제2 반도체 층(A2)으로 확산되는 양이 제한된다. 경우에 따라, 제1 반도체 층(A1)의 수소화 공정과 제2 반도체 층(A2)의 열처리 공정을 분리하여 수행할 수도 있다. (S510)

[0098] 제2 반도체 층(A2)이 형성된 기판(SUB)의 전체 표면 위에 소스-드레인 금속 물질을 증착한다. 제6 마스크 공정으로 소스-드레인 금속 물질을 패턴하여 제2 소스 전극(S2) 및 제2 드레인 전극(D2)을 형성한다. (S600)

[0099] 제1 및 제2 박막 트랜지스터(T1, T2)들이 형성된 기판(SUB) 전체 표면 위에 보호막(PAS)을 증착한다. (S700)

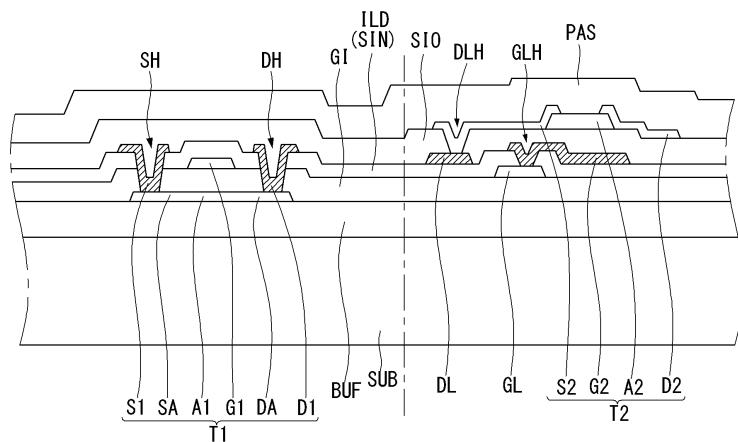

[0100] < 제3 실시 예 >

[0101] 이하, 도 5를 참조하여, 본 발명의 제3 실시 예에 대하여 설명한다. 도 5는 본 발명의 제3 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판을 나타내는 단면도이다.

[0102] 본 발명의 제3 실시 예는, 기본적인 구성은 제1 및 제2 실시 예와 동일하다. 차이가 있다면, 산화막(SIO)은 제1 박막 트랜지스터(T1)에 대해서는 중간 절연막 기능을 하며, 제2 박막 트랜지스터(T2)에 대해서는 게이트 절연막 기능을 한다는 데 있다. 구체적으로는, 중간 절연막(ILD)은 제1 중간 절연막(ILD1)과 제2 중간 절연막(ILD2)으로 이루어진다. 제1 중간 절연막(ILD1)은 하부 산화막(SI02)과 질화막(SIN)이 적층된 구조를 갖는다. 특히, 질화막(SIN)이 제2 박막 트랜지스터(T2)가 배치된 제2 영역에는 배치되지 않고, 제1 박막 트랜지스터(T1)가 배치된 제1 영역을 선택적으로 덮는 구조를 갖는다. 제2 중간 절연막(ILD2)은 산화막(SIO)으로 이루어지는 것으로 제2 박막 트랜지스터(T2)의 게이트 절연막 기능을 한다.

[0103] 제1 박막 트랜지스터(T1)가 배치된 영역에는 질화막(SIN)을 배치함으로써, 후속 열처리 공정을 통해, 질화막(SIN)에 포함된 수소를 제1 반도체 층(A1)으로 확산할 수 있다. 수소 확산 효율을 고려하여, 질화막(SIN)은 1,000Å ~ 3,000Å의 두께를 갖는 것이 바람직하다. 한편, 하부 산화막(SI02)은 500Å ~ 1,000Å 정도의 얇은 두께를 갖는 것이 바람직하다.

[0104] 질화막(SIN)이 3,000Å 정도의 두께를 갖더라도, 제2 박막 트랜지스터(T2)와는 상당한 거리로 이격되어 있으므로, 질화막(SIN) 내의 수소가 제2 반도체 층(A2)으로 확산될 가능성은 현저히 떨어진다. 또한, 질화막(SIN) 위에는 제2 중간 절연막(ILD2)인 산화막(SIO)이 더 적층되어 있으므로, 수소가 제2 반도체 층(A2)으로 확산되는 것을 확실히 방지할 수 있다.

[0105] 한편, 제3 실시 예에서는 제1 및 제2 실시 예와 달리, 제1 소스-드레인 전극(S1, D1)들과 제2 소스-드레인 전극(S2, D2)들이 동일층에서 동일한 물질로 형성된 특징이 있다.

[0106] 그 외의 다른 구성 요소들은 제1 및/또는 제2 실시 예의 것과 동일하므로, 중복되는 설명은 생략한다. 이후, 제3 실시 예에 의한 평판 표시장치용 박막 트랜지스터 기판을 제조하는 과정을 설명한다. 여기서도, 제1 및/또는 제2 실시 예의 것과 거의 동일하므로, 중복되는 설명은 생략한다. 도 5는 본 발명의 제3 실시 예에 의한 서로 다른 유형의 박막 트랜지스터들을 포함하는 평판 표시장치용 박막 트랜지스터 기판을 제조하는 과정을 나타내는 순서도이다.

[0107] 기판(SUB) 위에 베퍼 층(BUF)을 증착한다. (S100)

[0108] 베퍼 층(BUF) 위에 아몰퍼스 실리콘(a-Si) 물질을 증착하고, 결정화를 수행하여 다결정 실리콘(poly-silicon)으

로 만든다. 다결정 실리콘 물질을 제1 마스크 공정으로 패턴하여 제1 반도체 층(A1)을 형성한다. (S110)

[0109] 제1 반도체 층(A1)이 형성된 기판(SUB) 전체 표면 위에 산화 실리콘과 같은 절연 물질을 증착하여 게이트 절연막(GI)을 형성한다. 게이트 절연막(GI)은 약 1,000Å ~ 1,500Å의 두께를 갖는 산화 실리콘으로 형성하는 것이 바람직하다. (S120)

[0110] 게이트 절연막(GI) 상부에 게이트 금속 물질을 증착하고, 제2 마스크 공정으로 패턴하여 제1 게이트 전극(G1)을 형성한다. 제1 게이트 전극(G1)은 제1 반도체 층(A1)의 중심부와 중첩하도록 배치한다. (S200)

[0111] 제1 게이트 전극(G1)을 마스크로 하여, 하부에 배치된 제1 반도체 층(A1)에 불순물을 주입하여 소스 영역(SA) 및 드레인 영역(DA)을 포함하는 도핑 영역을 정의한다. (S210)

[0112] 제1 게이트 전극(G1)이 형성된 기판(SUB) 전체 표면 위에 제1 중간 절연막(ILD1)을 증착한다. 특히, 하부 산화막(SI02)과 질화막(SIN)이 적층된 이중층 구조로 형성한다. 제1 중간 절연막(ILD1)은 하부 산화막(SI02)이 아래에 질화막(SIN)이 상부에 적층될 수도 있고, 그 반대의 구조로 적층될 수도 있다. 아래에 하부 산화막(SI02)이 적층되는 경우, 하부 산화막(SI02)은 500Å ~ 1,000Å의 두께로, 질화막(SIN)은 1,000Å ~ 3,000Å의 두께를 갖도록 연속으로 적층하는 것이 바람직하다. 하부에 질화막(SIN)이 적층되는 경우, 하부 산화막(SI02)은 1,000Å ~ 3,000Å 정도로 적층하여 제2 반도체 층(A2)으로 수소가 지나치게 확산하는 것을 더 효과적으로 방지할 수 있다. (S220)

[0113] 제3 마스크 공정으로 제1 중간 절연막(ILD1)의 질화막(SIN)만을 제1 반도체 층(A1)을 덮도록 패턴한다. 질화막(SIN)이 하부에 배치되는 경우에는, 질화막(SIN)을 증착한 후 질화막(SIN)을 패턴하고, 하부 산화막(SI02)을 적층한다. 질화막(SIN)이 상부에 배치되는 경우에는, 하부 산화막(SI02)과 질화막(SIN)을 연속 증착한 후, 질화막(SIN)만을 패턴한다. (S300)

[0114] 제1 반도체 층(A1) 위에만 선택적으로 형성된 질화막(SIN)을 포함하는 제1 중간 절연막(ILD1) 위에 게이트 금속 물질을 증착한다. 제4 마스크 공정으로 게이트 금속 물질을 패턴하여, 제2 게이트 전극(G2)을 형성한다. 제2 게이트 전극(G2)은 제2 박막 트랜지스터(T2)가 형성될 위치에 배치한다. (S400)

[0115] 제2 게이트 전극(G2)들이 형성된 기판(SUB)의 전체 표면 위에 산화 실리콘(SiO<sub>x</sub>)과 같은 산화 무기물질을 이용하여 산화막(SI0)으로 이루어진 제2 중간 절연막(ILD2)을 증착한다. (S410)

[0116] 제2 중간 절연막(ILD2) 위에 산화물 반도체 물질을 증착하고, 제5 마스크 공정으로 패턴하여 제2 반도체 층(A2)을 형성한다. 제2 반도체 층(A2)은 제2 게이트 전극(G2)과 중첩하도록 배치한다. (S500)

[0117] 제2 반도체 층(A2)이 형성된 기판(SUB)을 후속 열처리하여, 다결정 실리콘을 포함하는 제1 반도체 층(A1)의 수소화 처리와 산화물 반도체 물질을 포함하는 제2 반도체 층(A2)의 열처리를 동시에 수행한다. 후속 열처리 공정은, 350°C 내지 380°C의 온도 상태에서 수행한다. 경우에 따라, 제1 반도체 층(A1)의 수소화 공정과 제2 반도체 층(A2)의 열처리 공정을 분리하여 수행할 수도 있다. 이때, 질화막(SIN)에 포함된 수소는 제1 반도체 층(A1)으로 다량 확산된다. 반면에, 질화막(SIN)은 제1 채널층(A1)이 있는 제1 영역에만 덮고 있으므로, 제2 채널층(A2)로는 확산되는 양이 제한된다. (S510)

[0118] 반도체 층에 대해 후속 열 처리를 수행한 후, 제6 마스크 공정으로, 제2 중간 절연막(ILD2) 및 제1 중간 절연막(ILD1)을 패턴하여, 소스 콘택홀(SH)과 드레인 콘택홀(DH)들을 형성한다. (S600)

[0119] 콘택홀(SH, DH)들과 제2 반도체 층(A2)이 형성된 기판(SUB)의 전체 표면 위에 소스-드레인 금속 물질을 증착한다. 제7 마스크 공정으로 소스-드레인 금속 물질을 패턴하여 제1 소스 전극, 제1 드레인 전극, 제2 소스 전극 및 제2 드레인 전극(S1, D1, S2, D2)을 형성한다. (S700)

[0120] 제1 및 제2 박막 트랜지스터(T1, T2)들이 형성된 기판(SUB) 전체 표면 위에 보호막(PAS)을 증착한다. (S800)

[0121] < 제1 응용 예 >

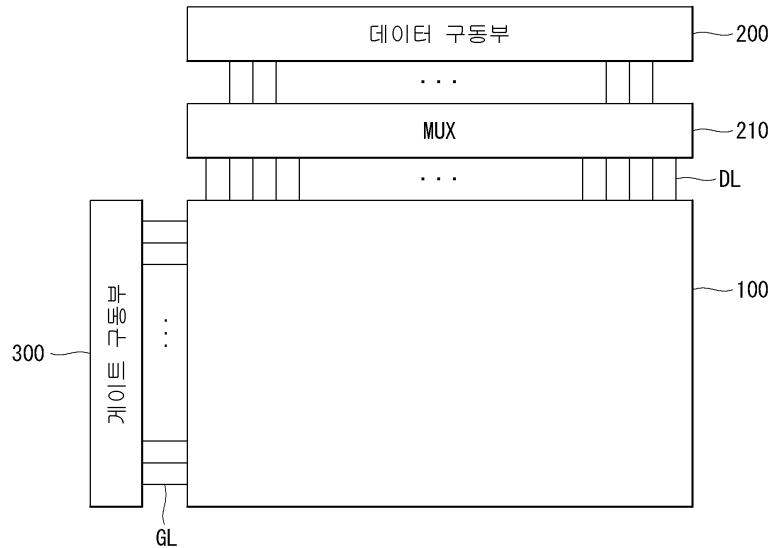

[0122] 지금까지 설명한 서로 다른 박막 트랜지스터들을 구비한 박막 트랜지스터 기판은, 다양한 평판 표시장치에 응용될 수 있다. 본 발명에서 제시한 바와 같이, 서로 다른 특징을 갖는 박막 트랜지스터들을 하나의 기판에 형성한 경우에 얻을 수 있는 장점은 다양하다. 이하, 도 7을 참조하여, 본 발명의 제1 응용 예에 의한 박막 트랜지스터 기판을 사용한 표시장치에서 어떠한 특징이 있으며, 어떠한 장점을 기대할 수 있는지 상세히 설명한다. 도 7은 본 발명의 제1 응용 예에 따른 표시장치의 구성을 개략적으로 보여 주는 블록도이다.

[0123] 제1 및 제2 박막 트랜지스터들(T1, T2) 중 하나 이상은 표시패널(100)의 화소들 각각에 형성되어 화소들에 기입되는 데이터 전압을 스위칭하거나 픽셀들을 구동하는 박막 트랜지스터일 수 있다. 유기발광 다이오드 표시장치의 경우에, 제2 박막 트랜지스터(T2)는 화소의 스위치 소자로 적용되고, 제1 박막 트랜지스터(T1)는 구동 소자로 적용될 수 있으나 이에 한정되지 않는다. 제1 및 제2 박막 트랜지스터(T1, T2)는 조합되어 하나의 스위치 소자나 하나의 구동 소자로 적용될 수도 있다.

[0124] 모바일 기기나 웨어러블 기기에서 소비 전력을 줄이기 위하여 프레임 레이트(Frame rate)를 낮추는 저속 구동 방법이 시도되고 있다. 이 경우에, 정지 영상이나 데이터의 업데이트 주기가 늦은 영상에서 프레임 주파수를 낮출 수 있다. 그런데 프레임 레이트를 낮추면, 데이터 전압이 바뀔 때마다 휘도가 번쩍이는 현상이 보이거나 픽셀의 전압 방전 시간이 길어져 데이터 업데이트 주기로 휘도가 깜빡이는 플리커 현상이 보일 수 있다. 본 발명의 제1 및 제2 박막 트랜지스터(T1, T2)를 화소에 적용하면 저속 구동 시의 플리커 문제를 해결할 수 있다.

[0125] 저속 구동시에 데이터 업데이트 주기가 길어지면 스위치 박막 트랜지스터의 누설 전류량이 커진다. 스위치 박막 트랜지스터의 누설 전류는 스토리지 커패시터(STG)의 전압과 구동 박막 트랜지스터의 게이트-소스 간 전압의 저하를 초래한다. 본 발명은 산화물 트랜지스터인 제2 박막 트랜지스터를 화소의 스위치 박막 트랜지스터로 적용할 수 있다. 산화물 트랜지스터는 오프 커런트가 낮기 때문에 스토리지 커패시터와 구동 박막 트랜지스터의 게이트 전압 강하를 방지할 수 있다. 따라서, 본 발명은 저속 구동시 플리커를 방지할 수 있다.

[0126] 폴리 실리콘 트랜지스터인 제1 박막 트랜지스터를 화소의 구동 박막 트랜지스터로 적용하면 전자의 이동도가 높기 때문에 유기 발광 다이오드로 공급되는 전류양을 크게 할 수 있다. 따라서, 본 발명은 화소의 스위치 소자에 제2 박막 트랜지스터(T2)를 적용하고, 화소의 구동 소자에 제1 박막 트랜지스터(T1)를 적용하여 소비 전력을 대폭 낮추면서 화질 저하를 방지할 수 있다.

[0127] 본 발명은 소비전력을 줄이기 위해서 저속 구동 방법을 적용할 때 화질 저하를 방지할 수 있기 때문에 모바일 기기나 웨어러블 기기에 적용하는데에 효과적이다. 일례로, 휴대용 전자시계는 소비전력을 낮추기 위하여 1초 단위로 표시화면의 데이터를 업데이트할 수 있다. 이 때의 프레임 주파수는 1Hz이다. 본 발명은 1Hz 또는 정지영상에 가까운 구동 주파수를 이용하여도 플리커 없는 우수한 화질을 구현할 수 있다. 본 발명은 모바일 기기나 웨어러블 기기의 대기 화면에서 정지 영상의 프레임 레이트를 크게 낮추어 화질 저하 없이 소비 전력을 대폭 감소시킬 수 있다. 그 결과, 본 발명은 모바일 기기나 웨어러블 기기의 화질을 개선하고 배터리 수명을 길게 하여 휴대성을 높일 수 있다. 본 발명은 데이터 업데이트 주기가 매우 긴 전자책(E-Book)에서도 화질 저하 없이 소비전력을 크게 줄일 수 있다.

[0128] 제1 및 제2 박막 트랜지스터들(T1, T2) 중 하나 이상은 구동회로 예를 들면, 도 7에서 데이터 구동부(200), 멀티플렉서(MUX, 210), 게이트 구동부(300) 중 하나 이상에 내장되어 구동 회로를 구성할 수 있다. 이 구동 회로는 화소에 데이터를 기입한다. 또한, 제1 및 제2 박막 트랜지스터들(T1, T2) 중에서 어느 하나는 화소 내에 형성되고 다른 하나는 구동회로에 형성될 수 있다. 데이터 구동부(200)는 입력 영상의 데이터를 데이터 전압으로 변환하여 출력한다. 멀티플렉서(210)는 데이터 구동부(200)로부터의 데이터 전압을 다수의 데이터 배선들(DL)로 시분할 분배함으로써 데이터 구동부(200)의 출력 채널 수를 줄인다. 게이트 구동부(300)는 데이터 전압에 동기되는 스캔 신호(또는 게이트 신호)를 게이트 배선(GL)으로 출력하여 입력 영상의 데이터가 기입되는 화소를 라인 단위로 순차적으로 선택한다. 게이트 구동부(300)의 출력 채널 수를 줄이기 위하여, 게이트 구동부(300)와 게이트 배선들(GL) 사이에 도시하지 않은 멀티플렉서가 추가될 수 있다. 멀티플렉서(210)와 게이트 구동부(300)는 도 7과 같이 화소 어레이와 함께 박막 트랜지스터 기판 상에 직접 형성할 수 있다. 멀티플렉서(210)와 게이트 구동부(300)는 도 7과 같이 비 표시 영역(NA)에 배치되고, 화소 어레이는 표시 영역(AA)에 배치된다.

[0129] 본 발명의 표시장치는 박막 트랜지스터를 이용한 능동형 표시장치 예를 들면, 액정 표시장치, 유기발광 다이오드 표시장치 및 전기영동 표시장치 등 박막 트랜지스터가 필요한 어떠한 표시장치에도 적용될 수 있다. 이하, 도면들을 더 참조하여, 본 발명에 의한 박막 트랜지스터 기판을 적용한 표시장치의 응용 예들에 대해서 설명한다.

[0130] < 제2 응용 예 >

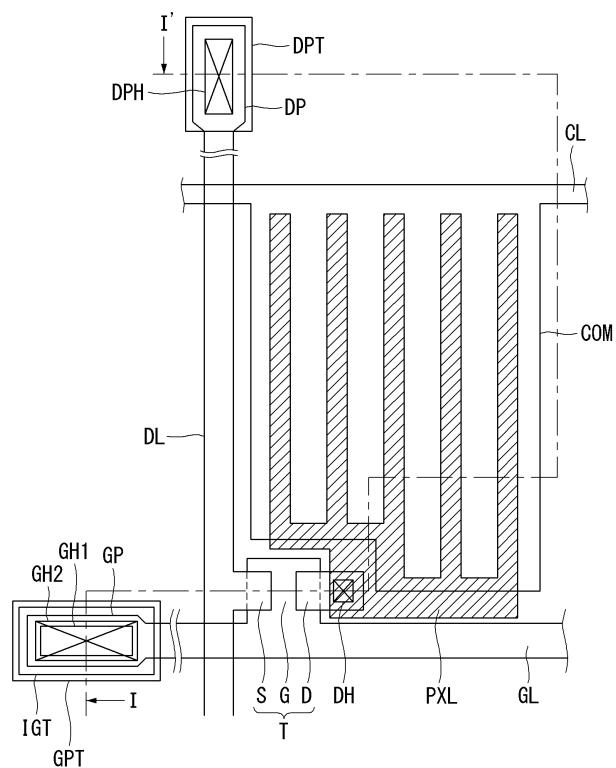

[0131] 도 8은 본 발명의 제2 응용 예에 의한 수평 전계형의 일종인 프린지 필드 방식의 액정 표시장치에 포함된 산화물 반도체 층을 갖는 박막 트랜지스터 기판을 나타내는 평면도이다. 도 9는 도 8에 도시한 박막 트랜지스터 기판을 절취선 I-I' 선을 따라 자른 단면도이다.

[0132] 도 8 및 도 9에 도시된 금속 산화물 반도체 층을 갖는 박막 트랜지스터 기판은 하부 기판(SUB) 위에 게이트 절

연막(GI)을 사이에 두고 교차하는 게이트 배선(GL) 및 데이터 배선(DL)과, 그 교차부마다 형성된 박막 트랜지스터(T)를 구비한다. 그리고 게이트 배선(GL)과 데이터 배선(DL)의 교차 구조에 의해 화소 영역이 정의된다.

[0133] 박막 트랜지스터(T)는 게이트 배선(GL)에서 분기한 게이트 전극(G), 데이터 배선(DL)에서 분기 된 소스 전극(S), 소스 전극(S)과 대향하는 드레인 전극(D), 그리고 게이트 절연막(GI) 위에서 게이트 전극(G)과 중첩하며, 소스 전극(S)과 드레인 전극(D) 사이에 채널 영역을 구비하는 반도체 층(A)을 포함한다.

[0134] 게이트 배선(GL)의 일측 단부에는 외부로부터 게이트 신호를 인가받기 위한 게이트 패드(GP)가 배치되어 있다. 게이트 패드(GP)는 게이트 절연막(GI)을 관통하는 제1 게이트 패드 콘택홀(GH1)을 통해 게이트 패드 중간 단자(IGT)와 접촉한다. 게이트 패드 중간 단자(IGT)는 제1 보호막(PA1)과 제2 보호막(PA2)을 관통하는 제2 게이트 패드 콘택홀(GH2)을 통해 게이트 패드 단자(GPT)와 접촉한다. 한편, 데이터 배선(DL)의 일측 단부에는 외부로부터 화소 신호를 인가받기 위한 데이터 패드(DP)가 배치되어 있다. 데이터 패드(DP)는 제1 보호막(PA1) 및 제2 보호막(PA2)을 관통하는 데이터 패드 콘택홀(DPH)을 통해 데이터 패드 단자(DPT)와 접촉한다.

[0135] 화소 영역에는 프린지 필드를 형성하도록 제2 보호막(PA2)을 사이에 두고 배치된 화소 전극(PXL)과 공통 전극(COM)을 구비한다. 공통 전극(COM)은 게이트 배선(GL)과 나란하게 배열된 공통 배선(CL)과 접속될 수 있다. 공통 전극(COM)은 공통 배선(CL)을 통해 액정 구동을 위한 기준 전압(혹은 공통 전압)을 공급받는다. 또 다른 방법으로, 공통 전극(COM)은, 드레인 콘택홀(DH)이 배치되는 부분을 제외한, 기판(SUB) 전체 표면에 배치된 모양을 가질 수 있다. 즉, 데이터 배선(DL)의 상층부를 덮는 형태를 가져, 공통 전극(COM)이 데이터 배선(DL)을 차폐하는 기능을 할 수도 있다.

[0136] 공통 전극(COM)과 화소 전극(PXL)의 위치 및 모양은 설계 환경과 목적에 맞추어 다양한 형상을 가질 수 있다. 공통 전극(COM)은 일정한 기준 전압이 인가되는 반면, 화소 전극(PXL)은 구현하고자 하는 비디오 데이터에 따라 수시로 변화하는 전압 값이 인가된다. 따라서, 데이터 배선(DL)과 화소 전극(PXL) 사이에 기생 용량이 발생할 수 있다. 이러한 기생 용량으로 인해 화질에 문제를 야기할 수 있기 때문에, 공통 전극(COM)을 먼저 배치하고, 화소 전극(PXL)을 최상위층에 배치하는 것이 바람직하다.

[0137] 즉, 데이터 배선(DL) 및 박막 트랜지스터(T)를 덮는 제1 보호막(PA1) 위에 유전율이 낮은 유기물질을 두껍게 적층하여 평탄화 막(PAC)을 형성한 후에, 공통 전극(COM) 형성한다. 그리고 공통 전극(COM)을 덮는 제2 보호막(PA2)을 형성 한 후, 공통 전극(COM)과 중첩하는 화소 전극(PXL)을 제2 보호막(PA2) 위에 형성한다. 이러한 구조에서는 화소 전극(PXL)이 데이터 배선(DL)과 제1 보호막(PA1), 평탄화막(PAC), 그리고 제2 보호막(PA2)에 의해 이격되므로 데이터 배선(DL)과 화소 전극(PXL) 사이에 기생 용량을 줄일 수 있다. 하지만 이에 국한하는 것은 아니며, 경우에 따라 화소 전극(PXL)을 먼저 배치하고, 공통 전극(COM)을 최 상위층에 배치할 수도 있다.

[0138] 공통 전극(COM)은 화소 영역의 형태에 대응하는 장방형을 가지며, 화소 전극(PXL)은 다수 개의 선분 형상을 갖는다. 특히, 화소 전극(PXL)은 제2 보호막(PA2)을 사이에 두고 공통 전극(COM)과 수직 상으로 중첩하는 구조를 갖는다. 이로써, 화소 전극(PXL)과 공통 전극(COM) 사이에서 프린지 필드가 형성된다. 프린지 필드형 전계에 의해, 박막 트랜지스터 기판과 컬러 필터 기판 사이에서 수평 방향으로 배열된 액정분자들이 유전 이방성에 의해 회전한다. 그리고 액정 분자들의 회전 정도에 따라 화소 영역을 투과하는 광 투과율이 달라져 계조를 구현한다.

[0139] 본 발명의 제2 응용 예를 설명하는 도 8 및 9에서는, 편의상, 액정 표시장치에서 박막 트랜지스터(T)의 구조를 개략적으로만 도시하였다. 본 발명의 제1 내지 제2 실시 예에서 설명한 제1 또는 제2 박막 트랜지스터들(T1, T2)의 구조를 적용할 수 있다. 예를 들어, 저속 구동이 필요한 경우, 산화물 반도체 층을 구비한 제2 박막 트랜지스터(T2)를 적용할 수 있다. 저 소비 전력이 필요한 경우, 다결정 반도체 층을 구비한 제1 박막 트랜지스터(T1)를 적용할 수 있다. 또는 제1 및 제2 박막 트랜지스터(T1, T2)들을 모두 구비하면서, 서로를 연결하도록 구성하여, 상호 보완할 수 있도록 구성할 수도 있다.

#### < Third Application Example >

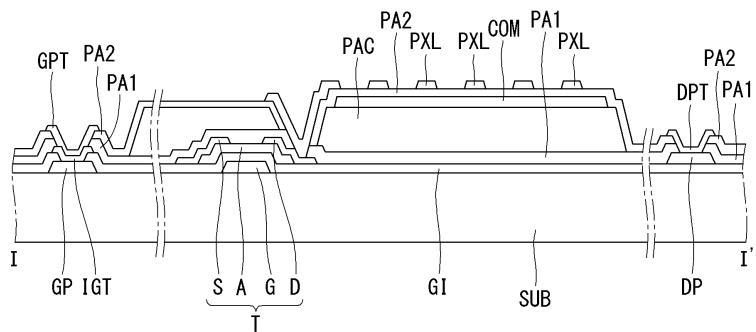

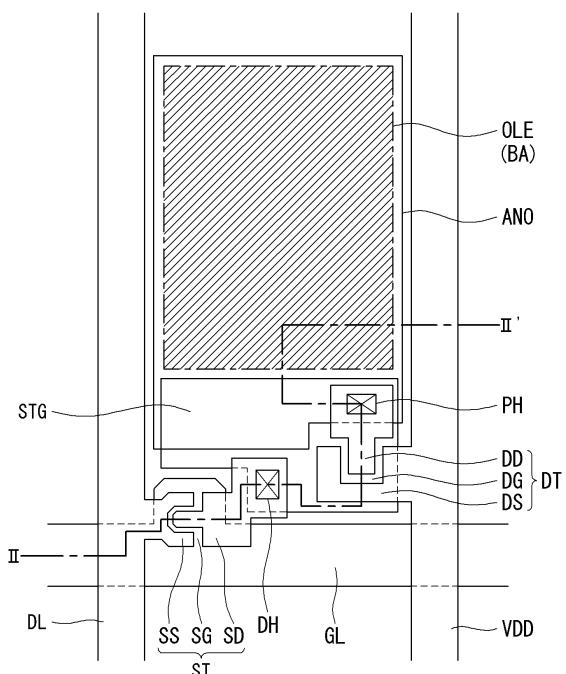

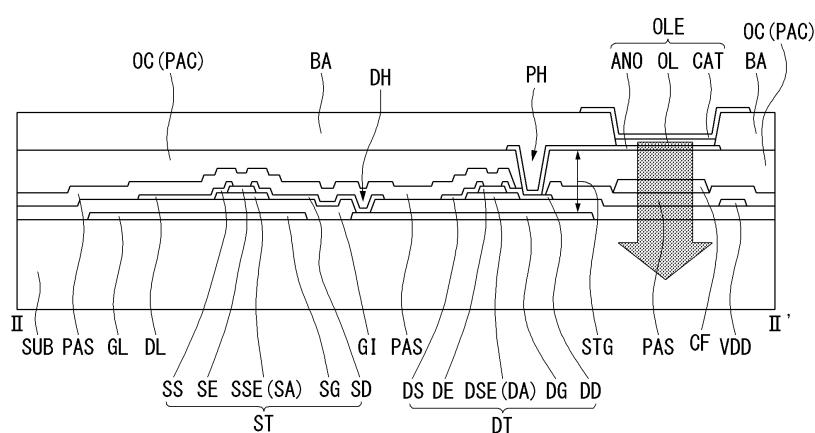

[0141] 도 10은 액티브 본 발명의 제3 응용 예에 의한 매트릭스 유기발광 다이오드 표시장치에서 한 화소의 구조를 나타내는 평면도이다. 도 11은 도 10에서 절취선 II-II'로 자른 액티브 매트릭스 유기발광 다이오드 표시장치의 구조를 나타내는 단면도이다.

[0142] 도 10 및 11을 참조하면, 액티브 매트릭스 유기발광 다이오드 표시장치는 스위칭 박막 트랜지스터(ST), 스위칭 박막 트랜지스터와 연결된 구동 박막 트랜지스터(DT), 구동 박막 트랜지스터(DT)에 접속된 유기발광 다이오드

(OLE)를 포함한다.

[0143] 스위칭 박막 트랜지스터(ST)는 기판(SUB) 위에서, 게이트 배선(GL)과 데이터 배선(DL)이 교차하는 부위에 배치되어 있다. 스위칭 박막 트랜지스터(ST)는, 스캔 신호에 응답하여 데이터 배선(DL)으로부터의 데이터 전압을 구동 박막 트랜지스터(DT)의 게이트 전극(DG)과 보조 용량(STG)에 공급함으로써, 화소를 선택하는 기능을 한다. 스위칭 박막 트랜지스터(ST)는 게이트 배선(GL)에서 분기하는 게이트 전극(SG)과, 반도체 층(SA)과, 소스 전극(SS)과, 드레인 전극(SD)을 포함한다. 그리고 구동 박막 트랜지스터(DT)는, 게이트 전압에 따라 화소의 유기발광 다이오드(OLE)에 흐르는 전류를 조절함으로써, 스위칭 박막 트랜지스터(ST)에 의해 선택된 화소의 유기발광 다이오드(OLE)를 구동한다.

[0144] 구동 박막 트랜지스터(DT)는 스위칭 박막 트랜지스터(ST)의 드레인 전극(SD)과 연결된 게이트 전극(DG)과, 반도체 층(DA), 구동 전류 배선(VDD)에 연결된 소스 전극(DS)과, 드레인 전극(DD)을 포함한다. 구동 박막 트랜지스터(DT)의 드레인 전극(DD)은 유기발광 다이오드(OLE)의 애노드 전극(ANO)과 연결되어 있다. 애노드 전극(ANO)과 캐소드 전극(CAT) 사이에는 유기발광 층(OL)이 개재되어 있다. 캐소드 전극(CAT)은 기저 배선(VSS)에 연결된다.

[0145] 좀 더 상세히 살펴보기 위해 도 11을 참조하면, 액티브 매트릭스 유기발광 다이오드 표시장치의 기판(SUB) 상에 스위칭 박막 트랜지스터(ST) 및 구동 박막 트랜지스터(DT)의 게이트 전극(SG, DG)이 배치되어 있다. 그리고 게이트 전극(SG, DG) 위에는 게이트 절연막(GI)이 덮고 있다. 게이트 전극(SG, DG)과 중첩되는 게이트 절연막(GI)의 일부에 반도체 층(SA, DA)이 배치되어 있다. 반도체 층(SA, DA) 위에는 일정 간격을 두고 소스 전극(SS, DS)과 드레인 전극(SD, DD)이 마주보도록 배치되어 있다. 스위칭 박막 트랜지스터(ST)의 드레인 전극(SD)은 게이트 절연막(GI)을 관통하는 드레인 콘택 홀(DH)을 통해 구동 박막 트랜지스터(DT)의 게이트 전극(DG)과 접촉한다. 이와 같은 구조를 갖는 스위칭 박막 트랜지스터(ST) 및 구동 박막 트랜지스터(DT)를 덮는 보호막(PAS)이 전체 표면에 적층되어 있다.

[0146] 애노드 전극(ANO)의 영역에 해당하는 부분에 칼라 필터(CF)가 배치되어 있다. 칼라 필터(CF)는 가급적 얇은 면적을 갖는 것이 바람직하다. 예를 들어, 데이터 배선(DL), 구동 전류 배선(VDD) 및 전단의 게이트 배선(GL)의 많은 영역과 중첩하는 형상을 갖는 것이 바람직하다. 이와 같이 스위칭 박막 트랜지스터(ST), 구동 박막 트랜지스터(DT) 및 칼라 필터(CF)들이 배치된 기판의 표면은 평탄하지 못하고, 단차가 심하다. 유기발광 층(OL)은 평탄한 표면에 적층되어야 발광이 일정하고 고르게 발산될 수 있다. 따라서, 기판의 표면을 평탄하게 할 목적으로 평탄화 막(PAC) 혹은 오버코트 층(OC)을 기판 전면에 적층한다.

[0147] 그리고 오버코트 층(OC) 위에 유기발광 다이오드(OLE)의 애노드 전극(ANO)이 배치되어 있다. 여기서, 애노드 전극(ANO)은 오버코트 층(OC) 및 보호막(PAS)에 형성된 화소 콘택 홀(PH)을 통해 구동 박막 트랜지스터(DT)의 드레인 전극(DD)과 연결된다.

[0148] 애노드 전극(ANO)이 배치된 기판 위에서, 화소 영역을 정의하기 위해 스위칭 박막 트랜지스터(ST), 구동 박막 트랜지스터(DT) 그리고 각종 배선들(DL, GL, VDD)이 배치된 영역 위에 뱅크(BA)(혹은, 뱅크 패턴)가 배치되어 있다. 뱅크(BA)에 의해 노출된 애노드 전극(ANO)이 발광 영역이 된다. 뱅크(BA)에 의해 노출된 애노드 전극(ANO) 위에 유기발광 층(OL)이 적층되어 있다. 그리고 유기발광 층(OL) 위에 캐소드 전극(CAT)이 순차적으로 적층되어 있다. 유기발광 층(OL)이 백색광을 발하는 유기물질로 이루어진 경우, 아래에 위치한 칼라 필터(CF)에 의해 각 화소에 배정된 색상을 나타낸다. 도 11과 같은 구조를 갖는 유기발광 다이오드 표시장치는 아래 방향으로 발광하는 하부 발광(Bottom Emission) 표시 장치가 된다.

[0149] 구동 박막 트랜지스터(DT)의 게이트 전극(DG)과 애노드 전극(ANO) 전극 사이에는 보조 용량(혹은, 'Storage Capacitance')(STG)이 배치되어 있다. 보조 용량(STG)은 구동 박막 트랜지스터(DT)에 연결되어 스위칭 박막 트랜지스터(ST)에 의해 구동 박막 트랜지스터(DT)의 게이트 전극(DG)에 인가되는 전압이 안정하게 유지되도록 한다.

[0150] 상기와 같이 박막 트랜지스터 기판을 응용함으로써, 고품질의 능동형 표시장치를 구현할 수 있다. 특히, 더욱 우수한 구동 특성을 갖도록 하기 위해서, 박막 트랜지스터의 반도체 층을 금속 산화물 반도체 물질로 형성하는 것이 바람직하다.

[0151] 금속 산화물 반도체 물질은 빛에 노출된 상태로 전압 구동될 경우 그 특성이 급격히 열화 되는 특성이 있다. 따라서, 반도체 층의 상부 및 하부에서 외부로부터 유입되는 빛을 차단할 수 있는 구조를 갖는 것이 바람직하다. 앞에서 설명한, 박막 트랜지스터 기판의 경우, 박막 트랜지스터는 바텀 게이트(Bottom Gate) 구조

를 갖는 것이 바람직하다. 즉, 하부에서 유입되는 빛은 금속 물질인 게이트 전극(G)에 의해 어느 정도 차단할 수 있다.

[0152] 이와 같이, 지금까지 평판 표시장치용 박막 트랜지스터 기판에는, 매트릭스 방식으로 배열된 다수 개의 화소 영역들이 배치된다. 또한, 각 단위 화소 영역들에는 적어도 하나 이상의 박막 트랜지스터가 배치된다. 즉, 기판 전체 영역에는 다수 개의 박막 트랜지스터들이 분포된 구조를 갖는다. 다수 개의 화소들 각각의 구조가 모두 동일한 목적으로 사용하고 동일한 품질과 성질을 가져야 하므로, 동일한 구조로 형성된다.

[0153] 하지만, 경우에 따라서는 박막 트랜지스터들의 특성을 다르게 할 필요가 있을 수도 있다. 예를 들어, 유기발광 다이오드 표시장치의 경우, 하나의 화소 영역 내에 스위칭 박막 트랜지스터(ST)와 구동 박막 트랜지스터(DT)를 포함한다. 스위칭 박막 트랜지스터(ST)와 구동 박막 트랜지스터(DT)는 그 목적이 서로 다르므로, 요구하는 특성도 다르다. 이를 위해, 동일한 구조와 동일한 반도체 채널층을 갖되 크기를 달리하여 각각의 기능에 맞도록 설계할 수 있다. 또는 필요하다면, 보상 박막 트랜지스터를 더 구비하여, 기능이나 성능을 보완할 수 있다.

[0154] 본 발명의 제3 응용 예를 설명하는 도 10 및 11에서는, 편의상, 유기발광 다이오드 표시장치의 박막 트랜지스터들(ST, DT)의 구조를 개략적으로만 도시하였다. 본 발명의 제1 내지 제2 실시 예에서 설명한 제1 또는 제2 박막 트랜지스터들(T1, T2)의 구조를 적용할 수 있다. 예를 들어, 스위칭 박막 트랜지스터(ST)에는 산화물 반도체 층을 구비한 제2 박막 트랜지스터(T2)를 적용할 수 있다. 구동 박막 트랜지스터(DT)에는, 다결정 반도체 층을 구비한 제1 박막 트랜지스터(T1)를 적용할 수 있다. 이와 같이, 제1 및 제2 박막 트랜지스터(T1, T2)들을 모두 구비하면서, 서로의 장점으로 상대 박막 트랜지스터의 단점을 상호 보완할 수 있다.

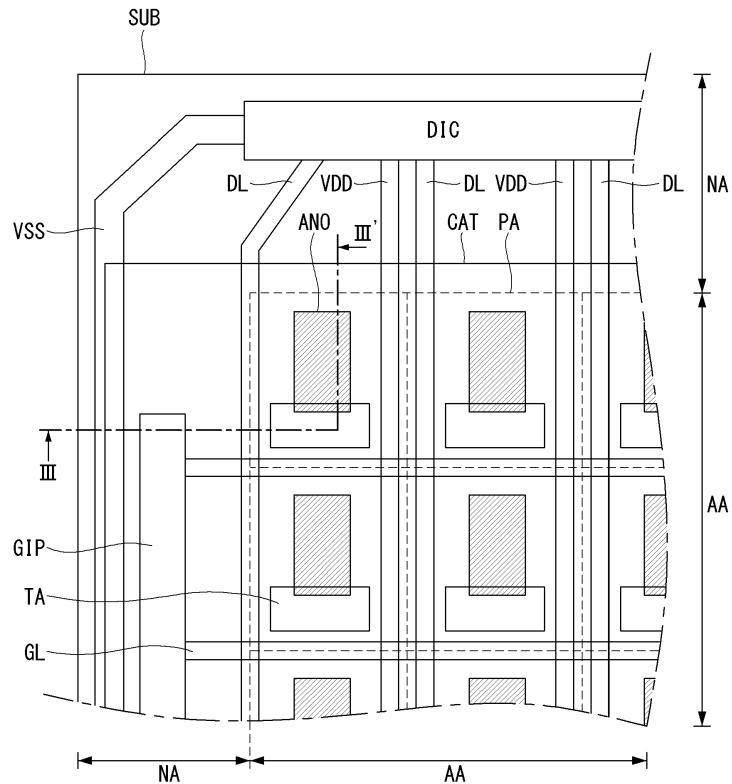

< 제4 응용 예 >

[0156] 또 다른 경우로, 표시장치의 비 표시 영역에 구동 소자를 내장한 박막 트랜지스터 기판을 사용하기도 한다. 이하, 도 12 및 13을 참조하여, 구동 소자를 표시 패널에 직접 형성한 경우에 대하여 상세히 설명한다.

[0157] 도 12는 본 발명의 제4 응용 예에 의한 유기발광 다이오드 표시장치의 개략적인 구조를 나타내는 평면 확대도이다. 도 13은 도 12에서 절취선 III-III'으로 자른 도면으로 본 발명의 제4 응용 예에 의한 유기발광 다이오드 표시장치의 구조를 나타내는 단면도이다. 여기서는, 구동 소자를 내장한 평판 표시장치용 박막 트랜지스터 기판을 설명하는 것으로서, 표시 영역 내에 배치된 박막 트랜지스터 및 유기발광 다이오드에 대한 상세한 설명은 생략한다.

[0158] 먼저, 도 12를 참조하여, 평면상에서의 구조에 대하여 설명한다. 본 발명의 제4 응용 예에 의한 게이트 구동부 (GIP)를 내장한 유기발광 다이오드 표시장치는 영상 정보를 표시하는 표시 영역(AA)과, 표시 영역(AA)을 구동하기 위한 여러 소자들이 배치되는 비 표시 영역(NA)으로 구분된 기판(SUB)을 포함한다. 표시 영역(AA)에는 매트릭스 방식으로 배열된 복수 개의 화소 영역(PA)들이 정의된다. 도 5에서는 점선으로 화소 영역(PA)들을 표시하였다.

[0159] 예를 들어, NxM 방식의 장방형으로 화소 영역(PA)들이 정의될 수 있다. 하지만, 반드시 이러한 방식에만 국한되는 것이 아니고, 다양한 방식으로 배열될 수도 있다. 각 화소 영역들이 동일한 크기를 가질 수도 있고, 서로 다른 크기를 가질 수도 있다. 또한, RGB(적녹청) 색상을 나타내는 세 개의 서브 화소를 하나의 단위로 하여, 규칙적으로 배열될 수도 있다. 가장 단순한 구조로 설명하면, 화소 영역(PA)들은 가로 방향으로 진행하는 복수 개의 게이트 배선(GL)들과 세로 방향으로 진행하는 복수 개의 데이터 배선(DL)들 및 구동 전류 배선(VDD)들의 교차 구조로 정의할 수 있다.

[0160] 화소 영역(PA)의 외주부에 정의된, 비 표시 영역(NA)에는 데이터 배선(DL)들에 화상 정보에 해당하는 신호를 공급하기 위한 데이터 구동부(혹은, Data Driving Integrated Circuit)(DIC)과, 게이트 배선(GL)들에 스캔 신호를 공급하기 위한 게이트 구동부(혹은, Gate Driving Integrated Circuit)(GIP)가 배치될 수 있다. 데이터 배선(DL)들 및 구동 전류 배선(VDD)들의 개수가 많아지는, VGA보다 더 높은 고 해상도의 경우에는, 데이터 구동부(DIC)는 기판(SUB)의 외부에 실장하고, 데이터 구동부(DIC) 대신에 데이터 접속 패드들이 배치될 수도 있다.

[0161] 표시장치의 구조를 단순하게 하기 위해, 게이트 구동부(GIP)는, 기판(SUB)의 일측 부에 직접 형성하는 것이 바람직하다. 그리고, 기판(SUB)의 최 외곽부에는 기저 전압을 공급하는 기저 배선(Vss)이 배치된다. 기저 배선(Vss)은 기판(SUB)의 외부에서 공급되는 기저 전압(Ground Voltage)을 인가받아, 데이터 구동부(DIC) 및 게이트 구동부(GIP)에 모두 기저 전압을 공급하도록 배치하는 것이 바람직하다. 예를 들어, 기전 배선(Vss)은 기판(SUB)의 상부 측면에 별도로 실장하게 될 데이터 구동부(DIC)에 연결되고, 기판(SUB)의 좌측 및/또는 우측 변에

배치된 게이트 구동부(GIP)의 외측에서 기판을 감싸듯이 배치될 수 있다.

[0162] 각 화소 영역(PA)에는 유기발광 다이오드 표시장치의 핵심 구성 요소들인 유기발광 다이오드와 유기발광 다이오드를 구동하기 위한 박막 트랜지스터들이 배치된다. 박막 트랜지스터들은 화소 영역(PA)의 일측 부에 정의된 박막 트랜지스터 영역(TA)에 배치될 수 있다. 유기발광 다이오드는 애노드 전극(ANO)과 캐소드 전극(CAT) 그리고, 두 전극들 사이에 개재된 유기발광 층(OL)을 포함한다. 실제로 발광하는 영역은 애노드 전극(ANO)과 중첩하는 유기발광 층의 면적에 의해 결정된다.

[0163] 애노드 전극(ANO)은 화소 영역(PA) 중에서 일부 영역을 차지하는 형상을 가지며, 박막 트랜지스터 영역(TA)에 배치된 박막 트랜지스터와 연결되어 있다. 애노드 전극(ANO) 위에 유기발광 층(OL)을 적층하는데, 애노드 전극(ANO)과 유기발광 층(OL)이 중첩된 영역이 실제 발광 영역으로 결정된다. 캐소드 전극(CAT)은 유기발광 층(OL) 위에서 적어도 화소 영역(PA)들이 배치된 표시 영역(AA)의 면적을 모두 덮도록 하나의 몸체로 형성한다.

[0164] 캐소드 전극(CAT)은 게이트 구동부(GIP)를 넘어 기판(SUB)의 외측부에 배치된 기저 배선(Vss)와 접촉한다. 즉, 기저 배선(Vss)을 통해 캐소드 전극(CAT)에 기저 전압을 인가한다. 캐소드 전극(CAT)은 기저 전압을 인가받고, 애노드 전극(ANO)은 화상 전압을 인가받아, 그 사이의 전압차이에 의해 유기발광 층(OL)에서 빛이 발광하여 화상 정보를 표시한다.

[0165] 도 13을 더 참조하여, 본 발명의 제4 응용 예에 의한 유기발광 다이오드 표시장치의 단면 구조를 더 상세히 설명한다. 기판(SUB) 위에 게이트 구동부(GIP)와 기저 배선(Vss)이 배치되는 비 표시 영역(NA), 그리고 스위칭 박막 트랜지스터(ST), 구동 박막 트랜지스터(DT) 및 유기발광 다이오드(OLE)가 배치되는 표시 영역(AA)이 정의된다.

[0166] 게이트 구동부(GIP)는 스위칭 박막 트랜지스터(ST) 및 구동 박막 트랜지스터(DT)를 형성하는 과정에서 함께 형성한 박막 트랜지스터를 구비할 수 있다. 화소 영역(PA)에 배치된 스위칭 박막 트랜지스터(ST)는 게이트 전극(SG), 게이트 절연막(GI), 채널층(SA), 소스 전극(SS) 및 드레인 전극(SD)을 포함한다. 또한, 구동 박막 트랜지스터(DT)는 스위칭 박막 트랜지스터(ST)의 드레인 전극(SD)과 연결된 게이트 전극(DG), 게이트 절연막(GI), 채널 층(DA), 소스 전극(DS) 및 드레인 전극(DD)을 포함한다.

[0167] 박막 트랜지스터들(ST, DT) 위에는 보호막(PAS)과 평탄화 막(PL)이 연속으로 적층되어 있다. 평탄화 막(PL) 위에는 화소 영역(PA) 내의 일정 부분만을 차지하는 고립된 장방형의 애노드 전극(ANO)이 배치되어 있다. 애노드 전극(ANO)은 보호막(PAS) 및 평탄화 막(PL)을 관통하는 콘택홀을 통해 구동 박막 트랜지스터(DT)의 드레인 전극(DD)과 접촉한다.

[0168] 애노드 전극(ANO)이 형성된 기판 위에는 발광 영역을 정의하는 뱅크(BA)가 배치되어 있다. 뱅크(BA)는, 애노드 전극(ANO)의 대부분을 노출하는 형상을 갖는다. 뱅크(BA) 패턴에 의해 노출된 애노드 전극(ANO) 위에는 유기발광 층(OL)이 적층되어 있다. 뱅크(BA)와 유기발광 층(OL) 위에는 투명 도전 물질로 이루어진 캐소드 전극(CAT)이 적층되어 있다. 이로써, 애노드 전극(ANO), 유기발광 층(OL) 및 캐소드 전극(CAT)을 포함하는 유기발광 다이오드(OLE)가 배치된다.

[0169] 유기발광 층(OL)이 백색광을 발현하고, 별도로 형성한 칼라 필터(CF)로 색상을 표현하도록 할 수 있다. 이 경우, 유기발광 층(OL)은 적어도 표시 영역(AA)을 모두 덮도록 적층하는 것이 바람직하다.

[0170] 캐소드 전극(CAT)은 게이트 구동부(GIP)를 넘어 기판(SUB)의 외측부에 배치된 기저 배선(Vss)와 접촉하도록 표시 영역(AA) 및 비 표시 영역(NA)에 걸쳐 덮고 있는 것이 바람직하다. 이로써, 기저 배선(Vss)을 통해 캐소드 전극(CAT)에 기저 전압을 인가할 수 있다.

[0171] 한편, 기저 배선(Vss)은 게이트 전극(G)과 동일한 물질로 동일한 층에 형성할 수 있다. 이 경우, 기저 배선(Vss)을 덮는 보호막(PAS) 및 게이트 절연막(GI)을 관통하는 콘택홀을 통해 캐소드 전극(CAT)과 접촉할 수 있다. 다른 방법으로, 기저 배선(Vss)은 소스-드레인(SS-SD, DS-DD) 전극과 동일한 물질로 동일한 층에 형성할 수도 있다. 이 경우, 기저 배선(Vss)은 보호막(PAS)을 관통하는 콘택홀을 통해 캐소드 전극(CAT)과 접촉할 수 있다.

[0172] 본 발명의 제4 응용 예를 설명하는 도 12 및 13에서는, 편의상, 유기발광 다이오드 표시장치의 박막 트랜지스터들(ST, DT) 및 게이트 구동 소자(GIP)의 박막 트랜지스터 구조를 개략적으로만 도시하였다. 본 발명의 제1 내지 제2 실시 예에서 설명한 제1 또는 제2 박막 트랜지스터들(T1, T2)의 구조를 적용할 수 있다. 예를 들어, 스위칭 박막 트랜지스터(ST)에는 산화물 반도체 층을 구비한 제2 박막 트랜지스터(T2)를 적용할 수 있다. 구동

박막 트랜지스터(DT)에는, 다결정 반도체 층을 구비한 제1 박막 트랜지스터(T1)를 적용할 수 있다. 그리고 게이트 구동부(GIP)에는 다결정 반도체 층을 구비한 제1 박막 트랜지스터(T1)를 적용할 수 있다. 필요하다면, 게이트 구동부(GIP)에는 P-MOS 형과 N-MOS 형을 모두 구비한 C-MOS 형 박막 트랜지스터를 구비할 수도 있다.

[0173]

이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특히 청구의 범위에 의해 정하여져야만 할 것이다.

### 부호의 설명

[0174]

|              |               |

|--------------|---------------|

| GL: 게이트 배선   | PAS: 보호막      |

| DL: 데이터 배선   | VDD: 구동 전류 배선 |

| PA: 화소 영역    | T: 박막 트랜지스터   |

| AA: 표시 영역    | NA: 비 표시 영역   |

| G: 게이트 전극    | A: 반도체 층      |

| S: 소스 전극     | D: 드레인 전극     |

| GI: 게이트 절연막  | ILD: 중간 절연막   |

| SIN: 질화막     | SIO: 산화막      |

| SIO1: 상부 산화막 | SIO2: 하부 산화막  |

### 도면

#### 도면 1a

도면1b

## 도면2

## 도면3

## 도면4

도면5

## 도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13