US 20010052785A1

# (19) United States (12) Patent Application Publication FARNWORTH et al. (10) Pub. No.: US 2001/0052785 A1 (43) Pub. Date: Dec. 20, 2001

# (54) TEST CARRIER FOR TESTING SEMICONDUCTOR COMPONENTS INCLUDING INTERCONNECT WITH SUPPORT MEMBERS FOR PREVENTING COMPONENT FLEXURE

(76) Inventors: WARREN M. FARNWORTH, NAMPA, ID (US); MIKE HESS, KUNA, ID (US); DAVID R. HEMBREE, BOISE, ID (US); JAMES M. WARK, BOISE, ID (US); JOHN O. JACOBSON, BOISE, ID (US); SALMAN AKRAM, BOISE, ID (US)

> Correspondence Address: STEPHEN A GRATTON 2764 SOUTH BRAUN WAY LAKEWOOD, CO 80228

- (\*) Notice: This is a publication of a continued prosecution application (CPA) filed under 37 CFR 1.53(d).

- (21) Appl. No.: 09/110,231

# (22) Filed: Jul. 6, 1998

# **Publication Classification**

| (51) | Int. Cl. <sup>7</sup> |  |

|------|-----------------------|--|

| (52) | U.S. Cl.              |  |

## (57) ABSTRACT

A test carrier and an interconnect for testing semiconductor components, such as bare dice and chip scale packages, are provided. The carrier includes a base on which the interconnect is mounted, and a force applying mechanism for biasing the component against the interconnect. The interconnect includes interconnect contacts configured to make temporary electrical connections with component contacts (e.g., bond pads, solder balls). The interconnect also includes support members configured to physically contact the component, to prevent flexure of the component due to pressure exerted by the force applying mechanism. The support members can be formed integrally with the interconnect using an etching process. In addition, the support members can include an elastomeric layer to provide cushioning and to accommodate Z-direction dimensional variations.

FIGURE 4

FIGURE 6

### TEST CARRIER FOR TESTING SEMICONDUCTOR COMPONENTS INCLUDING INTERCONNECT WITH SUPPORT MEMBERS FOR PREVENTING COMPONENT FLEXURE

# FIELD OF THE INVENTION

**[0001]** This invention relates generally to semiconductor manufacture, and more particularly to an improved test carrier and interconnect for temporarily packaging and testing semiconductor components, such as dice and chip scale packages. This invention also relates to a method for fabricating the carrier and the interconnect.

### BACKGROUND OF THE INVENTION

**[0002]** Semiconductor components, such as bare dice and chip scale packages, must be tested prior to shipment by semiconductor manufacturers. Since these components are relatively small and fragile, carriers have been developed for temporarily packaging the components for testing. The carriers permit electrical connections to be made between external contacts on the components, and testing equipment such as burn-in boards.

**[0003]** An interconnect on the carrier includes contacts that make the temporary electrical connections with the external contacts on the components. On bare dice, the external contacts typically comprise planar or bumped bond pads. On chip scale packages, the external contacts typically comprise solder balls in a dense array, such as a ball grid array, or a fine ball grid array.

[0004] One problem that can occur with a temporary carrier is flexure of the component in the assembled carrier. Typically, a force epplying mechanism of the carrier, such as a spring, presses the component against the interconnect. In order to insure physical and electrical contact between the external contacts on the component and the interconnect contacts, the force applying mechanism must exert a relatively large biasing force on the component. This large biasing force can sometimes cause the component to flex or bow. This flexure can cause some of the external contacts on the component to pull away from the interconnect contacts. Worse yet, the flexure can cause cracking and damage to the component.

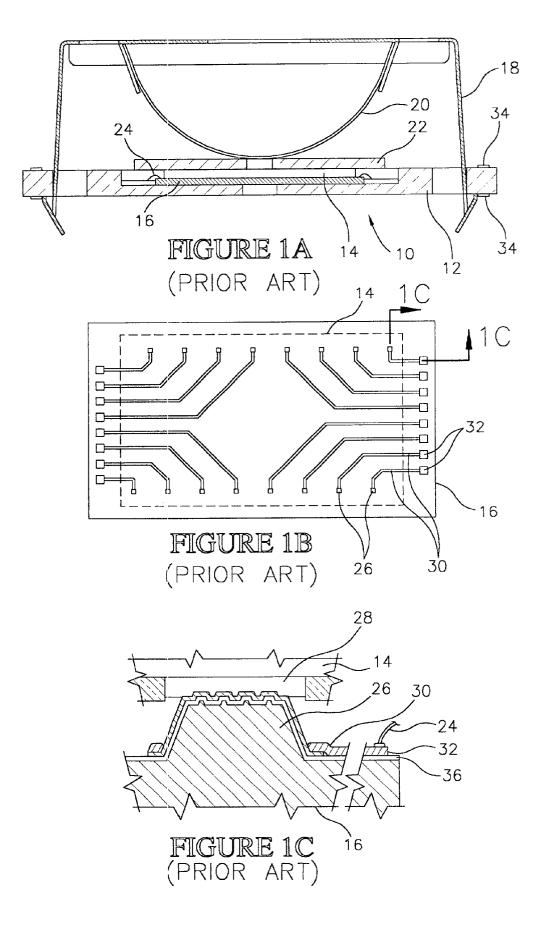

[0005] FIGS. 1A-1C illustrates a prior art test carrier 10 constructed to temporarily package a semiconductor component 14 for testing. In this case the component 14 comprises a bare semiconductor die. The test carrier 10 is further described in U.S. Pat. No. 5,519,332 to Wood et al., entitled "Carrier For Testing An Unpackaged Semiconductor Die", which is incorporated herein by reference.

[0006] The test carrier 10 includes a base 12 and an interconnect 16 mounted to the base 12. In addition, the test carrier 10 includes a bridge clamp 18, a spring 20 and a pressure plate 22, adapted to bias the component 14 against the interconnect 16.

[0007] As shown in FIGS. 1B and 1C, the interconnect 16 includes interconnect contacts 26 adapted to electrically engage component contacts 28 (FIG. 1C) on the component 14. For example, the component contacts 28 can comprise thin film aluminum bond pads in electrical communication with integrated circuits on the component 14. The intercon-

nect contacts 26 are in electrical communication with conductors 30 and bond pads 32 on the interconnect 16.

[0008] The interconnect 16 also includes an insulating layer 36 (FIG. 1C) for electrically insulating the interconnect contacts 26 and conductors 30. In addition, wires 24 (FIG. 1A) are bonded to the bond pads 32 on the interconnect 16, and electrically connect the interconnect contacts 26 to terminal contacts 34 (FIG. 1A) on the base 12 of the carrier 10.

**[0009]** The interconnect **16** is further described in U.S. Pat. No. 5,686,317 to Akram et al. entitled "Method For Forming An Interconnect Having A Penetration Limited Contact Structure For Establishing A Temporary Electrical Connection With A Semiconductor Die", which is incorporated herein by reference.

[0010] As shown in FIG. 1D, the component 14 can sometimes flex, or bow, under pressure from the spring 20 (FIG. 1A) and pressure plate 22 (FIG. 1A). This flexure can cause the component contacts 28 to pull away from the interconnect contacts 26. In addition, this flexure can cause damage to the component 14.

**[0011]** The present invention is directed to an improved test carrier and interconnect that are constructed to prevent flexure and bowing of a component under test.

# SUMMARY OF THE INVENTION

**[0012]** In accordance with the present invention, an improved test carrier and interconnect are provided. The test carrier can be used to temporarily package and test a semiconductor component, without flexure of the component in the assembled carrier. The component can comprise a bare die, or a chip scale package.

**[0013]** The carrier includes a base for mounting the interconnect, and a force applying mechanism for biasing the component against the interconnect. The interconnect includes a substrate, and contacts formed on the substrate configured to electrically engage contacts on the component. For planar component contacts (e.g., bond pads on a bare die), the interconnect contacts can comprise raised members having penetrating projections covered with conductive layers. For bumped component contacts (e.g., solder balls on a chip scale package), the interconnect contacts can comprise indentations covered with conductive layers.

[0014] The interconnect also includes support members configured to physically contact a surface of the component, to prevent flexure of the component while biasing pressure is exerted by the force applying mechanism. In an illustrative embodiment, the support members comprise raised pillars having a planar surface for engaging the surface of the component. In addition, the support members can include an elastomeric layer to provide cushioning, and to accommodate Z-direction dimensional variations in the component contacts. Further, the support members can be arranged to engage the component along edges thereof, in areas formed by streets, or scribe lines, of the component. In addition, the components can be provided with contact pads for physically engaging the support members on the interconnect. In an alternate embodiment, the support members are configured to physically contact a pressure plate of the force applying mechanism rather than the component.

**[0015]** In a first carrier embodiment the carrier base includes terminal contacts, and the interconnect is wire bonded to the base, with the interconnect contacts in electrical communication with -he terminal contacts on the base. In a second carrier embodiment, the interconnect includes conductive vias and external ball contacts in electrical communication with the interconnect contacts. In the second carrier embodiment, the interconnect contacts in electrical communication with the interconnect can be molded to the base with the external ball contacts exposed, to provide the terminal contacts for the carrier. In a third carrier embodiment the support members are formed on the carrier base rather than on the interconnect.

[0016] A method for fabricating the interconnect includes the steps of providing a substrate, and etching the substrate to form the interconnect contacts and support members. Conductive layers can then be deposited on the interconnect contacts, and if desired, an elastomeric layer can be deposited on the support members. For fabricating the interconnect with conductive vias, a laser machining process can be used to form openings in the substrate. The laser machined openings can then be filled with a conductive material, and ball contacts attached to the filled openings by soldering, brazing or welding pre-formed metal balls. Alternately a deposition process such as electroless or electrolytic plating can be used to form the ball contacts.

# BRIEF DESCRIPTION OF THE DRAWINGS

**[0017] FIG. 1A** is a cross sectional view of a prior art test carrier for temporarily packaging and testing a semiconductor component;

**[0018] FIG. 1B** is a plan view of a prior art interconnect of the test carrier with the component superimposed thereon;

[0019] FIG. 1C is an enlarged cross sectional view taken along section line 1C-1C of FIG. 1B illustrating an interconnect contact electrically engaging a component contact;

**[0020]** FIG. 1D is a schematic cross sectional view illustrating flexure of the component in the prior art test carrier;

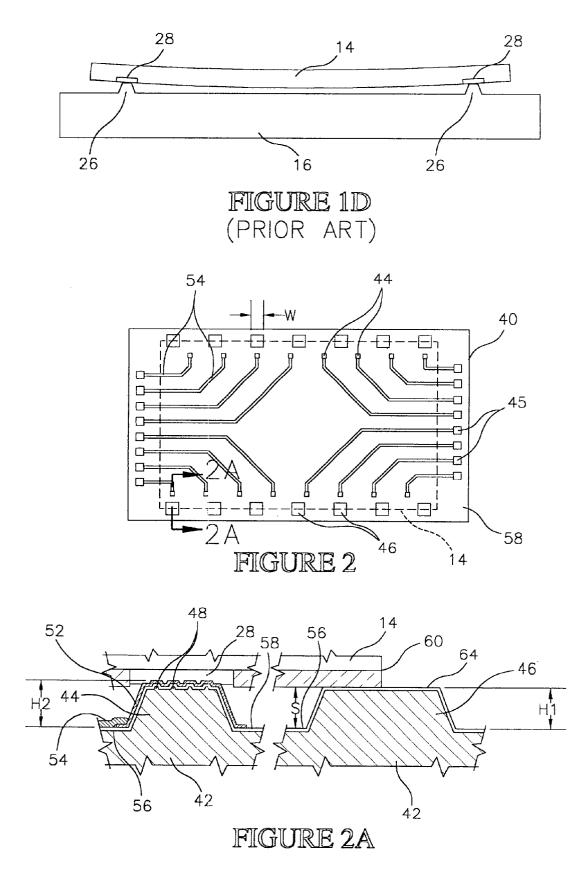

**[0021] FIG. 2** is a plan view of an interconnect constructed in accordance with the invention with the component superimposed thereon;

[0022] FIG. 2A is an enlarged cross sectional view taken along section line 2A-2A of FIG. 2 illustrating interconnect contacts and support members on the interconnect engaging the component;

**[0023]** FIG. 2B is an enlarged cross sectional view equivalent to a portion of FIG. 2B illustrating an alternate embodiment support member engaging the component;

**[0024]** FIG. 2C is an enlarged cross sectional view equivalent to a portion of FIG. 2B illustrating an alternate embodiment support member having an elastomeric layer thereon;

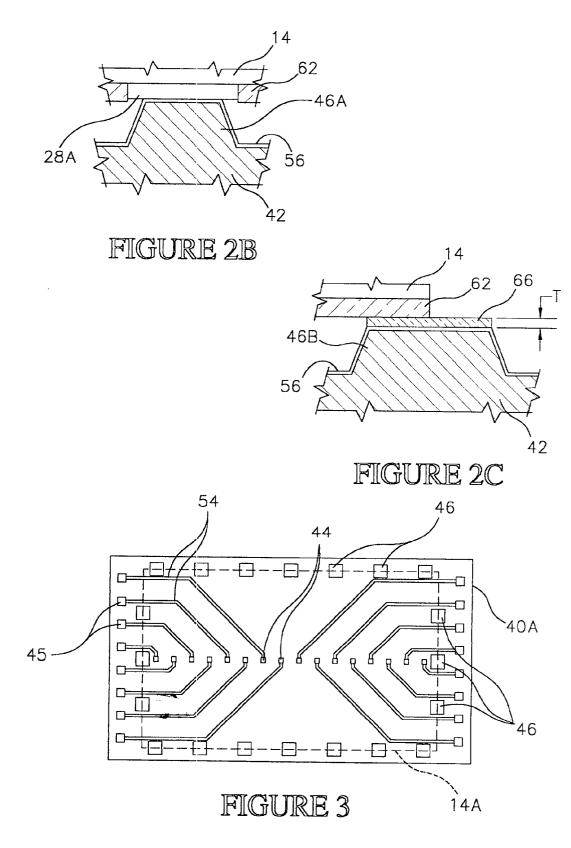

**[0025]** FIG. 3 is a plan view of an alternate embodiment interconnect constructed in accordance with the invention;

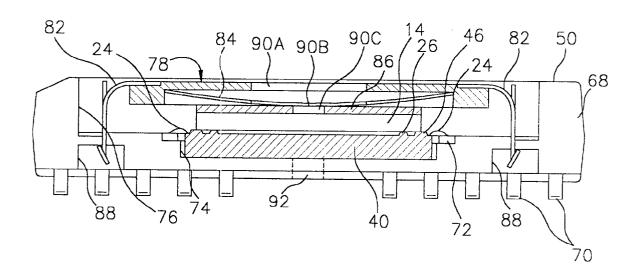

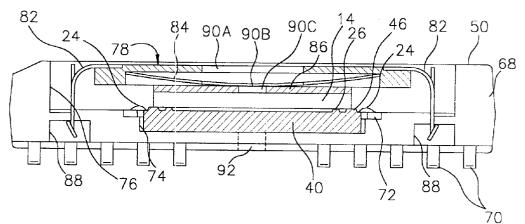

[0026] FIG. 4 is a cross sectional view of a carrier constructed with the interconnect of FIG. 2;

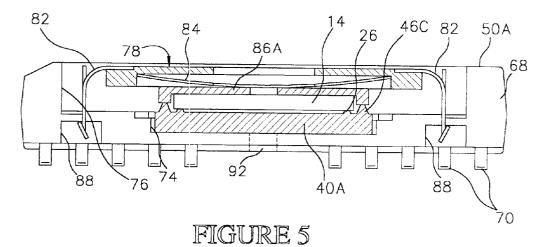

**[0027]** FIG. 5 is a cross sectional view of an alternate embodiment carrier constructed with an alternate embodiment interconnect;

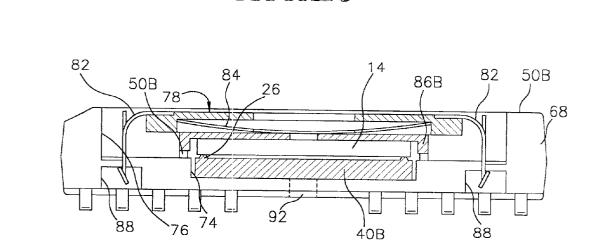

**[0028]** FIG. 6 is a cross sectional view of an alternate embodiment carrier;

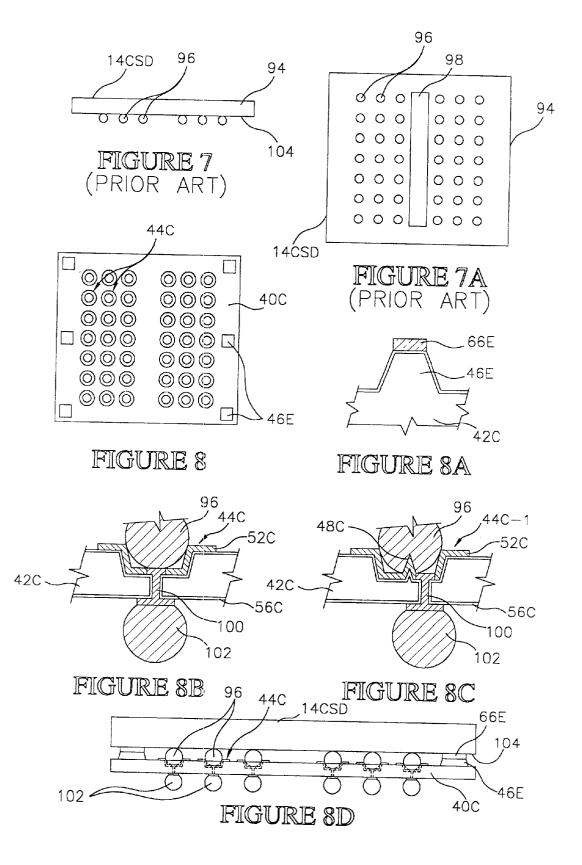

**[0029]** FIG. 7 is a side elevation view of a prior art chip scale package;

[0030] FIG. 7A is a bottom view of the package of FIG. 7;

[0031] FIG. 8 is plan view of an alternate embodiment interconnect;

**[0032] FIG. 8A** is a cross sectional view taken along section line **8A-8A** of **FIG. 8** illustrating a support member on the interconnect;

[0033] FIG. 8B is a cross sectional view taken along section line 8B-8B of FIG. 8 illustrating a contact of the interconnect;

[0034] FIG. 8C is a cross sectional view equivalent to FIG. 8B of an alternate embodiment contact;

[0035] FIG. 8D is e side elevation view of the carrier of FIG. 8 electrically engaging the chip scale package of FIG. 7;

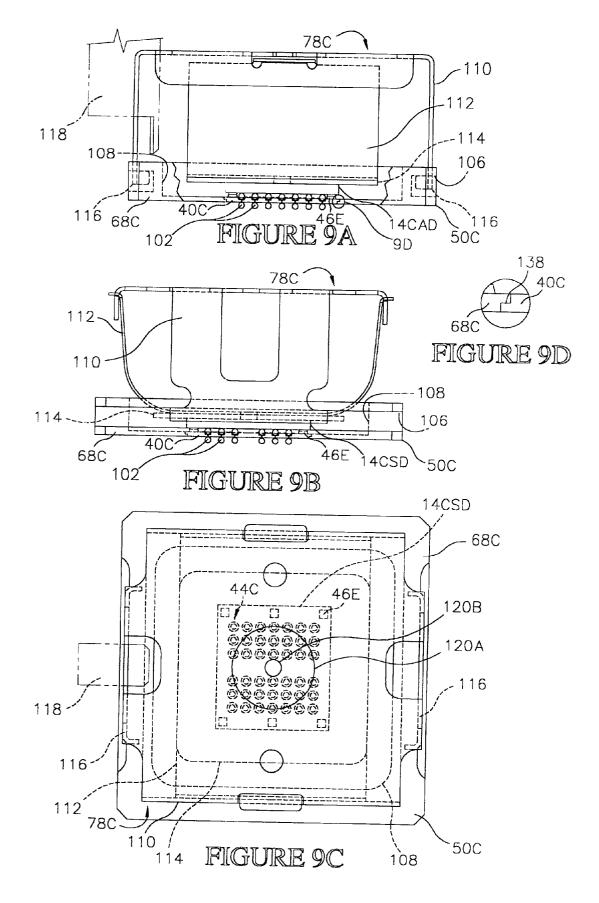

[0036] FIG. 9A is a side elevation view partially cut away of an alternate embodiment carrier constructed with the interconnect of FIG. 8;

[0037] FIG. 9B is an end elevation view of the carrier of FIG. 9A;

[0038] FIG. 9C is a plan view of the carrier of FIG. 9A;

[0039] FIG. 9D is an enlarged portion of FIG. 9A taken along section line 9D;

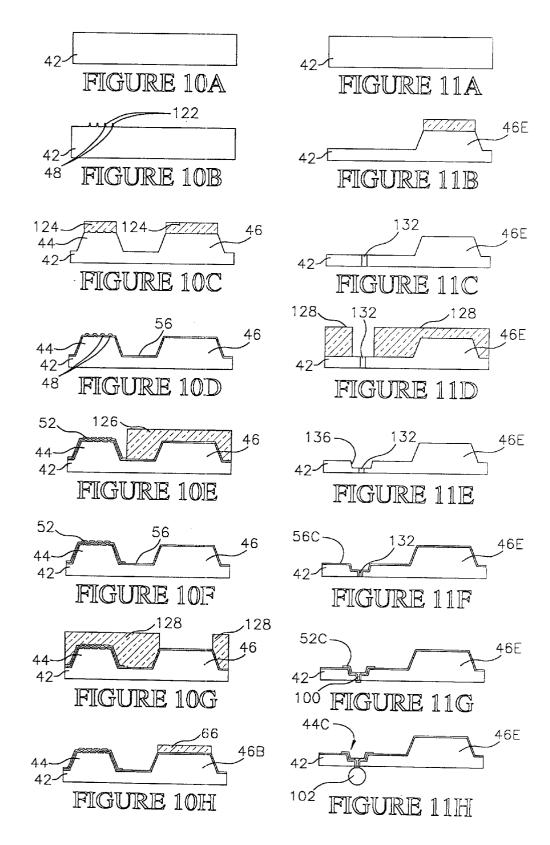

**[0040]** FIGS. **10A-10H** are schematic cross sectional views illustrating process steps in a method for fabricating the interconnect of **FIG. 2**; and

[0041] FIGS. 11A-11H are schematic cross sectional views illustrating process steps in a method for fabricating the interconnect of FIG. 8.

### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0042] Referring to FIGS. 2 and 2A, an interconnect 40 constructed in accordance with the invention is illustrated. The interconnect 40 includes a substrate 42, and a plurality of interconnect contacts 44 formed on the substrate 42. The interconnect contacts 44 are adapted to electrically engage component contacts 28 (FIG. 2A) on the component 14. In FIG. 2, the outline of the component 14 is superimposed on the interconnect 40.

[0043] The interconnect 40 also includes a plurality of support members 46. The support members 46 are adapted to physically engage the component 14 to provide support and prevent flexure of the component 14 during a test procedure. As will be further explained, the interconnect 40 will be mounted to a carrier 50 (FIG. 4) for testing the component 14.

[0044] In the illustrative embodiment the substrate 42 comprises monocrystalline silicon. However, the substrate 42 can also comprise ceramic, germanium, silicon-on-glass, or silicon-on-sapphire. The interconnect contacts 44 and

support members 46 can be formed integrally with the substrate 42 using a fabrication process to be hereinafter described.

[0045] The interconnect contacts 44 are formed in a pattern that matches a pattern of the component contacts 28. In the illustrative embodiment the component contacts 28 are arranged in a pattern along opposed longitudinal edges of the component 14. In addition, as shown in FIG. 2A, the interconnect contacts 44 include penetrating projections 48 adapted to penetrate the component contacts 28 to a limited penetration depth. With the component contacts 28 comprising thin film aluminum bond pads, the penetration depth will be less than about 1  $\mu$ m. The interconnect contacts 28 also include conductive layers 52 in electrical communication with conductors 54 on a surface 58 of the interconnect 40. The conductive layers 52 electrically contact the component contacts 28.

[0046] The substrate 42 includes an insulating layer 56 adapted to electrically insulate the conductive layers 52 and conductors 54 from a bulk of the substrate 42. The insulating layer 56 can also cover the support members 46. The conductors 54 include bonding pads 45 (FIG. 2) adapted to provide bonding sites for wire bonding to the carrier 50 (FIG. 4), or alternately contact sites for engagement by electrical connectors of the carrier 50.

[0047] As shown in FIGS. 2 and 2A, the support members 46 are sized and shaped to physically support edge portions 60 of the component 14. With the component 14 comprising a bare die, the edge portions 60 correspond to the streets, or scribe lines, on the wafer on which the die was fabricated. In the illustrative embodiment there are seven support members 46 on each opposed lateral edge of the component 14. However, a fewer (i.e., 1-6), or greater (i.e., more than 7), number of support members 46 can be used to support the component 14. In addition, one or more support members 46 can be sized and shaped to physically engage end edges of the component 14.

[0048] As shown in FIG. 2A, the component 14 includes a passivation layer 62, such as BPSG, formed on a surface thereof (e.g., face surface). In addition, the support members 46 include planar surfaces 64 adapted to physically touch the passivation layer 62 on the component 14. A height H1 of the support members 46 is selected such that the contacts 44 can electrically engage the component contacts 28, as the support members 46 prevent flexure and bowing of the component 14. Preferably the height H1 of the support members 46 is slightly less than a height H2 of the contacts 44. If an etch process, as hereinafter described, is used to form the support members 46 and the contacts 44, the height H1 will be less than the height H2 by a distance equal to the height of the penetrating projections 48 combined with a thickness of the conductive layer 52. The difference between H1 and H2 will be on the order of one to several microns. A representative height H1 of the support members 46 can be from 50  $\mu$ m to 400  $\mu$ m or greater.

[0049] A spacing S between the component 14 and the surface 58 of the interconnect 40 is approximately equal to the heights H1 and H2. The spacing S helps to clear particles and contaminants that may be present between the component 14 and surface 58 of the interconnect 40. Also, the spacing S helps to eliminate cross talk between the component 14 and interconnect 40.

**[0050]** In the illustrative embodiment, the support members **46** are generally pyramidally shaped pillars formed by anisotropically etching the monocrystalline silicon substrate **42**. In addition, the planar surfaces **64** of the support members **46** have a generally square peripheral configuration with a width W. However, the planar surfaces **64** of the support members **46** can also comprise rectangles, circles or other polygonal shapes. Also, the support members **46** can comprise elongated ridges having a length that is greater than the width W of the support members **46** can be from 50  $\mu$ m to 200  $\mu$ m or greater.

[0051] Referring to FIG. 2B, an alternate embodiment support member 46A is illustrated. In this embodiment the component 14 can be provided with one or more pads 28A. The support members 46A, rather than engaging the passivation layer 62 along the edge portion 60 of the component 14, physically engage the pads 28A on the component 14. The pads 28A can be similar in construction to thin film metal bond pads, but are not electrically connected to the integrated circuits contained on the component 14.

[0052] Referring to FIG. 2C, alternate embodiment support members 46B include an elastomeric layer 66. The elastomeric layer 66 is adapted to provide a compliant surface for physically engaging the passivation layer 62 on the component 14. The elastomeric layer 66 can also move in the Z direction while maintaining support and preventing flexure of the component 14. This Z direction movement can accommodate dimensional variations in the component contacts 28 or the support members 46B. The elastomeric layer 66 can comprise a deposited elastomer such as polyimide or silicone. A representative thickness T of the elastomeric layer 66 can be from 1  $\mu$ m to several  $\mu$ m or more.

[0053] Referring to FIG. 3, an alternate embodiment interconnect 40A is illustrated. In this embodiment the interconnect contacts 44 are formed along a center line of the interconnect 40A to accommodate testing of a component 14A. For example, the component 14A can comprise a leads-over-chip die having component contacts (not shown) formed along a center portion of the die. Alternately an interconnect (not shown) can be configured with interconnect contacts 44 for an end connect die having component contacts (e.g., bond pads) formed along opposed ends.

[0054] Referring to FIG. 4, the test carrier 50 is illustrated. The test carrier 50 includes a base 68 having a plurality of terminal leads 70 and a plurality of internal conductors 72 in electrical communication with the terminal leads 70. The base 68 includes a first recess 74 wherein the interconnect 40 is mounted. The interconnect 40 can be adhesively bonded to a surface of the base 68. Wires 24 can be wire bonded to the bond pads 45 (FIG. 2) on the interconnect 40 and to the internal conductors 72 on the base 68.

[0055] In addition, the base 68 includes a second recess 76 wherein a force applying mechanism 78 is mounted. The force applying mechanism 78 is adapted to bias the component 14 against the interconnect 40. The force applying mechanism 78 includes a lid 80, a pair of clips 82, a spring 84 and a pressure plate 86. The clips 82 removably attach to openings 88 in the base 68. In addition, openings 90A, 90B, 90C are formed in the lid (30, spring 84 and pressure plate 86 to allow access for a vacuum tool for holding the component 14 during assembly of the carrier 50. Also an

opening 92 can be provided in the base 68 to facilitate removal of the interconnect 40.

[0056] The base 68 can comprise plastic molded in a desired shape using an injection molding process. Previously incorporated U.S. Pat. No. 5,519,332 discloses a method for fabricating the base 68 using a process that combines electroless and electrolytic metal plating, photolithographic patterning and wet chemical etching. This fabrication technique for electronic components is sometimes referred to as 3-D fabrication because the molded components can include metal filled vias for interconnecting the circuitry. This permits the internal conductors 72 and terminal leads 70 to be molded integrally with the base 68. Suitable plastics for the base 68 include epoxy novolac resin, silicone, phenylsilane and thermoset plastics. Other suitable plastics for the base 68 include polyetherimide (PRI), polyethersulfone (PES), polyarylsalfone (PAS), polyphenylene sulfide (PPS), liquid crystal polymer (LCP) and polyether ether ketone (PEEK).

[0057] Preferably the carrier 50 has an outline and external lead configuration equivalent to a conventional semiconductor package. The permits standard burn-in boards and test equipment to be used with the carrier 50. In the illustrative embodiment the carrier 50 is in the configuration of a small outline j-bend package (SOJ). Other suitable package configurations include ball grid array (BGA), pin grid array (PGA), land grid array (LGA), zig zag in line (ZIP), dual in line (DIP), and leadless chip carrier (LCC).

[0058] Assembly of the carrier 50 with the component 14 therein can be accomplished by optically, or mechanically aligning the component 14 with the interconnect 16, and then placing the component 14 and interconnect 16 in contact as the force applying mechanism 78 is attached to the base 68. U.S. Pat. No. 5,634,267 to Farnworth et al. entitled "Method And Apparatus For Manufacturing Known Good Semiconductor Die", which is incorporated herein by reference, describes an assembly method and automated assembly apparatus. U.S. Pat. No. 5,739,050 to Farnworth et al. entitled "Method And Apparatus For Assembling A Semiconductor Package For Testing", which is incorporated herein by reference, discloses another method for assembling the carrier 50.

[0059] As shown in FIG. 4, in the assembled carrier 50 the interconnect contacts 26 establish electrical communication between the component 40 and the terminal leads 70 on the base 68. This allows test signals to be transmitted through the terminal leads 70, the internal conductors 72, the wires 45, the conductors 54 (FIG. 2), and the interconnect contacts 26 to the integrated circuits contained on the component 14. Also in the assembled carrier 50, the support members 46 support the component 14 and prevent flexure and bowing of the component 14. The interconnect 40 can also include support members 46B (FIG. 2C) having elastomeric layer 66. Still further, the interconnect 40 can include support members 46A (FIG. 2B) for contacting pads 28A (FIG. 2B) on the component 14.

[0060] Referring to FIG. 5, an alternate embodiment carrier 50A and interconnect 40A are illustrated. The alternate embodiment carrier 50A includes essentially the same components as previously described carrier 50 (FIG. 4). However, in this embodiment the pressure plate 86A is sized and shaped to engage support members 46C formed on the

interconnect **40**A. The support members **46**C thus prevent flexure and bowing of the pressure plate **86**A and component **14**. In this embodiment the support members **46**C can be substantially the same as support members **46** (**FIG. 4**), but in general can be larger and taller than the support members **46**. The support members **46**C can also include elastomeric layers as previously described for support members **46**B (**FIG. 2C**).

[0061] Referring to FIG. 6, an alternate embodiment carrier 50 includes support members 50B formed directly on the base 68 of the carrier 50B. Again, the support members 50B are adapted to physically contact pressure plate 86B of the force applying mechanism 78. In this embodiment the support members 50B can comprise molded pillars formed integrally with the base 68. Alternately, the support member 50B can comprise a single ring shaped member formed of an elastomeric material such as silicone. With a ring shape member the component 14 and interconnect 40B are in effect sealed from contaminants during the test procedure.

**[0062]** Referring to **FIGS. 7 and 7A**, a prior art component 14CSP in the form of a chip scale package is illustrated. The component 14CSP is constructed as described in U.S. Pat. No. 5,674,785 to Akram et al. entitled "Method Of Producing A Single Piece Package For Semiconductor Die", and in U.S. Pat. No. 5,739,585, entitled "Single Piece Package For Semiconductor Die", both of which are incorporated herein by reference.

[0063] The component 14CSP includes a body 94 and a plurality of external ball contacts 96. The ball contacts 96 can comprise metal (e.g., solder) or conductive polymer balls formed on the body 94 in a ball grid array (BGA). The component 14CSP also includes an elongated opening 98 that allows access during fabrication of the package 14CSP to a semiconductor die (not shown) contained within the package 14CSP. As is apparent, the component 14CSP is merely illustrative of chip scale packages. Alternately, other types of components having ball contacts in a dense array can be tested using the interconnect 40C (FIG. 8) and carrier 50C (FIG. 9) to be hereinafter described.

[0064] Referring to FIGS. 8-8D, interconnect 40C which is adapted to electrically engage component 14CSP is illustrated. The interconnect 40C comprises a substrate 42C, a plurality of interconnect contacts 44C formed on the substrate 42C, and a plurality of support members 46E formed on the substrate 42C.

[0065] As shown in FIG. 8A, the support members 46E can include an elastomeric layer 46E. In addition, the support members 46E can be sized and shaped substantially as previously described for support members 46 (FIG. 2A). A method for fabricating the support members 46E using an etching process will be hereinafter described.

[0066] As shown in FIG. 8B, the interconnect contacts 44C are adapted to electrically engage the ball contacts 96 on the component 14CSP. Each interconnect contact 44C comprises an indentation etched or machined in the substrate 42C and covered with a conductive layer 52C. The indentations and conductive layer 52C are sized and shaped to electrically engage the contact ball 96. Also, as shown in FIG. 8C, an interconnect contact 44C-1 can include penetrating projections 48C adapted to penetrate the ball contacts 96.

[0067] Further details of the interconnect contacts 44C and 44C-1, including methods of fabrication are disclosed in U.S. patent application Ser. No. 08/829,193, filed Mar. 3, 1997 entitled "Interconnect Having Recessed Contact Members For Testing Semiconductor Dice And Packages With Contact Bumps", which is incorporated herein by reference.

[0068] As also shown in FIG. 8B, the interconnect contacts 44C are in electrical communication with conductive vias 100 and external ball contacts 102 formed in a ball grid array (BGA). Insulating layers 56C electrically insulate the interconnect contacts 44C and conductive vias 100 from the bulk of the substrate 42C.

[0069] The conductive vias 100 can be fabricated by etching or machining openings in the substrate 42C, insulating the openings, and then filling the openings with a metal or conductive polymer material. A method for fabricating the conductive vias 100 is described in U.S. patent application Ser. No. 08/993,965 filed Dec. 12, 1997, entitled "Semiconductor Interconnect Having Laser Machined Contacts", which is incorporated herein by reference.

[0070] The external ball contacts 102 can be pre-formed metal balls that are attached to a pad portion of the conductive vias by soldering, welding or brazing. Alternately a ball bonding apparatus can be used to attach pre-formed metal balls to form the external ball contacts 102. Preferably the external ball contacts 102 comprise a hard metal able to resist wear and deformation. Suitable hard metals include nickel, copper, beryllium copper, alloys of nickel, alloys of copper, alloys of beryllium copper, nickel-cobalt-iron alloys, and iron-nickel alloys.

[0071] As shown in FIG. 8D, the component 14CSP can be placed on the interconnect 40C with the ball contacts 96 on the component 14CSP electrically engaging the interconnect contacts 44C. In addition, the support members 46E and elastomeric layers 56E physically contact a surface 104 of the component 14CSP, to support and prevent flexure of the component 14CSP during a test procedure, substantially as previously described.

[0072] Referring to FIGS. 9A-9C a carrier 50C constructed with the interconnect 40C is illustrated. The carrier 50C, broadly stated, includes: a base 68C, the interconnect 40C and a force applying mechanism 78C.

[0073] The base 68C comprises a generally rectangularshaped, member formed of melded plastic, or ceramic. The base 68C includes parallel spaced latching grooves 106 formed on either side thereof, for removably attaching the force applying mechanism 78C to the base 68C. In addition, the base 68C includes a recess 108 wherein the component 14CSP can be placed in electrical communication with the interconnect 40C.

[0074] Preferably the interconnect 40C is molded or laminated to the base 68C with the ball contacts 102 exposed to form the external contacts of the carrier 50C. In addition, the interconnect 40C preferably comprises ceramic to provide more strength. With the base 68C comprising molded plastic an injection molding process can be used to mold the interconnect 40C to the base 68C. With the base 68C comprising ceramic, a lamination process can be used to laminate the interconnect 40C to the base 68C. As shown in FIG. 9D, the interconnect 40C and base 68C can include mating stepped surfaces 138 to resist forces exerted on the interconnect 40C by the spring 112. The stepped surfaces 138 on the interconnect 40C can be made using a lamination process.

[0075] The force applying mechanism 78C includes a bridge clamp 110, a spring 112 and a pressure plate 114. The bridge clamp 110 includes latch portions 116 adapted to releasably engage the latching grooves 106 on the base 68C. An assembly tool 118, shown in phantom lines in FIG. 9A, can be used to manipulate the bridge clamp 110, and latch portions 116 thereon to attach the force applying mechanism 78C to the base 68C. In addition, the bridge clamp 110 includes an opening 120A (FIG. 9C) which allows access for a vacuum tool (not shown) for holding and manipulating the component 14CSP during assembly of the carrier 50C. The spring 112 also includes an opening (not shown), and the pressure plate 114 includes an opening 120B (FIG. 9C) for the vacuum tool (not shown). Previously cited U.S. Pat. No. 5,634,267 describes an automated assembly apparatus for assembling the carrier 50C with the component 14CSP therein.

[0076] In the assembled carrier 50C the component 14CSP is biased against the interconnect 40C by the pressure plate 114 and spring 112. With the component 14CSP biased against the interconnect 40C, the ball contacts 96 on the component 14CSP electrically engage the interconnect contacts 44C substantially as shown in FIG. 8D. In addition, the support members 46E on the interconnect 40C physically contact and support the component 14CSP and prevent flexure and bending thereof. Still further, the elastomeric layer 66E (FIG. 8D) cushions the component 14CSP and compensates for Z-direction dimensional variations in the ball contacts 96 on the component 14CSP.

[0077] Referring to FIGS. 10A-10H steps in a method for fabricating the interconnect 40 (FIG. 2) are illustrated. Initially, the substrate 42 can be provided. In the illustrative embodiment the substrate 42 comprises monocrystalline silicon. However, the substrate 42 can also comprise ceramic, germanium, silicon-on-glass, or silicon-on-Micron sapphire. A representative thickness for the substrate 42 can be from 12 mils to 200 mils or greater. The peripheral outline of the substrate 42 can correspond to the peripheral outline of the component 14 (e.g., square rectangular). A representative dimension for each side of the substrate 42 can be from 15 mm to 50 mm or greater.

[0078] Next, as shown in FIG. 10B, a first mask 122 can be formed on the substrate 42 and used to etch the penetrating projections 48. The first mask 122 can comprise resist, or a hard mask such as  $Si_3N_4$ . In addition, a wet etchant, such as KOH, can be used to etch the substrate 42 to form the penetrating projections 48. A representative height of the penetrating projections can be from 0.25  $\mu$ m to 1.0  $\mu$ m.

[0079] Next, as shown in FIG. 10C, a second mask 124 can be formed on the substrate 42 and used to etch the interconnect contacts 44 and the support members 46. The second mask 124 can comprise a hard mask or a resist mask. In addition, a wet etchant such a KOH can be employed to anisotropically etch the substrate 42 to form the contacts 44 and support members 46. The size and shape of the contacts 44 and support members 46 can be as previously described.

[0080] Next, as shown in FIG. 10D, the insulating layers 56 can be formed. The insulating layers 56 can comprise an

electrically insulating material, such as SiO<sub>2</sub>, or Si<sub>3</sub>N<sub>4</sub>, deposited to a desired thickness using CVD, or other deposition process. A SiO<sub>2</sub> layer can also be grown on exposed surfaces of the substrate **42** using an oxidizing atmosphere such as steam and O<sub>2</sub> at an elevated temperature (e.g., 950° C.). The insulating layers **56** can also comprise a polymer, such as polyimide, deposited and planarized using a suitable process (e.g., spin-on-process). Depending on the material, a representative thickness of the insulating layers **56** can be from about a 100 Å to several mils.

[0081] Next, as shown in FIG. 10E, a third mask 126 is formed on the substrate 42 and the conductive layers 52 are deposited on the contacts 44. The conductive layers 52 can comprise a thin film metal deposited to a thickness of several hundred Å or more using a process such as CVD. The conductors 54 (FIG. 2) and bond pads 45 (FIG. 2) can be formed at the same time as the conductive layers 52 or can be formed using a separate metallization process.

[0082] The conductive layers 52 and conductors 54 can comprise a patterned layer of a highly conductive metal such as aluminum, chromium, titanium, nickel, iridium, copper, gold, tungsten, silver, platinum, palladium, tantalum, molybdenum or alloys of these metals. Rather than being a single layer of metal, the conductive layers 52 and conductors 54 can comprise multi-layered stacks of metals (e.g., bonding layer/barrier layer). The bond pads 45 can be formed using a same process as the conductors 54, or can be formed separately. However, the bond pads 45 must be formed of a wire bondable metal such as aluminum or copper.

[0083] The third mask 126 can comprise a thick film resist adapted to cover the support members 46. One suitable thick film resist is sold by Shell Chemical under the trademark "EPON RESIN SU-8". The resist also includes an organic solvent (e.g., gamma-butyloracton), and a photoinitiator. A conventional resist coating apparatus, such as a spin coater, or a meniscus coater, along with a mask or stencil, can be used to deposit the resist in viscous form onto the interconnect 18. The deposited resist can then be hardened by heating to about 95° C. for about 15 minutes or longer.

**[0084]** Following formation of the conductive layers **52**, the third mask **126** can be stripped. A suitable wet etchant for stripping the previously described resist formulation is a solution of PGMEA (propyleneglycol-monomethylether-ac-etate).

[0085] FIG. 10F shows the completed interconnect contacts 44 and support members 16.

[0086] As optional additional steps, which are shown in FIG. 10G and 10H, a fourth mask 128 (FIG. 10G) can be formed and used to deposit the elastomeric layer 66 (FIG. 10H) to form support members 46B. The elastomeric layer 66 can comprise a deposited polymer, such as polyimide, deposited to a thickness of up to several microns or more.

[0087] Referring to FIGS. 11A-11H, steps in a method for fabricating the interconnect 40C (FIG. 8) are illustrated. Initially, as shown in FIG. 11A, the substrate 42C can be provided as previously described. In the illustrative embodiment the substrate comprises silicon. However, the substrate 42C can also comprise ceramic, germanium, silicon-onglass, or silicon-on-sapphire.

[0088] Next, as shown in FIG. 11B, a first mask 130 can be formed and the support member 46E etched as previously described.

[0089] Next, as shown in FIG. 11C, openings 132 can be formed in the substrate 42C for the conductive vias 100. One method for forming the openings 132 is with a laser machining process. A suitable laser machining apparatus is manufactured by General Scanning of Sommerville, Mass. and is designated a model no. 670-W. A representative diameter of the openings 132 can be from 10  $\mu$ m to 2 mils or greater. A representative laser fluence for forming the openings 132 through a substrate 42C comprising silicon and having a thickness of about 28 mils is from 2 to 10 watts/per opening at a pulse duration of 20-25 ns and at a repetition rate of up to several thousand per second. The wavelength of the laser beam can be a standard infrared or green wavelength (e.g., 1064 nm-532 nm).

[0090] Next, as shown in FIGS. 11D and 11E, a second mask 134 can be formed as previously described, and used to etch indentations 136 for the contacts 44C. The indentations 136 can have a diameter that corresponds to that of the ball contacts 96 (FIG. 7) of the component 14CSP. A representative diameter for the indentations 136 can be from 2 mils to 50 mils or greater. At the same time that the indentations 136 are etched the openings 132 can also be etched. This etch step can be performed using potassium hydroxide (KOH), or alternately a solution of tetra-methyl ammonium hydroxide (TMAH).

[0091] Next, as shown in FIG. 11F, the insulating layer 56C can be formed using a deposition or growth process as previously described. The insulating layer 56C can also be formed on the sidewalls of the openings 132.

[0092] Next, as shown in FIG. 11G, the conductive layers 52C can be formed in the indentations substantially as previously described for conductive layers 52 (FIG. 10E). In addition, the openings 132 can be filled with a conductive material to form the conductive vias 100 in electrical communication with the conductive layers 52C. This step is preferably performed prior to formation of the conductive layers 52.

[0093] The conductive material for the conductive vias 100 can comprise a metal, such as solder, aluminum, titanium, nickel, iridium, copper, gold, tungsten, silver, platinum, palladium, tantalum, molybdenum or alloys of these metals. The metal can be deposited within the etched laser openings 132 using a deposition process, such as CVD, electrolytic deposition or electroless deposition. A solder metal can be screen printed in the etched laser openings 132, as well as with capillary action, or with a vacuum system using a hot solder wave.

[0094] Rather than being a metal, the conductive material can comprise a conductive polymer, such as a metal filled silicone, or an isotropic epoxy. Suitable conductive polymers are sold by A.I. Technology, Trenton, N.J.; Sheldahl, Northfield, Minn.; and 3M, St. Paul, Minn. A conductive polymer can be deposited within the etched laser openings 132, as a viscous material, and then cured as required. A suitable deposition process, such as screen printing, or stenciling, can be used to deposit the conductive polymer into the etched laser openings 132.

[0095] Next, as shown in FIG. 11H, the ball contacts 102 can be formed in electrical communication with the conductive vias 100. One method for fabricating the ball contacts 102 is by bonding pre-fabricated metal balls to the

conductive vias **100**. For example, pre-fabricated metal balls are manufactured by Mitsui Comtek Corp. of Saratoga, Calif. under the trademark "SENJU SPARKLE BALLS". The metal balls can be attached to the conductive vias **100** by soldering, laser reflow, brazing, welding, or applying a conductive adhesive.

[0096] A solder ball bumper can also be used to attach the ball contacts 102. A suitable solder ball bumper is manufactured by Pac Tech Packaging Technologies of Falkensee, Germany. The ball contacts 102 can also be attached using a conventional wire bonder apparatus adapted to form a ball bond, and then to sever the attached wire. The ball contacts 102 can also be formed by electrolytic deposition or electroless deposition of a metal to form bumps. A representative diameter for the ball contacts 102 can be from about 4 mils to 50 mils or more. A pitch of the ball contacts 102 can be from about 6 mils to 50 mils or more.

**[0097]** Thus the invention provides an improved interconnect and carrier for testing semiconductor components. Although the invention has been described with reference to certain preferred embodiments, as will be apparent to those skilled in the art, certain changes and modifications can be made without departing from the scope of the invention, as defined by the following claims.

We claim:

1. A test carrier for a semiconductor component comprising:

a base;

- an interconnect on the base comprising a plurality of interconnect contacts configured to electrically engage a plurality of component contacts on the component;

- a force applying mechanism on the base configured to bias the component against the interconnect; and

- a support member on the interconnect, or on the base, configured to physically engage the component to support and prevent flexure of the component.

2. The carrier of claim 1 wherein the interconnect comprises a substrate and the support member comprises a raised member on the substrate having a planar surface for engaging a surface of the component.

**3**. The carrier of claim 1 wherein the interconnect comprises a substrate and the support member comprises a raised member on the substrate having a planar surface with an elastomeric layer thereon.

4. The carrier of claim 1 wherein the component comprises a pad and the support member is configured to engage the pad.

5. The carrier of claim 1 wherein the support member comprises an elastomeric member on the base.

6. The carrier of claim 1 wherein the base comprises plastic and the support member comprises a molded member on the base.

7. A test carrier for a semiconductor component comprising:

a base;

an interconnect on the base, the interconnect comprising a substrate with a plurality of interconnect contacts configured to electrically engage a plurality of component contacts on the component, the interconnect further comprising a support member on the substrate configured to physically engage the component; and a force applying mechanism on the base configured to bias the component against the interconnect as the support member supports and prevents flexure of the component.

**8**. The carrier of claim 7 wherein the substrate comprises silicon and the support member comprises a silicon pillar with a planar surface.

**9**. The carrier of claim 7 wherein the substrate comprises silicon and the support member comprises an etched pillar with a planar surface at least partially covered with an elastomeric layer.

**10**. The carrier of claim 7 wherein the interconnect contacts comprise raised members covered with conductive layers.

11. The carrier of claim 7 wherein the interconnect contacts comprise indentations covered with conductive layers.

**12**. The carrier of claim 7 wherein the interconnect includes a plurality of support members located to engage a surface of the component proximate to edge portions thereof.

**13**. A test carrier for a semiconductor component comprising:

a base comprising a plurality of terminal contacts;

- an interconnect on the base, the interconnect comprising a plurality of interconnect contacts in electrical communication with the terminal contacts and configured to electrically engage a plurality of component contacts on the component, the interconnect further comprising a raised support member having a planar surface with an elastomeric layer thereon configured to physically engage a surface of the component; and

- a force applying mechanism on the base configured to bias the component against the interconnect as the support member supports and prevents flexure of the component.

14. The carrier of claim 13 wherein the component comprises a bare die and the component contacts comprise thin film pads.

**15**. The carrier of claim 13 wherein the component comprises a chip scale package and the component contacts comprise solder balls.

**16**. The carrier of claim 13 wherein the interconnect and support member comprise silicon.

17. The carrier of claim 13 wherein the interconnect includes a plurality of support members located to engage the surface of the component proximate to edge portions thereof.

**18**. The carrier of claim 13 wherein the interconnect includes a plurality of support member located to engage the surface proximate to a periphery of the component.

**19**. A test carrier for a semiconductor component comprising:

a base;

an interconnect on the base, the interconnect comprising a substrate with a plurality of interconnect contacts configured to electrically engage a plurality of component contacts on the component, the interconnect further comprising a support member on the substrate configured to physically engage the component, and a plurality of conductive vias through the substrate in electrical communication with the interconnect contacts;

- a force applying mechanism on the base configured to bias the component against the interconnect as the support member supports and prevents flexure of the component; and

- a plurality of ball contacts formed on the interconnect in electrical communication with the conductive vias, the ball contacts forming terminal contacts for the carrier.

**20**. The carrier of claim 19 wherein the interconnect contacts comprise indentations covered with conductive layers.

**21**. The carrier of claim 19 wherein the base comprises plastic and the interconnect is molded to the base.

**22**. The carrier of claim 19 wherein the base comprises ceramic and the interconnect is laminated to the base.

**23**. An interconnect for testing semiconductor components comprising:

a substrate;

- a plurality of interconnect contacts on the substrate configured to electrically engage a plurality of component contacts on the component; and

- a raised support member on the substrate having a planar surface configured to physically contact and prevent flexure of the component.

**24**. The interconnect of claim 23 wherein the substrate and the support member comprise silicon.

**25**. The interconnect of claim 23 further comprising a plurality of support members located to physically contact a surface of the component proximate to an edge portion thereof.

**26**. The interconnect of claim 23 further comprising an elastomeric layer on the planar surface of the support member.

27. An interconnect for testing semiconductor components comprising:

a substrate;

- a plurality of interconnect contacts on the substrate configured to electrically engage a plurality of component contacts on the component;

- a plurality of raised support members on the substrate formed in a pattern to physically engage a surface of the component proximate to edge portions of the component to prevent flexure of the component as the component is biased against the interconnect.

**28**. The interconnect of claim 27 further comprising a plurality of elastomeric layers on the support members.

**29.** The interconnect of claim 27 wherein the substrate and the support members comprise silicon.

**30**. The interconnect of claim 27 wherein the interconnect contacts comprise indentations in the substrate covered with conductive layers.

**31**. The interconnect of claim 27 wherein the interconnect contacts comprise raised members having penetrating projections covered with conductive layers.

**32**. An interconnect for testing a semiconductor component having bumped contacts comprising:

a substrate;

- a plurality of interconnect contacts on the substrate comprising indentations covered with conductive layers configured to electrically engage the bumped contacts;

- a plurality of conductive vias in the substrate in electrical communication with the conductive layers;

- a plurality of ball contacts on the substrate in electrical communication with the conductive vias; and

- a plurality of support members on the substrate configured to physically engage a surface of the component to prevent flexure as the component and interconnect are biased together.

**33**. The interconnect of claim 32 wherein the component comprises a chip scale package and the bumped contacts comprise solder balls.

**34**. The interconnect of claim 32 wherein the substrate and support members comprise silicon.

**35**. A method for fabricating an interconnect for a semiconductor component comprising:

providing a substrate;

- etching the substrate to form a raised support member on the substrate configured to physically engage a surface of the component to support and prevent flexure of the component during a test procedure; and

- forming a plurality of interconnect contacts on the substrate configured to electrically engage component contacts on the component.

**36**. The method of claim 35 further comprising etching the substrate to form a plurality of raised support members configured to physically engage the surface of the component proximate to edge portions thereof.

**37**. The carrier of claim 35 wherein the interconnect contacts comprise raised members covered with conductive layers.

**38**. The carrier of claim 35 wherein the interconnect contacts comprise indentations covered with conductive layers.

**39**. The carrier of claim 35 wherein the substrate and the support member comprise silicon.

**40**. The carrier of claim 35 further comprising forming an elastomeric layer on the support member.

**41**. A method for fabricating an interconnect for a semiconductor component comprising:

providing a substrate;

etching the substrate to form a plurality of raised support members on the substrate in a pattern configured to physically engage a surface of the component proximate to edge portions thereof to support and prevent flexure of the component during a test procedure;

forming an elastomeric layer on the support members; and

forming a plurality of interconnect contacts on the substrate configured to electrically engage component contacts on the component.

**42**. The method of claim 41 further comprising forming a plurality of conductive vias in the substrate in electrical communication with the interconnect contacts.

**43**. The method of claim 42 further comprising attaching a plurality of ball contacts to the substrate in electrical communication with the ball contacts.

44. The method of claim 43 wherein the ball contacts comprise a metal selected from the group consisting of nickel, copper, beryllium copper, alloys of nickel, alloys of copper, alloys of beryllium copper, nickel-cobalt-iron alloys, and iron-nickel alloys.

**45**. A method for fabricating an interconnect for a semiconductor component comprising:

providing a substrate;

- etching the substrate to form a raised support member on the substrate configured to physically engage a surface of the component to support and prevent flexure of the component during a test procedure;

- forming a plurality of interconnect contacts on the substrate configured to electrically engage component contacts on the component;

laser machining a plurality of vias through the substrate; and

depositing a conductive material in the vias in electrical communication with the interconnect contacts.

**46**. The method of claim 45 further comprising attaching ball contacts to the substrate in electrical communication with the conductive material.

**47**. The method of claim 45 further comprising molding the interconnect to a base of a test carrier configured to package the component for testing.

\* \* \* \* \*