(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) DE 696 30 427 T2 2004.07.29

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 0 762 648 B1

(51) Int Cl.<sup>7</sup>: H03K 3/356

(21) Deutsches Aktenzeichen: 696 30 427.9

(96) Europäisches Aktenzeichen: 96 113 838.5

(96) Europäischer Anmeldetag: 29.08.1996

(97) Erstveröffentlichung durch das EPA: 12.03.1997

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 22.10.2003

(47) Veröffentlichungstag im Patentblatt: 29.07.2004

(30) Unionspriorität:

**22421895      31.08.1995      JP**

(84) Benannte Vertragsstaaten:

**DE, FR, GB, IT**

(73) Patentinhaber:

**Kabushiki Kaisha Toshiba, Kawasaki, Kanagawa,

JP**

(72) Erfinder:

**Shigehara, Hiroshi, Kita-Shimogori, JP; Kinugasa,

Masanori, Yokohama-shi, Kanagawa-ken, JP**

(74) Vertreter:

**HOFFMANN · EITLE, 81925 München**

(54) Bezeichnung: **Bus-Halteschaltung**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingereicht, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

### Hintergrund der Erfindung

[0001] Die vorliegende Erfindung bezieht sich auf eine Bus-Halteschaltung, und genauer auf eine Bus-Halteschaltung, die geeignet verwendet werden kann, wenn eine Ausgangsschaltung, die auf der Grundlage einer Versorgungsspannung betreibbar ist, welche sich von jener der Bus-Halteschaltung unterscheidet, mit einer Busleitung verbunden ist.

[0002] In einer elektronischen Vorrichtung, wie zum Beispiel einem Computer, werden Signale gewöhnlich durch eine gemeinsame Busleitung übertragen.

**Fig. 1** zeigt ein Beispiel, bei welchem eine Vielzahl von Ausgangsschaltungen mit einer Busleitung verbunden sind. Ausführlicher betrachtet sind zwei Ausgangsanschlüsse von zwei Ausgangsschaltungen, wie zwei Versuchszustandspuffer TB1 bzw. TB2 mit einer Busleitung **101** verbunden. Diese zwei Versuchszustandspuffer TB1 und TB2 haben beide eine CMOS-Struktur, welche auf der Grundlage von zwei unterschiedlichen Versorgungsspannungen Vcc1 bzw. Vcc2 betrieben werden.

[0003] Der Versuchszustandspuffer TB1 wird immer dann aktiv, wenn ein Freigabesignal niedrigen Pegels /EN1 eingegeben wird, und gibt auf die Busleitung **101** ein Signal, das einem Datensignal IN1 entspricht. Auf die gleiche Weise wird der Versuchszustandspuffer TB2 immer aktiv, wenn ein Freigabesignal niedrigen Pegels /EN2 eingegeben wird, und gibt der Busleitung **101** ein Signal aus, das einem Datensignal IN2 entspricht. Andererseits, immer wenn die Freigabesignale /EN1 und /EN2 auf einen hohen Pegel wechseln, werden die zwei Versuchszustandspuffer TB1 und TB2 inaktiv, so dass ihre Ausgänge in einen hohen Impedanzzustand wechseln.

[0004] Zusätzlich ist in **Fig. 1** eine Bus-Halteschaltung **102** mit der Busleitung **101** verbunden. Diese Bus-Halteschaltung **102** mit Flip-Flop-Mechanismus kann einen Signalpegel auf der Busleitung **101** auf dem Pegel der Versorgungsspannung Vcc und einer Erdspannung Vss halten. Die Bus-Halteschaltung **102** besteht aus zwei Stufen von in Reihe geschalteten Invertern IN101 und IN102, und ein Ausgangsanschluss des Inverters IN01 und ein Eingangsanschluss des Inverters IN102 sind mit der Busleitung **101** verbunden. Die zwei Inverter IN101 und IN102 werden auf der Grundlage einer Versorgungsspannung Vcc betrieben, die sich von beiden Versorgungsspannungen Vcc1 und Vcc2 unterscheidet, die den zwei Versuchszustandspuffern TB1 und TB2 zugeführt werden.

[0005] Wenn irgend einer der Versuchszustandspuffer TB1 und TB2 der Busleitung **101** ein Signal ausgibt, wechselt das Potential der Busleitung **101** auf den Pegel der logischen [1] oder [0]. Dieser Pegel wird von der Bus-Halteschaltung **102** gehalten. Ferner, nachdem die zwei Versuchszustandspuffer TB1 bzw. TB2 in einen hohen Impedanzzustand gewech-

selt sind, kann der Pegel der Busleitung **101** von dieser Bus-Halteschaltung **102** gehalten bleiben. Dementsprechend, nachdem die zwei Versuchszustandspuffer TB1 und TB2 in einen hohen Impedanzzustand gewechselt sind, ist es möglich eine Fluktuation des Potentialpegels der Busleitung **101** aufgrund von Rauschen oder eines Leckstroms zu verhindern.

[0006] Wie oben beschrieben, da die Bus-Halteschaltung **102** vorgesehen ist, um den logischen Pegel der Busleitung **101** zu halten, wird die Ansteuerleistung der Bus-Halteschaltung **102** niedrig genug bestimmt, um keinen schädlichen Einfluss auf den Betrieb der Versuchszustandspuffer TB1 und TB2 zum Ansteuern der Busleitung **101** auszuüben.

[0007] Im übrigen, wenn die Versuchszustandspuffer als CMOS-Struktur aufgebaut sind, sind ein P-Kanal MOS-Transistor und ein N-Kanal MOS-Transistor in der Ausgangsstufe angeordnet. Als Ergebnis ist eine Drain-Diffusionsschicht vom P-Typ des P-Kanaltransistors mit dem Ausgangsanschluss des Versuchszustandspuffers verbunden, so dass unweigerlich eine parasitäre pn-Übergangsdiode zwischen dem Ausgangsanschluss des Versuchszustandspuffers und einem Rück-Gate des P-Kanaltransistors gebildet wird.

[0008] Hierbei wird angenommen, dass es eine Beziehung gibt zwischen den zwei Versorgungsspannungen Vcc1 und Vcc2, die den zwei Versuchszustandspuffern TB1 bzw. TB2 zugeführt werden, nämlich  $Vcc1 < Vcc2$ . Ferner, in dem Fall, in dem der Versuchszustandspuffer TB2 ein Signal mit einem Pegel gleich der Versorgungsspannung Vcc2 an die Ausgangsleitung **101** ausgibt, wenn die Beziehung  $Vcc1 + Vf < Vcc2$  herrscht, wobei  $Vf$  die inhärente Spannung des parasitären pn-Übergangs ist, der zwischen dem Ausgangsanschluss des Versuchszustandspuffers TB2 und der Drain-Diffusionsschicht des P-Kanaltransistors der Ausgangsstufe gebildet ist, ist die parasitäre Diode in Durchlassrichtung geschaltet. Als Ergebnis fließt ein unnötiger Strom vom Versorgungsspannungsanschluss (Vcc2) zum Versorgungsspannungsanschluss (Vcc1) über die parasitäre Diode.

[0009] Um dieses Problem, welches mit Versuchszustandspuffern einhergeht, zu überwinden, hat die gleiche Anmelderin bereits in der japanischen Patentanmeldung Nr. 6-19432 Schaltungen vorgeschlagen, wie sie in den **Fig. 2** und **3** gezeigt sind. Im Falle der Bus-Halteschaltung existiert jedoch ein ähnliches Problem wie bei den oben erwähnten Versuchszustandspuffern.

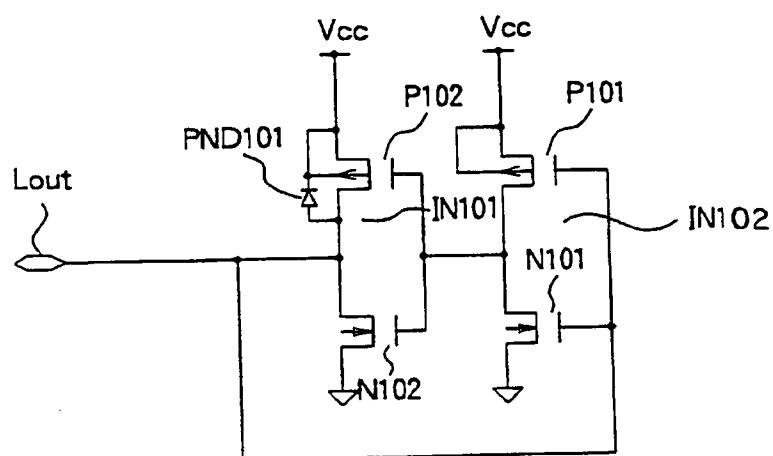

[0010] **Fig. 4** zeigt ein Beispiel von Halteschaltungen des Standes der Technik. In dieser Bus-Halteschaltung des Standes der Technik sind ein Inverter IN102, der aus einer Reihenschaltung eines P-Kanaltransistors P101 und N-Kanaltransistors N101 besteht, und ein weiterer Inverter IN101, der aus einer Reihenschaltung eines P-Kanaltransistors P102 und N-Kanaltransistors N102 besteht, zwischen einer Versorgungsspannung Vcc und einer Erdspannung

Vss parallel zueinander geschaltet. Ferner sind ein Eingangsanschluss des Inverters IN102 und ein Ausgangsanschluss des Inverters IN101 gemeinsam mit einem Ausgangsanschluss Lout verbunden, der mit einer Busleitung **101** verbunden ist.

[0011] Hierbei wird angenommen, dass die Beziehung  $Vcc < Vcc1 < Vcc2$  zwischen den zwei Versorgungsspannungen  $Vcc1$  und  $Vcc2$  herrscht, die den zwei Versuchszustandspuffern TB1 bzw. TB2 zugeführt werden, sowie der der Bus-Halteschaltung zugeführten Versorgungsspannung  $Vcc$ . Ferner, wenn der Pegel der Busleitung **101** gleich einer der Versorgungsspannungen  $Vcc1$  oder  $Vcc2$  wird, herrscht die Beziehung  $Vcc1 + Vf < Vcc1 < Vcc2$ , wobei  $Vf$  das inhärente Potential einer parasitären pn-Übergangsdiode PND101 ist, die zwischen einer Drain-Diffusionschicht und einem Rück-Gate des P-Kanaltransistors P102 des Ausgangsstufen-Inverters IN101 ist, der mit dem Ausgangsanschluss Lout der Bus-Halteschaltung verbunden ist. In diesem Fall ist die parasitäre pn-Übergangsdiode PND101 in Durchlassrichtung geschaltet. Als Ergebnis fließt ein unnötiger Strom vom Ausgangsanschluss Lout bei der Versorgungsspannung  $Vcc1$  oder der Versorgungsspannung  $Vcc2$  zum Versorgungsspannungsanschluss ( $Vcc$ ) über diese parasitäre Diode PND101.

[0012] Wie oben beschrieben, wenn in der Bus-Halteschaltung des Standes der Technik eine Ausgangsschaltung mit der Busleitung verbunden wird, der eine andere Versorgungsspannung zugeführt wird als jene der Bus-Halteschaltung, besteht das Problem, dass ein unnötiger Strom zum Versorgungsspannungsanschluss fließt, aufgrund des Vorliegens einer parasitären Diode, die in der Bus-Halteschaltung gebildet ist.

#### Zusammenfassung der Erfindung

[0013] Dementsprechend ist es Aufgabe der vorliegenden Erfindung eine Bus-Halteschaltung zu schaffen, welche den Fluss eines unnötigen Stroms vom Versorgungsspannungsanschluss zur Bus-Halteschaltung verhindern kann, selbst wenn eine Ausgangsschaltung mit der Busleitung verbunden ist, die mit einer anderen Versorgungsspannung versorgt wird als die Bus-Halteschaltung.

[0014] Diese Aufgabe wird durch Bus-Halteschaltungen gelöst, welche in den unabhängigen Ansprüchen beschrieben werden. Vorteilhafte Ausführungen werden in den abhängigen Ansprüchen beschrieben.

[0015] Eine Ausführung der vorliegenden Erfindung schafft eine Bus-Halteschaltung, die umfasst: einen Eingangsstufen-Inverter, der zwischen einem ersten Versorgungsspannungsanschluss und einem zweiten Versorgungsspannungsanschluss geschaltet ist, und enthält: einen ersten P-Kanaltransistor; und einen ersten N-Kanaltransistor, der in Reihe mit dem ersten P-Kanaltransistor geschaltet ist, wobei ein Gate des ersten P-Kanaltransistors und ein Gate des ersten N-Kanaltransistors gemeinsam mit einer Bus-

leitung verbunden sind; und einen Ausgangsstufen-Inverter, der ebenfalls zwischen dem ersten Versorgungsspannungsanschluss und dem zweiten Versorgungsspannungsanschluss angeschlossen ist, und enthält: einen zweiten P-Kanaltransistor; einen dritten P-Kanaltransistor, der in Reihe mit dem zweiten P-Kanaltransistor geschaltet ist; und einen zweiten N-Kanaltransistor, der in Reihe mit dem dritten P-Kanaltransistor geschaltet ist, wobei ein Gate des zweiten P-Kanaltransistors mit der Busleitung verbunden ist, ein Gate des dritten P-Kanaltransistors und ein Gate des zweiten N-Kanaltransistors gemeinsam mit einem Drain des ersten P-Kanaltransistors und einem Drain des ersten N-Kanaltransistors verbunden sind, ein Drain des dritten P-Kanaltransistors und ein Drain des zweiten N-Kanaltransistors gemeinsam mit der Busleitung verbunden sind, und wobei Rück-Gates der ersten, zweiten und dritten P-Kanaltransistoren alle mit einem Source des dritten P-Kanaltransistors verbunden sind.

[0016] In der Bus-Halteschaltung nach der vorliegenden Erfindung sind in dem Eingangsstufen-Inverter, der mit der Busleitung verbunden ist, und dem Ausgangsstufen-Inverter, der zwischen der Ausgangsseite des Eingangsstufen-Inverters und der Busleitung angeschlossen ist, der zweite und dritte P-Kanaltransistor und der zweite N-Kanaltransistor in Reihe zwischen der ersten Versorgungsspannung und der zweiten Versorgungsspannung geschaltet. Da hierbei die Rück-Gates von zumindest dem zweiten und dritten P-Kanaltransistor mit dem Source des dritten P-Kanaltransistors verbunden sind, ist es möglich den Fluss eines unnötigen Stroms zum ersten Spannungsversorgungsanschluss zu verhindern, selbst wenn ein höheres Potential als die Versorgungsspannung an die Busleitung angelegt wird, da eine Sperrspannung angelegt ist zwischen einer parasitären Diode, die zwischen dem Source und dem Rück-Gate des zweiten P-Kanaltransistors gebildet ist.

[0017] Hierbei ist es vorzuziehen den vierten P-Kanaltransistor mit verbundem Gate und Drain zwischen dem ersten Versorgungsspannungsanschluss und dem dritten P-Kanaltransistor anzuschließen.

[0018] Ferner, wenn der Ausgangsanschluss mit der Ausgangsseite des Eingangsstufen-Inverters verbunden ist, ist es möglich diesen Ausgangsanschluss mit der Eingangsseite einer anderen Schaltung zu verbinden, die mit der Busleitung verbunden ist.

[0019] Ferner ist es in der Bus-Halteschaltung auch vorzuziehen, das Rück-Gate des ersten P-Kanaltransistors mit dem ersten Versorgungsspannungsanschluss zu verbinden.

[0020] Ferner ist es auch vorzuziehen, dass eine Schwellspannung des Eingangsstufen-Inverters kleiner oder gleich einer Schwellspannung einer anderen Schaltung für den Empfang von Signalen aus der Busleitung eingestellt wird. Ferner ist es auch vorzuziehen, dass die zweiten und dritten P-Kanaltransis-

toren in einer Wanne des N-Typs gebildet sind, die sich von einer Wanne des N-Typs zur Bildung eines P-Kanaltransistors, der in einer anderen mit der Busleitung verbundenen Schaltung enthalten ist, unterscheidet. Ferner ist es auch vorzuziehen, dass die ersten, zweiten und dritten P-Kanaltransistoren alle in einer Wanne des N-Typs gebildet sind, die in einer Oberfläche eines Halbleitersubstrats des P-Typs gebildet ist.

#### Kurze Beschreibung der Zeichnungen

- [0021] **Fig. 1** ist ein Blockdiagramm, das eine Busleitung zeigt, mit welcher eine Bus-Halteschaltung und eine Ausgangsschaltung verbunden sind;

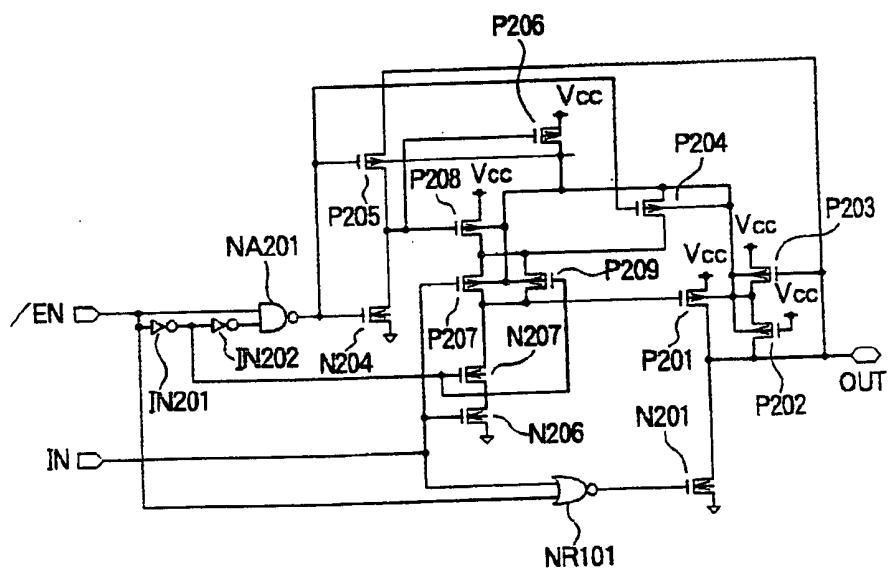

- [0022] **Fig. 2** ist ein Schaltbild, das eine Ausgangsschaltung des Standes der Technik zeigt;

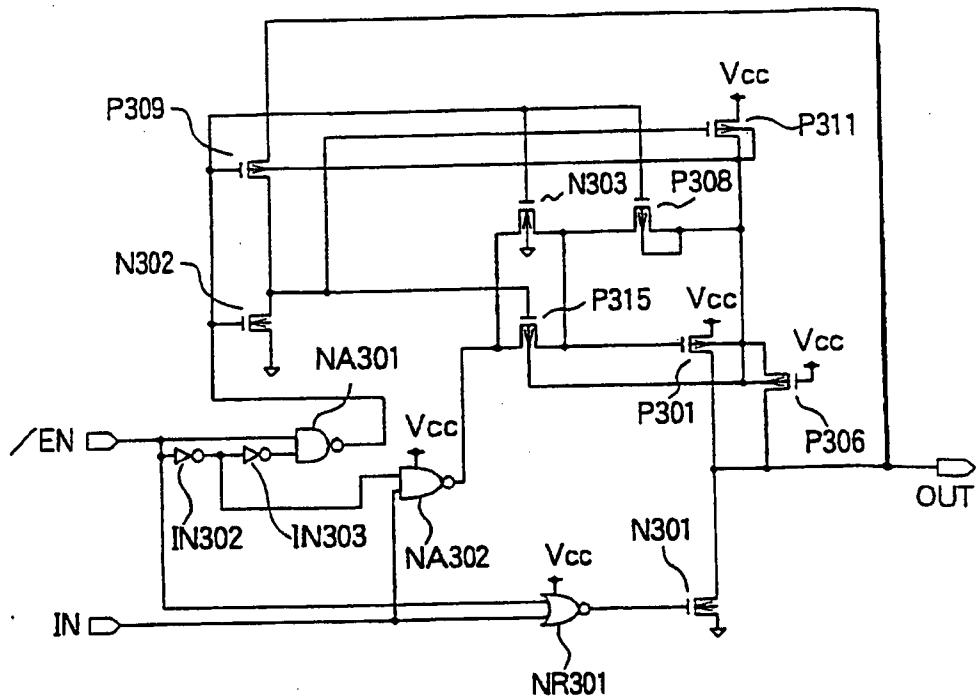

- [0023] **Fig. 3** ist ein Schaltbild, das eine weitere Ausgangsschaltung des Standes der Technik zeigt;

- [0024] **Fig. 4** ist ein Schaltbild, das eine Bus-Halteschaltung des Standes der Technik zeigt;

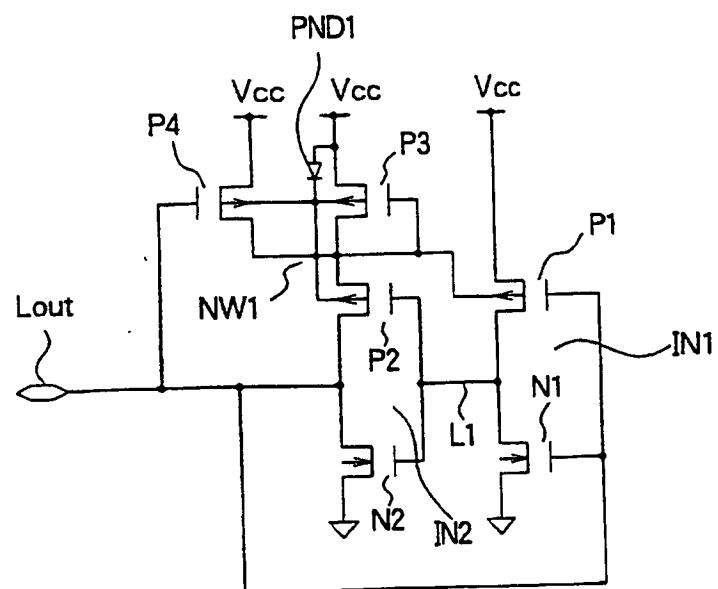

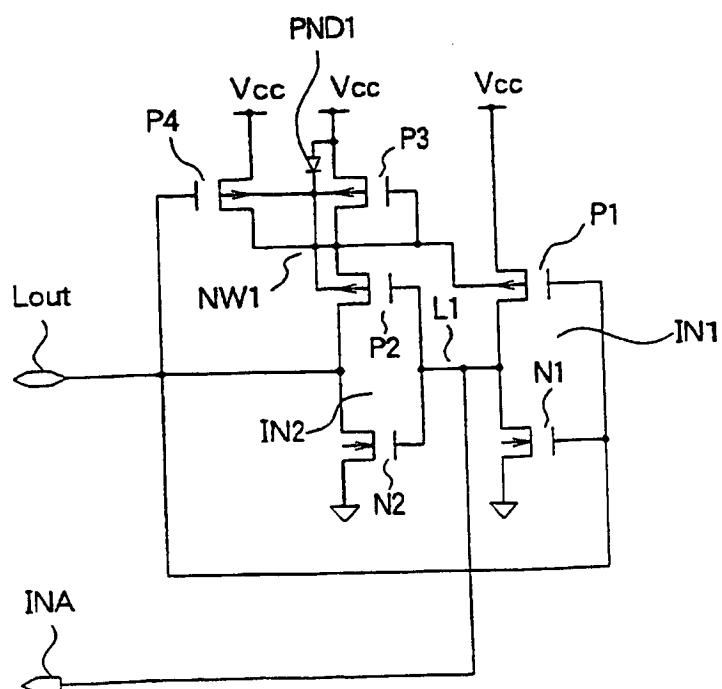

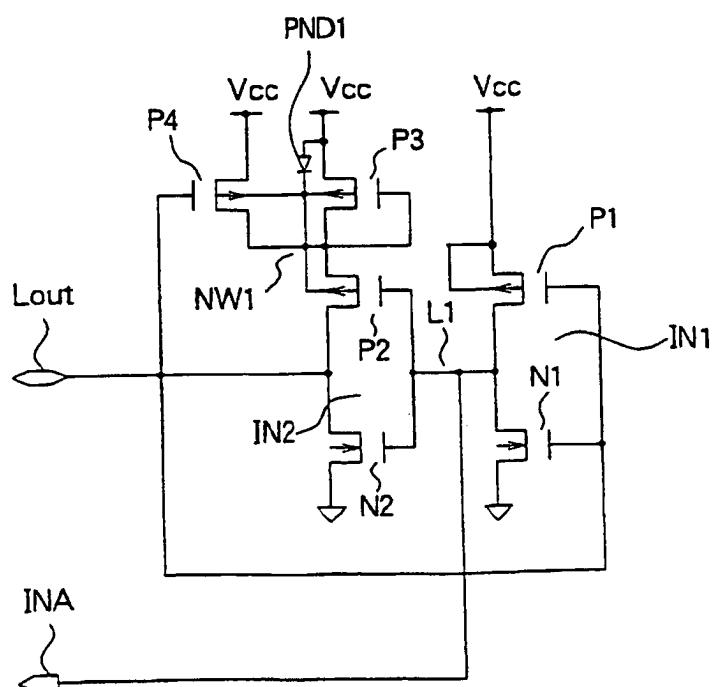

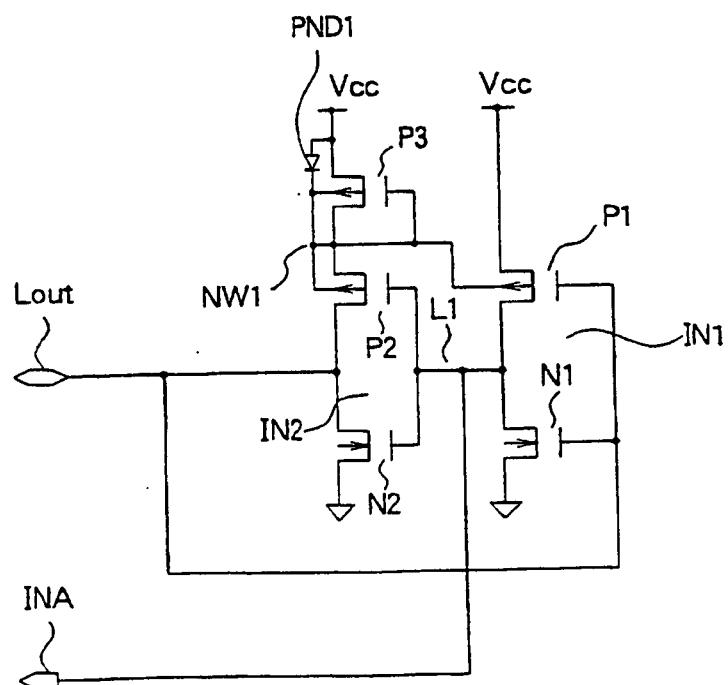

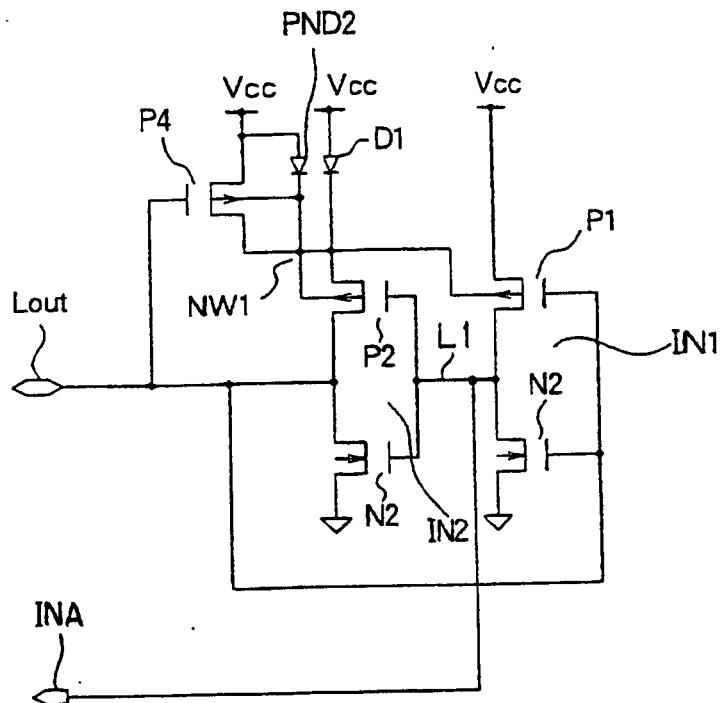

- [0025] **Fig. 5** ist ein Schaltbild, das eine erste Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt;

- [0026] **Fig. 6** ist ein Schaltbild, das eine zweite Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt;

- [0027] **Fig. 7** ist ein Schaltbild, das eine dritte Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt;

- [0028] **Fig. 8** ist ein Schaltbild, das eine vierte Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt;

- [0029] **Fig. 9** ist ein Schaltbild, das eine erste Modifikation der ersten Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt;

- [0030] **Fig. 10** ist ein Schaltbild, das eine erste Modifikation der zweiten Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt;

- [0031] **Fig. 11** ist ein Schaltbild, das eine erste Modifikation der dritten Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt;

- [0032] **Fig. 12** ist ein Schaltbild, das eine erste Modifikation der vierten Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt;

- [0033] **Fig. 13** ist ein Schaltbild, das eine zweite Modifikation der ersten Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt;

- [0034] **Fig. 14** ist ein Schaltbild, das eine zweite Modifikation der zweiten Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt;

- [0035] **Fig. 15** ist ein Schaltbild, das eine zweite Modifikation der dritten Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt;

- [0036] **Fig. 16** ist ein Schaltbild, das eine dritte Modifikation der vierten Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt.

- [0037] **Fig. 17** ist ein Schaltbild, das eine dritte Modifikation der vierten Ausführung (die erste Modifikation) der Bus-Halteschaltung nach der vorliegenden

Erfindung zeigt.

- [0038] **Fig. 18** ist ein Schaltbild, das eine Modifikation der in **Fig. 7** gezeigten Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt; und

- [0039] **Fig. 19** ist ein Schaltbild, das eine Modifikation der in **Fig. 11** gezeigten Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung zeigt.

#### Ausführliche Beschreibung der bevorzugten Ausführungen

[0040] Ausführungen der Bus-Halteschaltung nach der vorliegenden Erfindung werden im folgenden unter Bezugnahme auf die angehängten Zeichnungen beschrieben.

[0041] **Fig. 5** zeigt eine erste Ausführung der Bus-Halteschaltung. In **Fig. 5** ist ein Inverter IN1 zwischen einem Versorgungsspannungsanschluss (Vcc) und einem Erdspannungsanschluss (Vss) angeschlossen. Der Inverter IN1 besteht aus einem P-Kanaltransistor P1 und einem N-Kanaltransistor N1, welche beider zueinander in Reihe geschaltet sind. Ein Eingangsanschluss dieses Inverters IN1 ist mit einem Ausgangsanschluss Lout verbunden, der mit einer Busleitung (nicht abgebildet) verbunden ist. Ferner ist ein Ausgangsanschluss L1 des Inverters IN1 mit einem Eingangsanschluss eines Inverters IN2 verbunden. Der Inverter IN2 besteht aus einem P-Kanaltransistor P2 und einem N-Kanaltransistor N2. Ferner ist ein Ausgangsanschluss des Inverters IN2 mit dem Ausgangsanschluss Lout verbunden.

[0042] Zusätzlich ist ein P-Kanaltransistor P3, der ein mit seinem Drain verbundenes Gate hat, zwischen einem Source des P-Kanaltransistors P2 des Inverters IN2 und dem Versorgungsspannungsanschluss (Vcc) angeschlossen. Ferner ist parallel zu diesem P-Kanaltransistor P3 ein P-Kanaltransistor P4 zwischen dem Versorgungsspannungsanschluss (Vcc) und einem Source des P-Kanaltransistors P2 angeschlossen. Ein Gate des P-Kanaltransistors P4 ist mit dem Ausgangsanschluss Lout verbunden.

[0043] Ferner sind die Rück-Gates der P-Kanaltransistoren P1 bis P4, d. h. eine N-Wanne zur Bildung der Transistoren P1 bis P4, alle mit dem Source des P-Kanaltransistors P2 verbunden. Ferner sind die Rück-Gates der N-Kanaltransistoren N1 und N2 gemeinsam mit der Erdspannung bzw. Massespannung (Vss) verbunden.

[0044] Der Betrieb der ersten Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung wird im folgenden beschrieben.

[0045] (1) Wenn eine Ausgangsschaltung, die mit der mit dem Ausgangsanschluss Lout verbundenen Busleitung verbunden ist, die Erdspannung Vss ausgibt, und danach ein Ausgang der Ausgangsschaltung auf einen Zustand hoher Impedanz wechselt:

[0046] Wenn der Ausgangsanschluss Lout auf der Erdspannung Vss liegt, gibt der Inverter IN1 die Versorgungsspannung Vcc aus, so dass der P-Kanaltransistor P2 des Inverters IN2 ausgeschaltet ist und

der N-Kanaltransistor N2 des Inverters IN2 eingeschaltet ist. Daher wird das Potential des mit dem Ausgangsanschluss des Inverters IN2 verbundenen Ausgangsanschlusses Lout auf der Erdspannung Vss gehalten. Ferner, da die Erdspannung Vss an das Gate des P-Kanaltransistors P4 angelegt wird, ist der Transistor P4 eingeschaltet, so dass die Drains des P-Kanaltransistors P4 und P3 und das Source des P-Kanaltransistors P2 auf die Versorgungsspannung Vcc wechseln. Als Ergebnis gibt es innerhalb der Schaltung keinen Knoten hoher Impedanz.

[0047] (2) Wenn die Ausgangsschaltung, welche mit der mit dem Ausgangsanschluss Lout verbundenen Busleitung verbunden ist, die Versorgungsspannung Vcc1 oder Vcc2, welche höher als die Versorgungsspannung Vcc sind, ausgibt, und danach der Ausgang der Ausgangsschaltung auf einen Zustand hoher Impedanz wechselt:

[0048] Das Potential Vcc1 oder Vcc2 des Ausgangsanschlusses Lout wird dem Inverter IN1 eingegeben, und die Erdspannung Vss wird an den Inverter IN2 ausgegeben. Daher ist der P-Kanaltransistor P2 des Inverters IN2 eingeschaltet, und der N-Kanaltransistor N2 des Inverters IN2 ausgeschaltet. Daher wird das Potential Vcc1 oder Vcc2 des Ausgangsanschlusses Lout an den P-Kanaltransistor P2 übertragen, so dass das Potential des Ausgangsanschlusses des Inverters IN2 sich zu Vcc1 oder Vcc2 ändert. In diesem Fall wird das Potential jedoch vom statischen Standpunkt aus nicht gehalten, wie später beschrieben wird.

[0049] Ferner, da der P-Kanaltransistor P2 eingeschaltet ist, wechselt die Wanne NW1 des N-Typs, die mit dem Source des Transistors P2 verbunden ist, vom dynamischen Standpunkt aus auf das gleiche Potential wie Vcc1 oder Vcc2. Ferner sind beide P-Kanaltransistoren P3 und P4 ausgeschaltet, da ihr Gate bzw. Source auf dem gleichen Potential liegen.

[0050] Ferner existiert eine parasitäre pn-Übergangsdioden PND1 zwischen dem Source des P-Kanaltransistors P3 und der Wanne NW1 des N-Typs. Ferner, da das Potential Vcc1 oder Vcc2 der Wanne NW1 des N-Typs höher ist als das Source-Potential Vcc des P-Kanaltransistors P3, liegt eine Sperrspannung an der Diode PND1 an. Daher, selbst wenn ein höheres Potential als die Versorgungsspannung Vcc an den Ausgangsanschluss Lout angelegt wird, ist es möglich den Fluss eines unnötigen Stroms zum Versorgungsspannungsanschluss (Vcc) zu verhindern.

[0051] (3) Wenn das Potential Vcc1 oder Vcc2 des Ausgangsanschlusses Lout aufgrund eines Leckstroms unter die Versorgungsspannung Vcc abnimmt:

[0052] Hier wird eine Schwellspannung der P-Kanaltransistoren P3 und P4 mit Vtp bezeichnet (ein negativer Wert); ein inhärentes Potential (built-in Potential) des pn-Übergangs der Diode PND1 wird als Vf bezeichnet; und das Potential des Ausgangsanschlusses Vout wird mit Vout bezeichnet. Wenn die folgende Formel (1) zwischen der Versorgungsspan-

nung Vcc und dem Potential Vout herrscht:

$$Vcc - |Vtp| < Vout < Vcc \quad (1)$$

bleibt der P-Kanaltransistor P4 ausgeschaltet, und ferner bleibt auch der P-Kanaltransistor P3 ausgeschaltet.

[0053] In diesem Fall, da das Potential des Ausgangsanschlusses Lout durch die parasitäre pn-Übergangsdioden PND1 auf die Versorgungsspannung Vcc hochgezogen werden kann, kann das Potential Vout des Ausgangsanschlusses Lout durch die folgende Formel (2) ausgedrückt werden:

$$Vout = Vcc - Vf \quad (2)$$

[0054] Hierbei, wenn der Leckstrom zum Versorgungsspannungsanschluss (Vcc) groß ist und dadurch das Potential Vout die Spannung ( $Vcc - |Vtp|$ ) erreicht, werden beide P-Kanaltransistoren P3 und P4 eingeschaltet. Daher kann die Leistung zum Hochziehen des Potentials Vout vergrößert werden. Daher, selbst wenn das Potential Vout aufgrund des Einflusses von Versorgungsspannungsräuschen momentan unter die Spannung ( $Vcc - |Vtp|$ ) absinkt, kann das Potential Vout am Ausgangsanschluss Lout durch die parasitäre pn-Übergangsdioden PND1 und die P-Kanaltransistoren P3 und P4 hochgezogen werden.

[0055] Dementsprechend, da die Ansteuerfähigkeit der Diode PND1 und der P-Kanaltransistoren P3 und P4 auf jeden gewünschten Wert eingestellt werden kann, kann ein geeignet großer Anhebestrom (Pull-Up Strom) erhalten werden, so dass die Beziehung zwischen  $Vcc - |Vtp| < Vout$  verwirklicht werden kann.

[0056] Wie oben beschrieben, kann in dieser ersten Ausführung die Spannung Vout des Ausgangsanschlusses Vout in dem durch die Formel (1) definierten Bereich gehalten werden. Andererseits ist es notwendig, dass das oben beschriebene gehaltene Potential Vout in der mit der Busleitung verbundenen Eingangsschaltung als hoher Pegel erkannt werden kann. Wenn jedoch die Schwellspannung der Eingangsschaltung als Vthc bezeichnet wird, ist es möglich, diese gehaltene Spannung Vout ohne weiteres Problem als hohen Pegel zu erkennen, solange wie diese Schwellspannung Vthc die Beziehung  $Vthc < Vcc - |Vtp|$  erfüllt.

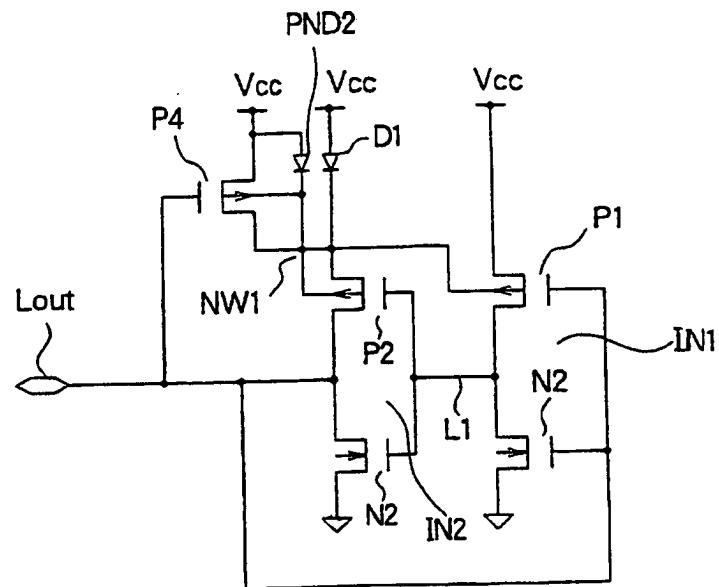

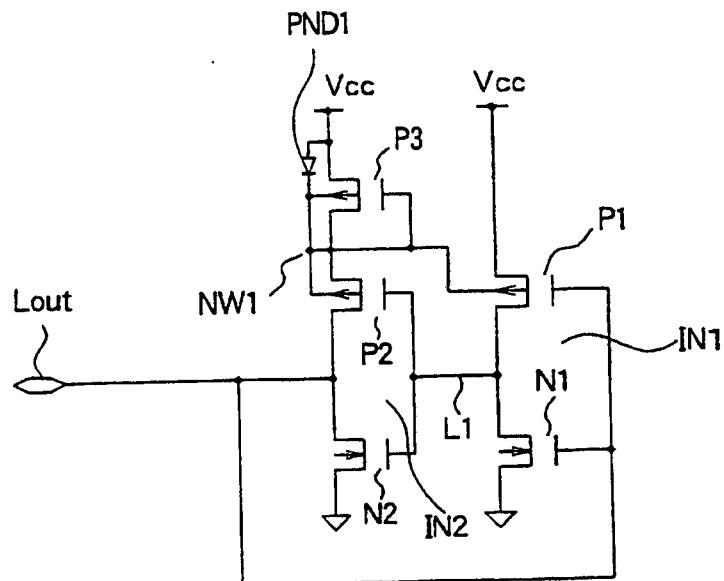

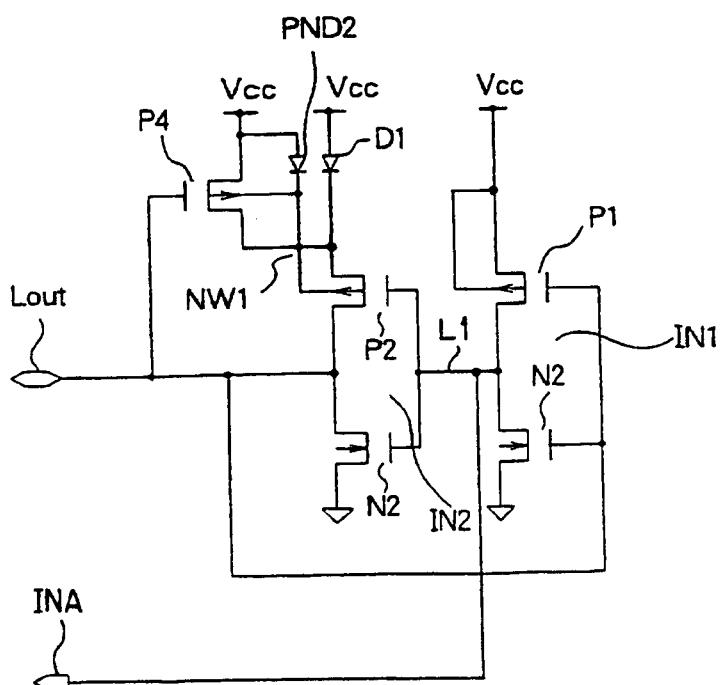

[0057] Eine zweite Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung wird im folgenden unter Bezugnahme auf **Fig. 6** beschrieben. Diese zweite Ausführung unterscheidet sich von der in **Fig. 5** gezeigten Ausführung darin, dass ein Ausgangsknoten L1 des Inverters IN1 als Eingangssignal INA an eine andere Eingangsschaltung (nicht abgebildet) herausgeführt ist, und ferner darin, dass das Rück-Gate des P-Kanaltransistors P1 mit dem Versorgungsspannungsanschluss (Vcc) verbunden ist. Die übrige Konstruktion ist gleich wie im Fall der ers-

ten Ausführung, so dass die zweite Ausführung gleich arbeitet wie im Falle der ersten Ausführung, um das Potential des Ausgangsanschlusses Lout zu halten.

[0058] Ferner ist es ein Merkmal dieser zweiten Ausführung, dass der Inverter IN1 mit der ursprünglichen Funktion als Initialstufen-Inverter der Bus-Halteschaltung ausgestattet ist, und mit der weiteren Funktion als Eingangsstufen-Inverter einer weiteren Eingangsschaltung zum Empfangen des an die Busleitung ausgegebenen Potentials. Dementsprechend können die folgenden Wirkungen erzielt werden:

(1) Das Verhältnis an eingenommener Fläche der Inverter zur gesamten integrierten Schaltung kann verringert werden.

(2) Der Schwellwert der Initialstufe der Bus-Halteschaltung kann perfekt abgeglichen werden mit dem Schwellwert des Inverters der Eingangsschaltung zum Empfangen des an die Busleitung ausgegebenen Potentials. Daher ist es im Vergleich mit dem Fall, bei dem diese Inverter getrennt gebildet sind, zum Beispiel möglich die Toleranz gegenüber Fluktuationen im Signalpegel auf der Busleitung aufgrund von Versorgungsspannungsrauschen zu erhöhen. Ferner, um die Toleranz gegenüber Rauschen zu erhöhen, ist es vorzuziehen den Schwellwert des Initialstufen-Inverters IN1 unter den minimalen Schwellwert der anderen Eingangsschaltung zum Empfangen der Signale auf der Busleitung einzustellen. Ferner, wenn die Inverter getrennt vorgesehen sind, um die Toleranz gegenüber Rauschen zu erhöhen, wie oben in Punkt (2) beschrieben, ist es vorzuziehen, dass eine Ansteuerrate des P-Kanaltransistors P1 und des N-Kanaltransistors N1 des Initialstufen-Inverters IN1 abgeglichen ist mit einer Ansteuerrate der Inverterschaltung (nicht abgebildet) zum Empfangen der Signale auf der Busleitung, die von dieser Bus-Halteschaltung gehalten werden.

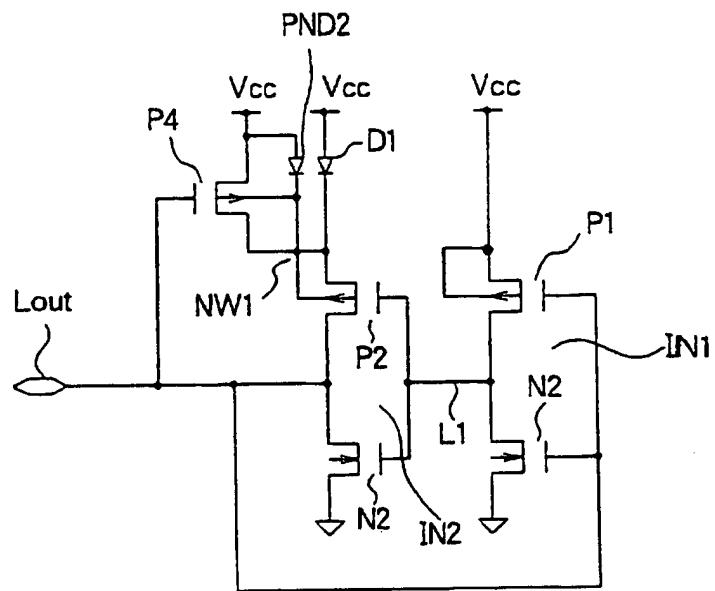

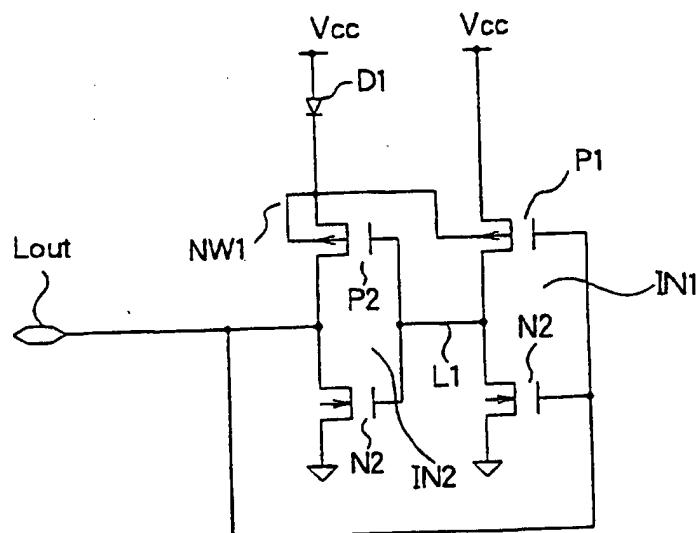

[0059] Eine dritte Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung wird im folgenden unter Bezugnahme auf **Fig. 7** beschrieben. Das Merkmal dieser dritten Ausführung ist, dass eine pn-Übergangsdiode D1 (nicht eine parasitäre Diode) zusätzlich gebildet ist, durch Entfernen des P-Kanaltransistors P3 der in **Fig. 5** gezeigten ersten Ausführung. In **Fig. 7** wurden die gleichen Bezugszeichen für ähnliche Elemente mit den gleichen Funktionen wie im Fall der ersten Ausführung beibehalten, ohne Wiederholung deren ähnlicher Beschreibung.

[0060] In dieser dritten Ausführung, auf die gleiche Weise wie im Fall der ersten und zweiten Ausführung, wenn eine höhere Spannung als die Versorgungsspannung Vcc an den Ausgangsanschluss Lout angelegt wird, ist es möglich das Fließen eines unnötigen Stroms zum Versorgungsspannungsanschluss (Vcc) zu verhindern. Im Vergleich mit der ersten Ausführung, da der P-Kanaltransistor P3 wegge-

lassen wird, obwohl die Fähigkeit zum Hochziehen der Wanne NW1 vom N-Typ relativ niedrig ist, ist es möglich die Wanne NW1 des N-Typs durch den P-Kanaltransistor P4 und eine parasitäre pn-Übergangsdiode hochzuziehen, die zwischen dem Source und dem Rück-Gate dieses P-Kanaltransistors P4 gebildet ist, zusätzlich zur neu hinzugefügten Diode D1.

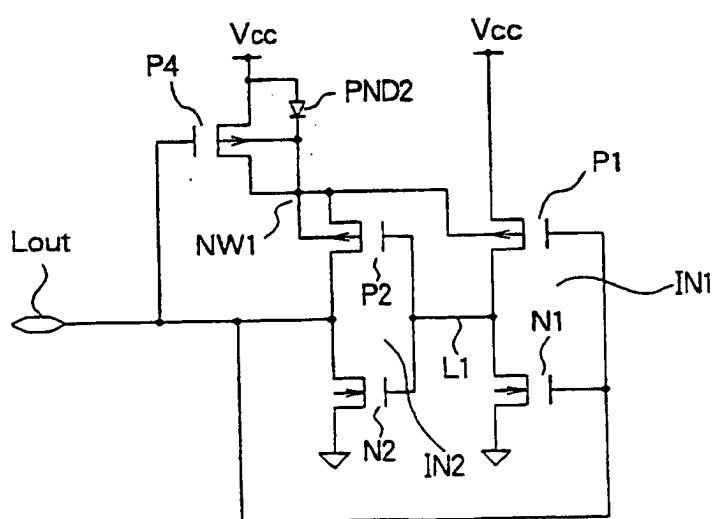

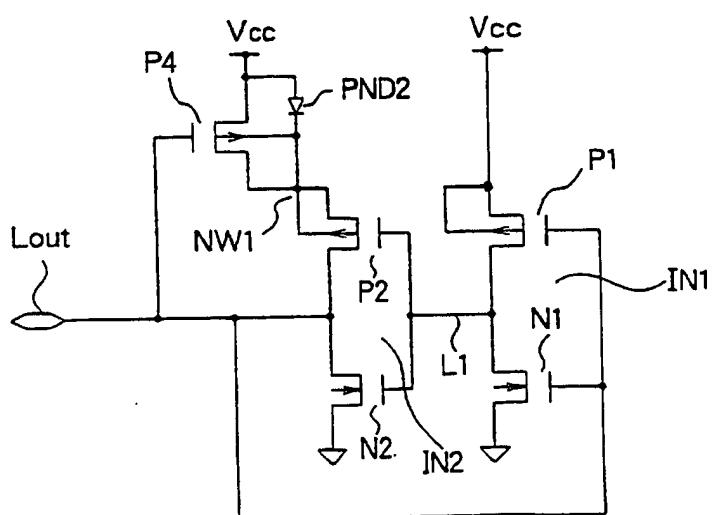

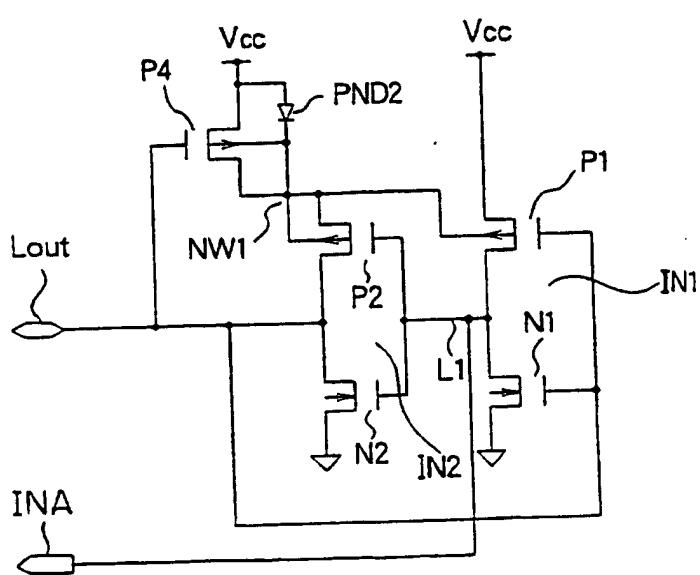

[0061] Eine vierte Ausführung der Bus-Halteschaltung nach der vorliegenden Erfindung wird im folgenden unter Bezugnahme auf **Fig. 8** beschrieben. Diese vierte Ausführung unterscheidet sich von der in **Fig. 5** gezeigten ersten Ausführung darin, dass der P-Kanaltransistor P3 entfernt ist. Die Wanne NW1 vom N-Typ kann von dem P-Kanaltransistor P4 und einem zwischen dem Source und Rück-Gate dieses P-Kanaltransistors P4 gebildeten pn-Übergang hochgezogen werden. Die Ansteuerfähigkeit zum Hochziehen der Wanne NW1 vom N-Typ dieser vierten Ausführung ist relativ niedriger als jene der ersten Ausführung, welche den P-Kanaltransistor P3 enthält, oder der zweiten Ausführung, welche die Diode D1 enthält.

[0062] Die oben beschriebenen Ausführungen wurden nur als Beispiele beschrieben. Dementsprechend ist die vorliegende Erfindung nicht auf die oben erwähnten ersten bis vierten Ausführungen beschränkt.

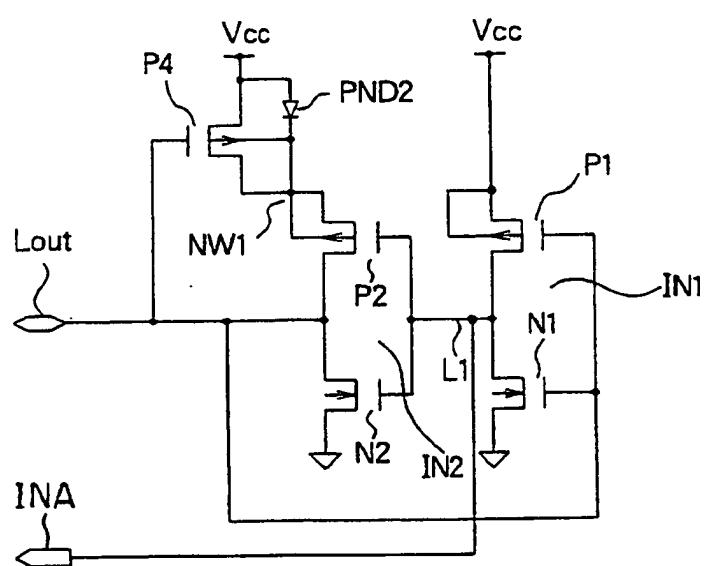

[0063] Zum Beispiel wird im Folgenden eine erste Modifikation beschrieben. In den ersten bis vierten Ausführungen, die in den **Fig. 5** bis **8** gezeigt sind, kann das Rück-Gate des P-Kanaltransistors P1 mit dem Versorgungsspannungsanschluss (Vcc) verbunden werden, wie in den **Fig. 9** bis **12** gezeigt, anstelle der Verbindung mit der Wanne NW1 vom N-Typ. In diesem Fall ist es jedoch notwendig, eine Wanne des N-Typs zur Bildung des P-Kanaltransistors P1 von einer Wanne des N-Typs zur Bildung der P-Kanaltransistoren P2 bis P4 elektrisch zu isolieren, auf solche Weise, dass das Rück-Gate-Potential des P-Kanaltransistors P1 sich vom Rück-Gate-Potential der P-Kanaltransistoren P2 bis P4 unterscheidet. Daher, da in dieser ersten Modifikation nicht alle P-Kanaltransistoren in der gleichen Wanne vom N-Typ gebildet werden können, nimmt die durch die Bus-Halteschaltung dieser ersten Modifikation eingenommene Fläche im Vergleich mit den ersten bis vierten Ausführungen zu.

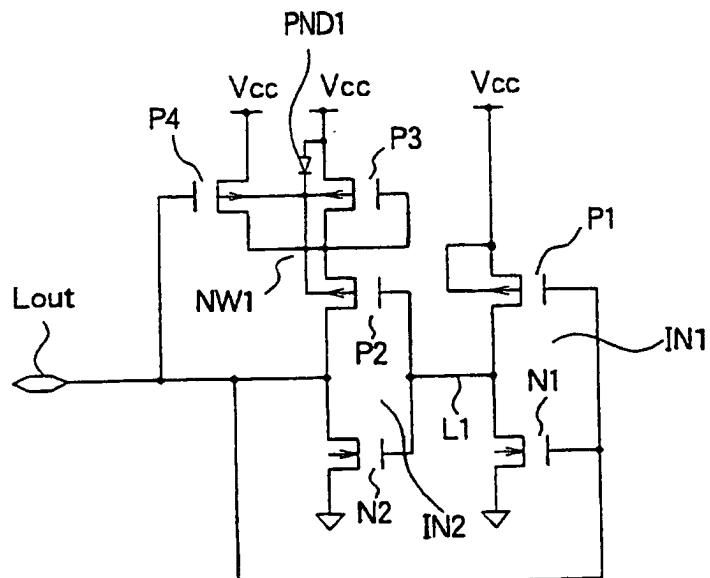

[0064] Nun wird eine zweite Modifikation beschrieben. In den in den **Fig. 5** bis **7** beschriebenen ersten bis dritten Ausführungen kann der P-Kanaltransistor P4 entfernt werden, wie in den **Fig. 13** bis **15** gezeigt. Da jedoch der P-Kanal-Transistor P4 sich vom P-Kanaltransistor P3 unterscheidet, da das Potential des Ausgangsanschlusses Lout direkt seinem Gate eingegeben wird, ist die Empfindlichkeit des P-Kanaltransistors P4 gegenüber einer Potentialänderung am Anschluss Lout hoch. Daher, um das Ansprechen auf eine Potentialänderung am Ausgangsanschluss Lout zu erhöhen, wird vorgezogen, den P-Kanaltran-

sistor P4 für die Bus-Halteschaltung vorzusehen.

[0065] Nun wird eine dritte Modifikation im Folgenden beschrieben. In der in **Fig. 7** gezeigten dritten Ausführung, der in **Fig. 1** gezeigten vierten Ausführung, der in **Fig. 11** gezeigten Modifikation der dritten Ausführung und der in **Fig. 12** gezeigten Modifikation der vierten Ausführung ist es möglich, einen Knoten L1 der Bus-Halteschaltung herauszuführen, und ferner das Potential an diesem Knoten L1 als Eingangssignal INA für eine weitere Eingangsschaltung (nicht abgebildet) zu verwenden, wie in den **Fig. 16, 17, 18** und **19** gezeigt.

[0066] Im übrigen ist es vorzuziehen, dass das Rück-Gate des P-Kanaltransistors (z. B. P-Kanaltransistor P201, der in **Fig. 2** gezeigt ist, oder P-Kanaltransistor P301, der in **Fig. 3** gezeigt ist) des Puffers, der mit der Busleitung verbunden ist, in einer Wanne des N-Typs gebildet ist, die sich unterscheidet von einer Wanne des N-Typs zur Bildung der P-Kanaltransistoren der vorliegenden Erfindung, damit das Rück-Gate-Potential des mit der Busleitung verbundenen Puffers nicht abgeglichen ist mit dem Rück-Gate-Potential des P-Kanaltransistors der erfindungsgemäßen Bus-Halteschaltung. Der Grund ist der folgende: Während des Prozesses, dass das Busleitungspotential durch die Ausgangsschaltung vom Erdpotential Vss auf das Versorgungsspannungspotential Vcc zunimmt, wenn das in **Fig. 5** gezeigte Potential des Ausgangsanschlusses Lout beginnt auf das Versorgungspotential Vcc anzusteigen, und ferner der Ausgangsknoten L1 des Initialstufen-Inverters beginnt auf das Erdpotential Vss herabzufallen, wird der P-Kanaltransistor P2 eingeschaltet und der N-Kanaltransistor N2 ausgeschaltet. Als Ergebnis wird das Potential am Ausgangsanschluss Lout über das Source des P-Kanaltransistors P2 an die Wanne NW1 des N-Typs übertragen, so dass ein Phänomen auftritt, bei dem das Potential der Wanne NW1 des N-Typs (bei einem Potential nahe Vcc – Vf) augenblicklich heruntergezogen wird.

[0067] In diesem Fall, im Fall bei dem der P-Kanaltransistor (z.B. der in **Fig. 2** gezeigte P-Kanaltransistor P201 oder der in **Fig. 3** gezeigte P-Kanaltransistor P301) der Ausgangsstufe der anderen Ausgangsschaltung, welche nicht die Busleitung ansteuert, auf der gleichen Wanne des N-Typs zur Bildung der P-Kanaltransistoren der vorliegenden Erfindung gebildet ist, wird das Rück-Gate-Potential des P-Kanaltransistors der Ausgangsstufe der anderen Ausgangsschaltung auch gleichzeitig heruntergezogen. Als Ergebnis wird der P-Kanaltransistor der Ausgangsstufe der anderen Ausgangsschaltung, die ursprünglich deaktiviert war, eingeschaltet, so dass ein solches Problem existiert, dass ein unnötiger Strom über diesen eingeschalteten P-Kanaltransistor zum Versorgungsspannungsanschluss fließt. Dementsprechend ist es vorzuziehen, den P-Kanaltransistor der Ausgangsstufe der anderen Ausgangsschaltung in einer Wanne des N-Typs zu bilden, die elektrisch getrennt ist von der Wanne des N-Typs zur Bildung

der P-Kanaltransistoren der Bus-Halteschaltung der vorliegenden Erfindung, auf solche Weise, dass das Rück-Gate des P-Kanaltransistors der Ausgangsstufe der anderen Ausgangsschaltung sich im Potential unterscheidet von dem Rück-Gate der P-Kanaltransistoren der Bus-Halteschaltung der vorliegenden Erfindung.

[0068] Ferner können in der Bus-Halteschaltung der vorliegenden Erfindung die P-Kanaltransistoren der Bus-Halteschaltung auf der Oberfläche einer Wanne des N-Typs gebildet sein, die auf der Oberfläche des Halbleitersubstrats vom P-Typ gebildet ist. Ferner können die P-Kanaltransistoren der Bus-Halteschaltung auf solche Weise gebildet sein, dass eine tiefe Wanne vom P-Typ zunächst in einem Halbleitersubstrat vom N-Typ gebildet wird, eine Wanne des N-Typs in der tiefen Wanne des P-Typs gebildet wird, und die P-Kanaltransistoren in der in der tiefen Wanne vom P-Typ gebildeten Wanne vom N-Typ gebildet werden, in dieser Reihenfolge.

### Patentansprüche

1. Bus-Halteschaltung, umfassend:

einen Eingangsstufen-Inverter, der zwischen einem ersten Versorgungsspannungsanschluss und einem zweiten Versorgungsspannungsanschluss geschaltet ist, wobei der Eingangsstufen-Inverter enthält:

einen ersten P-Kanaltransistor; und

einen ersten N-Kanaltransistor, der in Reihe mit dem ersten P-Kanaltransistor geschaltet ist, wobei ein Gate des ersten P-Kanaltransistors und ein Gate des ersten N-Kanaltransistors gemeinsam mit einer Busleitung verbunden sind; und

einen Ausgangsstufen-Inverter, der ebenfalls zwischen dem ersten Versorgungsspannungsanschluss und dem zweiten Versorgungsspannungsanschluss angeschlossen ist, wobei der Ausgangsstufen-Inverter enthält:

einen zweiten P-Kanaltransistor;

einen dritten P-Kanaltransistor, der in Reihe mit dem zweiten P-Kanaltransistor geschaltet ist, und einen zweiten N-Kanaltransistor, der in Reihe mit dem dritten P-Kanaltransistor geschaltet ist, wobei ein Gate des dritten P-Kanaltransistors und ein Gate des zweiten N-Kanaltransistors gemeinsam mit einem Drain des ersten P-Kanaltransistors und einem Drain des ersten N-Kanaltransistors verbunden sind, wobei ein Drain des dritten P-Kanaltransistors und ein Drain des zweiten N-Kanaltransistors gemeinsam mit der Busleitung verbunden sind, und

wobei Rück-Gates des zweiten und dritten P-Kanaltransistors alle mit einem Source des dritten P-Kanaltransistors verbunden sind.

2. Bus-Halteschaltung nach Anspruch 1, wobei ein Gate des zweiten P-Kanaltransistors mit der Busleitung verbunden ist.

3. Bus-Halteschaltung nach Anspruch 1, wobei

ein Gate des zweiten P-Kanaltransistors mit einem Source des dritten P-Kanaltransistors verbunden ist.

4. Bus-Halteschaltung nach Anspruch 1, wobei Rück-Gates des ersten, zweiten und dritten P-Kanaltransistors mit einem Source des dritten P-Kanaltransistors verbunden sind.

5. Bus-Halteschaltung nach Anspruch 1, wobei ein Rück-Gate des ersten P-Kanaltransistors mit dem ersten Versorgungsspannungsanschluss verbunden ist.

6. Bus-Halteschaltung nach Anspruch 1, wobei die Bus-Halteschaltung ferner einen Ausgangsanschluss umfasst, der mit den Drains des ersten P-Kanaltransistors und des ersten N-Kanaltransistors verbunden ist.

7. Bus-Halteschaltung nach Anspruch 1, wobei eine Schwellspannung des Eingangsstufen-Inverters kleiner oder gleich einer Schwellspannung einer anderen Schaltung für den Empfang von Signalen von der Busleitung eingestellt ist.

8. Bus-Halteschaltung nach Anspruch 1, wobei der zweite und dritte P-Kanaltransistor in einer N-Typwanne gebildet sind, die sich von einer N-Typwanne zur Bildung eines P-Kanaltransistors, der in einer anderen mit der Busleitung verbundenen Schaltung enthalten ist, unterscheidet.

9. Bus-Halteschaltung, umfassend:

einen Eingangsstufen-Inverter, der zwischen einem ersten Versorgungsspannungs-Anschluss und einem zweiten Versorgungs-Anschluss angeschlossen ist, wobei der Eingangsstufen-Inverter enthält:

einen ersten P-Kanaltransistor; und

einen ersten N-Kanaltransistor, der in Reihe mit dem ersten P-Kanaltransistor geschaltet ist, wobei ein Gate des ersten P-Kanaltransistors und ein Gate des ersten N-Kanaltransistors gemeinsam mit einer Busleitung verbunden sind; und

einen Ausgangsstufen-Inverter, der ebenfalls zwischen dem ersten Versorgungsspannungsanschluss und dem zweiten Versorgungsanschluss angeschlossen ist, wobei der Ausgangsstufen-Inverter enthält:

eine Diode;

einen zweiten P-Kanaltransistor, der in Reihe mit der Diode geschaltet ist; und

einen zweiten N-Kanaltransistor der in Reihe mit dem zweiten P-Kanaltransistor geschaltet ist, wobei ein Gate des zweiten P-Kanaltransistors und ein Gate des zweiten N-Kanaltransistors gemeinsam mit einem Drain des ersten P-Kanaltransistors und einem Drain des ersten N-Kanaltransistors verbunden sind, und ein Drain des zweiten P-Kanaltransistors und ein Drain des zweiten N-Kanaltransistors gemeinsam mit der Busleitung verbunden sind, und

wobei Rück-Gates des ersten und zweiten P-Kanaltransistors alle mit einem Source des zweiten P-Kanaltransistors verbunden sind, und eine Anode der Diode mit dem ersten Versorgungsspannungs-Anschluss verbunden ist, und eine Kathode der Diode mit einem Source des zweiten P-Kanaltransistors verbunden ist.

10. Bus-Halteschaltung nach Anspruch 9, wobei ein Rück-Gate des ersten P-Kanaltransistors mit dem ersten Versorgungsspannungs-Anschluss verbunden ist.

11. Bus-Haltesschaltung nach Anspruch 9, wobei die Bus-Halteschaltung ferner einen Ausgangsanschluss umfasst, der mit den Drains des ersten P-Kanaltransistors und des ersten N-Kanaltransistors verbunden ist.

12. Bus-Halteschaltung nach Anspruch 9, wobei eine Schwellspannung des Eingangsstufen-Inverters kleiner oder gleich einer Schwellspannung einer anderen Schaltung zum Empfangen von Signalen von der Busleitung eingestellt ist.

Es folgen 10 Blatt Zeichnungen

## Anhängende Zeichnungen

FIG. I

## **F I G. 2 Stand der Technik**

**F I G. 3** Stand der Technik

**F I G. 4** Stand der Technik

**F I G. 5**

**F I G. 6**

FIG. 7

FIG. 8

**F I G. 9**

**F I G. 10**

FIG. 11

FIG. 12

FIG. 13

FIG. 14

FIG. 15

FIG. 16

FIG. 17

**F I G. 18**

**F I G. 19**