(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6738262号

(P6738262)

(45) 発行日 令和2年8月12日(2020.8.12)

(24) 登録日 令和2年7月21日(2020.7.21)

(51) Int.Cl.

G06F 9/445 (2018.01)

F 1

G06F 9/445 130

請求項の数 20 (全 18 頁)

|                    |                               |           |                                                                                                                                                          |

|--------------------|-------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号          | 特願2016-229897 (P2016-229897)  | (73) 特許権者 | 390019839<br>三星電子株式会社<br>Samsung Electronics Co., Ltd.<br>大韓民国京畿道水原市靈通区三星路129<br>129, Samsung-ro, Yeongtong-gu, Suwon-si, Gyeonggi-do, Republic of Korea |

| (22) 出願日           | 平成28年11月28日 (2016.11.28)      |           |                                                                                                                                                          |

| (65) 公開番号          | 特開2017-102923 (P2017-102923A) |           |                                                                                                                                                          |

| (43) 公開日           | 平成29年6月8日 (2017.6.8)          |           |                                                                                                                                                          |

| 審査請求日              | 令和1年10月17日 (2019.10.17)       |           |                                                                                                                                                          |

| (31) 優先権主張番号       | 62/261306                     | (74) 代理人  | 110000051<br>特許業務法人共生国際特許事務所                                                                                                                             |

| (32) 優先日           | 平成27年11月30日 (2015.11.30)      | (72) 発明者  | ズン, 宏忠<br>アメリカ合衆国 94087 カリフォルニア州 サニーベール パーキントン アベニュー 1295                                                                                                |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |           |                                                                                                                                                          |

| (31) 優先権主張番号       | 15/086010                     |           |                                                                                                                                                          |

| (32) 優先日           | 平成28年3月30日 (2016.3.30)        |           |                                                                                                                                                          |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |           |                                                                                                                                                          |

| 早期審査対象出願           |                               |           |                                                                                                                                                          |

最終頁に続く

(54) 【発明の名称】 加速器コントローラ及びその加速器ロジックローディング方法

## (57) 【特許請求の範囲】

## 【請求項 1】

仮想マシン (Virtual Machine) 又はアプリケーションのランタイム (Runtime) 特徴を検出し、前記検出されたランタイム特徴に対応する前記アプリケーション又は前記仮想マシンと関連した加速器ロジックを特定 (identify) する検出器と、

前記特定された加速器ロジックを少なくとも 1 つのDRAM (Dynamic Random Access Memory) のアレイ (Array) にロード (Load) するローダーと、を含み、

前記少なくとも 1 つのDRAM の前記アレイは、前記特定された加速器ロジックに基づいて LUT (Look-up Table) として動作するか、又は、DRAM メモリアレイとして動作するか、選択的に再構成可能であることを特徴とする加速器コントローラ。

## 【請求項 2】

前記少なくとも 1 つのDRAM をさらに含むことを特徴とする請求項 1 に記載の加速器コントローラ。

## 【請求項 3】

前記少なくとも 1 つのDRAM の前記アレイは、オペレーティングシステム環境のキャッシュ貫性 (Cache-coherent) アドレス空間内にあることを特徴とする請求項 1 に記載の加速器コントローラ。

10

20

**【請求項 4】**

前記ランタイム特徴は、前記アプリケーション又は前記仮想マシンの予め定義された ID (Identification) に基づくことを特徴とする請求項 1 に記載の加速器コントローラ。

**【請求項 5】**

前記ランタイム特徴は、機能活用度 (Function Utilization)、中央処理 (Central Processing) 活用度、メモリ活用度、そして前記アプリケーション又は前記仮想マシンと関連されたレイテンシ (Latency) の中の少なくとも 1 つに基づくことを特徴とする請求項 1 に記載の加速器コントローラ。

**【請求項 6】**

前記加速器ロジックは、前記 LUT (Look-Up Table) を含むことを特徴とする請求項 1 に記載の加速器コントローラ。 10

**【請求項 7】**

前記少なくとも 1 つのDRAMの前記アレイは、DIMM (Dual In-line Memory Module) の一部であることを特徴とする請求項 1 に記載の加速器コントローラ。

**【請求項 8】**

前記DIMMは、前記LUT又は前記DRAMメモリアレイのように動作するように選択的に再構成可能ではない少なくとも 1 つのDRAMのアレイをさらに含むことを特徴とする請求項 7 に記載の加速器コントローラ。 20

**【請求項 9】**

前記特定された加速器ロジックは、ロード (Load) 及び格納コマンドを使用して前記少なくとも 1 つのDRAMの前記アレイ内にロード (Load) されることを特徴とする請求項 1 に記載の加速器コントローラ。

**【請求項 10】**

アプリケーション又は仮想マシンのランタイム特徴を検出する検出器と、前記検出されたランタイム特徴に対応する加速器ロジックを少なくとも 1 つのDRAMのアレイ (Array) にロード (Load) するローダーと、を含み、

前記ランタイム特徴は、前記アプリケーション又は前記仮想マシンの予め定義された ID (Identification)、機能活用度、中央処理活用度、メモリ活用度、そして前記アプリケーション又は前記仮想マシンと関連したレイテンシの中の少なくとも 1 つに基づき、

前記少なくとも 1 つのDRAMの前記アレイは、前記加速器ロジックに基づいて、LUT (Look-Up Table) として動作するか、DRAMメモリアレイとして動作するか、選択的に再構成可能であることを特徴とする加速器コントローラ。

**【請求項 11】**

前記検出器は、前記検出されたランタイム特徴に対応する前記アプリケーション又は前記仮想マシンと関連された前記加速器ロジックを特定することを特徴とする請求項 10 に記載の加速器コントローラ。

**【請求項 12】**

前記少なくとも 1 つのDRAMの前記アレイは、オペレーティングシステム環境のキャッシュ貫性アドレス空間内にあることを特徴とする請求項 10 に記載の加速器コントローラ。 40

**【請求項 13】**

前記加速器ロジックは、前記LUT (Look-Up Table) を含むことを特徴とする請求項 10 に記載の加速器コントローラ。

**【請求項 14】**

前記少なくとも 1 つのDRAMの前記アレイは、DIMM (Dual In-line Memory Module) の一部であることを特徴とする請求項 10 に記載の加速器コントローラ。 50

**【請求項 15】**

前記D I M Mは、L U T又はD R A Mメモリのアレイのように動作するように選択的に再構成可能ではない少なくとも1つのD R A Mのアレイをさらに含むことを特徴とする請求項14に記載の加速器コントローラ。

**【請求項 16】**

加速器コントローラは検出器とローダーを含み、

前記検出器が、O S環境内において実行されるアプリケーション又は仮想マシンのランタイム特徴を検出する段階と、

前記検出器が、前記検出されたランタイム特徴に対応する加速器ロジックを特定する段階と、

ローダーが、ロード(L o a d)及び格納コマンドを使用して前記特定された加速器ロジックを少なくとも1つのD R A Mのサブアレイ( S u b - a r r a y )内にロード(L o a d)する段階と、を含み、

前記少なくとも1つのD R A Mの前記サブアレイは、選択的にL U T( L o o k - U p T a b l e )として動作するか、D R A Mメモリアレイとして動作するか、選択的に再構成可能であることを特徴とする加速器ロジックローディング方法。

**【請求項 17】**

前記少なくとも1つのD R A Mの前記サブアレイは、前記L U Tのように動作するように構成され、

前記少なくとも1つのD R A Mの前記サブアレイは、オペレーティングシステム環境のキャッシュ貫性アドレス空間内にあり、

前記少なくとも1つのD R A Mの前記サブアレイは、D I M Mの一部であり、

前記検出されたランタイム特徴は、前記アプリケーション又は前記仮想マシンの予め定義されたI D(I d e n t i f i c a t i o n )、機能活用度、中央処理活用度、メモリ活用度、そして前記アプリケーション又は前記仮想マシンと関連されたレイテンシの中の少なくとも1つに基づくことを特徴とする請求項16に記載の加速器ロジックローディング方法。

**【請求項 18】**

前記加速器ロジックは、前記L U Tを含むことを特徴とする請求項16に記載の加速器ロジックローディング方法。

**【請求項 19】**

前記特定された加速器ロジックは、前記加速器コントローラによって前記少なくとも1つのD R A Mの前記サブアレイにロードされることを特徴とする請求項16に記載の加速器ロジックローディング方法。

**【請求項 20】**

前記特定された加速器ロジックは、前記アプリケーション又は前記仮想マシンによって前記少なくとも1つのD R A Mにロードされることを特徴とする請求項16に記載の加速器ロジックローディング方法。

**【発明の詳細な説明】**

40

**【技術分野】****【0 0 0 1】**

本発明はシステム構造に係り、より詳しくは、加速器コントローラ及びその加速器ロジックローディング方法に関する。

**【背景技術】****【0 0 0 2】**

従来のプロセッシング加速器(P r o c e s s i n g A c c e l e r a t o r)は効率的な加速器ロジックを提供するためにF P G A(F i e l d P r o g r a m m a b l e G a t e A r r a y)又はG P U(G r a p h i c s P r o c e s s i n g U n i t)のようなP L D(P r o g r a m m a b l e L o g i c D e v i c e)によつ

50

て具現される。データセンターとモバイル装置向けのアプリケーションはますますデータ集中型になっており、プロセシング加速器を使用するアプリケーションに対して、従来のメモリ階層 (Hierarchy) は良い性能とエネルギー効率とを提供できなかった。従来のメモリ階層内のプロセシング加速器の最大効率はオフチップ (即ち、非CPU) メモリアクセス等によって低下する。効率を改善するため、メモリ近傍に加速器ロジックを設置しても、高い費用と性能が次善に過ぎないと理由により、今まで限定的な成功のみしか達成できなかった。さらに、仮に加速器ロジックがDRAM (Dynamic Random Access Memory) のようなメモリの近傍に具現される場合、DRAM半導体ダイ (Die) 上に集積された非DRAMである加速器ロジックによってDRAM容量が減少する。

10

#### 【0003】

一般的に、PLDは再構成が可能なデジタル回路を構成するために使用される電子的な構成要素である。一般的に、機能が固定されるロジックゲート又はロジック回路と異なり、PLDは伝統的に製造の時には定義されない機能を有する。また、しばしばPLDが回路に使用される前に、PLDは望む機能を遂行するためにプログラムされるか、或いは再構成されなければならない。

#### 【0004】

伝統的に、PLDはロジック装置及びメモリ装置の組合せを含む。メモリは一般的に望む機能を定義するプログラミングパターンを格納するために使用される。集積回路内にデータを格納するのに使用される大部分のテクニックは、シリコンアンチヒューズ (Silicon Anti-Fuses)、SRAM (Static Random Access Memory)、EPROM (Erasable Programmable Read Only Memory)、EEPROM (Electrically Erasable PROM)、そして不揮発性RAM (Non-Volatile RAM) 等のようにPLD内において使用するために変更されて適用されて来た。大部分のPLDは一般的にPLD内部の変更すべき (to be modified) シリコン領域にわたって特別な電圧 (非通常動作電圧すなわち高電圧) を印加してプログラムされる構成要素を含む。このような特別な電圧は、使われる技術に依存するが、よって電気的連結を切るか、繋ぐかにより、PLDの電気回路のレイアウト (Layout) を変更する。

20

#### 【0005】

PLDの最も共通的なタイプの1つはFPGA (Field-Programmable Gate Array) である。FPGAは生産された後に顧客又は設計者によって構成されるように設計された集積回路である。このような意味により“Field-Programmable (現場でプログラムできる)”と称する。FPGAはプログラム可能なロジックブロックのアレイ、及びブロックをワイヤドORにより互いに連結するようにする再構成可能なインターフェクト (Interconnect) の階層を含む。FPGAのロジックブロックは、複雑な組合せ論理関数、又は、AND、XOR等の単純なロジックゲートを具現するように構成される。

30

#### 【先行技術文献】

#### 【特許文献】

40

#### 【0006】

【特許文献1】米国特許公開第2014/814503号明細書

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

本発明は上述した技術的課題を解決するためのものであって、本発明の目的は検出器とローダーとを含む加速器コントローラ及びその加速器ロジックローディング方法を提供することにある。

#### 【課題を解決するための手段】

#### 【0008】

50

本発明の実施形態に係る加速器コントローラは検出器とローダーとを含む。検出器は仮想マシン (Virtual Machine) 又はアプリケーションのランタイム (Runtime) 特徴を検出し、検出されたランタイム特徴に対応するアプリケーション又は仮想マシンと関連した加速器ロジックを特定 (identify) する。ローダーは特定された加速器ロジックを少なくとも1つのDRAM (Dynamic Random Access Memory) にロード (Load) する。少なくとも1つのDRAMのアレイ (Array) は特定された加速器ロジックに基づいてLUT (Look-Up Table) として動作するか、又はDRAMメモリアレイとして動作するか、選択的に再構成可能である。

## 【0009】

10

本発明の他の実施形態に係る加速器コントローラは、検出器とローダーとを含む。検出器はアプリケーション又は仮想マシンのランタイム特徴を検出する。ローダーは検出されたランタイム特徴に対応する加速器ロジックを少なくとも1つのDRAMにロード (Load) する。ここで、前記のランタイム特徴は、アプリケーション又は仮想マシンの予め定義されたID (Identification)、機能活用度、中央処理活用度、メモリ活用度、そしてアプリケーション又は仮想マシンと関連したレイテンシの中の少なくとも1つに基づく。また、前記少なくとも1つのDRAMのアレイ (Array) はランタイム特徴により特定された加速器ロジックに基づいて、LUT (Look-Up Table) として動作するか、DRAMメモリアレイとして動作するか、選択的に再構成される。

## 【0010】

20

本発明の他の実施形態に係る方法は、OS環境内において実行されるアプリケーション又は仮想マシンのランタイム特徴を検出する段階、検出されたランタイム特徴に対応する加速器ロジックを特定する段階、そしてロード (Load) 及び格納コマンドを使用して特定された加速器ロジックを少なくとも1つのDRAMのサブアレイ (Sub-array) 内にロード (Load) する段階を含む。

## 【発明の効果】

## 【0011】

30

本発明の実施形態によれば、DRAM基盤の再構成可能なロジックが提供される。提供されたロジックによって、従来のFPGAに比べて高い密度、低い費用、そしてさらにより柔軟性 (Flexibility) が提供される。

## 【図面の簡単な説明】

## 【0012】

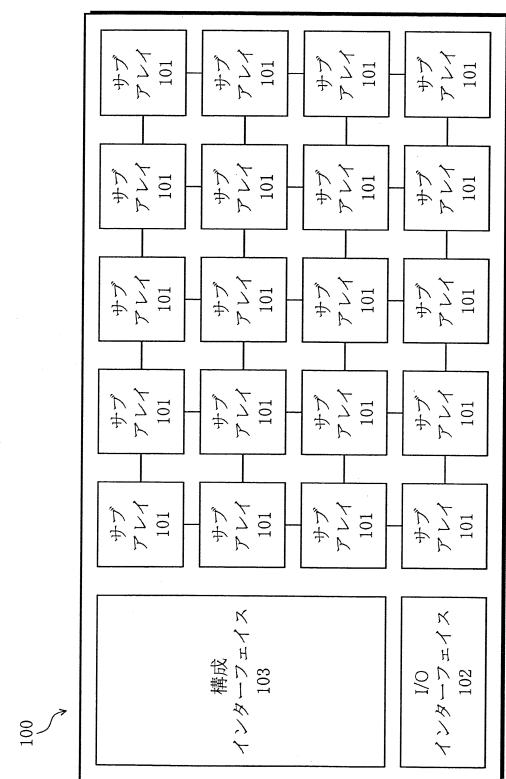

【図1】本発明の実施形態に係る再構成可能なメモリロジック装置を示す図面である。

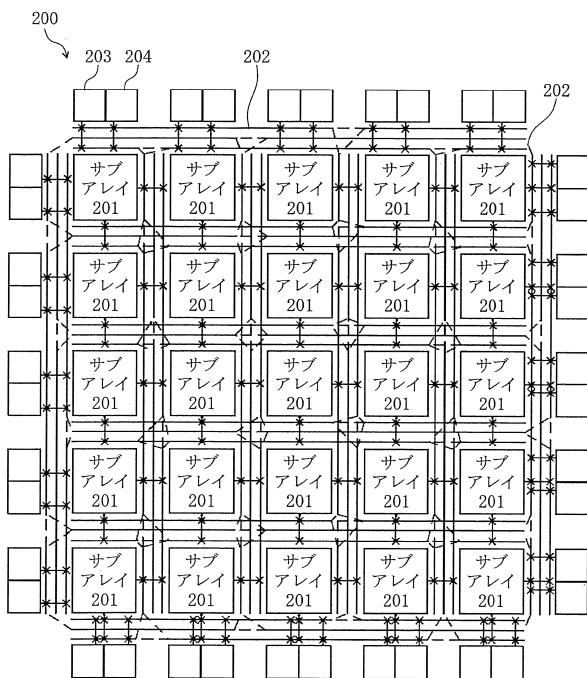

【図2】本発明の他の実施形態に係る再構成可能なメモリロジック装置を示すブロックダイヤグラムである。

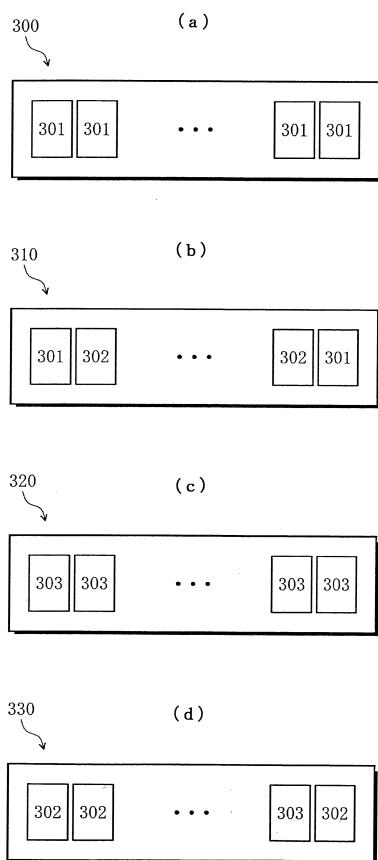

【図3】本発明に係る1つ以上のDRAM-FPGAを含むDIMMを示すブロック図である。

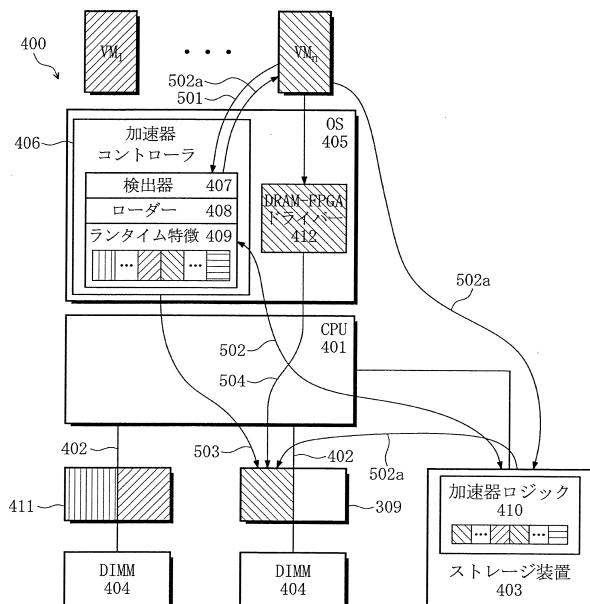

【図4】本発明に係るメモリチャネル内において1つ以上のDRAM-FPGAを使用するシステム構造を示す機能ブロック図である。

40

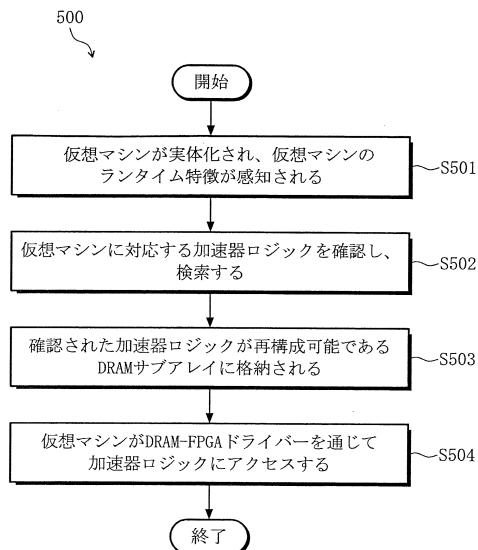

【図5】本発明に係る仮想マシン又はアプリケーションのランタイム特徴を検出し、再構成可能なDRAMサブアレイ内の仮想マシン又はアプリケーションに対応する加速器ロジックを格納する方法を示す順序図である。

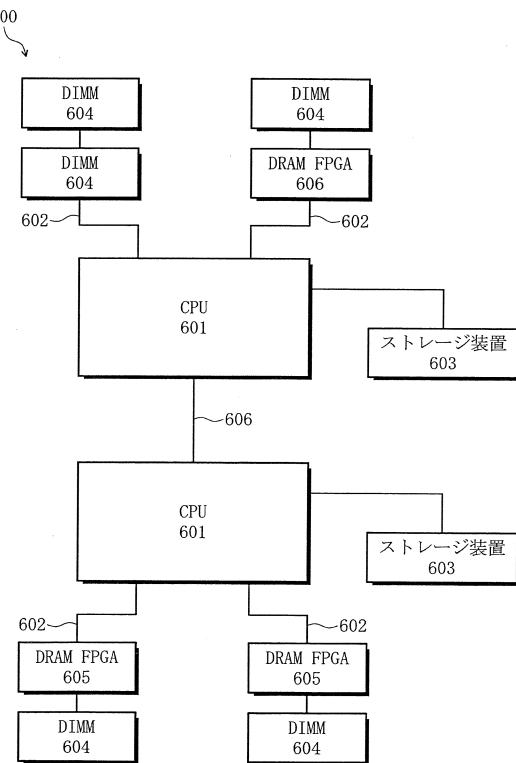

【図6】本発明に係るメモリチャネル内において1つ以上のDRAM-FPGAを使用するQPI基盤のシステム構造を示すブロック図である。

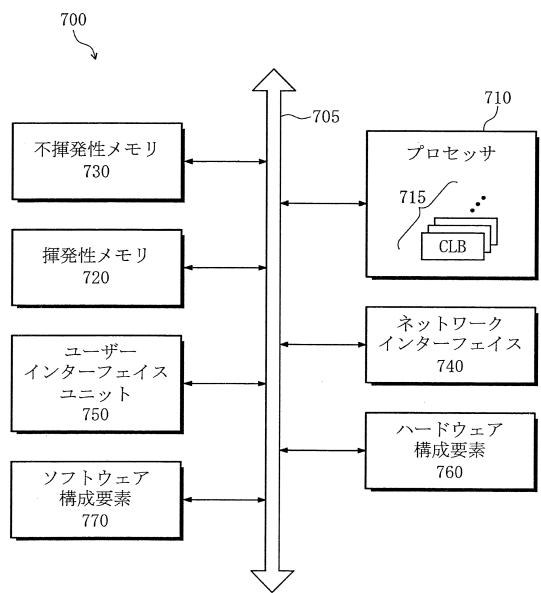

【図7】本発明に係るメモリチャネル内において1つ以上のDRAM-FPGAを含むシステム構造を使用できる情報処理システムを示す機能ブロック図である。

## 【発明を実施するための形態】

## 【0013】

以下においては、本発明の技術分野の通常の知識を有する者が本発明を容易に実施でき

50

る程度に、本発明の実施形態を明確かつ詳細に説明する。

#### 【0014】

本明細書に記載された技術的な特徴はメモリチャンネル内に1つ以上のDRAM-FPGA (Dynamic Random Access Memory Field Programmable Gate array) を使用するシステム構造に関する。DRAM-FPGAは選択的に再構成可能なDRAMセルアレイをLUT (Lookup Table) に使用し、再構成可能なロジックをメモリ近傍に具現する。また、DRAM-FPGAは任意のロジックデザインにより再構成可能である。

#### 【0015】

さらに、このようなDRAM基盤の再構成可能なロジックはDRAM製造工程と互換され、インメモリ (In-Memory) プロセシングに対する1つの良い候補である。従来のFPGAと比較して、DRAM基盤の再構成可能なロジックはより高い密度 (Density)、低い費用、そしてさらにより柔軟性 (Flexibility) を提供する。即ち、さらにより柔軟性はウェアハウススケール (Warehouse-Scale) のデータセンター内の他の演算ノード (Node) の間における速い移動 (Migration) を提供する自体変形 (Self-Modify) 及び速い動的再構成を意味する。

10

#### 【0016】

FPGAの形態を有するPLDを使用する従来のシステム構造は一般的にPCIe (Peripheral Component Interconnect-express) スロット内にFPGAを位置させる。PCIeスロットはキャッシュ貫性 (Cache-Coherent) アドレス空間に位置せず、低い通信バンド幅 (Bandwidth) を提供する。また、PCIeスロット内のFPGA内の加速器ロジックの動作はドライバーによって提供される明示的な命令によって遂行される。

20

#### 【0017】

図1は本発明の実施形態に係る再構成可能なメモリロジック装置100を示す図面である。再構成可能なメモリロジック装置100はLUT (Look-up Table) モード又は正規 (Regular) DRAM (Dynamic Random Access Memory) モードの2つのモードにより動作するように構成され、連結される。再構成可能なメモリロジック装置100は1つ以上のサブアレイ101、I/Oインターフェイス102、及び構成インターフェイス103を含む。サブアレイ101は複数の行及び列に整列される。サブアレイ101の各々は多数のメモリセル (図示せず) を含み、多数のメモリセルはまた複数の行及び列アレイに整列される。再構成可能なメモリロジック装置100は図1に図示されない他の構成要素及び/又は部品を含む。

30

#### 【0018】

一実施形態として、サブアレイ101はDRAMを含む。LUT又は従来のDRAMサブアレイのように動作するために、1つ以上のサブアレイ101は一般的なメモリアクセス動作を利用して選択的に再構成されるか、或いは再びプログラムされる。再構成可能なメモリロジック装置100はここでFPGAとして示す。DRAMを含むサブアレイ101を含む再構成可能なメモリロジック装置100の実施形態に対して、再構成可能なメモリロジック装置100は本明細書において“DRAM-FPGA”と称する。

40

#### 【0019】

一実施形態として、LUT又はRAM (Random Access Memory) により構成されたサブアレイ101の数は必要によって動的に調整される。他の実施形態として、1つ以上のサブアレイ101は再構成が不可能であるか、或いは従来のメモリサブアレイのように構成される反面、1つ以上のサブアレイ101はLUT又は従来のメモリサブアレイのように動作するために再構成される。LUT又は従来のメモリサブアレイのように動作するように再構成可能なサブアレイはRLUT (Reconfigurable LUT) サブアレイと称する。

#### 【0020】

50

仮にサブアレイ 101 が LUT のように動作するように構成される場合、LUT 動作は算術論理機能（足し算、掛け算等）、ロジック機能（AND、OR、XOR 等）、又はこれらの組合せ等のロジック機能を具現する。但し、本発明はこれに制限されない。ロジック機能はサブアレイ上にメモリ書き込み動作又は特別な書き込み動作を遂行することによって変更される。したがって、再構成可能なメモリロジック装置 100 の動作中に、ロジック機能は動的に再構成されるか、或いは変更される。特別な書き込み動作は書き込み動作が特定サブアレイと連関されることを表示する識別子を含む。従来の書き込み動作（又は類似な動作）の使用は EEPROM 等のプログラムのために使用されるような特別な電圧（非動作電圧又は高い電圧）の必要無しでも選択されたサブアレイ 101 が再プログラミングされるようにする。

10

## 【0021】

R LUT サブアレイ及びRAM サブアレイの混合（Co-mingling）は幾つか長所を提供する。例えば、RAM サブアレイ内に格納されたデータに隣接する場合、RLUT サブアレイによって遂行される計算が速くなり、電力要求量が減少する。これはデータが個別の構成要素の間のバスを通じて移動する必要がないためである。さらに、一実施形態として、1つ以上のサブアレイ 101 は1回によりアクセスされる。したがって、パワー消耗及び再構成可能なメモリロジック装置 100 の計算複雑度が減少する。このように、DRAM R LUT によって提供される近距離データコンピューティングはさらに速くてさらに効率的である。

20

## 【0022】

プロセッサ（図示せず）とメモリ（図示せず）とを製造するために使用されたのと類似するDRAM技術上のRLUT サブアレイに基づき、RLUT サブアレイはプロセッサ及び／又はメモリとして同一ダイ（Die）又はパッケージ内に存在する。同一の製造工程を使用すれば、本発明に係る1つのメモリチャンネル内に1つ以上のRLUT を使用するシステムの製造費用が低下できる。さらに、DRAM サブアレイ上のRLUT サブアレイに基づくことによって、SRAM 基盤のFPGA の密度と比較して相対的に高密度が達成される。例えば、SRAM 基盤のFPGA がメモリセル又はビット単位の情報当たり（Per）6 個のトランジスタ 6T を要求する反面、DRAM 基盤のRLUT はメモリセル又はビット単位の情報当たり（Per）単に1つのトランジスタ及び1つのキャパシター 1T 1C を要求する。その上、DRAM 基盤のRLUT はSRAM 又はフラッシュ基盤のFPGA と比較して費用を低下させる。

30

## 【0023】

I/Oインターフェイス 102 は選択されたサブアレイ 101 を読み出すか、或いは書き込むように構成される。書き込みアクセスはサブアレイ 101 に対する書き込み動作を含む。これはサブアレイ 101 が LUT として動作するか否か又は従来のDRAM サブアレイとして動作するか否かを定義するためである。一部の実施形態において、すべてのメモリアクセス又は動作は I/Oインターフェイス 102 を通過する。仮にメモリアクセスが RAM サブアレイ又は RAM サブアレイとして構成された RLUT サブアレイのリバイバル（Revival）のためにデータを格納するサブアレイに対するアクセスである場合、I/Oインターフェイス 102 は単純に従来のメモリアクセスとして読み出し／書き込み要請を処理する。しかし、仮にメモリアクセスが LUT として構成された RLUT サブアレイに対するアクセスである場合、I/Oインターフェイス 102 はプロセシングするためにメモリアクセスを構成インターフェイス 103 に通過させる。

40

## 【0024】

構成インターフェイス 103 は全体的に再構成可能なメモリロジック装置 100 内の信号のルーティング（Routing）を調整するか、又は各々のサブアレイ 101 内の信号のルーティングを調整するよう構成される。例えば、構成インターフェイス 103 は RLUT 及び／又は RAM により構成された複数のサブアレイ 101 の間の信号のルーティングを調整するよう構成される。一実施形態として、I/Oインターフェイス 102 はサブアレイ 101 に対するデータアクセスを管理するように構成される。例えば、一実施

50

形態として、I/Oインターフェイス102はプロセッサ(図示せず)から構成情報を受信する。構成情報はサブアレイ101に対するI/Oアクセスを制御するためにI/Oインターフェイス102を構成するのに使用され、これにサブアレイ101内のメモリの位置はアドレス化可能な(Addressable)レジスターとして示される。構成インターフェイス103は各々のサブアレイ101の間のインターフェクト(Interconnects)と信号ルーティングとを管理するように構成される。例えば、このようなインターフェクトと信号ルーティングとはポイントツーポイント(Point-to-Point)ルーティング、アドレス基盤のルーティング、又はこれらの組合せ等によって構成される。例えば、一実施形態として、構成情報は構成インターフェイス103を構成するのに使用されるI/Oインターフェイス102によって受信され、これにサブアレイ101は複数のサブアレイ101にわたって複雑な論理動作を遂行する。一実施形態として、I/Oインターフェイス102は構成インターフェイス103を含む。

10

#### 【0025】

メモリアクセスは特定サブアレイ101内のルックアップテーブル(Look-up Table)を格納する書き込み動作を含む。また、メモリアクセスはLUTの大きさにしたがって一連のメモリアクセスを含む。一部の実施形態において、特定メモリアクセスはLUTに対する入力数とLUTからの出力数を示す。また、追加的なメモリアクセスはサブアレイ101に対する信号ルーティング情報及び/又は2つ以上のサブアレイ101がロジック機能(加算器等)を遂行するためにカスケード(Cascade)されているか、或いは共にルーティングされているか否かを示す。サブアレイ101によって提供される論理機能の詳細説明は本明細書の参考として引用した特許文献1に開示されている。又は、メモリアクセスはサブアレイ101を従来のRAMサブアレイとして動作するように再構成する書き込み動作を含む。

20

#### 【0026】

図2は本発明の他の実施形態に係る再構成可能なメモリロジック装置200を示すブロックダイヤグラムである。図2を参照すれば、再構成可能なメモリロジック装置200は独立したダイ(Die)や單一ダイの一部として具現される。單一ダイの一部として具現される場合、再構成可能なメモリロジック装置200は共有ダイ(システムオンチップ、プロセッサキャッシュ等)上において他の構成要素(図示せず)と共に集積される。但し、共有ダイの種類はこれに限定されない。再構成可能なメモリロジック装置200は1つ以上のサブアレイ201、複数の通信バス202、入力信号パッド203、そして出力信号パッド204を含む。再構成可能なメモリロジック装置200はバス基盤のインターフェクションとルーティング方式により具現される。通信バス202はサブアレイ201の間のルーティング方式がサブアレイ201の間の信号を再びルーティングするために動的に変更されるようとする。

30

#### 【0027】

仮にサブアレイ201がLUTのように動作するように構成される場合、LUT動作は算術論理機能(足し算、掛け算等)、ロジック機能(AND、OR、XOR等)、又はこれらの組合せ等のロジック機能を具現する。サブアレイ201によって提供される数ある論理機能の詳細説明は本明細書の参考に引用された特許文献1に開示されている。ロジック機能はサブアレイ201にメモリ書き込み動作又は特別な書き込み動作を遂行して変更される。したがって、これは再構成可能なメモリロジック装置200の動作の中においてロジック機能を動的に再構成するか、或いは変更する。特別な書き込み動作は書き込み動作が特定サブアレイと連関されることを表示する識別子を含む。

40

#### 【0028】

一実施形態にしたがって、図1の1つ以上のサブアレイ101及び/又は図2の1つ以上の再構成可能なメモリロジック装置200はDIMM(Dual In-line Memory Module)内において使用される。即ち、1つ以上の正規DRAMモジュールと共に、DIMMは1つ以上のDRAM-FPGAモジュール、1つ以上のRLUTモジュール、1つ以上のDRAM-FPGAモジュールと1つ以上のRLUTモジュ

50

ルとの組合せ、又は1つ以上のDRAM-FPGAモジュール及び／又は1つ以上のRLUTモジュールの組合せを含むように構成される。

#### 【0029】

図3(a)乃至(d)は本発明に係る1つ以上のDRAM-FPGAを含むDIMMを示すブロック図である。

#### 【0030】

図3(a)を参照すれば、DIMM300は複数のDRAM-FPGAモジュール301を含む。ここで、4つのDRAM-FPGAモジュール301を図示した。したがって、DIMM300の特定実施形態に対して、すべてのモジュール位置はDRAM-FPGAモジュール301によって満たされる。又は、すべてのモジュール位置はRLUTモジュールによって満たされ、RLUTモジュールの各々はRLUT(Reconfigurable Look-up Table)を含む。

10

#### 【0031】

図3(b)を参照すれば、DIMM310は1つ以上のDRAM-FPGAモジュール301と1つ以上の正規DRAMモジュール302とを含む。ここで、2つのDRAM-FPGAモジュール301と2つの正規DRAMモジュール302とを図示した。DIMM310の特定実施形態に対して、DRAM-FPGAモジュール301と正規DRAMモジュール302との物理的な配置は何らかの順序も含む。又は、DIMM310の構成は1つ以上のRLUTモジュールと1つ以上の正規DRAMモジュール302である。

20

#### 【0032】

図3(c)を参照すれば、DIMM320は複数のハイブリッドDRAM-FPGAモジュール303を含む。ここで、4つのハイブリッドDRAM-FPGAモジュール303を図示した。ハイブリッドDRAM-FPGAモジュール303はLUT又は従来のDRAMサブアレイのように動作するように再構成可能な1つ以上のサブアレイを含み、従来のDRAMサブアレイのように動作する再構成が不可能である1つ以上のサブアレイを含む。即ち、DIMM320の構成はハイブリッドDRAM-FPGAモジュール303のみを含む。

#### 【0033】

図3(d)を参照すれば、DIMM330は1つ以上のハイブリッドDRAM-FPGAモジュール303と1つ以上の正規DRAMモジュール302とを含む。ここで、2つのハイブリッドDRAM-FPGAモジュール303と2つの正規DRAMモジュール302とを図示した。DIMM330の特定実施形態に対して、ハイブリッドDRAM-FPGAモジュール303と正規DRAMモジュール302との物理的配置は何らかの順序も含む。

30

#### 【0034】

DIMMは他の構成も含む。即ち、本発明は1つ以上のDRAM-FPGAモジュール、1つ以上の正規DRAMモジュール、1つ以上のハイブリッドDRAM-FPGAモジュール及び／又は1つ以上のRLUTモジュールを含むDIMM構成が可能となるが、これに制限されない。

#### 【0035】

図4は本発明に係るメモリチャネル内において1つ以上のDRAM-FPGAを使用するシステム構造400を示す機能ブロック図である。図5は本発明に係る仮想マシン又はアプリケーションのランタイム特徴を検出し、再構成可能なDRAMサブアレイ内の仮想マシン又はアプリケーションに対応する加速器ロジックを格納する方法500を示す順序図である。順序図500のS501乃至S504の段階は図5を参照して説明する。

40

#### 【0036】

図4を参照すれば、システム構造400はRAM(Random Access Memory)のようなシステムメモリ及び1つ以上の大容量ストレージ装置403に連結されたCPU401(Central Processing Unit)を含む。例えば、CPU401はメモリチャネル402を通じてシステムメモリと連結される。システ

50

ムメモリのRAMはSRAM(Static RAM)及び/又はDRAM(Dynamic RAM)を含む。一実施形態として、図4に図示したように、システムメモリは1つ以上のDIMM404内のDRAMを含む。一実施形態として、1つ以上の正規DRAMモジュールと共に、DIMM404は1つ以上のDRAM-FPGAモジュール、1つ以上のRLUTモジュール、1つ以上のDRAM-FPGAモジュールと1つ以上のRLUTモジュールの組合せ、又は1つ以上のDRAM-FPGAモジュール及び/又は1つ以上のRLUTモジュールの組合せを含むように構成される。メモリチャンネル内のDRAM-FPGAは1つ以上のDIMM404により具現される。

#### 【0037】

OS405(Operating System)はCPU401上において実行される。<sup>10</sup> OS405はUnix基盤のOS、Unixと類似なOS、リナックス(登録商標)基盤のOS、クロム基盤のOS又はウインドー基盤のOS等である。但し、本発明はこれに制限されない。1つ以上の仮想マシン(VM: Virtual Machine)はOS405上において実行される。図4に図示したように、仮想マシンVM1乃至VMnはOS405上において実行される。システム構造400がデータセンター環境において具現される状況において、仮想マシンVM1乃至VMnはデータセンターアプリケーションを意味する。システム構造400がモバイル装置環境により具現される状況において、仮想マシンVM1乃至VMnはモバイル装置アプリケーションを意味する。

#### 【0038】

OS405は加速器コントローラ406を含む。加速器コントローラ406は実体化された(instantiated)仮想マシンVMと関連されたランタイム特徴を検出器407により仮想マシンVMの実体を検出する。ここで使用したように、仮想マシンVMの“ランタイム特徴”という用語は動作特性を意味する。例えば、動作特性は仮想マシンVMのID(Identity)及び/又は特定設定構成である。但し、本発明はこれに制限されない。一実施形態として、加速器コントローラ406はソフトウェア基盤、ハードウェア基盤、又はこれらの組せによって具現される。一実施形態として、加速器コントローラ406はOS405内のソフトウェアモジュールを含む。他の実施形態として、加速器コントローラ406はメモリコントローラ(図示せず)内のハードウェアモジュールを含む。<sup>20</sup>

#### 【0039】

一実施形態として、加速器コントローラ406は検出器407とローダー408(loader)とを含む。検出器407はアプリケーション又は仮想マシンVMのランタイム特徴409を検出し、検出されたランタイム特徴409に対応するアプリケーション又は仮想マシンと関連された加速器ロジック410を特定する。他の実施形態として、加速器コントローラ406はランタイムの時に仮想マシンVM又はアプリケーションをプロファイル(Profile)し、ランタイム署名(Signature)を収集し、加速器ロジック410の保管場所を探すためにランタイム署名を利用する。ランタイム署名は機能活用度、CPU活用度、レイテンシ(Latency)、及び/又は他のマイクロ構造(Micro-architecture)統計等を含む。但し、本発明はこれに制限されない。一実施形態として、仮想マシンVM又はアプリケーションのランタイム特徴を検出するのに使用されるアプリケーションのランタイム特徴409は加速器コントローラ406内に格納されるか、或いは加速器コントローラ406の一部に格納される。例えば、他の実施形態として、ランタイム特徴409は大容量ストレージ装置403内に格納され、加速器コントローラ406が初期化される時、加速器ロジック410にロード(load)される。<sup>40</sup>

#### 【0040】

仮想マシンVM又はアプリケーションの検出されたランタイム特徴409に基づいて、加速器コントローラ406はローダー408を選択し、加速器ロジック410を回収し、仮想マシンVMのための加速器ロジック410をメモリチャンネル格納命令を利用してDRAM-FPGA411内にロードする。加速器ロジック410は大容量ストレージ装置<sup>50</sup>

403 内に格納され、仮想マシンによって利用される。一実施形態として、回収された加速器ロジック 410 は仮想マシン VM によって要請されるか、又は選択的に仮想マシン VM によって要請される。他の実施形態として、加速器ロジック 410 は OS 405 又はユーザーによって要請されるか、或いは勧奨 (Recommend) される。他の実施形態として、加速器コントローラ 406 は仮想マシン VMn に対する加速器ロジック 410 を特定し、仮想マシン VMn はメモリチャンネル格納命令を利用して加速器ロジック 410 を回収して DRAM - FPGA 411 内に格納する。加速器ロジック 410 がシステム構造 400 のメモリチャンネル 402 内にある DRAM - FPGA 411 内に格納されるので、これにしたがって加速器ロジック 410 は CPU 401 によって直接アクセスされるキャッシュ貫性 (Cache-Coherent) アドレス空間内に格納される。このような点において、加速器ロジック 410 は OS 405 によってアクセス可能なキャッシュ貫性 (Cache-Coherent) アドレス空間内に格納される。

10

#### 【0041】

図 4 を参照すれば、仮想マシン VMn、ランタイム特徴 409、加速器ロジック 410、加速器ロジック 410 が格納された特定 DRAM - FPGA 411、そして仮想マシン VMn に対する DRAM - FPGA ドライバー 412 は左側上から右側下までのハッチング (Cross hatching) によって表示する。他の仮想マシン、その各々のランタイム特徴、加速器ロジックと DRAM - FPGA 配置もまた類似に対応するハッチングによって表示する。一実施形態として、加速器コントローラ 406 は仮想マシン VM と対応する DRAM - FPGA ドライバー 412 のアドレスを仮想マシン VM に伝達する。仮想マシン VM が DRAM - FPGA ドライバー 412 にアクセスすることによって、DRAM - FPGA ドライバー 412 は DRAM - FPGA 411 に格納された仮想マシン VM に対する加速器ロジック 410 にアクセスする。

20

#### 【0042】

図 5 は本発明に係る仮想マシン又はアプリケーションのランタイム特徴を検出し、再構成可能な DRAM サブアレイ内の仮想マシン又はアプリケーションに対応する加速器ロジックを格納する方法を示す順序図である。図 4 を参照して、ここで仮想マシン VMn が図 5 の S501 段階において実体化された場合を仮定する。

#### 【0043】

S501 段階において、加速器コントローラ 406 は仮想マシン VMn が仮想マシン VMn と関連されたランタイム特徴 409 に基づいて実体化されたかを検出する。S502 段階において、加速器コントローラ 406 は仮想マシン VMn に対する加速器ロジック 410 を選択し、回収する。

30

#### 【0044】

S503 段階において、加速器コントローラ 406 のローダー 408 はメモリチャンネル格納命令を利用して DRAM - FPGA 411 内に選択された加速器ロジック 410 を格納する。他の実施形態において、S503 段階において加速器コントローラ 406 は仮想マシン VMn に対する加速器ロジック 410 を特定する。そして、仮想マシン VMn は図 4 の 502a のメモリチャンネル格納命令を利用して DRAM - FPGA 411 内の加速器ロジック 410 を回収し、格納する。

40

#### 【0045】

S504 段階において、仮想マシン VMn は DRAM - FPGA ドライバー 412 を通じて DRAM - FPGA 411 内の加速器ロジック 410 にアクセスする。他の実施形態として、システム構造 400 は QPI (Quick Path Interconnect) 環境のようなポイントツーポイント (Point-to-Point) プロセッサー・コネクト環境に適用される。但し、本発明はこれに制限されない。

#### 【0046】

図 6 は本発明に係るメモリチャンネル内において 1 つ以上の DRAM - FPGA を使用する QPI 基盤のシステム構造 600 を示すブロック図である。図 6 を参照すれば、システム構造 600 はメモリチャンネル 602 を通じて RAM (Random Access

50

Memory) のようなシステムメモリに、そして 1 つ以上の大容量ストレージ装置 603 に連結された 2 つの CPU601 を含む。システムメモリの RAM は SRAM 及び / 又は DRAM を含む。一実施形態として、システムメモリは 1 つ以上の DIMM604 (Dual In-line Memory Module) 内に具現された DRAM を含む。1 つ以上の DRAM-FPGA605 は CPU601 の各々のメモリチャンネル 602 内において使用される。CPU601 は互いに QPI 基盤のインターフェクト 606 を通じて連結される。

#### 【0047】

図 7 は本発明に係るメモリチャンネル内において 1 つ以上の DRAM-FPGA を含むシステム構造を使用できる情報処理システム 700 を示す機能プロック図である。情報処理システム 700 は本発明によって構成された 1 つ以上の装置を含む。

10

#### 【0048】

多様な実施形態において、情報処理システム 700 はコンピューティング装置として具現される。例えば、コンピューティング装置はラップトップ (Laptop)、デスクトップコンピュータ (Desktop)、ワークステーション (Workstation)、サーバー (Server)、ブレードサーバー (Blade Server)、個人用デジタル補助機 (Personal Digital Assistant)、スマートフォン、タブレット (Tablet)、そして他の多様なコンピュータ、又は仮想マシンやそれらの仮想コンピューティング装置を含む。多様な実施形態において、情報処理システム 700 はユーザー (図示せず) によって使用される。

20

#### 【0049】

情報処理システム 700 は CPU (Central Processing Unit)、ロジック、又はプロセッサ 710 をさらに含む。一部の実施形態において、プロセッサ 710 は 1 つ以上の FUB (Functional Unit Block) 又は CLB (Combinational Logic Block) 715 を含む。このような実施形態において、CLB 715 は多様なブール (Boolean) ロジック演算 (AND、NOR、NOT、XOR 等)、安定化されたロジック装置 (フリップフロップ、ラッチ等)、他のロジック装置、又はこれらの組合せを含む。組合せ論理演算 (Combinational Logic Operation) は望む結果を得るために入力信号を処理するために単純であるか、或いは複雑な形態として構成される。ここで、同期化された組合せ論理演算の実施形態を記述したが、本発明はこれに制限されず、非同期化された組合せ論理演算又はこれらの組合せを含むことは容易に理解される。

30

#### 【0050】

一実施形態において、組合せ論理演算は複数の CMOS (Complementary Metal Oxide Semiconductors) トランジスタを含む。多様な実施形態において、このような CMOS トランジスタはロジック演算を遂行するゲート (Gate) として配置される。但し、他の技術が使用でき、他の技術が本発明の範囲内にあることは容易に理解される。他の実施形態において、プロセッサ 710 を含む本発明に係る加速器コントローラを具現する構成要素をさらに含む。

#### 【0051】

本発明に係る情報処理システム 700 は RAM のような揮発性メモリ 720 をさらに含む。揮発性メモリ 720 はメモリチャンネルを通じてプロセッサ 710 によってアクセス可能である。本発明に係る情報処理システム 700 はハードドライブ、光学メモリ、 NAND 又はフラッシュメモリ等の不揮発性メモリ 730 をさらに含む。一部の実施形態において、揮発性メモリ 720、不揮発性メモリ 730、又はこれらの組合せや部分的な組合せの全ては ‘記憶媒体’ と称される。多様な実施形態において、揮発性メモリ 720 及び / 又は不揮発性メモリ 730 は半永久的 (Semi-Permanent) 又は実質的に永久的な形態としてデータを格納するように構成される。

40

#### 【0052】

多様な実施形態において、上述した 1 つ以上の RLT は揮発性メモリ 720 又は不揮

50

発性メモリ 730 内に含まれる。上述したように、R L U T は D R A M 又は他のメモリの一部として含まれる。上述したように、一部の実施形態において、揮発性メモリ 720 又は不揮発性メモリ 730 の一部分はデータを格納するのに使用され、他の部分は R L U T として使用される。一部の実施形態において、R L U T はまたプロセッサ 710 及び / 又はロジックの一部として看做される。上述したように、R L U T は 1 つ以上のロジック機能を遂行し、これにしたがって命令を遂行する。

#### 【 0053 】

多様な実施形態において、情報処理システム 700 は 1 つ以上のネットワークインターフェイス 740 を含む。ネットワークインターフェイス 740 は情報処理システム 700 が通信ネットワークの一部になるように構成され、また通信ネットワークを通じて通信するように構成される。例えば、Wi-Fi プロトコルは IEEE (Institute of Electrical and Electronics Engineers) 802.11g、IEEE 802.11n 等を含む。例えば、セルラー (Cellular) プロトコルは IEEE 802.16m (Wireless-MAN (Metropolitan Area Network) Advanced として公知される)、LTE (Long Term Evolution) Advanced、EDGE (Enhanced Data rates for GSM (登録商標) (Global System for Mobile Communications) Evolution)、HSPA+ (Evolved High-Speed Packet Access) 等を含む。例えば、有線プロトコルは IEEE 802.3 (Ethernet と公知される)、ファイバ (Fibre) チャンネル、電力ライン通信 (HomePlug、IEEE 1901 等) 等を含む。但し、本発明は上述した例に制限されない。

10

#### 【 0054 】

本発明に係る情報処理システム 700 はユーザーインターフェイスユニット 750 を含む。ユーザーインターフェイスユニット 750 はディスプレイアダプタ (Display Adapter)、ハaptiック (Haptic) インターフェイス、ヒューマン (Human) インターフェイス装置等を含む。多様な実施形態において、ユーザーインターフェイスユニット 750 はユーザーから入力を受信し、又はユーザーに出力を提供するように構成される。同様に、他の形態の装置はユーザーとの相互作用を提供するために使用される。例えば、ユーザーに提供されるフィードバック (Feedback) は視覚的フィードバック、聴覚的フィードバック、又は触覚的フィードバック等の何らかの形態の感覚上の (Sensory) フィードバックである。例えば、ユーザーからの入力は音響、音声、又は触覚入力等を含む何らかの形態としても受信される。

30

#### 【 0055 】

多様な実施形態において、情報処理システム 700 は 1 つ以上の他の装置又はハードウェア構成要素 760 を含む。ハードウェア構成要素 760 はディスプレイ又はモニター、キーボード、マウス、カメラ、指紋認識器、ビデオプロセッサ等を含む。但し、本発明はこれに制限されない。

#### 【 0056 】

本発明に係る情報処理システム 700 は 1 つ以上のシステムバス 705 をさらに含む。このような実施形態において、システムバス 705 は通信の観点で (Communicatively) プロセッサ 710、揮発性メモリ 720、不揮発性メモリ 730、ネットワークインターフェイス 740、ユーザーインターフェイスユニット 750、そして 1 つ以上のハードウェア構成要素 760 と連結されるように構成される。プロセッサ 710 によって処理されるデータ又は不揮発性メモリ 730 の外部からのデータ入力は不揮発性メモリ 730 又は揮発性メモリ 720 の中の 1 つの内部に格納される。

40

#### 【 0057 】

多様な実施形態において、情報処理システム 700 は 1 つ以上のソフトウェア構成要素 770 を含むか、或いは実行する。一部の実施形態において、ソフトウェア構成要素 770 は O S 及び / 又はアプリケーションを含む。一部の実施形態において、O S はアプリケ

50

ーションに1つ以上のサービスを提供するように構成され、情報処理システム700の多様なハードウェア構成要素（プロセッサ710、ネットワークインターフェイス740等）とアプリケーションとの間の仲介者（*Intermediary*）として動作するか、或いはこれを制御するように構成される。このような実施形態において、情報処理システム700は1つ以上のネイティブ（*Native*）アプリケーションを含む。ネイティブアプリケーションは不揮発性メモリ730等のように地域的に（*Locality*）設置され、プロセッサ710によって実行されるように構成されてOSと直接相互作用する。このような実施形態において、ネイティブアプリケーションは予めコンパイル（*Compile*）された機械実行（*Machine-executable*）コードを含む。一部の実施形態において、ネイティブアプリケーションはスクリプトインタプリタ（*Script Interpreter*）（*C shell (csh)*、*AppleScript*、*AutoHotkey*等）又は仮想実行マシンVM（*Java*（登録商標）*Virtual Machine*、*Microsoft Common Language Runtime*等）を含み、このようなスクリプトインタプリタ又は仮想実行マシンはソースコード又はオブジェクト（*Object*）コードをプロセッサ710によって実行される実行可能なコードにより翻訳するように構成される。一部の実施形態において、1つ以上のソフトウェア構成要素770は本発明の実施形態に係る加速器コントローラを具現する実行可能な命令語を含む。

10

## 【0058】

上述した内容は本発明を実施するための具体的な例である。本発明には上述した実施形態のみでなく、単純に設計変更するか、或いは容易に変更できる実施形態も含む。また、本発明には上述した実施形態を利用して将来に容易に変形して実施できる技術も含む。

20

## 【符号の説明】

## 【0059】

- |                                   |    |

|-----------------------------------|----|

| 100、200 再構成可能なメモリロジック装置           |    |

| 101、201 サブアレイ                     |    |

| 102 I/Oインターフェイス                   |    |

| 103 構成インターフェイス                    |    |

| 202 通信バス                          |    |

| 203 入力信号パッド                       | 30 |

| 204 出力信号パッド                       |    |

| 300、310、320、330、404、604 D I M M   |    |

| 301 D R A M - F P G A モジュール       |    |

| 302 正規D R A M モジュール               |    |

| 303 ハイブリッドD R A M - F P G A モジュール |    |

| 400、600 システム構造                    |    |

| 401、601 C P U                     |    |

| 402 メモリチャンネル                      |    |

| 403 大容量ストレージ装置                    |    |

| 404 D I M M                       | 40 |

| 405 O S                           |    |

| 406 加速器コントローラ                     |    |

| 407 検出器                           |    |

| 408 ローダー                          |    |

| 409 ランタイム特徴                       |    |

| 410 加速器ロジック                       |    |

| 411、605 D R A M - F P G A         |    |

| 412 D R A M - F P G A ドライバー       |    |

| 602 メモリチャンネル                      |    |

| 603 ストレージ装置                       | 50 |

6 0 6 インターコネクト

7 0 0 情報処理システム

7 0 5 システムバス

7 1 0 プロセッサ

7 1 5 C L B

7 2 0 振発性メモリ

7 3 0 不揮発性メモリ

7 4 0 ネットワークインターフェイス

7 5 0 ユーザーインターフェイスユニット

7 6 0 ハードウェア構成要素

7 7 0 ソフトウェア構成要素

10

【図1】

【図2】

【図3】

【 図 4 】

【図5】

【 四 6 】

【図7】

---

フロントページの続き

(72)発明者 張， 牧 天

アメリカ合衆国 95134 カリフォルニア州 サンノゼ #4103 パルミラ ドライブ

3507

審査官 北元 健太

(56)参考文献 特開2000-10770(JP, A)

特開平11-232309(JP, A)

特開2012-84220(JP, A)

特開平10-285014(JP, A)

特開2016-123092(JP, A)

特開2008-112508(JP, A)

特表2015-507234(JP, A)

中国特許出願公開第103959245(CN, A)

柴田裕一郎、外3名, HOSMII: DRAM混載型FPGAに基づく仮想ハードウェアシステム, 電子情報通信学会技術研究報告, 日本, 社団法人電子情報通信学会, 1997年 8月19日, 第97巻, 第225号, pp.69-76

(58)調査した分野(Int.Cl., DB名)

G06F 9/44 - 9/455

G06F 8/00 - 8/77