(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5578915号

(P5578915)

(45) 発行日 平成26年8月27日(2014.8.27)

(24) 登録日 平成26年7月18日(2014.7.18)

(51) Int.Cl.

F 1

H04N 5/374 (2011.01)

H04N 5/335 740

H04N 5/353 (2011.01)

H04N 5/335 530

H04N 5/341 (2011.01)

H04N 5/335 410

請求項の数 5 (全 17 頁)

(21) 出願番号

特願2010-85471 (P2010-85471)

(22) 出願日

平成22年4月1日(2010.4.1)

(65) 公開番号

特開2011-217280 (P2011-217280A)

(43) 公開日

平成23年10月27日(2011.10.27)

審査請求日

平成25年3月29日(2013.3.29)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 山崎 龍彦

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者 竹中 真太郎

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

審査官 木方 康輔

最終頁に続く

(54) 【発明の名称】 固体撮像装置及びその駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

光電変換により画素信号を生成する複数の画素が2次元行列状に配列された画素部と、前記画素部の行を選択する画素駆動部と、を有し、前記画素駆動部は、

第1のフィールドで読み出される前記画素部の行を走査して前記第1のフィールドで読み出される画素の画素信号を順次リセットし、その後、第2のフィールドで読み出される前記画素部の行を走査して前記第2のフィールドで読み出される画素の画素信号を順次リセットし、その後、前記第1のフィールドの画素の画素信号を順次読み出し、その後、前記第2のフィールドの画素の画素信号を順次読み出す第1の動作モードと、

前記第1のフィールドで読み出される前記画素部の行を走査して前記第1のフィールドで読み出される画素の画素信号を順次リセットし、その後、前記第1のフィールドの画素の画素信号を順次読み出し、その後、前記第2のフィールドで読み出される前記画素部の行を走査して前記第2のフィールドで読み出される画素の画素信号を順次リセットし、その後、前記第2のフィールドの画素の画素信号を順次読み出す第2の動作モードとを備え、

前記第2の動作モードに引き続き前記第1の動作モードが行われる際、前記第2の動作モードにおける前記第2のフィールドの画素の画素信号の読み出しの走査開始は、前記第1の動作モードにおける前記第1のフィールドの画素の画素信号のリセットの走査開始の後、かつ前記第1の動作モードにおける前記第2のフィールドの画素の画素信号のリセッ

トの走査開始の前に行われることを特徴とする固体撮像装置。

【請求項 2】

さらに、前記画素部の読み出しの行アドレスを生成する読み出し行カウンタと、

前記画素部の第1のフィールドのリセットの行アドレスを生成する第1のリセット行カウンタと、

前記画素部の前記第1のフィールドに引き続く第2のフィールドのリセットの行アドレスを生成する第2のリセット行カウンタと、

前記読み出し行カウンタ、前記第1のリセット行カウンタ及び前記第2のリセット行カウンタにより生成される行アドレスのうちの1つの行アドレスを選択するセレクタと、

前記読み出し行カウンタ、前記第1のリセット行カウンタ及び前記第2のリセット行カウンタを制御する行カウンタ制御部と、を有し、

前記行カウンタ制御部は、

前記読み出し行カウンタをカウントスタートさせるためのカウントスタートパルスを生成する第1のカウンタスタートパルス生成回路と、

垂直同期信号のタイミングでリセットし、水平同期信号のタイミングでカウントアップする水平同期信号カウンタと、

前記水平同期信号カウンタのカウンタ値に応じて、前記第1のリセット行カウンタをカウントスタートさせるためのカウントスタートパルスを生成する第2のカウンタスタートパルス生成回路と、

前記水平同期信号カウンタのカウンタ値に応じて、前記第2のリセット行カウンタをカウントスタートさせるためのカウントスタートパルスを生成する第3のカウンタスタートパルス生成回路とを有することを特徴とする請求項1記載の固体撮像装置。 10

【請求項 3】

さらに、前記画素部の読み出しの行アドレスを生成する読み出し行カウンタと、

前記画素部の第1のフィールドのリセットの行アドレスを生成する第1のリセット行カウンタと、

前記画素部の前記第1のフィールドに引き続く第2のフィールドのリセットの行アドレスを生成する第2のリセット行カウンタと、

前記読み出し行カウンタ、前記第1のリセット行カウンタ及び前記第2のリセット行カウンタにより生成される行アドレスのうちの1つの行アドレスを選択するセレクタと、 30

前記読み出し行カウンタ、前記第1のリセット行カウンタ及び前記第2のリセット行カウンタを制御する行カウンタ制御部と、を有し、

前記行カウンタ制御部は、

前記読み出し行カウンタをカウントスタートさせるためのカウントスタートパルスを生成する第1のカウンタスタートパルス生成回路と、

2つの垂直同期信号のタイミング毎にリセットし、水平同期信号のタイミングでカウントアップする第1の水平同期信号カウンタと、

2つの垂直同期信号のタイミング毎かつ前記第1の水平同期信号カウンタに対して1つの垂直同期信号分ずれてリセットし、水平同期信号のタイミングでカウントアップする第2の水平同期信号カウンタと、 40

前記第1の水平同期信号カウンタのカウンタ値に応じて、前記第1のリセット行カウンタをカウントスタートさせるためのカウントスタートパルスを生成する第2のカウンタスタートパルス生成回路と、

前記第2の水平同期信号カウンタのカウンタ値に応じて、前記第2のリセット行カウンタをカウントスタートさせるためのカウントスタートパルスを生成する第3のカウンタスタートパルス生成回路とを有することを特徴とする請求項1記載の固体撮像装置。

【請求項 4】

1つの読み出し行カウンタと2つのリセット行カウンタを有する行アドレス生成部と、

前記読み出し行カウンタと前記リセット行カウンタを制御する行カウンタ制御部と、

前記行アドレス生成部で生成された行アドレスを選択するセレクタと、 50

前記セレクタによって選択された行アドレスをデコードする行アドレスデコーダと、

前記行アドレスデコーダの出力ビットを入力してその状態を記憶する記憶部と、

前記記憶部に記憶された出力ビットに対応する行選択信号を出力する画素駆動部とを有し、

前記読み出し行カウンタは、第1のフィールド及び第2のフィールドのインテーレース読み出しの行アドレスを生成し、

前記2つのリセット行カウンタは、フィールド読み出し周期に対して短い蓄積時間と長い蓄積時間の2種類の蓄積動作の一方から他方へ切り替わる場合に、前記第1のフィールドと前記第2のフィールドが互いのフィールドの読み出し行を飛び越して行リセットするように行アドレスを生成することを特徴とする固体撮像装置。 10

#### 【請求項5】

光電変換により画素信号を生成する複数の画素が2次元行列状に配列された画素部と、前記画素部の行を選択する画素駆動部と、を有する固体撮像装置の駆動方法であって、前記画素駆動部は、

第1のフィールドで読み出される前記画素部の行を走査して前記第1のフィールドで読み出される画素の画素信号を順次リセットし、その後、第2のフィールドで読み出される前記画素部の行を走査して前記第2のフィールドで読み出される画素の画素信号を順次リセットし、その後、前記第1のフィールドの画素の画素信号を順次読み出し、その後、前記第2のフィールドの画素の画素信号を順次読み出す第1のステップと、

前記第1のフィールドで読み出される前記画素部の行を走査して前記第1のフィールドで読み出される画素の画素信号を順次リセットし、その後、前記第1のフィールドの画素の画素信号を順次読み出し、その後、前記第2のフィールドで読み出される前記画素部の行を走査して前記第2のフィールドで読み出される画素の画素信号を順次リセットし、その後、前記第2のフィールドの画素の画素信号を順次読み出す第2のステップとを備え、 20

前記第2のステップに引き続き前記第1のステップが行われる際、前記第2のステップにおける前記第2のフィールドの画素の画素信号の読み出しの走査開始は、前記第1のステップにおける前記第1のフィールドの画素の画素信号のリセットの走査開始の後、かつ前記第1のステップにおける前記第2のフィールドの画素の画素信号のリセットの走査開始の前に行われることを特徴とする固体撮像装置の駆動方法。

#### 【発明の詳細な説明】 30

##### 【技術分野】

##### 【0001】

本発明は、固体撮像装置及びその駆動方法に関する。

##### 【背景技術】

##### 【0002】

近年、数百万画素を超える固体撮像装置がデジタルカメラに使用されるようになり、高精細な静止画像を撮影することが可能となっている。動画撮影においても、滑らかな動画を撮影するために、固体撮像装置に高フレームレートで画像を読み出したいという要請がある。高フレームレートで読み出す場合、固体撮像装置の画素部の光電変換素子の、1フレームあたりの蓄積時間が短くなるので、特に暗い被写体からは充分な露光量が得られないという問題がある。限られた露光時間で、充分な露光量を得るための手段として、CCD型の撮像素子において、2つの間引きモードを用いる方法が下記の特許文献1に記載されている。特許文献1によると、2つのモードのうち一方は、蓄積時間が1垂直走査期間以内の場合に、電子シャッターを用いて細かな蓄積時間制御を行うモードである。また、他方のモードは、蓄積時間が1垂直走査期間を超える場合に、電子シャッターは使用せず蓄積時間を固定化し、被写体の明るさに応じて信号増幅手段の増幅率を変化させるモードである。 40

##### 【先行技術文献】

##### 【特許文献】

##### 【0003】

【特許文献 1】特開 2006 - 74440 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献 1 に開示された固体撮像装置では、2つの間引き読み出しモードを切り替えて行う為、切り替えたタイミングを境目にして間引きの仕方が変化する。つまり短秒（例えば 1 / 30 秒）蓄積の際は 3 行毎に 2 行を読み飛ばすのに対して、長秒（例えば 1 / 15 秒）では 3 行毎に 1 行だけを読み飛ばす。これは撮影シーンによっては視認され、違和感をもたらす。また、特許文献 1 では、蓄積時間 1 / 30 ~ 1 / 15 秒のシーンでは、回路の増幅率を変化させる。増幅率が変化すると回路のノイズも変化する。従って、特に暗い被写体を撮影している際、蓄積時間の切り替わりの前後で画質が変化する。これもシーンによって視認され、違和感をもたらす。

10

【0005】

本発明の目的は、動画撮影における画質を向上させることができる固体撮像装置及びその制御方法を提供することである。

【課題を解決するための手段】

【0006】

本発明の固体撮像装置は、光電変換により画素信号を生成する複数の画素が 2 次元行列状に配列された画素部と、前記画素部の行を選択する画素駆動部と、を有し、前記画素駆動部は、第 1 のフィールドで読み出される前記画素部の行を走査して前記第 1 のフィールドで読み出される画素の画素信号を順次リセットし、その後、第 2 のフィールドで読み出される前記画素部の行を走査して前記第 2 のフィールドで読み出される画素の画素信号を順次リセットし、その後、前記第 1 のフィールドの画素の画素信号を順次読み出し、その後、前記第 2 のフィールドの画素の画素信号を順次読み出す第 1 の動作モードと、前記第 1 のフィールドで読み出される前記画素部の行を走査して前記第 1 のフィールドで読み出される画素の画素信号を順次リセットし、その後、前記第 1 のフィールドの画素の画素信号を順次読み出し、その後、前記第 2 のフィールドで読み出される前記画素部の行を走査して前記第 2 のフィールドで読み出される画素の画素信号を順次リセットし、その後、前記第 2 のフィールドの画素の画素信号を順次読み出す第 2 の動作モードとを備え、前記第 2 の動作モードに引き続き前記第 1 の動作モードが行われる際、前記第 2 の動作モードにおける前記第 2 のフィールドの画素の画素信号の読み出しの走査開始は、前記第 1 の動作モードにおける前記第 1 のフィールドの画素の画素信号のリセットの走査開始の後、かつ前記第 1 の動作モードにおける前記第 2 のフィールドの画素の画素信号のリセットの走査開始の前に行われることを特徴とする。

20

30

【発明の効果】

【0007】

動画撮影における画質を向上させることができる。

【図面の簡単な説明】

【0008】

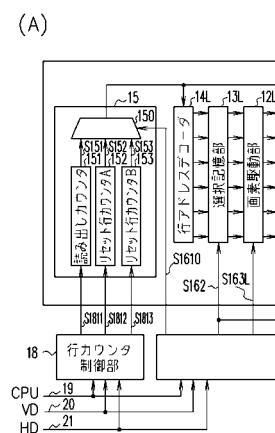

【図 1】固体撮像装置の構成例を示す図である。

40

【図 2】固体撮像装置の駆動方法の概要を示すタイミング図である。

【図 3】第 1 の実施形態による行カウンタ制御部の構成例を示すブロック図である。

【図 4】第 1 の実施形態による固体撮像装置の動作を示すタイミング図である。

【図 5】第 2 の実施形態による行カウンタ制御部の構成例を示すブロック図である。

【図 6】第 2 の実施形態による固体撮像装置の動作を示すタイミング図である。

【発明を実施するための形態】

【0009】

(第 1 の実施形態)

図 1 (A) は、本発明の第 1 の実施形態に係る固体撮像装置の構成例を示すブロック図である。固体撮像素子 1 は、画素部 1\_1 及び画素駆動部 1\_2\_L, 1\_2\_R を有する。画素部

50

11は、行と列の2次元行列状に配列された複数の画素で構成される。画素駆動部12L, 12Rは、画素を駆動する信号、すなわちフォトダイオードに蓄積された電荷を転送するための転送信号や、行列の中から特定の行の画素を選択するための行選択信号などを奇数行と偶数行のそれぞれに対して生成する。画素部11は、各々が光電変換素子(フォトダイオード)の光電変換により画素信号を生成する複数の画素を含む。各画素は、例えば光電変換素子の他に光電変換素子で蓄積された電荷に基づく電圧信号を出力する增幅部を有する、増幅型の画素が考えられる。固体撮像素子1は、奇数行と偶数行の行選択信号を保持するための選択記憶部13L, 13R、行カウント値S15に対応する1行を選択する行アドレスデコーダ14L, 14R、行アドレス生成部15、タイミング生成部16、行カウンタ制御部18を有する。行アドレス生成部15は、読み出し行カウンタ151、リセット行カウンタA(152)、リセット行カウンタB(153)及びセレクタ150を有する。セレクタ150は、3つの行カウンタ151～153が出力する行アドレスの内、1つを選択して行カウント値S15として出力する。読み出し行カウンタ151は、画素部11の読み出しの行アドレスを生成する。第1のリセット行カウンタA(152)は、画素部11の奇数フィールド(第1のフィールド)でリセットする行を示す行アドレスを生成する。第2のリセット行カウンタB(153)は、画素部11の偶数フィールド(第2のフィールド)でリセットする行を示す行アドレスを生成する。奇数フィールド及び偶数フィールドは1フレームを構成する。セレクタ150は、読み出し行カウンタ151、リセット行カウンタA(152)及びリセット行カウンタB(153)により生成される行アドレスのうちの1つの行アドレスを選択する。行カウンタ制御部18は、外部のCPUからの通信信号19、垂直同期信号20、水平同期信号21に基づき、3つの行カウンタ151～153のそれぞれに対し、カウンタスタートパルス等のカウンタ制御信号S1811～S1813を出力する。行カウンタ制御部18は、行カウンタ151～153を制御する。行アドレスデコーダ14L, 14Rは、セレクタ150によって選択された行アドレスをデコードする。選択記憶部13L, 13Rは、行アドレスデコーダ14L, 14Rの出力ビットを入力してその状態を記憶する。画素駆動部12L, 12Rは、選択記憶部13L, 13Rに記憶された出力ビットに対応する行選択信号を出力する。タイミング生成部16は、外部のCPUからの通信信号19、垂直同期信号20、水平同期信号21に基づき、3つの行カウンタ151～153のうちの1つを選択する行アドレス生成部選択信号S1610を生成する。さらに、タイミング生成部16は、選択記憶部13L, 13Rを制御する奇数行と偶数行共通の記憶部制御信号S162と、画素駆動部12L, 12Rを制御する画素駆動信号S163L, S163Rを生成する。第1の画素駆動部12Lは、セレクタ150により選択された行アドレスに対応する画素部11の奇数行を選択する。第2の画素駆動部12Rは、セレクタ150により選択された行アドレスに対応する画素部11の偶数行を選択する。第1及び第2の画素駆動部12L, 12Rは、対応する選択記憶部13L, 13Rの出力と、タイミング生成部16から供給される不図示の信号との論理和や論理積によって画素の動作を制御する構成になっている。固体撮像素子1、タイミング生成部16、行カウンタ制御部18は同一半導体上に集積されていても、されていなくてもかまわない。

## 【0010】

図1(B)は、図1(A)の選択記憶部13L, 13Rの構成例を示す回路図である。選択記憶部13L, 13Rは、それぞれ画素部11の1/2の行数の行選択記憶回路131を含んで構成される。行選択記憶回路131は、Dラッチ135と、論理積(AND)回路136と、SRラッチ137を含んで構成される。行選択記憶回路131には、行アドレスデコーダ14L, 14Rが出力するデコード信号132の1ビットと、記憶部制御信号S162である書き込み許可信号wen\_rd、SRラッチ137の消去信号clear\_sh及びセット信号wen\_shが入力される。書き込み許可信号wen\_rdは、Dラッチ135のクロック端子(CK)に入力され、データ端子(D)には、デコード信号132の内の1ビットが入力され、そのDラッチ135のQ出力信号は、画素信号を転送する行の行選択信号Lrd(133)となる。消去信号clear\_shは、SRラ

ツチ 137 のリセット端子 (R) に入力される。AND 回路 136 は、セット信号  $w_{en\_sh}$  及びデコード信号 132 の内の 1 ビットとが入力され、その論理積を、SR ラッチ 137 のセット端子 (S) に出力する。SR ラッチ 137 の Q 出力信号は、画素をリセットする行の行選択信号  $L_{sh}(134)$  となる。選択記憶部 13L, 13R でそれぞれ生成された、画素信号を転送する行の行選択信号  $L_{rd}(133)$  と、画素をリセットする行の行選択信号  $L_{sh}(134)$  は、画素駆動部 12L, 12R に入力される。これにより、行アドレスデコーダ 14L, 14R により選択された画素部 11 の対応する行の画素信号の転送、及びリセットが可能となる。

#### 【0011】

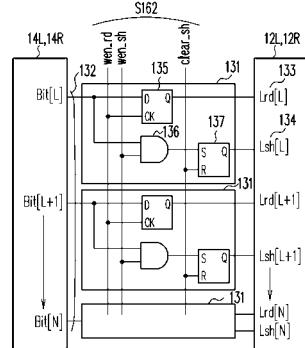

図 2 (A) 及び (B) は、図 1 (A) の行カウンタ制御部 18 と、タイミング生成部 16 と、選択記憶部 13L, 13R の動作の概要を示すタイミング図である。図 2 (A) は外部からの入力信号の入力タイミングを示す。CPU からの通信信号 19 は、垂直同期信号 (VD) 20 として入力されるパルス 201 に先立って、次の垂直同期期間 203 に実施する動作の通信信号 191 を含む。垂直同期期間 203 は、水平同期信号 (HD) 21 として入力される複数の水平同期パルス 211 により構成される。

10

#### 【0012】

図 2 (B) は、図 2 (A) の 1 水平同期期間 212 における固体撮像装置の駆動方法の概要を示すタイミング図である。1 水平同期期間 212 における動作は、ステート遷移 22 に示す、期間 221 ~ 期間 225 までの処理期間に大別される。行カウント値 S15 は、タイミング生成部 16 の行アドレス生成部選択信号 S1610 により、期間 221 では読み出し行カウンタ 151 の出力信号 S151 となり、期間 222 ではリセット行カウンタ A (152) の出力信号 S152 となる。また、行カウント値 S15 は、その他の期間では、リセット行カウンタ B (153) の出力信号 S153 となる。

20

#### 【0013】

最初に、1 水平同期期間 212 における行の画素信号の転送動作について述べる。まず、期間 221 にて、タイミング生成部 16 は、書き込み許可信号  $w_{en\_rd}$  のパルスを生成する。読み出し行カウンタ 151 の出力信号 S151 のデコード信号 132 は D ラッチ 135 にてラッチされる。ここでは、読み出し行カウンタ 151 の出力信号 S151 が L 行を選択している例を示しており、画素信号を転送する行の行選択信号  $L_{rd}(133)$  は L 行のみはハイレベルに遷移し、他の行 L+1 行、N 行はローレベルのままである。この時、行カウント値 S15 は、行アドレスデコーダ 14L, 14R 共通であり、かつ、書き込み許可信号  $w_{en\_rd}$  も、選択記憶部 13L, 13R に共通である。そのため、画素駆動部 12L, 12R では、奇数行のみからなる群の L 行と偶数行のみからなる群の L 行が選択されることとなる。期間 222 では、タイミング生成部 16 により、画素駆動部 12L が制御され、画素部 11 の奇数行のみからなる群の L 行の画素信号が、水平転送部 17 へ垂直転送される。期間 223 では、タイミング生成部 16 により、画素駆動部 12R が制御され、画素部 11 の偶数行のみからなる群の L 行の画素信号が、水平転送部 17 へ垂直転送される。期間 224 では、タイミング生成部 16 の制御により垂直転送された、奇数行と偶数行 2 つの L 行の画素信号が水平転送部 17 にて水平転送され固体撮像素子 1 の出力画素信号となる。

30

#### 【0014】

次に、1 水平同期期間 212 における行の画素信号のリセット動作について述べる。タイミング生成部 16 は、期間 221 にて、消去信号  $clear\_sh$  のパルス、期間 222 と期間 223 にて、セット信号  $w_{en\_sh}$  のパルスを生成する。ここでは、リセット行カウンタ A (152) の出力信号 S152 が L+1 行を選択し、リセット行カウンタ B (153) の出力信号 S153 が N 行を選択、1 つ前の 1 水平同期期間 212 では、L 行が選択されていたものとして例を示す。

40

#### 【0015】

期間 221 では、消去信号  $clear\_sh$  のパルスにより、全ての SR ラッチ 137 がリセットされ、選択されていた  $L_{sh}[L]$  はハイレベルからローレベルに遷移する。

50

期間 222 では、リセット行カウンタ A (152) の出力信号 S152 の選択した L+1 行をデコードしたデコード信号 132 と、セット信号 w e n \_ s h を入力とする AND 回路 136 の出力により、L s t [L+1] がローレベルからハイレベルに遷移する。期間 223 では、リセット行カウンタ B (153) の出力信号 S153 の選択した N 行をデコードしたデコード信号 132 と、セット信号 w e n \_ s h を入力とする AND 回路 136 の出力により、L s t [N] がローレベルからハイレベルに遷移する。この時、行カウント値 S15 は、行アドレスデコーダ 14L, 14R 共通であり、消去信号 c l e a r - s h、セット信号 w e n \_ s h も、選択記憶部 13L, 13R に共通である。そのため、画素駆動部 12L, 12R では、奇数行の L+1 行と偶数行の L+1 行と、奇数行の N 行と偶数行の N 行が選択されることとなる。期間 224 では、タイミング生成部 16 により、画素駆動部 12L, 12R が制御され、選択された、画素部 11 の奇数行の L+1 行と偶数行の L+1 行と、奇数行の N 行と偶数行の N 行の画素リセットを行う。以上により、1 水平同期期間 212 では、隣接する奇数行と偶数行を 1 組読み出し、2 組をリセットすることが出来る構成となっている。

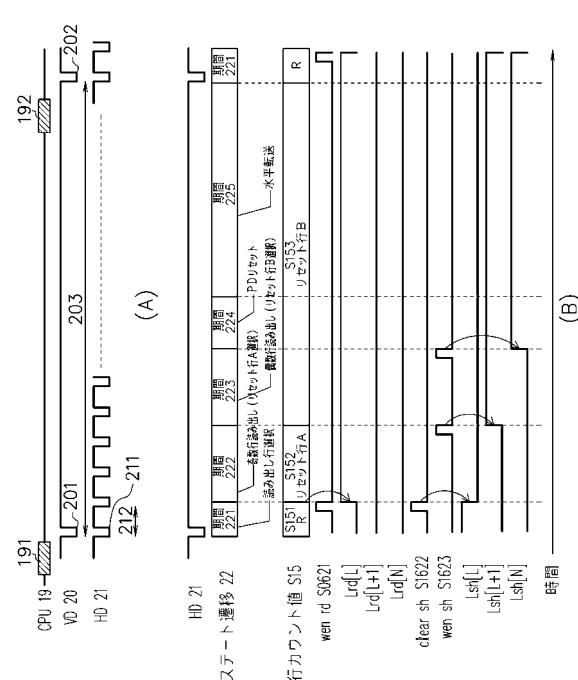

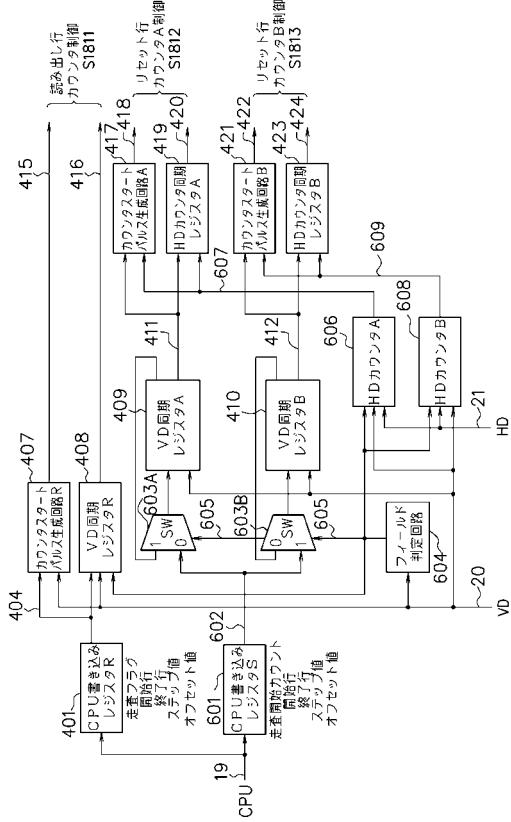

#### 【0016】

図 3 は、第 1 の実施形態による行カウンタ制御部 18 の構成例を示す図である。以下、露光時間が垂直同期期間より短い場合も長い場合も、連続的に蓄積時間を設定可能な固体撮像装置の駆動方法について述べる。CPU 書き込みレジスタ R (401) は、CPU 19 からの通信による読み出し行カウンタ 151 の制御用のレジスタであり、読み出し走査フラグ、読み出し開始行、読み出し終了行、読み出し行カウンタのカウントアップのステップ値を保持する。CPU 書き込みレジスタ A (402) は、CPU 19 からの通信によるリセット行カウンタ A (152) の制御用のレジスタであり、リセット走査開始カウント、リセット開始行、リセット終了行、リセット行カウンタ A のカウントアップのステップ値を保持する。CPU 書き込みレジスタ B (403) は、CPU 19 からの通信によるリセット行カウンタ B (153) の制御用のレジスタであり、リセット走査開始カウント、リセット開始行、リセット終了行、リセット行カウンタ B のカウントアップのステップ値を保持する。カウンタスタートパルス生成回路 R (407) は、CPU 書き込みレジスタ A (402) の読み出し走査フラグが “0” (走査オフ) でない場合は、垂直同期信号 20 のタイミングにて読み出し行カウンタ 151 のスタートパルス 415 を生成する。

#### 【0017】

VD 同期レジスタ R (408) は、垂直同期信号 20 のタイミングにて CPU 書き込みレジスタ R (401) の読み出し終了行、読み出し行カウンタのカウントアップのステップ値をコピーし保持すると共に信号線 416 により読み出し行カウンタ 151 に入力する。VD 同期レジスタ A (409) は、垂直同期信号 20 のタイミングにて、CPU 書き込みレジスタ A (402) のリセット走査開始カウント、リセット開始行、リセット終了行、リセット行カウンタ A のカウントアップのステップ値をコピーし保持する。VD 同期レジスタ B (410) は、垂直同期信号 20 のタイミングにて、CPU 書き込みレジスタ B (403) のリセット走査開始カウント、リセット開始行、リセット終了行、リセット行カウンタ B のカウントアップのステップ値をコピーし保持する。HD カウンタ 414 は、垂直同期信号 20 のタイミングにてリセットされ、水平同期信号 21 のタイミングでカウントアップするカウンタである。

#### 【0018】

水平同期信号 21 が連続して入力され、HD カウンタ 414 のカウント値が、VD 同期レジスタ A (409) のリセット走査開始カウントと一致すると、カウンタスタートパルス生成回路 A (417) と、HD カウンタ同期レジスタ A (419) は次の動作をする。まず、カウンタスタートパルス生成回路 A (417) は、リセット行カウンタ A (152) のスタートパルス 418 を生成する。HD カウンタ同期レジスタ A (419) は、VD 同期レジスタ A (409) のリセット終了行、リセット行カウンタ A のカウントアップのステップ値をコピーし保持すると共に、リセット行カウンタ A (152) にレジスタ値 420 として出力する。

10

20

30

40

50

## 【0019】

同様に、HDカウンタ414のカウント値が、VD同期レジスタB(410)のリセット走査開始カウントと一致すると、カウンタスタートパルス生成回路B(421)と、HDカウンタ同期レジスタB(423)は次の動作をする。まず、カウンタスタートパルス生成回路B(421)は、リセット行カウンタB(153)のスタートパルス422を生成する。HDカウンタ同期レジスタB(423)は、VD同期レジスタB(410)のリセット終了行、リセット行カウンタBのカウントアップのステップ値をコピーし保持すると共に、リセット行カウンタB(153)にレジスタ値424として出力する。

## 【0020】

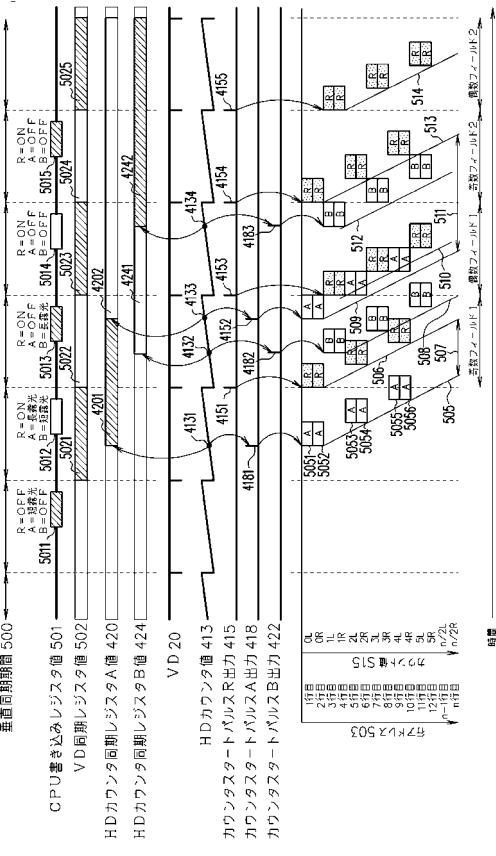

図4は、図3に示した、第1の実施形態による行カウンタ制御部18の動作と、その制御信号出力に基づく、読み出し行カウンタ151、リセット行カウンタA(152)、リセット行カウンタB(153)の動作を示すタイミング図である。図4は、垂直同期信号20により、垂直同期期間500が、期間V0から期間V6へと進む間の各部の動作を示している。CPU書き込みレジスタ値501は、CPU19からの通信により、CPU書き込みレジスタR(401)、CPU書き込みレジスタA(402)、CPU書き込みレジスタB(403)のレジスタに書き込まれるタイミングを示している。

10

## 【0021】

VD同期レジスタ値502は、垂直同期信号20に同期して、VD同期レジスタR(408)、VD同期レジスタA(409)、VD同期レジスタB(410)に、CPU書き込みレジスタ値501の内容がコピーされるタイミングを示している。HDカウンタ値(413)は、HDカウンタ414の出力であるカウンタのカウント値が、カウントアップしていく様子を示しており、そのカウント値は、垂直同期信号20に同期して0にリセットされ、水平同期信号21の入力毎に1ずつカウントアップする。HDカウンタ同期レジスタA値420は、HDカウンタ同期レジスタA(419)の出力であり、HDカウンタ値(413)を参照して、VD同期レジスタA(409)の内容がコピーされるタイミングを示している。HDカウンタ同期レジスタB値424は、HDカウンタ同期レジスタB(423)の出力であり、HDカウンタ値(413)を参照して、VD同期レジスタB(410)の内容がコピーされるタイミングを示している。カウンタスタートパルスR出力(415)は、カウンタスタートパルス生成回路R(407)のパルス出力タイミングを示している。カウンタスタートパルスA出力(418)は、カウンタスタートパルス生成回路A(417)のパルス出力タイミングを示している。カウンタスタートパルスB出力(422)は、カウンタスタートパルス生成回路B(421)のパルス出力タイミングを示している。

20

## 【0022】

行アドレス503は、画素部11の各行に対するアドレスを示しており、行アドレスデコーダ14L, 14Rの入力である行カウント値S15との対応を示している。例えば、行アドレス503の1行目は、行アドレスデコーダ14Lのカウント値0に対応し、行アドレス503の2行目は、行アドレスデコーダ14Rのカウント値0に対応することを示している。リセット走査A(505, 509)は、リセット行カウンタA(152)によるリセット走査を示している。例えばリセット走査A(505)において、リセット行5051, 5053, 5055は、行アドレスデコーダ14Lにて選択された行、リセット行5052, 5054, 5056は、行アドレスデコーダ14Rにて選択された行により構成されることを示す。同様に、リセット走査B(508, 512)は、リセット行カウンタB(153)によるリセット走査を示し、読み出し走査506, 510, 513, 514は、読み出し行カウンタ151による読み出し走査を示している。

30

## 【0023】

次に、図4で示す動作を説明する。まず、期間V1においてCPU19からの通信5011により、CPU書き込みレジスタR(401)には、読み出し走査フラグに“0”(走査オフ)を設定し、読み出し走査の禁止を指示する。CPU書き込みレジスタA(402)には、リセット走査開始カウントとしてHDカウンタ値(4131)を書き込み、リ

40

50

セット開始行には“0”、リセット終了行には“n / 2 - 1”、リセット行カウンタAのカウントアップのステップ値には“2”を書き込む。CPU書き込みレジスタB(403)には、リセット走査開始カウントとして、1垂直同期期間にカウントされるHDカウンタ値(413)より大きな値を設定することにより、実質的にリセット走査を禁止できる。

#### 【0024】

期間V2では、まず通信5011によるCPU書き込みレジスタ値501が、VD同期レジスタR(408)、VD同期レジスタA(409)、VD同期レジスタB(410)にコピーされる(5021)。次に、HDカウンタ値413が、VD同期レジスタA(409)のリセット走査開始カウントであるHDカウンタ値(4131)に一致したとき、VD同期レジスタA(409)が、HDカウンタ同期レジスタA(419)にコピーされる(4201)。さらに、カウンタスタートパルス生成回路A(417)はリセット行カウンタA(152)に対し、スタートパルス4181を生成する。スタートパルス4181を受け、リセット行カウンタA(152)は、リセット走査A(505)を開始する。リセット走査A(505)では、リセット行カウンタA(152)はHDカウンタ同期レジスタA値(4201)を参照する。リセット行カウンタA(152)は、スタートパルス4181の水平同期期間では、リセット開始行である“0”からカウントを開始し画素部11の1行目と2行目をリセットする(5051、5052)。次の水平同期期間では、リセット行カウンタA(152)はカウントアップのステップ値の“2”を加算した値を出力し画素部11の5行目と6行目をリセットする(5053、5054)。以降、水平同期期間毎にステップ値の“2”を加算しリセット終了行まで“n / 2 - 1”リセット走査を行う。

#### 【0025】

さらに、期間V2では、通信5012により、CPU書き込みレジスタR(401)には、以下の書き込みを行う。読み出し走査フラグに“1”(走査オン)、読み出し開始行には“0”、読み出し終了行には“n / 2 - 1”、読み出し行カウンタのカウントアップのステップ値には“2”を書き込む。CPU書き込みレジスタA(402)には、リセット走査開始カウントとしてHDカウンタ値(4133)を書き込み、リセット開始行には“0”、リセット終了行には“n / 2 - 1”、リセット行カウンタAのカウントアップのステップ値には“2”を書き込む。CPU書き込みレジスタB(403)には、リセット走査開始カウントとしてHDカウンタ値(4132)を書き込み、リセット開始行には“1”、リセット終了行には“n / 2”、リセット行カウンタAのカウントアップのステップ値には“2”を書き込む。

#### 【0026】

期間V3では、まず通信5012によるCPU書き込みレジスタ値501が、VD同期レジスタにコピーされる(5022)。カウンタスタートパルス生成回路R(407)は、読み出し走査フラグが“1”(走査オン)であるのでスタートパルス4151を生成する。スタートパルス4151を受け、読み出し行カウンタ151は、読み出し開始行“0”、読み出し終了行“n / 2 - 1”、読み出し行カウンタのカウントアップのステップ値“2”的設定に基づき読み出し走査(506)を開始する。読み出し走査(506)は、リセット走査A(505)にてリセットされた画素部11の奇数フィールド1を読みだす処理であり、リセット走査A(505)から読み出し走査(506)までの時間差が、露光時間507となる。

#### 【0027】

次に、HDカウンタ値413が、VD同期レジスタB(410)のリセット走査開始カウントであるHDカウンタ値(4132)に一致したとき、VD同期レジスタB(410)が、HDカウンタ同期レジスタB(424)にコピーされる(4241)。さらに、カウンタスタートパルス生成回路B(421)はリセット行カウンタB(153)に対し、スタートパルス4182を生成する。スタートパルス4182を受け、リセット行カウンタB(153)は、リセット開始行“1”、リセット終了行“n / 2”、カウントアップ

10

20

30

40

50

のステップ値“2”に基づきリセット走査B(508)を開始する。3、4、7、8、…行目の偶数フィールドの画素がリセットされる。

#### 【0028】

次に、HDカウンタ値413が、VD同期レジスタA(409)のリセット走査開始カウントであるHDカウンタ値(4133)に一致したとき、VD同期レジスタA(409)が、HDカウンタ同期レジスタA(419)にコピーされる(4202)。さらに、カウンタスタートパルス生成回路A(417)はリセット行カウンタA(152)に対し、スタートパルス4152を生成する。スタートパルス4152を受け、リセット行カウンタA(152)は、リセット走査A(509)を開始する。1、2、5、6、…行目の奇数フィールドの画素がリセットされる。

10

#### 【0029】

以降、同様に期間V4の読み出し走査510と、リセット走査B(512)の為の設定を通信5013により行い、期間V5の読み出し走査513の為の設定を通信5014により行う事を示している。読み出し走査513は、リセット走査A(509)にてリセットされた画素部11の奇数フィールド2を読み出す処理であり、リセット走査A(509)から読み出し走査513までの時間差が、露光時間511となる。ここで、露光時間507は、垂直同期期間より短い時間であるのに対し、露光時間511は、垂直同期期間より長い時間を設定できることを示しており、これは読み出し走査の対応する、リセット走査の為のCPUによる通信信号19のタイミングにより制御できる。つまり露光時間507での読み出し走査506の為の通信5012は期間V2であり、対応するリセット走査A(505)の為の通信5011は期間V1でありその差は1垂直走査期間である。これに対して、読み出し走査513の為の通信5014は期間V4であり、対応するリセット走査A(509)の為の通信5012は2垂直走査期間前の期間V2に行えば、露光時間511となる。なお、奇数フィールド2のリセット走査509は、偶数フィールド1の読み出し走査510より時間的に前に走査される。ただし、リセット走査509は、カウントアップのステップ値“2”により、偶数フィールド1の読み出し行を飛び越して走査されるため、偶数フィールド1の読み出し行は、読み出し前にリセットされることはない。

20

#### 【0030】

画素駆動部12L, 12Rは、セレクタ150により選択された行アドレスに応じて、1つの奇数行とそれに隣接する1つの偶数行との2行を1組みとして画素部11の行を選択する。短蓄積動作の露光時間507は、1垂直同期期間より短く、フィールドの周期に対して短い。画素部11は、露光時間507の短蓄積動作では、画素駆動部12L, 12Rにより選択される画素部11の奇数番目の組みの行を走査505により順次走査して奇数フィールド1の画素の画素信号をリセットする。その後、画素駆動部12L, 12Rにより選択される画素部11の奇数番目の組みの行を走査506により順次走査して奇数フィールド1の画素の画素信号を読み出す。その後、画素駆動部12L, 12Rにより選択される画素部11の偶数番目の組みの行を順次走査して偶数フィールド1の画素の画素信号をリセットする。その後、画素駆動部12L, 12Rにより選択される画素部11の偶数番目の組みの行を順次走査して偶数フィールド1の画素の画素信号を読み出す。

30

#### 【0031】

長蓄積動作の露光時間511は、1垂直同期期間より長く、フィールドの周期に対して長い。画素部11は、露光時間511の長蓄積動作では、画素駆動部12L, 12Rにより選択される画素部11の奇数番目の組みの行を順次走査して奇数フィールド2の画素の画素信号をリセットする。その後、画素駆動部12L, 12Rにより選択される画素部11の偶数番目の組みの行を順次走査して偶数フィールド2の画素の画素信号をリセットする。その後、画素駆動部12L, 12Rにより選択される画素部11の奇数番目の組みの行を順次走査して奇数フィールド2の画素の画素信号を読み出す。その後、画素駆動部12L, 12Rにより選択される画素部11の偶数番目の組みの行を順次走査して偶数フィールド2の画素の画素信号を読み出す。

40

#### 【0032】

50

露光時間 5 0 7 の短蓄積動作に引き続き露光時間 5 1 1 の長蓄積動作が行われる際には、以下の動作が行われる。短蓄積動作における偶数フィールド 1 の画素の画素信号の読み出しの走査 5 1 0 の開始は、長蓄積動作における奇数フィールド 2 の画素の画素信号のリセットの走査 5 0 9 の開始の後に行われる。かつ、短蓄積動作における偶数フィールド 1 の画素の画素信号の読み出しの走査 5 1 0 の開始は、長蓄積動作における偶数フィールド 2 の画素の画素信号のリセットの走査 5 1 2 の開始の前に行われる。

#### 【 0 0 3 3 】

読み出し行カウンタ 1 5 1 は、奇数フィールド及び偶数フィールドのインターレース読み出しの行アドレスを生成する。フィールド読み出し周期に対して短い蓄積時間と長い蓄積時間の 2 種類の蓄積動作の一方から他方へ切り替わる場合に、2 つのリセット行カウンタ 1 5 2 , 1 5 3 は、以下の動作を行う。2 つのリセット行カウンタ 1 5 2 , 1 5 3 は、奇数フィールドと偶数フィールドが互いのフィールドの読み出し行を飛び越して行リセットするように行アドレスを生成する。10

#### 【 0 0 3 4 】

図 3 に示すように、行カウンタ制御部 1 8 は、第 1 のカウンタスタートパルス生成回路 R ( 4 0 7 ) と、水平同期信号カウンタ 4 1 4 と、第 2 のカウンタスタートパルス生成回路 A ( 4 1 7 ) と、第 3 のカウンタスタートパルス生成回路 B ( 4 2 3 ) とを有する。第 1 のカウンタスタートパルス生成回路 R ( 4 0 7 ) は、読み出し行カウンタ 1 5 1 をカウントスタートさせるためのカウントスタートパルス 4 1 5 を生成する。水平同期信号カウンタ 4 1 4 は、垂直同期信号 2 0 のタイミングでリセットし、水平同期信号 2 1 のタイミングでカウントアップする。第 2 のカウンタスタートパルス生成回路 A ( 4 1 7 ) は、水平同期信号カウンタ 4 1 4 のカウンタ値に応じて、第 1 のリセット行カウンタ A ( 1 5 2 ) をカウントスタートさせるためのカウントスタートパルス 4 1 8 を生成する。第 3 のカウンタスタートパルス生成回路 B ( 4 2 3 ) は、水平同期信号カウンタ 4 1 4 のカウンタ値に応じて、第 2 のリセット行カウンタ B ( 1 5 3 ) をカウントスタートさせるためのカウントスタートパルス 4 2 2 を生成する。20

#### 【 0 0 3 5 】

##### ( 第 2 の実施形態 )

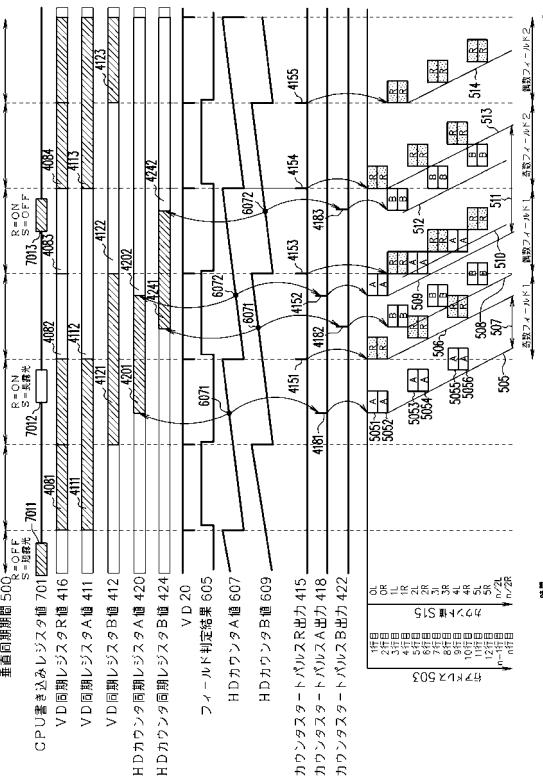

次に、本発明の第 2 の実施形態の固体撮像装置について、第 1 の実施形態と異なる点を中心に説明する。図 1 ( A ) で示した固体撮像装置の構成は本実施形態においても同じであり、かつ行カウンタ制御部 1 8 以外の動作は同じである。30

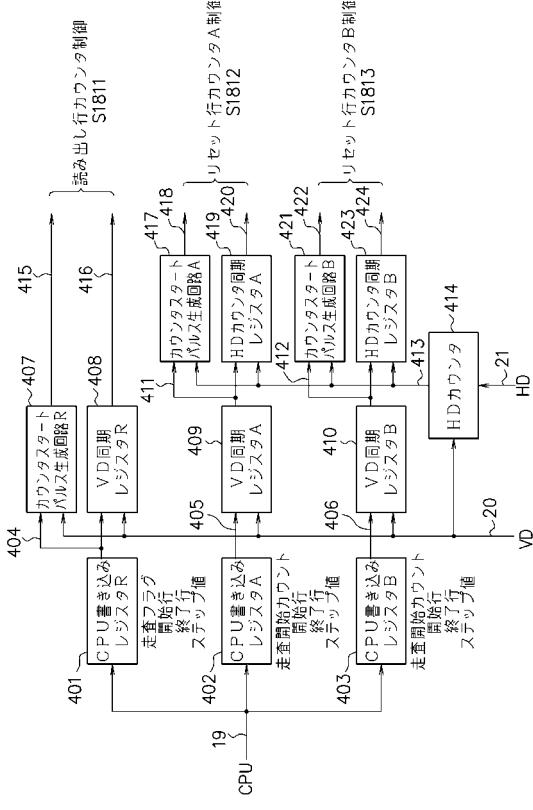

#### 【 0 0 3 6 】

図 5 は、第 2 の実施形態による行カウンタ制御部 1 8 の構成例を示す図である。以下、露光時間が垂直同期期間より短い場合も、長い場合も、外部 C P U からの通信タイミングが変わらない動作を説明する。フィールド判定回路 6 0 4 は、垂直同期信号 2 0 に同期して “ 0 ” と “ 1 ” が交互に変化するフィールド判定結果 6 0 5 を出力する。C P U 書き込みレジスタ R ( 4 0 1 ) 、カウンタスタートパルス生成回路 R ( 4 0 7 ) 、V D 同期レジスタ R ( 4 0 8 ) は、図 3 の説明と同じ動作であるが、奇数フィールドに対する偶数フィールドの読み出し開始行の差分であるオフセット値のレジスタが追加される。垂直同期信号 2 0 に同期して C P U 書き込みレジスタ R ( 4 0 1 ) から、V D 同期レジスタ R ( 4 0 8 ) に開始行と終了行をコピーする際、フィールド判定結果 6 0 5 を参照し、“ 0 ” であれば、そのままコピーし、“ 1 ” であればオフセット値を加算してコピーする。40

#### 【 0 0 3 7 】

C P U 書き込みレジスタ S ( 6 0 1 ) は、リセット行カウンタ A ( 1 5 2 ) 、リセット行カウンタ B ( 1 5 3 ) の共通の設定レジスタである。C P U 書き込みレジスタ S ( 6 0 1 ) は、リセット走査開始カウント、リセット開始行、リセット終了行、カウントアップのステップ値、および、奇数フィールドに対する偶数フィールドのリセット開始行の差分であるオフセット値を保持する。V D 同期レジスタ A ( 4 0 9 ) は、垂直同期信号 2 0 に同期して C P U 書き込みレジスタ S ( 6 0 1 ) の値をコピーする際、スイッチ 6 0 3 A により、フィールド判定結果 6 0 5 が、“ 0 ” であればコピーし、“ 1 ” であれば値を保持50

する。V D同期レジスタB(409)は、垂直同期信号20に同期してC P U書き込みレジスタS(601)の値をコピーする際、スイッチ603Bにより、フィールド判定結果605が、“1”であればコピーし、“0”であれば値を保持する。さらにV D同期レジスタB(410)には、C P U書き込みレジスタS(601)の開始行と終了行をコピーする際、オフセット値を加算してコピーする。

#### 【0038】

H DカウンタA(606)は、フィールド判定結果605が、“0”的きのみ垂直同期信号20のタイミングにてリセットされ、水平同期信号21のタイミングでカウントアップするカウンタである。H DカウンタB(608)は、フィールド判定結果605が、“1”的きのみ垂直同期信号20のタイミングにてリセットされ、水平同期信号21のタイミングでカウントアップするカウンタである。なお、H DカウンタA(606)、H DカウンタB(608)は、2垂直同期期間に入力される水平同期信号21のパルス数をカウント可能なカウンタである。カウンタスタートパルス生成回路A(417)及びH Dカウンタ同期レジスタA(419)は、図3での説明と同じ動作であるが、H DカウンタA(606)の出力信号607を参照する点が異なる。カウンタスタートパルス生成回路B(421)及びH Dカウンタ同期レジスタB(423)は、図3での説明と同じ動作であるが、H DカウンタB(608)の出力信号609を参照する点が異なる。

#### 【0039】

図6は、図5に示した、第2の実施形態による行カウンタ制御部18の動作と、その制御信号に基づく、読み出し行カウンタ151、リセット行カウンタA(152)、リセット行カウンタB(153)の動作を示すタイミング図である。フィールド判定結果605は、フィールド判定回路604の出力であり、垂直同期信号20に同期して、“0”と“1”が交互に出力される。H DカウンタA値(607)は、フィールド判定結果605が“0”的時に垂直同期信号20に同期してリセットされ、水平同期信号21の入力毎にカウントアップする。H DカウンタB値(609)は、フィールド判定結果605が“1”的時に垂直同期信号20に同期してリセットされ、水平同期信号21の入力毎にカウントアップする。カウンタスタートパルスR出力(415)、カウンタスタートパルスA出力(418)、カウンタスタートパルスB出力(422)、リセット走査A(505、509)、リセット走査B(508、512)の動作とタイミングは図3と同じである。読み出し走査506、510、513、514の動作とタイミングも図3と同じである。

#### 【0040】

次に、図6で示す動作を説明する。まず、期間V0においてC P Uからの通信7011により、C P U書き込みレジスタR(401)には、読み出し走査フラグに“0”(走査オフ)を設定し、読み出し走査の禁止を指示する。C P U書き込みレジスタS(601)には、リセット走査開始カウントにはH Dカウンタ値A(6071)、リセット開始行には“0”、リセット終了行には“n/2-1”、カウントアップのステップ値には“2”、オフセット値には“1”が書き込まれる。この時、リセット走査開始カウント値6071は、1垂直同期期間に入力される水平同期信号21のパルス数より大きな値である。

#### 【0041】

期間V1にて、垂直同期信号20に同期して、C P U書き込みレジスタR(401)の値が、V D同期レジスタR(408)にコピーされる(4081)。期間V1の、垂直同期信号20の入力タイミングでの、フィールド判定結果605は“0”であるので、スイッチ603Aにより、C P U書き込みレジスタS(601)の値が、V D同期レジスタA(409)にコピーされる(4111)。一方、V D同期レジスタB(410)は、スイッチ603Bによりコピーされず、値が保持されるが、期間V2にてフィールド判定結果605は“1”となったタイミングで、C P U書き込みレジスタS(601)の値がコピーされる(4121)。この時、V D同期レジスタB(410)の、リセット開始行とりセット終了行には、オフセット値が加算された値が保持される。

#### 【0042】

また、期間V2では、H DカウンタA値(607)が、V D同期レジスタA値(411)

) のリセット走査開始カウント 6071 に一致すると、VD 同期レジスタ A 値 (411) が、HD 同期レジスタ A (419) にコピーされる。そして、カウンタスタートパルス生成回路 A (417) は、スタートパルス 4181 を生成し、リセット走査 A (505) が行われる。さらに、期間 V2 において、通信 7012 により、CPU 書き込みレジスタ R (401) には、読み出し走査フラグに “1” (走査オン)、読み出し開始行に “0”、読み出し終了行に “n / 2 - 1”、ステップ値に “2”、オフセット値に “1” が書き込まれる。CPU 書き込みレジスタ S (601) には、リセット走査開始カウントには HD カウンタ値 A (6072)、リセット開始行には “0”、リセット終了行には “n / 2 - 1”、カウントアップのステップ値には “2”、オフセット値には “1” が書き込まれる。この時、リセット走査開始カウント値 6072 は、1 垂直同期期間に入力される水平同期信号 21 のパルス数より小さな値である。

#### 【0043】

期間 V3 では、まず通信 7012 による CPU 書き込みレジスタ 値 701 が、VD 同期レジスタ R 408 にコピーされる (4082)。この時、フィールド判定結果 605 は “0” であるので、VD 同期レジスタ A (409) にはコピーされ、VD 同期レジスタ B (410) にはコピーされない。カウンタスタートパルス生成回路 R (407) は、読み出し走査フラグが “1” (走査オン) であるのでスタートパルス 4151 を生成する。スタートパルス 4151 を受け、読み出し行カウンタ 151 は、読み出し開始行 “0”、読み出し終了行 “n / 2 - 1”、読み出し行カウンタのカウントアップのステップ値 “2” の設定に基づき読み出し走査 (506) を開始する。

#### 【0044】

次に、HD カウンタ値 B (609) が、VD 同期レジスタ B (410) のリセット走査開始カウントである HD カウンタ値 (6071) に一致したとき、VD 同期レジスタ B (410) の値が、HD カウンタ同期レジスタ B (424) にコピーされる (4241)。さらに、カウンタスタートパルス生成回路 B (421) はリセット行カウンタ B (153) に対し、スタートパルス 4182 を生成する。スタートパルス 4182 を受け、リセット行カウンタ B (153) は、オフセット値が加算された、リセット開始行 “1”、リセット終了行 “n / 2”、カウントアップのステップ値 “2” に基づきリセット走査 B (508) を開始する。

#### 【0045】

次に、HD カウンタ A 値 607 が、VD 同期レジスタ A (409) のリセット走査開始カウントである HD カウンタ値 (6072) に一致したとき、VD 同期レジスタ A (409) の値が、HD カウンタ同期レジスタ A (419) にコピーされる (4202)。さらに、カウンタスタートパルス生成回路 A (417) はリセット行カウンタ A (152) に対し、スタートパルス 4152 を生成する。スタートパルス 4152 を受け、リセット行カウンタ A (152) は、リセット走査 A (509) を開始する。

#### 【0046】

期間 V4 では、期間 V3 での通信 7012 による CPU 書き込みレジスタ 値 701 が、VD 同期レジスタ R (408) にコピーされる (4083)。この時、フィールド判定結果 605 は “1” であるので、VD 同期レジスタ R 408 の、読み出し開始行、読み出し終了行にはオフセット値 “1” が加算されて書き込まれる。同様に、VD 同期レジスタ A (409) はコピーされず、VD 同期レジスタ B (410) は、オフセット値 “1” が加算されて書き込まれる。カウンタスタートパルス生成回路 R (407) は、読み出し走査フラグが “1” (走査オン) であるのでスタートパルス 4153 を生成する。スタートパルス 4153 を受け、読み出し行カウンタ 151 は、オフセット値が加算された読み出し開始行 “1”、読み出し終了行 “n / 2” にて読み出し走査 (506) を開始する。

#### 【0047】

次に、HD カウンタ値 B (609) が、VD 同期レジスタ B (410) のリセット走査開始カウントである HD カウンタ値 (6072) に一致したとき、VD 同期レジスタ B (410) の値が、HD カウンタ同期レジスタ B (424) にコピーされる (4242)。

10

20

30

40

50

さらに、カウンタスタートパルス生成回路 B (421) はリセット行カウンタ B (153) に対し、スタートパルス 4183 を生成する。スタートパルス 4183 を受け、リセット行カウンタ B (153) は、オフセット値が加算された、リセット開始行 “1”、リセット終了行 “n/2”、カウントアップのステップ値 “2” に基づきリセット走査 B (512) を開始する。

#### 【0048】

以降、同様に期間 V5、期間 V6 の読み出し走査 513、514 と、リセット走査禁止の為の設定を通信 7013 により行う事を示している。以上により、露光時間 507、511 は第 1 の実施形態と同様に制御できている。かつ、露光時間が垂直同期期間より、長い、または短いに関わらず、奇数フィールドの読み出し期間に対して、常に 2 垂直走査期間前に通信すればよいことを示している。10

#### 【0049】

図 5 に示すように、行カウンタ制御部 18 は、第 1 のカウンタスタートパルス生成回路 R (407) と、第 2 のカウンタスタートパルス生成回路 A (417) と、第 3 のカウンタスタートパルス生成回路 B (421) とを有する。さらに、行カウンタ制御部 18 は、第 1 の水平同期信号カウンタ A (606) と、第 2 の水平同期信号カウンタ B (608) とを有する。第 1 のカウンタスタートパルス生成回路 R (407) は、読み出し行カウンタ 151 をカウントスタートさせるためのカウントスタートパルス 415 を生成する。第 1 の水平同期信号カウンタ A (606) は、2 つの垂直同期信号 20 のタイミング毎にリセットし、水平同期信号 21 のタイミングでカウントアップする。第 2 の水平同期信号カウンタ B (608) は、2 つの垂直同期信号 20 のタイミング毎かつ第 1 の水平同期信号カウンタ A (606) に対して 1 つの垂直同期信号 20 分ずれてリセットし、水平同期信号 21 のタイミングでカウントアップする。第 2 のカウンタスタートパルス生成回路 A (417) は、第 1 の水平同期信号カウンタ A (606) のカウンタ値に応じて、第 1 のリセット行カウンタ A (152) をカウントスタートさせるためのカウントスタートパルス 418 を生成する。第 3 のカウンタスタートパルス生成回路 B (421) は、第 2 の水平同期信号カウンタ B (608) のカウンタ値に応じて、第 2 のリセット行カウンタ B (153) をカウントスタートさせるためのカウントスタートパルス 421 を生成する。20

#### 【0050】

第 1 及び第 2 の実施形態の固体撮像装置は、デジタルカメラ等に使用される固体撮像装置に利用することができる。第 1 及び第 2 の実施形態によれば、1 垂直走査期間以内の短蓄積動作の蓄積時間設定要求時と、1 垂直走査期間を超える長蓄積動作の蓄積時間設定要求時とで、画素部 11 の読み出しの間引き行を切り替えない。そのため、短蓄積動作と長蓄積動作の切り替わり前後で画質の変化がない自然な動画撮影が可能となる。また、低照度時の動画撮影における画質を向上させることができ、その制御の簡略化を実現することができる。30

#### 【0051】

また、上述の各実施形態においては、画素部 11 の制御を行うために、行アドレスデコーダ 14、選択記憶部 13、画素駆動部 12 をそれぞれ 2 系統設けているが、1 系統で画素部 11 を制御しても良い。つまり、行アドレスデコーダから出力しうるデコード値の総数が、上述の実施形態で示したものの 2 倍の数になる。図 1 に示すように、選択記憶部 13 は論理回路やラッチ回路を含んで成るため、素子数が多くなる。したがって、画素の微細化が進んだ際には、図示されるように 2 系統の行アドレスデコーダ 14、選択記憶部 13、画素駆動部 12 を設けた方が、レイアウトが容易になるという利点がある。40

#### 【0052】

また、各実施形態においては、隣接する 2 行の画素を 1 組として選択する例を示したが、1 行ずつ独立に選択しても良いことはいうまでもない。また、上記では、奇数フィールド（第 1 のフィールド）とそれに引き続く偶数フィールド（第 2 のフィールド）の場合を例に説明したが、奇数フィールドと偶数フィールドの順番は逆でもよい。

#### 【0053】

50

なお、上記実施形態は、何れも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらによって本発明の技術的範囲が限定的に解釈されてはならないものである。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な形で実施することができる。

## 【符号の説明】

( 0 0 5 4 )

11 画素部、12 L, 12 R 画素駆動部、18 行カウンタ制御部、150 セレクタ、151 読み出し行カウンタ、152, 153 リセット行カウンタ

( 1 )

(B)

( 2 )

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(56)参考文献 特開2011-071927(JP,A)

特開2008-288946(JP,A)

特開2008-028608(JP,A)

特開2009-124317(JP,A)

特開2005-123758(JP,A)

特開2008-288903(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |             |   |             |

|--------|-------------|---|-------------|

| H 04 N | 5 / 3 0     | - | 5 / 3 7 8   |

| H 04 N | 5 / 2 2 2   | - | 5 / 2 5 7   |

| H 01 L | 2 1 / 3 3 9 |   |             |

| H 01 L | 2 7 / 1 4   | - | 2 7 / 1 4 8 |

| H 01 L | 2 9 / 7 6 2 |   |             |