## 【特許請求の範囲】

## 【請求項 1】

スイッチング素子と、前記スイッチング素子のスイッチング動作を制御する制御回路と、

入力される第1の直流電圧を前記スイッチング素子のスイッチング動作により交流電力に

変換して出力する変圧器と、前記交流電力から第2の直流電圧を生成して出力する出力電

圧生成回路と、前記第2の直流電圧に応じた直流電圧を生成し前記制御回路の電源電圧と

する電源回路とからなりり、前記制御回路が前記電源電圧を帰還信号として前記スイッチ

ング素子のスイッチング動作を制御するスイッチング電源装置であって、

前記制御回路は、

前記スイッチング素子にスイッチング動作をさせるためのスイッチング信号を生成する発

振器と、

前記スイッチング素子を流れる素子電流を検出し素子電流検出信号として出力する素子電

流検出回路と、

基準の電圧と前記電源電圧の差に応じた電圧値となる誤差電圧信号を生成して出力する誤

差増幅器と、

前記素子電流検出信号と前記誤差電圧信号の電圧値を比較しその比較結果に応じた比較信

号を出力する素子電流検出用比較器と、

前記素子電流検出用比較器からの比較信号を基に前記第2の直流電圧が所定の電圧となる

ように前記スイッチング信号を制御し、これを制御信号として前記スイッチング素子へ出

力するスイッチング信号制御回路と、

前記スイッチング素子がオンした瞬間から負荷状態に応じた期間、前記素子電流検出用比

較器からの比較信号を無効にし、この期間においては前記スイッチング素子がターンオフ

しないようにするブランкиングパルス信号を生成するオン時ブランкиングパルス発生回路と

を有し、前記オン時ブランкиングパルス発生回路は、前記誤差電圧信号の電圧値を基に前

記ブランкиングパルス信号を生成し、前記素子電流検出用比較器からの比較信号を無効に

する期間を負荷状態に応じて調整することを特徴とするスイッチング電源装置。

## 【請求項 2】

前記オン時ブランкиングパルス発生回路は、

ブランкиング期間生成用コンデンサと、

定電流源が接続されたミラー回路と、

前記スイッチング信号制御回路から前記スイッチング素子をターンオンさせる制御信号を

受けると、前記ブランкиング期間生成用コンデンサと前記ミラー回路を接続し前記ブラン

киング期間生成用コンデンサから電流を流出させる第1のスイッチ素子と、

前記ブランкиング期間生成用コンデンサの電位がしきい値に達するまで前記素子電流検出

用比較器からの比較信号を無効にする前記ブランкиングパルス信号を生成するブランки

ングパルス信号生成回路と

からなりり、前記誤差電圧信号の電圧値を基に前記ブランкиング期間生成用コンデンサの電

位低下速度を調整することで、前記素子電流検出用比較器からの比較信号を無効にする期

間を負荷状態に応じて調整することを特徴とする請求項1記載のスイッチング電源装置。

## 【請求項 3】

請求項2記載のスイッチング電源装置であって、

前記オン時ブランкиングパルス発生回路は、

基準電圧と前記誤差電圧信号の電圧値を比較しその比較結果に応じた比較信号を出力する

負荷検出回路と、

前記負荷検出回路からの比較信号に応じて前記ミラー回路に流れる電流値を切り替える第

2のスイッチ素子と

を有し、前記誤差電圧信号の電圧値を基に前記第2のスイッチ素子を制御して前記ミラー

回路に流れる電流値を2段階に調整することで、前記ブランкиング期間生成用コンデンサ

の電位低下速度を2段階に調整することを特徴とするスイッチング電源装置。

10

20

30

40

50

**【請求項 4】**

請求項 2 記載のスイッチング電源装置であって、

前記オン時ブランкиングパルス発生回路は、

基準電圧と前記誤差電圧信号の電圧値を比較しその比較結果に応じた比較信号を出力する

負荷検出回路と、

前記負荷検出回路からの比較信号に応じて前記ブランкиング期間生成用コンデンサの容量

値を切り替える第 3 のスイッチ素子と

を有し、前記誤差電圧信号の電圧値を基に前記第 3 のスイッチ素子を制御して前記ブラン

キング期間生成用コンデンサの容量値を 2 段階に調整することで、前記ブランкиング期間

生成用コンデンサの電位低下速度を 2 段階に調整することを特徴とするスイッチング電源

装置。

10

**【請求項 5】**

請求項 3 もしくは 4 のいずれかに記載のスイッチング電源装置であって、前記負荷検出回路の基準電圧が、最小パルス期間により素子電流値が制御されたときの誤差電圧信号の電圧値に設定されることを特徴とするスイッチング電源装置。

**【請求項 6】**

請求項 2 記載のスイッチング電源装置であって、前記オン時ブランкиングパルス発生回路は、前記定電流源から前記ミラー回路へ流れる電流値を前記誤差電圧信号の電圧値に応じて線形的に変化させることで、前記ブランкиング期間生成用コンデンサの電位低下速度を線形的に調整することを特徴とするスイッチング電源装置。

20

**【請求項 7】**

前記スイッチング素子および前記制御回路は、前記スイッチング素子の入力端子および出力端子、並びに前記帰還信号が入力される前記制御回路の入力端子を外部接続端子として、一つの半導体基板上に集積化され形成されることを特徴とする請求項 1 乃至 6 のいずれかに記載のスイッチング電源装置。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、スイッチング電源装置に関する。

**【0002】****【従来の技術】**

以下、従来のスイッチング電源装置について図面を参照しながら説明する。図 8 は、入力側と出力側とが電気的に絶縁された従来の絶縁型のスイッチング電源装置の概略を示す回路図である。

**【0003】**

図 8 に示すように、該スイッチング電源装置は、例えば商用電源等から主入力端子 101 に印加された交流電力を、ダイオードブリッジ等からなる整流器 102 により整流し且つ入力コンデンサ 103 により平滑化して直流電圧  $V_{in}$  とし、電力変換用のトランス 104 の第 1 の 1 次巻線 104a に印加する。この 1 次巻線 104a は、例えば N 型パワー MOSFET 等からなるスイッチング素子 105 に接続されており、該スイッチング電源装置は、該スイッチング素子 105 をスイッチング動作させることにより、トランス 104 の 2 次巻線 104c に磁気誘導による起電力を発生させる。そして、2 次巻線 104c に発生した起電力による交流電力を、2 次巻線 104c に接続されたダイオード 107 及び出力コンデンサ 108 により整流し且つ平滑化し、出力電圧  $V_o$  の直流電力として主出力端子 109 に接続された負荷 110 へ供給する。

40

**【0004】**

図 8 において、点線 120 は、半導体装置を表しており、スイッチング素子 105 と、該スイッチング素子 105 のスイッチング動作を制御する制御回路 106 とで構成され、スイッチング素子 105 のドレイン端子 TD とソース端子 TS、および制御回路 106 の制御端子 TC の 3 端子を有している。

50

## 【0005】

トランス104には第2の1次巻線（以下、補助巻線と称す。）104bが設けられており、2次巻線104cと同様に、スイッチング素子105によるスイッチング動作によって磁気誘導による起電力が発生する。

## 【0006】

補助巻線104bに発生した起電力による交流電力は、ダイオード112及び出力コンデンサ113からなる補助電源回路111により整流され且つ平滑化されて、補助電源電圧Vccとして出力される。

## 【0007】

この補助電源電圧Vccは、制御端子TCに入力され、制御回路106を駆動する駆動信号として用いられるとともに、補助電源電圧Vccと出力電圧Voが補助巻線104bと2次巻線104cの巻数比に比例しているので、該出力電圧Voを安定させる帰還信号としても用いられる。つまり、制御回路106は、出力電圧Voが所定の電圧で安定するよう、補助電源電圧Vccを基にスイッチング素子105のスイッチング動作を制御している。

## 【0008】

以下、制御回路106について説明する。

まず、発振器121は、スイッチング素子105をスイッチング動作（ON/OFFの繰り返し動作）させるためのスイッチング信号を生成する。すなわち、スイッチング素子105のスイッチング周波数を決定するための信号CLKと、スイッチング素子105の最大デューティーサイクルを決定するための最大デューティーサイクル信号MDCを生成して出力する。

## 【0009】

また、誤差増幅器122は、補助電源電圧Vccと基準の電圧との差に応じた電圧値となる誤差電圧信号VEAOを生成して出力する。具体的には、誤差増幅器122は、制御端子TCに入力され抵抗分圧された補助電源電圧Vccが予め設定された所定の基準電圧を下回ると、この差からなる誤差電圧信号VEAOを生成して素子電流検出用比較器124へ出力する。なお、誤差電圧信号VEAOの電圧は、補助電源電圧Vccが上昇すると低下する関係にある。

## 【0010】

素子電流検出回路123は、トランス104の1次巻線104aからスイッチング素子105へ流入する素子電流IDを検出しこの電流値に応じた電圧信号に変換して、素子電流検出信号VCLとして素子電流検出用比較器124へ出力する。

## 【0011】

素子電流検出用比較器124は、素子電流検出信号VCLと誤差電圧信号VEAOの電圧を比較し、この比較結果を基にスイッチング素子105をターンオフするための比較信号を生成して出力することで、スイッチング素子105へ流入する電流量を調整し、出力電圧Voが所定の電圧で安定するようにする。具体的には、素子電流検出用比較器124は、スイッチング素子105がターンオンし素子電流検出信号VCLの電圧が上昇して誤差電圧信号VEAOの電圧と等しくなったとき、AND回路130の一方の入力端子へハイ信号（電位がハイレベルの信号。以下、同じ。）を出力する。このハイ信号が後述するRSフリップフロップ回路126のリセット端子へ入力されることで、スイッチング素子105がターンオフする。

## 【0012】

スイッチング信号制御回路125は、セット端子に発振器121から出力されるクロック信号CLKを受け、リセット端子にAND回路130から出力される信号を受けるRSフリップフロップ回路126と、一方の入力端子に発振器121から出力される最大デューティサイクル信号MDCを受け、もう一方の入力端子にRSフリップフロップ回路126から出力される信号を受けるNAND回路127と、NAND回路127から出力される信号を受けこれを反転増幅してスイッチング素子105の制御信号を出力するゲートド

10

20

30

40

50

イバ128とから構成され、素子電流検出用比較器124からの比較信号（AND回路130からの出力信号）を基にスイッチング信号を制御することで、スイッチング素子105のオン期間を制御する。すなわち、スイッチング信号制御回路125は、誤差電圧信号V<sub>EAO</sub>の電圧と素子電流検出信号V<sub>CL</sub>の電圧が等しくなり、素子電流検出用比較器124からの比較信号がハイ信号となったとき、スイッチング素子105がターンオフするようにスイッチング信号を制御する。

#### 【0013】

このように、制御回路106は、負荷110へ供給される出力電圧V<sub>O</sub>と比例する補助電源電圧V<sub>CC</sub>を帰還信号として、スイッチング素子105のオン期間（オフ期間）を制御することで、トランス104の1次巻線104aからスイッチング素子105へ流入する素子電流I<sub>D</sub>を制御し、出力電圧V<sub>O</sub>が所定の電圧で安定するようにしている。10

#### 【0014】

また、過電流保護回路129は、誤差増幅器122から出力される誤差電圧信号V<sub>EAO</sub>の最大電圧値をクランプし、スイッチング素子105に過電流が流れるのを防止している。。

#### 【0015】

続いて、AND回路130のもう一方の入力端子に接続されるオン時ブランкиングパルス発生回路131について説明する。

このオン時ブランкиングパルス発生回路131は、スイッチング素子105がターンオンしてから一定期間（以下、この期間をブランкиング期間と称す。）、素子電流検出用比較器124からの比較信号を無効にし、容量性スパイク電流によってスイッチング素子105がターンオフしないようにするブランкиングパルス信号を出力する。具体的には、AND回路130に対し、ブランкиング期間はロー信号（電位がローの信号。以下、同じ。）となり、ブランкиング期間経過後ハイ信号となるブランкиングパルス信号を出力する。20

#### 【0016】

このようにすることにより、オン時ブランкиングパルス発生回路131は、容量性スパイク電流によってスイッチング素子105の発振が停止することを防止している。すなわち、スイッチング素子105のターンオン時には、容量性スパイク電流が発生し素子電流検出回路123から出力される素子電流検出信号V<sub>CL</sub>の電位が急峻に上昇するので、ターンオン直後に、誤差電圧信号V<sub>EAO</sub>と素子電流検出信号V<sub>CL</sub>の電位が等しくなり、素子電流検出用比較器124からハイ信号が出力される。そのため、仮に、素子電流検出用比較器124からの比較信号をRSフリップフロップ回路126のリセット端子へ直接入力するように構成すると、スイッチング素子105はターンオン直後にターンオフすることになり、スイッチング素子105の発振が停止してしまう。そこで、オン時ブランкиングパルス発生回路131とAND回路130により、容量性スパイク電流が発生している間は、素子電流検出用比較器124からの比較信号がRSフリップフロップ回路126のリセット端子に入力されないようにしている。30

#### 【0017】

以下、オン時ブランкиングパルス発生回路131の構成について詳説する。

図8において、140はブランкиング期間生成用コンデンサ、141はブランкиング期間生成用コンデンサ140の電位に応じた信号（ブランкиングパルス信号）を出力する反転器である。ブランкиング期間生成用コンデンサ140は反転器141の入力端子と制御回路106のグランド間に接続される。反転器141は、ブランкиング期間生成用コンデンサ140の電位がしきい値電圧を上回る間はロー信号を出力し、しきい値電圧に達するとハイ信号を出力する。40

#### 【0018】

また、142はP型トランジスタ、143はN型トランジスタである。両トランジスタは、ドレイン端子間で接続されるとともに、それぞれのゲート端子にゲートドライバ128からの制御信号が入力され、この制御信号に応じてその開閉が反転する反転回路となっている。つまり、ゲートドライバ128からスイッチング素子105をターンオンするため50

の制御信号（ハイ信号）を受けると、P型トランジスタ142がターンオフするとともにN型トランジスタ143がターンオンし、スイッチング素子105をターンオフするための制御信号（ロー信号）を受けると、P型トランジスタ142がターンオンするとともにN型トランジスタ143がターンオフする。

#### 【0019】

また、P型トランジスタ142とN型トランジスタ143の接続部（ドレイン端子間）にはブランкиング期間生成用コンデンサ140が接続されている。

145はスイッチングトランジスタ146、147からなるミラー回路、144はブランкиング期間生成用コンデンサ140の電位低下用の定電流源であり、スイッチングトランジスタ146には定電流源144が接続され、スイッチングトランジスタ146にはN型トランジスタ143のソース端子が接続される。

10

#### 【0020】

続いて、オン時ブランкиングパルス発生回路131の動作を説明する。

スイッチング素子105のターンオン時には、ゲートドライバ128からハイ信号が出力され、P型トランジスタ142はターンオフしN型トランジスタ143はターンオンする。そのため、ミラー効果により、定電流源144に流れる電流に比例した電流がブランкиング期間生成用コンデンサ140を介してスイッチングトランジスタ147へ流入し、ブランкиング期間生成用コンデンサ140の電位が低下していく。そして、ブランкиング期間生成用コンデンサ140の電位が反転器141のしきい値電圧に達すると、反転器141からハイ信号が出力される。

20

#### 【0021】

このスイッチング素子105がターンオンしてから（ゲートドライバ128からハイ信号が出力されてから）、ブランкиング期間生成用コンデンサ140の電位が反転器141のしきい値電圧に達するまでの期間がブランкиング期間であり、反転器141はこの間ロー信号を出力している。なお、ブランкиング期間は、ブランкиング期間生成用コンデンサ140の容量、反転器141に設定されたしきい値、定電流源144の電流値により決定する一定期間である。

#### 【0022】

その後、スイッチング素子105がターンオフすると（ゲートドライバ128からロー信号が出力されると）、P型トランジスタ142がターンオンするとともに、N型トランジスタ143がターンオフし、ブランкиング期間生成用コンデンサ140に電流が流れ込みその電位が上昇する。そして、ブランкиング期間生成用コンデンサ140の電位が反転器141のしきい値電圧に達すると、反転器141からロー信号が出力される。

30

#### 【0023】

このように、従来のスイッチング電源装置は、オン時ブランкиングパルス発生回路131が、ブランкиング期間はロー信号となり、ブランкиング期間経過後ハイ信号となるブランкиングパルス信号を生成することで、スイッチング素子がターンオンしたときに発生する容量性スパイク電流により、スイッチング素子の発振が停止しないようにしている。

#### 【0024】

続いて、当該スイッチング電源装置の負荷変動における動作について、図9に示すタイミングチャート図を用いて説明する。図9は定常負荷の状態から無負荷あるいは軽負荷の状態（出力コンデンサ108から負荷110へ流れ出る電流量が定常負荷時に比べて低下している状態）へ負荷変動するときのタイミングチャート図である。

40

#### 【0025】

図9に示すように、定常負荷の状態から無負荷あるいは軽負荷の状態へ負荷変動すると、つまり負荷供給電流Io(A)が低下すると、負荷110に対する電力供給が過剰となり出力電圧Vo(B)が若干上昇する。これを受け、補助電源回路111の生成する補助電源電圧Vcc(C)も上昇し、誤差增幅器122からの誤差電圧信号VEAO(a)の電圧が低下する。

#### 【0026】

誤差電圧信号 V E A O ( a ) の電圧が低下すると、定常負荷時よりも早いタイミングで素子電流検出信号 V C L ( c ) の電圧が誤差電圧信号 V E A O ( a ) の電圧と等しくなり、スイッチング素子 105 をターンオフする制御信号が出力される。その結果、スイッチング素子 105 のオン期間が短くなるため、スイッチング素子 105 を流れる素子電流 I D ( b ) が減少し素子電流検出信号 V C L ( c ) も低下する。

#### 【 0 0 2 7 】

このように、従来のスイッチング電源装置は、負荷 110 に供給される負荷供給電流 I o の電流値に応じて、スイッチング素子 105 に流れる素子電流 I D の電流値を制御する電流モード制御方式を探っている。

#### 【 0 0 2 8 】

続いて、無負荷時あるいは軽負荷時、および重負荷時における素子電流 I D について説明する。図 10 は無負荷時あるいは軽負荷時、および重負荷時における素子電流 I D の波形を示す図である。無負荷時あるいは軽負荷時には、スイッチング素子がオンした期間にトランジスタ 104 に蓄えられたエネルギーが、オフ期間に全て放出され、次のオン期間で素子電流が流れ出すときにトランジスタ 104 にエネルギーが蓄えられていない状態（非連続モード）となるので、図 10 に示すようにその波形は非連続モード波形 1 となる。また重負荷時には、トランジスタ 104 に蓄えられたエネルギーが、オフ期間に全て放出されず、次のオン期間で素子電流が流れ出すときにトランジスタ 104 にエネルギーが残っている状態（連続モード）となるので、図 10 に示すようにその波形は連続モード波形 2 となる。

#### 【 0 0 2 9 】

このように無負荷時あるいは軽負荷時には素子電流 I D が非連続モード波形 1 となり、重負荷時には連続モード波形 2 となるので、図 10 に示すように、重負荷時の方が容量性スパイク電流の発生期間が長くなる。そのため、ブランкиング期間 t B L K は、重負荷時においても容量性スパイク電流による誤動作を防ぐことが可能となる程度の期間とする必要がある。

#### 【 0 0 3 0 】

なお、素子電流検出信号 V C L の電圧が誤差電圧信号 V E A O の電圧と等しくなりスイッチング素子 105 にロー信号が入力されても、スイッチング素子 105 のゲート電圧がしきい値電圧に達するまでは、素子電流 I D が流れづける。

このスイッチング素子 105 にロー信号が入力されてから、スイッチング素子 105 のゲート電圧がしきい値電圧に達してターンオフするまでの時間を、素子電流検出遅れ時間と呼び、この間素子電流検出信号 V C L の電圧は誤差電圧信号 V E A O の電圧を上回っているので、素子電流検出用比較器 124 からはハイ信号が出力される。

#### 【 0 0 3 1 】

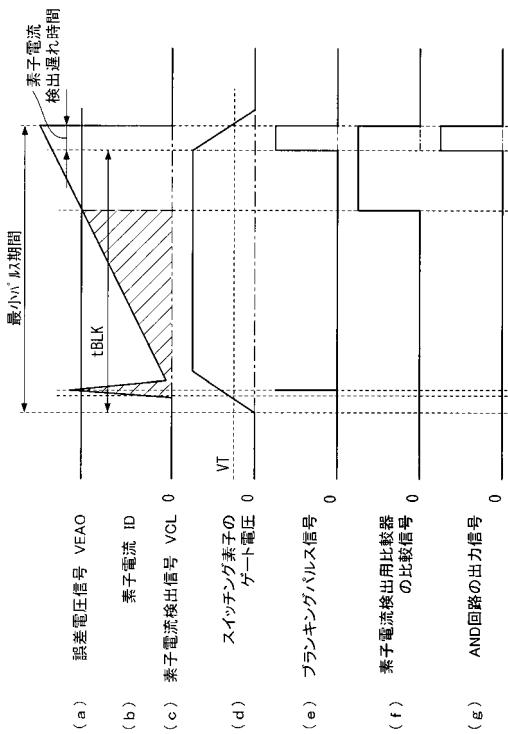

続いて、スイッチング素子がターンオンしてからターンオフするまでの動作について、図 11 に示すタイミングチャート図を用いて詳説する。

ゲートドライバ 128 からの制御信号がスイッチング素子 105 をターンオンするハイ信号となり、スイッチング素子 105 のゲート電圧 ( d ) が上昇し、しきい値電圧 V T に達するとスイッチング素子 105 はターンオンし素子電流 I D ( b ) が流れ始める。この素子電流 I D ( b ) が流れ始める瞬間にには、容量性スパイク電流が発生する。

#### 【 0 0 3 2 】

また、オン時ブランкиングパルス発生回路 131 は、スイッチング素子 105 がターンオンしてから、ブランкиング期間生成用コンデンサ 140 の容量、反転器 141 に設定されたしきい値、定電流源 144 の電流値により決定する一定期間（ブランкиング期間 t B L K ）ロー信号となり、ブランкиング期間 t B L K 経過後ハイ信号となるブランкиングパルス信号 ( e ) を生成する。

#### 【 0 0 3 3 】

そのため、容量性スパイク電流により素子電流検出信号 ( c ) の電圧が誤差電圧信号 ( a ) の電圧と等しくなり素子電流検出比較器からの比較信号 ( f ) がハイ信号となっても、オン時ブランкиングパルス発生回路 131 からのブランкиングパルス信号 ( e ) がロー信

10

20

30

40

50

号であるので、AND回路130の出力信号(g)はロー信号のままとなる。

【0034】

ブランкиング期間 $t_{BLK}$ が経過しオン時ブランкиングパルス発生回路131からのブランкиングパルス信号(e)がハイ信号となった後、素子電流検出信号VCL(c)の電圧が誤差電圧信号VEAO(a)の電圧と等しくなると、AND回路130の出力信号(g)がハイ信号となりゲートドライバ128からロー信号が出力される。上述したように、スイッチング素子105にロー信号が入力されても、スイッチング素子105のゲート電圧(d)がしきい値電圧VTに達するまではスイッチング素子105がターンオフせず、素子電流IDは流れ続ける。

【0035】

しかしながら、従来のスイッチング電源装置においては、ブランкиング期間が一定であるため、以下のような問題が生じるおそれがある。

図12は、無負荷時あるいは軽負荷時におけるスイッチング素子がターンオンしてからターンオフするまでの動作を説明するためのタイミングチャート図である。

【0036】

上述したように、ブランкиング期間 $t_{BLK}$ は、重負荷時においても容量性スパイク電流による誤動作を防ぐことが可能となる程度の期間に設定してある。しかし、無負荷時あるいは軽負荷時においては、この重負荷時に合わせたブランкиング期間 $t_{BLK}$ が長すぎ、スイッチング素子へ流入すべき電流値以上の素子電流が流れるおそれがある。

【0037】

すなわち、図12に示すように無負荷時あるいは軽負荷時においては、スイッチング素子をターンオンする制御信号(ハイ信号)が出力されてから誤差電圧信号VEAO(a)と素子電流検出信号VCL(c)の電圧が互いに等しくなるまでの時間の方が、ブランкиング期間 $t_{BLK}$ よりも短くなる場合がある。

【0038】

このような場合、誤差電圧信号VEAO(a)と素子電流検出信号VCL(c)の電圧が互いに等しくなり素子電流検出用比較器からの比較信号(f)がハイ信号となっても、ブランкиング期間 $t_{BLK}$ が経過するまでは、オン時ブランкиングパルス発生回路からのブランкиングパルス信号(e)がロー信号であるので、AND回路の出力信号(g)はロー信号となり、素子電流ID(b)が流れ続ける。

【0039】

さらに、オン時ブランкиングパルス発生回路からハイ信号が出力されても、上述したように素子電流検出遅れ時間分は素子電流ID(b)が流れ続ける。

つまり、無負荷時あるいは軽負荷時など素子電流IDの電流値が小さい範囲においては、ブランкиング期間と素子電流検出遅れ時間からなる最小パルス期間によって素子電流値が決まり、またその値は出力に対するフィードバックにより制御されるべき値よりも大きくなるため、必要以上に過大なエネルギーがトランスの2次側(出力側)へ伝達されることになり、出力電圧Voが所定の電圧以上になるという問題があった。

【0040】

一方、上記問題点を解決するために、無負荷時あるいは軽負荷時に合わせてブランкиング期間を設定すると、図13に示すような問題が生じる。すなわち、重負荷時において、容量性スパイク電流によって誤差電圧信号VEAO(a)と素子電流検出信号VCL(c)の電圧が互いに等しくなったときに、ゲートドライバからスイッチング素子をターンオフする制御信号(ロー信号)が出力されることになり、ごく短い期間しか素子電流ID(b)が流れず、そのため負荷に対して必要なエネルギーがトランスの2次側へ送られず、出力電力Voが所定の電圧以下になるという問題が生じる。

【0041】

以上のように、従来のスイッチング電源装置は、待機時等の無負荷時あるいは軽負荷時にはスイッチング素子に流れる素子電流が低減され、逆に重負荷時にはスイッチング素子に流れる素子電流が増加する電流モード制御方式を探っている。しかし、無負荷時あるいは

10

20

30

40

50

軽負荷時、重負荷時にかかわらずプランキング期間が一定であるため、無負荷時あるいは軽負荷時においては、最小パルス期間により素子電流が制御され、過大なエネルギーが2次側へ伝達され、出力電圧が上昇し過ぎることになる。そこで、例えばダミー抵抗を追加するなどの措置を取る必要があった（例えば、特許文献1参照。）。しかしながら、ダミー抵抗を追加すると、電源の効率が低下するなどの問題が発生した。

#### 【0042】

また、重負荷時においては、容量性スパイク電流によってスイッチング素子がターンオフする誤動作を起こし、素子電流の流れる期間が短いものとなり、負荷に対して必要なエネルギーが2次側へ送られず、所定の出力電力が得られなくなるおそれがあった。

#### 【0043】

#### 【特許文献1】

特開2002-112538号公報

#### 【0044】

#### 【発明が解決しようとする課題】

本発明は、上記問題を解決するために、プランキング期間を負荷状態に応じて可変とし、全負荷範囲において、正常な素子電流の制御を行えるようにすることができるスイッチング電源装置を提供することを目的とする。

#### 【0045】

#### 【課題を解決するための手段】

本発明の請求項1記載のスイッチング電源装置は、スイッチング素子と、前記スイッチング素子のスイッチング動作を制御する制御回路と、入力される第1の直流電圧を前記スイッチング素子のスイッチング動作により交流電力に変換して出力する変圧器と、前記交流電力から第2の直流電圧を生成して出力する出力電圧生成回路と、前記第2の直流電圧に応じた直流電圧を生成し前記制御回路の電源電圧とする電源回路とからなり、前記制御回路が前記電源電圧を帰還信号として前記スイッチング素子のスイッチング動作を制御するスイッチング電源装置であって、前記制御回路は、前記スイッチング素子にスイッチング動作をさせるためのスイッチング信号を生成する発振器と、前記スイッチング素子を流れる素子電流を検出し素子電流検出信号として出力する素子電流検出回路と、基準の電圧と前記電源電圧の差に応じた電圧値となる誤差電圧信号を生成して出力する誤差増幅器と、前記素子電流検出信号と前記誤差電圧信号の電圧値を比較しその比較結果に応じた比較信号を出力する素子電流検出用比較器と、前記素子電流検出用比較器からの比較信号を基に前記第2の直流電圧が所定の電圧となるように前記スイッチング信号を制御し、これを制御信号として前記スイッチング素子へ出力するスイッチング信号制御回路と、前記スイッチング素子がオンした瞬間から負荷状態に応じた期間、前記素子電流検出用比較器からの比較信号を無効にし、この期間においては前記スイッチング素子がターンオフしないようにするプランキングパルス信号を生成するオン時プランキングパルス発生回路とを有し、前記オン時プランキングパルス発生回路は、前記誤差電圧信号の電圧値を基に前記プランキングパルス信号を生成し、前記素子電流検出用比較器からの比較信号を無効にする期間を負荷状態に応じて調整することを特徴とする。

#### 【0046】

本発明の請求項2記載のスイッチング電源装置は、請求項1記載のスイッチング電源装置であって、前記オン時プランキングパルス発生回路が、プランキング期間生成用コンデンサと、定電流源が接続されたミラー回路と、前記スイッチング信号制御回路から前記スイッチング素子をターンオンさせる制御信号を受けると、前記プランキング期間生成用コンデンサと前記ミラー回路を接続し前記プランキング期間生成用コンデンサから電流を流出させる第1のスイッチ素子と、前記プランキング期間生成用コンデンサの電位がしきい値に達するまで前記素子電流検出用比較器からの比較信号を無効にする前記プランキングパルス信号を生成するプランキングパルス信号生成回路とからなり、前記誤差電圧信号の電圧値を基に前記プランキング期間生成用コンデンサの電位低下速度を調整することで、前記素子電流検出用比較器からの比較信号を無効にする期間を負荷状態に応じて調整するこ

10

20

30

40

50

とを特徴とする。

【0047】

本発明の請求項3記載のスイッチング電源装置は、請求項2記載のスイッチング電源装置であって、前記オン時プランキングパルス発生回路が、基準電圧と前記誤差電圧信号の電圧値を比較しその比較結果に応じた比較信号を出力する負荷検出回路と、前記負荷検出回路からの比較信号に応じて前記ミラー回路に流れる電流値を切り替える第2のスイッチ素子とを有し、前記誤差電圧信号の電圧値を基に前記第2のスイッチ素子を制御して前記ミラー回路に流れる電流値を2段階に調整することで、前記プランキング期間生成用コンデンサの電位低下速度を2段階に調整することを特徴とする。

【0048】

本発明の請求項4記載のスイッチング電源装置は、請求項2記載のスイッチング電源装置であって、前記オン時プランキングパルス発生回路が、基準電圧と前記誤差電圧信号の電圧値を比較しその比較結果に応じた比較信号を出力する負荷検出回路と、前記負荷検出回路からの比較信号に応じて前記プランキング期間生成用コンデンサの容量値を切り替える第3のスイッチ素子とを有し、前記誤差電圧信号の電圧値を基に前記第3のスイッチ素子を制御して前記プランキング期間生成用コンデンサの容量値を2段階に調整することで、前記プランキング期間生成用コンデンサの電位低下速度を2段階に調整することを特徴とする。

【0049】

本発明の請求項5記載のスイッチング電源装置は、請求項3もしくは4のいずれかに記載のスイッチング電源装置であって、前記負荷検出回路の基準電圧が、最小パルス期間により素子電流値が制御されたときの誤差電圧信号の電圧値に設定されることを特徴とする。

【0050】

本発明の請求項6記載のスイッチング電源装置は、請求項2記載のスイッチング電源装置であって、前記オン時プランキングパルス発生回路が、前記定電流源から前記ミラー回路へ流れる電流値を前記誤差電圧信号の電圧値に応じて線形的に変化させることで、前記プランキング期間生成用コンデンサの電位低下速度を線形的に調整することを特徴とする。

【0051】

本発明の請求項7記載のスイッチング電源装置は、請求項1乃至6のいずれかに記載のスイッチング電源装置であって、前記スイッチング素子および前記制御回路が、前記スイッチング素子の入力端子および出力端子、並びに前記帰還信号が入力される前記制御回路の入力端子を外部接続端子として、一つの半導体基板上に集積化され形成されることを特徴とする。

【0052】

以上のように、本発明によれば、プランキング期間が負荷状態に応じて可変となるので、全負荷範囲において最適なプランキング期間が得られる。

よって、待機時等の軽負荷時あるいは無負荷時にプランキング期間を短くすることが可能となるので、軽負荷時あるいは無負荷時においても、従来のスイッチング電源装置のように最小パルス期間によって素子電流量が制御されることがなくなり、帰還信号（補助電源電圧VCC）に基づいて制御できるようになり、出力電圧を所定の電圧に安定させることができるとなる。また、ダミー抵抗を用いずに済むので、電源の効率が低下することもない。

【0053】

また、重負荷時においても、スイッチング素子のターンオン時に発生する容量性スパイク電流による誤動作を防止できるので、出力電圧を所定の電圧に安定させることが可能となる。

【0054】

【発明の実施の形態】

以下、本発明の実施の形態について図面を参照しながら説明する。なお、ここで示す実施の形態はあくまでも一例であって、必ずしもこの実施の形態に限定されるものではない。

10

20

30

40

50

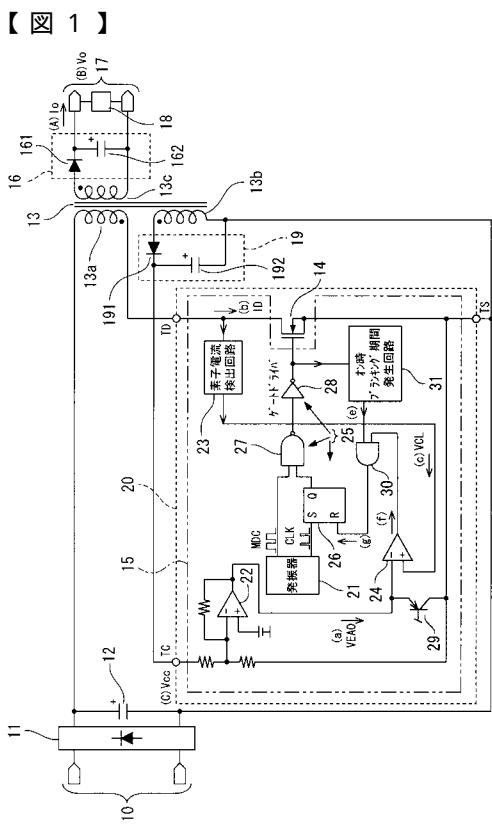

## 【0055】

図1は、本発明の実施の形態による入力側と出力側が絶縁された絶縁型のスイッチング電源装置の概略を示す回路図である。図1に示すように、該スイッチング電源装置は、例えば商用電源等から主入力端子10に印加された交流電力を整流し且つ平滑化して第1の直流電圧である直流電圧 $V_{in}$ とし、この直流電圧 $V_{in}$ を電力変換用のトランス(変圧器)13の1次側の巻線(第1の1次巻線13a。以下、単に1次巻線13aと称す。)に印加しながらスイッチング素子14によるスイッチング動作を行うことにより、2次側の巻線(2次巻線13c)に磁気誘導による起電力を発生させ、この起電力による交流電力をトランス13の2次側に設けられた出力電圧生成回路16により整流し且つ平滑化して第2の直流電圧である出力電圧 $V_o$ にまで降下して主出力端子17に出力する。

10

## 【0056】

以下、該スイッチング電源装置を詳細に説明する。

主入力端子10には、交流電力を整流するダイオードブリッジ等からなる整流器11と、この整流された信号を平滑化し直流電圧 $V_{in}$ を生成する入力コンデンサ12とがそれぞれ並列に接続されている。

## 【0057】

生成された直流電圧 $V_{in}$ は、トランス13の1次巻線13aに入力された後、例えばN型パワーMOSFET等からなるスイッチング素子14のドレイン端子TDに入力される。ここで、スイッチング素子14のソース端子TSは主入力端子10のローレベル側の端子と接続され、そのゲート端子には、該スイッチング素子14のスイッチング動作を制御する制御回路15から出力される制御信号が入力される。

20

## 【0058】

トランス13の2次巻線13cには、出力電圧生成回路16が接続されている。出力電圧生成回路16は、スイッチング素子14のスイッチング動作により2次巻線13cに発生した起電力による交流電力を整流する第1のダイオード161と、この整流された信号を平滑化する第1の出力コンデンサ162とから構成される。なお、出力電圧生成回路16は、整流し且つ平滑化する構成であればよく、これに限るものではない。

20

## 【0059】

出力電圧生成回路16に接続されている主出力端子17には、そのハイレベル側の端子とローレベル側の端子との間に負荷18が接続され、該負荷18には出力電圧生成回路16により生成された出力電圧 $V_o$ による負荷供給電流 $I_o$ が流れる。

30

## 【0060】

トランス13の1次側には第2の1次巻線(以下、補助巻線と称す。)13bが設けられており、2次巻線13cと同様に、スイッチング素子14によるスイッチング動作によって磁気誘導による起電力が発生する。補助巻線13bには制御回路15の補助電源電圧(電源電圧) $V_{cc}$ を生成する補助電源回路(電源回路)19が接続されている。補助電源回路19は、補助巻線13bに発生した起電力による交流電力を整流する第2のダイオード191と、この整流された信号を平滑化する第2の出力コンデンサ192とから構成されており、補助電源電圧 $V_{cc}$ を生成する。補助巻線13bは、補助電源電圧 $V_{cc}$ と出力電圧 $V_o$ とが比例するよう設けられている。また、補助電源回路19により生成される補助電源電圧 $V_{cc}$ は、制御回路15の制御端子TCに入力される。なお、補助電源回路19は、整流し且つ平滑化する構成であればよく、これに限るものではない。

40

## 【0061】

補助電源電圧 $V_{cc}$ は、制御端子TCに入力され、制御回路15を駆動する駆動信号として用いられるとともに、補助電源電圧 $V_{cc}$ と出力電圧 $V_o$ が補助巻線13bと2次巻線13cの巻数比に比例しているので、該出力電圧 $V_o$ を安定させる帰還信号としても用いられる。つまり、制御回路15は、出力電圧 $V_o$ が所定の電圧で安定するように、補助電源電圧 $V_{cc}$ を基にスイッチング素子14のスイッチング動作を制御している。

## 【0062】

なお、本実施の形態においては、点線20で囲まれる領域、すなわちスイッチング素子1

50

4と制御回路15を含み、スイッチング素子14のドレイン端子T D（入力端子）とソース端子T S（出力端子）並びに制御回路15の制御端子T C（帰還信号の入力端子）の少なくとも3端子で外部と接続可能な領域を、基板上形成領域と呼ぶ。基板上形成領域20は、この領域内の各素子が1つの半導体基板上に集積化されて半導体チップ（半導体装置）に形成可能であることを表している。

#### 【0063】

また、基板上形成領域20を1つの半導体チップで形成する代わりに、複数の半導体チップに分割して形成してもよい。但し、複数の半導体チップに分割する場合であっても、ドレイン端子T D、ソース端子T S、および制御端子T Cの少なくとも3端子で外部と接続可能な1つのパッケージに収容されていることが好ましい。

10

#### 【0064】

以下、制御回路15について説明する。

まず、発振器21は、スイッチング素子14をスイッチング動作（ON/OFFの繰り返し動作）させるためのスイッチング信号を生成する。すなわち、スイッチング素子14のスイッチング周波数を決定するためのクロック信号C L K（発振周波数100kHz程度）と、スイッチング素子14の最大デューティーサイクルを決定するための最大デューティーサイクル信号M D Cを生成して出力する。

#### 【0065】

また、誤差増幅器22は、補助電源電圧Vccと基準の電圧との差に応じた電圧値となる誤差電圧信号V E A Oを生成して出力する。具体的には、誤差増幅器22は、制御端子T Cに入力され抵抗分圧された補助電源電圧Vccを逆相入力端子に受け、正相入力端子に受ける予め設定された所定の基準電圧との差からなる誤差電圧信号V E A Oを生成して素子電流検出用比較器24へ出力する。ここで、誤差増幅器22の逆相入力端子は、スイッチング素子14のソース端子T Sとも抵抗を介して接続されている。なお、誤差電圧信号V E A Oの電圧は、補助電源電圧Vccが上昇すると低下する関係にある。

20

#### 【0066】

素子電流検出回路23は、トランス13の1次巻線13aからスイッチング素子14へ流入する素子電流I Dを検出しこの電流値に応じた電圧信号に変換して、素子電流検出信号V C Lとして素子電流検出用比較器24へ出力する。

30

#### 【0067】

素子電流検出用比較器24は、素子電流検出信号V C Lと誤差電圧信号V E A Oの電圧を比較し、この比較結果を基にスイッチング素子14をターンオフするための比較信号を生成して出力することで、スイッチング素子14へ流入する電流量を調整し、出力電圧V oが所定の電圧で安定するようとする。具体的には、素子電流検出用比較器24は、スイッチング素子14がターンオンし素子電流検出信号V C Lの電圧が上昇して誤差電圧信号V E A Oの電圧と等しくなったとき、AND回路30の一方の入力端子へハイ信号（電位がハイレベルの信号。以下、同じ。）を出力する。このハイ信号が後述するRSフリップフロップ回路26のリセット端子へ入力されることで、スイッチング素子14がターンオフする。

#### 【0068】

スイッチング信号制御回路25は、セット端子に発振器21から出力されるクロック信号C L Kを受け、リセット端子にAND回路30から出力される信号を受けるRSフリップフロップ回路26と、一方の入力端子に発振器21から出力される最大デューティサイクル信号M D Cを受け、もう一方の入力端子にRSフリップフロップ回路26から出力される信号を受けるNAND回路27と、NAND回路27から出力される信号を受けこれを反転増幅してスイッチング素子14の制御信号を出力するゲートドライバ28とから構成され、素子電流検出用比較器24からの比較信号（AND回路130からの出力信号）を基にスイッチング信号を制御することで、スイッチング素子14のオン期間を制御する。すなわち、スイッチング信号制御回路25は、誤差電圧信号V E A Oの電圧と素子電流検出信号V C Lの電圧が等しくなり、素子電流検出用比較器24からの比較信号がハイ信号

40

50

となったとき、スイッチング素子 14 がターンオフするようにスイッチング信号を制御する。

#### 【 0 0 6 9 】

このように、制御回路 15 は、負荷 18 へ供給される出力電圧  $V_o$  と比例する補助電源電圧  $V_{cc}$  を帰還信号として、スイッチング素子 14 のオン期間（オフ期間）を制御することで、トランジスタ 13 の 1 次巻線 13a からスイッチング素子 14 へ流入する素子電流  $I_D$  を制御し、出力電圧  $V_o$  が所定の電圧で安定するようにしている。

#### 【 0 0 7 0 】

また、誤差増幅器 22 の出力側には誤差電圧信号  $V_{EA0}$  の最大電圧値をクランプする PNP 型バイポーラトランジスタからなる過電流保護回路 29 が設けられている。このように誤差電圧信号  $V_{EA0}$  の最大電圧値をクランプすることにより、スイッチング素子 14 に流れる素子電流  $I_D$  の最大値をクランプし、スイッチング素子 14 へ過電流が流れるのを防止している。

#### 【 0 0 7 1 】

なお、制御回路 15 は、スイッチング素子 14 のドレイン端子  $T_D$  と制御回路 15 の制御端子  $T_C$ との間に接続されている。

また、該スイッチング電源装置においては、直流電圧  $V_{in}$  及び出力電圧  $V_o$  の電圧値に制限はない。

#### 【 0 0 7 2 】

また、スイッチング素子 14 に N 型パワー MOSFET を用いたが、代わりに NPN 型バイポーラトランジスタを用いてもよい。

続いて、AND 回路 30 のもう一方の入力端子に接続されるオン時ブランкиングパルス発生回路 31 について説明する。

#### 【 0 0 7 3 】

このオン時ブランкиングパルス発生回路 31 は、スイッチング素子 14 がターンオンしてから負荷状態に応じた期間（以下、この期間をブランкиング期間と称す。）、素子電流検出用比較器 24 からの比較信号を無効にし、容量性スパイク電流によってスイッチング素子 14 がターンオフしないようにするブランкиングパルス信号を出力する。具体的には、AND 回路 30 に対し、ブランкиング期間はロー信号（電位がローの信号。以下、同じ。）となり、ブランкиング期間経過後ハイ信号となるブランкиングパルス信号を出力する。

#### 【 0 0 7 4 】

本実施の形態によるオン時ブランкиングパルス発生回路は、誤差電圧信号  $V_{EA0}$  を基にブランкиングパルス信号を生成し、負荷状態に応じたブランкиング期間となるようにする点が従来のものと異なる。つまり、該スイッチング電源装置においては、従来のスイッチング電源装置において一定の期間であったブランкиング期間が、負荷状態に応じて可変となる。

#### 【 0 0 7 5 】

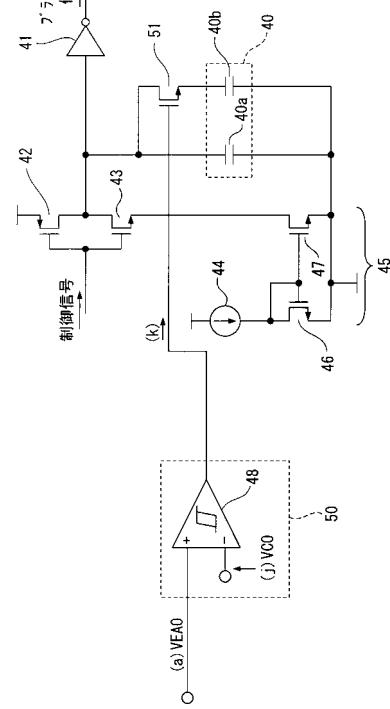

以下、本実施の形態によるオン時ブランкиングパルス発生回路の第 1 の構成例について、図 2 を用いて詳説する。

図 2において、40 はブランкиング期間生成用コンデンサ、41 はブランкиング期間生成用コンデンサ 40 の電位に応じた信号（ブランкиングパルス信号）を出力する反転器（ブランкиングパルス信号生成回路）である。ブランкиング期間生成用コンデンサ 40 は反転器 41 の入力端子と制御回路 15 のグランド間に接続される。反転器 41 は、ブランкиング期間生成用コンデンサ 40 の電位がしきい値電圧を上回る間はロー信号を出力し、しきい値電圧に達するとハイ信号を出力する。つまり、スイッチング素子 14 をターンオフする制御信号がゲートドライバ 28 から出力されてから、ブランкиング期間生成用コンデンサ 40 の電位が反転器 41 のしきい値電圧に達するまでの期間、素子電流検出量比較器 24 からの比較信号を無効とする。この期間がブランкиング期間となる。

#### 【 0 0 7 6 】

また、42 は P 型トランジスタ、43 は N 型トランジスタである。両トランジスタは、ド

10

20

30

40

50

レイン端子間で接続されるとともに、それぞれのゲート端子にゲートドライバ28からの制御信号が入力され、この制御信号に応じてその開閉が反転する反転回路となっている。つまり、ゲートドライバ28からスイッチング素子14をターンオンするための制御信号（ハイ信号）を受けると、P型トランジスタ42がターンオフするとともにN型トランジスタ（第1のスイッチ素子）43がターンオンし、スイッチング素子14をターンオフするための制御信号（ロー信号）を受けると、P型トランジスタ42がターンオンするとともにN型トランジスタ43がターンオフする。

#### 【0077】

また、P型トランジスタ42とN型トランジスタ43の接続部（ドレイン端子間）にはブランкиング期間生成用コンデンサ40が接続されている。

10

45はN型トランジスタ46、47、52からなるミラー回路、44はブランкиング期間生成用コンデンサ40の電位低下用の定電流源である。N型トランジスタ46には定電流源44が接続される。N型トランジスタ47にはN型トランジスタ43のソース端子が接続される。N型トランジスタ52にはスイッチングトランジスタ（第2のスイッチ素子）51を介してN型トランジスタ43のソース端子が接続される。

#### 【0078】

また、50は正相入力端子に誤差増幅器22からの誤差電圧信号VEAOを受け、逆相入力端子にヒステリシスを有する基準電圧VCO（VCO1、2）を受ける負荷検出用比較器48と、これを反転して出力する反転器49とからなる負荷検出回路である。スイッチングトランジスタ51はこの負荷検出回路50（反転器49）の出力信号に応じて開閉する。つまり、負荷検出回路50は、誤差電圧信号VEAOの電圧値を基にスイッチングトランジスタ51を制御することにより、N型トランジスタ43のソース端子とN型トランジスタ52の接続を制御する。

20

#### 【0079】

以上のような構成とすることにより、該オン時ブランкиングパルス発生回路においては、N型トランジスタ43がオンしており、かつスイッチングトランジスタ51がオンしているとき、定電流源44から流れる電流に比例した電流が、N型トランジスタ47とN型トランジスタ52それぞれへ流れるように、ブランкиング期間生成用コンデンサ40から電流が流出する。また、N型トランジスタ43がオンしており、かつスイッチングトランジスタ51がオフしているときには、従来と同様に、定電流源44から流れる電流に比例した電流が、N型トランジスタ47へ流れるように、ブランкиング期間生成用コンデンサ40から電流が流出する。

30

#### 【0080】

このように、該オン時ブランкиングパルス発生回路においては、誤差電圧信号VEAOを基にスイッチングトランジスタ51の開閉を制御することによりブランкиング期間生成用コンデンサ40の電流流出量、つまりブランкиング期間生成用コンデンサ40の電位低下速度が2段階に可変となり、結果、ブランкиング期間が2段階に可変となる。

40

#### 【0081】

続いて、該オン時ブランкиングパルス発生回路の動作を説明する。

負荷検出用比較器48は、入力される誤差電圧信号VEAOの電圧とヒステリシスを有する基準電圧VCOとを比較して、誤差電圧信号VEAOの電圧が基準電圧VCOよりも低い場合にはロー信号を出力し、高い場合にはハイ信号を出力する。つまり、負荷検出回路50は、誤差電圧信号VEAOの電圧と基準電圧VCOを比較し、誤差電圧信号VEAOの電圧が基準電圧VCOよりも低い場合には、ハイ信号を出力してスイッチングトランジスタ51をオンする。逆に、誤差電圧信号VEAOが基準電圧VCOよりも高い場合には、スイッチングトランジスタ51をオフする。

#### 【0082】

そこで、無負荷時や軽負荷時にはスイッチングトランジスタ51がオンし、定常負荷時や重負荷時にはオフするように基準電圧VCOを設定する。つまり、無負荷時や軽負荷時には、ブランкиング期間生成用コンデンサ40から流出する電流量を増加させてブランキン

50

グ期間が短くなるようにし、定常負荷時や重負荷時には、流出する電流量を減少させてブランкиング期間が長くなるようにする。

#### 【0083】

スイッチング素子14のターンオン時には、ゲートドライバ28からハイ信号が出力され、P型トランジスタ42はターンオフしN型トランジスタ43はターンオンする。

#### 【0084】

このとき定常負荷や重負荷の状態であれば（スイッチングトランジスタ51がオフ状態）、従来と同様、ミラー効果により、定電流源44に流れる電流に比例した電流がブランкиング期間生成用コンデンサ40からN型トランジスタ47へ流れ、ブランкиング期間生成用コンデンサ40の電位が低下していく。

10

#### 【0085】

また、無負荷や軽負荷の状態であれば（スイッチングトランジスタ51がオン状態）、定電流源44に流れる電流に比例した電流が、N型トランジスタ47とN型トランジスタ52それぞれへ流れるように、ブランкиング期間生成用コンデンサ40から電流が流出する。

#### 【0086】

そのため無負荷時や軽負荷時には、ブランкиング期間生成用コンデンサ40から流れる電流量が定常負荷時や重負荷時よりも増加するので、ブランкиング期間生成用コンデンサ40の電位低下速度も速くなる。従って、反転器41のしきい値電圧に達するまでの時間が定常負荷時や重負荷時よりも短くなり、結果、ブランкиング期間が短くなる。

20

#### 【0087】

このように、ブランкиング期間生成用コンデンサ40の電位を低下させるための電流量が、負荷状態に応じて2段階に可変となるので、ブランкиング期間も2段階に可変となる。

#### 【0088】

ブランкиング期間生成用コンデンサ40の電位が反転器41のしきい値電圧に達すると、反転器41からハイ信号が出力される。

スイッチング素子14がターンオフすると（ゲートドライバ28からロー信号が出力されると）、P型トランジスタ42がターンオンするとともに、N型トランジスタ43がターンオフし、ブランкиング期間生成用コンデンサ40に電流が流れ込みその電位が上昇する。そして、ブランкиング期間生成用コンデンサ40の電位が反転器41のしきい値電圧に達すると、反転器41からロー信号が出力される。

30

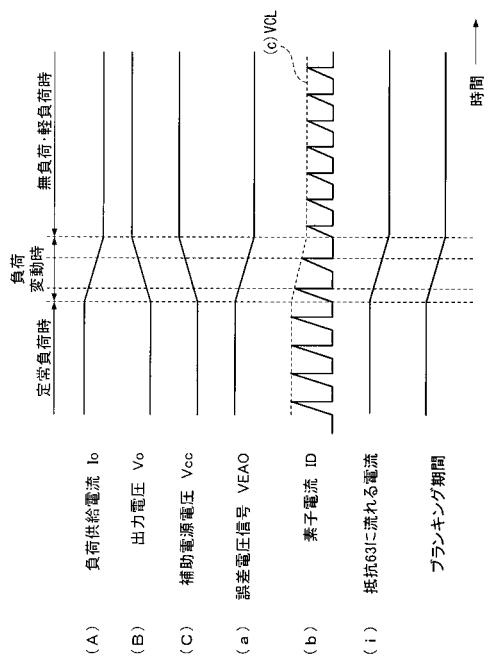

#### 【0089】

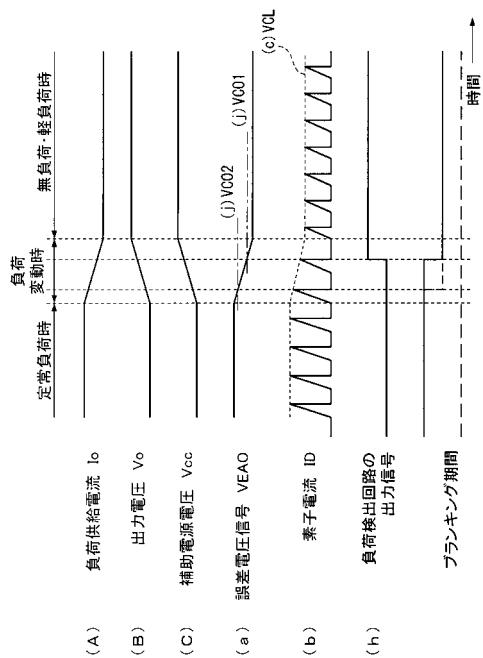

続いて、該スイッチング電源装置の負荷変動時における動作について、図3に示すタイミングチャート図を用いて説明する。図3は定常負荷の状態から無負荷あるいは軽負荷の状態（出力電圧生成回路16から負荷18へ流れ出る電流量が定常負荷時に比べて低下している状態）へ負荷変動するときのタイミングチャート図である。

#### 【0090】

図3に示すように、定常負荷の状態から無負荷あるいは軽負荷の状態へ負荷変動すると、つまり負荷供給電流Io(A)が低下すると、負荷18に対する電力供給が過剰となって出力電圧Vo(B)が若干上昇する。これを受けて、補助電源回路19の生成する補助電源電圧Vcc(C)も上昇し、制御回路15において、誤差増幅器22の逆相入力端子へ印加される電圧が上昇するため、誤差増幅器22から出力される誤差電圧信号VEAO(a)の電圧が低下する。

40

#### 【0091】

誤差電圧信号VEAO(a)の電圧が低下すると、定常負荷時よりも早いタイミングで素子電流検出信号VCL(c)の電圧が誤差電圧信号VEAO(a)の電圧と等しくなり、スイッチング素子14をターンオフする制御信号が出力される。その結果、スイッチング素子14のオン期間が短くなるため、スイッチング素子14を流れる素子電流ID(b)が減少し素子電流検出信号VCL(c)も低下する。

#### 【0092】

50

誤差電圧信号 V E A O ( a ) の電圧が低下し、負荷検出用比較器 4 8 に与えられる基準電圧 V C O 1 よりも小さくなると、負荷検出回路 5 0 の出力信号 ( h ) がハイ信号となり、スイッチングトランジスタ 5 1 がオンし、定常負荷時や重負荷時と比べてブランкиング期間生成用コンデンサ 4 0 の電位を低下させる電流量が増加するので、ブランкиング期間が定常負荷時や重負荷時と比べて短くなる。

そのため、無負荷時あるいは軽負荷時においても、従来のように最小パルス期間により素子電流 I D が制御されず ( 図 1 2 参照。 ) 、帰還信号 ( 補助電源電圧 V C C ) に基づいて制御できるようになるので、出力電圧 V o を所定の電圧で安定させることができる。

#### 【 0 0 9 3 】

なお、基準電圧 V C O には、誤差電圧信号 V E A O の電圧が変化しても直ちにブランкиング期間が変化することがないようにヒステリシス特性が与えられており、誤差電圧信号 V E A O ( a ) の電圧が基準電圧 V C O 1 よりも小さくなると、 V C O 2 となる。逆に、誤差電圧信号 V E A O ( a ) の電圧が基準電圧 V C O 2 よりも大きくなると、 V C O 1 となる。

#### 【 0 0 9 4 】

一方、無負荷あるいは軽負荷の状態から定常負荷の状態へ負荷変動する場合には、誤差電圧信号 V E A O ( a ) の電圧が上昇し、負荷検出用比較器 4 8 に与えられる基準電圧 V C O 2 よりも大きくなると、スイッチングトランジスタ 5 1 がオフし、無負荷時や軽負荷時と比べてブランкиング期間生成用コンデンサ 4 0 の電位を低下させる電流量が減少するので、ブランкиング期間が無負荷時や軽負荷時と比べて長くなる。

#### 【 0 0 9 5 】

なお、ブランкиング期間を、定常負荷時において容量性スパイク電流による誤動作を防ぐことが可能となる期間の 1 . 5 倍程度に広げると、重負荷時においても容量性スパイク電流による誤動作を防ぐことができるので、スイッチングトランジスタ 5 1 がオフしている場合のブランкиング期間をこれに合わせることが好ましい。

#### 【 0 0 9 6 】

また、スイッチングトランジスタ 5 1 がオフしている状態で軽負荷の状態としたときの素子電流値は、つまり、従来のスイッチング電源装置において最小パルス期間により素子電流が制御されたときの素子電流値は、誤差電圧信号 V E A O の電圧値が過電流保護回路 2 9 によりクランプされたときの素子電流値の 3 0 % 程度である。そこで、負荷検出用比較器の基準電圧 V C O 1 を、誤差電圧信号 V E A O の最大電圧値、つまり過電流保護回路 2 9 によりクランプされる値の 3 0 % 程度の値 ( 最小パルス期間により素子電流値が制御されたときの誤差電圧信号の電圧値程度の値 ) に設定することが好ましい。このようにすれば、無負荷時あるいは軽負荷時において、最小パルス期間により素子電流が制御されないようにすることができる。

#### 【 0 0 9 7 】

以上のように、この第 1 の構成例においては、無負荷時あるいは軽負荷時には、ミラー回路に流れる電流値を増加させて急速にブランкиング期間生成用コンデンサの電位を下げることでブランкиング期間を短くし、重負荷時には、電流値を減少させ、ブランкиング時間を長くするので、スイッチング素子に流れる素子電流を正常に制御することができる。

#### 【 0 0 9 8 】

なお、この第 1 の構成例においては、無負荷時あるいは軽負荷時にミラー回路に流れる電流を増加させるために、ブランкиング期間生成用コンデンサから電流を流出させるための N 型トランジスタを 1 つ増設したが、無論、複数個増設するようにしてもよい。

#### 【 0 0 9 9 】

また、基板上形成領域 2 0 は、1 次側、すなわち入力側の制御回路 1 5 及びスイッチング素子 1 4 のみからなるので、半導体集積回路として 1 パッケージ化又は 1 チップ化することが容易に行える。また、1 パッケージ化又は 1 チップ化すれば、部品数を削減するので、電源装置本体を小型化することができ、コストの低減もできる。

#### 【 0 1 0 0 】

10

20

30

40

50

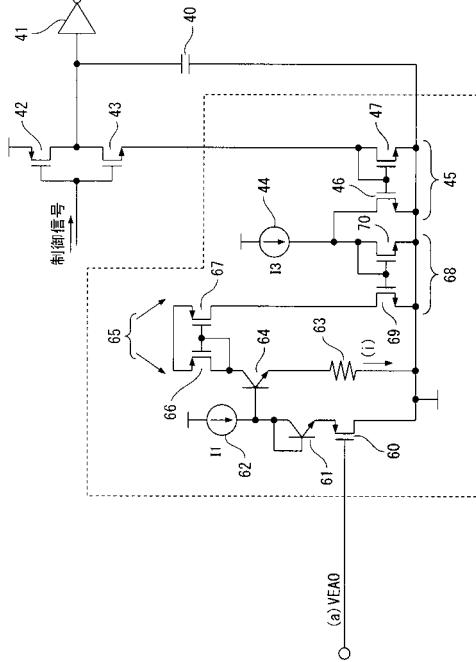

続いて、本実施の形態によるオン時プランキングパルス発生回路の第2の構成例について図4を用いて詳説する。但し、図2に基づいて説明した部材に対応する部材には同一符号を付して説明を省略する。

#### 【0101】

該オン時プランキングパルス発生回路においては、負荷状態に応じてプランキング期間生成用コンデンサの容量値が2段階に可変となる点が第1の構成例と異なる。つまり、該オン時プランキングパルス発生回路は、誤差電圧信号V<sub>EA0</sub>を基に、プランキング期間生成用コンデンサの容量を2段階に調整することにより、プランキング期間生成用コンデンサの電位低下速度を2段階に調整し、プランキング期間を2段階に調整する。

#### 【0102】

図4に示すように、該オン時プランキングパルス発生回路におけるプランキング期間生成用コンデンサ40は、第1のコンデンサ40aと第2のコンデンサ40bが、スイッチングトランジスタ（第3のスイッチ素子）51を介して並列に接続された構成となっている。スイッチングトランジスタ51は、負荷検出回路50（負荷検出用比較器48）の出力信号に応じて開閉する。つまり、負荷検出回路50は、誤差電圧信号V<sub>EA0</sub>の電圧値を基にスイッチングトランジスタ51を制御することにより、プランキング期間生成用コンデンサ40の容量値を2段階に調整する。

#### 【0103】

また、該オン時プランキングパルス発生回路の負荷検出回路50は負荷検出用比較器48のみからなる。

以上のような構成とすることにより、該オン時プランキングパルス発生回路においては、N型トランジスタ43がオンしており、かつスイッチングトランジスタ51がオンしているとき、定電流源44から流れる電流に比例した電流が、N型トランジスタ47へ流れるよう、第1のコンデンサ40aと第2のコンデンサ40bが並列接続されたプランキング期間生成用コンデンサ40から電流が流出する。また、N型トランジスタ43がオンしており、かつスイッチングトランジスタ51がオフしているときには、定電流源44から流れる電流に比例した電流が、N型トランジスタ47へ流れるよう、第1のコンデンサ40aのみからなるプランキング期間生成用コンデンサ40から電流が流出する。

#### 【0104】

このように、該オン時プランキングパルス発生回路においては、誤差電圧信号V<sub>EA0</sub>を基にスイッチングトランジスタ51の開閉を制御することによりプランキング期間生成用コンデンサ40の容量値、つまりプランキング期間生成用コンデンサ40の電位低下速度が2段階に可変となり、結果、プランキング期間が2段階に可変となる。

#### 【0105】

続いて、該オン時プランキングパルス発生回路の動作を説明する。負荷検出回路50（負荷検出用比較器48）は、負荷検出用比較器48に入力される誤差電圧信号V<sub>EA0</sub>の電圧とヒステリシスを有する基準電圧V<sub>C0</sub>とを比較して、誤差電圧信号V<sub>EA0</sub>の電圧が基準電圧V<sub>C0</sub>よりも低い場合にはロー信号を出力し、スイッチングトランジスタ51をオフする。逆に誤差電圧信号V<sub>EA0</sub>が基準電圧V<sub>C0</sub>よりも高い場合には、スイッチングトランジスタ51をオンする。

#### 【0106】

そこで、無負荷時や軽負荷時にはスイッチングトランジスタ51をオフし、定常負荷時や重負荷時にはオンするように基準電圧V<sub>C0</sub>を設定する。つまり、無負荷時や軽負荷時には、プランキング期間生成用コンデンサ40の容量値を減少させてプランキング期間が短くなるようにし、定常負荷時や重負荷時には容量値を増加させてプランキング期間が長くなるようにする。

#### 【0107】

スイッチング素子14のターンオン時には、ゲートドライバ28からハイ信号が出力され、P型トランジスタ42はターンオフしN型トランジスタ43はターンオンする。

#### 【0108】

10

20

30

40

50

このとき定常負荷や重負荷の状態であれば(スイッチングトランジスタ51がオン状態)、ミラー効果により、定電流源44に流れる電流に比例した電流が、第1のコンデンサ40aと第2のコンデンサ40bが並列に接続されたプランキング期間生成用コンデンサ40からN型トランジスタ47へ流れる。また、無負荷や軽負荷の状態であれば(スイッチングトランジスタ51がオフ状態)、ミラー効果により、定電流源44に流れる電流に比例した電流が、第1のコンデンサ40aのみからなるプランキング期間生成用コンデンサ40からN型トランジスタ47へ流れる。

#### 【0109】

そのため無負荷時や軽負荷時には、プランキング期間生成用コンデンサ40の容量値が減少するので、プランキング期間生成用コンデンサ40の電位低下速度が常負荷時や重負荷時よりも速くなる。従って、反転器41のしきい値電圧に達するまでの時間が定常負荷時や重負荷時よりも短くなり、結果、プランキング期間も短くなる。

10

#### 【0110】

このように、プランキング期間生成用コンデンサ40の容量値が、負荷状態に応じて2段階に可変となるので、プランキング期間も2段階に可変となる。

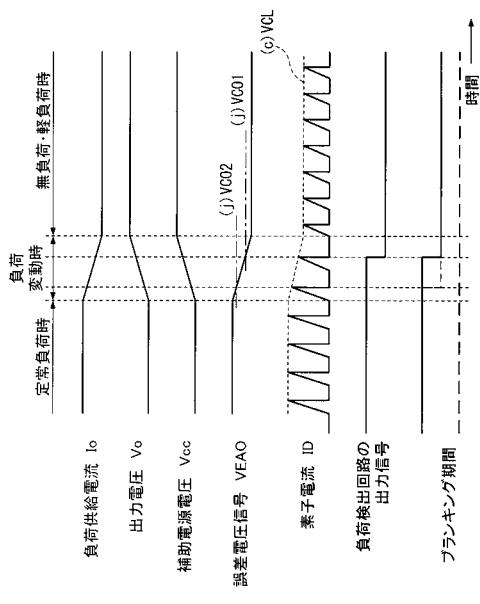

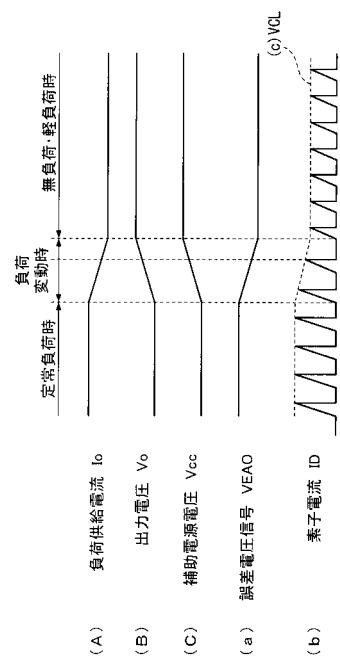

続いて、該スイッチング電源装置の負荷変動時における動作について、図5に示すタイミングチャート図を用いて説明する。図5は定常負荷の状態から無負荷あるいは軽負荷の状態(出力電圧生成回路16から負荷18へ流れ出る電流量が定常負荷時に比べて低下している状態)へ負荷変動するときのタイミングチャート図である。

20

#### 【0111】

図5に示すように、定常負荷の状態から無負荷あるいは軽負荷の状態へ負荷変動すると、つまり負荷供給電流Io(A)が低下すると、出力電圧Vo(B)が若干上昇する。これを受け、補助電源回路19の生成する補助電源電圧Vcc(C)も上昇し誤差増幅器22から出力される誤差電圧信号VEAO(a)の電圧が低下する。

#### 【0112】

誤差電圧信号VEAO(a)の電圧が低下すると、スイッチング素子14を流れる素子電流ID(b)が減少し素子電流検出信号VCL(c)も低下する。

誤差電圧信号VEAO(a)の電圧が低下し、負荷検出用比較器48に与えられる基準電圧VCO1よりも小さくなると、負荷検出回路50の出力信号(k)がロー信号となり、スイッチングトランジスタ51がオフし、定常負荷時や重負荷時と比べてプランキング期間生成用コンデンサ40の容量値が減少するので、プランキング期間が定常負荷時や重負荷時と比べて短くなる。

30

#### 【0113】

一方、無負荷あるいは軽負荷の状態から定常負荷の状態へ負荷変動する場合には、誤差電圧信号VEAO(a)の電圧が上昇し、負荷検出用比較器48に与えられる基準電圧VCO2よりも大きくなると、スイッチングトランジスタ51がオンし、無負荷時や軽負荷時と比べてプランキング期間生成用コンデンサ40の容量値が増加するので、プランキング期間が無負荷時や軽負荷時と比べて長くなる。

#### 【0114】

以上のように、この第2の構成例においては、無負荷時あるいは軽負荷時には、プランキング期間生成用コンデンサの容量値を小さくしてその電位が下がるスピードを上げることでプランキング期間を短くし、重負荷時には、容量値を大きくし、プランキング時間を長くするので、スイッチング素子に流れる素子電流を正常に制御することができる。

40

#### 【0115】

なお、この第2の構成例においては、無負荷時あるいは軽負荷時にプランキング期間生成用コンデンサの容量値を小さくするために、プランキング期間生成用コンデンサを、2つのコンデンサを並列接続して構成したが、無論2つに限るものではない。

#### 【0116】

続いて、本実施の形態によるオン時プランキングパルス発生回路の第3の構成例について、図6を用いて説明する。但し、図2に基づいて説明した部材に対応する部材には同一符

50

号を付して説明を省略する。

【0117】

該オン時プランキングパルス発生回路においては、プランキング期間生成用コンデンサからの電流流出量が負荷状態に応じて線形的に可変となる点が第1の構成例と異なる。つまり、該オン時プランキングパルス発生回路は、誤差電圧信号V<sub>EA</sub>Oの電圧値に応じて定電流源44からミラー回路45(N型トランジスタ46)へ流れ込む電流量を線形的に変化させることで、プランキング期間生成用コンデンサからの電流流出量を線形的に調整することにより、プランキング期間生成用コンデンサの電位低下速度を線形的に調整し、プランキング期間を線形的に調整する。

【0118】

図6に示すように、該オン時プランキングパルス発生回路は、定電流源44からN型トランジスタ46へ流れ込む電流を誤差電圧信号V<sub>EA</sub>Oの電圧値に応じて線形的に変動させることで、プランキング期間生成用コンデンサからの電流流出量を線形的に調整する。つまり、出力電圧から帰還されて生成される制御回路用の電源電圧V<sub>CC</sub>と基準電圧との差からなる誤差電圧信号V<sub>EA</sub>Oの電圧値に応じてP型トランジスタ60のゲート電圧が変動するので、NPN型バイポーラトランジスタ64のベース電流、すなわち抵抗63に流れる電流量もこれに応じて変動する。従って、ミラー回路65、68のミラー効果により、N型トランジスタ70に流れる電流量も誤差電圧信号V<sub>EA</sub>Oの電圧値に応じて変動し、その結果、定電流源44からN型トランジスタ46へ流れ込む電流量が変動する。

【0119】

例えば、無負荷時や軽負荷時には、誤差電圧信号V<sub>EA</sub>Oの電圧が低下する。誤差電圧信号V<sub>EA</sub>Oの電圧が低下すると、その分P型トランジスタ60のゲート電圧が低下し、P型トランジスタ60へ流れ込む電流量が増加する。定電流源62からは一定の電流が供給されるので、NPN型バイポーラトランジスタ64のベース電流は減少する。そのため、抵抗63に流れる電流量も減少する。ここで、ミラー回路65、68のミラー効果により、N型トランジスタ70に流れる電流量も減少するが、定電流源44は一定の電流を供給するため、N型トランジスタ46に流れる電流量は増加する。N型トランジスタ46に流れる電流量が増加すると、ミラー回路45のミラー効果により、プランキング期間生成用コンデンサ40からの電流流出量が増加し、プランキング期間生成用コンデンサ40の電位低下速度が速くなつてプランキング期間は短くなる。

【0120】

逆に重負荷時には、誤差電圧信号V<sub>EA</sub>Oの電圧が高くなるので、プランキング期間生成用コンデンサ40から流出する電流量が減少することになるため、プランキング期間生成用コンデンサ40の電位低下速度は遅くなり、プランキング期間は長くなる。

【0121】

このような構成とすることにより、該オン時プランキングパルス発生回路においては、誤差電圧信号V<sub>EA</sub>Oの電圧値に応じて、つまり負荷状態に応じてプランキング期間生成用コンデンサからの電流流出量が線形的に可変となり、結果、プランキング期間が負荷状態に応じて線形的に可変となる。

【0122】

続いて、該スイッチング電源装置の負荷変動時における動作について、図7に示すタイミングチャート図を用いて説明する。図7は定常負荷の状態から無負荷あるいは軽負荷の状態(出力電圧生成回路16から負荷18へ流れ出る電流量が定常負荷時に比べて低下している状態)へ負荷変動するときのタイミングチャート図である。

【0123】

図7に示すように、定常負荷の状態から無負荷あるいは軽負荷の状態へ負荷変動するとき、その負荷状態に応じて誤差電圧信号V<sub>EA</sub>Oの電圧値が低下していく、この誤差電圧信号V<sub>EA</sub>Oの電圧値に応じて抵抗63に流れる電流(i)も同様に低下していく。そのため、誤差電圧信号V<sub>EA</sub>Oの電圧値に応じてプランキング期間も短くなっていく。

【0124】

10

20

30

40

50

以上のように、この第3の構成例においては、無負荷時あるいは軽負荷時から重負荷時までのすべての負荷状態においてプランキング期間を線形的に変化させるため、素子電流を正常に制御することができる。

#### 【0125】

以上のように、本実施の形態によるスイッチング電源装置によれば、プランキング期間が負荷状態に応じて可変となるので、全負荷範囲において最適なプランキング期間が得られる。

#### 【0126】

よって、待機時等の軽負荷時あるいは無負荷時にプランキング期間を短くすることが可能となるので、軽負荷時あるいは無負荷時においても、従来のスイッチング電源装置のように最小パルス期間によって素子電流量が制御されることがなくなり、帰還信号（補助電源電圧VCC）に基づいて制御できるようになり、出力電圧を所定の電圧に安定させることが可能となる。また、ダミー抵抗を用いずに済むので、電源の効率が低下することもない。

#### 【0127】

また、重負荷時においても、スイッチング素子のターンオン時に発生する容量性スパイク電流による誤動作を防止できるので、出力電圧を所定の電圧に安定させることが可能となる。

#### 【0128】

#### 【発明の効果】

以上のように、本発明によれば、プランキング期間が負荷状態に応じて可変となるので、全負荷範囲において最適なプランキング期間が得られる。

#### 【0129】

よって、待機時等の軽負荷時あるいは無負荷時にプランキング期間を短くすることが可能となるので、軽負荷時あるいは無負荷時においても、従来のスイッチング電源装置のように最小パルス期間によって素子電流量が制御されることがなくなり、帰還信号（補助電源電圧VCC）に基づいて制御できるようになり、出力電圧を所定の電圧に安定させることができが可能となる。また、ダミー抵抗を用いずに済むので、電源の効率が低下することもない。

#### 【0130】

また、重負荷時においても、スイッチング素子のターンオン時に発生する容量性スパイク電流による誤動作を防止できるので、出力電圧を所定の電圧に安定させることができる。

#### 【図面の簡単な説明】

【図1】本発明の実施の形態によるスイッチング電源装置の概略を示す回路図

【図2】本発明の実施の形態によるスイッチング電源装置に係るオン時プランキングパルス発生回路の第1の構成例の概略を示す回路図

【図3】本発明の実施の形態によるスイッチング電源装置の負荷変動時における動作を説明するための第1のタイミングチャート図

【図4】本発明の実施の形態によるスイッチング電源装置に係るオン時プランキングパルス発生回路の第2の構成例の概略を示す回路図

【図5】本発明の実施の形態によるスイッチング電源装置の負荷変動時における動作を説明するための第2のタイミングチャート図

【図6】本発明の実施の形態によるスイッチング電源装置に係るオン時プランキングパルス発生回路の第3の構成例の概略を示す回路図

【図7】本発明の実施の形態によるスイッチング電源装置の負荷変動時における動作を説明するための第3のタイミングチャート図

【図8】従来のスイッチング電源装置の概略を示す回路図

【図9】従来のスイッチング電源装置の負荷変動時における動作を説明するためのタイミングチャート図

10

20

30

40

50

【図10】スイッチング素子に流れる素子電流の波形を示す図

【図11】従来のスイッチング電源装置におけるスイッチング素子がターンオンしてからターンオフするまでの動作を説明するためのタイミングチャート図(定常負荷時)

【図12】従来のスイッチング電源装置におけるスイッチング素子がターンオンしてからターンオフするまでの動作を説明するためのタイミングチャート図(無負荷時あるいは軽負荷時)

【図13】従来のスイッチング電源装置におけるスイッチング素子がターンオンしてからターンオフするまでの動作を説明するためのタイミングチャート図(重負荷時)

【符号の説明】

|                                                   |                       |    |

|---------------------------------------------------|-----------------------|----|

| 1 0 、 1 0 1                                       | 主入力端子                 | 10 |

| 1 1 、 1 0 2                                       | 整流器                   |    |

| 1 2 、 1 0 3                                       | 入力コンデンサ               |    |

| 1 3 、 1 0 4                                       | トランス(変圧器)             |    |

| 1 3 a 、 1 0 4 a                                   | 1次巻線(第1の1次巻線)         |    |

| 1 3 b 、 1 0 4 b                                   | 補助巻線(第2の1次巻線)         |    |

| 1 3 c 、 1 0 4 c                                   | 2次巻線                  |    |

| 1 4 、 1 0 5                                       | スイッチング素子              |    |

| 1 5 、 1 0 6                                       | 制御回路                  |    |

| 1 6                                               | 出力電圧生成回路              |    |

| 1 6 1 、 1 0 7                                     | 第1のダイオード              | 20 |

| 1 6 2 、 1 0 8                                     | 第1の出力コンデンサ            |    |

| 1 7 、 1 0 9                                       | 主出力端子                 |    |

| 1 8 、 1 1 0                                       | 負荷                    |    |

| 1 9 、 1 1 1                                       | 補助電源回路(電源回路)          |    |

| 1 9 1 、 1 1 2                                     | 第2のダイオード              |    |

| 1 9 2 、 1 1 3                                     | 第2の出力コンデンサ            |    |

| 2 0 、 1 2 0                                       | 基板上形成領域(半導体装置)        |    |

| 2 1 、 1 2 1                                       | 発振器                   |    |

| 2 2 、 1 2 2                                       | 誤差増幅器                 |    |

| 2 3 、 1 2 3                                       | 素子電流検出回路              | 30 |

| 2 4 、 1 2 4                                       | 素子電流検出用比較器            |    |

| 2 5 、 1 2 5                                       | スイッチング信号制御回路          |    |

| 2 6 、 1 2 6                                       | R S フリップフロップ回路        |    |

| 2 7 、 1 2 7                                       | N A N D 回路            |    |

| 2 8 、 1 2 8                                       | ゲートドライバ               |    |

| 2 9 、 1 2 9                                       | 過電流保護回路               |    |

| 3 0 、 1 3 0                                       | A N D 回路              |    |

| 3 1 、 1 3 1                                       | オン時ブランкиングパルス発生回路     |    |

| 4 0 、 1 4 0                                       | ブランкиング期間生成用コンデンサ     |    |

| 4 0 a                                             | 第1のコンデンサ              | 40 |

| 4 0 b                                             | 第2のコンデンサ              |    |

| 4 1 、 1 4 1                                       | 反転器(ブランкиングパルス信号生成回路) |    |

| 4 2 、 1 4 2                                       | P型トランジスタ              |    |

| 4 3 、 1 4 3                                       | N型トランジスタ(第1のスイッチ素子)   |    |

| 4 4 、 1 4 4                                       | 定電流源                  |    |

| 4 5 、 6 5 、 6 8 、 1 4 5                           | ミラー回路                 |    |

| 4 6 、 4 7 、 6 6 、 6 7 、 6 9 、 7 0 、 1 4 6 、 1 4 7 | N型トランジスタ              |    |

| 4 8                                               | 負荷検出用比較器              |    |

| 4 9                                               | 反転器                   |    |

| 5 0                                               | 負荷検出回路                | 50 |

- 5 1 スイッチングトランジスタ(第2、第3のスイッチ素子)

5 2 N型トランジスタ

6 0 N型トランジスタ

6 1、6 4 NPN型バイポーラトランジスタ

6 2 定電流源

6 3 抵抗

【図3】

【図5】

【図4】

【図6】

【図7】

【図9】

【図8】

【図10】

【図 1-1】

【図 1-3】

【図 1-2】