등록특허 10-2723101

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2024년10월28일

(11) 등록번호 10-2723101

(24) 등록일자 2024년10월24일

- (51) 국제특허분류(Int. Cl.)

*H04W 72/231* (2023.01) *H04W 72/04* (2009.01)

- (52) CPC특허분류

*H04W 72/231* (2023.01)

*H04W 72/0446* (2023.01)

- (21) 출원번호 10-2023-7030403(분할)

- (22) 출원일자(국제) 2018년11월19일

심사청구일자 2023년09월06일

- (85) 번역문제출일자 2023년09월06일

- (65) 공개번호 10-2023-0133400

- (43) 공개일자 2023년09월19일

- (62) 원출원 특허 10-2020-7017555

원출원일자(국제) 2018년11월19일

심사청구일자 2021년11월18일

- (86) 국제출원번호 PCT/CN2018/116114

- (87) 국제공개번호 WO 2019/096291

국제공개일자 2019년05월23일

- (30) 우선권주장

201711148126.3 2017년11월17일 중국(CN)

- (56) 선행기술조사문헌

3GPP R1-1713125\*

3GPP R1-1717031\*

3GPP R1-1717032\*

3GPP R1-1710773

\*는 심사관에 의하여 인용된 문헌

(73) 특허권자

지티이 코포레이션

중화인민공화국 광동 프로방스 518057, 난산 디스트릭트 샌젠, 하이테크 인더스트리얼 파크, 케지 로드 사우스, 지티이 플라자

(72) 발명자

리우 싱

중국 광동 518057 샌젠 난산 디스트릭트 하이-테크 인더스트리얼 파크 케지 로드 사우스 지티이 플라자

하오 펑

중국 광동 518057 샌젠 난산 디스트릭트 하이-테크 인더스트리얼 파크 케지 로드 사우스 지티이 플라자

(뒷면에 계속)

(74) 대리인

김태홍, 김진희

전체 청구항 수 : 총 8 항

심사관 : 이미현

(54) 발명의 명칭 정보 송신 및 수신 방법들 및 장치들

**(57) 요약**

정보 송신 및 수신 방법들 및 장치가 개시되며, 송신 방법은, 물리적 브로드캐스트 채널 상에서 제어 자원 세트의 구성 정보를 반송하는 단계 - 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보 및 주파수 도메인 위치 정보 중 적어도 하나를 단말에 표시하기 위해 사용됨 -; 및 구성 정보에 따라 제어 자원 세트를 단말에 송신하는 단계를 포함한다.

**대 표 도** - 도1

(72) 발명자

해 하이강

중국 광동 518057 켄젠 난산 디스트릭트 하이-테크

인더스트리얼 파크 케지 로드 사우스 지티이 플라

자

---

비 평

중국 광동 518057 켄젠 난산 디스트릭트 하이-테크

인더스트리얼 파크 케지 로드 사우스 지티이 플라

자

## 명세서

### 청구범위

#### 청구항 1

방법에 있어서,

물리적 브로드캐스트 채널 상에서 공통 제어 자원 세트의 구성 정보를 단말로 송신하는 단계; 및

상기 구성 정보에 따라, 상기 공통 제어 자원 세트를 제1 슬롯 및 제2 슬롯에서 상기 단말로 송신하는 단계

를 포함하고,

상기 제1 슬롯은 동기화 신호 블록(synchronization signal block; SSB)을 포함하고, 상기 제2 슬롯은 상기

SSB를 포함하지 않고, 상기 제1 슬롯과 상기 제2 슬롯 모두에서 상기 공통 제어 자원 세트에 대해 동일한 자원

맵핑 규칙이 적용되며,

상기 공통 제어 자원 세트는, 나머지 최소 시스템 정보(remaining minimum system information; RMSI)에 대한

것이고,

상기 구성 정보는 상기 공통 제어 자원 세트의 시간 도메인 위치 정보를 표시하고,

상기 공통 제어 자원 세트의 상기 시간 도메인 위치 정보는: (1) 상기 공통 제어 자원 세트가 위치되는 상기 제

1 슬롯의 정보, (2) 상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 적어도 하나의 심볼의 시작

심볼 인덱스, 및 (3) 상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 상기 적어도 하나의 심볼의

수를 포함하고,

상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 상기 적어도 하나의 심볼은 상기 제1 슬롯의 제3

심볼, 제5 심볼, 제7 심볼, 및 제9 심볼, 중 적어도 하나를 포함하는 것인, 방법.

#### 청구항 2

삭제

#### 청구항 3

삭제

#### 청구항 4

삭제

#### 청구항 5

제1항에 있어서,

상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 상기 적어도 하나의 심볼의 시작 심볼 인덱스와

상기 제1 슬롯에서 상기 SSB에 의해 점유되는 심볼의 시작 심볼 인덱스가 동일한 것인, 방법.

#### 청구항 6

방법에 있어서,

물리적 브로드캐스트 채널 상에서 공통 제어 자원 세트의 구성 정보를 단말에 의해 수신하는 단계; 및

상기 구성 정보에 따라, 제1 슬롯 및 제2 슬롯에서 상기 공통 제어 자원 세트를 상기 단말에 의해 수신하는 단

계

를 포함하고,

상기 제1 슬롯은 동기화 신호 블록(synchronization signal block; SSB)을 포함하고, 상기 제2 슬롯은 상기

SSB를 포함하지 않고, 상기 제1 슬롯과 상기 제2 슬롯 모두에서 상기 공통 제어 자원 세트에 대해 동일한 자원 맵핑 규칙이 적용되며,

상기 공통 제어 자원 세트는, 나머지 최소 시스템 정보(remaining minimum system information; RMSI)에 대한 것이고,

상기 구성 정보는 상기 공통 제어 자원 세트의 시간 도메인 위치 정보를 표시하고,

상기 공통 제어 자원 세트의 상기 시간 도메인 위치 정보는: (1) 상기 공통 제어 자원 세트가 위치되는 상기 제1 슬롯의 정보, (2) 상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 적어도 하나의 심볼의 시작 심볼 인덱스, 및 (3) 상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 상기 적어도 하나의 심볼의 수를 포함하고,

상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 상기 적어도 하나의 심볼은 상기 제1 슬롯의 제3 심볼, 제5 심볼, 제7 심볼, 및 제9 심볼, 중 적어도 하나를 포함하는 것인, 방법.

#### **청구항 7**

삭제

#### **청구항 8**

삭제

#### **청구항 9**

삭제

#### **청구항 10**

제6항에 있어서,

상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 상기 적어도 하나의 심볼의 시작 심볼 인덱스와 상기 제1 슬롯에서 상기 SSB에 의해 점유되는 심볼의 시작 심볼 인덱스가 동일한 것인, 방법.

#### **청구항 11**

프로세서를 포함하는 기지국에 있어서,

상기 프로세서는,

물리적 브로드캐스트 채널 상에서 공통 제어 자원 세트의 구성 정보를 단말로 송신하고;

상기 구성 정보에 따라, 상기 공통 제어 자원 세트를 제1 슬롯 및 제2 슬롯에서 상기 단말로 송신하도록 구성되고,

상기 제1 슬롯은 동기화 신호 블록(synchronization signal block; SSB)을 포함하고, 상기 제2 슬롯은 상기 SSB를 포함하지 않고, 상기 제1 슬롯과 상기 제2 슬롯 모두에서 상기 공통 제어 자원 세트에 대해 동일한 자원 맵핑 규칙이 적용되며,

상기 공통 제어 자원 세트는, 나머지 최소 시스템 정보(remaining minimum system information; RMSI)에 대한 것이고,

상기 구성 정보는 상기 공통 제어 자원 세트의 시간 도메인 위치 정보를 표시하고,

상기 공통 제어 자원 세트의 상기 시간 도메인 위치 정보는: (1) 상기 공통 제어 자원 세트가 위치되는 상기 제1 슬롯의 정보, (2) 상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 적어도 하나의 심볼의 시작 심볼 인덱스, 및 (3) 상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 상기 적어도 하나의 심볼의 수를 포함하고,

상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 적어도 하나의 심볼은 상기 제1 슬롯의 제3 심볼, 제5 심볼, 제7 심볼, 및 제9 심볼, 중 적어도 하나를 포함하는 것인, 기지국.

**청구항 12**

삭제

**청구항 13**

삭제

**청구항 14**

삭제

**청구항 15**

제11항에 있어서,

상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 상기 적어도 하나의 심볼의 시작 심볼 인덱스와 상기 제1 슬롯에서 상기 SSB에 의해 점유되는 심볼의 시작 심볼 인덱스가 동일한 것인, 기지국.

**청구항 16**

프로세서를 포함하는 단말에 있어서,

상기 프로세서는,

물리적 브로드캐스트 채널 상에서 공통 제어 자원 세트의 구성 정보를 수신하고;

상기 구성 정보에 따라, 제1 슬롯 및 제2 슬롯에서 상기 공통 제어 자원 세트를 수신하도록 구성되고,

상기 제1 슬롯은 동기화 신호 블록(synchronization signal block; SSB)을 포함하고, 상기 제2 슬롯은 상기 SSB를 포함하지 않고, 상기 제1 슬롯과 상기 제2 슬롯 모두에서 상기 공통 제어 자원 세트에 대해 동일한 자원 맵핑 규칙이 적용되며,

상기 공통 제어 자원 세트는, 나머지 최소 시스템 정보(remaining minimum system information; RMSI)에 대한 것이고,

상기 구성 정보는 상기 공통 제어 자원 세트의 시간 도메인 위치 정보를 표시하고,

상기 공통 제어 자원 세트의 상기 시간 도메인 위치 정보는: (1) 상기 공통 제어 자원 세트가 위치되는 상기 제1 슬롯의 정보, (2) 상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 적어도 하나의 심볼의 시작 심볼 인덱스, 및 (3) 상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 상기 적어도 하나의 심볼의 수를 포함하고,

상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 상기 적어도 하나의 심볼은 상기 제1 슬롯의 제3 심볼, 제5 심볼, 제7 심볼, 및 제9 심볼, 중 적어도 하나를 포함하는 것인, 단말.

**청구항 17**

삭제

**청구항 18**

삭제

**청구항 19**

삭제

**청구항 20**

제16항에 있어서,

상기 제1 슬롯에서 상기 공통 제어 자원 세트에 의해 점유되는 상기 적어도 하나의 심볼의 시작 심볼 인덱스와

상기 제1 슬롯에서 상기 SSB에 의해 점유되는 심볼의 시작 심볼 인덱스가 동일한 것인, 단말.

## 발명의 설명

### 기술 분야

- [0001] 관련 출원들에 대한 상호 참조

- [0002] 본 출원은 2017년 11월 17일에 중국 특허청에 출원된 중국 특허 출원 제201711148126.3호의 우선권을 주장하고, 상기 출원의 전체 내용은 본 명세서에 참조로 통합된다.

- [0003] 기술분야

- [0004] 본 출원은 통신 분야, 예를 들어, 정보 송신 및 수신 방법들 및 장치들에 관한 것이다.

## 배경 기술

- [0005] 차세대 무선 통신 시스템(NR(New Radio))에서, 시스템 정보는 최소 시스템 정보(최소 SI) 및 다른 시스템 정보(다른 SI)로 분할된다. 최소 시스템 정보는 물리적 브로드캐스트 채널(Physical Broadcast Channel, PBCH) 상에서 반송되는 "마스터 시스템 정보(Master Information Block, MIB)", 및 물리적 다운링크 공유 채널 상에서 반송되는 "나머지 최소 시스템 정보(나머지 최소 SI, RMSI)"로 분할되고; 마스터 시스템 정보는 셀의 기본 시스템 파라미터들을 제공하기 위해 사용되고, 나머지 최소 시스템 정보는 초기 액세스와 관련된 구성 정보, 예를 들어, 초기 액세스 요청의 송신 구성 및 초기 액세스 응답의 메시지 수신 구성을 제공하기 위해 사용된다. 브로드캐스트될 필요가 있는 다른 시스템 정보는 다른 시스템 정보로 지칭된다.

- [0006] RMSI는 물리적 다운링크 제어 채널(Physical Downlink Control Channel, PDCCH)에 의해 스케줄링되고, 물리적 다운링크 공유 채널(Physical Downlink Shared Channel, PDSCH) 상에서 반송된다. RMSI 스케줄링 정보가 위치되는 공통 제어 자원 세트(control-resource set, CORESET)의 시간 및 주파수 도메인 위치들은 PBCH에서 표시될 수 있다.

- [0007] NR 시스템에서, PBCH는 동기화 신호(Synchronization Signal, SS)/물리적 브로드캐스트 채널 블록(PBCH 블록)에서 반송되고 송신되고, 하나의 동기화 기간은 복수의 SS/PBCH 블록들을 포함하고, 예상되는 구역의 전체 커버리지를 구현하기 위해 상이한 SS/PBCH 블록들이 동일하거나 상이한 빔 방향들 또는 포트들의 동기식 브로드캐스트 신호들을 함께 송신할 수 있다. 상이한 빔 방향들 및 포트들의 PBCH들은 조합된 수신에 대한 필요성을 갖고; 따라서, PBCH들로의 표시 정보의 도입을 고려할 때 정보 콘텐츠가 동일한 것을 보장할 필요가 있다.

- [0008] 데이터 송신의 융통성을 보장하기 위해, 상이한 SS/PBCH 블록들의 시간 도메인 위치들과 개개의 대응하는 RMSI 공통 제어 자원 세트들의 시간 도메인 위치들 사이의 관계들은 상이할 수 있고, PBCH들의 조합된 수신에 영향을 미치지 않으면서 RMSI 공통 제어 자원 세트의 시간 도메인 위치를 효과적으로 표시하는 방법에 대한 어떠한 효과적인 솔루션도 관련 분야에 존재하지 않는다.

## 발명의 내용

- [0009] 본 출원의 실시예들은, PBCH들의 조합된 수신에 영향을 미치지 않으면서 제어 자원 세트의 시간 및 주파수 도메인 자원 위치들이 효과적으로 표시될 수 없는, 적어도 관련 분야의 기술적 문제를 해결하기 위한 정보 송신 및 수신 방법들 및 장치들을 제공한다.

- [0010] 본 출원의 일 실시예에 따르면, 물리적 브로드캐스트 채널 상에서 제어 자원 세트의 구성 정보를 반송하는 단계 - 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보 및 주파수 도메인 위치 정보 중 적어도 하나를 단말에 표시하기 위해 사용됨 -; 및 구성 정보에 따라 제어 자원 세트를 단말에 송신하는 단계를 포함하는, 정보 송신 방법이 제공된다.

- [0011] 본 출원의 일 실시예에 따르면, 제어 자원 세트의 구성 정보를 수신하는 단계 - 제어 자원 세트의 구성 정보는 물리적 브로드캐스트 채널 상에서 반송되고, 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보 및 주파수 도메인 위치 정보 중 적어도 하나를 표시하기 위해 사용됨 -; 및 구성 정보에 따라 제어 자원 세트를 수신하는 단계를 포함하는, 다른 정보 수신 방법이 제공된다.

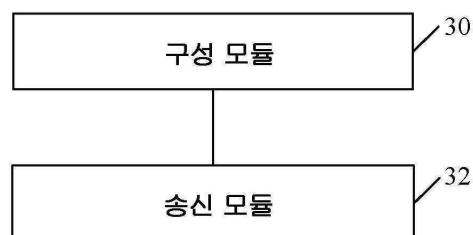

- [0012] 본 출원의 다른 실시예에 따르면, 물리적 브로드캐스트 채널 상에서 제어 자원 세트의 구성 정보를 반송하도록 구성되는 구성 모듈 - 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보 및 주파수 도메인 위치 정보 중 적

어도 하나를 단말에 표시하기 위해 사용됨 -; 및 구성 정보에 따라 제어 자원 세트를 송신하도록 구성되는 송신 모듈을 포함하는, 정보 송신 장치가 제공된다.

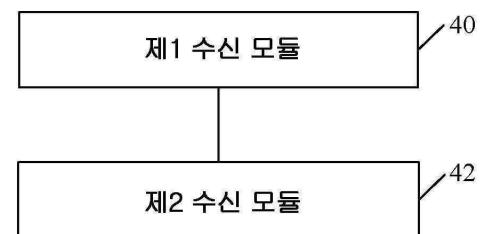

[0013] 본 출원의 다른 실시예에 따르면, 제어 자원 세트의 구성 정보를 수신하도록 구성되는 제1 수신 모듈 - 제어 자원 세트의 구성 정보는 물리적 브로드캐스트 채널 상에서 반송되고, 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보 및 주파수 도메인 위치 정보 중 적어도 하나를 표시하기 위해 사용됨 -; 및 구성 정보에 따라 제어 자원 세트를 수신하도록 구성되는 제2 수신 모듈을 포함하는, 다른 정보 수신 장치가 제공된다.

[0014] 본 출원의 추가적 실시예에 따르면, 저장된 프로그램을 포함하고, 프로그램이 실행될 때 전술한 방법 중 어느 하나에 따른 방법이 실행되는 저장 매체가 추가로 제공된다.

[0015] 본 출원의 추가적 실시예에 따르면, 프로그램을 실행하도록 구성되고, 프로그램이 실행될 때 전술한 방법 중 어느 하나에 따른 방법이 실행되는 프로세서가 추가로 제공된다.

### 도면의 간단한 설명

[0016] 본 명세서에 설명된 도면들은 본 출원의 추가적 이해를 제공하고 본 출원의 일부를 형성하기 위해 사용되고; 본 출원의 예시적인 실시예들 및 그 설명은 본 출원을 설명하기 위해 사용되고 본 출원을 제한하려는 의도가 아니다. 도면들에서:

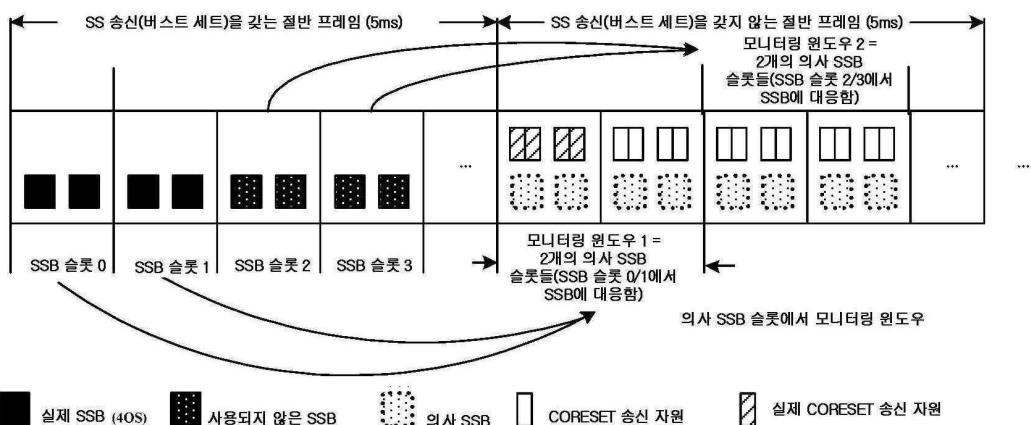

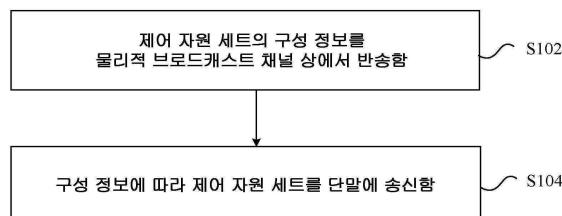

도 1은 본 출원의 일 실시예에 따른 정보 송신 방법의 흐름도이다.

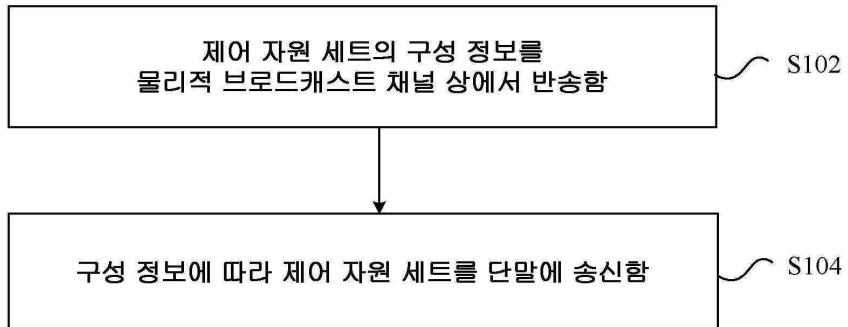

도 2는 본 출원의 일 실시예에 따른 정보 수신 방법의 흐름도이다.

도 3은 본 출원의 일 실시예에 따른 정보 송신 장치의 구조적 블록도이다.

도 4는 본 출원의 일 실시예에 따른 정보 수신 장치의 구조적 블록도이다.

도 5는 본 실시예에 따른 동기화 신호 블록의 개략도이다.

도 6은 본 실시예에 따라 주파수 도메인 위치가 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시되는 개략도 I이다.

도 7은 본 실시예에 따라 주파수 도메인 위치가 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시되는 개략도 II이다.

도 8은 본 실시예에 따라 주파수 도메인 위치가 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시되는 개략도 III이다.

도 9는 본 실시예에 따라 주파수 도메인 위치가 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시되는 개략도 IV이다.

도 10은 본 실시예에 따라 주파수 도메인 위치가 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시되는 개략도 V이다.

도 11은 본 실시예에 따라 주파수 도메인 위치가 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시되는 개략도 VI이다.

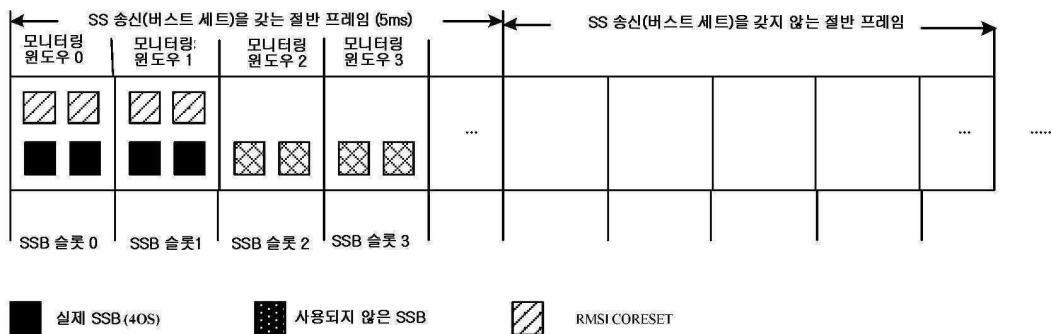

도 12는 본 실시예에 따라 SSB가 위치되는 슬롯에서만 CORESET가 송신되는 개략적 구조도이다.

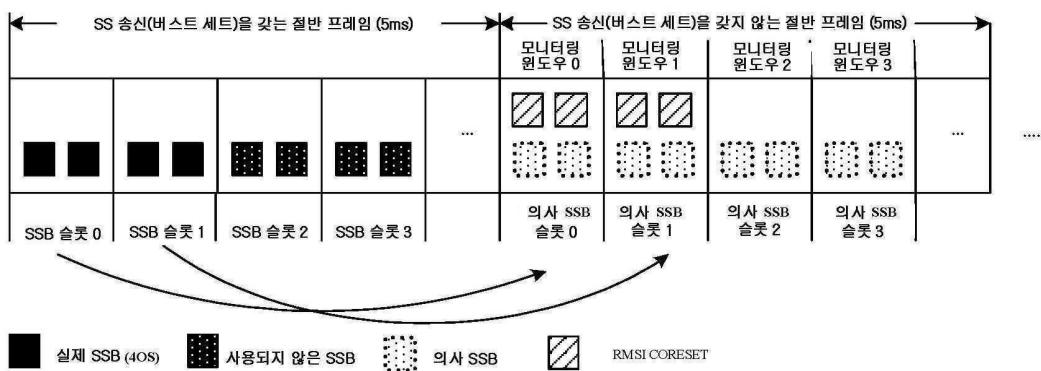

도 13은 본 실시예에 따른 복수의 동기화 신호 블록 송신 기간들의 사용에 대한 개략도이다.

도 14는 본 실시예에 따른 슬롯에 대한 현재 동기화 신호 블록(SSB)의 맵핑 패턴들의 개략도이다.

도 15는 본 실시예에 따른 슬롯에서 CORESET에 의해 점유되는 심볼의 위치 정보의 개략도 I이다.

도 16은 본 실시예에 따른 슬롯에서 CORESET에 의해 점유되는 심볼의 위치 정보의 개략도 II이다.

도 17은 본 실시예에 따라 CORESET가 SSB 외부의 슬롯에 맵핑되는 개략도 I이다.

도 18은 본 실시예에 따라 CORESET가 SSB 외부의 슬롯에 맵핑되는 개략도 II이다.

도 19는 본 실시예에 따라 CORESET가 동기화 신호 블록을 포함하는 슬롯에서 송신되는 개략도이다.

도 20은 본 실시예에 따라 CORESET가 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 개략도이다.

도 21은 본 실시예에 따라 CORESET가 동기화 신호 블록을 포함하는 슬롯에서 송신되고 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 개략도이다.

도 22는 본 실시예에 따라 동기화 신호 블록이 위치되는 슬롯에서 CORESET가 송신되는 개략도이다.

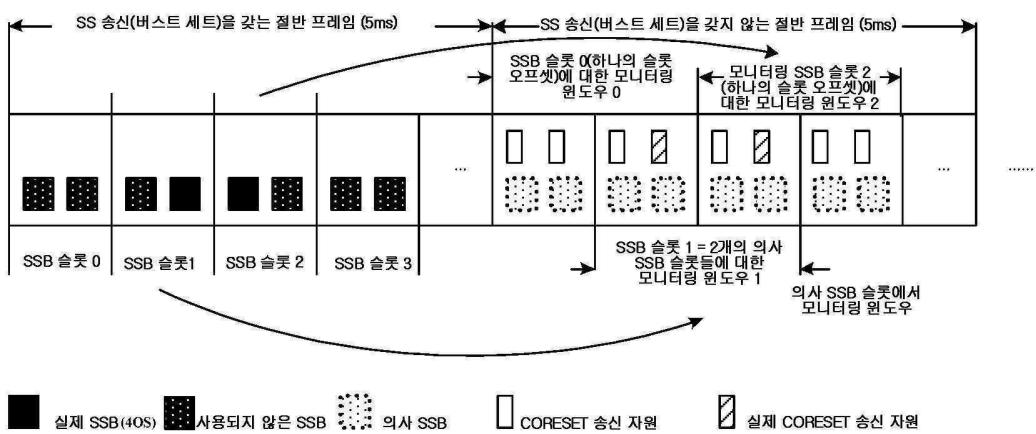

도 23은 본 실시예에 따라 CORESET가 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 개략도 I이다.

도 24는 본 실시예에 따라 CORESET가 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 개략도 II이다.

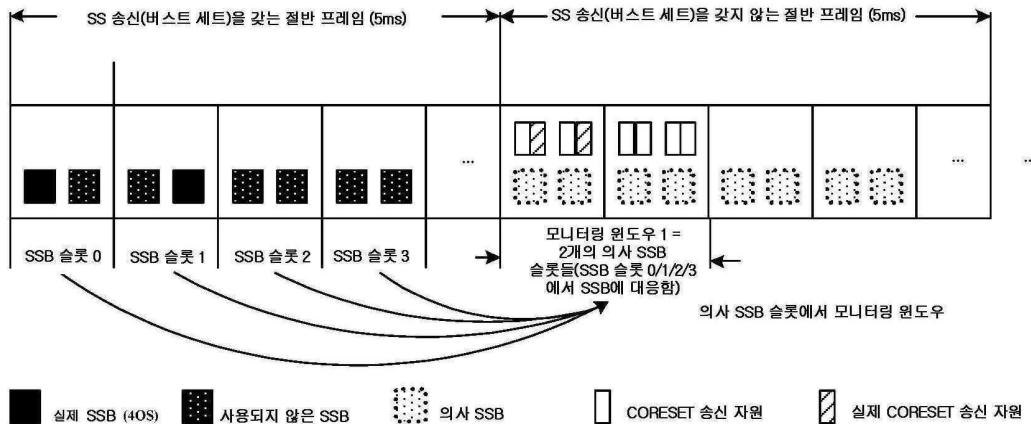

도 25는 본 실시예에 따라 모든 동기화 신호 블록들이 동일한 CORESET 모니터링 윈도우에 대응하는 개략도이다.

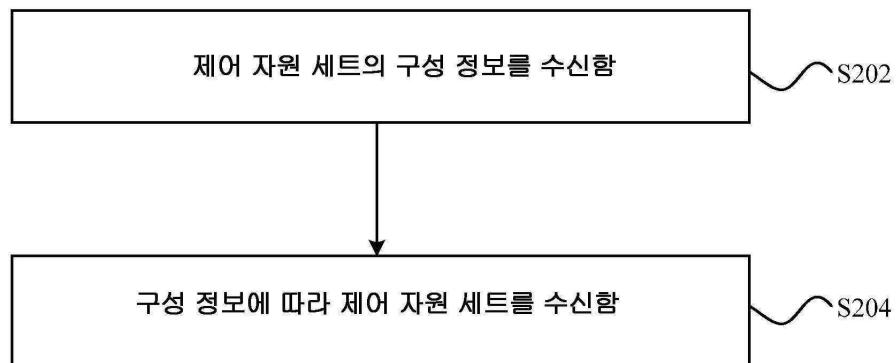

도 26은 본 실시예에 따라 복수의 동기화 신호 블록들이 하나의 CORESET 모니터링 윈도우에 대응하는 개략도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0017] 본 출원은 실시예들과 관련하여 도면들을 참조하여 아래에서 상세히 예시될 것이다. 본 출원의 실시예들 및 실시예들의 특징들은, 충돌이 초래되지 않는다면 상호 조합될 수 있음에 유의해야 한다.

- [0018] 본 출원의 명세서, 청구항들 및 첨부된 도면들에서 용어들 "제1", "제2" 등은 유사한 객체들을 구별하도록 의도되지만 반드시 특정 순서 또는 시퀀스를 표시하는 것은 아님에 유의해야 한다.

- [0019] 실시예 1

- [0020] 본 출원의 실시예에서, 실행될 수 있는 네트워크 아키텍처는 기지국 및 단말을 포함하고, 기지국과 단말 사이에서 정보 교환이 수행된다.

- [0021] 전술한 네트워크 아키텍처에 적용되는 정보 송신 방법이 본 실시예에서 제공된다. 도 1은 본 출원의 일 실시예에 따른 정보 송신 방법의 흐름도이고, 도 1에 도시된 바와 같이 흐름은 단계(S102) 및 단계(S104)를 포함한다. 단계(S102)에서, 제어 자원 세트의 구성 정보는 물리적 브로드캐스트 채널 상에서 반송된다.

- [0022] 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보 및 주파수 도메인 위치 정보 중 적어도 하나를 단말에 표시하기 위해 사용된다.

- [0023] 단계(S104)에서, 제어 자원 세트는 구성 정보에 따라 단말에 송신된다.

- [0024] 전술한 단계들을 통해, 제어 자원 세트의 구성 정보를 물리적 브로드캐스트 채널 상에서 반송하고 구성 정보에 따라 제어 자원 세트를 단말에 송신함으로써, PBCH들의 조합된 수신에 영향을 미치지 않으면서 제어 자원 세트의 시간 및 주파수 도메인 자원 위치들이 효과적으로 표시될 수 있는 관련 분야의 기술적 문제가 해결되고, 데이터 송신의 융통성이 개선된다.

- [0025] 일 실시예에서, 전술한 단계들의 실행 주체는 기지국과 같은 네트워크측일 수 있지만, 이에 제한되는 것은 아니다.

- [0026] 일 실시예에서, 제어 자원 세트의 구성 정보는 제어 자원 세트의 대역폭 정보를 포함한다.

- [0027] 일 실시예에서, 대역폭 정보는 최소 채널 대역폭 및 최소 단말 대역폭 중 적어도 하나를 포함한다.

- [0028] 일 실시예에서, 제어 자원 세트의 구성 정보는 제어 자원 세트의 주파수 도메인 위치 정보를 포함하고, 주파수 도메인 위치 정보는 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시된다.

- [0029] 일 실시예에서, 제어 자원 세트의 주파수 도메인 위치 정보는,

- [0030]  $M \times SC_{SSB}$ 인, 제어 자원 세트의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋;

- [0031]  $(BW_{CORESET} - BW_{SSB})/2 - M \times SC_{SSB}$ 인, 제어 자원 세트의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋;

- [0032]  $(BW_{CORESET} - BW_{SSB})/2 - (12 \times SC_{CORESET} - M \times SC_{SSB})$ 인, 제어 자원 세트의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋;

- [0033]  $(BW_{CORESET} + BW_{SSB})/2 + M \times SC_{SSB}$ 인, 제어 자원 세트의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋;

이의 오프셋; 및

- [0034]  $(\text{BW}_{\text{CORESET}} + \text{BW}_{\text{SSB}})/2 + (12 \times \text{SC}_{\text{CORESET}} + M \times \text{SC}_{\text{SSB}})$ 인, 제어 자원 세트의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋

- [0035] 중 하나에 의해 표시되고;

- [0036]  $M$ 은 동기화 신호 블록과 캐리어 물리적 자원 블록 그리드(carrier physical resource block grid; PRB grid) 사이의 주파수 도메인 오프셋에서 동기화 신호 블록 서브캐리어들의 수이고,  $M$ 은 정수이고,  $\text{SC}_{\text{CORESET}}$ 는 제어 자원 세트 서브캐리어의 주파수 도메인 폭이고,  $\text{SC}_{\text{SSB}}$ 는 동기화 신호 블록 서브캐리어의 주파수 도메인 폭이고,  $\text{BW}_{\text{CORESET}}$ 는 제어 자원 세트 대역폭이고,  $\text{BW}_{\text{SSB}}$ 는 동기화 신호 블록 대역폭이다.

- [0037] 일 실시예에서, 제어 자원 세트의 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보를 포함하고; 시간 도메인 위치 정보는, 제어 자원 세트가 위치되는 슬롯의 정보 및 슬롯에서 제어 자원 세트에 의해 점유되는 심볼의 위치 정보 중 적어도 하나를 포함한다.

- [0038] 일 실시예에서, 슬롯에서 제어 자원 세트에 의해 점유되는 심볼의 위치 정보는, 슬롯에서 제어 자원 세트에 의해 점유되는 심볼의 시작 심볼 인덱스 및 슬롯에서 제어 자원 세트에 의해 점유되는 심볼들의 수를 포함한다.

- [0039] 일 실시예에서, 제어 자원 세트가 위치되는 슬롯의 정보는,

- [0040] 제어 자원 세트가 동기화 신호 블록을 포함하는 슬롯에서 송신되는 것;

- [0041] 제어 자원 세트가 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 것; 및

- [0042] 제어 자원 세트가 동기화 신호 블록을 포함하는 슬롯에서 송신되고 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 것 중 하나를 포함한다.

- [0043] 일 실시예에서, 제어 자원 세트의 구성 정보는, 동기화 신호 블록을 포함하는 슬롯에서 제어 자원 세트가 송신되는지 여부; 또는 동기화 신호 블록을 포함하지 않는 슬롯에서 제어 자원 세트가 송신되는지 여부를 표시하기 위해 추가로 사용된다.

- [0044] 일 실시예에서, 제어 자원 세트가 동기화 신호 블록을 포함하는 슬롯에서 송신되고 동기화 신호 블록을 포함하지 않는 슬롯에서 송신될 때, 동기화 신호 블록을 포함하는 슬롯 및 동기화 신호 블록을 포함하지 않는 슬롯에서 제어 자원 세트에 대해 동일한 자원 맵핑 규칙이 채택된다.

- [0045] 일 실시예에서, 제어 자원 세트의 구성 정보는 제어 자원 세트의 모니터링 윈도우 구성 정보를 포함하고, 제어 자원 세트의 모니터링 윈도우 구성 정보는, 제어 자원 세트의 모니터링 기간, 모니터링 윈도우의 시간 도메인 지속기간, 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋 및 모니터링 윈도우의 시작 위치 중 적어도 하나를 포함하고, 제어 자원 세트의 모니터링 윈도우는 제어 자원 세트의 적어도 하나의 모니터링 기회를 포함한다.

- [0046] 일 실시예에서, 제어 자원 세트의 모니터링 윈도우는 동기화 신호 블록에 대응한다.

- [0047] 일 실시예에서, 제어 자원 세트의 모니터링 윈도우의 시간 도메인 지속기간은 1개 이상의 슬롯이다.

- [0048] 일 실시예에서, 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋은, 0, 모니터링 윈도우의 시간 도메인 지속기간, 및 모니터링 윈도우의 시간 도메인 지속기간의  $1/X$  중 적어도 하나를 포함하고,  $X$ 는 1 초파의 정수이고,  $X$ 의 값은 미리 결정된 프로토콜에 의해 미리 정의되거나 시그널링에 의해 표시된다.

- [0049] 일 실시예에서, 제어 자원 세트의 모니터링 윈도우의 시간 도메인 지속기간이 1개 슬롯일 때, 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋은 모니터링 윈도우의 시간 도메인 지속기간, 또는 모니터링 윈도우의 시간 도메인 지속기간의  $1/X$ 이고; 제어 자원 세트의 모니터링 윈도우의 시간 도메인 지속기간이 1개 초파의 슬롯일 때, 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋은 0, 또는 모니터링 윈도우의 시간 도메인 지속기간의  $1/X$ 이다.

- [0050] 일 실시예에서, 모니터링 윈도우의 시작 위치는 모니터링 윈도우의 시작 위치와 동기화 신호 블록의 시작 슬롯 사이의 시간 도메인 오프셋에 의해 표시되거나, 또는 모니터링 윈도우의 시작 위치는 고정식으로 구성된다.

- [0051] 일 실시예에서, 제어 자원 세트는, 나머지 최소 시스템 정보(remaining minimum system information; RMSI)의

공통 제어 자원 세트 및 페이징 정보의 공통 제어 자원 세트 중 하나이다.

[0052] 전술한 네트워크 아키텍처에 적용되는 정보 수신 방법이 본 실시예에서 제공된다. 도 2는 본 출원의 일 실시예에 따른 정보 수신 방법의 흐름도이고, 도 2에 도시된 바와 같이 흐름은 하기 단계들, 즉, 단계(S202) 및 단계(S204)를 포함한다.

[0053] 단계(S202)에서, 제어 자원 세트의 구성 정보가 수신된다.

[0054] 제어 자원 세트의 구성 정보는 물리적 브로드캐스트 채널 상에서 반송되고, 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보 및 주파수 도메인 위치 정보 중 적어도 하나를 표시하기 위해 사용된다.

[0055] 단계(S204)에서, 제어 자원 세트는 구성 정보에 따라 수신된다.

[0056] 일 실시예에서, 제어 자원 세트의 구성 정보는 제어 자원 세트의 대역폭 정보를 포함한다.

[0057] 일 실시예에서, 제어 자원 세트의 구성 정보는 제어 자원 세트의 주파수 도메인 위치 정보를 포함하고, 주파수 도메인 위치 정보는 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시된다.

[0058] 일 실시예에서, 제어 자원 세트의 주파수 도메인 위치 정보는,

M×SC<sub>SSB</sub>인, 제어 자원 세트의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋;

[0060] (BW<sub>CORESET</sub> - BW<sub>SSB</sub>)/2 - M×SC<sub>SSB</sub>인, 제어 자원 세트의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋;

[0061] (BW<sub>CORESET</sub> - BW<sub>SSB</sub>)/2 - (12×SC<sub>CORESET</sub> - M×SC<sub>SSB</sub>)인, 제어 자원 세트의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋;

[0062] (BW<sub>CORESET</sub> + BW<sub>SSB</sub>)/2 + M×SC<sub>SSB</sub>인, 제어 자원 세트의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋; 및

[0063] (BW<sub>CORESET</sub> + BW<sub>SSB</sub>)/2 + (12×SC<sub>CORESET</sub> + M×SC<sub>SSB</sub>)인, 제어 자원 세트의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋

[0064] 중 하나에 의해 표시되고;

[0065] M은 동기화 신호 블록과 캐리어 물리적 자원 블록 그리드(carrier physical resource block grid; PRB grid) 사이의 주파수 도메인 오프셋에서 동기화 신호 블록 서브캐리어들의 수이고, M은 정수이고, SC<sub>CORESET</sub>는 제어 자원 세트 서브캐리어의 주파수 도메인 폭이고, SC<sub>SSB</sub>는 동기화 신호 블록 서브캐리어의 주파수 도메인 폭이고, BW<sub>CORESET</sub>는 제어 자원 세트 대역폭이고, BW<sub>SSB</sub>는 동기화 신호 블록 대역폭이다.

[0066] 일 실시예에서, 제어 자원 세트의 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보를 포함하고; 시간 도메인 위치 정보는, 제어 자원 세트가 위치되는 슬롯의 정보 및 슬롯에서 제어 자원 세트에 의해 점유되는 심볼의 위치 정보 중 적어도 하나를 포함한다.

[0067] 일 실시예에서, 제어 자원 세트의 구성 정보는 제어 자원 세트의 모니터링 윈도우 구성 정보를 포함하고, 제어 자원 세트의 모니터링 윈도우 구성 정보는, 제어 자원 세트의 모니터링 기간, 모니터링 윈도우의 시간 도메인 지속기간, 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋 및 모니터링 윈도우의 시작 위치 중 적어도 하나를 포함하고, 제어 자원 세트의 모니터링 윈도우는 제어 자원 세트의 적어도 하나의 모니터링 기회를 포함한다.

[0068] 전술한 구현 방식들의 설명으로부터, 당업자들은, 본 출원이 전술한 실시예들의 방법들에 따라 필요한 범용 하드웨어와 함께 소프트웨어에 의해 구현될 수 있고, 또한 명백하게 하드웨어만으로 달성될 수 있지만, 전자가 선호될 것임을 명백하게 이해할 것이다. 이러한 이해에 기초하여, 본 출원의 기술적 솔루션들은 실질적으로, 또는 종래 기술에 기여하는 본 출원의 일부는 소프트웨어 제품의 형태로 구현될 수 있고, 컴퓨터 소프트웨어 제품은, 단말 장비(셀 폰, 컴퓨터, 서버, 네트워크 장비 등일 수 있음)가 본 출원의 실시예들에서 설명되는 방법들을 실행할 수 있게 하는 다수의 명령들을 포함하는 저장 매체(예를 들어, ROM/RAM, 자기 디스크 또는 광디스크)에 저장된다.

## [0069] 실시예 2

본 실시예에서, 정보 송신 및 수신 장치들이 추가로 제공되며, 장치들은 전술한 실시예 및 선호되는 구현 방식들을 구현하도록 구성되고, 예시된 것은 과도하게 반복되지 않을 것이다. 이하 사용되는 바와 같이, 용어 "모듈"은 미리 결정된 기능에 대한 소프트웨어 및 하드웨어 중 적어도 하나를 구현할 수 있다. 하기 실시예에서 설명되는 장치들은 바람직하게는 소프트웨어에 의해 구현되지만, 하드웨어 또는 소프트웨어와 하드웨어의 조합의 구현이 또한 가능하고 인식가능하다.

[0071] 도 3은 본 출원의 일 실시예에 따른 정보 송신 장치의 구조적 블록도이고, 기지국과 같은 네트워크측의 네트워크 요소에 적용될 수 있고; 도 3에 도시된 바와 같이, 장치는 구성 모듈(30) 및 송신 모듈(32)을 포함한다.

[0072] 구성 모듈(30)은 물리적 브로드캐스트 채널 상에서 제어 자원 세트의 구성 정보를 반송하도록 구성되고, 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보 및 주파수 도메인 위치 정보 중 적어도 하나를 단말에 표시하기 위해 사용된다.

[0073] 송신 모듈(32)은 구성 정보에 따라 제어 자원 세트를 송신하도록 구성된다.

[0074] 도 4는 본 출원의 일 실시예에 따른 정보 수신 장치의 구조적 블록도이고, 단말에 적용될 수 있고; 도 4에 도시된 바와 같이, 장치는 제1 수신 모듈(40) 및 제2 수신 모듈(42)을 포함한다.

[0075] 제1 수신 모듈(40)은 제어 자원 세트의 구성 정보를 수신하도록 구성되고, 제어 자원 세트의 구성 정보는 물리적 브로드캐스트 채널 상에서 반송되고, 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보 및 주파수 도메인 위치 정보 중 적어도 하나를 표시하기 위해 사용된다.

[0076] 제2 수신 모듈(42)은 구성 정보에 따라 제어 자원 세트를 수신하도록 구성된다.

[0077] 전술한 모듈들 각각은 소프트웨어 또는 하드웨어에 의해 구현될 수 있고; 하드웨어의 경우, 하기 방식에 의해 구현될 수 있지만 이에 제한되지 않으며, 전술한 모듈들은 동일한 프로세서에 위치되거나, 또는 전술한 모듈들 각각은 임의의 조합으로 상이한 프로세서들에 각각 위치됨에 유의해야 한다.

## [0078] 실시예 3

[0079] 데이터 송신의 유통성을 보장하기 위해, 상이한 SS/PBCH 블록들의 시간 도메인 위치들과 개개의 대응하는 RMSI 공통 제어 자원 세트들의 시간 도메인 위치들 사이의 관계들은 상이할 수 있고, PBCH들의 조합된 수신에 영향을 미치지 않으면서 RMSI 공통 자원 세트의 시간 도메인 위치를 효과적으로 표시하는 방법은 고려되고 해결되어야 할 문제이다.

[0080] 차세대 무선 통신 시스템 NR에서, 시스템 정보는 최소 시스템 정보(최소 SI) 및 다른 시스템 정보(다른 SI)로 분할된다. 최소 시스템 정보는 물리적 브로드캐스트 채널(PBCH) 상에서 반송되는 "마스터 시스템 정보(MIB)", 및 물리적 다운링크 공유 채널 상에서 반송되는 "나머지 최소 시스템 정보"로 추가로 분할되고; 마스터 시스템 정보는 셀의 기본 시스템 파라미터들을 제공하기 위해 사용되고, 나머지 최소 시스템 정보는 초기 액세스와 관련된 구성 정보, 예를 들어, 초기 액세스 요청의 송신 구성 및 초기 액세스 응답의 메시지 수신 구성을 제공하기 위해 사용된다. 브로드캐스트될 필요가 있는 다른 시스템 정보는 다른 시스템 정보로 지칭된다.

[0081] RMSI는 물리적 다운링크 제어 채널 PDCCH에 의해 스케줄링되고, 물리적 다운링크 공유 채널 PDSCH 상에서 반송된다. RMSI 스케줄링 정보가 위치되는 공통 제어 자원 세트 CORESET의 시간 및 주파수 도메인 위치들은 PBCH에서 표시될 수 있다.

[0082] NR 시스템에서, PBCH는 동기화 신호/물리적 브로드캐스트 채널 블록(SS/PBCH 블록)에서 반송되고 송신되고, 하나의 동기화 기간은 복수의 SS/PBCH 블록들을 포함하고, 예상되는 구역의 전체 커버리지를 구현하기 위해 상이한 SS/PBCH 블록들이 동일하거나 상이한 범위를 또는 포트들의 동기식 브로드캐스트 신호들을 함께 송신할 수 있다. 상이한 범위를 및 포트들의 PBCH들은 조합된 수신에 대한 필요성을 갖고; 따라서, PBCH들로의 표시 정보의 도입을 고려할 때 정보 콘텐츠가 동일한 것을 보장할 필요가 있다.

[0083] 데이터 송신의 유통성을 보장하기 위해, 상이한 SS/PBCH 블록들의 시간 도메인 위치들과 개개의 대응하는 RMSI 공통 제어 자원 세트들의 시간 도메인 위치들 사이의 관계들은 상이할 수 있고, PBCH들의 조합된 수신에 영향을 미치지 않으면서 RMSI 공통 자원 세트의 시간 도메인 위치를 효과적으로 표시하는 방법은 고려되고 해결되어야 할 문제이다.

- [0084] 본 출원은,

- [0085] 네트워크측에서, 제어 자원 세트(Control Resource Set, CORESET)의 구성 정보를 물리적 브로드캐스트 채널 상에서 반송하는 방식 - 제어 자원 세트의 구성 정보는 제어 자원 세트의 시간 및 주파수 도메인 위치 정보를 단말에 표시하기 위해 사용됨 -; 및

- [0086] 네트워크측에서, 구성 정보에 따라 제어 자원 세트 CORESET를 송신하는 방식을 포함하는 정보 송신 방법 및 시스템을 제공한다.

- [0087] 제어 자원 세트의 구성 정보는,

- [0088] 제어 자원 세트의 대역폭 정보;

- [0089] 제어 자원 세트의 주파수 도메인 위치 정보;

- [0090] 제어 자원 세트의 시간 도메인 위치 정보 - 시간 도메인 위치 정보는, 제어 자원 세트가 위치되는 슬롯의 정보 및 슬롯에서 제어 자원 세트에 의해 점유되는 심볼의 위치 정보 중 적어도 하나를 포함한다. 슬롯에서 제어 자원 세트에 의해 점유되는 심볼의 위치 정보는, 슬롯에서 제어 자원 세트에 의해 점유되는 심볼의 시작 심볼 인덱스 및 슬롯에서 제어 자원 세트에 의해 점유되는 심볼들의 수를 포함함 -; 및

- [0091] 제어 자원 세트의 모니터링 윈도우 구성 정보 중 하나 이상을 포함하고, 제어 자원 세트의 모니터링 윈도우 구성 정보는, 제어 자원 세트의 모니터링 기간, 모니터링 윈도우의 시간 도메인 지속기간, 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋 및 모니터링 윈도우의 시작 위치 중 적어도 하나를 포함한다.

- [0092] 본 실시예의 공통 제어 자원 세트 CORESET는 하기 다운링크 제어 정보, 즉, 페이징 다운링크 제어 정보, 나머지 최소 시스템 정보의 스케줄링 정보, 페이징 표시자 등 중 하나 이상을 포함할 수 있다. 정보는 예상되는 범위의 전체 커버리지를 구현할 필요가 있기 때문에, 소정의 특정 다운링크 포트/다운링크 빔 방향의 공통 제어 정보는 특정 CORESET에서 송신되고; 하나 이상의 CORESET들이 하나의 스위핑 송신 기간/CORESET 모니터링 기간에 포함되고, 하나 이상의 다운링크 포트들/다운링크 빔 방향들의 공통 제어 정보의 송신은 예상되는 범위의 커버리지를 구현한다.

- [0093] 페이징 다운링크 제어 정보(페이징 DCI)는 페이징 메시지의 스케줄링 정보를 표시하기 위해 사용되고, 또한 페이징 스케줄링 다운링크 제어 정보(페이징 스케줄링 DCI)로 지칭된다.

- [0094] 차세대 무선 통신 시스템 NR에서, 시스템 정보는 최소 시스템 정보(최소 SI) 및 다른 시스템 정보(다른 SI)로 분할된다. 최소 시스템 정보는 물리적 브로드캐스트 채널(PBCH) 상에서 반송되는 "마스터 시스템 정보(MIB)", 및 물리적 다운링크 공유 채널 상에서 반송되는 "나머지 최소 시스템 정보"로 추가로 분할되고; 마스터 시스템 정보는 셀의 기본 시스템 파라미터들을 제공하기 위해 사용되고, 나머지 최소 시스템 정보는 초기 액세스와 관련된 구성 정보, 예를 들어, 초기 액세스 요청의 송신 구성 및 초기 액세스 응답의 메시지 수신 구성을 제공하기 위해 사용된다. 브로드캐스트될 필요가 있는 다른 시스템 정보는 다른 시스템 정보(다른 SI)로 지칭된다.

- [0095] RMSI는 물리적 다운링크 제어 채널 PDCCH에 의해 스케줄링되고, 물리적 다운링크 공유 채널 PDSCH 상에서 반송된다. RMSI 스케줄링 정보가 위치되는 공통 제어 자원 세트 CORESET의 시간 및 주파수 도메인 위치들은 PBCH에서 표시될 수 있다.

- [0096] 페이징 표시자는 다운링크 선호 빔을 보고하도록 단말을 트리거하기 위해 사용되고, 또한 페이징 그룹 표시자로 지칭된다.

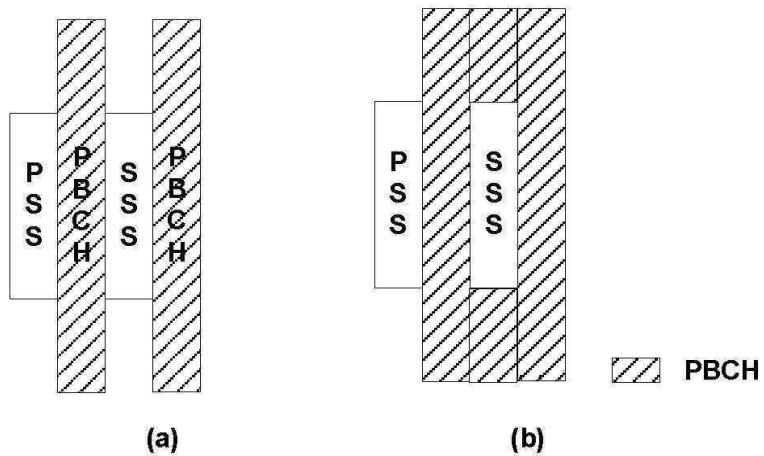

- [0097] 동기화 신호 블록(SS/PBCH 블록)은 동기화 신호 및 물리적 브로드캐스트 채널(및 대응하는 복조 기준 신호 DMRS)과 같은 액세스 관련 신호 채널들을 반송하기 위해 사용되는 시간 및 주파수 도메인 자원들이다. 도 5는 본 실시예에 따른 동기화 신호 블록의 개략도이고; 도 5에 도시된 바와 같이, 동기화 신호 블록은 통상적으로 4개의 심볼들을 포함하고, 제1 및 제3 심볼들은 1차 동기화 신호(primary synchronization signal; PSS) 및 2차 동기화 신호(secondary synchronization signal; SSS)를 각각 반송하고, 동기화 신호 시그널링들은 12개의 물리적 자원 블록들(PRBS) 내의 127개의 자원 요소들(RE)에 맵핑된다. 도 5의 (a)에 도시된 바와 같이, 일부 구성들에서, 물리적 브로드캐스트 채널들(PBCHs)은 오직 동기화 신호 블록의 제2 및 제4 심볼들에서만 반송되고 24개의 PRB들을 점유하거나; 또는 다른 자원 구성들에서, PBCH들은 동기화 신호 블록의 제2, 제3 및 제4 심볼들에 맵핑되고, 복수의 심볼들 상에서, 점유되는 PRB들의 수들은 다음과 같다: 20개의 PRB들이 제2 및 제4 심볼들 상에서 점유되고, 제3 심볼 상에서, PBCH는 2차 동기화 신호의 양측에서 각각 4개의 PRB들, 즉, 총 8개의 PRB들을

점유한다. 전술한 구성들에서, 동기화 신호들의 중심 주파수들은 PBCH들의 중심 주파수들과 정렬된다.

[0098] 본 실시예는 하기 구현 방식들을 더 포함한다.

[0099] 구현 방식 1:

[0100] 본 구현 방식은 CORESET의 대역폭 정보의 표시를 설명하며, 이는 특히 다음과 같이 설명된다: 제어 자원 세트의 구성 정보는 제어 자원 세트의 대역폭 정보가 최소 채널 대역폭 또는 최소 단말 대역폭일 수 있는 것을 포함한다.

[0101] 최소 채널 대역폭은 특정 주파수 범위 내에서 시스템에 의해 지원되는 최소 대역폭으로 정의되는데; 예를 들어, 6 GHz 아래의 주파수 범위 내에서 최소 채널 대역폭은 5MHz로 정의되거나; 또는 6 GHz 위의 주파수 범위 내에서, 최소 채널 대역폭은 50MHz로 정의된다.

[0102] 최소 단말 대역폭은 모든 단말들에 의해 지원될 수 있는 대역폭의 최대 값을 지칭한다.

[0103] CORESET 대역폭 정보의 표시의 경우, 현재 캐리어의 CORESET 대역폭이 최소 채널 대역폭인지 또는 최소 단말 대역폭인지 여부를 표시하기 위해 1비트(bit)가 물리적 브로드캐스트 채널에 포함될 수 있다. 예를 들어, 0은 현재 캐리어의 CORESET 대역폭이 최소 채널 대역폭인 것을 표현하고, 1은 현재 캐리어의 CORESET 대역폭이 최소 단말 대역폭인 것을 표현한다.

[0104] 대안적으로, CORESET 대역폭은 주파수 대역에 기초하여 미리 정의되는데; 예를 들어, 특정 주파수 대역의 CORESET 대역폭이 최소 채널 대역폭 또는 최소 단말 대역폭과 동일한 것이 프로토콜에서 특정된다. 대안적으로, 24개의 PRB들(physical transmission block) 또는 48개의 PRB들과 같은 주파수 대역의 CORESET 대역폭의 값이 프로토콜에서 주어진다. 이러한 경우, 대역폭 표시 비트를 별개로 도입하는 것은 불필요하다.

[0105] 대안적으로, CORESET 대역폭은 슬롯 내의 제어 자원 세트에 의해 점유된 심볼들의 수에 의해 목시적으로 표시되는데; 예를 들어, 슬롯에서 CORESET에 의해 점유된 심볼들의 수는 1이고, 이는 CORESET 대역폭이 48개의 PRB들인 것에 대응하고; 슬롯에서 CORESET에 의해 점유된 심볼들의 수가 2일 때 CORESET 대역폭은 24개의 PRB들이다. 이러한 경우, 대역폭 표시 비트를 별개로 도입하는 것은 불필요하다.

[0106] 구현 방식 2:

[0107] 본 구현 방식은 CORESET 주파수 도메인 위치 정보의 표시를 설명하며, 이는 다음과 같이 설명된다: 제어 자원 세트의 구성 정보는 제어 자원 세트의 주파수 도메인 위치 정보를 포함하고, 주파수 도메인 위치는 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시된다.

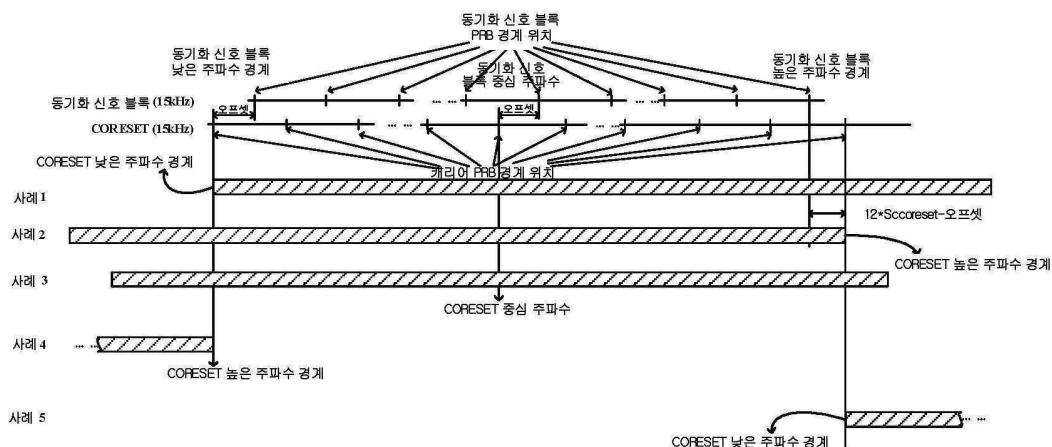

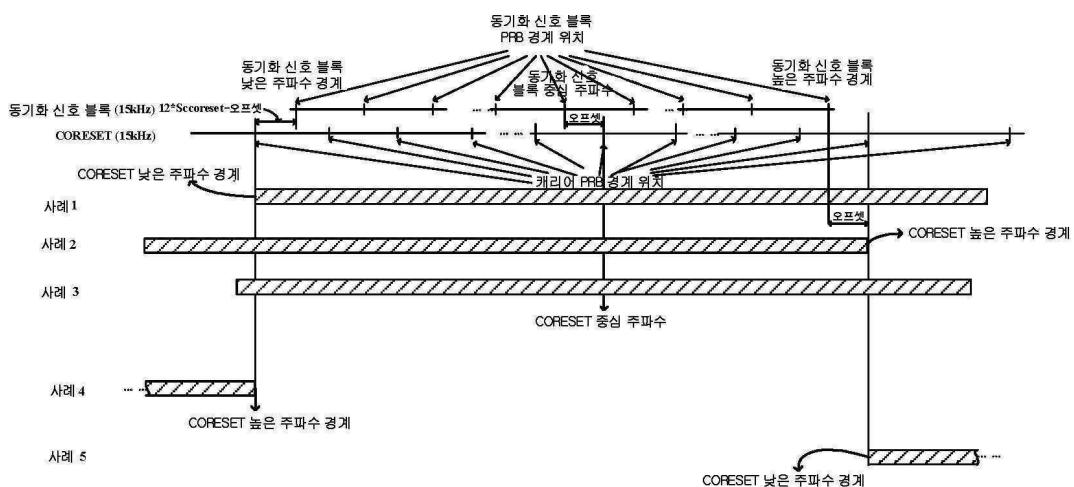

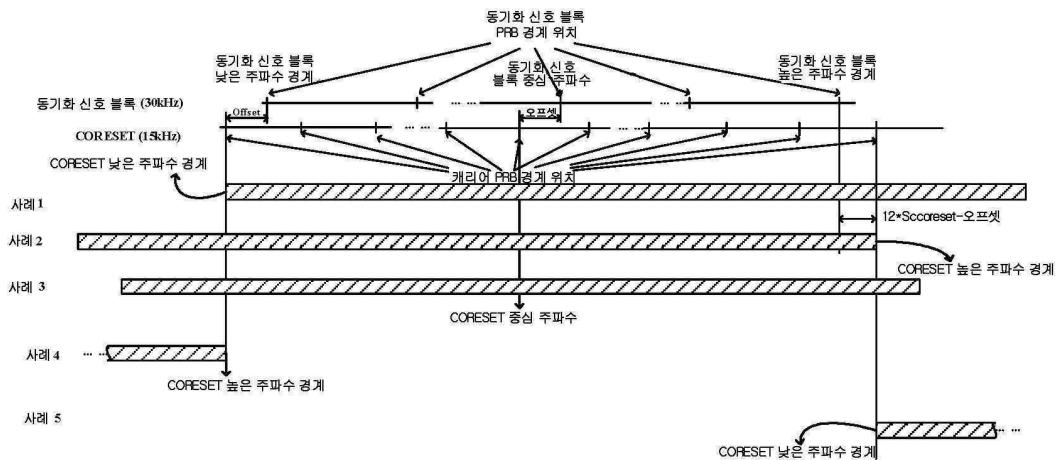

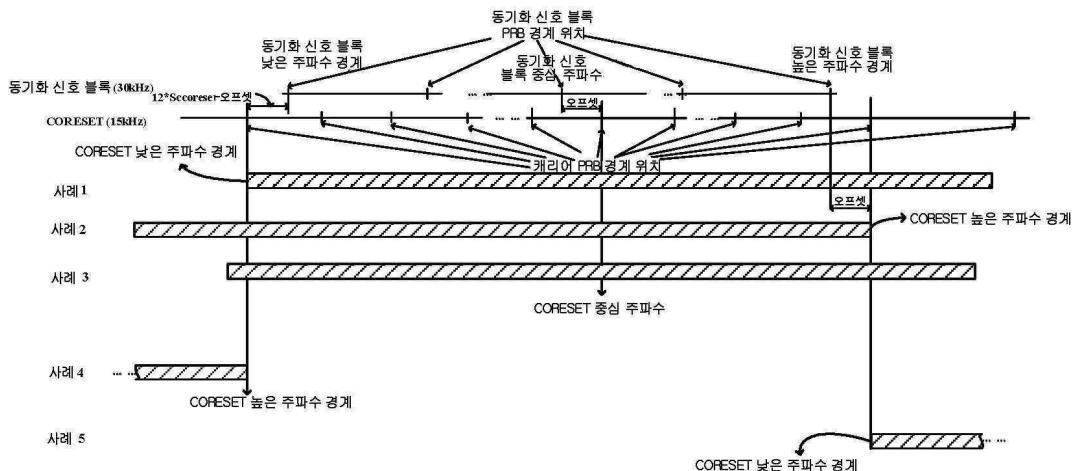

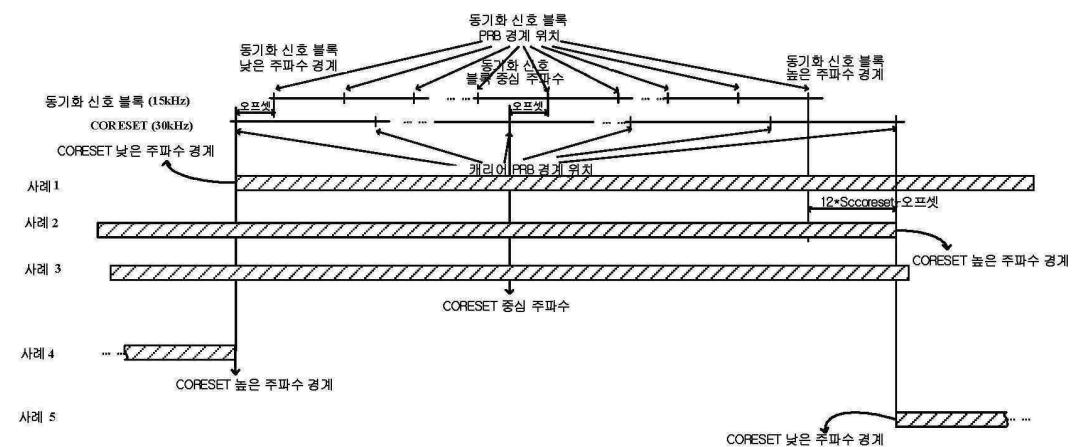

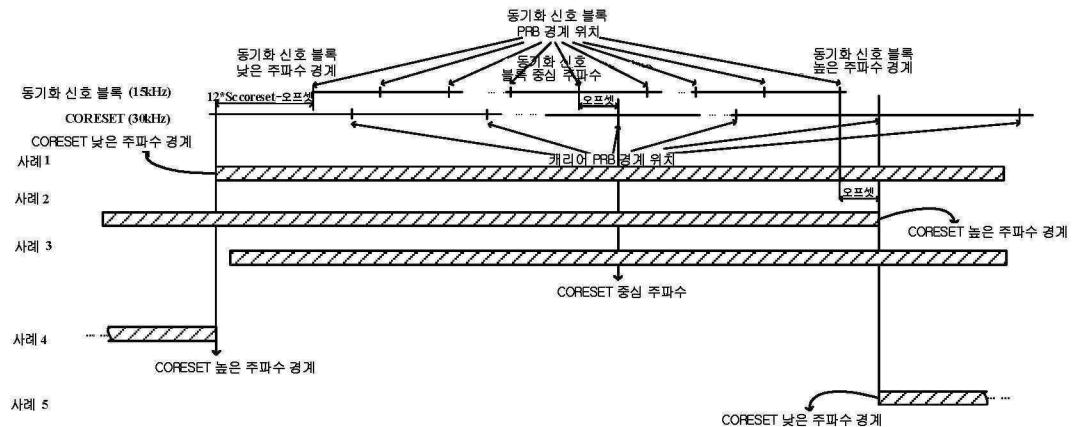

[0108] 도 6은 본 실시예에 따라 주파수 도메인 위치가 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시되는 개략도 I이고, 도 7은 본 실시예에 따라 주파수 도메인 위치가 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시되는 개략도 II이고, 도 8은 본 실시예에 따라 주파수 도메인 위치가 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시되는 개략도 III이고, 도 9는 본 실시예에 따라 주파수 도메인 위치가 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시되는 개략도 IV이고, 도 10은 본 실시예에 따라 주파수 도메인 위치가 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시되는 개략도 V이고, 도 11은 본 실시예에 따라 주파수 도메인 위치가 제어 자원 세트와 동기화 신호 블록 사이의 주파수 오프셋에 의해 표시되는 개략도 VI이다. 도 6, 도 7, 도 8, 도 9, 도 10 및 도 11에 (오프셋들의 예시로서) 도시된 바와 같이, 동기화 신호 블록의 물리적 자원 블록 PRB 경계들과 캐리어의 실제 PRB 경계들(물리적 자원 블록 그리드(PRB 그리드)) 사이에 오프셋들이 존재할 수 있다. 상기 오프셋을 명시적으로 표시하기 위해 물리적 브로드캐스트 채널에 정보 비트(예를 들어, 4개의 비트들 또는 5개의 비트들)가 도입될 수 있고, 오프셋은 동기화 신호 블록의 물리적 자원 블록 PRB 경계와 하위 주파수에서 캐리어의 PRB 경계 사이의 오프셋(도 6, 도 8 및 도 10에 도시된 바와 같음), 또는 동기화 신호 블록의 물리적 자원 블록 PRB 경계와 상위 주파수에서 캐리어의 PRB 경계 사이의 오프셋(도 7, 도 9 및 도 11에 도시된 바와 같음)으로서 미리 정의될 수 있지만, CORESET의 송신과 캐리어의 실제 PRB 경계 사이에 어떠한 오프셋도 없고; 따라서 동기화 신호 블록으로부터의 주파수 오프셋을 사용함으로써 CORESET의 주파수 도메인 위치가 표시될 때, 이러한 오프셋을 고려할 필요가 있고; CORESET 주파수 도메인 위치에 대한 표시 방식들은, CORESET의 서브캐리어 간격이 동기화 신호 블록의 서브캐리어 간격과 동일하거나, 그 미만이거나 또는 그 초과일 때 각각 아래에서 설명된다.

[0109] CORESET의 서브캐리어 간격이 동기화 신호 블록의 서브캐리어 간격과 동일할 때(예를 들어, CORESET의 서브캐리어 간격 및 동기화 신호 블록이 15kHz일 때), 도 6 및 도 7에 도시된 바와 같이, 캐리어 물리적 자원 블록 그리

드(PRB 그리드)에서, 하나의 캐리어 PRB는 주파수 도메인에서 12개의 동기화 신호 블록 서브캐리어들을 포함하고; 따라서, 12개의 가능한 오프셋 값들이 존재하는데, 즉, 오프셋의 값의 범위는 0 내지 11 서브캐리어들이고, 특정 오프셋 번호(즉, 오프셋의 값)는 PBCH에서 4개의 비트들로 표시된다.

[0110] 도 8 및 도 9에 도시된 바와 같이, CORESET의 서브캐리어 간격이 동기화 신호 블록의 서브캐리어 간격 미만일 때(예를 들어, CORESET의 서브캐리어 간격은 15kHz이고, 동기화 신호 블록의 서브캐리어 간격은 30kHz일 때), 캐리어 물리적 자원 블록 그리드(PRB 그리드)는 더 큰 서브캐리어 간격(30kHz)에 의해 정의되고, 더 작은 서브캐리어는 더 큰 서브캐리어 내에 네스팅되는데, 즉, 하나의 30kHz 서브캐리어는 주파수 도메인에서 2개의 15kHz 서브캐리어들에 대응한다. 이러한 경우, 캐리어 물리적 자원 블록 그리드(PRB 그리드)에서, 하나의 캐리어 PRB는 주파수 도메인에서 12개의 동기화 신호 블록 서브캐리어들을 포함하고, 오프셋(offset)의 값의 범위는 0 내지 11 동기화 신호 블록(30kHz) 서브캐리어들이고, 특정 오프셋 번호(즉, 오프셋의 값)는 PBCH에서 4개의 비트들로 표시된다.

[0111] 도 10 및 도 11에 도시된 바와 같이, CORESET의 서브캐리어 간격이 동기화 신호 블록의 서브캐리어 간격 초과일 때(예를 들어, CORESET의 서브캐리어 간격은 30kHz이고, 동기화 신호 블록의 서브캐리어 간격은 15kHz일 때), 캐리어 물리적 자원 블록 그리드(PRB 그리드)는 더 큰 서브캐리어 간격(30kHz)에 의해 정의되고, 더 작은 서브캐리어는 더 큰 서브캐리어 내에 네스팅되는데, 즉, 하나의 30kHz 서브캐리어는 주파수 도메인에서 2개의 15kHz 서브캐리어들에 대응한다. 이러한 경우, 캐리어 물리적 자원 블록 그리드(PRB 그리드)에서, 하나의 캐리어 PRB는 주파수 도메인에서 24개의 동기화 신호 블록 서브캐리어들을 포함하고, 오프셋(offset)의 값의 범위는 0 내지 23 동기화 신호 블록(30kHz) 서브캐리어들이고, 특정 오프셋 번호(즉, 오프셋의 값)는 PBCH에서 5개의 비트들로 표시된다.

[0112] 하위 구현 방식 2.1:

[0113] 오프셋이 동기화 신호 블록의 물리적 자원 블록 PRB 경계와 하위 주파수에서 캐리어의 PRB 경계 사이의 오프셋으로서 정의될 때(예를 들어, 도 6, 도 8 및 도 10에 도시된 바와 같음), CORESET의 주파수 도메인 위치는 하기 주파수 도메인 위치의 사례 1 내지 사례 5 중 하나이다.

[0114] 사례 1: CORESET의 낮은 주파수 경계는 M개의 15kHz 서브캐리어들에 의한 동기화 신호 블록의 낮은 주파수 경계보다 낮고; 이러한 경우, CORESET의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋은,  $(BW_{CORESET} - BW_{SSB})/2 - M \times SC_{SSB}$ 이다.

[0115] 사례 2: CORESET의 높은 주파수 경계는 동기화 신호 블록의 높은 주파수 경계보다  $12 \times SC_{CORESET} - M \times SC_{SSB}$ 만큼 높고; 이러한 경우, CORESET의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋은,  $(BW_{CORESET} - BW_{SSB})/2 - (12 \times SC_{CORESET} - M \times SC_{SSB})$ 이다.

[0116] 사례 3: CORESET의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋은 M개의 15kHz 서브캐리어들 인데; 즉, 중심 주파수들 사이의 절대적 오프셋은  $M \times SC_{SSB}$ 이다.

[0117] 사례 4: CORESET의 높은 주파수 경계는 M개의 15kHz 서브캐리어들에 의한 동기화 신호 블록의 낮은 주파수 경계보다 낮고; 이러한 경우, CORESET의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋은,  $(BW_{CORESET} + BW_{SSB})/2 + M \times SC_{SSB}$ 이다.

[0118] 사례 5: CORESET의 낮은 주파수 경계는 동기화 신호 블록의 높은 주파수 경계보다  $12 \times SC_{CORESET} - M \times SC_{SSB}$ 만큼 높고; 이러한 경우, CORESET의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋은,  $(BW_{CORESET} - BW_{SSB})/2 + (12 \times SC_{CORESET} - M \times SC_{SSB})$ 이고;

[0119] 여기서 M은 동기화 신호 블록과 PRB 경계 사이의 주파수 도메인 오프셋에서 동기화 신호 블록 서브캐리어들의 수이고, M은 정수이며, CORESET의 서브캐리어 간격이 동기화 신호 블록의 서브캐리어 간격 이하일 때, 오프셋의 값의 범위는,  $0 \leq M \leq 11$ 이다. CORESET의 서브캐리어 간격이 동기화 신호 블록의 서브캐리어 간격 초과일 때, 오프셋의 값의 범위는,  $0 \leq M \leq 23$ 이다.  $SC_{CORESET}$ 는 제어 자원 세트 서브캐리어의 주파수 도메인 폭이고,  $SC_{SSB}$ 는 동기화 신호 블록 서브캐리어의 주파수 도메인 폭이고,  $BW_{CORESET}$ 는 제어 자원 세트 대역폭이고,  $BW_{SSB}$ 는 동기화 신호 블록 대역폭이다.

- [0120] 상기 5개의 사례들 중, 사례들 1, 2 및 3에서, CORESET의 주파수 도메인 범위는 동기화 신호 블록의 주파수 도메인 범위를 포함하고; 사례들 4 및 5에서, CORESET의 주파수 도메인 범위는 동기화 신호 블록의 주파수 도메인 범위와 중첩하지 않는다.

- [0121] 하위 구현 방식 2.2:

- [0122] 도 7, 도 9 및 도 11은, 오프셋(offset)이 동기화 신호 블록의 물리적 자원 블록 PRB 경계와 상위 주파수에서 캐리어의 PRB 경계 사이의 오프셋인 경우들을 예시하며; 도 6에 예시된 사례들과 유사한 하기 사례 1 내지 사례 5가 존재한다.

- [0123] 사례 1: CORESET의 낮은 주파수 경계는 동기화 신호 블록의 낮은 주파수 경계보다  $12 \times SC_{CORESET} - M \times SC_{SSB}$ 만큼 낮고; 이러한 경우, CORESET의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋은,  $(BW_{CORESET} - BW_{SSB})/2 - (12 \times SC_{CORESET} - M \times SC_{SSB})$ 이다.

- [0124] 사례 2: CORESET의 높은 주파수 경계는 동기화 신호 블록의 높은 주파수 경계보다  $M \times SC_{SSB}$ 만큼, 즉,  $M$ 개의 동기화 신호 블록 서브캐리어들만큼 높고; 이러한 경우, CORESET의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋은,  $(BW_{CORESET} - BW_{SSB})/2 - M \times SC_{SSB}$ 이다.

- [0125] 사례 3: CORESET의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋은  $M$ 개의 15kHz 서브캐리어들 인데; 즉, 중심 주파수들 사이의 절대적 오프셋은  $M \times SC_{SSB}$ 이다.

- [0126] 사례 4: CORESET의 높은 주파수 경계는 동기화 신호 블록의 낮은 주파수 경계보다  $12 \times SC_{CORESET} - M \times SC_{SSB}$ 만큼 낮고; 이러한 경우, CORESET의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋은,  $(BW_{CORESET} + BW_{SSB})/2 + (12 \times SC_{CORESET} - M \times SC_{SSB})$ 이다.

- [0127] 사례 5: CORESET의 낮은 주파수 경계는 동기화 신호 블록의 높은 주파수 경계보다  $M \times SC_{SSB}$ 만큼, 즉,  $M$ 개의 동기화 신호 블록 서브캐리어들만큼 높고; 이러한 경우, CORESET의 중심 주파수와 동기화 신호 블록의 중심 주파수 사이의 오프셋은,  $(BW_{CORESET} + BW_{SSB})/2 + M \times SC_{SSB}$ 이다.

- [0128] 여기서  $M$ 은 동기화 신호 블록과 PRB 경계 사이의 주파수 도메인 오프셋에서 동기화 신호 블록 서브캐리어들의 수이고,  $M$ 은 정수이며, CORESET의 서브캐리어 간격이 동기화 신호 블록의 서브캐리어 간격 이하일 때, 오프셋의 값의 범위는,  $0 \leq M \leq 11$ 이다. CORESET의 서브캐리어 간격이 동기화 신호 블록의 서브캐리어 간격 초과일 때, 오프셋의 값의 범위는,  $0 \leq M \leq 23$ 이다.  $SC_{CORESET}$ 는 제어 자원 세트 서브캐리어의 주파수 도메인 폭이고,  $SC_{SSB}$ 는 동기화 신호 블록 서브캐리어의 주파수 도메인 폭이고,  $BW_{CORESET}$ 는 제어 자원 세트 대역폭이고,  $BW_{SSB}$ 는 동기화 신호 블록 대역폭이다.

- [0129] 상기 5개의 사례들 중, 사례들 1, 2 및 3에서, CORESET의 주파수 도메인 범위는 동기화 신호 블록의 주파수 도메인 범위를 포함하고; 사례들 4 및 5에서, CORESET의 주파수 도메인 범위는 동기화 신호 블록의 주파수 도메인 범위와 중첩하지 않는다.

- [0130] 상기와 같은 CORESET 주파수 도메인 위치들에서, 이들의 임의의 하나 이상의 선택적인 위치들은 프로토콜에서 특정될 수 있고, 표시 비트가 PBCH의 CORESET 구성 정보 표시 필드에 도입되어, 현재 캐리어의 CORESET의 주파수 도메인 위치를 단말에 표시한다. 예를 들어, CORESET의 주파수 도메인 위치는 하기 4개의 사례들, 사례 1, 사례 2, 사례 4 및 사례 5를 포함하고, 상기 4개의 주파수 도메인 위치들 중 어느 구성이 현재 사용되는지를 표시하기 위해 PBCH에서 2개의 비트들이 사용되는 것이 프로토콜에서 특정된다.

- [0131] 대안적으로, 아래에 정의된 바와 같이, 사례 1 및 사례 2에서, CORESET 대역폭은 동기화 신호 블록 대역폭과 중첩하고, 이는, 둘 모두의 서브캐리어 간격이 동일한 경우에 더 적합하며; 반대로 사례 4 및 사례 5에서, CORESET 대역폭은 동기화 신호 블록 대역폭과 중첩하지 않고, 이는 둘 모두의 서브캐리어 간격이 상이한 경우에 더 적합하다. 따라서, CORESET의 서브캐리어 간격 및 동기화 신호 블록의 서브캐리어 간격이 동일할 때, 사례 1 및 사례 2에서 상기 주파수 도메인 위치들 중 어느 구성이 현재 사용되는지를 표시하기 위해 1 비트가 PBCH에 도입되며; CORESET의 서브캐리어 간격 및 동기화 신호 블록의 서브캐리어 간격이 상이할 때, 사례 4 및 사례 5에서 상기 주파수 도메인 위치들 중 어느 구성이 현재 사용되는지를 표시하기 위해 1 비트가 PBCH에 도입되는

것이 프로토콜에서 특정된다.

[0132] 구현 방식 3:

본 구현 방식은 제어 자원 세트가 위치되는 슬롯의 정보에 대한 표시 방식들을 설명한다.

[0134] CORESET가 위치되는 슬롯의 정보에 대한 하기 3개의 사례들이 존재한다.

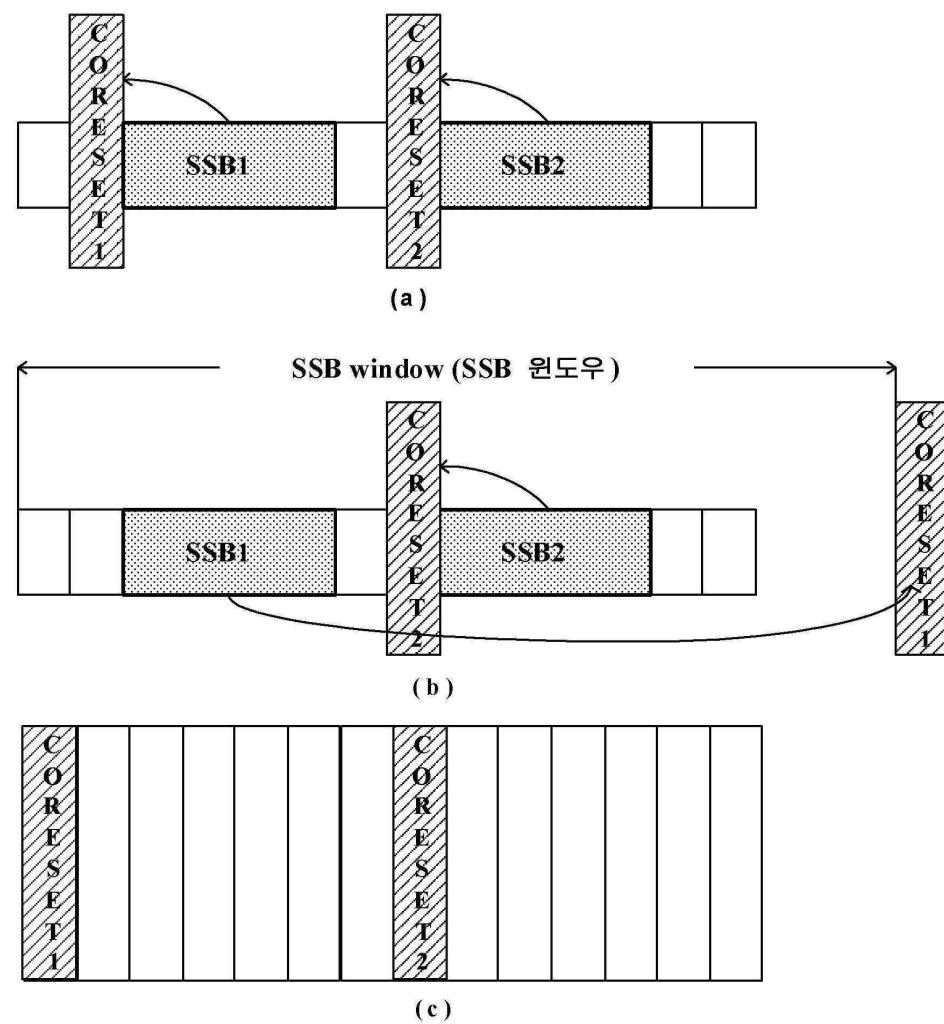

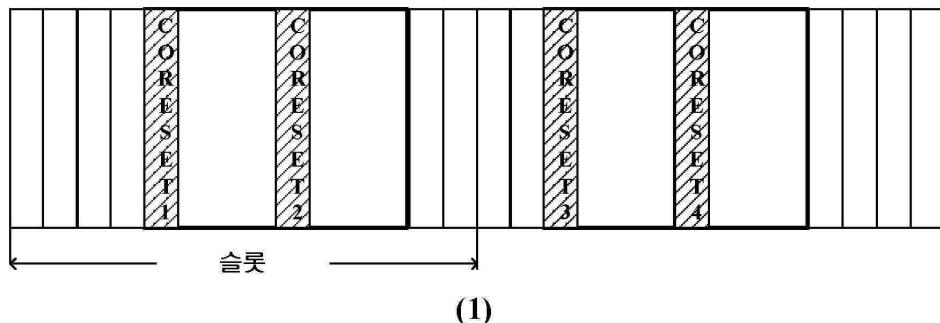

[0135] 사례 1: CORESET는 동기화 신호 블록을 포함하는 슬롯에서 송신된다(도 12의 (a)에 도시된 바와 같이, 도 12는, 본 실시예에 따른 동기화 신호 블록(Synchronization Signal Block, SSB)이 위치되는 슬롯에서 CORESET가 송신되는 개략적 구조도인데: 즉, 2개의 동기화 신호 블록들 SSB1, SSB2가 하나의 슬롯에 포함되고, 개개의 대응하는 CORESET들은 SSB들에 의해 점유된 심볼 이전의 심볼 내에 있다).

[0136] 사례 2: CORESET는 동기화 신호 블록을 포함하는 슬롯에서 송신되고 동기화 신호 블록을 포함하지 않는 슬롯에서 송신된다(도 12의 (b)에 도시된 바와 같이, 이는, CORESET가, SSB가 위치된 슬롯에서 송신되고 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 개략적 구조도인데: 즉, 2개의 동기화 신호 블록들 SSB1, SSB2가 하나의 슬롯에 포함되고, SSB2에 대응하는 CORESET는 SSB에 의해 점유된 심볼 이전의 심볼 내에 있고, SSB1에 대응하는 CORESET는 SSB를 포함하지 않는 슬롯에서 송신된다).

[0137] 사례 3: CORESET는 동기화 신호 블록을 포함하지 않는 슬롯에서 송신된다(도 12의 (c)에 도시된 바와 같이, 이는, CORESET가 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 개략적 구조도인데; 즉, SSB를 포함하지 않는 하나의 슬롯에서, CORESET들은 슬롯 내의 제1 및 제7 심볼들에 각각 맵핑된다).

[0138] 도 13에 도시된 바와 같이, 동기화 신호 블록을 포함하는 슬롯에서 제어 자원 세트의 송신을 위한 다른 형태가 존재하는데, 즉, 복수의 동기화 신호 블록 송신 기간들이 사용된다. 도 13은 본 실시예에 따른 복수의 동기화 신호 블록 송신 기간들의 사용에 대한 개략도이다(도 13에서, SS 버스트 세트 주기성은 동기화 신호 블록들의 송신 기간을 지칭한다). 2개의 동기화 신호 블록들이 하나의 슬롯(slot)에 맵핑되고, 앞의 SSB에 대응하는 CORESET1은, SSB1이 제1 기간에 위치되는 슬롯에서 송신되고, 뒤의 SSB에 대응하는 CORESET2는, SSB2가 제2 기간에 위치되는 슬롯에서 송신된다. 이러한 경우, CORESET의 송신 기간은 SSB들의 송신 기간의 2배이다.

[0139] 어느 SS 버스트 세트 기간에서 어느 SSB들이 송신되는지에 대응하는 그러한 CORESET들은 시스템에 의해 미리 정의될 수 있는데, 예를 들어, SSB들에 대응하는 홀수의 CORESET들은 시스템 프레임 번호 SFN 모드 4=0을 갖는 무선 프레임 상에 포함되고; SSB들에 대응하는 짝수의 CORESET들은 SFN 모드 4=2를 갖는 무선 프레임 상에 포함된다. 대안적으로, SSB들에 대응하는 홀수의 CORESET들은 SFN 모드 4=0 또는 1을 갖는 무선 프레임 상에 포함되고; SSB들에 대응하는 짝수의 CORESET들은 SFN 모드 4=2 또는 3을 갖는 무선 프레임 상에 포함된다.

[0140] 현재 캐리어의 CORESET가 단말에 대해 위치되는 슬롯의 정보를 표시하기 위해 PBCH의 CORESET 구성 정보 표시 필드에 표시 비트가 도입될 수 있다. 예를 들어, 2개의 비트들이 표시를 위해 사용되고, '00'은 '제어 자원 세트가 동기화 신호 블록을 포함하는 슬롯에서 송신되는 것'을 표현하고, '01'은 '제어 자원 세트가 동기화 신호 블록을 포함하는 슬롯에서 송신되고 또한 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 것을 표현하고, '10'은 '제어 자원 세트가 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 것'을 표현하고, '11'은 '(도 13에 대응하는) 기간들에 걸쳐 있는 CORESET 송신 방식'을 표현한다.

[0141] 대안적으로, 1 비트가 표시를 위해 사용되고, '0'은 '제어 자원 세트가 동기화 신호 블록을 포함하는 슬롯에서 송신되는 것'을 표현하고, '1'은 '제어 자원 세트가 오직 동기화 신호 블록을 포함하지 않는 슬롯에서만 송신되는 것'을 표현한다. 이러한 경우, '0'은 실제로, 도 12의 (a), 도 12 및 도 13의 (b)에 도시된 3개의 사례들을 포함한다.

[0142] 대안적으로, 1 비트가 표시를 위해 사용되고, '0'은 '제어 자원 세트가 오직 동기화 신호 블록을 포함하는 슬롯에서만 송신되는 것'을 표현하고; '1'은 '제어 자원 세트가 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 것'을 표현한다. 이러한 경우, '0'은 실제로, 도 12 및 도 13의 (a)에 도시된 2개의 사례들을 포함하고; '1'은 실제로, 도 12의 (b) 및 도 12의 (c)에 도시된 2개의 사례들을 포함한다.

[0143] 대안적으로, 상기 4개의 사례들 중 임의의 2개가 포함되고, 현재 캐리어에 대해 특히 어느 구성이 사용되는지를 표시하기 위해 PBCH에서 1 비트가 추가로 사용되는 것이 프로토콜에서 특정된다.

[0144] 구현 방식 4:

[0145] 본 구현 방식은 슬롯에서 CORESET에 의해 점유되는 심볼의 위치 정보에 대한 표시 방식들을 설명하며; 슬롯에서

CORESET에 의해 점유되는 심볼의 위치 정보는 슬롯에서 CORESET에 의해 점유되는 심볼의 시작 심볼 인덱스 및 슬롯에서 CORESET에 의해 점유되는 심볼들의 수를 포함한다.

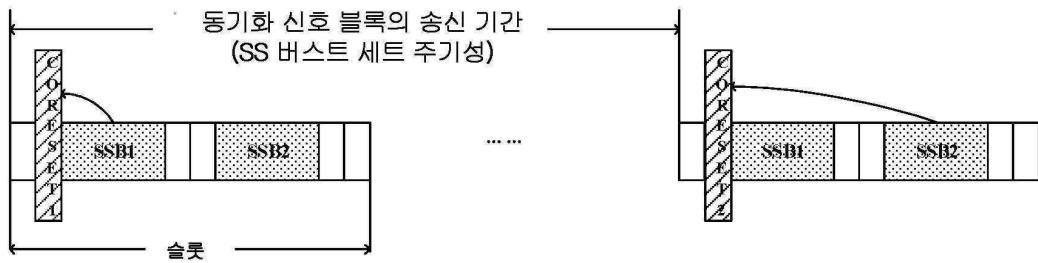

[0146] 도 14에 도시된 바와 같이, 도 14는 본 실시예에 따른 슬롯에 대한 현재 동기화 신호 블록(SSB)의 맵핑 패턴들의 개략도이고, 도 14의 (a)는 15kHz 또는 30kHz(패턴 2)의 서브캐리어 간격을 갖는 동기화 신호 블록들의 슬롯으로의 맵핑에 적용되고; 도 14의 (b)는 30kHz(패턴 1) 또는 120kHz의 서브캐리어 간격을 갖는 동기화 신호 블록들의 슬롯으로의 맵핑에 적용되고; 도 14의 (c)는 240kHz의 서브캐리어 간격을 갖는 동기화 신호 블록들의 슬롯으로의 맵핑에 적용된다. 도 14의 (a) 및 도 14의 (b)의 슬롯들은 현재 동기화 신호 블록들의 서브캐리어 간격에 대응하는 슬롯들이고; 도 14의 (c)의 슬롯은 120kHz의 슬롯에 대응한다.

[0147] 하위 구현 방식 4.1:

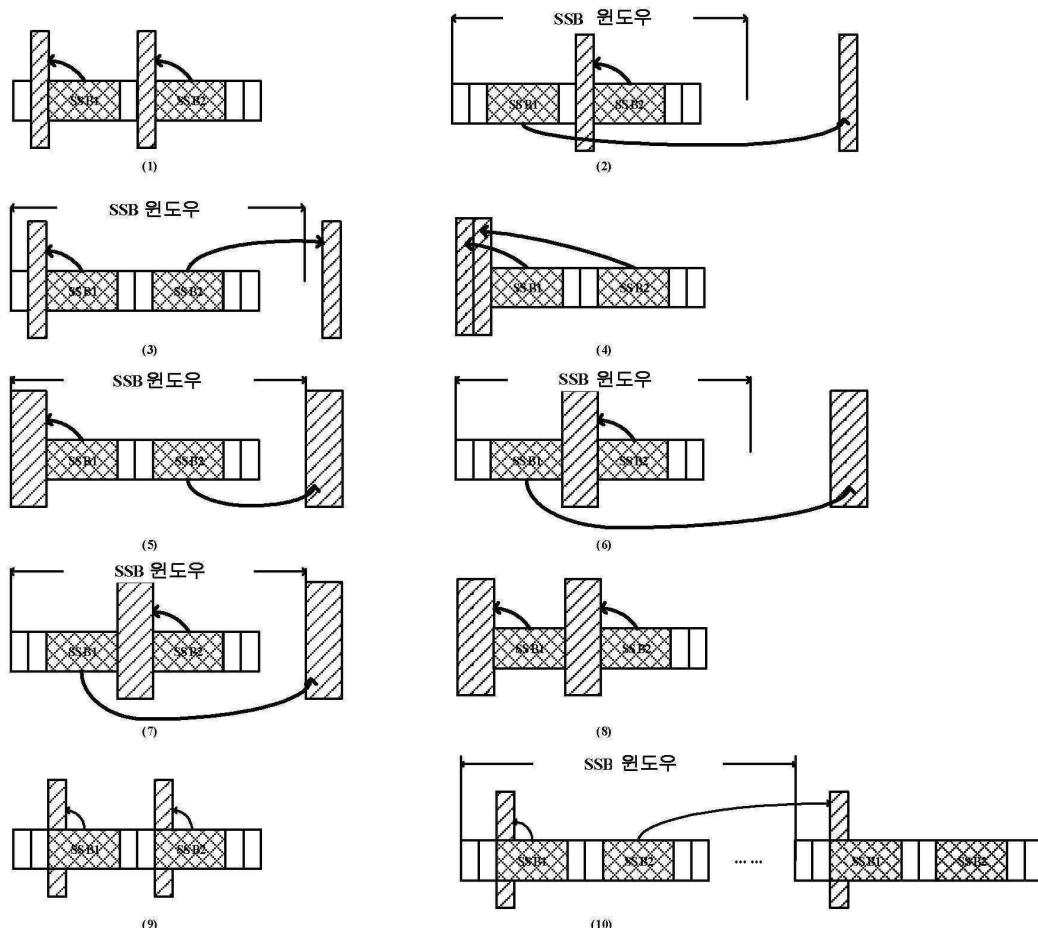

[0148] 도 14의 (a)에 도시된 15kHz 또는 30kHz(패턴 2)의 동기화 신호 블록들의 맵핑의 경우, 도 15는 본 실시예에 따른 슬롯에서 CORESET에 의해 점유되는 심볼의 위치 정보의 개략도 I이다. 도 15에 도시된 바와 같이, CORESET에 의해 점유된 심볼의 위치 정보는 다음 중 하나 이상을 포함하고, SSB로부터 시작하는 화살표는 그에 대응하는 CORESET를 향한다.

[0149] 도 15 (1)의 구성에서, 각각의 CORESET는 1 심볼을 점유하고 동일한 슬롯에서 맵핑되고, SSB는 특히 SSB 이전의 하나의 심볼을 점유하는데, 즉, 슬롯에서 제1 SSB에 대응하는 CORESET는 슬롯에서 제2 심볼을 점유하고, 슬롯에서 제2 SSB에 대응하는 CORESET는 슬롯에서 제8 심볼을 점유한다.

[0150] 도 15 (2)의 구성에서, 각각의 CORESET는 1 심볼을 점유하고, 슬롯에서 제1 SSB에 대응하는 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯의 제8 심볼에 맵핑되고; 슬롯에서 제2 SSB에 대응하는 CORESET는, SSB가 위치되는 슬롯에서 맵핑되고, 특히 SSB 이전의 1 심볼, 즉, 슬롯에서 제8 심볼을 점유한다.

[0151] 도 15 (3)의 구성에서, 각각의 CORESET는 1 심볼을 점유하고, 슬롯에서 제1 SSB에 대응하는 CORESET는, SSB가 위치되는 슬롯에서 맵핑되고, 특히 SSB 이전의 1 심볼, 즉, 슬롯에서 제2 심볼을 점유하고; 슬롯에서 제2 SSB에 대응하는 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯의 제2 심볼에 맵핑된다.

[0152] 도 15 (4)의 구성에서, 각각의 CORESET는 1 심볼을 점유하고, SSB가 위치되는 슬롯에서 맵핑되고, SSB는 특히 슬롯에서 처음 2개의 심볼들을 점유하는데, 즉, 슬롯에서 제1 SSB에 대응하는 CORESET는 슬롯에서 제1 심볼을 점유하고, 슬롯에서 제2 SSB에 대응하는 CORESET는 슬롯에서 제2 심볼을 점유한다.

[0153] 도 15 (5)의 구성에서, 각각의 CORESET는 2개의 심볼들을 점유하고, 슬롯에서 제1 SSB에 대응하는 CORESET는, SSB가 위치되는 슬롯에서 맵핑되고, 특히 SSB가 위치되는 슬롯의 처음 2개의 심볼들을 점유하고; 슬롯에서 제2 SSB에 대응하는 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯의 제1 및 제2 심볼들에 맵핑된다.

[0154] 도 15 (6)의 구성에서, 각각의 CORESET는 2 심볼을 점유하고, 슬롯에서 제1 SSB에 대응하는 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯의 제7 및 제8 심볼들에 맵핑되고; 슬롯에서 제2 SSB에 대응하는 CORESET는, SSB가 위치되는 슬롯에서 맵핑되고, 특히 SSB가 위치되는 슬롯의 제7 및 제8 심볼들을 점유한다.

[0155] 도 15 (7)의 구성에서, 각각의 CORESET는 2 심볼을 점유하고, 슬롯에서 제1 SSB에 대응하는 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯의 제1 및 제2 심볼들에 맵핑되고; 슬롯에서 제2 SSB에 대응하는 CORESET는, SSB가 위치되는 슬롯에서 맵핑되고, 특히 SSB가 위치되는 슬롯의 제7 및 제8 심볼들을 점유한다.

[0156] 도 15 (8)의 구성에서, 각각의 CORESET는 2 심볼을 점유하고 동일한 슬롯에서 맵핑되고, SSB는 특히 SSB 이전의 2개의 심볼들을 점유하는데, 즉, 슬롯에서 제1 SSB에 대응하는 CORESET는 슬롯에서 제1 및 제2 심볼들을 점유하고, 슬롯에서 제2 SSB에 대응하는 CORESET는 슬롯에서 제7 및 제8 심볼들을 점유한다.

[0157] 도 15 (9)의 구성에서, 각각의 CORESET는 1 또는 2 또는 3 또는 4개의 심볼들을 점유하고, 주파수 분할 멀티플렉싱(Frequency-division multiplexing, FDM)의 멀티플렉싱 방식이 CORESET들 및 대응하는 SSB들에 대해 사용되는데, 즉, 슬롯에서 제1 SSB에 대응하는 CORESET는 SSB가 위치되는 슬롯에서 맵핑된다. 일 실시예에서, CORESET가 1 심볼을 점유할 때, 이는 SSB가 위치되는 슬롯의 제3 심볼을 점유하고; CORESET의 2개의 심볼들의 경우, 제3 및 제4 심볼들이 점유되고; CORESET의 3개의 심볼들의 경우, 제3, 제4 및 제5 심볼들이 점유되고; CORESET의 4개의 심볼들의 경우, 제3, 제4, 제5 및 제6 심볼들이 점유되고; 슬롯에서 제2 SSB에 대응하는 CORESET는 SSB가 위치되는 슬롯에서 맵핑된다. 일 실시예에서, CORESET가 1 심볼을 점유할 때, 이는 SSB가 위치되는 슬롯의 제9 심볼을 점유하고; CORESET의 2개의 심볼들의 경우, 제9 및 제10 심볼들이 점유되고; CORESET의 3개의 심볼들의 경우, 제9, 제10 및 제11 심볼들이 점유되고; CORESET의 4개의 심볼들의 경우, 제9, 제10,

제11 및 제12 심볼들이 점유되고; SSB 이외의 자원은 주파수 도메인에서 점유된다.

[0158] 도 15 (10)의 구성에서, 각각의 CORESET는 1 또는 2 또는 3 또는 4개의 심볼들을 점유하고, FDM의 멀티플렉싱 방식이 CORESET들 및 대응하는 SSB들에 대해 사용되는데, 즉, 슬롯에서 제1 SSB에 대응하는 CORESET는 SSB가 위치되는 슬롯에서 맵핑된다. 일 실시예에서, CORESET가 1 심볼을 점유할 때, 이는 SSB가 위치되는 슬롯의 제3 심볼을 점유하고; CORESET의 2개의 심볼들의 경우, 제3 및 제4 심볼들이 점유되고; CORESET의 3개의 심볼들의 경우, 제3, 제4 및 제5 심볼들이 점유되고; CORESET의 4개의 심볼들의 경우, 제3, 제4, 제5 및 제6 심볼들이 점유되고; 슬롯에서 제2 SSB에 대응하는 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯에 맵핑된다. 일 실시예에서, CORESET가 1 심볼을 점유할 때, 이는 SSB가 위치되는 슬롯의 제3 심볼을 점유하고; CORESET의 2개의 심볼들의 경우, 제3 및 제4 심볼들이 점유되고; CORESET의 3개의 심볼들의 경우, 제3, 제4 및 제5 심볼들이 점유되고; CORESET의 4개의 심볼들의 경우, 제3, 제4, 제5 및 제6 심볼들이 점유된다. SSB에 대응하는 주파수 도메인 자원 이외의 자원은 주파수 도메인에서 점유된다.

[0159] 하위 구현 방식 4.2:

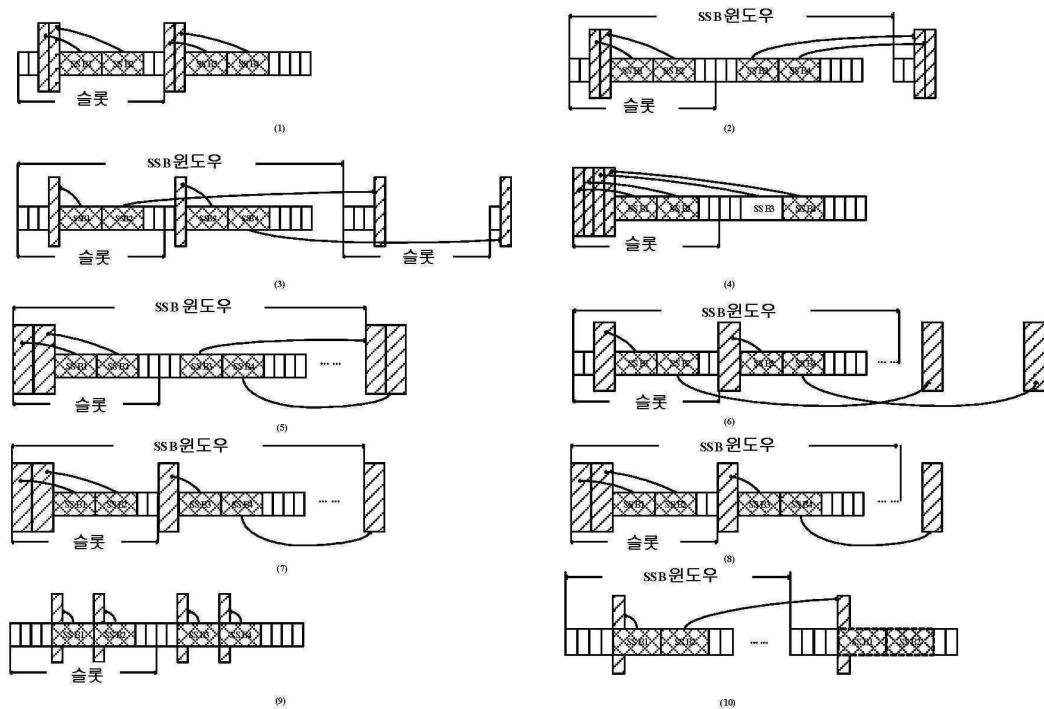

[0160] 도 14의 (b)에 도시된 30kHz(패턴 1) 또는 120kHz의 동기화 신호 블록들의 맵핑의 경우, 맵핑 자원 구성은 기간으로서 2개의 슬롯들 및 4개의 SSB들에 기초하여 수행된다. 도 16은 본 실시예에 따른 슬롯에서 CORESET에 의해 점유되는 심볼의 위치 정보의 개략도 II이다. 도 16에 도시된 바와 같이, CORESET에 의해 점유된 심볼의 위치 정보는 다음 중 하나 이상을 포함하고, SSB로부터 시작하는 화살표는 그에 대응하는 CORESET를 향한다.

[0161] 도 16 (1)의 구성에서, 각각의 CORESET는 1 심볼을 점유하고, 제1 SSB의 CORESET는 앞의 슬롯에서 제3 심볼을 점유하고; 제2 SSB의 CORESET는 앞의 슬롯에서 제4 심볼을 점유하고; 제3 SSB의 CORESET는 뒤의 슬롯에서 제1 심볼을 점유하고; 제4 SSB의 CORESET는 뒤의 슬롯에서 제2 심볼을 점유한다.

[0162] 도 16 (2)의 구성에서, 각각의 CORESET는 1 심볼을 점유하고, 제1 SSB의 CORESET는 앞의 슬롯에서 제3 심볼을 점유하고; 제2 SSB의 CORESET는 앞의 슬롯에서 제4 심볼을 점유하고; 제3 SSB의 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯에서 제3 심볼을 점유하고; 제4 SSB의 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯에서 제4 심볼을 점유하고; '제1 SSB의 CORESET와 제3 SSB의 CORESET 사이의 간격'은 '제2 SSB의 CORESET와 제4 SSB의 CORESET 사이의 간격'과 동일하여, 예를 들어, 간격은 5ms와 동일하다.

[0163] 도 16 (3)의 구성에서, 각각의 CORESET는 1 심볼을 점유하고, 제1 SSB의 CORESET는 앞의 슬롯에서 제4 심볼을 점유하고; 제2 SSB의 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯의 제4 심볼을 점유하고; 제3 SSB의 CORESET는 뒤의 슬롯에서 제4 심볼을 점유하고; 제4 SSB의 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯에서 제2 심볼을 점유하고; '제1 SSB의 CORESET와 제3 SSB의 CORESET 사이의 간격'은 '제2 SSB의 CORESET와 제4 SSB의 CORESET 사이의 간격'과 동일하여, 예를 들어, 간격은 5ms와 동일하다.

[0164] 도 16 (4)의 구성에서, 각각의 CORESET는 1 심볼을 점유하고, CORESET들은 제1 슬롯에서 처음 4개의 심볼들에 각각 맵핑된다. 일 실시예에서, 제1 SSB의 CORESET는 앞의 슬롯에서 1 심볼을 점유하고; 제2 SSB의 CORESET는 앞의 슬롯에서 제2 심볼을 점유하고; 제3 SSB의 CORESET는 앞의 슬롯에서 제3 심볼을 점유하고; 제4 SSB의 CORESET는 앞의 슬롯에서 제4 심볼을 점유한다.

[0165] 도 16 (5)의 구성에서, 각각의 CORESET는 2개의 심볼들을 점유하고, 제1 SSB의 CORESET는 앞의 슬롯에서 제1 및 제2 심볼들을 점유하고; 제2 SSB의 CORESET는 앞의 슬롯에서 제3 및 제4 심볼들을 점유하고; 제3 SSB의 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯에서 제1 및 제2 심볼들을 점유하고; 제4 SSB의 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯에서 제3 및 제4 심볼들을 점유하고; '제1 SSB의 CORESET와 제3 SSB의 CORESET 사이의 시간 도메인 간격'은 '제2 SSB의 CORESET와 제4 SSB의 CORESET 사이의 시간 도메인 간격'과 동일하여, 예를 들어, 간격은 5ms와 동일하다.

[0166] 도 16 (6)의 구성에서, 각각의 CORESET는 2개의 심볼들을 점유하고, 제1 SSB의 CORESET는 앞의 슬롯에서 제3 및 제4 심볼들을 점유하고; 제2 SSB의 CORESET는 뒤의 슬롯에서 제1 및 제2 심볼들을 점유하고; 제3 SSB의 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯에서 제3 및 제4 심볼들을 점유하고; 제4 SSB의 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯에서 제1 및 제2 심볼들을 점유하고; '제1 SSB의 CORESET와 제3 SSB의 CORESET 사이의 시간 도메인 간격'은 '제2 SSB의 CORESET와 제4 SSB의 CORESET 사이의 시간 도메인 간격'과 동일하여, 예를 들어, 간격은 5ms와 동일하다.

[0167] 도 16 (7)의 구성에서, 각각의 CORESET는 2개의 심볼들을 점유하고, 제1 SSB의 CORESET는 앞의 슬롯에서 제1 및 제2 심볼들을 점유하고; 제2 SSB의 CORESET는 앞의 슬롯에서 제3 및 제4 심볼들을 점유하고; 제3 SSB의 CORESET

는 뒤의 슬롯에서 제1 및 제2 심볼들을 점유하고; 제4 SSB의 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯에서 제1 및 제2 심볼들을 점유하고; '제1 SSB의 CORESET와 제4 SSB의 CORESET 사이의 시간 도메인 간격'은 5ms와 동일하다.

[0168] 도 16 (8)의 구성에서, 각각의 CORESET는 2개의 심볼들을 점유하고, 제1 SSB의 CORESET는 앞의 슬롯에서 제1 및 제2 심볼들을 점유하고; 제2 SSB의 CORESET는 앞의 슬롯에서 제3 및 제4 심볼들을 점유하고; 제3 SSB의 CORESET는 앞의 슬롯에서 제1 및 제2 심볼들을 점유하고; 제4 SSB의 CORESET는 5ms SSB 시간 윈도우 외부의 슬롯에서 제1 및 제2 심볼들을 점유하고; '제2 SSB의 CORESET와 제4 SSB의 CORESET 사이의 시간 도메인 간격'은 5ms와 동일하거나, 또는 '제3 SSB의 CORESET와 제4 SSB의 CORESET 사이의 시간 도메인 간격'은 5ms와 동일하다.

[0169] 도 16 (9)의 구성에서, 각각의 CORESET는 1 또는 2 또는 3 또는 4개의 심볼들을 점유하고, FDM의 멀티플렉싱 방식이 CORESET들 및 대응하는 SSB들에 대해 사용되는데, 즉,

[0170] 제1 SSB에 대응하는 CORESET은 SSB가 위치되는 슬롯에서 맵핑된다. 일 실시예에서, CORESET가 1 심볼을 점유할 때, 이는 SSB가 위치되는 슬롯의 제5 심볼을 점유하고; CORESET의 2개의 심볼들의 경우, 제5 및 제6 심볼들이 점유되고; CORESET의 3개의 심볼들의 경우, 제5, 제6 및 제7 심볼들이 점유되고; CORESET의 4개의 심볼들의 경우, 제5, 제6, 제7 및 제8 심볼들이 점유되고; SSB 이외의 자원은 주파수 도메인에서 점유된다.

[0171] 제2 SSB에 대응하는 CORESET은 SSB가 위치되는 슬롯에서 맵핑된다. 일 실시예에서, CORESET가 1 심볼을 점유할 때, 이는 SSB가 위치되는 슬롯의 제9 심볼을 점유하고; CORESET의 2개의 심볼들의 경우, 제9 및 제10 심볼들이 점유되고; CORESET의 3개의 심볼들의 경우, 제9, 제10 및 제11 심볼들이 점유되고; CORESET의 4개의 심볼들의 경우, 제9, 제10, 제11 및 제12 심볼들이 점유되고; SSB 이외의 자원은 주파수 도메인에서 점유된다.

[0172] 제3 SSB에 대응하는 CORESET은 SSB가 위치되는 슬롯에서 맵핑된다. 일 실시예에서, CORESET가 1 심볼을 점유할 때, 이는 SSB가 위치되는 슬롯의 제3 심볼을 점유하고; CORESET의 2개의 심볼들의 경우, 제3 및 제4 심볼들이 점유되고; CORESET의 3개의 심볼들의 경우, 제3, 제4 및 제5 심볼들이 점유되고; CORESET의 4개의 심볼들의 경우, 제3, 제4, 제5 및 제6 심볼들이 점유되고; SSB 이외의 자원은 주파수 도메인에서 점유된다.

[0173] 제4 SSB에 대응하는 CORESET은 SSB가 위치되는 슬롯에서 맵핑된다. 일 실시예에서, CORESET가 1 심볼을 점유할 때, 이는 SSB가 위치되는 슬롯의 제7 심볼을 점유하고; CORESET의 2개의 심볼들의 경우, 제7 및 제8 심볼들이 점유되고; CORESET의 3개의 심볼들의 경우, 제7, 제8 및 제9 심볼들이 점유되고; CORESET의 4개의 심볼들의 경우, 제7, 제8, 제9 및 제10 심볼들이 점유되고; SSB 이외의 자원은 주파수 도메인에서 점유된다.

[0174] 도 16 (10)의 구성에서, 각각의 CORESET은 1 또는 2 또는 3 또는 4개의 심볼들을 점유하고, FDM의 멀티플렉싱 방식이 CORESET들 및 대응하는 SSB들에 대해 사용되는데, 즉,

[0175] 제1 SSB에 대응하는 CORESET은 SSB가 위치되는 슬롯에서 맵핑된다. 일 실시예에서, CORESET가 1 심볼을 점유할 때, 이는 SSB가 위치되는 슬롯의 제5 심볼을 점유하고; CORESET의 2개의 심볼들의 경우, 제5 및 제6 심볼들이 점유되고; CORESET의 3개의 심볼들의 경우, 제5, 제6 및 제7 심볼들이 점유되고; CORESET의 4개의 심볼들의 경우, 제5, 제6, 제7 및 제8 심볼들이 점유되고; SSB 이외의 자원은 주파수 도메인에서 점유된다.

[0176] 제2 SSB에 대응하는 CORESET은 5ms와 시간 윈도우 외부의 슬롯에서 맵핑된다. 일 실시예에서, CORESET가 1 심볼을 점유할 때, 이는 제5 심볼을 점유하고; CORESET의 2개의 심볼들의 경우, 제5 및 제6 심볼들이 점유되고; CORESET의 3개의 심볼들의 경우, 제5, 제6 및 제7 심볼들이 점유되고; CORESET의 4개의 심볼들의 경우, 제5, 제6, 제7 및 제8 심볼들이 점유되고; SSB에 대응하는 주파수 도메인 자원 이외의 자원은 주파수 도메인에서 점유되고, 또한 '제1 SSB의 CORESET와 제3 SSB의 CORESET 사이의 시간 도메인 간격'은 5ms와 동일하다.

[0177] 제3 SSB에 대응하는 CORESET은 SSB가 위치되는 슬롯에서 맵핑된다. 일 실시예에서, CORESET가 1 심볼을 점유할 때, 이는 SSB가 위치되는 슬롯의 제3 심볼을 점유하고; CORESET의 2개의 심볼들의 경우, 제3 및 제4 심볼들이 점유되고; CORESET의 3개의 심볼들의 경우, 제3, 제4 및 제5 심볼들이 점유되고; CORESET의 4개의 심볼들의 경우, 제3, 제4, 제5 및 제6 심볼들이 점유되고; SSB 이외의 자원은 주파수 도메인에서 점유된다.

[0178] 제4 SSB에 대응하는 CORESET은 5ms와 시간 윈도우 외부의 슬롯에서 맵핑된다. 일 실시예에서, CORESET가 1 심볼을 점유할 때, 이는 제7 심볼을 점유하고; CORESET의 2개의 심볼들의 경우, 제7 및 제8 심볼들이 점유되고; CORESET의 3개의 심볼들의 경우, 제7, 제8 및 제9 심볼들이 점유되고; CORESET의 4개의 심볼들의 경우, 제7, 제8, 제9 및 제10 심볼들이 점유되고; SSB에 대응하는 주파수 도메인 자원 이외의 자원은 주파수 도메인에서 점유된다. 또한 '제2 SSB의 CORESET와 제4 SSB의 CORESET 사이의 시간 도메인 간격'은 5ms와 동일하다.

[0179] 하위 구현 방식 4.3:

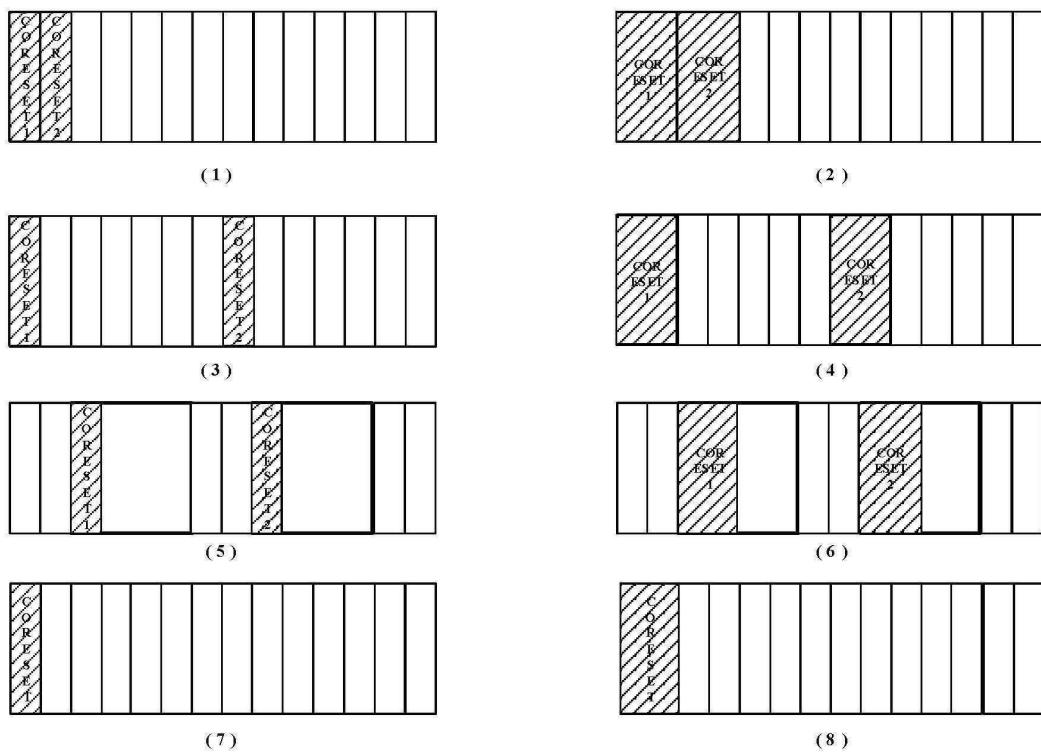

[0180] CORESET가 오직 SSB 외부의 슬롯에만 맵핑될 때, 도 17은 본 실시예에 따라 CORESET가 SSB 외부의 슬롯에 맵핑되는 개략도 I이고, 도 18은 본 실시예에 따라 CORESET가 SSB 외부의 슬롯에 맵핑되는 개략도 II이다. 도 17 및 도 18에 도시된 바와 같이, 슬롯에서 CORESET에 의해 점유된 심볼의 위치 정보는 다음 중 하나 이상을 포함한다.

[0181] 도 17 (1)의 구성에서, 슬롯은 2개의 CORESET들을 포함하고, CORESET들 각각은 1개의 심볼을 점유하고, CORESET들은 슬롯의 제1 및 제2 심볼들 상에 각각 위치된다.

[0182] 도 17 (2)의 구성에서, 슬롯은 2개의 CORESET들을 포함하고, CORESET들 각각은 2개의 심볼들을 점유한다. 일 실시예에서, 하나의 CORESET는 슬롯에서 제1 및 제2 심볼들에 맵핑되고, 다른 CORESET는 슬롯에서 제3 및 제4 심볼들에 맵핑된다.

[0183] 도 17 (3)의 구성에서, 슬롯은 2개의 CORESET들을 포함하고, CORESET들 각각은 1개의 심볼을 점유하고, CORESET들은 슬롯의 제1 및 제8 심볼들 상에 각각 위치된다.

[0184] 도 17 (4)의 구성에서, 슬롯은 2개의 CORESET들을 포함하고, CORESET들 각각은 2개의 심볼들을 점유한다. 일 실시예에서, 하나의 CORESET는 슬롯에서 제1 및 제2 심볼들에 맵핑되고, 다른 CORESET는 슬롯에서 제8 및 제9 심볼들에 맵핑된다.

[0185] 도 17 (5)의 구성에서, 슬롯은 2개의 CORESET들을 포함하고, CORESET들 각각은 1개의 심볼을 점유하고, CORESET들은 슬롯의 제3 및 제9 심볼들 상에 각각 위치된다.

[0186] 도 17 (6)의 구성에서, 슬롯은 2개의 CORESET들을 포함하고, CORESET들 각각은 2개의 심볼들을 점유한다. 일 실시예에서, 하나의 CORESET는 슬롯에서 제3 및 제4 심볼들에 맵핑되고, 다른 CORESET는 슬롯에서 제9 및 제10 심볼들에 맵핑된다.

[0187] 도 17 (7)의 구성에서, 슬롯은 1개의 CORESET를 포함하고, 이는 1개의 심볼을 점유한다. 일 실시예에서, CORESET는 슬롯에서 제1 심볼에 맵핑된다.

[0188] 도 17 (8)의 구성에서, 슬롯은 1개의 CORESET를 포함하고, 이는 2개의 심볼들을 점유한다. 일 실시예에서, CORESET는 슬롯에서 제1 및 제2 심볼들에 맵핑된다.

[0189] 구성 기간으로서 2개의 슬롯들을 갖는 도 18 (1)의 구성에서, 4개의 CORESET들이 포함되고, 각각의 CORESET는 1 개의 심볼을 포함하고: 제1 CORESET는 앞의 슬롯의 제5 심볼에 맵핑되고, 제2 CORESET는 앞의 슬롯의 제9 심볼에 맵핑되고, 제3 CORESET는 뒤의 슬롯의 제3 심볼에 맵핑되고, 제4 CORESET는 뒤의 슬롯의 제7 심볼에 맵핑된다.

[0190] 구성 기간으로서 2개의 슬롯들을 갖는 도 18 (2)의 구성에서, 4개의 CORESET들이 포함되고, 각각의 CORESET는 2 개의 심볼들을 포함하고: 제1 CORESET는 앞의 슬롯의 제5 및 제6 심볼들에 맵핑되고, 제2 CORESET는 앞의 슬롯의 제9 및 제10 심볼들에 맵핑되고, 제3 CORESET는 뒤의 슬롯의 제3 및 제4 심볼들에 맵핑되고, 제4 CORESET는 뒤의 슬롯의 제7 및 제8 심볼들에 맵핑된다.

[0191] 상기 구성들에서, 심볼에서 현재 사용되는 CORESET에 의해 점유된 심볼의 위치는 하기 방식들에 의해 단말에 표시될 수 있다.

[0192] 구현 방식 1에서 설명된 CORESET 대역폭 구성에 따르면, 단말은 현재 CORESET의 대역폭을 결정할 수 있고, CORESET 대역폭이 최소 채널 대역폭을 취할 때, 대역폭 값은 비교적 작기 때문에, CORESET들 및 SSB들에 대한 시분할 멀티플렉싱 방식이 바람직하다.

[0193] 반대로, CORESET 대역폭이 더 큰 값을 취할 때, 즉, 최소 UE 대역폭일 때, CORESET들 및 SSB들에 대한 주파수-분할 멀티플렉싱 방식이 바람직하다.

[0194] 또한, 구현 방식 3에서 설명되는 방식에 따르면, 단말은 CORESET가 위치되는 슬롯의 정보를 결정할 수 있다.

[0195] 하기 3개의 표들, 표 1, 표 2 및 표 3이 정의된다.

[0196] 표 1은, CORESET 대역폭이 '최소 채널 대역폭'으로서 구성되는 경우에 적용가능하고, CORESET가 위치되는 슬롯의 정보는 '제어 자원 세트가 동기화 신호 블록을 포함하는 슬롯에서 송신되는 것'이고; PBCH에서, 표 1의 8개

의 구성들 중 어느 것이 사용되는지를 3개의 비트들이 특히 단말에 표시한다.

[0197] 표 2는, CORESET 대역폭이 더 큰 값을 취하는 경우, 즉, '최소 UE 대역폭'에 적용가능하고, CORESET가 위치되는 슬롯의 정보는 '제어 자원 세트가 동기화 신호 블록을 포함하는 슬롯에서 송신되는 것'이고; PBCH에서, 표 2의 8개의 구성들 중 어느 것이 사용되는지를 3개의 비트들이 특히 단말에 표시한다.

[0198] 표 3은, CORESET가 위치되는 슬롯의 정보가, '제어 자원 세트가 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 것'인 경우에 적용가능하거나; 또는 CORESET의 서브캐리어 간격 및 동기화 신호 블록의 서브캐리어 간격은 상이하고, CORESET 및 동기화 신호 블록은 상이한 대역폭 부분들(Bandwidth Parts, BWP)에 속하고; PBCH에서, 표 3의 8개의 구성들 중 어느 것이 사용되는지를 3개의 비트들이 특히 단말에 표시한다.

표 1

| 인덱스 | CORESET OFDM<br>심볼들의 수 | 15kHz/30kHz (패턴 2) | 30kHz (패턴 1)/120kHz |

|-----|------------------------|--------------------|---------------------|

| 000 | 1                      | 도 15(1) 의 구성       | 도 16(1) 의 구성        |

| 001 | 1                      | 도 15(2) 의 구성       | 도 16(2) 의 구성        |

| 010 | 1                      | 도 15(3) 의 구성       | 도 16(3) 의 구성        |

| 011 | 1                      | 도 15(4) 의 구성       | 도 16(4) 의 구성        |

| 100 | 2                      | 도 15(5) 의 구성       | 도 16(5) 의 구성        |

| 101 | 2                      | 도 15(6) 의 구성       | 도 16(6) 의 구성        |

| 110 | 2                      | 도 15(7) 의 구성       | 도 16(7) 의 구성        |

| 111 | 2                      | 도 15(8) 의 구성       | 도 16(8) 의 구성        |

[0199]

표 2

| 인덱스 | CORESET OFDM<br>심볼들의 수 | 15kHz/30kHz (패턴 2) | 30kHz (패턴 1)/120kHz |

|-----|------------------------|--------------------|---------------------|

| 000 | 1                      |                    |                     |

| 001 | 2                      |                    |                     |

| 010 | 3                      | 도 15(9) 의 구성       | 도 16(9) 의 구성        |

| 011 | 4                      |                    |                     |

| 100 | 1                      |                    |                     |

| 101 | 2                      |                    |                     |

| 110 | 3                      |                    |                     |

| 111 | 4                      | 도 15(10) 의 구성      | 도 16(10) 의 구성       |

[0200]

표 3

| 인덱스 | CORESET OFDM<br>심볼들의 수 | 15kHz/30kHz (패턴 2) | 30kHz (패턴 1)/120kHz |

|-----|------------------------|--------------------|---------------------|

| 000 | 1                      | 도 17(1) 의 구성       |                     |

| 001 | 2                      | 도 17(2) 의 구성       |                     |

| 010 | 1                      | 도 17(3) 의 구성       |                     |

| 011 | 2                      | 도 17(4) 의 구성       |                     |

| 100 | 1                      | 도 17(5) 의 구성       | 도 18(1) 의 구성        |

| 101 | 2                      | 도 17(6) 의 구성       | 도 18(2) 의 구성        |

| 110 | 1                      | 도 17(7) 의 구성       |                     |

| 111 | 2                      | 도 17(8) 의 구성       |                     |

[0201]

구현 방식 5:

본 구현 방식은 CORESET 모니터링 윈도우(PDCCH 모니터링 윈도우) 구성 정보의 표시 방식을 설명한다.

[0204]

CORESET 모니터링 윈도우 구성 정보는, 하기 정보, 즉, CORESET의 모니터링 기간, 모니터링 윈도우의 시작 위치, 모니터링 윈도우의 시간 도메인 지속기간, 및 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋 중 적어도 하나를 포함한다.

[0205]

CORESET 모니터링 윈도우는 또한 물리적 다운링크 채널 PDCCH 모니터링 윈도우로 지칭되고, 각각의 모니터링 윈도우는 동기화 신호 블록에 대응하고, CORESET의 모니터링 윈도우는 하나 이상의 CORESET 모니터링 기회들, 즉, PDCCH를 송신하기 위한 하나 이상의 자원들을 포함한다. 기지국은 PDCCH 송신을 위해 CORESET 모니터링 윈도우에서 하나의 PDCCH 송신 자원을 선택하고, 단말은 CORESET 모니터링 윈도우에서 하나 이상의 PDCCH 송신 자원들 상에서 동기화 신호 블록에 대응하는 PDCCH를 수신하려 시도할 수 있다. 대응하는 모니터링 윈도우에서 동기화 신호 블록과 CORESET 또는 PDCCH 사이에 의사-공동-위치(Quasi-co-location, QCL) 관계가 존재한다.

[0206]

CORESET의 모니터링 기간은 또한 CORESET의 송신 기간으로서 이해될 수 있고, 기간의 값은 예를 들어, 40ms로서 미리 정의될 수 있다. 프로토콜에서 20ms, 40ms와 같이 복수의 모니터링 기간들의 값들을 미리 정의하는 것이 또한 가능하고, PBCH에서 현재 캐리어의 모니터링 기간의 특정 값이 1 비트로 표시된다.

[0207]

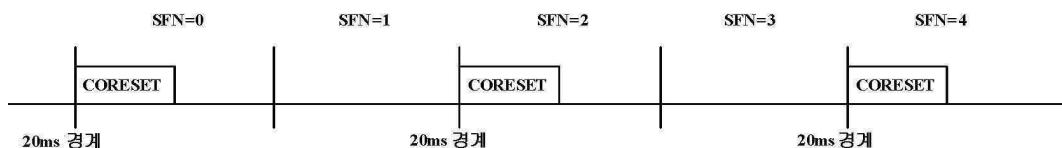

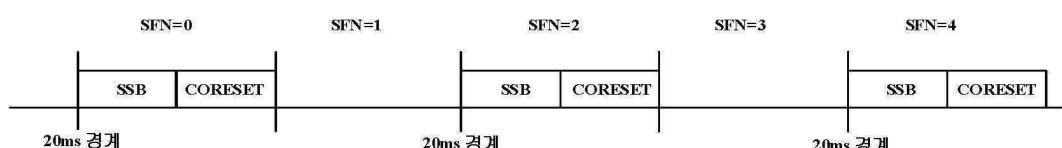

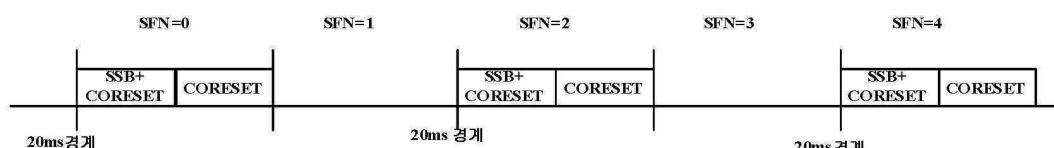

CORESET의 모니터링 윈도우의 시작 위치는 제1 CORESET 모니터링 윈도우의 시간 도메인 시작 위치를 지칭하고; 예로서 20ms의 CORESET 송신 기간에 있어서, CORESET가 동기화 신호 블록을 포함하는 슬롯에서 송신될 때, 모니터링 윈도우의 CORESET 시작 위치는 미리 정의된다. 도 19는 본 실시예에 따른 동기화 신호 블록을 포함하는 슬롯에서 CORESET가 송신되는 개략도이고, 도 19에 도시된 바와 같이, CORESET의 모니터링 윈도우의 시작 위치는 SFN mod 2=0을 갖는 무선 프레임의 시작 포인트이다.

[0208]

CORESET가 동기화 신호 블록을 포함하지 않는 슬롯에서 송신될 때, 모니터링 윈도우의 CORESET 시작 위치는 미리 정의된다. 도 20은 본 실시예에 따른 동기화 신호 블록을 포함하지 않는 슬롯에서 CORESET가 송신되는 개략도이고, 도 20에 도시된 바와 같이, CORESET의 모니터링 윈도우의 시작 위치는 SFN mod 2=0을 갖는 무선 프레임의 제6 서브프레임(즉, 제2 절반 프레임)이다.

[0209]

CORESET가 동기화 신호 블록을 포함하는 슬롯에서 송신되고 또한 동기화 신호 블록을 포함하지 않는 슬롯에서 송신될 때, 도 21은, 본 실시예에 따라, CORESET가 동기화 신호 블록을 포함하는 슬롯에서 송신되고 또한 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 개략도이다. (도 21에 도시된 바와 같이, 동기화 신호 블록이 위치되는 슬롯에서 송신되는 CORESET의 경우, 그 모니터링 윈도우의 시작 위치는 SFN mod 2=0을 갖는 무선 프레임의 시작 포인트이고; 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 CORESET의 경우, 그 모니터링 윈도우의 시작 위치는 SFN mod 2=0을 갖는 무선 프레임의 제6 서브프레임(즉, 제2 절반 프레임)이다).

[0210]

CORESET의 모니터링 윈도우의 시간 도메인 지속기간은 하나 이상의 슬롯들인데; 예를 들어, 모니터링 윈도우의

시간 도메인 지속기간은 다음 중 하나 이상이다: 1개의 슬롯, 2개의 슬롯들, 4개의 슬롯들 또는 M개의 슬롯들, 여기서 M은 동기화 신호 블록 송신 기간에서 동기화 신호 블록들에 의해 점유된 슬롯들의 수이다.

[0211] 동기화가 위치되는 슬롯에서 CORESET가 송신될 때, 모니터링 윈도우의 시간 도메인 지속기간은 1개 슬롯이고; 동기화 신호 블록을 포함하지 않는 슬롯에서 CORESET가 송신될 때, 모니터링 윈도우의 시간 도메인 지속기간은 하나 이상의 슬롯들일 수 있다.

[0212] 현재 캐리어의 CORESET 모니터링 윈도우의 시간 도메인 지속기간을 단말에 표시하기 위해 PBCH의 CORESET 구성 정보 표시 필드에 표시 비트가 도입될 수 있다. 예를 들어, 표시를 위해 2개의 비트들이 사용되며, '00'은 '모니터링 윈도우의 시간 도메인 지속기간이 1개 슬롯인 것'을 표현하고, '01'은 '모니터링 윈도우의 시간 도메인 지속기간이 2개 슬롯들인 것'을 표현하고, '10'은 '모니터링 윈도우의 시간 도메인 지속기간이 M개 슬롯들인 것'을 표현하고, '11'은 '상태 예비'를 표현한다.

[0213] 대안적으로, CORESET 모니터링 윈도우의 상기 4가지 유형들의 시간 도메인 지속기간 중 오직 임의의 2개가 포함되고, 현재 캐리어에 대해 특히 어느 구성이 사용되는지를 표시하기 위해 PBCH에서 1 비트가 추가로 사용되는 것이 프로토콜에서 특정되는데; 예를 들어, '0'은 '모니터링 윈도우의 시간 도메인 지속기간이 1개 슬롯인 것'을 표현하고, '1'은 '모니터링 윈도우의 시간 도메인 지속기간이 2개 슬롯들인 것'을 표현한다.

[0214] 대안적으로, CORESET 모니터링 윈도우의 시간 도메인 지속기간은 하기 3가지 유형들, 즉, 1개 슬롯, 2개 슬롯들 및 4개 슬롯들 중 하나에서 구성될 수 있고; CORESET 모니터링 윈도우의 시간 도메인 송신 자원들 및 모니터링 윈도우의 시간 도메인 지속기간은 공동으로 표시되고, 총 2개의 비트들이 점유되어, 예를 들어,

[0215] '00': CORESET는 SS/PBCH 블록을 포함하는 슬롯에서 송신되고, CORESET 모니터링 윈도우 길이는 1개 슬롯과 동일하고;

[0216] '01': CORESET는 SS/PBCH 블록을 포함하지 않는 슬롯에서 송신되고, CORESET 모니터링 윈도우 길이는 1개 슬롯과 동일하고;

[0217] '10': CORESET는 SS/PBCH 블록을 포함하지 않는 슬롯에서 송신되고, CORESET 모니터링 윈도우 길이는 2개 슬롯들과 동일하고;

[0218] '11': CORESET는 SS/PBCH 블록을 포함하지 않는 슬롯에서 송신되고, CORESET 모니터링 윈도우 길이는 4개 슬롯들과 동일하고;

[0219] 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋은 다음 중 하나 이상을 포함한다: 0, 모니터링 윈도우의 시간 도메인 지속기간, 및 모니터링 윈도우의 시간 도메인 지속기간의 1/X 중 적어도 하나를 포함하고, X는 1 초과의 정수이고, 그 값은 프로토콜에서 미리 정의되거나 시그널링에 의해 표시될 수 있다.

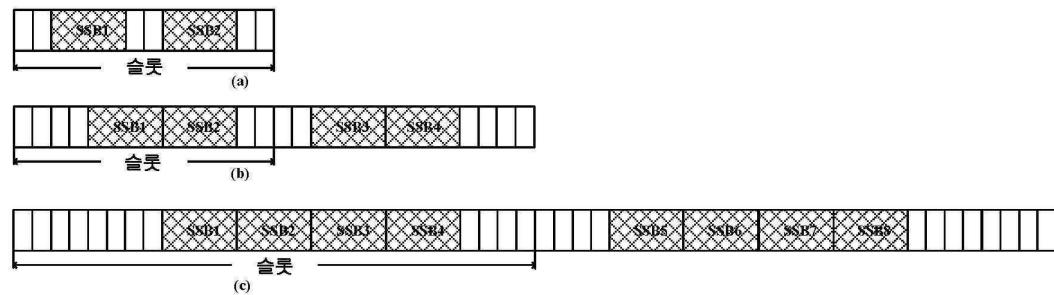

[0220] 도 22는 본 실시예에 따라 동기화 신호 블록이 위치되는 슬롯에서 CORESET가 송신되는 개략도이다. 도 22에 도시된 바와 같이, 동기화 신호 블록이 위치되는 슬롯에서 CORESET가 송신되고, CORESET 및 대응하는 SSB가 주파수-분할 멀티플렉싱되고 송신될 때, 모니터링 윈도우의 시간 도메인 지속기간은 1개 슬롯이고, 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋은 모니터링 윈도우의 시간 도메인 지속기간, 즉, 1개 슬롯과 동일하다. 이러한 경우, 인접한 모니터링 윈도우들 사이에 어떠한 중첩도 없다. 도 22에서, 포함된 8개의 동기화 신호 블록들이 동기화 신호 및 물리적 브로드캐스트 채널을 송신하기 위한 자원들로서 사용될 수 있고, 기지국은 이를 중 일부 또는 전부를 실제 송신되는 동기화 신호 블록들(실제 SSB들)로서 선택할 수 있다.

[0221] 도 23은 본 실시예에 따라 CORESET가 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 개략도 I이다. 도 23에서, CORESET는 동기화 신호 블록을 포함하지 않는 슬롯, 즉, 동기화 신호 블록이 위치되는 무선 프레임의 제2 절반 프레임에서 송신되고, 모니터링 윈도우의 시간 도메인 지속기간은 1개 슬롯이고, 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋은 모니터링 윈도우의 시간 도메인 지속기간, 즉, 1개 슬롯과 동일하다. 이러한 경우, 인접한 모니터링 윈도우들 사이에 어떠한 중첩도 없다. 도 23의 파선 블록들은 의사 동기화 신호 블록들(의사 SSB들)이고, CORESET의 송신은 또한 이러한 의사 동기화 신호 블록들을 회피하고, 슬롯에서 CORESET에 의해 점유된 자원들은 도 22의 자원과 동일하다. 이러한 구성의 이점은, 동기화 신호 블록들의 송신 기간이 5ms일 때, 다음 기간의 동기화 신호 블록들은 또한, CORESET가 위치되는 슬롯에서 송신될 것이고, CORESET의 송신이 동기화 신호 블록들을 송신하기 위한 자원들을 회피하기 때문에, 동기화 신호 블록들의 송신 기간이 5ms인 경우에도, 둘 사이에 어떠한 충돌도 없다. 단말은 현재 캐리어의 실제 동기화 신호 블록 송신 기간을 알 필요가 없다.

- [0222] 도 24는 본 실시예에 따라 CORESET가 동기화 신호 블록을 포함하지 않는 슬롯에서 송신되는 개략도 II이다. 도 24에 도시된 바와 같이, CORESET는 동기화 신호 블록을 포함하지 않는 슬롯, 즉, 동기화 신호 블록이 위치되는 무선 프레임의 제2 절반 프레임에서 송신되고, 모니터링 윈도우의 시간 도메인 지속기간은 2개 슬롯들이고, 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋은 모니터링 윈도우의 시간 도메인 지속기간의 1/2, 즉, 1개 슬롯과 동일하다. 이어서, 인접한 모니터링 윈도우들이 부분적으로 중첩한다. 일 실시예에서, 동기화 신호 블록이 위치되는 슬롯에서 제2 동기화 신호 블록은 실제로 송신되고, 이러한 동기화 신호 블록은 모니터링 윈도우 1, 즉, 제2 절반 프레임의 제2 및 제3 슬롯들에 대응하고, 이러한 2개의 슬롯들은 4개의 CORESET 송신 자원들을 포함하고, 기지국은 동기화 신호 블록에 대응하는 CORESET를 송신하기 위해 이들 중 하나를 선택한다. 유사하게, 슬롯 2의 제1 동기화 신호 블록은 실제로 송신되고, 이는 모니터링 윈도우 2, 즉, 제3 및 제4 슬롯들에 대응하고, 기지국은 이러한 동기화 신호 블록에 대응하는 CORESET를 송신하기 위해 2개의 슬롯들에서 CORESET 송신 자원들 중 하나를 선택한다.

- [0223] 상이한 동기화 신호 블록들에 대응하는 CORESET들은 동일한 CORESET 송신 자원들을 점유할 수 없고; 따라서 CORESET 송신 자원들이 후속 동기화 신호 블록들에 대한 대응하는 모니터링 윈도우들에서 선택될 때, 점유된 CORESET 송신 자원들을 회피할 필요가 있음에 유의해야 한다.

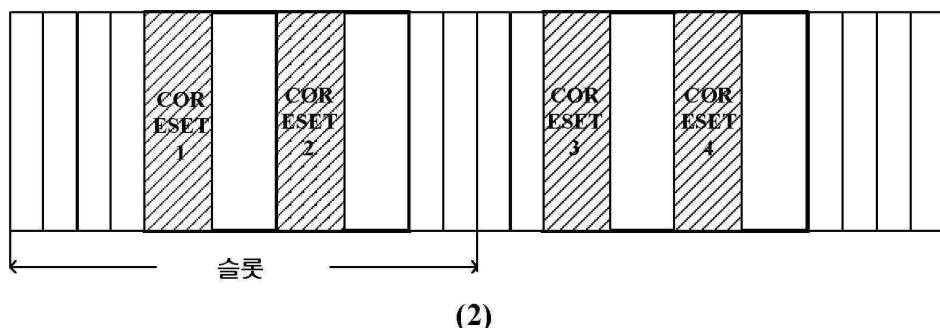

- [0224] 도 25는 본 실시예에 따라 모든 동기화 신호 블록들이 동일한 CORESET 모니터링 윈도우에 대응하는 개략도이다. 도 25에 도시된 바와 같이, 모든 동기화 신호 블록들은 동일한 CORESET 모니터링 윈도우에 대응한다. 일 실시예에서, 동기화 신호 블록들을 포함하는 4개의 슬롯들은 8개의 동기화 신호 블록 자원들을 포함하고, 이러한 경우, 동기화 신호 블록들 중 오직 2개만이 송신되고, 8개의 동기화 신호 블록들은 동일한 CORESET 모니터링 윈도우에 대응하고, 모니터링 윈도우는 8개의 CORESET 송신 자원들을 포함하고; 단말에 대해, 어느 동기화 신호 블록이 수신되는지와 무관하게, 이러한 모니터링 윈도우에서 8개의 CORESET 모니터링 기회를 상에서 대응하는 CORESET를 수신하려 시도할 필요가 있다.

- [0225] 도 26은 본 실시예에 따라 복수의 동기화 신호 블록들이 하나의 CORESET 모니터링 윈도우에 대응하는 개략도이다. 도 26에 도시된 바와 같이, 복수의 동기화 신호 블록들은 하나의 CORESET 모니터링 윈도우에 대응한다. 일 실시예에서, 동기화 신호 블록들을 포함하는 4개의 슬롯들은 8개의 동기화 신호 블록 자원들을 포함하고, 이러한 경우, 처음 4개의 동기화 신호 블록들이 실제로 송신되고, 처음 2개의 슬롯들에서 4개의 동기화 신호 블록들은 제1 CORESET 모니터링 윈도우에 대응하고(시간 도메인에서 처음 2개의 의사 동기화 신호 블록 슬롯들에 대응함), 마지막 2개의 슬롯들에서 4개의 동기화 신호 블록들은 제2 CORESET 모니터링 윈도우에 대응하고(시간 도메인에서 제3 및 제4 의사 동기화 신호 블록 슬롯들에 대응함); 단말에 대해, 처음 4개의 SSB들 중 하나가 수신될 때, 모니터링 윈도우 1에서 8개의 CORESET 모니터링 기회를 상에서 대응하는 CORESET를 수신하려 시도할 필요가 있고, 마지막 4개의 SSB들 중 하나가 수신될 때, 모니터링 윈도우 2에서 8개의 CORESET 모니터링 기회를 상에서 대응하는 CORESET를 수신하려 시도할 필요가 있다.

- [0226] 현재 캐리어의 인접한 CORESET 모니터링 윈도우들 사이의 시간 도메인 오프셋을 단말에 표시하기 위해 PBCH의 CORESET 구성 정보 표시 필드에 표시 비트가 도입될 수 있다. 예를 들어, 표시를 위해 2개의 비트들이 사용되며, '00'은 '인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋이 0인 것'을 표현하고, '01'은 '인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋이 모니터링 윈도우 길이인 것'을 표현하고, '10'은 '인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋이 모니터링 윈도우 길이의 1/X인 것'을 표현하고, '11'은 '상태 예비'를 표현한다. X는 1 초과의 정수이고, 그 값은 프로토콜에서 특정되거나 시그널링에 의해 표시될 수 있다.

- [0227] 상기 표시 방법에서, 2-비트 표시 오버헤드를 도입하는 것이 필요하고, 이러한 오버헤드를 감소시키기 위해, 상이한 종류의 모니터링 윈도우의 시간 도메인 지속기간에 따라 인접한 모니터링 윈도우들 사이의 시간 도메인 오버헤드의 유형을 제한하는 것이 또한 가능하다. 예를 들어, 모니터링 윈도우 길이가 1개 슬롯일 때, 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋에 대해 오직 2개의 가능성들만이 존재하는 것이 특정되고: 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋은 모니터링 윈도우 길이이거나(즉, 인접한 모니터링 윈도우들은 중첩하고 연속적으로 구성됨), 또는 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋은 모니터링 윈도우의 시간 도메인 지속기간의 1/X이다(즉, 인접하는 모니터링 윈도우들은 부분적으로 중첩한다). 이러한 경우, 오프셋 값을 표시하기 위해 오직 1 비트만이 필요하고, 예를 들어, '0'은 '인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋이 모니터링 윈도우 길이인 것'을 표현하고, '1'은 '인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋이 모니터링 윈도우 길이의 1/X인 것'을 표현한다. 유사하게, X는 1 초과의 정수이고, 그 값은 프로토콜에서 특정되거나 시그널링에 의해 표시될 수 있다.

- [0228] 모니터링 윈도우 길이가 1개 슬롯 초과인 경우, 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋에 대해 오직 2개의 가능성들만이 존재하는 것이 특정되고: 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋은 0이거나(즉, 인접한 모니터링 윈도우들은 완전히 중첩됨), 또는 인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋은 모니터링 윈도우 길이 1/X이다(즉, 인접하는 모니터링 윈도우들은 부분적으로 중첩한다). 이러한 경우, 오프셋 값을 표시하기 위해 오직 1 비트만이 필요하고, 예를 들어, '0'은 '인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋이 0인 것'을 표현하고, '1'은 '인접한 모니터링 윈도우들 사이의 시간 도메인 오프셋이 모니터링 윈도우 길이의 1/X인 것'을 표현한다. 유사하게, X는 1 초과의 정수이고, 그 값은 프로토콜에서 특정되거나 시그널링에 의해 표시될 수 있다.

- [0229] 본 출원에서, 개개의 구현 방식들에서 기술적 특징들은 충돌 없이 하나의 구현 방식에서 조합하여 사용될 수 있다. 각각의 구현 방식은 단지 본 출원의 최적의 구현 방식이다.

- [0230] 이러한 실시예는 공통 제어 정보 블록 구성 정보의 송신 방법을 제공하고, 이러한 솔루션으로, 제어 자원 세트의 시간 및 주파수 도메인 자원 위치들은 PBCH들의 조합된 수신에 영향을 미치지 않고 효과적으로 표시될 수 있다(즉, 각각의 SS 블록의 PBCH 콘텐츠가 동일한 것이 보장된다). 또한, 인접한 SS 블록들에 대응하는 모니터링 윈도우들 사이의 시간 도메인 오프셋 및 제어 자원 세트 모니터링 윈도우의 시간 도메인 지속기간을 구성함으로써, 공통 제어 블록의 송신 자원들은 더 유연하며, 공통 제어 블록 송신에 대한 버스트 트래픽 송신의 영향은 양호하게 회피된다.

- [0231] 실시예 4

- [0232] 본 출원의 일 실시예는 저장 매체를 추가로 제공하고, 저장 매체는 저장된 프로그램을 포함하고, 상기 프로그램이 실행될 때 전술한 것 중 임의의 하나에 따른 방법이 실행된다.

- [0233] 본 실시예에서, 상기 저장 매체는 하기 단계(S1) 및 단계(S2)를 실행하기 위한 프로그램 코드들을 저장하도록 구성될 수 있다:

- [0234] 단계(S1)에서, 제어 자원 세트의 구성 정보는 물리적 브로드캐스트 채널 상에서 반송되고, 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보 및 주파수 도메인 위치 정보 중 적어도 하나를 단말에 표시하기 위해 사용된다.

- [0235] 단계(S2)에서, 제어 자원 세트는 구성 정보에 따라 단말에 송신된다.

- [0236] 일 실시예에서는, 본 실시예에서 상기 저장 매체가 USB 플래시 드라이브, 판독 전용 메모리(Read-Only Memory, ROM), 랜덤 액세스 메모리(Random Access Memory, RAM), 착탈식 하드 디스크, 자기 디스크 또는 광학 디스크와 같은, 프로그램 코드들을 저장할 수 있는 임의의 매체를 포함할 수 있지만, 이에 제한되는 것은 아니다.

- [0237] 본 출원의 일 실시예는 프로세서를 추가로 제공하고, 프로세서는 프로그램을 실행하도록 구성되고, 프로그램이 실행될 때 상기 방법들 중 임의의 하나에 따른 단계가 실행된다.

- [0238] 본 실시예에서, 상기 프로그램은 하기 단계(S1) 및 단계(S2)를 실행하기 위해 사용된다:

- [0239] 단계(S1)에서, 제어 자원 세트의 구성 정보는 물리적 브로드캐스트 채널 상에서 반송되고, 구성 정보는 제어 자원 세트의 시간 도메인 위치 정보 및 주파수 도메인 위치 정보 중 적어도 하나를 단말에 표시하기 위해 사용된다.

- [0240] 단계(S2)에서, 제어 자원 세트는 구성 정보에 따라 단말에 송신된다.

- [0241] 일 실시예에서, 본 실시예의 특정 예는 상기 실시예 및 선택적인 구현 방식에서 설명된 예를 지칭할 수 있고, 이는 본 명세서에서 과도하게 반복되지 않을 것이다.

- [0242] 명백하게, 당업자들은, 본 출원의 상기 각각의 모듈 또는 각각의 단계가 범용 컴퓨팅 디바이스들에 의해 구현될 수 있고, 이들이 단일 컴퓨팅 디바이스 상에 집중되거나 또는 복수의 컴퓨팅 디바이스들로 이루어진 네트워크를 통해 분산될 수 있고; 일 실시예에서, 이들이 컴퓨팅 디바이스의 실행가능한 프로그램 코드들에 의해 구현될 수 있고, 따라서 이들이 컴퓨팅 디바이스에 의한 실행을 위해 저장 디바이스에 저장될 수 있고; 일부 경우들에서, 예시된 또는 설명된 단계들이 본 명세서의 순서와는 상이한 순서로 실행될 수 있거나, 이들이 개별적인 집적 회로 모듈들에 각각 제조되거나, 이들의 복수의 모듈들 또는 단계들이 단일 집적 회로 모듈에 제조됨으로써 구현되는 것을 이해해야 한다. 따라서, 본 출원은 하드웨어 및 소프트웨어의 임의의 특정 조합으로 제한되지 않는

다.

### 도면

#### 도면1

#### 도면2

#### 도면3

#### 도면4

## 도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10

## 도면11

## 도면12

## 도면13

## 도면14

## 도면15

도면16

도면17

## 도면18

## 도면19

## 도면20

## 도면21

### 도면22

### 도면23

### 도면24

## 도면25

## 도면26