(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5662702号

(P5662702)

(45) 発行日 平成27年2月4日(2015.2.4)

(24) 登録日 平成26年12月12日(2014.12.12)

(51) Int.Cl.

G06T 3/60 (2006.01)

H04N 1/387 (2006.01)

F 1

G06T 3/60

H04N 1/387

請求項の数 12 (全 14 頁)

(21) 出願番号 特願2010-124613 (P2010-124613)

(22) 出願日 平成22年5月31日 (2010.5.31)

(65) 公開番号 特開2011-253218 (P2011-253218A)

(43) 公開日 平成23年12月15日 (2011.12.15)

審査請求日 平成25年5月30日 (2013.5.30)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】 画像処理装置、画像処理方法

## (57) 【特許請求の範囲】

## 【請求項 1】

入力画像を格納する格納手段と、

前記入力画像を変形させるための指示を取得する取得手段と、

前記指示に応じた変形後の画像を含む表示画面を生成するために、前記入力画像の画像データの参照が必要であるか否かを、前記表示画面を構成する複数の領域のそれぞれについて判定することで、前記表示画面の生成のために、前記入力画像の画像データの参照が必要となる回数を、前記入力画像を構成する複数の領域のそれぞれについて判定する判定手段と、

前記表示画面の生成のために、前記入力画像を構成する一の領域の画像データが参照された回数が、前記判定手段により判定された回数に達すると、前記一の領域の前記画像データを格納する前記格納手段の領域が上書き可能となるように制御する制御手段とを備えることを特徴とする画像処理装置。

## 【請求項 2】

前記指示は、前記入力画像を回転させる指示であることを特徴とする請求項 1 に記載の画像処理装置。

## 【請求項 3】

前記判定手段は、前記表示画面を生成するための前記入力画像の画像データの参照順序をさらに判定し、

前記制御手段は、前記判定手段により判定された参照順序に基づいて、前記格納手段よ

りも読み出し速度が遅い前記画像処理装置の記憶手段から前記格納手段へ画像データを移動するタイミングを制御することを特徴とする請求項1又は2に記載の画像処理装置。

**【請求項4】**

前記判定手段は、前記入力画像から前記表示画面の生成のための写像行列を用いて、前記入力画像の画像データの参照が必要であるか否かの前記判定を行うことを特徴とする請求項1乃至3の何れか1項に記載の画像処理装置。

**【請求項5】**

前記判定手段は、前記表示画面に対応する画素ブロックごとに、前記入力画像の画像データの参照が必要であるか否かを、前記表示画面の走査順に従って判定することで、前記入力画像の画像データの参照順序を判定することを特徴とする請求項3に記載の画像処理装置。

10

**【請求項6】**

前記表示画面は矩形であることを特徴とする請求項1乃至5の何れか1項に記載の画像処理装置。

**【請求項7】**

前記制御手段は、前記一の領域の画像データが参照された回数が、前記判定手段により判定された回数に達すると、前記一の領域の前記画像データを前記格納手段から削除することを特徴とする請求項1乃至6の何れか1項に記載の画像処理装置。

**【請求項8】**

前記入力画像を格納する格納手段を有する画像処理装置が行う画像処理方法であって、前記入力画像を変形させるための指示を取得する取得工程と、前記指示に応じた変形後の画像を含む表示画面を生成するために、前記入力画像の画像データの参照が必要であるか否かを、前記表示画面を構成する複数の領域のそれぞれについて判定することで、前記表示画面の生成のために、前記入力画像の画像データの参照が必要となる回数を、前記入力画像を構成する複数の領域のそれぞれについて判定工程と、前記表示画面の生成のために、前記入力画像を構成する一の領域の画像データが参照された回数が、前記判定工程で判定された回数に達すると、前記一の領域の前記画像データを格納する前記格納手段の領域が上書き可能となるように制御する制御工程とを備えることを特徴とする画像処理方法。

20

前記表示画面の生成のために、前記入力画像を構成する一の領域の画像データが参照された回数が、前記判定工程で判定された回数に達すると、前記一の領域の前記画像データを格納する前記格納手段の領域が上書き可能となるように制御する制御工程とを備えることを特徴とする画像処理方法。

30

**【請求項9】**

前記判定工程では、前記表示画面を生成するための前記入力画像の画像データの参照順序をさらに判定し、

前記制御工程では、前記判定工程で判定された参照順序に基づいて、前記格納手段よりも読み出し速度が遅い前記画像処理装置の記憶手段から前記格納手段へ画像データを移動するタイミングを制御することを特徴とする請求項8に記載の画像処理方法。

**【請求項10】**

前記判定工程では、前記入力画像から前記表示画面の生成のための写像行列を用いて、前記入力画像の画像データの参照が必要であるか否かの前記判定を行うことを特徴とする請求項8又は9に記載の画像処理方法。

40

**【請求項11】**

前記判定工程では、前記表示画面に対応する画素ブロックごとに、前記入力画像の画像データの参照が必要であるか否かを、前記表示画面の走査順に従って判定することで、前記入力画像の画像データの参照順序を判定することを特徴とする請求項9に記載の画像処理方法。

**【請求項12】**

コンピュータを請求項1乃至7の何れか1項に記載の画像処理装置の各手段として機能させるためのコンピュータプログラム。

**【発明の詳細な説明】**

**【技術分野】**

50

**【0001】**

本発明は、画像管理技術に関するものである。

**【背景技術】****【0002】**

幾何変形などの画像の変形を伴う処理では、入力画像と出力画像の画素位置が異なるため、フレームメモリなどの記憶部を介して出力画像を生成する方法が用いられる。フレームメモリ用の記憶部には入力画像と同等のデータサイズを格納できることが要求されるため、一般にダイナミックRAM(DRAM)等の安価で大容量な第一記憶部が使用される。DRAMはスタティックRAM(SRAM)に対し、構造的に比較的安価にサイズの大きな記憶部を実現可能であるが、データのアクセスレイテンシが比較的長いという欠点をもつ。10

**【0003】**

DRAMを用いた処理の場合、DRAMのアクセスレイテンシが比較的長いため、DRAMのメモリアクセスがボトルネックとなって処理のスループットが低下するという現象が通常起こりえる。具体的には、画像処理モジュールがDRAM上の任意アドレスのデータを要求してからデータが帰ってくるまでのアクセスレイテンシが長いため、その間は画像処理モジュールの処理が停止し、処理モジュール単体の持つピーク性能に対しスループットが低下する。この問題を解決する方法として、スタティックRAM(SRAM)等の、サイズ当たりのコストは高価だがアクセスレイテンシが短い補助記憶部を持ち、必要なデータを予め部分的にSRAM内に格納しておくことで処理のスループットを向上させる方法がある。20

**【0004】**

必要なデータを予めSRAM内に格納するための1つ目の方法として、プリフェッチという方法がある。プリフェッチを用いると、処理モジュールが次に必要とするデータのDRAM上のアドレスを前もって発行してSRAMにデータを格納し、処理モジュールが実際にこのデータを必要とするときまでにSRAMにこのデータを格納した状態にすることができる。この様にすることで、DRAMのアクセスレイテンシを隠ぺいし、処理モジュールを停止する事無く動作させることが可能になるため、スループットを向上させることが出来る。30

**【0005】**

必要なデータを予めSRAM内に格納するための2つ目の方法として特許文献1に記載の方法がある。特許文献1では、画像の回転処理を行う際に、入力画像を複数の画像ブロックに分割し、回転角度に応じた順序で画像ブロックを第一記憶部から読み出して補助記憶部(文献中にはバッファメモリと表記)に格納する。次に回転角度に応じた順序でバッファメモリの画像ブロックからピクセルデータを読み出す。第一記憶部からの画像ブロックの回転角度に応じた読み出しと、補助記憶部からのピクセルデータの回転角度に応じた読み出しを、入力画像の全ての画像ブロックに適用することで入力画像の回転を行う。30

**【0006】**

特許文献1の方法によれば、画像ブロックの読み出し順序は回転角度によって一意に決まる。また、個々の画像ブロックの回転処理は画像ブロック内で完結するため、第一記憶部上へのアクセスアドレスを記憶しておけば、アドレス計算を逐次行う事無くプリフェッチと同等の技術を実現できる。40

**【先行技術文献】****【特許文献】****【0007】**

【特許文献1】特開2002-125116号公報

**【発明の概要】****【発明が解決しようとする課題】****【0008】**

1つ目の従来技術では、画像処理モジュールはプリフェッチの為の機構を備えなければ

50

ならない。プリフェッヂは画像処理モジュールのデータ消費に先行して実行されなければならぬため、画像処理モジュールは2つの独立したアドレス発行機構（フェッヂ、プリフェッヂ）を持つ必要がある。幾何変形などの画像の変形を伴う処理では、アドレス発行機構が画像処理モジュールの回路全体に占める割合は比較的大きく、コスト・消費電力の面で問題がある。

【0009】

2つ目の従来技術では、アドレス計算を逐次行う事無くプリフェッヂと同等のことが可能であるものの、画像の回転角度は単一の画像ブロック内で完結する角度に限られるという問題がある。具体的には画像ブロックが矩形であった場合、処理可能な回転角度は90度の倍数に制限され、任意の形状変形は行えない。

10

【0010】

本発明は以上の問題に鑑みてなされたものであり、画像変形処理回路において比較的大きな割合を占めるプリフェッヂの機構を持たずに任意の形状変形を実現するための技術を提供することを目的とする。

【課題を解決するための手段】

【0011】

本発明の目的を達成するために、本発明の一例としての画像処理装置は以下の構成を備える。即ち、入力画像を格納する格納手段と、

前記入力画像を変形させるための指示を取得する取得手段と、

前記指示に応じた変形後の画像を含む表示画面を生成するために、前記入力画像の画像データの参照が必要であるか否かを、前記表示画面を構成する複数の領域のそれぞれについて判定することで、前記表示画面の生成のために、前記入力画像の画像データの参照が必要となる回数を、前記入力画像を構成する複数の領域のそれぞれについて判定する判定手段と、

20

前記表示画面の生成のために、前記入力画像を構成する一の領域の画像データが参照された回数が、前記判定手段により判定された回数に達すると、前記一の領域の前記画像データを格納する前記格納手段の領域が上書き可能となるように制御する制御手段と

を備えることを特徴とする。

【発明の効果】

【0012】

本発明の構成によれば、画像変形処理回路において比較的大きな割合を占めるプリフェッヂの機構を持たずに任意の形状変形を実現することができ、これより回路規模を削減することができる。

30

【図面の簡単な説明】

【0013】

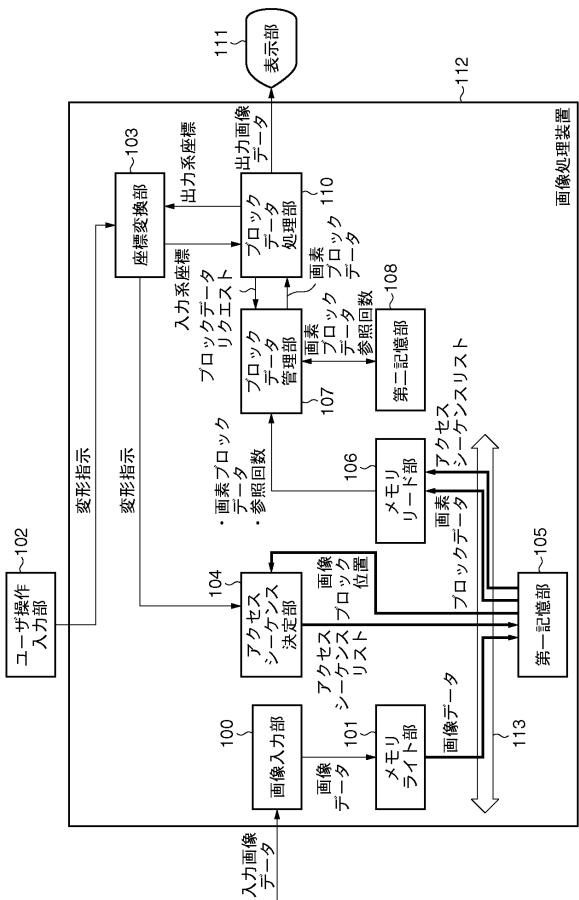

【図1】画像処理装置の機能構成例を示すブロック図。

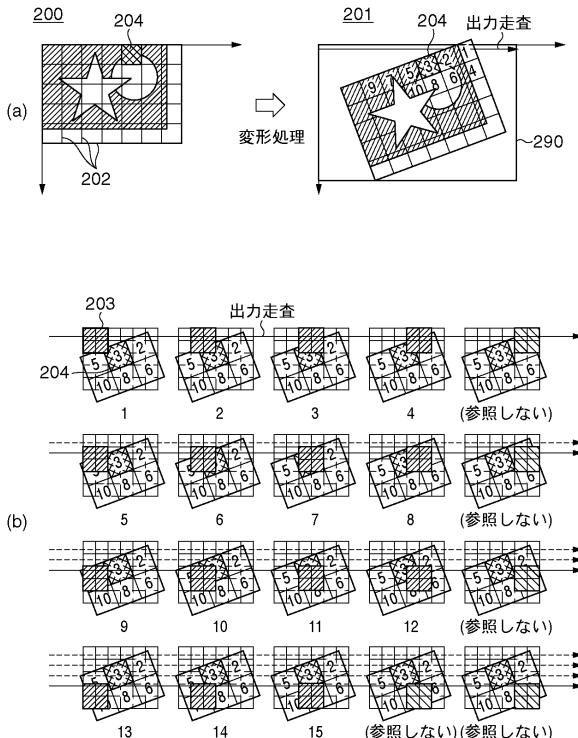

【図2】アクセスシーケンスリストを説明する図。

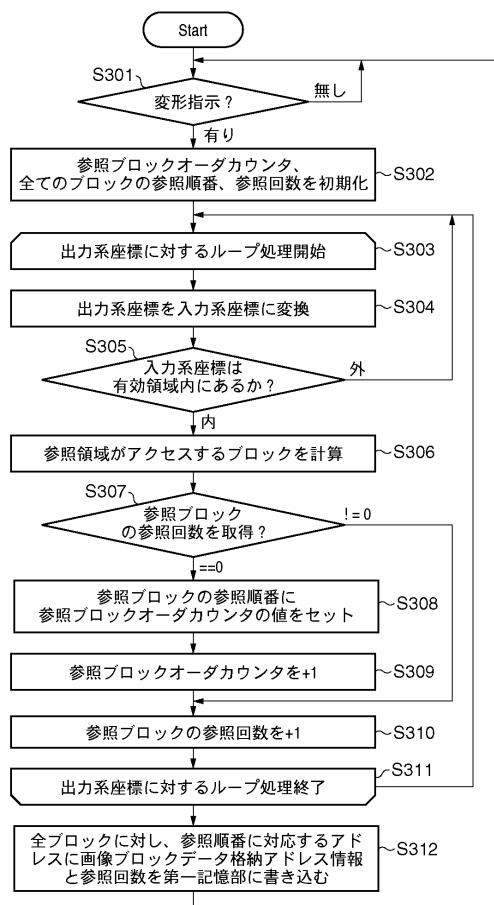

【図3】アクセスシーケンス決定部104が行う処理のフローチャート。

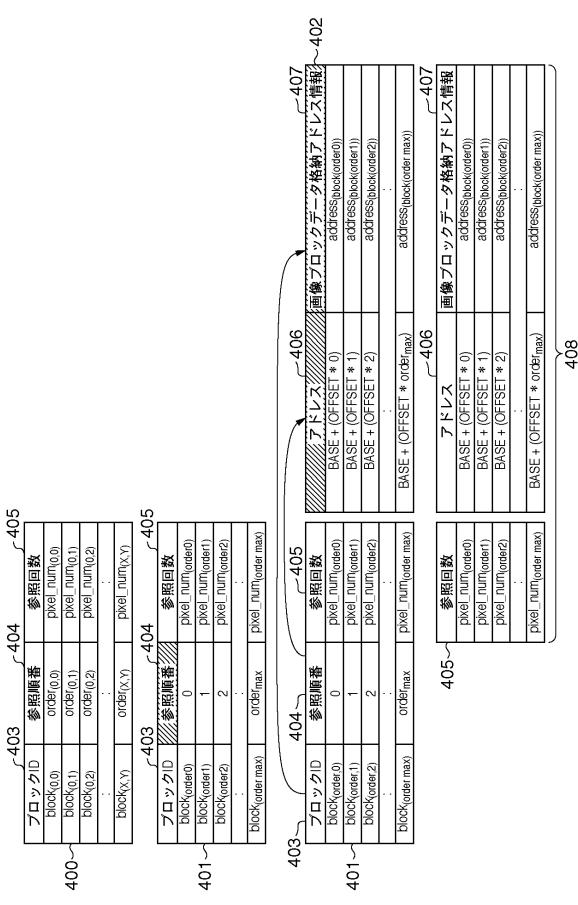

【図4】アクセスシーケンスリストが作成される過程を示す図。

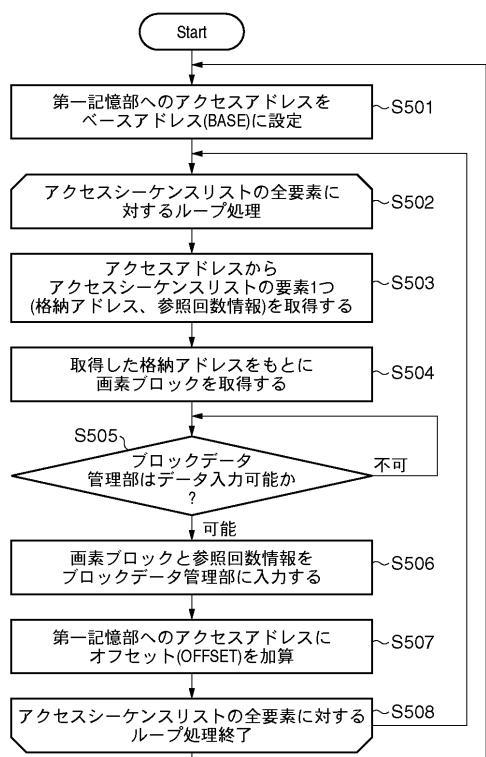

【図5】メモリリード部106が行う処理のフローチャート。

40

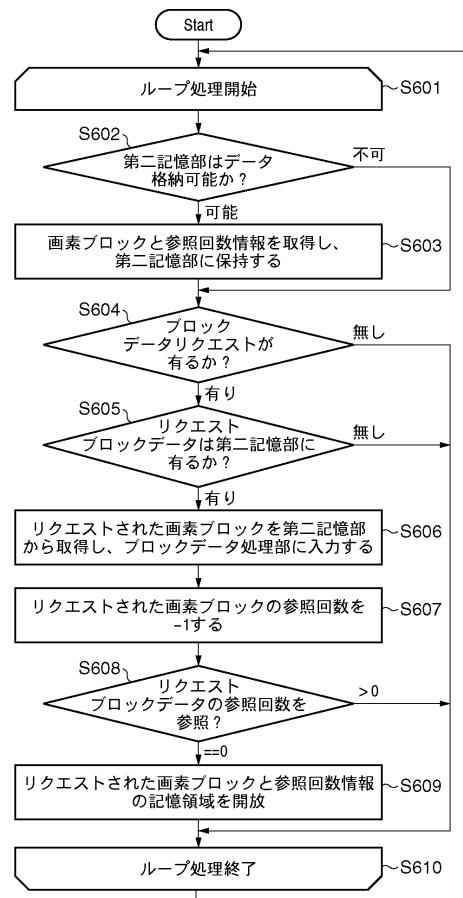

【図6】ブロックデータ管理部107が行う処理のフローチャート。

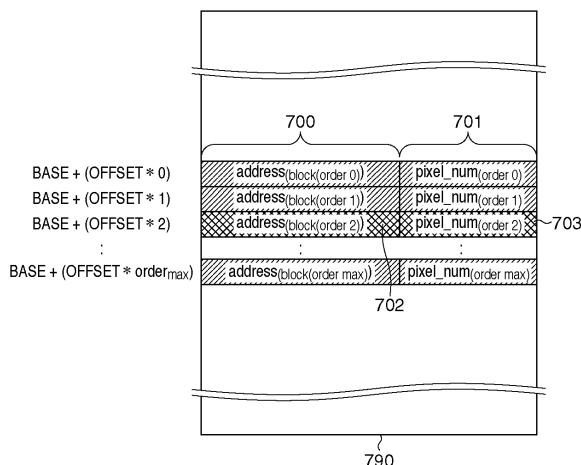

【図7】アクセスシーケンスリストを説明する図。

【発明を実施するための形態】

【0014】

以下、添付図面を参照し、本発明の好適な実施形態について説明する。なお、以下説明する実施形態は、本発明を具体的に実施した場合の一例を示すもので、特許請求の範囲に記載の構成の具体的な実施例の1つである。

【0015】

[第1の実施形態]

先ず、本実施形態に係る画像処理装置について、図1のブロック図を用いて説明する。

50

本実施形態に係る画像処理装置 112 は、画像入力部 100 を介して外部の装置から入力された入力画像を先ず、第一記憶部 105 に格納する。そして画像処理装置 112 はブロックデータ処理部 110 を用いて、この入力画像の形状を幾何的に変形させる幾何変形処理を行い、変形画像を生成する。この変形内容を示す変形指示は、ユーザがユーザ操作入力部 102 を用いて行う。以下に、この画像処理装置 112 の動作について、より詳細に説明する。

#### 【0016】

上記の通り、入力画像のデータは、画像入力部 100 を介して画像処理装置 112 内に取り込まれ、メモリライト部 101 は、この取り込まれた入力画像のデータを第一記憶部 105 に格納する。

10

#### 【0017】

第一記憶部 105 は、一般的にはダイナミック RAM (DRAM) で構成されており、本実施形態でもこの第一記憶部 105 は DRAM であるものとして説明するが、読み書き可能なメモリであれば他のタイプのメモリを第一記憶部 105 として用いても良い。なお、DRAM は、アクセスレイテンシの比較的長いメモリである。また、メモリライト部 101 は、一般的には DMA コントローラ (DMAC) と呼ばれるものである。メモリライト部 101 は、このような第一記憶部 105 に対して入力画像のデータを、複数の画素から成る画素ブロック毎に格納する。

#### 【0018】

なお、個々の画素ブロックには、入力画像上における画素ブロックの位置を示す情報が添付されているものとするが、この情報は個々の画素ブロックに添付せずに 1 つのヘッダ情報としてまとめて第一記憶部 105 に格納しても良い。

20

#### 【0019】

ユーザ操作入力部 102 は、キーボードやマウスに代表される指示入力装置であり、入力画像をどのように幾何変形させるのかを示す指示（変形指示）を入力することができるのであれば、如何なる入力デバイスをユーザ操作入力部 102 として用いても良い。

#### 【0020】

ここで、画像の幾何変形を行うということは、画像上の画素位置が他の画素位置に写像されることに等価である。例えば、画像を だけ回転させるような幾何変形を行うということは、 だけ回転させる回転行列を画像上の各画素位置に掛け合わせてこの各画素位置を他の画素位置に写像することである。これは、画像の任意の方向へのシフト、拡大などの他の幾何変形についても同じことである。然るに、この変形指示には、入力画像を P、変形画像を Q、とすると、 $Q = M \cdot P$  を満たす写像行列 M を表す情報が含まれていることになる。ユーザ操作入力部 102 を介して入力されたこの変形指示は、座標変換部 103 に入力される。

30

#### 【0021】

座標変換部 103 は、この変形指示に含まれている写像行列 M を用いて、変形画像上の画素位置を入力画像上の画素位置に変換する為の写像行列 ( $M^{-1}$ ) を求める。即ち、上記写像行列 M を用いて、入力画像上の画素位置 S (入力系座標) が変形画像上の画素位置 T (出力系座標) に写像されるとすると、画素位置 T から画素位置 S を求める為の写像行列を求ることになる。

40

#### 【0022】

なお、座標変換部 103 は、ユーザ操作入力部 102 から変形指示が入力される毎にこのような写像行列を求める演算を行う。即ち、座標変換部 103 は常に動作しているのではなく、ユーザ操作入力部 102 からの入力があればこの入力に対して 1 回のみ動作する。もちろん、座標変換部 103 は、前回入力された変形指示と今回入力された変形指示とに規定量以上の差があったときのみ動作するようにしても良い。

#### 【0023】

また、座標変換部 103 は、変形画像上の画素位置を入力画像上の画素位置に変換する為の情報（若しくはそれぞれの画素位置間の関係を示す情報）であれば、写像行列でなく

50

ても良く、他の情報を求めて良い。

【0024】

アクセスシーケンス決定部104は、メモリリード部106が第一記憶部105に格納されている入力画像を複数の画素から成る画素ブロック毎に読み出す場合の、画素ブロックの読み出し順（アクセス順）等を規定するアクセスシーケンスリストを生成する。そしてアクセスシーケンス決定部104は、この生成したアクセスシーケンスリストを第一記憶部105に格納する。

【0025】

このアクセスシーケンスリストについて、図7を用いて説明する。アクセスシーケンスリスト790には、第一記憶部105における画素ブロック $i$ （ $i = 1, 2, \dots, N$  :  $N$ は画素ブロックの総数）の格納アドレス700と、画素ブロック $i$ の参照回数を示す参照回数情報701、のセットが、画素ブロック毎に格納されている。このセットは、より先に参照される画素ブロックについてのセットがより上に位置している。例えば、第一記憶部105内におけるメモリアドレス（BASE + (OFFSET \* 2)）に格納されているセット中の格納アドレス702は、3番目に参照する画素ブロックの第一記憶部105における格納アドレスを示す。また、第一記憶部105内におけるメモリアドレス（BASE + (OFFSET \* 2)）に格納されているセット中の参照回数情報703は、3番目に参照する画素ブロックの参照回数を示す。

【0026】

次に、図2を用いて、アクセスシーケンスリストについてより詳細に説明する。図2では、入力画像200を回転させた変形画像201を作成する場合について示している。図2(a)に示す如く、変形画像201は、変形画像201を含む1つの矩形画面290の最上ラインから最下ラインまで走査順（出力走査順）に生成する。変形画像201における画素ブロックの生成には当然ながら、第一記憶部105に格納されているこの画素ブロックのデータを参照する必要がある。然るに、最上ラインにより近い画素ブロックから参照されることになる。例えば、入力画像200において着目画素ブロック204は変形画像201上では「3」が付されている画素ブロックに写像されているが、この画素ブロックは最上ラインから3番目に近いので、この画素ブロックは3番目に参照する画素ブロックとなる。

【0027】

然るにアクセスシーケンス決定部104は、第一記憶部105に格納されているそれぞれの画素ブロックに添付の情報から、それぞれの画素ブロックの入力画像上における位置を特定する。もちろん、画素ブロックの位置を他の管理方法で管理している場合には、他の方法でこの位置を取得する。そしてアクセスシーケンス決定部104は、この特定した位置を座標変換部103から受けた変形指示で写像した写像位置を求める。そして、最上ラインにより近い写像位置を求めた画素ブロックをより先の参照順として特定する。これにより、図7に示した各セットの並び順が決まる。

【0028】

次に、図2(b)を用いて、各画素ブロックの参照回数情報の決定方法について、上記の「3」が付された画素ブロック（写像後画素ブロック）を例に取り説明する。即ち、写像後画素ブロックを例に取った以下の説明は、他の画素ブロックについても同様に当てはまる。

【0029】

本実施形態では、原理的には、矩形画面290内で2画素×2画素の矩形領域を1画素毎に出力走査順に移動させ、矩形領域が位置Xにある場合、この位置Xにおける画素値を、この矩形領域と重なる部分を有する画素ブロック内の画素値を用いて求める。これにより変形画像201を生成する。図2(b)の例で、矩形領域が写像後画素ブロックと重なる部分を有する場合、矩形領域の位置における画素値を求めるためには、写像後画素ブロックの写像元である着目画素ブロック204を参照する必要がある。即ち、着目画素ブロック204を参照する回数は、写像後画素ブロックと矩形領域とが重なる回数に相当する

10

20

30

40

50

。図2(b)に示す如く、この矩形領域は写像後画素ブロックと15回重なることが分かるので、この場合、着目画素ブロック204に対する参照回数は「15」となる。このように、アクセスシーケンス決定部104は、それぞれの画素ブロックについて参照回数情報を求める。これにより、図7に示した各セットが確定することになる。

【0030】

なお、アクセスシーケンス決定部104は、座標変換部103から変形指示が入力される毎にこのようなアクセスシーケンスリストを生成する。即ち、アクセスシーケンス決定部104は常に動作しているのではなく、座標変換部103からの入力があればこの入力に対して1回のみ動作する。

【0031】

そしてアクセスシーケンス決定部104は、このようにして生成したアクセスシーケンスリストを第一記憶部105に格納する。なお、アクセスシーケンス決定部104が行う処理の詳細については後述する。

【0032】

メモリリード部106は先ず第一記憶部105に格納されているアクセスシーケンスリストを読み出す。そしてメモリリード部106は、読み出したアクセスシーケンスリストに登録されているセット群を上から参照し、参照したセット中の格納アドレスに格納されている画素ブロックを第一記憶部105から読み出す。そして、メモリリード部106は、参照したセット中の参照回数情報を、このセット中の格納アドレスに格納されている画素ブロックと、をブロックデータ管理部107に送出する。メモリリード部106が行う処理の詳細については後述する。

【0033】

ブロックデータ管理部107は、メモリリード部106から受けた画素ブロック及び参照回数情報をセットにして第二記憶部108に格納する。本実施形態では、第二記憶部108は、スタティックRAM(SRAM)であるものとして説明する。このSRAMはアクセスレイテンシの比較的短いメモリである。しかし、読み書き可能なメモリであれば他のタイプのメモリを第二記憶部108として用いても良い。

【0034】

また、ブロックデータ管理部107は、ブロックデータ処理部110から要求された画素ブロックを第二記憶部108から読み出してブロックデータ処理部110に供給する。このとき、ブロックデータ管理部107は、供給した画素ブロックとセットにして第二記憶部108に格納した参照回数情報が示す参照回数を1つ減じることでこの参照回数情報を更新する。そしてブロックデータ管理部107は、この更新後の参照回数情報が示す参照回数が0になった場合には、この参照回数情報、及びこの参照回数情報とセットにして第二記憶部108に格納した画素ブロックを第二記憶部108から削除する。

【0035】

ブロックデータ処理部110は、座標変換部103とのやり取りにより、変形指示に従って、ブロックデータ管理部107から受けた画素ブロックを用いて変形画像を生成する。

【0036】

より詳しくは、ブロックデータ処理部110は、変形画像を包含する矩形領域(図2の場合、矩形領域290)内で出力走査順に2画素×2画素のサイズの矩形領域(参照領域)を移動させる。そして、変形画像内の各画素ブロックのうちこの参照領域と重なる部分を有する画素ブロックを特定し、特定した画素ブロックにおいて参照領域と重なっている部分を構成する各画素の画素位置に対して、座標変換部103が求めた写像行列を掛け合わせる。これにより、入力画像上の対応する画素位置を求めることができる。また、ブロックデータ処理部110は、この特定した画素ブロックのデータをブロックデータ管理部107に要求する。そして、この供給に応じてブロックデータ管理部107から受けた画素ブロックにおいて、この求めた画素位置の画素の画素値を用いて、参照領域の位置における画素値を求める。このような処理により各画素の画素値が確定した変形画像を生成す

10

20

30

40

50

ることができる。

【0037】

なお、この説明した処理は換言すれば次の処理に等価である。即ち先ず、入力画像における画素ブロックの領域が、変形指示が示す変形に伴って写像される写像先の、入力画像中における写像後領域を演算によって求める。ここで、入力画像中のそれぞれの画素位置に規定サイズ（例えば2画素×2画素）の矩形領域を設けた場合に、入力画像中の着目画素ブロックの領域の写像先である着目写像後領域と重なる部分を有するそれぞれの矩形領域Pの入力画像中における位置をXとする。この場合、変形画像上（矩形領域290上）の位置Xにおける画素値を、矩形領域Pと重なる部分を有する写像後領域の写像元となる画素ブロック内の画素の画素値を用いて計算する。

10

【0038】

なお、ブロックデータ処理部110は、上記の何れの演算で画素値を求めるにせよ、変形画像の各画素の画素値を確定させた後、この変形画像に対して画素値の補間処理やフィルタ処理などの画像処理を適宜適用しても良い。

【0039】

そしてブロックデータ処理部110は、この生成した変形画像を表示部111に送出する。この表示部111はCRTや液晶画面などにより構成されており、ブロックデータ処理部110から受けた変形画像のデータ（出力画像データ）に基づく画像を表示する。

【0040】

次に、アクセスシーケンス決定部104が行う処理について、同処理のフローチャートを示す図3を用いて説明する。アクセスシーケンス決定部104は座標変換部103からの変形指示を受けない限りはステップS301で待機しているが、この変形指示を受けた場合には、処理はステップS301からステップS302に進む。

20

【0041】

ステップS302でアクセスシーケンス決定部104は、それぞれの画素ブロックの参照順番を決めるために用いる変数である参照ブロックオーダカウンタを1に初期化する。更にアクセスシーケンス決定部104は、画素ブロック毎に設けられる変数である参照順番を示す変数、参照回数を示す変数を0に初期化する。

【0042】

そしてアクセスシーケンス決定部104は、ステップS304～ステップS310の処理を、変形画像を包含する矩形領域（図2の場合、矩形領域290）内の各画素位置について行う。なお、図3のフローチャートには示していないが、この矩形領域内で変形画像外の領域については0等の規定の画素値を与えるものとする。以下では、この矩形領域内の画素位置i（i=1, ..., M: Mはこの矩形領域の総画素数）についての処理を説明する。

30

【0043】

ステップS304では画素位置iを、座標変換部103が求めた写像行列で変換し、変換画素位置iを求める。ステップS305ではアクセスシーケンス決定部104は、変換画素位置iが入力画像上の画素位置であるか否かを判断する。この判断の結果、変換画素位置iが入力画像上の画素位置である場合には処理はステップS306に進み、変換画素位置iが入力画像上の画素位置ではない場合には処理はステップS302に戻り、次の画素位置（i+1）について以降の処理を行う。

40

【0044】

ステップS306ではアクセスシーケンス決定部104は、変形画像を包含する矩形領域内の画素位置iに参照領域を設定し、変形画像内の各画素ブロックのうちこの参照領域と重なる部分を有する画素ブロックを特定する。変形画像内の各画素ブロックは、入力画像における画素ブロックの領域が、変形指示が示す変形に伴って写像される写像先の領域に相当する。

【0045】

ステップS307ではアクセスシーケンス決定部104は、ステップS306で特定し

50

た画素ブロックに対する参照回数を示す変数が0であるか否かを判断する。この判断の結果、0である場合には処理をステップS308に進め、0でない場合には処理はステップS310に進む。

【0046】

ステップS308ではアクセスシーケンス決定部104は、ステップS306で特定した画素ブロックに対する参照順番を示す変数に、現在の参照ブロックオーダカウンタの値を設定する。

【0047】

ステップS309ではアクセスシーケンス決定部104は、参照ブロックオーダカウンタの値を1つインクリメントしてこの参照ブロックオーダカウンタを更新する。ステップS310ではアクセスシーケンス決定部104は、参照回数を示す変数の値を1つインクリメントしてこの変数を更新する。

【0048】

以上のステップS304～S310の処理を、変形画像を包含する矩形領域内の各画素位置について行うことで、各画素ブロックについて参照順番情報、参照回数情報を求めることができる。然るにステップS312ではアクセスシーケンス決定部104は、画素ブロック毎の格納アドレス及び参照回数情報のセットを参照順番順に並べたアクセスシーケンスリストを作成し、この作成したアクセスシーケンスリストを第一記憶部105に格納する。

【0049】

上記の処理によってアクセスシーケンスリストが作成される過程について、図4を用いて説明する。先ずはリスト400に示す如く、各画素ブロックには画素ブロックの格納時などで付けられる識別情報（ブロックID）403が割り当てられていると共に、参照順番情報404、参照回数情報405が割り当てられている。これらの参照順番情報情報404、参照回数情報405は何れも上記の通り最初は初期化されている。

【0050】

そして上記の処理を行うことで、リスト401に示す如く、各画素ブロックに対してステップS308で設定された参照順番が確定する。リスト401では、画素ブロック毎の情報は、参照順番でソートされている。

【0051】

そしてリスト401の先頭に登録されているブロックID、参照順番情報、参照回数情報情報のセットのアドレスを（BASE + (OFFSET \* 0)）として決定する。本実施形態では、リストのベースアドレスをBASE、各セットの先頭アドレス間をOFFSETとしたとき、リストの先頭からorder番目に登録されているセットのアドレスはBASE + (OFFSET \* order)で求める。更に、それぞれの画素ブロックの第一記憶部105における格納アドレスを特定する。これによりリスト402に示す如く、リスト401におけるそれぞれのセットのアドレス406、画素ブロックの格納アドレス407が作成される。そして最終的には、不要なデータであるブロックID403と参照順番情報404を削除して残ったリスト408を、図7に示すようなアクセスシーケンスリストとする。図7ではアドレス406はアクセスシーケンスリストに含めていないが、含めても良い。

【0052】

次に、メモリリード部106が行う処理について、同処理のフローチャートを示す図5を用いて説明する。ステップS501ではメモリリード部106は、第一記憶部105へのアクセスアドレスに、アクセスシーケンスリストの先頭アドレスであるベースアドレス（BASE）を設定する。そしてメモリリード部106は、アクセスシーケンスリストに登録されている全てのセットについてステップS502～S508の間の各処理を行う。

【0053】

ステップS503ではメモリリード部106は、現在設定されているアクセスアドレス（最初はステップS501で設定したアクセスアドレス）に対してアクセスし、そこに格

10

20

30

40

50

納されているセット（格納アドレスと参照回数情報のセット）を読み出す。

【0054】

ステップS504ではメモリリード部106は、ステップS503で読み出した格納アドレスに対してアクセスし、そこに格納されている画素ブロックを読み出す。そしてブロックデータ管理部107からの要求がない限りはステップS505で待機し、要求があれば処理はステップS505を介してステップS506に進む。

【0055】

ステップS506ではメモリリード部106は、ステップS504で読み出した画素ブロックと、ステップS503で読み出したセット中の参照回数情報と、をブロックデータ管理部107に送出する。ステップS507ではメモリリード部106は、現在のアクセスアドレスにオフセットアドレス(OFFSET)を加算してこのアクセスアドレスを更新する。

【0056】

次に、ブロックデータ管理部107が行う処理について、同処理のフローチャートを示す図6を用いて説明する。ステップS602ではブロックデータ管理部107は、第二記憶部108に充分な空き容量があるか否かを判断する。この判断の結果、充分な空き容量があると判断した場合には処理はステップS603に進み、無いと判断した場合には処理はステップS604に進む。

【0057】

ステップS603ではブロックデータ管理部107は、メモリリード部106から受けた画素ブロック及び参照回数情報をセットにして第二記憶部108に格納する。ステップS604ではブロックデータ管理部107は、ブロックデータ処理部110から画素ブロックの転送要求があるか否かを判断する。この判断の結果、転送要求があった場合には処理はステップS605に進み、転送要求がない場合には処理はステップS602に戻る。

【0058】

ステップS605ではブロックデータ管理部107は、この要求された画素ブロックが第二記憶部108に格納されているか否かを判断する。この判断の結果、格納されている場合には処理はステップS606に進み、格納されていない場合には、処理はステップS602に戻る。

【0059】

ステップS606ではブロックデータ管理部107は、この転送要求によって要求された画素ブロックを第二記憶部108から読み出してブロックデータ処理部110に供給する。

【0060】

ステップS607ではブロックデータ管理部107は、この供給した画素ブロックとセットにして第二記憶部108に格納した参照回数情報が示す参照回数を1つ減じてこの参照回数情報を更新する。ステップS608では、この減じた参照回数が0であるか否かを判断する。この判断の結果、0であれば処理はステップS609に進み、0でない場合(0より大きい場合)には処理はステップS602に戻る。

【0061】

ステップS609でブロックデータ管理部107は、参照回数0を示す参照回数情報及びこの参照回数情報とセットにして第二記憶部108に格納した画素ブロックを第二記憶部108から削除し、第二記憶部108におけるこれらの情報の記憶領域を開放する。これにより、新たな画素ブロックを取得可能な状態にする。

【0062】

以降の構成によれば、ブロックデータ処理部110が要求する順序で、画素ブロックをブロックデータ管理部107によって供給することができる。また、参照回数を用いることで、ブロックデータ処理部110が必要とする間は対応する画素ブロックが保持されることが保証されるため、処理の破綻が起きない。

【0063】

10

20

30

40

50

以上の説明により、本実施形態によれば、画像変形処理を行う場合に比較的大きな割合を占めるプリフェッヂの機構を持たずに任意の画像変形処理を行うことができる。また、これにより、画像処理装置の回路規模（上記処理をソフトウェアで実現する場合にはソフトウェアの規模）を削減することができる。

#### 【0064】

以上の説明では、画素ブロックを参照して変形画像上の画素値を求める毎にこの画素ブロックに対して設定された参照回数をカウントダウンしていた。しかし、画素ブロックに対して新たにカウントアップ用の変数を設け、この画素ブロックが画素値生成用に用いられる毎にこの変数の値をカウントアップしても良い。この場合、このカウントアップ後の変数の値が、この画素ブロックについて設定された上限回数に達した場合には、この画素ブロックを第一記憶部105から削除することになる。10

#### 【0065】

また、本実施形態では、画像を取り扱った処理を例にとって説明した。しかし、以上の説明は、画像を取り扱った例に限定するものではなく、画像以外のデータを取り扱う場合にも適用することができる。

#### 【0066】

##### 〔第2の実施形態〕

第1の実施形態では、図1に示した各部は何れもハードウェアで構成されているものとして説明した。しかし、その一部若しくは全部をコンピュータプログラムとして構成しても良い。この場合、このコンピュータプログラムは、PC（パーソナルコンピュータ）等の装置にインストールされ、この装置が有するCPUなどにより実行され、これによりこの装置は、第1の実施形態で説明した各処理を実行することができる。20

#### 【0067】

また、図1に示した各部のうち1以上をそれぞれ別個の装置としても良い。この場合、それぞれの装置間では有線や無線によるネットワークを介して互いにデータ通信を行いながら、第1の実施形態で説明した各処理を進めていくことになる。

#### 【0068】

##### 〔その他の実施例〕

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア（プログラム）を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ（またはCPUやMPU等）がプログラムを読み出して実行する処理である。30

【 図 1 】

【 四 2 】

【図3】

【 四 4 】

【図5】

【図6】

【図7】

---

フロントページの続き

(72)発明者 北莊 哲郎

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 岡本 俊威

(56)参考文献 特開平04-329482 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 T 3 / 60

H 04 N 1 / 387