(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3759758号

(P3759758)

(45) 発行日 平成18年3月29日(2006.3.29)

(24) 登録日 平成18年1月13日(2006.1.13)

(51) Int.C1.

F 1

G 11 C 11/403 (2006.01)

G 11 C 11/407 (2006.01)G 11 C 11/34 363M

G 11 C 11/34 354F

請求項の数 9 (全 58 頁)

(21) 出願番号 特願平6-44369

(22) 出願日 平成6年3月15日(1994.3.15)

(65) 公開番号 特開平7-262771

(43) 公開日 平成7年10月13日(1995.10.13)

審査請求日 平成13年3月13日(2001.3.13)

(31) 優先権主張番号 特願平6-11900

(32) 優先日 平成6年2月3日(1994.2.3)

(33) 優先権主張国 日本国(JP)

前置審査

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100064746

弁理士 深見 久郎

(74) 代理人 100085132

弁理士 森田 俊雄

(74) 代理人 100083703

弁理士 仲村 義平

(74) 代理人 100096781

弁理士 堀井 豊

(74) 代理人 100098316

弁理士 野田 久登

(74) 代理人 100109162

弁理士 酒井 将行

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項1】

セルフリフレッシュ動作が行なわれる半導体記憶装置であって、

前記セルフリフレッシュ動作の期間を規定するセルフリフレッシュ期間規定信号を発生するセルフリフレッシュ期間規定手段と、

前記半導体記憶装置の内部回路の擬似接地電位線に接続され、前記擬似接地電位線に擬似接地電位を発生させる擬似接地電位発生手段とを備え、

前記擬似接地電位発生手段は、前記セルフリフレッシュ期間規定信号で規定される期間の開始に応答して前記擬似接地電位を第1の電位から第2の電位に上昇させ、前記セルフリフレッシュ期間規定信号で規定される期間の終了に応答して前記擬似接地電位を前記第2の電位から前記第1の電位まで降下させる、半導体記憶装置。

## 【請求項2】

前記擬似接地電位発生手段によって前記擬似接地電位が下降される期間の長さと、前記擬似接地電位発生手段によって前記擬似接地電位が上昇される期間の長さとを異ならせる手段をさらに備えた、請求項1に記載の半導体記憶装置。

## 【請求項3】

内部電源電位差によりスイング幅が規定される電圧スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、

前記セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生するセルフリフレッシュ期間規定手段と、

前記内部電源電位差を発生し、前記セルフリフレッシュ期間規定信号に応答して、発生する内部電源電位差を制御する1つもしくは複数の内部電源電圧発生手段とを備え、

少なくとも1つの前記内部電源電圧発生手段は、

前記セルフリフレッシュ期間規定信号で規定される期間の開始に応答して、発生する内部電源電位差を第1の電位差から第2の電位差まで減少させる制御を行なうとともに、前記セルフリフレッシュ期間規定信号で規定される期間の終了に応答して、発生する内部電源電位差を前記第2の電位差から前記第1の電位差まで増加させる制御を行ない、

前記内部電源電圧発生手段によって前記内部電源電位差が前記第1の電位差から前記第2の電位差まで減少される期間に活性化する減少期間規定信号を発生する減少期間規定信号発生手段と、

前記内部電源電圧発生手段によって前記内部電源電位差が前記第2の電位差から前記第1の電位差まで増加される期間に活性化する増加期間規定信号を発生する増加期間規定信号発生手段と、

前記内部電源電圧発生手段によって前記内部電源電位差が前記第2の電位差に保持される期間に活性化する保持期間規定信号を発生する保持期間規定信号発生手段と、

前記減少期間規定信号、前記増加期間規定信号および前記保持期間規定信号に応答し、前記セルフリフレッシュ動作時のリフレッシュ周期を設定するリフレッシュ周期設定手段とをさらに備え、

前記リフレッシュ周期設定手段は、

前記減少期間規定信号に応答して第1のリフレッシュ周期を設定する第1のリフレッシュ周期設定手段と、

前記増加期間規定信号に応答して第2のリフレッシュ周期を設定する第2のリフレッシュ周期設定手段と、

前記保持期間規定信号に応答して第3のリフレッシュ周期を設定する第3のリフレッシュ周期設定手段とを含み、

前記第1および第2のリフレッシュ期間を前記第3のリフレッシュ周期よりも短くした半導体記憶装置。

#### 【請求項4】

前記リフレッシュ周期設定手段で設定される前記第1のリフレッシュ周期と前記第2のリフレッシュ周期とを異ならせた、請求項3記載の半導体記憶装置。

#### 【請求項5】

内部電源電位差によりスイング幅が規定される電圧スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、

前記セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生するセルフリフレッシュ期間規定手段と、

前記内部電源電位差を発生し、前記セルフリフレッシュ期間規定信号に応答して、発生する内部電源電位差を制御する1つもしくは複数の内部電源電圧発生手段とを備え、

少なくとも1つの前記内部電源電圧発生手段は、

前記セルフリフレッシュ期間規定信号で規定される期間の開始に応答して、発生する内部電源電位差を第1の電位差から第2の電位差まで減少させる制御を行なうとともに、前記セルフリフレッシュ期間規定信号で規定される期間の終了に応答して、発生する内部電源電位差を前記第2の電位差から前記第1の電位差まで増加させる制御を行ない、

前記内部電源電圧発生手段は、前記第1の電位差から前記第2の電位差までの内部電源電位差の減少および前記第2の電位差から前記第1の電位差までの内部電源電位差の増加のそれぞれをステップ状に複数段階で行なう制御をする電圧制御手段を含む、半導体記憶装置。

#### 【請求項6】

前記内部電源電圧発生手段は、前記内部電源電位差のステップ状の減少および増加のそれぞれの1段階を、すべてのメモリセルがリフレッシュされる周期の倍数の期間にて行なう、請求項5記載の半導体記憶装置。

**【請求項 7】**

前記擬似接地電位発生手段は、

前記擬似接地電位線と接地ノードとの間に接続されるトランジスタと、

前記トランジスタを制御する電圧を発生する電圧発生手段とを含み、

前記電圧発生手段は、

第3の電位を受ける第1の電位ノードと、

前記第3の電位よりも低い第4の電位を受ける第2の電位ノードと、

前記トランジスタを制御する電圧を出力する出力ノードと、

前記第1の電位ノードと前記出力ノードとの間に設けられ、定電流を発生する定電流発生手段と、

前記出力ノードと前記第2の電位ノードとの間に設けられた抵抗手段と、

前記第1の電位ノードと前記出力ノードとの間に前記定電流発生手段に直列に接続され、

前記セルフリフレッシュ期間規定信号に応答してスイッチングするトランジスタ手段とを含む、請求項1に記載の半導体記憶装置。

**【請求項 8】**

内部電源電位差によりスイング幅が規定される電圧スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、

前記セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生するセルフリフレッシュ期間規定手段と、

前記内部電源電位差を発生し、前記セルフリフレッシュ期間規定信号に応答して、発生する内部電源電位差を制御する1つもしくは複数の内部電源電圧発生手段とを備え、

少なくとも1つの前記内部電源電圧発生手段は、

前記セルフリフレッシュ期間規定信号で規定される期間の開始に応答して、発生する内部電源電位差を第1の電位差から第2の電位差まで減少させる制御を行なうとともに、前記セルフリフレッシュ期間規定信号で規定される期間の終了に応答して、発生する内部電源電位差を前記第2の電位差から前記第1の電位差まで増加する制御を行ない、

少なくとも1つの前記内部電源電圧発生手段は、

内部電源電圧の基準電圧を発生させる基準電圧発生手段と、

発生する内部電源電圧と前記基準電圧との差に基づいて前記内部電源電圧を制御するための制御電圧を出力する差動增幅手段と、

前記セルフリフレッシュ期間規定信号に応答し、その信号で規定されるセルフリフレッシュ動作の期間に前記差動增幅手段の動作を停止させる停止手段と、

前記内部電源電圧を出力するための電圧出力ノードと、

前記外部電源電圧を受ける電源ノードと、

前記電源ノードと前記電圧出力ノードとの間に設けられ、ゲート電極に受ける信号に応答して前記外部電源電圧に基づく内部電源電圧を前記電圧出力ノードに供給するためのNチャネルトランジスタと、

前記セルフリフレッシュ期間規定信号に応答し、その信号で規定されるセルフリフレッシュ動作の期間に前記基準電圧を前記Nチャネルトランジスタの前記ゲート電極に与えるトランジスタ制御手段とを備えた、半導体記憶装置。

**【請求項 9】**

内部電源電位差によりスイング幅が規定される電圧スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、

前記セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生するセルフリフレッシュ期間規定手段と、

前記内部電源電位差を発生し、前記セルフリフレッシュ期間規定信号に応答して、発生する内部電源電位差を制御する1つもしくは複数の内部電源電圧発生手段とを備え、

少なくとも1つの前記内部電源電圧発生手段は、

前記セルフリフレッシュ期間規定信号で規定される期間の開始に応答して、発生する内部電源電位差を第1の電位差から第2の電位差まで減少させる制御を行なうとともに、前

記セルフリフレッシュ期間規定信号で規定される期間の終了に応答して、発生する内部電源電位差を前記第2の電位差から前記第1の電位差まで増加させる制御を行ない、

前記内部電源電圧発生手段が発生する内部電源電位差と所定電位差とを比較し、前記内部電源電圧が前記所定電圧と同程度となった場合に出力信号を活性化する比較手段と、

前記比較手段の出力信号を受け、その信号が活性化した場合に、前記内部電源電位差が前記通常動作時の電位差に復帰したこと示す所定レベルの信号を外部に出力する外部出力手段とをさらに備えた、半導体記憶装置。

#### 【発明の詳細な説明】

##### 【0001】

##### 【産業上の利用分野】

この発明は、半導体記憶装置に関し、特に、セルフリフレッシュを行なうDRAM(ダイナミックランダムアクセスメモリ)に関するものである。

##### 【0002】

##### 【従来の技術】

半導体記憶装置であるDRAMでは、メモリセルのセルフリフレッシュが行なわれる。このセルフリフレッシュの1つの方法として、DRAMが形成されたチップの内部回路が発生するリフレッシュ周期でリフレッシュを行なうセルフリフレッシュが用いられている。

##### 【0003】

このセルフリフレッシュにおいては、リフレッシュ周期となる信号を外部から与えることなくリフレッシュが実行できる。すなわち、チップの内部回路で比較的長周期のリフレッシュ周期を発生し、その発生したリフレッシュ周期にてチップの内部回路によりリフレッシュが行なわれる。

##### 【0004】

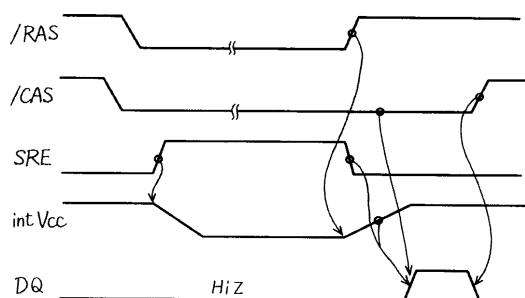

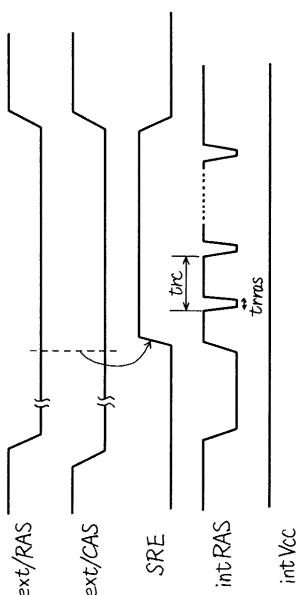

次に、従来のセルフリフレッシュについて説明する。図27は、従来のセルフリフレッシュ動作のタイミングの一例を示すタイミングチャートである。

##### 【0005】

図37を参照して、外部コラムアドレスストローブ信号ext/CASがLレベルに立下がった後に外部ロウアドレスストローブ信号ext/RASがLレベルに立下がったタイミング、すなわち、/CAS Before /RASタイミング(以下CBRタイミングと呼ぶ)で、これらの信号がともにLレベルを所定期間保持すると、セルフリフレッシュ期間を規定するセルフリフレッシュイネーブル信号SREがHレベルに立上がる。

##### 【0006】

信号SREがHレベルになると、チップの内部で、内部ロウアドレスストローブ信号int/RASが比較的長周期のリフレッシュ周期trcを発生する。この信号int/RASに応答して、リフレッシュが実行される。このセルフリフレッシュが行なわれている場合も内部電源電圧intVccは、一定に保持される。

##### 【0007】

このようなセルフリフレッシュにおける課題は、リフレッシュ周期をいかに長くし、かつ、セルフリフレッシュ動作時のスタンバイ期間およびアクティブ期間のそれぞれにおいて低消費電流化を図ることである。

##### 【0008】

##### 【発明が解決しようとする課題】

しかし、16MDRAM以降の技術開発においては、微細化の進行に対して電源電圧のスケールダウンが追いついていない。このため、デバイスの信頼性を確保しつつ高集積度を実現するために、チップ内に内部降圧回路を設けたデバイスが出現した。この内部降圧回路は、外部電源電圧を降圧した低い内部電源電圧を発生させる。

##### 【0009】

また、外部電源電圧よりも低い内部電源電圧にて動作するデバイスにおけるアクセスの高速化を図るため、ワード線の昇圧電圧発生回路もチップ内に設けられるようになった。

##### 【0010】

10

20

30

40

50

このように、DRAMにおいては、内部降圧回路および昇圧電圧発生回路をチップ内に設けたために、これらの回路によって、セルフリフレッシュ動作におけるスタンバイ期間等における消費電流が増加するという問題があった。

【0011】

また、セルフリフレッシュ動作のアクティブ電流を低減する方法としてセルフリフレッシュ動作時に外部電源電圧を低下させる制御を行なう方法がある。しかし、この方法では、チップ外で電源電圧の制御を行なう必要があり、このために、メモリボード上の電源の上昇および下降の制御が難しいという問題があった。

【0012】

この発明は、このような問題を解決すべくなされたものであり、内部回路における制御によってセルフリフレッシュ時の消費電流を低減することを可能とする半導体記憶装置を提供することを目的とする。

10

【0013】

この発明の他の目的は、内部降圧回路の消費電流を低減することである。

この発明のさらに他の目的は、昇圧電圧発生回路の消費電流を低減することである。

【0014】

この発明のさらに他の目的は、通常動作からセルフリフレッシュ動作に移行する場合およびセルフリフレッシュ動作から通常動作に移行する場合のそれぞれにおいて、リフレッシュの実力の初期化を、複雑な外部制御を必要とすることなく実現することである。

【0015】

20

【課題を解決するための手段】

請求項1に記載の本発明は、セルフリフレッシュ動作が行なわれる半導体記憶装置であつて、セルフリフレッシュ期間規定手段および内部電源電位差発生手段を備える。

【0016】

セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作の期間を規定するセルフリフレッシュ期間規定信号を発生する。

【0017】

内部電源電位差発生手段は、半導体記憶装置の内部回路の基準電圧がスイッチング手段により調整可能な基準電圧発生手段と、基準電圧に基づいて内部回路に内部電源電位と接地電位との差である内部電源電位差を発生する手段とを含む。

30

【0018】

内部電源電位差発生手段は、セルフリフレッシュ期間規定信号で規定される期間の開始に応答して内部電源電位差を第1の電位差から第2の電位差まで減少させ、セルフリフレッシュ期間規定信号で規定される期間の終了に応答して内部電源電位差を第2の電位差から第1の電位差まで増加させる。

【0019】

請求項2に記載の本発明は、請求項1に記載の発明において、内部電源電位差発生手段が内部降圧手段であることを特徴とする。

【0020】

請求項3に記載の本発明は、セルフリフレッシュ動作が行なわれる半導体記憶装置であつて、セルフリフレッシュ期間規定手段とおよび接地電位発生手段を備える。

40

【0021】

セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作の期間を規定するセルフリフレッシュ期間規定信号を発生する。

【0022】

接地電位発生手段は、半導体記憶装置の内部回路の接地電位を発生させ、セルフリフレッシュ期間規定信号で規定される期間の開始に応答して接地電位を第1の電位から第2の電位に上昇させる。

【0023】

接地電位発生手段は、セルフリフレッシュ期間規定信号で規定される期間の終了に応答し

50

て接地電位を第2の電位から第1の電位まで降下させる。

【0024】

請求項4に記載の本発明は、内部電源電位差によりスイング幅が規定される電圧スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、セルフリフレッシュ期間規定手段、および1つもしくは複数の内部電源電圧発生手段を備える。セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生する。1つもしくは複数の内部電源電圧発生手段は、内部電源電位差を発生し、セルフリフレッシュ期間規定信号に応答して、発生する内部電源電位差を制御する。少なくとも1つの内部電源電圧発生手段は、セルフリフレッシュ期間規定信号で規定される期間の開始に応答して、発生する内部電源電位差を第1の電位差から第2の電位差まで減少させる制御を行なうとともに、セルフリフレッシュ期間規定信号で規定される期間の終了に応答して、発生する内部電源電位差を第2の電位差から第1の電位差まで増加させる制御を行なう。半導体記憶装置はさらに、内部電源電圧発生手段によって内部電源電位差が減少される期間の長さと、内部電源電圧発生手段によって内部電源電位差が増加される期間の長さとを異ならせる手段をさらに備える。

10

【0025】

請求項5に記載の本発明は、内部電源電位差によりスイング幅が規定される電圧スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、セルフリフレッシュ期間規定手段、および1つもしくは複数の内部電源電圧発生手段を備える。セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生する。1つもしくは複数の内部電源電圧発生手段は、内部電源電位差を発生し、セルフリフレッシュ期間規定信号に応答して、発生する内部電源電位差を制御する。少なくとも1つの内部電源電圧発生手段は、セルフリフレッシュ期間規定信号で規定される期間の開始に応答して、発生する内部電源電位差を第1の電位差から第2の電位差まで減少させる制御を行なうとともに、セルフリフレッシュ期間規定信号で規定される期間の終了に応答して、発生する内部電源電位差を第2の電位差から第1の電位差まで増加させる制御を行なう。半導体記憶装置はさらに、減少期間規定信号発生手段、増加期間規定信号発生手段、保持期間規定信号発生手段およびリフレッシュ周期設定手段をさらに備え、そのセルフリフレッシュ周期設定手段が、第1のリフレッシュ周期設定手段、第2のリフレッシュ周期設定手段および第3のリフレッシュ周期設定手段を含む。

20

【0026】

減少期間規定信号発生手段は、内部電源電圧発生手段によって内部電源電位差が第1の電位差から第2の電位差まで減少される期間に活性化する減少期間規定信号を発生する。

【0027】

増加期間規定信号発生手段は、内部電源電圧発生手段によって内部電源電位差が第2の電位差から第1の電位差まで増加される期間に活性化する増加期間規定信号を発生する。

【0028】

保持期間規定信号発生手段は、内部電源電圧発生手段によって内部電源電位差が第2の電位差に保持される期間に活性化する保持期間規定信号を発生する。

30

【0029】

リフレッシュ周期設定手段は、減少期間規定信号、増加期間規定信号および保持期間規定信号に応答し、セルフリフレッシュ動作時のリフレッシュ周期を設定する。

【0030】

このリフレッシュ周期設定手段は、第1のリフレッシュ周期設定手段、第2のリフレッシュ周期設定手段および第3のリフレッシュ周期設定手段を含む。第1のリフレッシュ周期設定手段は、減少期間規定信号に応答して第1のリフレッシュ周期を設定する。第2のリフレッシュ周期設定手段は、増加期間規定信号に応答して第2のリフレッシュ周期を設定する。第3のリフレッシュ周期設定手段は、保持期間規定信号に応答して第3のリフレッシュ周期を規定する。第1および第2のリフレッシュ周期は、第3のリフレッシュ周期よ

40

50

りも短くした。

【0031】

請求項6に記載の本発明は、請求項5に記載の発明において、リフレッシュ周期設定手段で設定される第1のリフレッシュ周期と第2のリフレッシュ周期とを異ならせたことを特徴とする。

【0032】

請求項7に記載の本発明は、内部電源電位差によりスイング幅が規定される電圧スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、セルフリフレッシュ期間規定手段、および1つもしくは複数の内部電源電圧発生手段を備える。セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生する。1つもしくは複数の内部電源電圧発生手段は、内部電源電位差を発生し、セルフリフレッシュ期間規定信号に応答して、発生する内部電源電位差を制御する。少なくとも1つの内部電源電圧発生手段は、セルフリフレッシュ期間規定信号で規定される期間の開始に応答して、発生する内部電源電位差を第1の電位差から第2の電位差まで減少させる制御を行なうとともに、セルフリフレッシュ期間規定信号で規定される期間の終了に応答して、発生する内部電源電位差を第2の電位差から第1の電位差まで増加させる制御を行なう。内部電源電圧発生手段が、第1の電位差から第2の電位差までの内部電源電位差の減少および第2の電位差から第1の電位差までの内部電源電位差の増加のそれぞれをステップ状に複数段階で行なう制御をする電圧制御手段を含む。

10

【0033】

請求項8に記載の本発明は、請求項7に記載の発明の内部電源電圧発生手段が、内部電源電位差のステップ状の減少および増加のそれぞれの1段階を、すべてのメモリセルがリフレッシュされる周期の倍数の期間にて行なう。

【0034】

請求項9に記載の本発明は、内部電源電位差によりスイング幅が規定される電圧スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、セルフリフレッシュ期間規定手段、および1つもしくは複数の内部電源電圧発生手段を備える。セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生する。1つもしくは複数の内部電源電圧発生手段は、内部電源電位差を発生し、セルフリフレッシュ期間規定信号に応答して、発生する内部電源電位差を制御する。少なくとも1つの内部電源電圧発生手段は、セルフリフレッシュ期間規定信号で規定される期間の開始に応答して、発生する内部電源電位差を第1の電位差から第2の電位差まで減少させる制御を行なうとともに、セルフリフレッシュ期間規定信号で規定される期間の終了に応答して、発生する内部電源電位差を第2の電位差から第1の電位差まで増加させる制御を行なう。内部電源電圧発生手段の少なくとも1つが、内部電源電圧の基準電圧を発生する基準電圧発生手段を含み、その基準電圧発生手段が、第1の電位ノード、第2の電位ノード、出力ノード、定電流発生手段、抵抗手段およびトランジスタ手段を含む。

30

【0035】

第1の電位ノードは、第1の電位を受ける。第2の電位ノードは、第2の電位を受ける。出力ノードは、基準電圧を出力する。

40

【0036】

定電流発生手段は、第1の電位ノードと出力ノードとの間に設けられ、定電流を発生する。抵抗手段は、出力ノードと第2の電位ノードとの間に設けられる。トランジスタ手段は、抵抗手段の一部と並列に接続され、セルフリフレッシュ期間規定信号に応答してスイッチングする。

【0037】

請求項10に記載の本発明は、内部電源電圧によりセルフリフレッシュ動作を行なう半導体記憶装置であって、電源ノード、セルフリフレッシュ期間規定手段および内部降圧手段

50

を備え、内部降圧手段が、基準電圧発生手段を含み、その基準電圧発生手段が、出力ノード、第1の基準電圧供給手段、第2の基準電圧供給手段および供給停止手段を含む。

【0038】

電源ノードは、外部電源電圧を受ける。セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生する。内部降圧手段は、外部電源電圧を降圧し、内部電源電圧を発生する。

【0039】

基準電圧発生手段は、内部電源電圧の基準電圧を発生する。

出力ノードは、基準電圧を出力する。第1の基準電圧供給手段は、一定の第1の基準電圧を出力ノードに供給する。第2の基準電圧供給手段は、外部電源電圧を受け、バーンインテストのために外部電源電圧が所定レベル以上になった場合に、外部電源電圧に応答する第2の基準電圧を出力ノードに供給する。

10

【0040】

供給停止手段は、セルフリフレッシュ期間規定信号を受け、その信号で規定されるセルフリフレッシュの期間に第2の基準電圧供給手段への外部電源電圧の供給を停止する。

【0041】

請求項11に記載の本発明は、内部電源電位差によりスイング幅が規定される電圧スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、セルフリフレッシュ期間規定手段、および1つもしくは複数の内部電源電圧発生手段を備える。セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生する。1つもしくは複数の内部電源電圧発生手段は、内部電源電位差を発生し、セルフリフレッシュ期間規定信号に応答して、発生する内部電源電位差を制御する。少なくとも1つの内部電源電圧発生手段は、セルフリフレッシュ期間規定信号で規定される期間の開始に応答して、発生する内部電源電位差を第1の電位差から第2の電位差まで減少させる制御を行なうとともに、セルフリフレッシュ期間規定信号で規定される期間の終了に応答して、発生する内部電源電位差を第2の電位差から第1の電位差まで増加する制御を行なう。少なくとも1つの内部電源電圧発生手段が、基準電圧発生手段、差動增幅手段、停止手段、電圧出力ノード、電源ノード、Nチャネルトランジスタおよびトランジスタ制御手段を含む。

20

【0042】

基準電圧発生手段は、内部電源電圧の基準電圧を発生させる。差動增幅手段は、発生する内部電源電圧と基準電圧との差に基づいて内部電源電圧を制御するための制御電圧を出力する。停止手段は、セルフリフレッシュ期間規定信号に応答し、その信号で規定されるセルフリフレッシュ動作の期間に差動增幅手段の動作を停止させる。

30

【0043】

電圧出力ノードは、内部電源電圧を出力する。電源ノードは、外部電源電圧を受ける。Nチャネルトランジスタは、電源ノードと電圧出力ノードとの間に設けられ、ゲート電極に受ける信号に応答して外部電源電圧に基づく内部電源電圧を電圧出力ノードに供給する。

【0044】

トランジスタ制御手段は、セルフリフレッシュ期間規定信号に応答し、その信号で規定されるセルフリフレッシュ動作の期間に基準電圧をNチャネルトランジスタのゲート電極に与える。

40

【0045】

請求項12に記載の本発明は、メモリセルアレイと周辺回路とを有し、内部電源電圧により通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、第1の内部電源電圧発生手段、第2の内部電源電圧発生手段、第1の電圧制御手段および第2の電圧制御手段を備える。

【0046】

第1の内部電源電圧発生手段は、メモリセルアレイに供給する第1の内部電源電圧を発生する。第2の内部電源電圧発生手段は、周辺回路に供給する第2の内部電源電圧を発生す

50

る。

【0047】

第1の電圧制御手段は、セルフリフレッシュ動作時に第1の内部電源電圧発生手段で発生される第1の内部電源電圧を通常動作時に発生される第1の内部電源電圧よりも低く制御する。

【0048】

第2の電圧制御手段は、セルフリフレッシュ動作時に第2の内部電源電圧発生手段で発生される第2の内部電源電圧を通常動作時に発生される第2の内部電源電圧よりも低く制御する。

【0049】

請求項13に記載の本発明は、内部電源電位差によりスイング幅が規定される電圧スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、セルフリフレッシュ期間規定手段、および1つもしくは複数の内部電源電圧発生手段を備える。セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生する。1つもしくは複数の内部電源電圧発生手段は、内部電源電位差を発生し、セルフリフレッシュ期間規定信号に応答して、発生する内部電源電位差を制御する。少なくとも1つの内部電源電圧発生手段は、セルフリフレッシュ期間規定信号で規定される期間の開始に応答して、発生する内部電源電位差を第1の電位差から第2の電位差まで減少させる制御を行なうとともに、セルフリフレッシュ期間規定信号で規定される期間の終了に応答して、発生する内部電源電位差を第2の電位差から第1の電位差まで増加させる制御を行なう。半導体記憶装置は、昇圧電圧を発生させる昇圧電圧発生手段をさらに備え、その昇圧電圧発生手段が、リング発振手段、ポンピング手段および周波数変更手段を含む。

10

【0050】

リング発信手段は、パルス信号を発信する。ポンピング手段は、パルス信号に応答して昇圧電圧を出力する。周波数変更手段は、セルフリフレッシュ期間規定信号に応答して、その信号で規定されるセルフリフレッシュ動作の期間に、リング発信手段が発信するパルス信号の周波数を通常動作時の周波数よりも低くする。

20

【0051】

請求項14に記載の本発明は、内部電源電圧およびそれを昇圧した昇圧電圧により通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、セルフリフレッシュ期間規定手段、および昇圧電圧発生手段を備え、その昇圧電圧発生手段が、基準電源ノード、昇圧電圧出力ノード、リング発信手段、ポンピング手段、遮断手段およびNチャネルトランジスタを含む。

30

【0052】

セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生する。昇圧電圧発生手段は、内部電源電圧を昇圧した昇圧電圧を発生させる。

【0053】

基準電源ノードは、所定の基準電源電圧を受ける。昇圧電圧出力ノードは、発生した昇圧電圧を出力する。

40

【0054】

リング発信手段は、セルフリフレッシュ期間規定信号に応答して、通常動作時にパルス信号を発信し、セルフリフレッシュ動作時にパルス信号の発信を停止する。ポンピング手段は、パルス信号に応答して昇圧電圧を昇圧電圧出力ノードに供給する。

【0055】

遮断手段は、セルフリフレッシュ期間規定信号に応答して、セルフリフレッシュ動作時にポンピング手段から昇圧電圧出力ノードへの昇圧電圧の供給を遮断する。

【0056】

Nチャネルトランジスタは、基準電源ノードと昇圧電圧出力ノードとの間に設けられ、セ

50

ルフリフレッシュ期間規定信号に応答してセルフリフレッシュ時に導通し、基準電源電圧からしきい値電圧だけ低い昇圧電圧を昇圧電圧出力ノードに供給する。

【0057】

請求項15に記載の本発明は、請求項14に記載の発明の基準電源電圧が、外部電源電圧であることを特徴とする。

【0058】

請求項16に記載の本発明は、内部電源電圧およびそれを昇圧した昇圧電圧により通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、セルフリフレッシュ期間規定手段および昇圧電圧発生手段を備え、その昇圧電圧発生手段が、電源ノード、昇圧電圧出力ノード、ポンピング手段、遮断手段および外部電源電圧供給手段を含む。 10

【0059】

セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生する。昇圧電圧発生手段は、内部電源電圧を昇圧した昇圧電圧を発生させる。電源ノードは、外部電源電圧を受ける。昇圧電圧出力ノードは、発生した昇圧電圧を出力する。リング発信手段は、セルフリフレッシュ期間規定信号に応答して、通常動作時にパルス信号を発信し、セルフリフレッシュ動作時にパルス信号の発信を停止する。ポンピング手段は、パルス信号に応答して昇圧電圧を昇圧電圧出力ノードに供給する。

【0060】

遮断手段は、セルフリフレッシュ期間規定信号に応答して、セルフリフレッシュ動作時にポンピング手段から昇圧電圧出力ノードへの昇圧電圧の供給を遮断する。外部電源電圧供給手段は、外部電源電圧を受け、セルフリフレッシュ期間規定信号に応答して、セルフリフレッシュ動作時に外部電源電圧を昇圧電圧出力ノードに供給する。 20

【0061】

請求項17に記載の本発明は、内部電源電圧により通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、CMOS回路、アナログ回路、第1の内部電源電圧供給手段および第2の内部電源電圧供給手段を備える。

【0062】

CMOS回路およびアナログ回路のそれぞれは、周辺回路として動作する。

第1の内部電源電圧供給手段は、CMOS回路に対応して設けられ、セルフリフレッシュ動作時に、通常動作時よりも低い第1の内部電源電圧を供給する。 30

【0063】

第2の内部電源電圧供給手段は、アナログ回路に対応して設けられ、セルフリフレッシュ動作時に、通常動作時よりも低い第2の内部電源電圧を供給する。

【0064】

請求項18に記載の本発明は、内部電源電位差によりスイング幅が規定される電圧スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、セルフリフレッシュ期間規定手段、および1つもしくは複数の内部電源電圧発生手段を備える。セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作を行なう期間を規定するセルフリフレッシュ期間規定信号を発生する。1つもしくは複数の内部電源電圧発生手段は、内部電源電位差を発生し、セルフリフレッシュ期間規定信号に応答して、発生する内部電源電位差を制御する。少なくとも1つの内部電源電圧発生手段は、セルフリフレッシュ期間規定信号で規定される期間の開始に応答して、発生する内部電源電位差を第1の電位差から第2の電位差まで減少させる制御を行なうとともに、セルフリフレッシュ期間規定信号で規定される期間の終了に応答して、発生する内部電源電位差を第2の電位差から第1の電位差まで増加させる制御を行なう。半導体記憶装置は、比較手段および外部出力手段をさらに備える。 40

【0065】

比較手段は、内部電源電圧発生手段が発生する内部電源電位差と所定電位差とを比較し、内部電源電位差が所定電位差と同程度となった場合に出力信号を活性化する。

**【 0 0 6 6 】**

外部出力手段は、比較手段の出力信号を受け、その信号が活性化した場合に、内部電源電位差が通常動作時の電位差に復帰したこと示す所定レベルの信号を外部に出力する。

**【 0 0 6 7 】**

請求項 1 9 に記載の本発明は、第 1 の内部電源電位と、その電位よりも低い第 2 の内部電源電位との電位差によりスイング幅が規定される電位スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、第 1 の内部電源電位発生手段および第 2 の内部電源電位発生手段を備え、第 1 の内部電源電位発生手段が第 1 の電位制御手段を含み、第 2 の内部電源電位発生手段が第 2 の電位制御手段を含む。

**【 0 0 6 8 】**

第 1 の内部電源電位発生手段は、第 1 の内部電源電位を発生する。第 2 の内部電源電位発生手段は、第 2 の内部電源電位を発生する。

**【 0 0 6 9 】**

第 1 の電位制御手段は、セルフリフレッシュ動作における第 1 の内部電源電位のレベルが、通常動作における第 1 の内部電源電位のレベルよりも所定幅低くなるように、第 1 の内部電源電位のレベルを制御する。

**【 0 0 7 0 】**

第 2 の電位制御手段は、セルフリフレッシュ動作における第 2 の内部電源電位のレベルが、通常動作における第 2 の内部電源電位のレベルよりも、第 1 の電位制御手段による電位のレベルの制御幅と同じ幅だけ高くなるように、第 2 の内部電源電位のレベルを制御する。

**【 0 0 7 1 】**

電位スイングは、その中心値を通常動作時とセルフリフレッシュ動作時とて同じもしくは同程度となるように制御される。

**【 0 0 7 2 】**

請求項 2 0 に記載の本発明は、内部電源電位差でスイング幅が規定される電位スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、内部電源電位差発生手段、第 1 のリフレッシュ周期設定手段および第 2 のリフレッシュ周期設定手段を備える。

**【 0 0 7 3 】**

内部電源電位差発生手段は、内部電源電位差を発生し、セルフリフレッシュ動作の動作中の少なくとも一定期間において、電位スイングのスイング幅が通常動作におけるスイング幅よりも小さくなるように、内部電源電位差を、通常動作における内部電源電位差よりも減少させて一定値に保持した後に通常動作における内部電源電位差まで増加させる制御を行なう。

**【 0 0 7 4 】**

第 1 のリフレッシュ周期設定手段は、セルフリフレッシュ動作における標準のリフレッシュ周期を設定する。

**【 0 0 7 5 】**

第 2 のリフレッシュ周期設定手段は、内部電源電位差発生手段による内部電源電位差の減少前のセルフリフレッシュ動作におけるリフレッシュ周期を、標準のリフレッシュ周期よりも短い周期に設定する。

**【 0 0 7 6 】**

請求項 2 1 に記載の本発明は、内部電源電位差でスイング幅が規定される電位スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、内部電源電位差発生手段、第 1 のリフレッシュ周期設定手段および第 2 のリフレッシュ周期設定手段を備える。

**【 0 0 7 7 】**

内部電源電位差発生手段は、内部電源電位差を発生し、セルフリフレッシュ動作の動作中の少なくとも一定期間において、電位スイングのスイング幅が通常動作におけるスイング

10

20

30

40

50

幅よりも小さくなるように、内部電源電位差を、通常動作における内部電源電位差よりも減少させて一定値に保持した後に通常動作における内部電源電位差まで増加させる制御を行なう。

【0078】

第1のリフレッシュ周期設定手段は、セルフリフレッシュ動作における標準のリフレッシュ周期を設定する。

【0079】

第2のリフレッシュ周期設定手段は、内部電源電位差発生手段による内部電源電位差の増加前の所定の期間でのセルフリフレッシュ動作におけるリフレッシュ周期を、標準のリフレッシュ周期よりも短い周期に設定する。 10

【0080】

請求項22に記載の本発明は、内部電源電位差でスイング幅が規定される電位スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、内部電源電位差発生手段、第1のリフレッシュ周期設定手段および第2のリフレッシュ周期設定手段を備える。

【0081】

内部電源電位差発生手段は、内部電源電位差を発生し、セルリフレッシュ動作の動作中の少なくとも一定期間において、電位スイングのスイング幅が通常動作におけるスイング幅よりも小さくなるように、内部電源電位差を、通常動作における内部電源電位差よりも減少させて一定値に保持した後に通常動作における内部電源電位差まで増加させる制御を行なう。 20

【0082】

第1のリフレッシュ周期設定手段は、セルフリフレッシュ動作における標準のリフレッシュ周期を設定する。

【0083】

第2のリフレッシュ周期設定手段は、内部電源電位差発生手段による内部電源電位差の増加完了後のセルフリフレッシュ動作におけるリフレッシュ周期を、標準のリフレッシュ周期よりも短い周期に設定する。

【0084】

請求項23に記載の本発明は、内部電源電位差でスイング幅が規定される電位スイングで通常動作およびセルフリフレッシュ動作を行なう半導体記憶装置であって、第1のリフレッシュ周期設定手段および第2のリフレッシュ周期設定手段を備える。 30

【0085】

第1のリフレッシュ周期設定手段は、セルフリフレッシュ動作における標準のリフレッシュ周期を設定する。

【0086】

第2のリフレッシュ周期設定手段は、セルフリフレッシュ動作の開始当初の所定期間ににおいて、セルフリフレッシュ動作のリフレッシュ周期を、標準のリフレッシュ周期よりも短い周期に設定する。請求項24に記載の本発明は、セルフリフレッシュ動作が行なわれる半導体記憶装置であって、セルフリフレッシュ期間規定手段および内部電源電位差発生手段を備える。セルフリフレッシュ期間規定手段は、セルフリフレッシュ動作の期間を規定するセルフリフレッシュ期間規定信号を発生する。内部電源電位差発生手段は、半導体記憶装置の内部回路の基準電圧がスイッチング手段により調整可能な基準電圧発生手段と、基準電圧に基づいて内部回路に内部電源電位と接地電位との差である内部電源電位差を発生する手段とを含む。内部電源電位差発生手段は、セルフリフレッシュ期間規定信号で規定される期間に、規定される期間の前に比べ内部電源電位差を減少させる。 40

【0087】

【作用】

請求項1に記載の本発明によれば、セルフリフレッシュ動作時に、基準電圧発生手段のスイッチング手段により調整可能な基準電圧に基づいて内部電源電位差発生手段により発生 50

される、内部電源電位と接地電位との差である内部電源電位差は、通常動作時よりも電位スイングのスイング幅が小さくなるような電位差にされる。したがって、セルフリフレッシュ動作時の消費電流が減少する。

【0088】

請求項2に記載の本発明によれば、内部電源電位差発生手段は内部降圧手段であるので、セルフリフレッシュ動作時に内部電源電位差発生手段により発生される内部電源電位差は、通常動作時よりも低くされる。したがって、セルフリフレッシュ動作時の消費電流が減少する。

【0089】

請求項3に記載の本発明によれば、接地電位発生手段は、セルフリフレッシュ期間規定信号に応答して発生する接地電位を制御する。その制御においては、セルフリフレッシュ動作の開始時に接地電位が第1の電位から第2の電位まで上昇され、セルフリフレッシュ動作の終了時に接地電位が第2の電位から第1の電位まで降下される。10

【0090】

このため、セルフリフレッシュ動作において、通常動作時よりも内部電源電位差が減少される。したがって、セルフリフレッシュ動作時の消費電流が減少する。

【0091】

請求項4に記載の本発明によれば、内部電源電圧発生手段において、内部電源電位差が減少される期間と、内部電源電位差が増加される期間とが異なるため、内部電源電位差の減少期間および増加期間のそれぞれの期間を最適な長さにすることができる。したがって、20それぞれの期間における動作の安定化が図れる。

【0092】

請求項5に記載の本発明によれば、リフレッシュ周期設定手段が、減少期間規定信号、増加期間規定信号および保持期間規定信号に応答してリフレッシュ周期を設定する。その設定において、内部電源電位差の減少期間に対応して第1のリフレッシュ周期が設定される。また、内部電源電位差の増加期間に対応して第2のリフレッシュ周期が設定される。さらに、内部電源電位差が第2の電位差が保持される期間に対応して第3のリフレッシュ周期が設定される。

【0093】

第1および第2のセルフリフレッシュ周期のそれは、第3のセルフリフレッシュ周期よりも短い。したがって、内部電源電位差の増加期間および減少期間のそれにおいては、内部電源電位差が保持される期間よりも短い周期でセルフリフレッシュが行なわれる。30

【0094】

このため、内部電源電位差の増加期間および減少期間におけるメモリセルの蓄積電荷の低下に起因するバンプ等の影響を受けにくくなり、結果的に、動作が安定化する。

【0095】

請求項6に記載の本発明によれば、第1のリフレッシュ周期と第2のリフレッシュ周期とが異なるため、内部電源電位差の増加状態および減少状態のそれに適したリフレッシュを実行することが可能である。このために、請求項5に記載の本発明よりもさらに動作40が安定化する。

【0096】

請求項7に記載の本発明によれば、内部電源電位差の増加および減少のそれが、複数段階で行なわれるため、内部電源電位差が急激に変化しない。したがって、バンプ等により動作が不安定になる期間である内部電源電位差の増加期間および減少期間のそれぞれの動作が安定化される。

【0097】

請求項8に記載の本発明によれば、内部電源電位差のステップ状の減少および増加のそれぞれの1段階が、すべてのメモリセルがリフレッシュされる周期の倍数である。このため、内部電源電位差の増加期間および減少期間のバンプ等の影響が減少し、それぞれの動作50

が安定化される。

【0098】

請求項9に記載の本発明によれば、セルフリフレッシュ期間規定信号に応答して、トランジスタが導通すると、抵抗手段の抵抗値が減少する。このため、その場合には、出力ノードの電圧、すなわち、内部電源電圧の基準電圧が減少する。これにより、セルフリフレッシュ動作時において内部電源電圧が減少する。

【0099】

請求項10に記載の本発明によれば、基準電圧発生手段は、第1の基準電圧供給手段からの第1の基準電圧と第2の基準電圧供給手段からの第2の基準電圧との和を出力ノードから出力する。

10

【0100】

第2の基準電圧は、バーンインテストを行なうための基準電圧であるため、セルフリフレッシュ動作時には必要がない。このため、供給停止手段によってセルフリフレッシュ動作時の第1の基準電圧供給手段が停止される。これにより、セルフリフレッシュ動作時の消費電流が減少する。

【0101】

請求項11に記載の本発明によれば、通常動作時においては、差動増幅手段が出力する制御電圧により内部電源電圧が制御される。

【0102】

セルフリフレッシュ動作時においては、停止手段により差動増幅手段の動作が停止され、トランジスタ制御手段によりNチャネルトランジスタが導通させられる。Nチャネルトランジスタは、電源ノードと電圧出力ノードとの間に設けられているので、導通すると、外部電源電圧に基づく内部電源電圧が電圧出力ノードに供給される。

20

【0103】

したがって、セルフリフレッシュ動作のスタンバイ時にも電流を消費する差動増幅手段がセルフリフレッシュ時に停止されるので、消費電流が減少する。

【0104】

請求項12に記載の本発明によれば、メモリセルアレイおよび周辺回路に対応して第1および第2の内部電源電圧発生手段が設けられる。第1および第2の内部電源電圧発生手段により発生される第1および第2の内部電源電圧は、セルフリフレッシュ動作時において、第1および第2の電圧制御手段により通常動作時よりも低く制御される。

30

【0105】

このように、メモリセルアレイと周辺回路とで別の内部電源電圧を供給可能である。このため、特に、セルフリフレッシュ時において、メモリセルアレイおよび周辺回路のそれを最適な電源電圧で動作させることができる。

【0106】

請求項13に記載の本発明によれば、昇圧電圧発生手段においては、セルフリフレッシュ動作時に、リング発信手段の発信するパルス信号の周波数が通常動作時よりも低くされる。

【0107】

40

このため、ポンピング手段のポンピング周波数が低くなる。したがって、セルフリフレッシュ動作時の消費電流が減少する。

【0108】

請求項14に記載の本発明によれば、セルフリフレッシュ動作時に、昇圧電圧発生手段においてリング発信手段が停止するとともにポンピング手段から昇圧電圧出力ノードへの昇圧電圧の供給が遮断される。それとともに、Nチャネルトランジスタを介して基準電源電圧よりもしきい値電圧分だけ低い昇圧電圧が昇圧電圧出力ノードに供給される。

【0109】

このように、セルフリフレッシュ動作時にリング発信手段の動作が停止され、それに従つてポンピング手段の動作も停止されて、別の供給経路から昇圧電圧が供給されるため、セ

50

ルフリフレッシュ時の消費電流が減少する。

【0110】

請求項15に記載の本発明によれば、請求項14に記載の基準電源電圧として外部電源電圧が用いられる。これにより、Nチャネルトランジスタにより外部電源電圧よりもしきい値電圧分だけ低い電圧が昇圧電圧になる。

【0111】

請求項16に記載の本発明によれば、セルフリフレッシュ動作時に、昇圧電圧発生手段においてリング発信手段が停止するとともに、ポンピング手段から昇圧電圧出力ノードへの昇圧電圧の供給が遮断される。それとともに、外部電源電圧供給手段から外部電源電圧が昇圧電圧として昇圧電圧出力ノードに供給される。

10

【0112】

このように、セルフリフレッシュ動作時にリング発信手段の動作が停止され、それに伴ってポンピング手段の動作も停止されて、別の供給経路から昇圧電圧が供給されるため、セルフリフレッシュ動作時の消費電流が減少する。

【0113】

さらに、昇圧電圧が外部電源電圧のレベルとなるため、セルフリフレッシュ動作を通常動作よりも低い内部電源電圧で行なう場合のみならず、セルフリフレッシュ動作を通常動作と同じ内部電源電圧で行なう場合にも用いることが可能となる。

【0114】

請求項17に記載の本発明によれば、CMOS回路およびアナログ回路には、それぞれ対応する第1および第2の内部電源電圧供給手段から第1および第2の内部電源電圧が供給される。第1および第2の内部電源電圧のそれぞれは、セルフリフレッシュ動作時に通常動作時よりも低い電圧にされる。これにより、セルフリフレッシュ動作時の消費電流が減少する。

20

【0115】

また、内部電源電圧の供給源が異なるため、セルフリフレッシュ動作時の第1および第2の内部電源電圧を、CMOS回路およびアナログ回路の各々の安定動作に最適な電圧にすることが可能である。そのようにすれば、CMOS回路およびアナログ回路が安定して動作する。

【0116】

30

請求項18に記載の本発明によれば、セルフリフレッシュ動作の終了時において、内部電源電位差が通常動作時の電位差のレベルに復帰する場合、その内部電源電位差が所定値と同程度になると、比較手段の出力信号が活性化される。そして、その活性化に応答して、外部出力手段により所定レベルの信号が外部に出力される。

【0117】

したがって、セルフリフレッシュ動作の終了後、内部電源電位差が通常動作時の電位差に復帰したことを外部にて知ることが可能となる。

【0118】

請求項19に記載の本発明によれば、セルフリフレッシュ動作時において、第1の内部電源電位差発生手段により発生される第1の内部電源電位および第2の内部電源電位差発生手段により発生される第2の内部電源電位がそれぞれ変化する。

40

【0119】

第1の内部電源電位のレベルは、第1の電位制御手段によって、通常動作時のレベルよりも所定幅低くされる。第2の内部電源電位のレベルは、第2の電位制御手段によって、第1の内部電源電位のレベルの変化幅と同じ幅だけ、通常動作時のレベルよりも高くされる。

【0120】

このため、セルフリフレッシュ動作時の内部電源電位差は、通常動作時のその電位差よりも小さくされる。したがって、セルフリフレッシュ動作時において消費電流が減少する。さらに、その場合は、第1の内部電源電位の変化幅と、第2の内部電源電位の変化幅とが

50

等しく、かつそれらが逆に変化する。このため、セルフリフレッシュ時ににおける電位スイッチングの中心値である内部電源電位差の1/2のレベルの値は、通常動作時のその値に対して変化しない。

【0121】

内部電源電位差の1/2のレベルの値は、データの書き込みおよび読み出しが基準の電位であるが、内部電源電位差を変化させてもその値が変化しないため、内部電源電位差の変化時のパンプの影響が全くなくなる。

【0122】

請求項20に記載の本発明によれば、セルフリフレッシュ動作時に内部電源電位差発生手段により発生される内部電源電位差は、少なくとも一定期間、通常動作時の電位差よりも小さくされる。したがって、セルフリフレッシュ動作時の消費電流が減少する。

10

【0123】

また、セルフリフレッシュ動作時におけるリフレッシュは、基本的に、第1のリフレッシュ周期設定手段により設定される標準のリフレッシュ周期で実行される。そして、例外的に、内部電源電位差の減少前におけるリフレッシュは、標準のリフレッシュ周期よりも短い周期で実行される。そのリフレッシュ周期は、第2のリフレッシュ周期設定手段で設定される。

【0124】

このため、セルフリフレッシュ動作の開始までに蓄積電荷が減少して厳しい状態となっているメモリセルが、十分な電荷が蓄積された状態にされる。したがって、その時点で、リフレッシュの実力の初期化が行なえる。これにより、内部電源電位差を減少させる場合におけるパンプの影響を受けにくくなり、その結果として動作が安定化する。

20

【0125】

それに加えて、セルフリフレッシュ開始時において、短い周期でセルフリフレッシュを実行するため、メモリセルが、電荷が十分に蓄積された状態になる。このため、リフレッシュの開始時に要求されるリフレッシュの実力に関する条件を、外部からの複雑な制御を行なうことなく満足させることができる。

【0126】

請求項21に記載の本発明によれば、セルフリフレッシュ動作時に内部電源電位差発生手段により発生される内部電源電位差は、少なくとも一定期間、通常動作時の電位差よりも小さくされる。したがって、セルフリフレッシュ動作時の消費電流が減少する。

30

【0127】

また、セルフリフレッシュ動作時におけるリフレッシュは、基本的に第1のリフレッシュ周期設定手段により設定される標準のリフレッシュ周期で実行される。そして、例外的に、内部電源電位差の増加前の所定期間におけるリフレッシュは、標準のリフレッシュ周期よりも短い周期で実行される。そのリフレッシュ周期は、第2のリフレッシュ周期設定手段で設定される。

【0128】

このため、内部電源電位差の増加前において、蓄積電荷が減少して厳しい状態となっているメモリセルが、十分な電荷が蓄積された状態にされる。

40

【0129】

これにより、内部電源電位差を増加させる場合におけるパンプの影響を受けにくくなり、その結果として動作が安定化する。

【0130】

請求項22に記載の本発明によれば、セルフリフレッシュ動作時に内部電源電位差発生手段により発生される内部電源電位差は、少なくとも一定期間、通常動作時の電位差よりも小さくされる。したがって、セルフリフレッシュ動作時の消費電流が減少する。

【0131】

また、セルフリフレッシュ動作時におけるリフレッシュは、基本的に、第1のリフレッシュ周期設定手段により設定される標準のリフレッシュ周期で実行される。そして、例外的

50

に、内部電源電位差の増加完了後におけるリフレッシュは、標準のリフレッシュ周期よりも短い周期で実行される。そのリフレッシュ周期は、第2のリフレッシュ周期設定手段により設定される。

#### 【0132】

このため、内部電源電位差の増加完了までに蓄積電荷が減少して厳しい状態となっているメモリセルが、十分な電荷が蓄積された状態にされる。したがって、その時点で、リフレッシュの実力の初期化が行なえる。したがって、リフレッシュ動作から通常動作に移行する前に要求されるリフレッシュの実力に関する条件を、外部からの複雑な制御を行なうことなく満足させることができる。

#### 【0133】

請求項23に記載の本発明によれば、セルフリフレッシュ動作においては、基本的に、第1のリフレッシュ周期設定手段により設定される標準のリフレッシュ周期でリフレッシュが実行される。そして、例外的に、セルフリフレッシュ動作の開始当初の所定期間においては、第2のリフレッシュ周期設定手段により、標準のリフレッシュ周期よりも短いリフレッシュ周期が設定され、そのリフレッシュ周期でリフレッシュが行なわれる。

#### 【0134】

したがって、セルフリフレッシュ動作の開始当初において、メモリセルに十分な電荷が蓄積された状態が実現できる。これにより、その時点で、リフレッシュの実力の初期化が行なえる。請求項24に記載の本発明によれば、セルフリフレッシュ動作時に、基準電圧発生手段のスイッチング手段により調整可能な基準電圧に基づいて内部電源電位差発生手段により発生される内部電源電位と接地電位との差である内部電源電位差は、通常動作時よりも電位スイングのスイング幅が小さくなるような電位差にされる。したがって、セルフリフレッシュ動作時の消費電流が減少する。

#### 【0135】

#### 【実施例】

次に、この発明の実施例を図面に基づいて詳細に説明する。

#### 【0136】

#### 第1実施例

まず、第1実施例について説明する。

#### 【0137】

以下の説明において、ノーマル動作とは、セルフリフレッシュ動作以外の動作をいい、書込動作および読出動作を含む動作である。

#### 【0138】

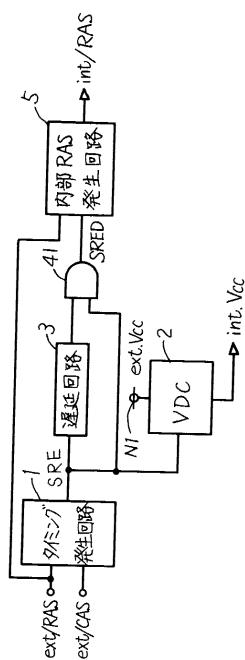

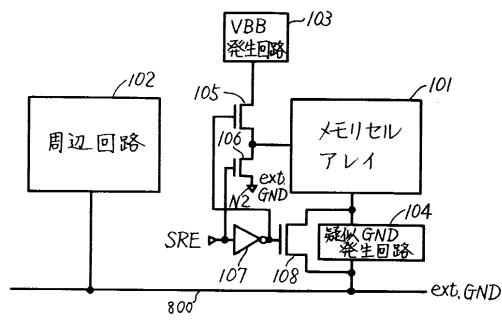

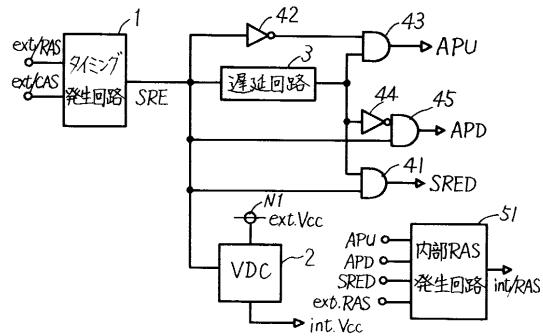

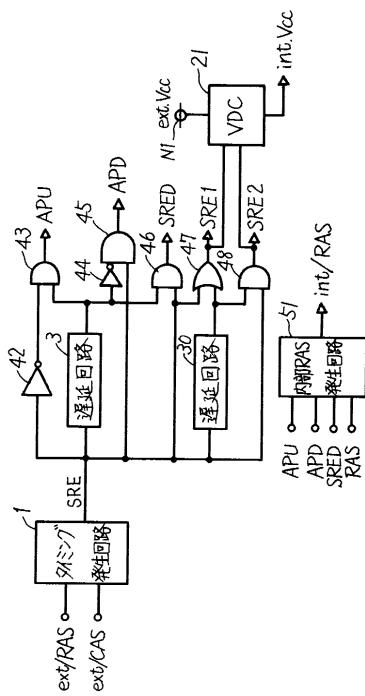

図1は、第1実施例によるDRAMのセルフリフレッシュに関連する部分の回路のブロック図である。図1を参照して、この回路には、タイミング発生回路1、内部降圧回路2、遅延回路3、ANDゲート41および内部RAS発生回路5が含まれる。

#### 【0139】

タイミング発生回路1は、外部ロウアドレスストローブ信号ext/RASおよび外部コラムアドレスストローブ信号ext/CASを受け、これらの信号に応答してセルフリフレッシュイネーブル信号SREを発生する。

#### 【0140】

内部降圧回路(VDC)2は、外部電源ノードN1から電源電圧として外部電源電圧extVccを受けるとともに制御信号として信号SREを受ける。内部降圧回路2は、外部電源電圧extVccを降圧した内部電源電圧intVccを発生する。また、内部降圧回路2は、信号SREに応答して内部電源電圧intVccのレベルを制御する。

#### 【0141】

ANDゲート41は、信号SREと、その信号SREが遅延回路3で遅延された信号とを受け、これらの信号に応答して信号SREDを出力する。

#### 【0142】

内部RAS発生回路は、信号ext/RASおよび信号SREDを受け、これらの信号に

10

20

30

40

50

応答して内部ロウアドレスストローブ信号 *int/RAS* を発生する。この信号 *int/RAS* は、セルフリフレッシュ周期を規定する信号である。

#### 【0143】

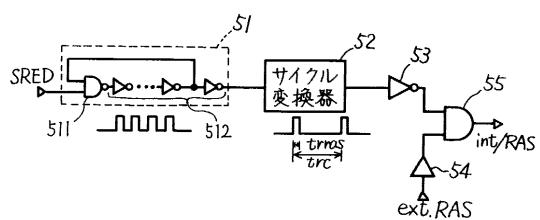

次に、図1の内部RAS発生回路5について詳細に説明する。

図2は、第1実施例による内部RAS発生回路5の構成を示す回路図である。図2を参照して、この内部RAS発生回路5は、リング発信器51、サイクル変換器52、インバータ53、バッファ54およびANDゲート55を含む。

#### 【0144】

リング発信器51は、NANDゲート511および複数のインバータよりなるインバータ列512を含む。NANDゲート511およびインバータ列512は、環状に接続される。NANDゲート511は、インバータ列512の一部のノードからフィードバックされる信号と、信号 *SRED* とを受ける。

10

#### 【0145】

このリング発信器51においては、信号 *SRED* をトリガ信号として所定周期のパルス信号を発生する。サイクル変換器52は、リング発信器51から出力されるパルス信号の間引きを行ない、入力されるパルス信号よりも長い周期のパルス信号を発生する。

#### 【0146】

サイクル変換器52で発生するパルス信号のパルス幅 *t\_rras* は、セルフリフレッシュ動作のアクティブ期間を規定するものである。したがって、そのパルス信号のパルス幅 *t\_rras* は、低電源電圧での動作状態においても十分な動作マージンを有するような幅に設定される。

20

#### 【0147】

ANDゲート55は、サイクル変換器52から出力されるパルス信号がインバータ53で反転された信号と、信号 *extRAS* がバッファ54を経た信号とを受け、これらの信号に応答して信号 *int/RAS* を出力する。すなわち、内部アドレスストローブ信号 *int/RAS* は、信号 *SRED* がHレベルであり、かつ、信号 *extRAS* がHレベルである状態で所定周期のパルス信号となる。

#### 【0148】

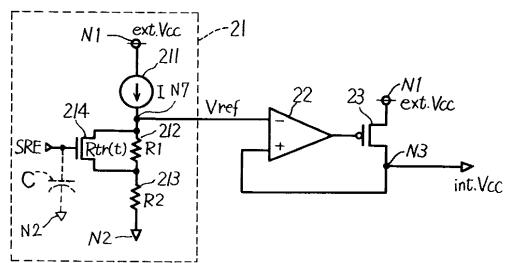

次に、図1の内部降圧回路2について詳細に説明する。

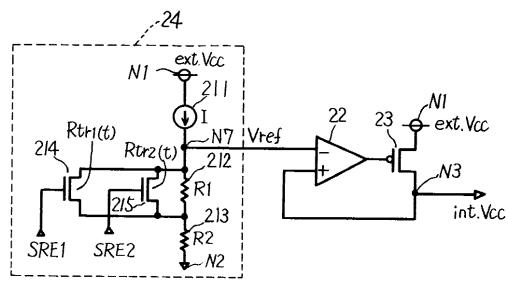

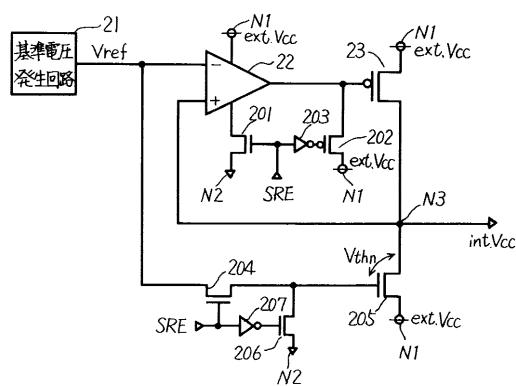

図3は、第1実施例による内部降圧回路2の構成を示す回路図である。図3を参照して、この内部降圧回路2は、基準電圧発生回路21、差動增幅回路22およびPMOSトランジスタ23を含む。

30

#### 【0149】

基準電圧発生回路21は、定電流源211、抵抗212、抵抗213およびNMOSトランジスタ214を含む。外部電源ノードN1と、出力ノードN7との間に定電流源211が接続される。出力ノードN7と、接地電位を受ける接地ノードN2との間に抵抗212および213が直列に接続される。出力ノードN7と、抵抗212および213の間のノードとの間にトランジスタ214が接続される。このトランジスタ214は、ゲートに信号 *SRE* を受けて動作する。

#### 【0150】

40

この基準電圧発生回路21は、次のように動作して基準電圧 *Vref* を発生する。

#### 【0151】

定電流源211が一定の電流 *I* を発生する。このため、抵抗212および213とトランジスタ214とに定電流源211からの電流が流れる。このように流れる電流と、抵抗212の抵抗値 *R1*、抵抗213の抵抗値 *R2* およびトランジスタ214の抵抗値 *Rtr(t)* に基づいて、出力ノードN7における電圧である基準電圧 *Vref* が発生する。この基準電圧 *Vref* は、下記(1)式で表わされる。

#### 【0152】

$$V_{ref} = I \times \{ R_1 / [1 + R_1 / R_{tr}(t) + R_2] \} \dots (1)$$

前記(1)式に基づいて、トランジスタ214がオンしている場合およびオフしている場

50

合のそれにおける基準電圧  $V_{ref}$  について説明する。

【0153】

トランジスタ 214 が完全にオンしている場合の基準電圧  $V_{ref}$  は、この場合のトランジスタ 214 のオン抵抗を  $R_{tr}$  とすると、下記(2)式で表わされる値となる。

【0154】

$$V_{ref} = I \times (R_1 / (1 + R_1 / R_{tr}) + R_2) \dots (2)$$

トランジスタ 214 がオフしている場合の基準電圧  $V_{ref}$  は、下記(3)式で表わされる値となる。

【0155】

$$V_{ref} = I \times (R_1 + R_2) \dots (3)$$

10

このように、基準電圧発生回路 21 が発生する基準電圧  $V_{ref}$  は、信号 SRE が H レベルになるセルフリフレッシュ動作時における電圧が、信号 SRE が L レベルでなるノーマル動作時の電圧よりも低く設定される。

【0156】

トランジスタ 23 は、外部電源ノード N1 と、内部電源電圧出力ノードとしての出力ノード N3 との間に接続される。差動增幅回路 22 は、基準電圧発生回路 21 からの基準電圧  $V_{ref}$  を負側入力端子に受け、出力ノード N3 から出力される内部電源電圧  $intVcc$  を正側入力端子に受ける。

【0157】

差動增幅回路 22 は、それらの信号を差動增幅し、その出力電圧をトランジスタ 23 のゲートに与える。トランジスタ 23 は、ゲートに受ける電圧に応答して導通状態が制御される。その導通状態の変化により、内部電源電圧  $intVcc$  が基準電圧  $V_{ref}$  と同じになるよう制御される。

20

【0158】

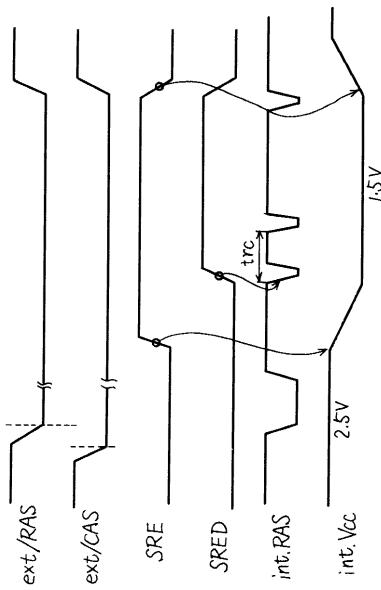

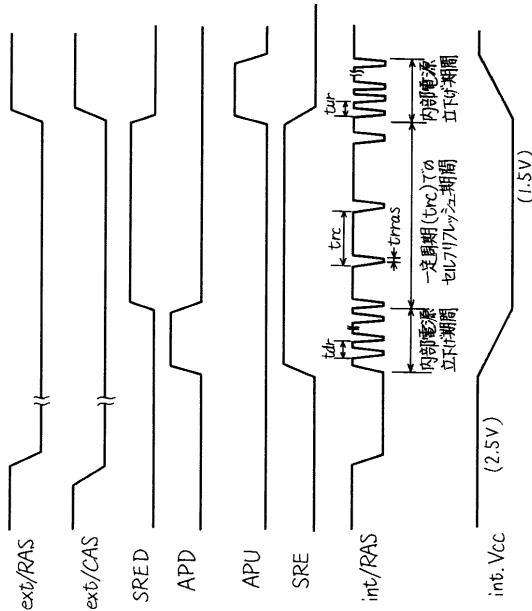

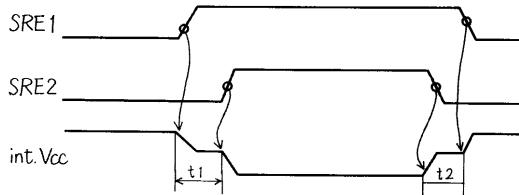

次に、図 1 の回路の動作について説明する。

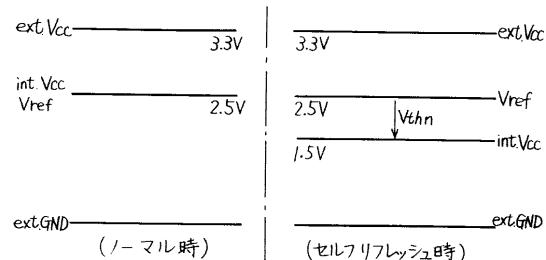

図 4 は、セルフリフレッシュ動作時における図 1 の回路の動作タイミングを示すタイミングチャートである。図 4 を参照して、CBR タイミングの後、その状態が所定期間保持されると、タイミング発生回路 1 により信号 SRE が H レベルに立上げられる。それに応答して、内部降圧回路 2 が内部電源電圧  $intVcc$  をたとえば 2.5V から 1.5V まで下降させる。

30

【0159】

その後、信号 SRE の立上がりに遅延して遅延回路 3 の出力信号が H レベルになり、これによって、信号 SRED が H レベルに立上がる。その立上がりに応答して、内部 RAS 発生回路 5 が出力する信号  $int/RAS$  が、所定のリフレッシュ周期  $t_{rc}$  のパルス信号となり、セルフリフレッシュ動作が開始される。

【0160】

そのセルフリフレッシュ動作は、たとえば、1.5V の内部電源電圧  $intVcc$  で行なわれる。したがって、この場合の電圧スイングのスイング幅は、ノーマル動作時の 2.5V よりも小さい 1.5V となる。

【0161】

その後、信号 ext/RAS が H レベルに立上がる。それに応答して、信号 SRE が L レベルに立下がる。これがセルフリフレッシュ動作停止のトリガとなる。

40

【0162】

信号 SRE が L レベルに立下がると、それに応答して、内部降圧回路 2 が内部電源電圧  $intVcc$  を、たとえば 1.5V から 2.5V に上昇させる。また、信号 SRE の立下がりに応答して信号 SRED が L レベルに立下がる。それに応答して、内部 RAS 発生回路 5 が出力する信号  $int/RAS$  がパルスの発生を停止し、セルフリフレッシュ動作が終了する。

【0163】

このように、図 1 の回路においては、セルフリフレッシュ動作時の内部電源電圧  $intV$

50

$i_{ntVcc}$  のレベルがノーマル動作時の内部電源電圧  $i_{ntVcc}$  のレベルよりも低く制御される。その結果、セルフリフレッシュ動作時の消費電流が低減できる。

#### 【0164】

具体的には、内部電源電圧  $i_{ntVcc}$  がノーマル動作時の 2.5V からセルフリフレッシュ動作時の 1.5V に下げられるという条件下では、セルフリフレッシュ動作時のアクティブ期間の消費電流が 1.5 / 2.5 に減少する。

#### 【0165】

このように、内部電源電圧を低くすると、アクセス速度は遅くなる。しかし、セルフリフレッシュ動作時においては、アクセス速度は最低限確保されていなければよいため、アクセス速度の低下は大きな問題ではない。したがって、セルフリフレッシュ動作時の内部電源電圧  $i_{ntVcc}$  が、セルフリフレッシュ動作に対するマージンを十分に確保できるような 10 10 の電圧であればよい。

#### 【0166】

以上のように、第1実施例では、内部回路における容易な制御によりセルフリフレッシュ動作時の消費電流を低減できる。

#### 【0167】

なお、以上に説明した内部降圧回路 2 は、次のような回路であってもよい。図 3 を参照して、その内部降圧回路において、トランジスタ 214 のゲートと接地ノード N2との間に、極性を有するキャパシタ C を設けてもよい。このキャパシタ C は、たとえば、MOS キャパシタである。 20 20

#### 【0168】

このようなキャパシタ C を設けると、キャパシタ C の容量により、トランジスタ 214 のゲートが受ける信号 SRE が L レベルから H レベルに変化する速度と、その信号 SRE が H レベルから L レベルに変化する速度とを異ならせることができる。

#### 【0169】

したがって、内部電源電圧  $i_{ntVcc}$  を下降させる期間の長さとそれを上昇させる期間の長さとを異ならせることができる。好ましくは、内部電源電圧  $i_{ntVcc}$  を上昇させる期間を下降させる期間よりも長くする。

#### 【0170】

このようにすると、バンプの影響を受けやすい内部電源電圧の上昇期間において、内部電源電圧  $i_{ntVcc}$  をゆっくりと上昇させることができる。したがって、バンプの影響を受けにくくすることができ、動作の安定化を図ることができる。 30 30

#### 【0171】

#### 第2実施例

次に、第2実施例について説明する。第2実施例においては、セルフリフレッシュ動作時の消費電流を低減させるその他の例として、セルフリフレッシュ動作時に、メモリセルアレイの接地電位を外部接地電位 extGND よりも高く制御する例について説明する。

#### 【0172】

図 5 は、第2実施例によるDRAMのセルフリフレッシュに関連する部分の回路のプロック図である。図 5 を参照して、このDRAMは、メモリセルアレイ 101、周辺回路 102、VBB発生回路 103、疑似 GND 発生回路 104、NMOSトランジスタ 105, 106, 108 およびインバータ 107 を含む。 40 40

#### 【0173】

接地線 800 は、外部接地電位 extGND を受ける。周辺回路 102 は、接地線 800 に接続される。メモリセルアレイ 101 は、疑似 GND 発生回路 104 およびトランジスタ 108 のそれぞれを介して接地線 800 に接続される。言い換えると、メモリセルアレイ 101 と接地線 800 との間に、疑似 GND 発生回路 104 とトランジスタ 108 とが並列に接続される。

#### 【0174】

VBB 発生回路 103 は、基板電位 VBB を発生させる。VBB 発生回路 103 と、外部 50 50

接地電位  $e_{xt}$  GND を受ける外部接地ノード N2 との間に、トランジスタ 105 および 106 が直列に接続される。トランジスタ 105 および 106 の間のノードから基板電位がメモリセルアレイ 101 に与えられる。

#### 【0175】

インバータ 107 は、図 1 に示されるような信号 SRE を受け、その信号を反転させてトランジスタ 105 および 108 のそれぞれのゲートに与える。また、トランジスタ 106 のゲートには、信号 SRE が与えられる。

#### 【0176】

疑似 GND 発生回路 104 は、疑似 GND 電位を発生する。ここで、疑似 GND 電位とは、メモリセルアレイ 101 におけるビット線のプリチャージレベルと外部接地電位  $e_{xt}$  GND との間において新たに発生される接地電位のレベルをいう。10

#### 【0177】

このような疑似 GND 電位は、具体的には、疑似 GND 発生回路 104 において、たとえば次のように発生される。疑似 GND 発生回路 104 は、メモリセルアレイと接続される疑似 GND 線およびその疑似 GND 線と接地線 800 との間に接続された NMOS トランジスタを含む。疑似 GND 発生回路 104 においては、接地線 800 の電位である外部接地  $e_{xt}$  GND から前記 NMOS トランジスタのしきい値電圧だけ高い電位である疑似 GND 電位が前記疑似 GND 線に発生する。

#### 【0178】

次に、図 5 の回路の動作について説明する。20

ノーマル動作時においては、信号 SRE が L レベルである。この場合にはトランジスタ 105 および 108 がともにオンし、トランジスタ 106 がオフする。このため、メモリセルアレイ 101 には、VBB 発生回路 103 によって発生される基板電位がトランジスタ 105 を介して与えられる。それとともに、メモリセルアレイ 101 には、外部接地電位  $e_{xt}$  GND がトランジスタ 108 を介して与えられる。

#### 【0179】

セルフリフレッシュ動作時には、信号 SRE が H レベルになる。この場合には、トランジスタ 106 がオンし、トランジスタ 105 および 108 がともにオフする。このため、メモリセルアレイ 101 への基板電位の供給が停止される。それとともに、メモリセルアレイ 101 には、接地電位として疑似 GND 発生回路 104 からの疑似 GND 電位が供給される。30

#### 【0180】

このようなセルフリフレッシュ動作時においては、メモリセルアレイ 101 の接地電位が外部接地電位  $e_{xt}$  GND よりも高い疑似 GND 電位になるため、メモリセルの電圧スイシングのスイング幅が減少する。したがって、セルフリフレッシュ動作時の消費電流が減少する。

#### 【0181】

さらに、セルフリフレッシュ動作時においてメモリセルアレイ 101 への基板電位の供給が停止されるので、VBB 発生回路 103 の消費電流が減少する。このため、セルフリフレッシュ動作時の消費電流がさらに減少することになる。40

#### 【0182】

なお、セルフリフレッシュ動作時にメモリセルアレイ 101 への基板電位の供給を停止するのは、メモリセルアレイの接地電位が外部接地電位  $e_{xt}$  GND よりも高い電位に設定されることにより、リーク電流が減少するため、敢えて、基板電位を供給する必要がないためである。

#### 【0183】

なお、第 1 実施例においては、セルフリフレッシュ動作時に内部電源電圧を低くする場合について説明し、第 2 実施例においては、セルフリフレッシュ動作時に接地電位を上昇させる場合について説明したが、セルフリフレッシュ動作時において、内部電源電圧を低下させかつ接地電位を上昇させる制御を行なってもよい。50

## 【0184】

## 第3実施例

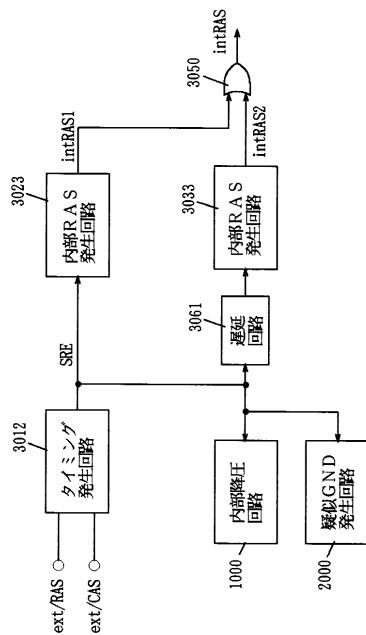

次に、第3実施例について説明する。図6は、第3実施例によるDRAMのセルフリフレッシュに関連する部分の回路のブロック図である。

## 【0185】

図6の回路が図1の回路と異なるのは、次の点である。セルフリフレッシュ動作開始時に内部電源電圧を下降させる期間を規定する内部電源電圧低下活性化信号APDを発生させるためのインバータ42およびANDゲート43が、図1の回路に付加される。

## 【0186】

また、セルフリフレッシュ動作終了時に内部電源電圧を上昇させる期間を規定する内部電源電圧上昇活性化信号APUを発生させるためのインバータ44およびANDゲート45が図1の回路に付加されている。さらに、内部RAS発生回路51の構成が図1の内部RAS発生回路と異なる。

## 【0187】

ANDゲート43は、信号SREがインバータ42で反転された信号と、遅延回路3の出力信号とを受け、それらの信号に応答して信号APUを発生する。ANDゲート45は、遅延回路3の出力信号がインバータ44で反転された信号と信号SREとを受け、それらの信号に応答して信号APDを発生する。

## 【0188】

内部RAS発生回路51は、信号APU、APD、SREDおよびextRASを受け、それらの信号に応答して、内部電源電圧intVccの下降期間、保持期間および上昇期間のそれぞれに対応した周波数の信号int/RASを発生する。

## 【0189】

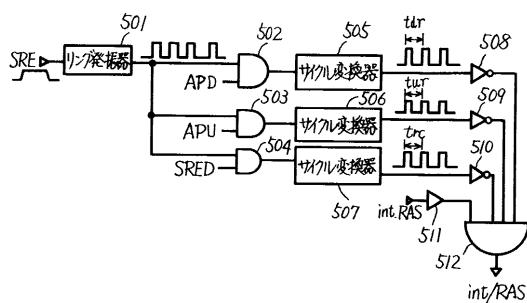

次に、内部RAS発生回路51について詳細に説明する。

図7は、内部RAS発生回路51の構成を示すブロック図である。図7を参照して、この内部RAS発生回路51は、リング発信器501、ANDゲート502, 503, 504、サイクル変換器505, 506, 507、インバータ508, 509, 510、バッファ511および4入力のANDゲート512を含む。

## 【0190】

リング発信器501は、信号SREを受け、その信号に応答して所定周期のパルス信号を発生する。ANDゲート502は、信号APUおよびリング発信器501からのパルス信号を受け、それらの信号に応答して出力信号を発生させる。ANDゲート503は、信号APDおよびリング発信器501からのパルス信号を受け、それらの信号に応答して出力信号を発生する。ANDゲート504は、信号SREDおよびリング発信器501からのパルス信号を受け、それらの信号に応答して出力信号を発生する。

## 【0191】

サイクル変換器505は、ANDゲート502からのパルス信号を受け、その信号に基づいて第1の周期tdrのパルス信号を発生する。サイクル変換器506は、ANDゲート503からのパルス信号を受け、その信号に基づいて第2の周期turのパルス信号を発生させる。サイクル変換器507は、ANDゲート504からのパルス信号を受け、その信号に基づいて第3の周期trcのパルス信号を発生させる。

## 【0192】

サイクル変換器505において発生したパルス信号はインバータ508を介して反転されてANDゲート512に与えられる。サイクル変換器506で発生したパルス信号は、インバータ509を介して反転されてANDゲート512に与えられる。サイクル変換器507で発生したパルス信号はインバータ510を介して反転されてANDゲート512に与えられる。さらに、信号ext/RASの反転信号であるextRASがバッファ511を介してANDゲート512に与えられる。

## 【0193】

ANDゲート512は、与えられた4つの信号に応答して、信号int/RASを発生す 50

る。

**【0194】**

このような内部RAS発生回路51においては、セルフリフレッシュ動作が行なわれる場合には信号SREおよび信号extRASがともにHレベルになる。このため、リング発信器501においてパルス信号が発生される。

**【0195】**

この状態において信号APDがHレベルになると、ANDゲート502からパルス信号が出力される。このため、サイクル変換器505からの第1の周期tdrを有するパルス信号が、インバータ508で反転されてANDゲート512に与えられる。この状態においては、インバータ509およびインバータ510のそれぞれからANDゲート512に与えられる信号はともにHレベルであるため、ANDゲート512から出力される信号int/RASは第1の周期のパルス信号となる。10

**【0196】**

同様に、このような状態において、信号SREDがHレベルになると、ANDゲート512から出力されるint/RASは、第3の周期trcのパルス信号となる。さらに同様に、このような状態において、信号APUがHレベルになると、ANDゲート512から第2の周期turのパルス信号が出力される。

**【0197】**

このように、内部RAS発生回路51においては、信号APD、信号SREDおよび信号APUのそれぞれに応答して、3種類の周期を有するパルス信号が信号int/RASとして発生される。20

**【0198】**

前述した第1～第3の周期のそれぞれは、内部電源電圧intVccの下降期間、保持期間および上昇期間のそれぞれについて最適な周期に設定される。なお、前記下降期間および上昇期間は、内部電源電圧intVccの過渡期であるため、バンプ等の影響を受けやすい。そのため、バンプ等の影響を受けにくくするために、第1の周期tdrおよび第2の周期tunのそれぞれは、前記保持期間における第3の周期trcよりも短い周期に設定される。

**【0199】**

これにより、セルフリフレッシュ動作時における内部電源電圧intVccの下降期間および上昇期間のそれぞれにおいてバンプ等の影響を受けにくくなる。30

**【0200】**

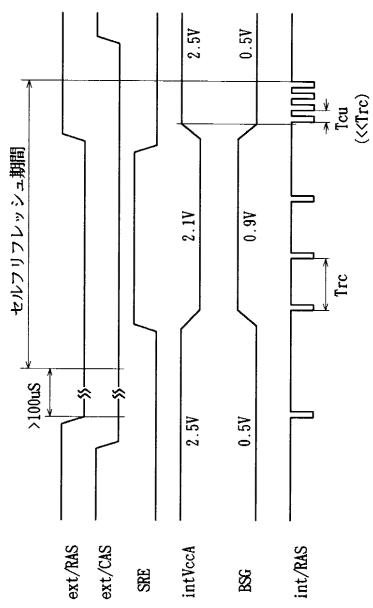

次に、図6の回路の動作について説明する。

図8は、セルフリフレッシュ動作時の図6の回路の動作タイミングを示すタイミングチャートである。図8の動作タイミングが、図4の動作タイミングと異なるのは、信号SRED、信号APD、信号APUおよび信号int/RASのそれぞれの変化である。

**【0201】**

内部電源電圧intVccは、図4の場合と同様に変化する。

信号SREがHレベルに立上ると、それに応答して、信号APDが立上る。信号APDは、内部電源電圧intVccの下降期間に対応してHレベルに保持される。これにより、信号APDがHレベルである期間、すなわち内部電源電圧intVccの下降期間において信号int/RASが第1の周期tdrを有するパルス信号となり、それに従って第1の周期tdrでのセルフリフレッシュ動作が実行される。40

**【0202】**

その後、遅延回路3における信号の遅延時間の経過後、信号APDがLレベルに立下がるとともに信号SREDがHレベルに立上る。信号SREDは、内部電源電圧intVccが低いレベルに保持されている期間に対応してHレベルに保持される。信号SREDがHレベルに保持されている期間、すなわち内部電源電圧intVccの保持期間においては、信号int/RASが第3の周期trcを有するパルス信号となる。このため、内部電源電圧intVccの保持期間においては、第3の周期trcでセルフリフレッシュ動作50

が実行される。

**【0203】**

その後、信号SREがLレベルに立下がる。その立下りに応答して、信号SREDがLレベルに立下がるとともに信号APUがHレベルに立上る。信号APUは、内部電源電圧intVccの上昇期間に対応してHレベルに保持される。このため、信号APUがHレベルに保持されている期間、すなわち、内部電源電圧intVccの上昇期間においては、信号int/RASが第2の周期turrを有するパルス信号となる。このため内部電源電圧intVccの上昇期間においては、第2の周期turrでセルフリフレッシュ動作が実行される。

**【0204】**

以上のように、第3実施例では、第1の実施例と同様に、内部回路における容易な制御によりセルフリフレッシュ動作時の消費電流を低減できる。それに加えて、第3実施例では、内部電源電圧intVccの下降期間および上昇期間のそれぞれにおいて、バンプ等の影響を受けにくい最適な周期でセルフリフレッシュが行なわれるため、第1実施例の場合よりもセルフリフレッシュ動作時の動作の安定化を図ることができる。

10

**【0205】**

なお、この第3実施例においては、セルフリフレッシュ動作時に内部電源電圧intVccの下降制御を行なうことにより電圧スイングのスイング幅を小さくしたが、これに限らず、第2実施例に示されるような接地電位の上昇制御を行なってもよい。また、前記下降制御および上昇制御を併用してもよい。

20

**【0206】**

**第4実施例**

次に、第4実施例について説明する。

**【0207】**

図9は、第4実施例によるDRAMのセルフリフレッシュに関連する部分の回路のプロック図である。図9を参照して、図9の回路が、図6の回路と異なるのは、次の点である。

**【0208】**

セルフリフレッシュ動作時における内部電源電圧intVccの下降および上昇のそれを複数段階で行なうための期間を規定する信号SRE1および信号SRE2を発生するために、図6の回路に加えて、遅延回路30、ORゲート47およびANDゲート48が設けられる。

30

**【0209】**

また、内部降圧回路21の構成が図6の内部降圧回路2と異なる。

遅延回路30は、信号SREを受け、その信号を遅延させて出力する。ORゲート47は、信号SREと遅延回路30の出力信号とを受け、それらの信号に応答して信号SRE1を発生する。ANDゲート48は、遅延回路30の出力信号と信号SREとを受け、それらの信号に応答して信号SRE2を発生する。

**【0210】**

内部降圧回路21は、信号SRE1および信号SRE2を受け、セルフリフレッシュ動作時における内部電源電圧intVccの上昇および下降のそれを2段階で行なう。

40

**【0211】**

次に、図9の内部降圧回路21について詳細に説明する。

図10は、第4実施例による内部降圧回路21の構成を示す回路図である。図10を参照して、図10の回路が図3の回路と異なるのは、基準電圧発生回路24の構成である。

**【0212】**

基準電圧発生回路24が図3の基準電圧発生回路21と異なるのは、出力ノードN7と抵抗242および243の間のノードとの間にトランジスタ214の他にNMOSトランジスタ215が接続されたことである。この基準電圧発生回路24においては、トランジスタ214が信号SRE1をゲートに受け、一方、トランジスタ215が、信号SRE2をゲートに受ける。

50

**【0213】**

次に、図10の内部降圧回路の動作について説明する。その説明においては、図3の内部降圧回路の動作と異なる動作を主に説明する。

**【0214】**

定電流源211からの電流は、抵抗212および213とトランジスタ214および215に流れる。このように流れる電流と、抵抗212の抵抗値R1、抵抗213の抵抗値R2、トランジスタ214の抵抗値R<sub>tr1</sub>(t)およびトランジスタ215の抵抗値R<sub>tr2</sub>(t)に基づいて、出力ノードN7における電圧である基準電圧V<sub>ref</sub>が発生する。この基準電圧V<sub>ref</sub>は、下記(4)式で表される。

**【0215】**

$$V_{ref} = I \times (R1 / (1 + R1 / (R_{tr1}(t) + R_{tr2}(t))) + R2) \dots (4)$$

前記(4)式に基づいて、トランジスタ214および215のそれぞれの動作状態別に発生する基準電圧V<sub>ref</sub>について説明する。

**【0216】**

トランジスタ214および215がともに完全にオンしている場合は、この場合のトランジスタ214および215のそれぞれのオン抵抗をR<sub>tr1</sub>およびR<sub>tr2</sub>とすると下記(5)式で表される値となる。

**【0217】**

$$V_{ref} = I \times (R1 / (1 + R1 / (R_{tr1} + R_{tr2}) + R2)) \dots (5)$$

トランジスタ215のみがオフしている場合の基準電圧V<sub>ref</sub>は、下記(6)式で表される値となる。

**【0218】**

$$V_{ref} = I \times (R1 / (1 + R1 / R_{tr1}) + R2) \dots (6)$$

トランジスタ214および215がともにオフしている場合の基準電圧V<sub>ref</sub>は、下記(7)式で表される値となる。

**【0219】**

$$V_{ref} = I \times (R1 + R2) \dots (7)$$

このように、内部降圧回路24においては、基準電圧V<sub>ref</sub>が3種類のレベルの電圧になり得る。したがって、内部電源電圧intVccの下降および上昇のそれぞれを2段階で実行し得る。

**【0220】**

なお、図10においては、内部電源電圧intVccを2段階で変化させる回路について説明したが、内部電源電圧intVccを3段階以上で変化させることも可能である。すなわち、トランジスタ214および215のようなNMOSトランジスタを3個以上設け、それぞれを異なる信号で制御するようにすると、内部電源電圧intVccの下降および上昇を3段階以上で実行することが可能となる。

**【0221】**

次に、図9の回路の動作について説明する。

図11は、セルフリフレッシュ動作時の図9の回路の動作タイミングを示すタイミングチャートである。図11に示される信号SRE1、信号SRE2および内部電源電圧intVcc以外の信号の変化は、図8に示されるタイミングチャートと同じである。したがって、信号SRE1、信号SRE2および内部電源電圧intVccについてのみ説明する。

**【0222】**

図11、図9および図10を参照して、信号SREが立上ると同時に信号SRE1がHレベルに立上がる。それに応答してトランジスタ214がオンし、内部電源電圧intVccが1段階下降される。そして、遅延回路30の遅延期間経過後、信号SRE2がHレベルに立上がる。それに応答してトランジスタ215がオンし、内部電源電圧intVccがさらに1段階下降される。

10

20

30

40

50

**【0223】**

そして、信号 S R E が立下がると同時に信号 S R E 2 が L レベルに立下がる。それに応答してトランジスタ 215 がオフし、内部電源電圧 i n t V c c が 1 段階上昇される。そして、遅延回路 30 の遅延期間経過後、信号 S R E 1 が L レベルに立下がる。それに応答してトランジスタ 214 がオフし、内部電源電圧 i n t V c c がさらに 1 段階上昇される。

**【0224】**

このように、内部電源電圧 i n t V c c の下降および上昇のそれぞれが 2 段階のステップで実行されると、内部電源電圧 i n t V c c の 1 回の電圧変化が小さいため、第 1 および第 3 の実施例に比べてさらに動作の安定化が図れる。

**【0225】**

また、内部電源電圧を下降および上昇させる期間のそれぞれの 1 段階の期間 t 1 および t 2 は、すべてのメモリセルがリフレッシュされるタイミングと同期させる。好ましくは、期間 t 1 および t 2 が、それぞれ第 2 の周期 t d r および第 1 の周期 t u r で全メモリセルがリフレッシュされる期間の倍数の期間に設定する。このように設定すると、下降期間および上昇期間のような電源電圧の過渡期におけるパンプの影響が減少される。そのため、動作の安定化を図ることができる。

**【0226】****第 5 実施例**

次に、第 5 実施例について説明する。

**【0227】**

第 5 実施例においては、内部降圧回路における基準電圧発生回路のその他の例について説明する。

**【0228】**

具体的には、バインテストにおいて、基準電圧を通常の内部電源電圧よりも高くする機能を有する基準電圧発生回路について説明する。

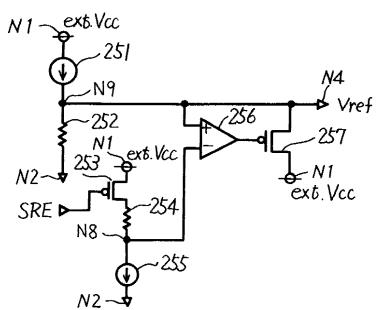

**【0229】**

図 12 は、第 5 実施例による内部降圧回路の基準電圧発生回路の構成を示すブロック図である。この基準電圧発生回路は、たとえば、図 3 における基準電圧発生回路 21 に相当するものである。図 12 を参照して、この基準電圧発生回路は、定電流源 251, 255、抵抗 252, 254、PMOS トランジスタ 253, 257 および差動增幅回路 256 を含む。

**【0230】**

外部電源ノード N 1 と接地ノード N 2 との間に定電流源 251 および抵抗 252 が接続される。定電流源 251 および抵抗 252 の間のノード N 9 が、出力ノード N 4 と接続される。外部電源ノード N 1 と接地ノード N 2 との間にトランジスタ 253、抵抗 254 および定電流源 255 が直列に接続される。

**【0231】**

トランジスタ 253 は、たとえば図 1 に示されるようなセルフリフレッシュイネーブル信号 S R E をゲートに受ける。抵抗 254 および定電流源 255 の間のノード N 8 から電圧が出力される。差動增幅回路 256 は、その正側入力端子が出力ノード N 9 に接続され、その負側入力端子がノード N 8 に接続される。

**【0232】**

外部電源ノード N 1 と出力ノード N 4 との間には、トランジスタ 257 が接続される。トランジスタ 257 のゲートは、差動增幅回路 256 の出力電圧を受ける。

**【0233】**

次に、図 12 の基準電圧発生回路の動作について説明する。定電流源 251 から抵抗 252 に一定の電流が流れ。これにより、定電流源 251 および抵抗 252 の間のノードの電圧（以下第 1 の基準電圧と呼ぶ）は常に一定の電圧になる。

**【0234】**

ノーマル動作時においては、信号 S R E が L レベルであるため、トランジスタ 253 がオ

10

20

40

50

ンしている。この場合、ノードN 8の電圧は、外部電源電圧 $extVcc$ から抵抗254の電圧効果分だけ下がった電圧値になる。すなわち、ノードN 8の電圧は、外部電源電圧 $extVcc$ に依存する。

#### 【0235】

バーインテスト時においては、外部電源電圧 $extVcc$ が通常の値よりも高く設定されるため、ノードN 8の電圧は、ノードN 9の電圧よりも高くなる。したがって、差動增幅回路256の出力電圧は、負の電圧となり、これによってトランジスタ257が導通する。これにより、外部電源電圧 $extVcc$ に基づく電圧が第2の基準電圧として出力ノードN 4に供給される。

#### 【0236】

この場合、基準電圧 $Vref$ は、前記第1の基準電圧と前記第2の基準電圧との和となる。このようにバーインテスト時において基準電圧 $Vref$ が高くなるのでバーインテストの実行が可能となる。

#### 【0237】

しかし、セルフリフレッシュ動作時には、前述のようなバーインテストを実行する必要がない。このため、セルフリフレッシュ動作時においては、信号SREに応答してトランジスタ253をオフさせる。これにより、前記第2の基準電圧を供給する回路が停止する。したがって、セルフリフレッシュ動作時における消費電流を低減できる。

#### 【0238】

#### 第6実施例

20

次に、第6実施例について説明する。前述したような内部降圧回路は、基本的に基準電圧発生回路と差動增幅回路とから構成される。差動增幅回路は、内部電源電圧を基準電圧と常に比較して内部電源電圧を調整する。したがって、セルフリフレッシュ動作のスタンバイ期間において差動增幅回路は、直流的に電流を消費する。

#### 【0239】

第6実施例においては、このような無駄な電流の消費をなくすことにより、消費電流の低減を図る例について説明する。

#### 【0240】

図13は、第6実施例による内部降圧回路の構成を示す回路図である。図13の内部降圧回路において図3と同じものには同一の参照符号を付してある。図13の内部降圧回路が図3のものと異なるのは、次の点である。

30

#### 【0241】

図13を参照して、セルフリフレッシュ動作時に差動增幅回路22の動作を停止し、かつ、PMOSトランジスタ23を介した出力ノードN3への外部電源電圧 $extVcc$ の供給を停止させるために、NMOSトランジスタ201、PMOSトランジスタ202およびインバータ203が設けられる。

#### 【0242】

また、セルフリフレッシュ動作時に外部電源電圧 $extVcc$ に基づく電圧を出力ノードN3に供給するために、NMOSトランジスタ204, 205, 206およびインバータ207が設けられる。

40

#### 【0243】

トランジスタ202は、差動增幅回路22と接地ノードN2との間に接続される。トランジスタ23のゲートと外部電源ノードN1との間にトランジスタ202が接続される。トランジスタ201は、信号SREをゲートに受け、トランジスタ202は、インバータ203を介して与えられる信号SREの反転信号をゲートに受ける。

#### 【0244】

外部電源ノードN1と出力ノードN3との間にトランジスタ205が接続される。基準電圧発生回路21の出力ノードとトランジスタ205のゲートとの間にトランジスタ204が接続される。また、トランジスタ205のゲートと接地ノードN2との間にトランジスタ206が接続される。トランジスタ205はソースホロワを構成する。

50

**【0245】**

トランジスタ204のゲートには、信号SREが与えられ、トランジスタ206のゲートには、信号SREの反転信号が与えられる。

**【0246】**

次に、図13の内部降圧回路の動作について説明する。ノーマル動作時においては、トランジスタ201, 202, 204がそれぞれオフし、トランジスタ206がオンする。したがって、トランジスタ205のゲートには接地電位が供給されるため、トランジスタ205がオフする。このため、ノーマル動作時において図13の内部降圧回路は、図3の回路と同様の動作を行なう。

**【0247】**

一方、セルフリフレッシュ動作時においては、逆に、トランジスタ201, 202, 204がそれぞれオンし、トランジスタ206がオフする。したがって、この場合、差動増幅回路22が停止される。それとともにトランジスタ23のゲート電位が外部電源電圧extVccに基づく電圧になり、トランジスタ23を介した外部電源電圧extVccの供給が停止される。

**【0248】**

さらに、それとともに、トランジスタ205のゲートにトランジスタ204を介して基準電圧Vrefが与えられるため、トランジスタ205がオンする。これにより、基準電圧Vrefからトランジスタ205のしきい値電圧Vthnだけ低い電圧が出力ノードN3に内部電源電圧として供給される。

**【0249】**

このように、セルフリフレッシュ動作時に、差動増幅回路22が停止されるため、セルフリフレッシュ動作時の消費電流を低減できる。また、セルフリフレッシュ動作時に基準電圧Vrefよりも低い電圧が内部電源電圧となるため、図3の回路と同様にセルフリフレッシュ動作時の消費電流を低減できる。次に、図13の内部降圧回路のノーマル動作時およびセルフリフレッシュ動作時の基準電圧Vrefおよび内部電源電圧intVccの具体例について説明する。

**【0250】**

図14は、図13の内部降圧回路の基準電圧Vrefおよび内部電源電圧intVccの一例を示す図である。

**【0251】**

図14を参照して、たとえば、外部電源電圧extVccが3.3Vである場合、ノーマル動作時の基準電圧Vrefと同じレベル(2.5V)の内部電源電圧intVccが発生される。一方、セルフリフレッシュ動作時においては、基準電圧Vref(2.5V)からしきい値電圧Vthn(1.0V)だけ低い1.5Vの内部電源電圧intVccが発生される。このように、第6実施例では、内部回路における容易な制御によりセルフリフレッシュ動作時の消費電流を低減できる。

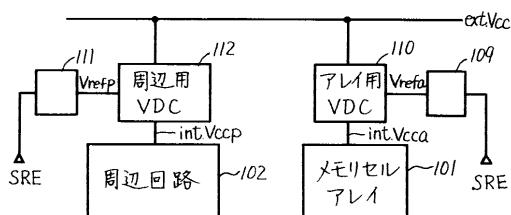

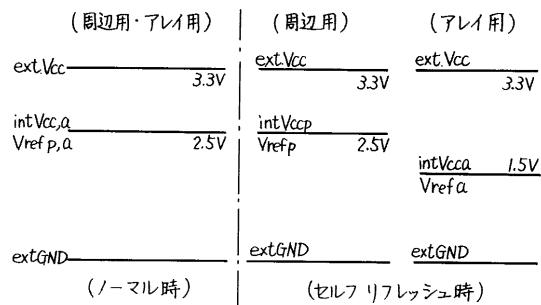

**【0252】****第7実施例**

次に、第7実施例について説明する。DRAMにおける内部電源電圧の供給方法として、メモリセルアレイへの供給経路と周辺回路への供給経路とを分離し、メモリセルアレイおよび周辺回路の各々に独立的に内部電源電圧を供給する方法がある。この供給方法は、センスアンプによるセンス動作時に生じる大電流による電圧低下が周辺回路に与える影響を防ぐために用いられる。

**【0253】**

第7実施例では、このような構成を利用し、前述したような、セルフリフレッシュ動作時の内部電源電圧を通常動作時よりも低くする制御をメモリセルアレイと周辺回路とに分けて行なう例について説明する。

**【0254】**

図15は、第7実施例によるDRAMのセルフリフレッシュ動作に関連する部分のプロッ

10

20

30

40

50

ク図である。図15の回路にはメモリセルアレイ101、周辺回路102、アレイ用基準電圧発生回路109、アレイ用内部降圧回路110、周辺用基準電圧発生回路111および周辺用内部降圧回路112が含まれる。

#### 【0255】

アレイ用基準電圧発生回路109は、メモリセルアレイ101に供給される内部電源電圧 $intV_{cc}$ の基準電圧 $V_{refa}$ を発生する。このアレイ用基準電圧発生回路109は、図1に示されるようなセルフリフレッシュイネーブル信号を受け、その信号に応答して、発生する基準電圧 $V_{refa}$ のレベルをセルフリフレッシュ動作時に通常動作時よりも低くする。

#### 【0256】

アレイ用内部降圧回路110は、電源電圧として外部電源電圧 $extV_{cc}$ を受け、制御電圧として基準電圧 $V_{refa}$ を受ける。アレイ用内部降圧回路110は、基準電圧 $V_{refa}$ に基づいて内部電源電圧 $intV_{cc}$ をメモリセルアレイ101に供給する。

#### 【0257】

周辺用基準電圧発生回路111は、周辺回路102に供給される内部電源電圧 $intV_{cc}$ の基準電圧 $V_{refp}$ を発生する。この基準電圧発生回路111は、信号SREを受け、その信号に応答して、基準電圧 $V_{refp}$ をセルフリフレッシュ動作時に通常動作時よりも低くする。

#### 【0258】

周辺用内部降圧回路112は、電源電圧として外部電源電圧 $extV_{cc}$ を受け、制御電圧として基準電圧 $V_{refp}$ を受ける。周辺用内部降圧回路112は、基準電圧 $V_{refp}$ に基づいて内部電源電圧 $intV_{cc}$ を周辺回路102に供給する。

#### 【0259】

このように、メモリセルアレイ101と周辺回路102とには、それぞれ独立的に設けられた内部降圧回路110および112から内部電源電圧 $intV_{cc}$ および $intV_{cc}$ が供給される。したがって、これらの内部電源電圧 $intV_{cc}$ および $intV_{cc}$ のそれぞれを、対応するメモリセルアレイ101および周辺回路102が安定動作するのに適した電圧に設定することにより、動作の安定化が実現できる。

#### 【0260】

次に、図15の回路により、メモリセルアレイ101および周辺回路102の各々の内部電源電圧制御の具体例について説明する。

#### 【0261】

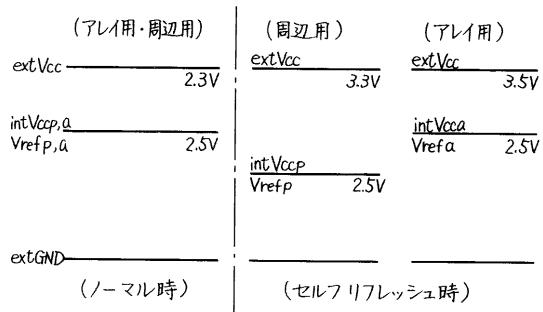

図16および図17は、図15の回路によるメモリセルアレイ101および周辺回路102の各々の内部電圧の制御方法を示す図である。

#### 【0262】

図16には、セルフリフレッシュ動作時にメモリセルアレイ101の内部電源電圧のみを低く制御する例を示す。図17には、セルフリフレッシュ動作時に周辺回路の内部電源電圧のみを低く制御する例を示す。

#### 【0263】

図16を参照して、ノーマル動作時においては、周辺回路101およびメモリセルアレイ102の内部電源電圧 $intV_{cc}$ および $intV_{cc}$ のそれぞれがたとえば2.5Vに設定される。そして、セルフリフレッシュ動作時には、メモリセルアレイ101について、信号SREに応答して基準電圧 $V_{refa}$ がたとえば1.5Vに下げられる。それに従って内部電源電圧 $intV_{cc}$ が1.5Vに下げられる。

#### 【0264】

次に図17を参照して、ノーマル動作時には、周辺回路102およびメモリセルアレイ101の内部電源電圧 $intV_{cc}$ および $intV_{cc}$ がたとえば2.5Vに設定される。そして、セルフリフレッシュ動作時には、図16の場合とは逆に、周辺回路102について、信号SREに応答して基準電圧 $V_{refp}$ がたとえば1.5Vに下げられる。それに従って、内部電源電圧 $intV_{cc}$ が1.5Vに下げられる。

10

20

30

40

50

**【0265】**

また、その他の例としては、セルフリフレッシュ動作時に周辺回路102およびメモリセルアレイ101の各々の内部電源電圧をともに下げてもよい。

**【0266】**

このように、第7の実施例においては、セルフリフレッシュ動作時に、周辺回路およびメモリセルアレイの内部電源電圧を一方のみまたは両方下げるにより、セルフリフレッシュ動作時における消費電流を低減することができる。

**【0267】**

なお、この第7実施例においては、セルフリフレッシュ動作時に内部電源電圧の下降制御を行なうことにより電圧スイングのスイング幅を小さくしたが、これに限らず、第2実施例に示されるような接地電位の上昇制御を行なってもよい。また、前記下降制御および前記上昇制御を併用してもよい。

10

**【0268】****第8実施例**

DRAMでは、チップ内に、ワード線の昇圧電圧供給回路としての昇圧電圧発生回路が設けられている。この昇圧電圧発生回路は、基本的に、リング発信器およびポンピング回路にて構成される。この昇圧回路においては、リング発信器の周波数の変化に従って消費電流が変化する。具体的には、リング発信器の周波数が低くなると消費電流が減少する。

**【0269】**

このような昇圧電圧発生回路は、ノーマル動作時において、アクセス速度の高速化のために、どのような負荷に対しても常に所定の昇圧電圧を安定して発生する必要がある。

20

**【0270】**

しかし、セルフリフレッシュ動作時においては、アクセス速度をシビアに気にする必要がない。このため、セルフリフレッシュ動作時においては、ノーマル動作時よりもリング発信器の周波数を低くしてポンピング回路のポンピング周波数を低くしてもよい。

**【0271】**

第8実施例においては、セルフリフレッシュ動作時において、リング発信器の周波数をノーマル動作時よりも低くしてポンピング回路のポンピング周波数を低くする例について説明する。

**【0272】**

30

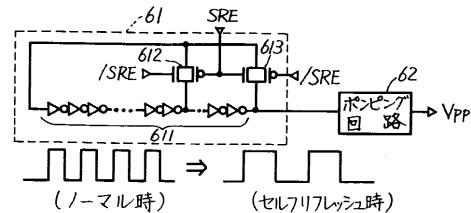

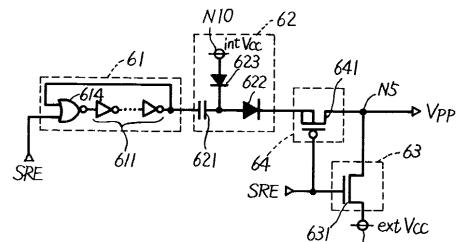

図18は、第8実施例による昇圧電圧発生回路の構成を示す回路図である。図18を参照して、この昇圧電圧発生回路は、リング発信器61およびポンピング回路62を含む。リング発信器61は、複数のインバータよりなるインバータ列611、トランスマッパー612および613を含む。

**【0273】**

インバータ列611は、その最終段のインバータと、初段のインバータとの間に設けられたトランスマッパー613を介して環状に接続される。さらに、インバータ列611は、その最終段のインバータおよび初段のインバータの間の所定のノードと、初段のインバータとの間に設けられたトランスマッパー612を介して環状に接続される。インバータ列611の最終段のインバータからポンピング回路62にパルス信号が与えられる。

40

**【0274】**

トランスマッパー613は、図1に示されるようなセルフリフレッシュイネーブル信号SREをNチャネル側のゲートに受け、Pチャネル側のゲートに信号SREの反転信号である信号/SREを受ける。トランスマッパー612は、Nチャネル側のゲートに信号/SREを受け、Pチャネル側のゲートに信号SREを受ける。

**【0275】**

このようなインバータ列611の最終段のインバータからポンピング回路62にパルス信号が与えられる。ポンピング回路62は、リング発信器61から出力されるパルス信号に応答してポンピング動作を行ない、昇圧電圧Vppを発生する。

50

**【0276】**

この昇圧電圧発生回路においては、信号 SRE が L レベルである場合には、トランスマニアゲート 612 がオンするとともにトランスマニアゲート 613 がオフする。その結果、トランスマニアゲート 612 を介在させた第 1 のインバータチェーンが形成される。

**【0277】**

一方、信号 SRE が H レベルである場合には、トランスマニアゲート 612 がオフするとともにトランスマニアゲート 613 がオンする。その結果、トランスマニアゲート 613 を介在させた第 2 のインバータチェーンが形成される。前記第 2 のインバータチェーンは、前記第 1 のインバータチェーンよりも長い。

**【0278】**

したがって、図 18 中のパルス波形が示すように、セルフリフレッシュ動作時には、ノーマル動作時よりも低い周波数のパルス信号がリング発信器 61 により発生する。このため、そのパルス信号を受けたポンピング回路 62 は、セルフリフレッシュ動作時にノーマル動作時よりも低い周波数でポンピングを行なう。

**【0279】**

このように、セルフリフレッシュ動作時にノーマル動作時よりも低い周波数でポンピングが行なわれるため、セルフリフレッシュ動作時の消費電流を低減できる。

**【0280】****第 9 実施例**

次に、第 9 実施例について説明する。

10

**【0281】**

第 9 実施例では、第 8 実施例のようにセルフリフレッシュ動作時の消費電流を低減するその他の昇圧電圧発生回路について説明する。

**【0282】**

図 19 は、第 9 実施例による昇圧電圧発生回路の構成を示す回路図である。

図 19 を参照して、この昇圧電圧発生回路は、リング発信器 61、ポンピング回路 62、外部電圧供給回路 63 および遮断回路 64 を含む。

**【0283】**

リング発信器 61 は、NOR ゲート 614 およびインバータ列 611 を含む。NOR ゲート 614 およびインバータ列 611 は、環状に接続される。NOR ゲート 614 の一方の入力端子には、図 1 に示されるようなセルフリフレッシュイネーブル信号が入力される。ポンピング回路 62 は、キャパシタ 621、ダイオード 622 および 623 を含む。キャパシタ 621 およびダイオード 622 は、リング発信器 61 と遮断回路 64 との間に接続される。ダイオード 623 は、内部電源電圧 intVcc を受ける内部電源ノード N10 と、キャパシタ 621 およびダイオード 622 の間のノードとの間に接続される。

30

**【0284】**

遮断回路 64 は、PMOS トランジスタ 641 を含む。トランジスタ 641 は、ダイオード 622 と出力ノード N5 との間に接続され、ゲートに信号 SRE を受ける。外部電圧供給回路 63 は、NMOS トランジスタ 631 を含む。トランジスタ 631 は、外部電源ノード N1 と出力ノード N5 との間に接続され、ゲートに信号 SRE を受ける。

40

**【0285】**

次に、図 19 の昇圧電圧発生回路の動作について説明する。

ノーマル動作の場合は次のように動作する。信号 SRE が L レベルである。このため、リング発信器 61 からポンピング回路 62 にパルス信号がきょうきゅうされる。そして、ポンピング回路 62 は、供給されたパルス信号に応答してポンピング動作を行ない、昇圧電圧 Vpp を発生する。

**【0286】**

この場合、トランジスタ 641 は、オンしているため、昇圧電圧 Vpp は、トランジスタ 641 を介して出力ノード N5 に供給される。また、その場合には、トランジスタ 631 がオフしているため、出力ノード N5 にはトランジスタ 641 を介した昇圧電圧が供給さ

50

れる。

**【0287】**

一方、セルフリフレッシュ動作時の場合は次のように動作する。信号 S R E が H レベルである。このため、リング発信器 61 が停止する。それに従って、ポンピング回路 62 のポンピング動作も停止する。さらに、トランジスタ 641 がオフしているので、ポンピング回路 62 からの昇圧電圧が出力ノード N5 に供給されない。

**【0288】**

一方、トランジスタ 631 がオンするので、外部電源電圧  $e_{xtVcc}$  よりもトランジスタ 631 のしきい値電圧だけ低い電圧が外部電圧供給回路 63 から出力ノード N5 に供給される。

10

**【0289】**

次に、セルフリフレッシュ動作時にポンピング回路 62 からの電圧の供給を遮断する理由について説明する。たとえば、セルフリフレッシュ動作時に内部電源電圧  $i_{ntVcc}$  をたとえば 1.5V とすると、ワード線の昇圧レベルは、たとえば 2.2V 以上必要である。図 19 の回路の場合は、外部電源電圧がたとえば 3.3V であれば、この 3.3V からトランジスタ 63 のしきい値電圧だけ低い電圧は、2.5V 程度とすることが可能である。

**【0290】**

したがって、ワード線の昇圧レベルは、前述の 2.2V よりも高い 2.5V の電圧を確保できる。このため、リング発信器 61 およびポンピング回路 62 を停止させても支障はない。

20

**【0291】**

このように、第 9 実施例ではセルフリフレッシュ動作時にリング発信器 61 およびポンピング回路 62 を停止し、昇圧電圧を、外部電源電圧  $e_{xtVcc}$  に基づく電圧で代用するため、セルフリフレッシュ動作時の消費電流を低減できる。

**【0292】**

第 10 実施例

次に、第 10 実施例について説明する。

**【0293】**

第 10 実施例は、第 9 実施例において説明した外部電圧供給回路 63 のその他の例である。

30

**【0294】**

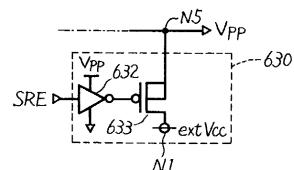

図 20 は、第 10 実施例による昇圧電圧発生回路の外部電圧供給回路の構成を示す回路図である。

**【0295】**

図 20 を参照して、この外部電圧供給回路 630 は、インバータ 632 および PMOS トランジスタ 633 を含む。トランジスタ 633 は、外部電源ノード N1 と出力ノード N5 との間に接続される。インバータ 632 は、信号 S R E を反転させてトランジスタ 633 のゲートに与える。

**【0296】**

この外部電圧供給回路 630 においては、セルフリフレッシュ動作時にトランジスタ 633 がオンする。これにより、出力ノード N5 には、外部電源電圧  $e_{xtVcc}$  と同じレベルの電圧が昇圧電圧として供給される。

40

**【0297】**

このように、セルフリフレッシュ動作時の昇圧電圧が外部電源電圧  $e_{xtVcc}$  と同じレベルになるため、このような外部電圧供給回路 630 を備えた昇圧電圧発生回路は、セルフリフレッシュ動作時にノーマル動作時よりも低いレベルの内部電源電圧を発生するのみならず、セルフリフレッシュ動作時にノーマル動作時と同じレベルの内部電源電圧を発生する場合でも使用可能である。

**【0298】**

50

次に、セルフリフレッシュ動作時の昇圧電圧を外部電源電圧  $ext\text{Vcc}$  と同じレベルにすることが妥当である理由について説明する。

**【0299】**

たとえば、セルフリフレッシュ動作時の内部電源電圧をノーマル動作時の場合と同じ 2.5 V のレベルにする場合、ワード線の昇圧レベルは、メモリセルのトランスマネージャートランジスタのしきい値電圧（たとえば 0.5 V）だけ高い 3.0 V 以上必要である。

**【0300】**

図 20 の外部電圧供給回路 630 を備えた昇圧電圧発生回路では、外部電源電圧  $ext\text{Vcc}$  がたとえば 3.3 V であれば、ワード線の昇圧レベルを 3.0 V 以上に確保できる。

**【0301】**

このように第 10 実施例においては、セルフリフレッシュ動作時にリング発信器およびポンピング回路を停止し、昇圧電圧を外部電源電圧と同じレベルの電圧で代用するため、セルフリフレッシュ動作時の消費電流を低減できる。

**【0302】**

**第 11 実施例**

次に、第 11 実施例について説明する。

**【0303】**

DRAM の周辺回路を機能的に大きく類別すると、周辺回路は、CMOS 論理で動作する CMOS 回路と、アナログ的に動作するアナログ回路とに分けられる。

**【0304】**

前記 CMOS 回路は、かなり低い内部電源電圧でも正常に動作するが、前記アナログ回路は、あまりに低い内部電源電圧では正常に動作しない。

**【0305】**

したがって、第 11 実施例では、セルフリフレッシュ動作時の前記アナログ回路の動作の安定を図るために、内部電源電圧の供給方法として、前記 CMOS 回路と前記アナログ回路との電源線を分離し、これらの回路に異なる内部電源電圧を供給する例について説明する。

**【0306】**

図 21 は、第 11 実施例による周辺回路の電源供給系の回路構成を示すブロック図である。

**【0307】**

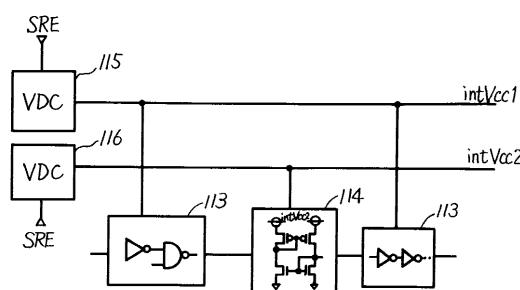

図 21においては、CMOS 回路 113, 113、アナログ回路 114、第 1 の内部降圧回路 115 および第 2 の内部降圧回路 116 が示される。この CMOS 回路 113, 113 およびアナログ回路 114 は、周辺回路を構成する。

**【0308】**

第 1 の内部降圧回路 115 は、第 1 の内部電源電圧  $int\text{Vcc1}$  を発生する。第 1 の内部降圧回路 115 は、図 1 に示されるようなセルフリフレッシュイネーブル信号 SRE を受け、その信号に応答してセルフリフレッシュ動作時にノーマル動作時よりも第 1 の内部電源電圧  $int\text{Vcc1}$  を低く制御する。第 2 の内部降圧回路 116 は、第 2 の内部電源電圧  $int\text{Vcc2}$  を発生する。第 2 の内部降圧回路 116 は、信号 SRE を受け、その信号に応答して、セルフリフレッシュ動作時にノーマル動作時よりも第 2 の内部電源電圧  $int\text{Vcc2}$  のレベルを低く制御する。

**【0309】**

この第 2 の内部降圧回路 116 においてセルフリフレッシュ動作時に発生する第 2 の内部電源電圧  $int\text{Vcc2}$  のレベルは、セルフリフレッシュ動作時の第 1 の内部電源電圧  $int\text{Vcc1}$  のレベルよりも高いレベルに設定される。

**【0310】**

第 1 の内部電源電圧  $int\text{Vcc1}$  は、CMOS 回路 113 に供給される。第 2 の内部電源電圧  $int\text{Vcc2}$  は、アナログ回路 114 に供給される。

**【0311】**

10

20

30

40

50

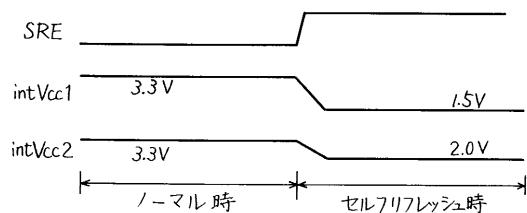

次に、図21に示される第1の内部降圧回路115および第2の内部降圧回路116の動作について説明する。図22は、図21の第1および第2の内部降圧回路115および116の動作タイミングを示すタイミングチャートである。

#### 【0312】

図22を参照して、ノーマル動作時においては、第1の内部電源電圧 $i_{ntVcc1}$ と第2の内部電源電圧 $i_{ntVcc2}$ とが同じレベル(たとえば3.3V)に設定される。そして、セルフリフレッシュ動作時には、信号SREの立上りに応答して、第1の内部電源電圧 $i_{ntVcc1}$ が1.5Vまで下降される。一方、第2の内部電源電圧 $i_{ntVcc2}$ は、信号SREの立上りに応答してたとえば2.0Vのレベルまで下降される。

#### 【0313】

このように、第1および第2の内部電源電圧 $i_{ntVcc1}$ および $i_{ntVcc2}$ はともにセルフリフレッシュ動作時に下降されるが、第2の内部電源電圧 $i_{tnVcc2}$ は第1の内部電源電圧 $i_{ntVcc1}$ よりも高いレベルに設定されるため、セルフリフレッシュ動作時におけるアナログ回路114の誤動作が防がれる。

#### 【0314】

このように、第11実施例においては、周辺回路におけるCMOS回路およびアナログ回路に対してそれぞれに異なる内部降圧回路から内部電源電圧を供給するようにし、かつ、セルフリフレッシュ動作時におけるアナログ回路の内部電源電圧がCMOS回路の内部電源電圧よりも高いレベルになるようにしたため、セルフリフレッシュ動作時における消費電流の低減が実現できるとともに周辺回路の安定動作を確保することもできる。

#### 【0315】

なお、この第11実施例においては、セルフリフレッシュ動作時に内部電源電圧の下降制御を行なうことにより電圧スイングのスイング幅を小さくしたが、これに限らず、第2実施例に示されるような接地電位の上昇制御を行なってもよい。また、前記下降制御および前記上昇制御を併用してもよい。

#### 【0316】

#### 第12実施例

次に、第12実施例について説明する。

#### 【0317】

以上の実施例で説明したようにセルフリフレッシュ動作時の内部電源電圧のレベルをノーマル動作時よりも低く制御する場合、そのセルフリフレッシュ動作の終了後にノーマル動作を行なうときには、その際に内部電源電圧がノーマル動作時のレベルに復帰しているか否かを外部のシステムにおいて確認する必要がある。

#### 【0318】

第12実施例においては、そのような内部電源電圧の復帰状態を示す信号を外部に出力する回路について説明する。

#### 【0319】

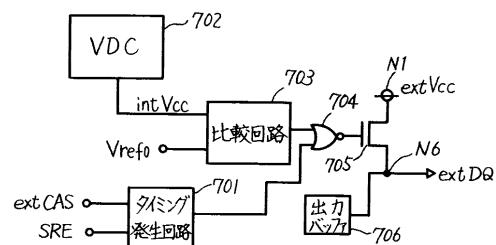

図23は、セルフリフレッシュ動作終了後の内部電源電圧の復帰状態を示す信号を外部に出力する回路のブロック図である。

#### 【0320】

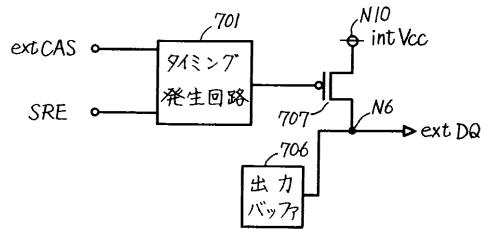

図23を参照して、この回路は、タイミング発生回路701、内部降圧回路702、比較回路703、NORゲート704およびNMOSトランジスタ705を含む。なお、出力バッファ706は、データを出力するためのバッファである。

#### 【0321】

タイミング発生回路701は、ext/CAS信号の反転信号である信号extCASおよび信号SREを受け、それらの信号に応答して、出力信号を発生する。タイミング発生回路701は、信号extCASがHレベルであり、かつ、信号SREがLレベルである場合にのみ出力信号をLレベルとし、それ以外の場合には、出力信号をHレベルとする。

#### 【0322】

内部降圧回路702は、内部電源電圧 $i_{ntVcc}$ を発生する。比較回路703は、内部

10

20

30

40

50

電源電圧  $i_{nt}V_{cc}$  と所定の基準電圧  $V_{ref0}$  を受ける。この基準電圧  $V_{ref0}$  は、内部電源電圧  $i_{nt}V_{cc}$  がノーマル動作時のレベルに復帰したことを判別するための基準レベルである。この基準電圧  $V_{ref0}$  は、内部降圧回路 702 の内部の基準電圧であってもよく、また、それ以外の信号を用いてもよい。

#### 【0323】

比較回路 703 は、内部電源電圧  $i_{nt}V_{cc}$  が基準電圧  $V_{ref0}$  以上になると出力信号を L レベルとし、内部電源電圧  $i_{nt}V_{cc}$  が基準電圧  $V_{ref0}$  よりも低い場合には出力信号を H レベルとする。

#### 【0324】

トランジスタ 705 は、外部電源ノード N1 とデータ出力ピンである出力ノード N6 との間に接続される。NOR ゲート 704 は、比較回路 703 の出力信号およびタイミング発生回路 701 の出力信号を受け、それらの信号に応答する出力信号をトランジスタ 705 のゲートに与える。10

#### 【0325】

トランジスタ 705 は、ゲートに与えられる信号に応答して導通状態が変化する。出力ノード N6 の電位は、トランジスタ 705 が導通している場合に H レベルとなる。これにより、外部出力信号  $extDQ$  が H レベルとなる。この H レベルは、外部電源電圧  $extV_{cc}$  に基づく電圧である。逆に、トランジスタ 705 が導通していない場合には、出力ノード N6 の電圧は、ハイインピーダンス状態となり、外部出力信号  $extDQ$  もハイインピーダンス状態となる。20

#### 【0326】

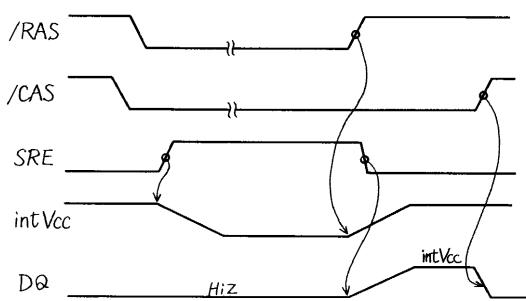

次に、図 23 の回路の動作について説明する。図 24 は、図 23 の回路の動作タイミングを示すタイミングチャートである。

#### 【0327】

図 23 および図 24 を参照して、セルフリフレッシュ動作の終了のトリガとなる信号  $ext/RAS$  が H レベルに立上ると、信号  $SRE$  が L レベルに立下る。それに応答して、内部電源電圧  $i_{nt}V_{cc}$  が上昇を開始する。その場合、信号  $i_{nt}/CAS$  が L レベルであるため、信号  $extCAS$  が H レベルであり、かつ信号  $SRE$  が L レベルであるという条件が満たされたので、タイミング発生回路 701 の出力信号が L レベルになる。30

#### 【0328】

その後、内部電源電圧  $i_{nt}V_{cc}$  が基準電圧  $V_{ref0}$  以上になると、比較回路 703 の出力信号が L レベルになる。その時点で、トランジスタ 705 がオンし、外部出力信号  $extDQ$  が H レベルに立上がる。

#### 【0329】

その後、信号  $ext/CAS$  が H レベルに立上がるため、信号  $extCAS$  が L レベルになり、トランジスタ 705 がオフする。これにより、外部出力信号  $extDQ$  が L レベルに立下がる。

#### 【0330】

なお、内部電源電圧がノーマル動作時のレベルに復帰した場合に、外部出力信号  $extDQ$  を H レベルになるようにしたが、これに限らず、そのような場合に外部出力信号  $extDQ$  を L レベルなどどのようなレベルにしてもよい。40

#### 【0331】

このように、第 12 実施例においては、セルフリフレッシュ動作の終了後に内部電源電圧が通常動作時のレベルに復帰した場合に所定レベルの信号が出力されるため、外部のシステムにおいてそのような状態を確認することができる。

#### 【0332】

なお、第 12 実施例においては、セルフリフレッシュ動作時に内部降圧回路 702 によって内部電源電圧を制御したが、これに限らず、実施例 2 に示されるような接地電位の制御を行なってもよい。また、それらの制御を併用してもよい。

#### 【0333】

10

20

30

40

50

### 第13実施例

次に、第13実施例について説明する。この第13実施例においては、第12実施例の変形例について説明する。図25は、第13実施例によるセルフリフレッシュ動作終了後の内部電源電圧の復帰状態を示す信号を外部に出力する回路のブロック図である。

#### 【0334】

図25を参照して、この回路は、タイミング発生回路701、トランジスタ707を含む。タイミング発生回路701は、図23におけるものと同じものである。

#### 【0335】

トランジスタ707は、内部電源ノードN4と出力ノードN6との間に接続され、ゲートにタイミング発生回路701の出力信号を受ける。トランジスタ707は、ゲートに受ける信号のレベルに応答して導通状態が変化する。

10

#### 【0336】

トランジスタ707がオンすると、外部出力信号 $extDQ$ はHレベルとなる。一方、トランジスタ707がオフしている状態では、外部出力信号 $extDQ$ がハイインピーダンス状態となる。したがって、外部出力信号 $extDQ$ は、内部電源電圧 $intVcc$ に依存するレベルの信号となる。

#### 【0337】

次に、図25の回路の動作について説明する。図26は、図25の回路の動作タイミングを示すタイミングチャートである。図26および図25を参照して、信号 $extRAS$ がHレベルに立上り、それに応答して信号 $SRE$ がLレベルに立下がると、それに応答して内部電源電圧 $intVcc$ が上昇を開始する。

20

#### 【0338】

その場合、信号 $extCAS$ がLレベルであるため、信号 $extCAS$ がHレベルであり、かつ信号 $SRE$ がLレベルになる。このため、タイミング発生回路701の出力信号がLレベルになる時点でトランジスタ707がオンする。

#### 【0339】

したがって、外部出力信号 $extDQ$ が内部電源電圧 $intVcc$ の増加に従って増加する。

#### 【0340】

その後、信号 $extCAS$ がHレベルに立上がるため、信号 $extCAS$ がLレベルになり、トランジスタ707がオフする。これにより外部出力信号 $extDQ$ がLレベルに立下がる。

30

#### 【0341】

なお、外部出力信号 $extDQ$ のレベルは、内部電源電圧 $intVcc$ のレベルと同じレベルとなっているが、これに限らず、内部電源電圧 $intVcc$ からNMOSトランジスタのしきい値電圧分だけ低下した電圧等、内部電源電圧 $intVcc$ に追従して変動するレベルの信号であればその他の信号でもよい。

#### 【0342】

このように、第13実施例においては、第12実施例と同様にセルフリフレッシュ動作終了後に内部電源電圧のレベルがノーマル動作時のレベルまで復帰した状態を示す信号を出力するため、外部のシステムにおいてそのような状態を確認することができる。

40

#### 【0343】

なお、この第13実施例においては、セルフリフレッシュ動作時に内部降圧回路によって内部電源電圧を低くする制御でしたが、これに限らず、第2実施例に示されるような接地電位の上昇制御を行なってもよい。また、これらの制御を併用してもよい。

#### 【0344】

### 第14実施例

次に、第14実施例について説明する。第14実施例においては、セルフリフレッシュ動作時に、内部電源電圧を低下させる制御および接地電位を上昇させる制御を行ない、その際に、 $1/2Vcc$ のレベルを変化させないようにする例について説明する。

**【0345】**

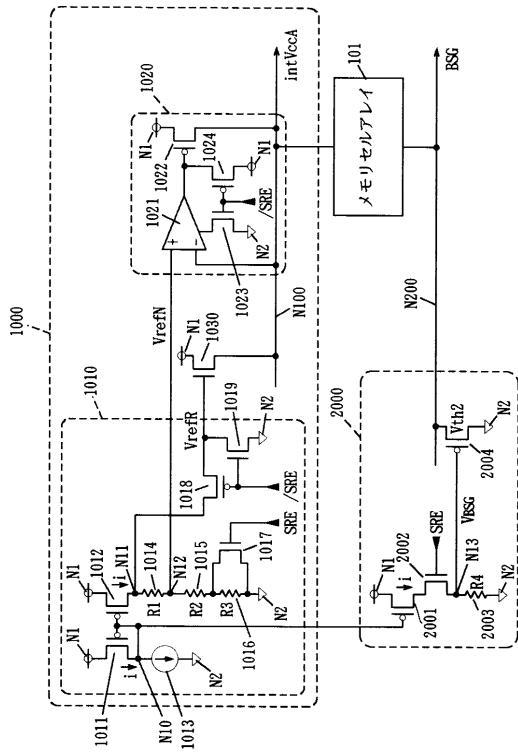

図27は、第14実施例によるDRAMのセルフリフレッシュに関する部分の回路図である。

**【0346】**

図27を参照して、このDRAMは、内部降圧回路1000、メモリセルアレイ101および疑似GND発生回路2000を含む。

**【0347】**

内部降圧回路1000は、基準電圧発生回路1010、差動增幅回路1020およびNMOTranzistor1030を含む。

**【0348】**

基準電圧発生回路1010は、PMOSトランジスタ1011, 1012, 1018、NMOSトランジスタ1017, 1019、定電流源1013および抵抗1014, 1015, 1016を含む。

**【0349】**

外部電源ノードN1と接地ノードN2との間に、トランジスタ1011および定電流源1013が直列に接続される。外部電源ノードN1と接地ノードN2との間には、トランジスタ1012、抵抗1014, 1015および1016も直列に接続される。抵抗1015および1016の間のノードと、接地ノードN2との間にトランジスタ1017が接続される。

**【0350】**

トランジスタ1011および1012のそれぞれのゲートが、トランジスタ1011および定電流源1013の間のノードN10に接続される。

**【0351】**

トランジスタ1030は、外部電源ノードN1と出力ノードN100との間に接続される。トランジスタ1012および抵抗1014の間のノードN11と、トランジスタ1030のゲートとの間にトランジスタ1018が接続される。トランジスタ1030のゲートと、接地ノードN2との間にトランジスタ1019が接続される。トランジスタ1030のゲートが受ける電圧を、以下の説明においてリフレッシュ時基準電圧VrefRと呼ぶ。

**【0352】**

トランジスタ1017は、たとえば、図1に示されるような信号SREをゲートに受ける。トランジスタ1018および1019は、信号SREの反転信号/SREをそれぞれのゲートに受ける。

**【0353】**

差動增幅回路1020は、差動增幅器1021、PMOSトランジスタ1022, 1024およびNMOSトランジスタ1023を含む。

**【0354】**

差動増幅器1021は、負側入力端子がノードN12と接続され、正側入力端子が出力ノードN100と接続される。これにより、差動増幅器1021には、ノードN12からノーマル時基準電圧VrefNを受けるとともに、出力ノードN100から内部電源電圧intVccAを受ける。

**【0355】**

外部電源ノードN1と出力ノードN100との間にトランジスタ1022が接続される。このトランジスタ1022は、ゲートに差動増幅器1021の出力電圧を受ける。外部電源ノードN1と、トランジスタ1022のゲートとの間にトランジスタ1024が接続される。差動増幅器1021と接地ノードN2との間にトランジスタ1023が接続される。トランジスタ1023および1024のそれぞれは、ゲートに、信号/SREを受ける。

**【0356】**

このように構成された差動増幅回路1020は、図13に示されたものとほぼ同様の構成

10

20

30

40

50

である。したがって、この差動増幅回路 1020 は、内部電源電圧  $intV_{ccA}$  がノーマル時基準電圧  $V_{refN}$  と一致するように、内部電源電圧  $intV_{ccA}$  を制御する。出力ノード N100 からメモリセルアレイ 101 に内部電源電圧  $intV_{ccA}$  が供給される。

#### 【0357】

このような内部降圧回路 1000 は、信号 SRE が L レベルである場合にノーマル時基準電圧  $V_{refN}$  に基づく内部電源電圧  $intV_{ccA}$  をメモリセルアレイ 101 に供給する。一方、信号 SRE が H レベルである場合に内部降圧回路 1000 は、リフレッシュ時基準電圧  $V_{refR}$  に基づく内部電源電圧  $intV_{ccA}$  をメモリセルアレイ 101 に供給する。

10

#### 【0358】

疑似 GND 発生回路 2000 は、PMOS トランジスタ 2001, 2004、NMOS トランジスタ 2002 および抵抗 2003 を含む。外部電源ノード N1 と接地ノード N2 との間にトランジスタ 2001、2002 および抵抗 2003 が直列に接続される。

#### 【0359】

出力ノード N200 と接地ノード N2 との間にトランジスタ 2004 が接続される。トランジスタ 2004 は、ゲートがトランジスタ 2002 および抵抗 2003 の間のノード N13 に接続される。以下の説明において、トランジスタ 2004 のゲートが受ける電位を VBSG と呼ぶ。トランジスタ 2001 は、ゲートがノード N10 と接続される。トランジスタ 2002 は、ゲートに信号 SRE を受ける。

20

#### 【0360】

このような疑似 GND 発生回路 2000 は、ノード N13 の電位 VBSG に応答する疑似 GND 電位 BSG をノード N200 からメモリセルアレイ 101 に供給する。この疑似 GND 電位 BSG は、信号 SRE が H レベルである場合に、信号 SRE が L レベルである場合よりも高い電位をメモリセルアレイ 101 に供給する。

#### 【0361】

次に、図 27 の回路の動作について説明する。以下の説明においては、抵抗 1014、1015、1016 および 2003 のそれぞれの抵抗値を R1、R2、R3 および R4 とする。ここでは、抵抗値 R3 および R4 が等しいと仮定する。また、トランジスタ 1030 のしきい値電圧を  $V_{th1}$  とし、トランジスタ 2004 のしきい値電圧を  $V_{th2}$  とする。また、トランジスタ 1011、1012 および 2001 は、サイズが等しいものとする。

30

#### 【0362】

図 27 の回路においては、定電流源 1013 が一定の電流  $i$  を発生する。トランジスタ 1011, 1012 および 2001 の各々は、ゲートにノード N10 の電位を受ける。このため、これらのトランジスタには等しい電流  $i$  が流れる。

#### 【0363】

まず、内部降圧回路 1000 の動作について説明する。

内部降圧回路 1000 は、ノーマル動作時において次のように動作する。

#### 【0364】

この場合、信号 SRE が L レベルであり、信号 /SRE が H レベルである。このため、基準電圧発生回路 1010 においては、トランジスタ 1017 がオフする。したがって、ノーマル時基準電圧  $V_{refN}$  は、 $i(R_2 + R_3)$  となる。

40

#### 【0365】

この場合、トランジスタ 1018 がオフし、トランジスタ 1019 がオンするため、リフレッシュ時基準電圧  $V_{refR}$  は、接地電位となる。したがって、トランジスタ 1030 がオンせず、このトランジスタ 1030 を介した電圧が出力ノード N100 に供給されない。

#### 【0366】

この場合、差動増幅回路 1020 においては、トランジスタ 1023 がオンし、トランジ

50

スタ 1 0 2 4 がオフする。したがって、差動増幅回路 1 0 2 0 が動作する。このため、内部電源電圧  $i_{nt} V_{ccA}$  は、差動増幅回路 1 0 2 0 によって、下記(8)式に示されるようなノーマル時基準電圧  $V_{refN}$  に制御される。

#### 【0367】

$$i_{nt} V_{ccA} = V_{refN} = i \times (R_2 + R_3) \dots (8)$$

一方、セルフリフレッシュ動作時において内部降圧回路 1 0 0 0 は、次のように動作する。この場合、信号 SRE が H レベルであり、信号 /SRE が L レベルである。このため、差動増幅回路 1 0 2 0 においては、トランジスタ 1 0 2 3 がオフし、トランジスタ 1 0 2 4 がオンする。したがって、差動増幅回路 1 0 2 0 が停止する。

#### 【0368】

この場合、基準電圧発生回路 1 0 1 0 においては、トランジスタ 1 0 1 7 がオンし、抵抗 1 0 1 6 が短絡される。また、トランジスタ 1 0 1 8 がオンし、トランジスタ 1 0 1 9 がオフするため、ノード N 1 1 の電圧がリフレッシュ時基準電圧  $V_{refR}$  としてトランジスタ 1 0 3 0 のゲートに供給される。

#### 【0369】

この場合のリフレッシュ時基準電圧  $V_{refR}$  は、 $i \times (R_1 + R_2)$  となる。そして、そのリフレッシュ時基準電圧  $V_{refR}$  からトランジスタ 1 0 3 0 のしきい値電圧  $V_{th1}$  だけ低い電圧が、出力ノード N 1 0 0 に内部電源電圧  $i_{nt} V_{ccA}$  として供給される。したがって、この場合の内部電源電圧  $i_{nt} V_{ccA}$  は、下記(9)式で表される値となる。

#### 【0370】

$$i_{nt} V_{ccA} = V_{refR} - V_{th1} = i \times (R_1 + R_2) - V_{th1} = i \times R_2 \dots (9)$$

したがって、セルフリフレッシュ動作時における内部電源電圧  $i_{nt} V_{ccA}$  のレベルは、ノーマル動作時のレベルよりも  $i \times R_3$  だけ低くなる。

#### 【0371】

次に、疑似 GND 発生回路 2 0 0 0 の動作について説明する。

まず、疑似 GND 電位 BSG について説明する。この疑似 GND 電位 BSG は、下記(10)式で表される値となる。

#### 【0372】

$$BSG = V_{BSG} + V_{th2} \dots (10)$$

疑似 GND 発生回路 2 0 0 0 は、ノーマル動作時において次のように動作する。この場合、トランジスタ 2 0 0 2 がオフするため、電位  $V_{BSG}$  は、0V となる。したがって、前記(10)式に基づいて、疑似 GND 電位 BSG は、 $V_{th2}$  のレベルになる。

#### 【0373】

一方、セルフリフレッシュ動作時においては次のように動作する。この場合、トランジスタ 2 0 0 2 がオンする。したがって、電位  $V_{BSG}$  は、 $i \times R_4$  となる。これにより、セルフリフレッシュ動作時の疑似 GND 電位 BSG は下記(11)式で表される値となる。

#### 【0374】

$$BSG = i \times R_4 + V_{th2} \dots (11)$$

このように、セルフリフレッシュ動作時における疑似 GND 電位 BSG のレベルは、ノーマル時のレベルよりも  $i \times R_4$  だけ上昇する。

#### 【0375】

この場合は、抵抗 1 0 1 6 の抵抗値と抵抗 2 0 0 3 の抵抗値とが等しいため、セルフリフレッシュ動作時に低下する内部電源電圧  $i_{nt} V_{ccA}$  の低下の幅と、疑似 GND 電位 BSG の上昇幅とが等しくなる。このため、セルフリフレッシュ動作時における 1/2  $V_{cc}$  のレベルは、ノーマル動作時における 1/2  $V_{cc}$  のレベルと同じになる。

#### 【0376】

このように、第 14 実施例による回路においては、セルフリフレッシュ動作時の内部電源電圧  $i_{nt} V_{ccA}$  のレベルがノーマル動作時のそのレベルよりも低く制御され、かつ、

10

20

30

40

50

セルフリフレッシュ動作時の疑似 GND 電位 BSG のレベルがノーマル動作時のそのレベルよりも高く制御される。

#### 【0377】

これにより、セルフリフレッシュ動作時の電圧スイングのスイング幅がノーマル動作時よりも小さくなる。その結果、セルフリフレッシュ動作時の消費電流が低減できる。

#### 【0378】

さらに、第14実施例においては、電圧スイングのスイング幅を変化させる際に、 $1 / 2 \text{ V}_{\text{cc}}$  のレベルが変化しない。この $1 / 2 \text{ V}_{\text{cc}}$  のレベルは、データの読み出しが書込の基準となる電位である。したがって、この $1 / 2 \text{ V}_{\text{cc}}$  のレベルが、スイング幅の変化時に変化しないことにより、第14実施例では、電圧スイングのスイング幅の変化時にパンプの影響を受けなくなり、動作が安定化される。10

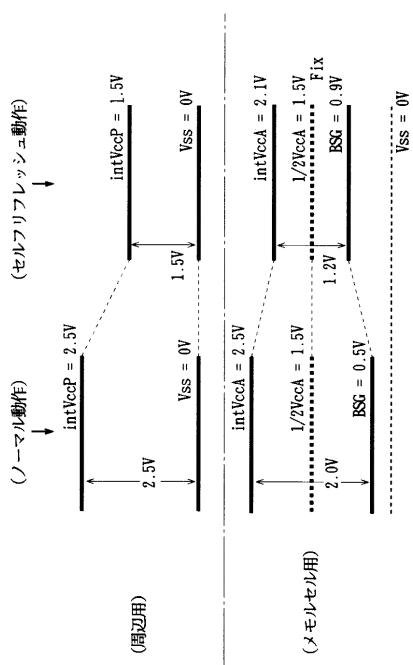

#### 【0379】

図28は、図27の回路により制御される電圧スイングのスイング幅の一例を示す図である。図28においては、上段に、周辺回路についてのスイング幅の変化の具体例が示され、下段に、メモリセルアレイ101についてのスイング幅の変化の具体例が示される。

#### 【0380】

このように、メモリセルアレイ101においては、電圧スイングのスイング幅が、ノーマル動作時の $2.0 \text{ V}$ からセルフリフレッシュ動作時には、 $1.2 \text{ V}$ に変化させられる。一方、周辺回路のスイング幅は、内部電源電圧 $\text{intV}_{\text{ccP}}$ を低下させる場合について示したが、これに限らず、少なくともメモリセルアレイ101のスイング幅を小さくすればよく、周辺回路の内部電源電圧 $\text{intV}_{\text{ccP}}$ を低下させなくてもよい。20

#### 【0381】

#### 第15実施例

次に、第15実施例について説明する。第15実施例は、セルフリフレッシュ動作を行なう期間中の一定期間にて電圧スイングのスイング幅を小さくする制御を行なう場合において、そのスイング幅を減少させる前に、標準のリフレッシュ周期よりも短いリフレッシュ周期でリフレッシュを実行させる例について説明する。

#### 【0382】

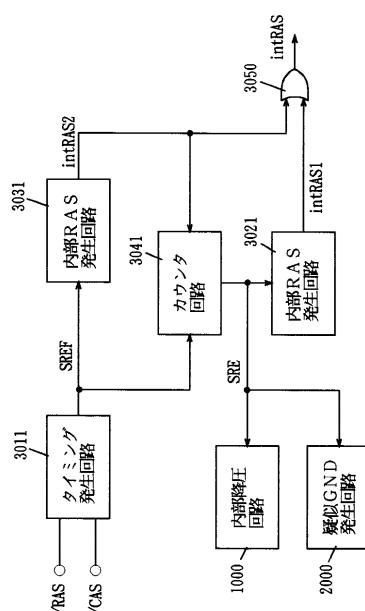

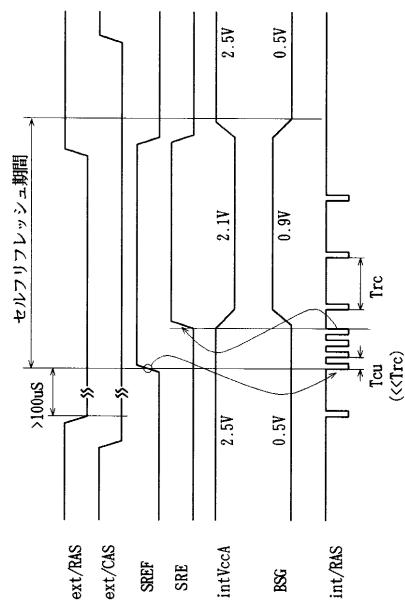

図29は、第15実施例によるDRAMのセルフリフレッシュに関する部分の回路のプロック図である。図29を参照して、この回路には、タイミング発生回路3011、内部RAS発生回路3021, 3031、カウンタ回路3041、ORゲート3050、内部降圧回路1000および疑似GND発生回路2000が含まれる。30

#### 【0383】

タイミング発生回路3011は、信号ext/RASおよび信号ext/CASを受け、これらの信号に応答して信号SREFを発生する。

#### 【0384】

内部RAS発生回路3031は、信号SREFを受け、その信号に応答して、標準のリフレッシュ周期よりもかなり短いリフレッシュ周期Tcuを規定するパルス信号である内部RAS信号intRAS2を所定期間発生する。

#### 【0385】

カウンタ回路3041は、信号SREFおよび信号intRAS2を受け、これらの信号に応答して、信号SREを発生する。カウンタ回路3041において、信号SREは、次のように発生される。カウンタ回路3041は、信号SREFの立ち上がりから信号intRAS2のカウントを開始し、そのカウント値が所定数になると信号SREをHレベルに立上げる。そして、カウンタ回路3041は、信号SREFの立ち下りに応答して信号SREを立下げる。40

#### 【0386】

内部RAS発生回路3021は、信号SREを受け、その信号に応答して、標準のリフレッシュ周期Trcを規定するパルス信号である内部RAS信号intRAS1を発生する。その信号intRAS1は、信号SREの立ち上がりからその立ち下りまで出力される。50

**【0387】**

内部降圧回路1000および疑似GND発生回路2000は、図27に示されるものと同じものである。したがって、これらは、信号SREに応答して、前述したようなスイング幅の制御を行なう。

**【0388】**

信号intRAS1および信号intRAS2のそれぞれは、ORゲート3005を経て、内部ローアドレスストーブ信号intRASとして出力される。したがって、この信号intRASは、信号intRAS1と信号intRAS2とが合成された信号となる。

**【0389】**

次に、図29の回路の動作について説明する。

10

図30は、セルフリフレッシュ動作時の図29の回路の動作タイミングを示すタイミングチャートである。図30を参照して、CBRタイミングの後、その状態が所定期間（たとえば $100\mu s$ 以上）保持されるとタイミング発生回路3011により信号SREFがHレベルに立上げられ、セルフリフレッシュ動作の期間が開始する。それに応答して、内部RAS発生回路3031が信号intRAS2の出力を開始する。このために、信号intRASが、短い周期Tcuの信号となる。

**【0390】**

その後、カウンタ回路3041のカウントアップにより、信号SREFに遅れて、信号SREが立上げられる。この信号SREの立上りと同時に、信号intRAS2の出力が停止されるとともに、内部RAS発生回路3021による信号intRAS1の出力が開始される。したがって、信号SREの立上りと同時に信号intRASの周期が、短い周期Tcuから標準の周期Trcに切換わる。

20

**【0391】**

また、信号SREの立上りに応答して、内部降圧回路1000および疑似GND発生回路2000により、電圧スイングのスイング幅が小さくされる。その後、信号ext/RASがHレベルに立上る。それに応答して、信号SREFがLレベルに立下がる。信号SREFの立下りに応答して、カウンタ回路3041により信号SREが立下げられる。

20

**【0392】**

信号SREの立下りに応答して、内部降圧回路1000および疑似GND発生回路2000により、電圧スイングのスイング幅がノーマル動作時の値まで増加させられる。この場合は、そのスイング幅がノーマル動作時の値に復帰した時点で、セルフリフレッシュ動作の期間が終了する。

30

**【0393】**

このような第15実施例においては、次のような効果が得られる。

セルフリフレッシュ動作時の電圧スイングのスイング幅が、ノーマル動作時のスイング幅よりも小さく制御される。その結果、セルフリフレッシュ動作時の消費電流が低減できる。

**【0394】**

また、セルフリフレッシュ動作の開始前において、メモリセルは、蓄積電荷が減少した厳しい状態となっている。このため、セルフリフレッシュ動作が実行される前においては、蓄積電荷が十分な状態が得られるように、外部からの複雑な制御によりリフレッシュが行なわれるのが一般的である。

40

**【0395】**

しかし、この第15実施例によれば、電圧スイングのスイング幅を小さくする前に、短周期でセルフリフレッシュが行なわれるため、前述のような外部からの複雑な制御を必要としない。そして、セルフリフレッシュ動作の期間の開始当初において、リフレッシュの実力の初期化が行なえる。

**【0396】**

さらに、このような短周期のセルフリフレッシュによりメモリセルに十分な電荷が蓄積されるため、電圧スイングのスイング幅を減少させる際のバンプの影響を受けにくくするこ

50

とができる。

**【0397】**

**第16実施例**

次に、第16実施例について説明する。第16実施例は、セルフリフレッシュ動作を行なう期間中の一定期間にて電圧スイングのスイング幅を小さくする制御を行なう場合において、そのスイング幅をノーマル動作時の値まで復帰させる前に、標準のリフレッシュ周期よりも短いリフレッシュ周期でリフレッシュを実行させる例について説明する。

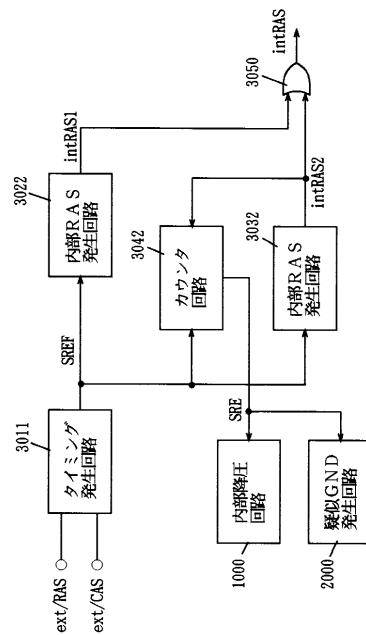

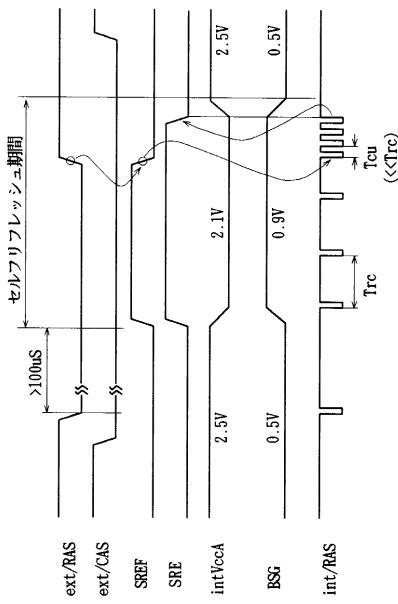

**【0398】**

図31は、第16実施例によるDRAMのセルフリフレッシュに関する部分の回路のブロック図である。図31の回路において図29と同じ部分には同一の参照符号を付し、その説明を省略する。

**【0399】**

図31を参照して、この回路には、タイミング発生回路3011、内部RAS発生回路3022, 3032、カウンタ回路3042、ORゲート3050、内部降圧回路1000および疑似GND発生回路2000が含まれる。

**【0400】**

内部RAS発生回路3022は、信号SREFを受け、その信号に応答して、標準のリフレッシュ周期Trcを規定するパルス信号である内部RAS信号intRAS1を発生する。その信号intRAS1は、信号SREFの立上りからその立下りまで出力される。

**【0401】**

内部RAS発生回路3032は、信号SREFを受け、その信号に応答して、標準のリフレッシュ周期Trcよりもかなり短いリフレッシュ周期Tcuを規定するパルス信号である内部RAS信号intRAS2を所定期間発生する。

**【0402】**

カウンタ回路3042は、信号SREFおよび信号intRAS2を受け、それらの信号に応答して信号SREを発生する。カウンタ3042において信号SREは、次のように発生される。カウンタ3042は、信号SREFの立上りに応答して信号SREをHレベルに立上げる。そして、信号SREFの立下りから、信号intRAS2のカウントを開始し、そのカウント値が所定数になると信号SREをLレベルに立下げる。

**【0403】**

次に、図31の回路の動作について説明する。

図32は、セルフリフレッシュ動作時の図31の回路の動作タイミングを示すタイミングチャートである。

**【0404】**

図32を参照して、信号SREFの立上りに応答して、内部RAS発生回路3022が信号intRAS1の出力を開始する。このために、信号int/RASが標準の周期Trcの信号となる。それとともに、信号SREFの立上りに応答して、カウンタ回路3042が信号SREをHレベルに立上げる。

**【0405】**

そして、信号SREの立上りに応答して、内部降圧回路1000および疑似GND発生回路2000により、電圧スイングのスイング幅が小さくされる。

**【0406】**

その後、信号ext/RASがHレベルに立上がる。それに応答して、信号SREFがLレベルに立下がる。信号SREFの立下りに応答して、信号intRAS1の出力が停止するとともに、内部RAS発生回路3032により信号intRAS2の出力が開始される。したがって、信号SREFの立下りに応答して、信号int/RASの周期が、標準の周期Trcから短い周期Tcuに切換わる。

**【0407】**

また、信号SREFの立下りに応答して、カウンタ回路3042が信号intRAS2のカウントを開始する。その後、カウンタ回路3042のカウントアップにより、信号SR

10

20

30

40

50

EがLレベルに立下がる。

**【0408】**

この信号SREの立下りに応答して、内部降圧回路1000および疑似GND発生回路2000により、電圧スイングのスイング幅が、ノーマル動作時の値まで復帰するように増加させられる。この場合、信号intRASの短い周期Tcuの期間の終了と同時に電圧スイングのスイング幅の増加が開始されることになる。

**【0409】**

このようにスイング幅がノーマル動作時の値に復帰した時点でセルフリフレッシュ動作の期間が終了する。

**【0410】**

このような第16実施例においては、次のような効果が得られる。

10

セルフリフレッシュ動作時の電圧スイングのスイング幅の制御により、第15実施例と同様にセルフリフレッシュ動作時の消費電流が低減できる。

**【0411】**

また、電圧スイングのスイング幅をノーマル動作時の値まで増加させる前において、一部のメモリセルは、蓄積電荷が減少した状態となっている。このため、前記一部のメモリセルにおいては、そのままの状態で電圧スイングのスイング幅が増加させられると、バンプの影響を受けやすい。

**【0412】**

しかし、この第16実施例によれば、電圧スイングのスイング幅を増加させる前に短周期でセルフリフレッシュが行なわれるため、スイング幅の増加前にすべてのメモリセルが十分な蓄積電荷を有する状態となる。したがって、電圧スイングのスイング幅を増加させる際にバンプの影響を受けにくくなる。

20

**【0413】**

**第17実施例**

次に、第17実施例について説明する。第17実施例は、セルフリフレッシュ動作を行なう期間中の一定期間にて電圧スイングのスイング幅を小さくする制御を行なう場合において、そのスイング幅をノーマル動作時の値まで復帰させた後に、標準のリフレッシュ周期よりも短いリフレッシュ周期でリフレッシュを実行させる例について説明する。

**【0414】**

30

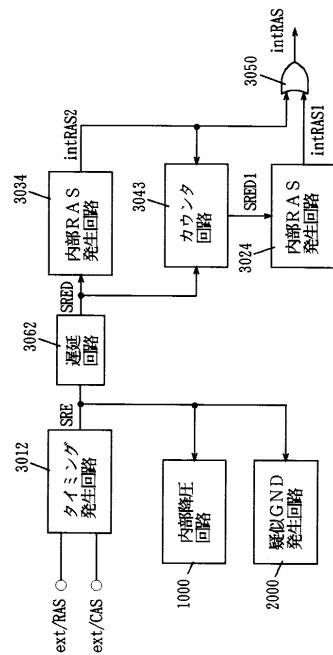

図33は、第17実施例によるDRAMのセルフリフレッシュに関する部分の回路のブロック図である。図33において、図29と同じ部分には同一の参照符号を付し、その説明を省略する。

**【0415】**

図33を参照して、この回路には、タイミング発生回路3012、内部RAS発生回路3023, 3033、ORゲート3050、遅延回路3061、内部降圧回路1000および疑似GND発生回路2000が含まれる。

**【0416】**

タイミング発生回路3012は、信号ext/RASおよび信号ext/CASを受け、これらの信号に応答して信号SREを発生する。

40

**【0417】**

内部RAS発生回路3023は、信号SREを受け、その信号に応答して、周期Trcを規定する内部RAS信号intRAS1を発生する。その信号intRAS1は、信号SREの立上りからその立下りまで出力される。

**【0418】**

遅延回路3061は、信号SREを、所定期間遅延させて内部RAS発生回路3033に与える。内部RAS発生回路3033は、遅延した信号SREを受け、その信号に応答して周期Tcuを規定する内部RAS信号intRAS2を発生する。その信号intRAS2は、遅延した信号SREの立下りから所定期間発生される。

**【0419】**

50

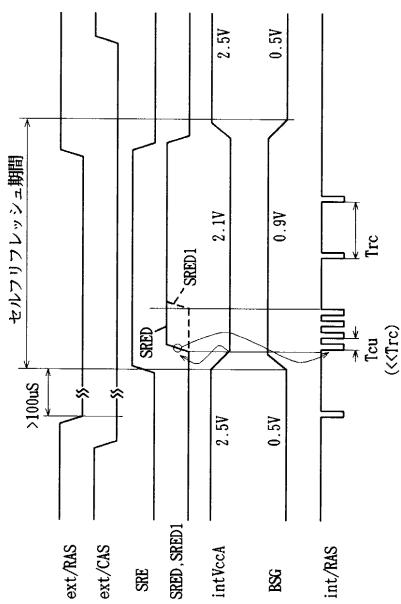

次に、図33の回路の動作について説明する。

図34は、セルフリフレッシュ動作時の図33の回路の動作タイミングを示すタイミングチャートである。

#### 【0420】

図33を参照して、CBRタイミングの後、タイミング発生回路3012により信号SREがHレベルに立上げられる。この場合のセルフリフレッシュ動作の期間は、CBRタイミングの後、その状態が所定期間（たとえば100μs以上）継続した時点から始まる。

#### 【0421】

信号SREの立上りに応答して、内部RAS発生回路3023が信号intRAS1の出力を開始する。このために、信号int/RASが標準の周期Trcの信号となる。 10

#### 【0422】

それとともに、信号SREFの立上りに応答して、内部降圧回路1000および疑似GND発生回路2000により、電圧スイングのスイング幅が小さくされる。

#### 【0423】

その後、信号ext/RASがHレベルに立上る。それに応答して、信号SREがLレベルに立下がる。その信号SREの立下りに応答して、信号intRAS1の出力が停止する。それとともに、内部降圧回路1000および疑似GND発生回路2000により電圧スイングのスイング幅が、ノーマル動作時の値まで増加を開始させられる。

#### 【0424】

遅延回路3061は、電圧スイングのスイング幅の増加開始から終了までの期間だけ信号SREを遅延させる。したがって、内部RAS発生回路3033に与えられる遅延した信号SREは、電圧スイングの増加が終了した時点でLレベルに立下がる。 20

#### 【0425】

内部RAS発生回路3033では、与えられる信号SREの立下りに応答して、信号intRAS2の出力を開始する。したがって、信号int/RASは、電圧スイングのスイング幅の増加が終了した時点から所定期間短い周期Tcuの信号となる。

#### 【0426】

このような信号intRAS2の出力が停止した時点で、この場合のセルフリフレッシュ動作の期間が終了する。

#### 【0427】

このような第17実施例においては、次のような効果が得られる。

セルフリフレッシュ動作時の電圧スイングのスイング幅の制御により、セルフリフレッシュ動作時の消費電流が低減できる。 30

#### 【0428】

また、セルフリフレッシュ動作からノーマル動作に移行する前に、メモリセルの一部は、蓄積電荷が減少した厳しい状態となっている。このため、セルフリフレッシュ動作からノーマル動作に移行する前においては、すべてのメモリセルが十分な蓄積電荷を有する状態が実現できるように、外部からの制御によりリフレッシュが行なわれるのが一般的である。

#### 【0429】

しかし、この第17実施例によれば、電圧スイングのスイング幅の増加が完了した後に、短周期でセルフリフレッシュが行なわれるため、前述のような外部からの複雑な制御を必要としない。そして、このために、セルフリフレッシュ動作の終了直前において、リフレッシュの実力の初期化が行なえる。 40

#### 【0430】

#### 第18実施例

次に、第18実施例について説明する。第18実施例は、セルフリフレッシュ動作を行なう期間中の一定期間にて電圧スイングのスイング幅を小さくする制御を行なう場合において、そのスイング幅を減少させた直後に、標準のリフレッシュ周期よりも短いリフレッシュ周期でリフレッシュを実行させる例について説明する。 50

**【0431】**

図35は、第18実施例によるDRAMのセルフリフレッシュに関する部分の回路のブロック図である。図35において、図33と同じ部分には同一の参照符号を付し、その説明を省略する。

**【0432】**

図35を参照して、この回路には、タイミング発生回路3012、内部RAS発生回路3024, 3034、カウンタ回路3043、ORゲート3050、遅延回路3062、内部降圧回路1000および疑似GND発生回路2000が含まれる。

**【0433】**

内部RAS発生回路3034は、信号SREを受け、その信号に応答して、短いリフレッシュ周期Tcuを規定するパルス信号であるintRAS2を所定期間発生する。10

**【0434】**

遅延回路3062は、信号SREを、電圧スイングのスイング幅の減少開始から終了までの期間と同じ期間だけ遅延させた信号SREDを発生する。内部RAS発生回路3034は、信号SREDを受け、その信号に応答して、短いリフレッシュ周期Tcuを規定するパルス信号である信号intRAS2を所定期間発生する。

**【0435】**

カウンタ回路3043は、信号SREDおよび信号intRAS2を受け、それらの信号に応答して、内部RAS発生回路3024を動作させるための信号SRED1を発生する。20

**【0436】**

カウンタ回路3043において、信号SRED1は、次のように発生される。カウンタ回路3043は、信号SREDの立上りから、信号intRAS2のカウントを開始し、そのカウント値が所定数になると信号SRED1をHレベルに立上げる。そして、カウンタ回路3043は、信号SREDの立下がりに応答して信号SRED1を立下げる。

**【0437】**

内部RAS発生回路3024は、信号SRED1を受け、その信号に応答して、標準のリフレッシュ周期Trcを規定するパルス信号である信号intRAS1を発生する。その信号intRAS1は、信号SRED1の立上りからその立下りまで出力される。

**【0438】**

次に、図35の回路の動作について説明する。

図36は、セルフリフレッシュ動作時の図35の回路の動作タイミングを示すチャートである。図36を参照して、CBRタイミングの後、その状態が所定期間継続されると、タイミング発生回路3012により信号SREがHレベルに立上げられ、セルフリフレッシュ動作の期間が開始する。

**【0439】**

信号SREの立上りに応答して、内部降圧回路1000および疑似GND発生回路2000により電圧スイングのスイング幅の減少が開始される。そのスイング幅の減少の終了と同時に信号SREDがHレベルに立上がる。

**【0440】**

信号SREDの立上りに応答して、内部RAS発生回路3034が、信号intRAS2の出力を開始する。このために、信号int/RASが、短い周期Tcuの信号となる。

**【0441】**

その後、カウンタ回路3043のカウントアップにより、信号SRED1が立上がる。この信号SRED1の立上りと同時に、信号intRAS2の出力が停止するとともに、内部RAS発生回路3024により信号intRAS1の出力が開始される。したがって、信号SRED1の立上りと同時に、信号intRASの周期が、短い周期Tcuから標準の周期Trcに切換わる。

**【0442】**

その後、信号ext/RASの立上りに応答して、信号SREがLレベルに立下がる。そ50

れに応答して、内部降圧回路 1000 および疑似 GND 発生回路 2000 により、電圧スイングのスイング幅がノーマル動作時の値まで増加させられる。また、信号 SRE の立下りに遅延して信号 SRED1 が立下がる。その立下りに応答して、信号 intRAS1 の出力が停止される。

#### 【0443】

この場合は、電圧スイングのスイング幅がノーマル動作時の値に復帰した時点で、セルフリフレッシュ動作の期間が終了する。

#### 【0444】

このような第 18 実施例においては、次のような効果が得られる。

セルフリフレッシュ動作時の開始当初において、メモリセルに十分な電荷が蓄積された状態が実現できる。これにより、その時点で、リフレッシュの実力の初期化が行なえる。

10

#### 【0445】

なお、この第 18 実施例においては、短い周期でのセルフリフレッシュを、電圧スイングのスイング幅の減少終了直後に実行したが、これに限らず、このような短い周期のセルフリフレッシュは、電圧スイングのスイング幅を変更しない場合のセルフリフレッシュ動作の開始当初に行なっても、同様に、リフレッシュの実力の初期化を行なうことができる。

#### 【0446】

##### 【発明の効果】

請求項 1 に記載の本発明によれば、セルフリフレッシュ動作時に、基準電圧発生手段のスイッチング手段により調整可能な基準電圧に基づいて内部電源電位差発生手段により発生される、内部電源電位と接地電位との差である内部電源電位差は、通常動作時よりも電位スイングのスイング幅が小さくなるような電位差にされる。したがって、内部回路における容易な制御によってセルフリフレッシュ動作時の消費電流を低減することができる。

20

#### 【0447】

請求項 2 に記載の本発明によれば、内部電源電位差発生手段は内部降圧手段であるので、セルフリフレッシュ動作時に内部電源電位差発生手段により発生される内部電源電圧は、通常動作時よりも低くされる。したがって、内部回路における容易な制御によってセルフリフレッシュ動作時の消費電流を低減することができる。

#### 【0448】

請求項 3 に記載の本発明によれば、セルフリフレッシュ動作の開始時に接地電位が第 1 の電位から第 2 の電位まで上昇され、セルフリフレッシュ動作の終了時に接地電位が第 2 の電位から第 1 の電位まで低下される制御が行なわれる。したがって、セルフリフレッシュ動作において、通常動作時よりも内部電源電位差が減少される。このため、内部回路における容易な制御によってセルフリフレッシュ動作時の消費電流を低減できる。

30

#### 【0449】

請求項 4 に記載の本発明によれば、内部電源電位差が減少される期間と、内部電源電位差が増加される期間とが異なるため、内部電源電位差の減少期間および増加期間のそれぞれに適した動作の安定化を図ることができる。

#### 【0450】

請求項 5 に記載の本発明によれば、内部電源電位差の減少期間および増加期間に対応して設定される第 1 および第 2 のセルフリフレッシュ周期は、第 3 のセルフリフレッシュ周期よりも短い。したがって、内部電源電位差の増加期間および減少期間においては、保持期間よりも短い周期でセルフリフレッシュが行なわれる。このため、内部電源電位差の増加期間および減少期間におけるメモリセルの蓄積電荷の低下に起因するバンプ等の影響を受けにくくすることができ、その結果、動作を安定化することができる。

40

#### 【0451】

請求項 6 に記載の本発明によれば、第 1 のリフレッシュ周期と第 2 のリフレッシュ周期とが異なるため、内部電源電位差の増加および減少のそれぞれに適した周期でのリフレッシュが実行でき、請求項 5 に記載の発明よりもさらに動作を安定化することができる。

#### 【0452】

50

請求項 7 に記載の本発明によれば、内部電源電位差の減少および増加のそれぞれが複数段階で行なわれるため、内部電源電位差が急激に変化しない。したがって、バンプ等により動作が不安定化される、内部電源電位差の増加期間および減少期間のそれぞれの動作が、安定化できる。

【 0 4 5 3 】

請求項 8 に記載の本発明によれば、内部電源電位差のステップ状の減少および増加のそれぞれの 1 段階が、すべてのメモリセルがリフレッシュされる周期の倍数であるため、内部電源電位差の増加期間および減少期間のバンプ等の影響を減少させることができ、それぞれの動作を安定化することができる。

【 0 4 5 4 】

請求項 9 に記載の本発明によれば、セルフリフレッシュ期間規定信号に応答してトランジスタ手段がオンすると、抵抗手段の抵抗値が減少する。このため、その場合には、出力ノードの電圧、すなわち、内部電源電圧の基準電圧が減少する。これにより、内部電源電圧が減少する。したがって、セルフリフレッシュ動作時の消費電流を低減することができる。

【 0 4 5 5 】

請求項 10 に記載の本発明によれば、セルフリフレッシュ動作時において、供給停止手段によってセルフリフレッシュ動作時に使用されない第 2 の基準電圧供給手段が停止される。これにより、セルフリフレッシュ動作時の消費電流を低減することができる。

【 0 4 5 6 】

請求項 11 に記載の本発明によれば、セルフリフレッシュ動作時においては、差動増幅手段の動作が停止され、N チャネルトランジスタが導通させられる。N チャネルトランジスタが導通すると、外部電源電圧に基づく内部電源電圧が電圧出力ノードに供給される。したがって、セルフリフレッシュ動作のスタンバイ時にも電流を消費する差動増幅手段がセルフリフレッシュ時に停止されるので、セルフリフレッシュ動作時における消費電流が低減できる。

【 0 4 5 7 】