# ITALIAN PATENT OFFICE

Document No.

102012902060125A1

**Publication Date**

20131214

**Applicant**

STMICROELECTRONICS S.R.L.

Title

ASSEMBLAGGIO DI UN DISPOSITIVO INTEGRATO A SEMICONDUTTORI E RELATIVO PROCEDIMENTO DI FABBRICAZIONE

#### DESCRIZIONE

del brevetto per invenzione industriale dal titolo:

"ASSEMBLAGGIO DI UN DISPOSITIVO INTEGRATO A SEMICONDUTTORI

E RELATIVO PROCEDIMENTO DI FABBRICAZIONE"

di 1) STMICROELECTRONICS S.R.L.

di nazionalità italiana

con sede: VIA C. OLIVETTI, 2

AGRATE BRIANZA (MB)

2) STMICROELECTRONICS INTERNATIONAL N.V.

di nazionalità olandese

con sede: WTC SCHIPHOL AIRPORT, SCHIPHOL BOULEVARD 265

1118 BH SCHIPHOL AIRPORT

AMSTERDAM (PAESI BASSI)

Inventori: CONTI Sebastiano, VIGNA Benedetto

\* \* \*

La presente invenzione è relativa ad un assemblaggio di un dispositivo integrato a semiconduttori e ad un relativo procedimento di fabbricazione; in particolare, la seguente trattazione farà riferimento, senza per questo perdere in generalità, all'assemblaggio di un trasduttore acustico di tipo microelettromeccanico (MEMS - MicroElectroMechanical System).

Come noto, un trasduttore acustico, ad esempio un microfono MEMS di tipo capacitivo, comprende generalmente una struttura sensibile micromeccanica, atta a trasdurre

primo utensile di taglio, avente una prima larghezza, in modo da scavare detta fetta (65) a partire da detta faccia posteriore (65b); ed in cui detta fase di tagliare detta fetta (65) comprende utilizzare un secondo utensile di taglio, avente una seconda larghezza, minore della prima.

16. Procedimento secondo la rivendicazione 13, in cui detta fase di conformare detta seconda piastrina (52) comprende:

predisporre una fetta (65) di materiale semiconduttore, avente una faccia anteriore (65a) ed una faccia posteriore (65b);

formare circuiti elettronici ASIC (52') in corrispondenza di detta faccia anteriore (65a);

scavare intagli (71) a partire da detta faccia anteriore (65a) tra circuiti elettronici ASIC (52'), tra loro adiacenti;

tagliare detta fetta (65) a partire da detta faccia posteriore (65b) per formare trincee (66) che raggiungano rispettivi intagli (71), in modo tale da ottenere una pluralità di piastrine, ciascuna atta a definire detta seconda piastrina (52).

p.i.: 1) STMICROELECTRONICS S.R.L.

2) STMICROELECTRONICS INTERNATIONAL N.V.

Lorenzo NANNUCCI.

### RIVENDICAZIONI

1. Assemblaggio di un dispositivo integrato a semiconduttori (40), comprendente:

un contenitore (package) (42) definente uno spazio interno (45);

una prima piastrina (die) (51) includente materiale semiconduttore;

una seconda piastrina (52), distinta rispetto alla prima piastrina (51), anch'essa includente materiale semiconduttore;

dette prima (51) e seconda (52) piastrina essendo accoppiate ad una superficie interna (43a; 44a) del contenitore (42) rivolta verso detto spazio interno (45),

caratterizzato dal fatto che detta seconda piastrina (52) è conformata in modo da essere parzialmente sovrapposta a detta prima piastrina (51), al di sopra di detta superficie interna (43a; 44a).

- 2. Assemblaggio secondo la rivendicazione 1, in cui detta prima piastrina (51) integra una struttura di rilevamento micromeccanica (51'), e detta seconda piastrina (52) integra un circuito elettronico ASIC (52') accoppiato funzionalmente a detta struttura di rilevamento micromeccanica (51').

- 3. Assemblaggio secondo la rivendicazione 1 o 2, in cui detta seconda piastrina (52) include una prima porzione

- (54) direttamente accoppiata a detta superficie interna (43a; 44a), ed una seconda porzione (55), supportata da detta prima porzione (54), in modo tale da essere sospesa a sbalzo a distanza da detta superficie interna (43a; 44a), sovrapposta al di sopra di detta prima piastrina (51) per una distanza di sovrapposizione (d).

- 4. Assemblaggio secondo la rivendicazione 3, in cui detta prima porzione (54) e detta seconda porzione (55) sono parte integrale di uno stesso corpo (65), includente materiale semiconduttore.

- 5. Assemblaggio secondo la rivendicazione 3 o 4, in cui detta seconda porzione (55) integra un circuito elettronico ASIC (52'), e porta, in corrispondenza di una sua superficie esterna (55a) non affacciata a detta prima piastrina (51) prime piazzole di collegamento (56a); includente inoltre fili di collegamento elettrici (57) tra dette prime piazzole di collegamento (56a) e rispettive piazzole di collegamento (58) portate da una rispettiva superficie esterna (51a) di detto primo die (51), affacciata a detto secondo die (52).

- 6. Assemblaggio secondo una qualsiasi delle rivendicazioni 3-5, in cui detta prima porzione (54) presenta una dimensione verticale, in una direzione (z) ortogonale a detta superficie interna (43a; 44a), maggiore rispetto ad una corrispondente dimensione verticale di

detto primo die (51).

- 7. Assemblaggio secondo una qualsiasi delle rivendicazioni precedenti, in cui detto contenitore (42) comprende un substrato di base (43) ed un elemento di copertura (44), definenti congiuntamente detto spazio interno (45); in cui detto substrato di base (43) presenta una superficie esterna (43b) affacciata all'esterno di detto spazio interno (45) e portante contatti elettrici (49), e detto elemento di copertura (44) presenta una conformazione a tazza; ed in cui detta superficie interna (44a) è una parete interna di detto elemento di copertura (44) affacciata a detto spazio interno (45).

- 8. Assemblaggio secondo una qualsiasi delle rivendicazioni 1-6, in cui detto contenitore (42) comprende un substrato di base (43) ed un elemento di copertura (44), definenti congiuntamente detto spazio interno (45); in cui detto substrato di base (43) presenta una superficie (43b) affacciata all'esterno di detto spazio esterna interno (45) e portante contatti elettrici (49), e detto elemento di copertura (44) presenta una conformazione a tazza; ed in cui detta superficie interna (43a) è una parete interna di detto substrato di base (43) affacciata a detto spazio interno (45) ed opposta a detta superficie esterna (43b).

- 9. Assemblaggio secondo la rivendicazione 7 o 8, in

cui detto contenitore (42) presenta un'apertura di accesso (46) attraverso almeno uno tra detto substrato di base (43) e detto elemento di copertura (44), atta a mettere in comunicazione detto spazio interno (45) con un ambiente esterno (47); ed in cui detta prima piastrina (51) integra un trasduttore acustico MEMS (1), includente una membrana (2) sospesa al di sopra di una cavità (3) ed affacciata ad un piatto rigido (5); detta prima piastrina (51) essendo interposta tra detta apertura di accesso (46) e detto spazio interno (45), con detta cavità (3) in comunicazione fluidica con detta apertura di accesso (46).

- 10. Assemblaggio secondo qualsiasi una delle rivendicazioni 7-9, in cui detto elemento di copertura (44) presenta una conformazione a tazza con pareti laterali; dette pareti laterali essendo accoppiate a detto substrato di base (43) mediante elementi di accoppiamento includenti materiale almeno parzialmente conduttivo; in cui collegamenti elettrici (60) sono previsti tra detta seconda piastrina (52) e detto substrato di base (43) attraverso detti elementi di accoppiamento (50) e regioni di contatto (34) portate da dette pareti laterali, disposte a contatto di detti elementi di accoppiamento (50).

- 11. Apparecchio elettronico (70), comprendente un assemblaggio di un dispositivo integrato a semiconduttori (40) secondo una qualsiasi delle rivendicazioni precedenti,

detto apparecchio elettronico (70) essendo scelto nel gruppo comprendente: un cellulare, un PDA, un notebook, un registratore vocale, un lettore audio con funzionalità di registratore vocale, una consolle per videogiochi, un idrofono.

12. Procedimento di fabbricazione di un dispositivo integrato a semiconduttori (40), comprendente:

predisporre una prima piastrina (die) (51) includente materiale semiconduttore;

predisporre una seconda piastrina (52), distinta rispetto alla prima piastrina (51), anch'essa includente materiale semiconduttore; ed

accoppiare dette prima (51) e seconda (52) piastrina ad una superficie interna (43a; 44a) di un contenitore (42) rivolta verso uno spazio interno (45) di detto contenitore (42),

caratterizzato dal fatto che detta fase di accoppiare comprende disporre detta seconda piastrina (52) affiancata a detta prima piastrina (51), al di sopra di detta superficie interna (43a; 44a); in cui detta fase di predisporre detta seconda piastrina (52) comprende conformare detta seconda piastrina (52) in modo da essere parzialmente sovrapposta a detta prima piastrina (51), al di sopra di detta superficie interna (43a; 44a), in seguito a detta fase di disporre.

- 13. Procedimento secondo la rivendicazione 12, in cui detta fase di conformare detta seconda piastrina (52) comprende formare detta seconda piastrina in modo tale che includa una prima porzione (54) atta ad essere accoppiata a detta superficie interna (43a; 44a), ed una seconda porzione (55), supportata da detta prima porzione (54), destinata ad essere sospesa a sbalzo a distanza da detta superficie interna (43a; 44a), al di sopra di detta prima piastrina (51).

- 14. Procedimento secondo la rivendicazione 13, in cui detta fase di conformare detta seconda piastrina (52) comprende:

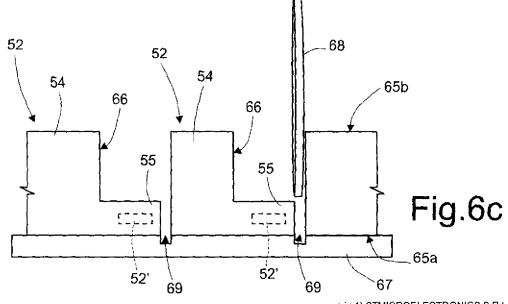

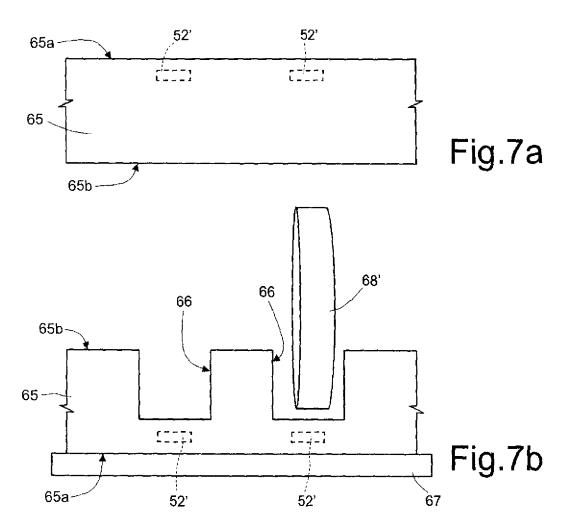

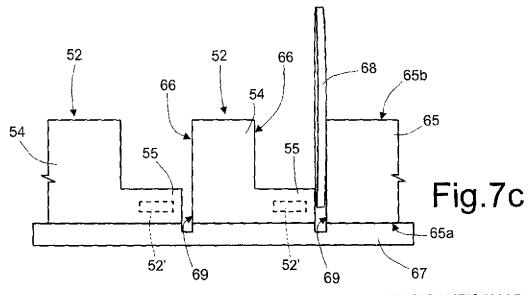

predisporre una fetta (65) di materiale semiconduttore, avente una faccia anteriore (65a) ed una faccia posteriore (65b);

formare circuiti elettronici ASIC (52') in corrispondenza di detta faccia anteriore (65a);

formare trincee (66) in detta fetta (65) a partire da detta faccia posteriore (65b);

tagliare detta fetta (65) in corrispondenza di una porzione terminale di dette trincee (66), in modo tale da ottenere una pluralità di piastrine, ciascuna atta a definire detta seconda piastrina (52).

15. Procedimento secondo la rivendicazione 14, in cui detta fase di formare trincee (66) comprende utilizzare un

primo utensile di taglio, avente una prima larghezza, in modo da scavare detta fetta (65) a partire da detta faccia posteriore (65b); ed in cui detta fase di tagliare detta fetta (65) comprende utilizzare un secondo utensile di taglio, avente una seconda larghezza, minore della prima.

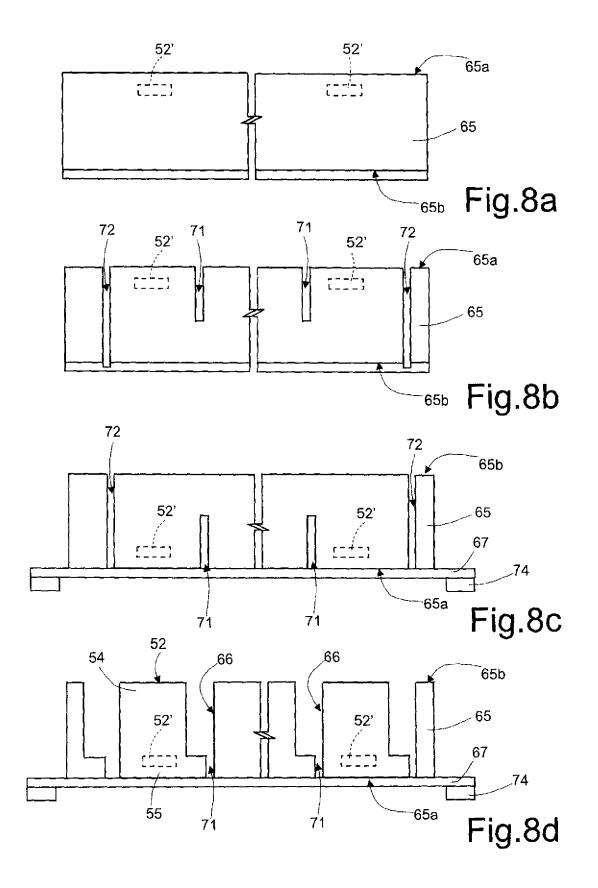

16. Procedimento secondo la rivendicazione 13, in cui detta fase di conformare detta seconda piastrina (52) comprende:

predisporre una fetta (65) di materiale semiconduttore, avente una faccia anteriore (65a) ed una faccia posteriore (65b);

formare circuiti elettronici ASIC (52') in corrispondenza di detta faccia anteriore (65a);

scavare intagli (71) a partire da detta faccia anteriore (65a) tra circuiti elettronici ASIC (52'), tra loro adiacenti;

tagliare detta fetta (65) a partire da detta faccia posteriore (65b) per formare trincee (66) che raggiungano rispettivi intagli (71), in modo tale da ottenere una pluralità di piastrine, ciascuna atta a definire detta seconda piastrina (52).

p.i.: 1) STMICROELECTRONICS S.R.L.

2) STMICROELECTRONICS N.V.

## Lorenzo NANNUCCI

.

#### CLAIMS

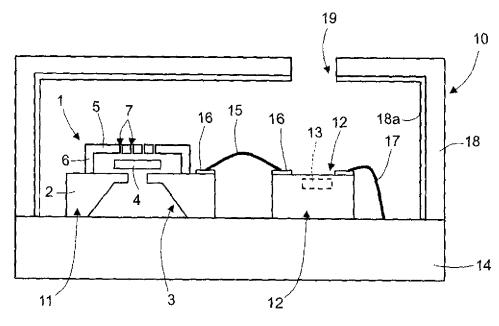

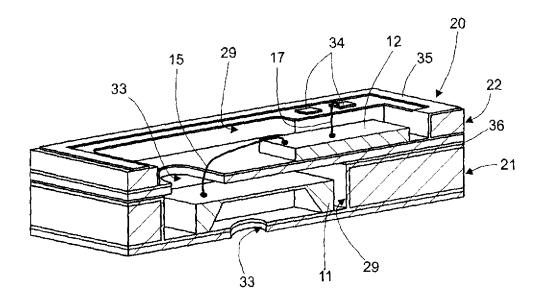

- 1. A semiconductor integrated device assembly (40), comprising:

- a package (42) defining an internal space (45); a first die (51) including semiconductor material; and a second die (52), distinct from the first die (51), also including semiconductor material;

- the first die (51) and second die (52) being coupled to an inner surface (43a; 44a) of the package (42) facing said internal space (45), characterized in that said second die (52) is shaped so as to

15

20

partially overlap said first die (51), above said inner surface (43a; 44a).

- 2. The assembly according to claim 1, wherein said first die (51) integrates a micromechanical detection structure (51'), and said second die (52) integrates an ASIC (52') functionally coupled to said micromechanical detection structure (51').

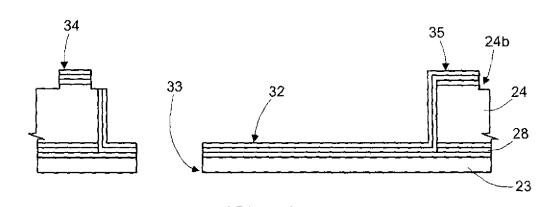

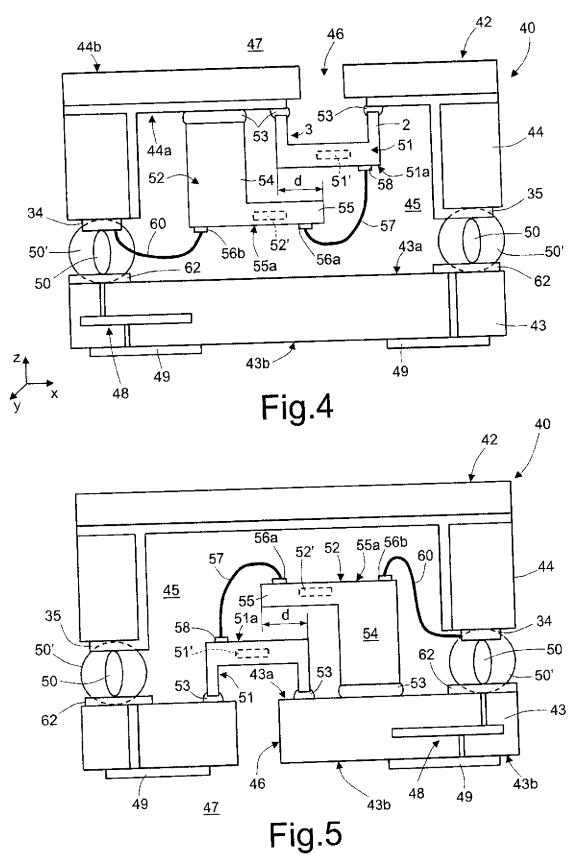

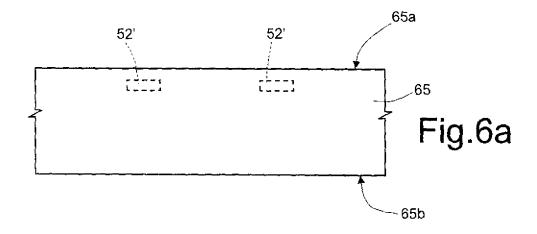

- 3. The assembly according to claim 1 or 2, wherein said second die (52) includes a first portion (54) directly coupled to said inner surface (43a; 44a), and a second portion (55), supported by said first portion (54) in such a way as to be suspended in cantilever fashion at a distance from said inner surface (43a; 44a), overlapping said first die (51) by an overlapping distance (d).

- 4. The assembly according to claim 3, wherein said first portion (54) and said second portion (55) are an integral part of one and the same body (65), including semiconductor material.

- 5. The assembly according to claim 3 or 4, wherein said second portion (55) integrates an ASIC (52'), and carries first connection pads (56a) on an outer surface (55a) thereof not

facing said first die (51); further including electrical-connection wires (57) between said first connection pads (56a) and respective connection pads (58) carried by a respective outer surface (51a) of said first die (51), facing said second die (52).

5

10

25

30

35

- 6. The assembly according to any one of claims 3-5, wherein said first portion (54) has a vertical dimension, along a direction (z) orthogonal to said inner surface (43a; 44a), greater than a corresponding vertical dimension of said first die (51).

- 7. The assembly according to any one of the preceding claims, wherein said package (42) comprises a base substrate (43) and a cap element (44), jointly defining said internal space (45); wherein said base substrate (43) has an outer surface (43b) facing the outside of said internal space (45) and carrying electrical contacts (49), and said cap element (44) has a cupshaped conformation; and wherein said inner surface (44a) is an inner wall of said cap element (44) facing said internal space (45).

- 8. The assembly according to any one of claims 1-6, wherein said package (42) comprises a base substrate (43) and a cap element (44), jointly defining said internal space (45); wherein said base substrate (43) has an outer surface (43b) facing the outside of said internal space (45) and carrying electrical contacts (49), and said cap element (44) has a cupshaped conformation; and wherein said inner surface (43a) is an inner wall of said base substrate (43) facing said internal space (45) and opposite to said outer surface (43b).

- 9. The assembly according to claim 7 or 8, wherein said package (42) has an access opening (46) through at least one between said base substrate (43) and said cap element (44), designed to set said internal space (45) in communication with

an external environment (47); and wherein said first die (51) integrates a MEMS acoustic transducer (1), including a membrane (2) suspended above a cavity (3) and facing a rigid plate (5); said first die (51) being arranged between said access opening (46) and said internal space (45), with said cavity (3) in fluid communication with said access opening (46).

- 10. The assembly according to any one of claims 7-9, wherein said cap element (44) is cup-shaped with side walls; said side walls being coupled to said base substrate (43) by means of coupling elements (50), which include at least partially conductive material; wherein electrical connections (60) are provided between said second die (52) and said base substrate (43) by means of said coupling elements (50) and contact regions (34) carried by said side walls, set in contact with said coupling elements (50).

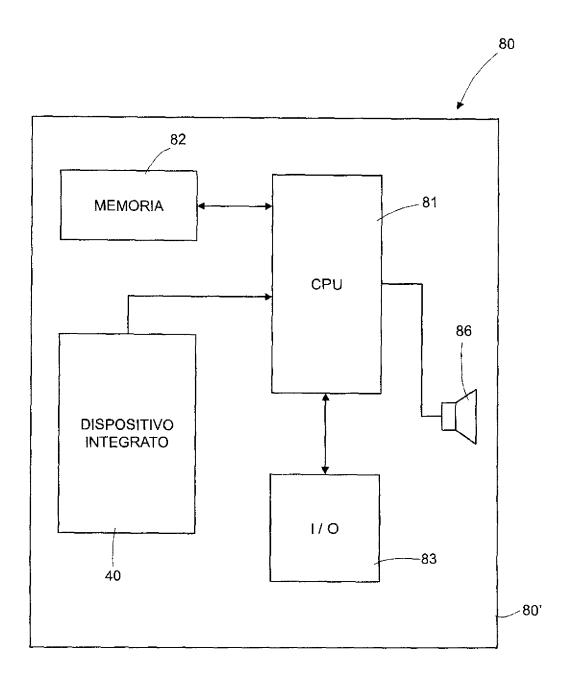

- 11. An electronic apparatus (70), comprising a semiconductor integrated device assembly (40) according to any one of the preceding claims, said electronic apparatus (70) being chosen in the group comprising: a cellphone, a PDA, a notebook, a voice recorder, an audio reader with voice recorder functions, a console for videogames, a hydrophone.

25

5

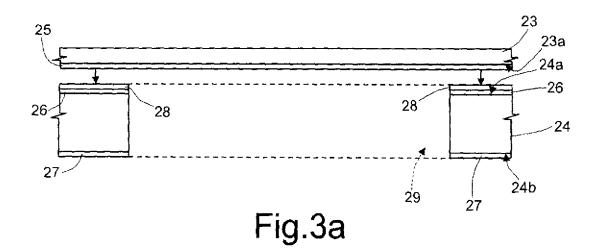

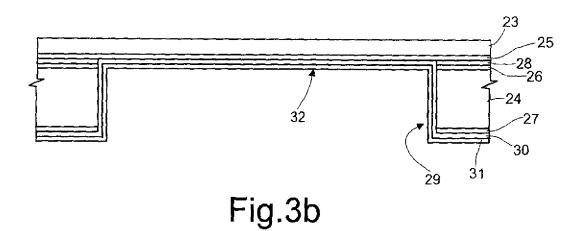

12. A process for manufacturing an integrated semiconductor device (40), comprising:

providing a first die (51) including semiconductor material; providing a second die (52), distinct from the first die (51),

- also including semiconductor material; and coupling said first die (51) and said second die (52) to an inner surface (43a; 44a) of a package (42) facing an internal space (45) of said package (42),

- characterized in that the step of coupling comprises arranging said second die (52) alongside said first die (51), on said inner surface (43a; 44a); wherein the step of providing said

second die (52) comprises shaping said second die (52) so as to partially overlap said first die (51), above said inner surface (43a; 44a), after said step of arranging said second die (52) alongside said first die (51).

5

10

- 13. The process according to claim 12, wherein said step of shaping said second die (52) comprises forming said second die so that it includes a first portion (54) designed to be coupled to said inner surface (43a; 44a), and a second portion (55), supported by said first portion (54), that is to be suspended in cantilever fashion at a distance from said inner surface (43a; 44a), above said first die (51).

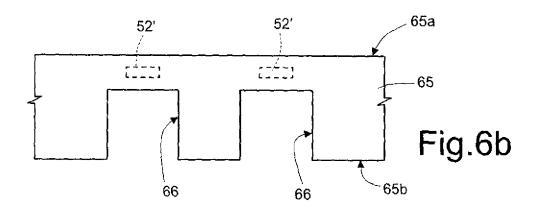

- 14. The process according to claim 13, wherein said step of shaping said second die (52) comprises: providing a wafer (65) of semiconductor material having a front face (65a) and a rear face (65b); forming ASIC electronic circuits (52') at said front face (65a);

- forming trenches (66) in said wafer (65) starting from said rear face (65b); and cutting said wafer (65) at a terminal portion of said trenches (66) in such a way as to obtain a plurality of dice, each designed to define said second die (52).

25

30

- 15. The process according to claim 14, wherein said step of forming trenches (66) comprises using a first cutting tool, having a first width, so as to dig said wafer (65) starting from said rear face (65b); and wherein said step of cutting said wafer (65) comprises using a second cutting tool, having a second width, smaller than the first width.

- 16. The process according to claim 13, wherein said step of shaping said second die (52) comprises:

- 35 providing a wafer (65) of semiconductor material, having a front face (65a) and a rear face (65b);

forming ASIC electronic circuits (52') at said front face (65a);

digging grooves (71) starting from said front face (65a) between mutually adjacent ASIC electronic circuits (52'); and cutting said wafer (65) starting from said rear face (65b) to form trenches (66) reaching respective grooves (71) in such a way as to obtain a plurality of dice, each designed to define said second die (52).

5

Fig.1

Fig.2

Fig.3c

p.i.: 1) STMICROELECTRONICS S.R.L.

2) STMICROELECTRONICS INTERNATIONAL N.V.

Fig.9