(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(43) International Publication Date

22 April 2010 (22.04.2010)

(10) International Publication Number

WO 2010/045021 A2

(51) International Patent Classification:

H01L 21/762 (2006.01)

(21) International Application Number:

PCT/US2009/058832

(22) International Filing Date:

29 September 2009 (29.09.2009)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/106,076 16 October 2008 (16.10.2008) US

12/437,256 7 May 2009 (07.05.2009) US

(71) Applicant (for all designated States except US): APPLIED MATERIALS, INC. [US/US]; P.O. Box 450A, Santa Clara, California 95052 (US).

(72) Inventors; and

(75) Inventors/Applicants (for US only): KWON, Young Soo [KR/KR]; #903-1603 Hanra Vivaldi Apt., Sangha Dong, Kiheung gu, Younginsi, Kyunggi 446-581 (KR). JANG,

Bi [KR/KR]; 115 Dong-403Ho, LG APT, Shingbong-Don, Yongin-City, Kyunggi-do 448-533 (KR). WANG, Anchuan [CN/US]; 7250 Blue Hill Dr., Apt.107, San Jose, California 95129 (US). LEE, Young, S. [US/US]; 1714 Via Cortina, San Jose, California 95120 (US). BALSEANU, Mihaela [RO/US]; 1639 Belleville Way Apt. T, Sunnyvale, California 94087 (US). XIA, Li-Qun [US/US]; 10221 Western Drive, Cupertino, California 95014 (US). JEON, Jin Ho [KR/US]; 1824 Barossa Drive, San Ramon, California 94582 (US).

(74) Agents: BERNARD, Eugene et al.; Townsend and Townsend and Crew LLP, 1400 Wewatta, Suite 600, Denver, Colorado 80202 (US).

(81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI

[Continued on next page]

(54) Title: GAPFILL IMPROVEMENT WITH LOW ETCH RATE DIELECTRIC LINERS

(57) Abstract: A method of filling a trench is described and includes depositing a dielectric liner with a high ratio of silicon oxide to dielectric liner etch rate in fluorine-containing etch chemistries. Silicon oxide is deposited within the trench and etched to reopen or widen a gap near the top of the trench. The dielectric liner protects the underlying substrate during the etch process so the gap can be made wider. Silicon oxide is deposited within the trench again to substantially fill the trench.

FIG. 1

NO, NZ, OM, PE, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

**(84) Designated States** (*unless otherwise indicated, for every kind of regional protection available*): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE,

ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

**Published:**

— without international search report and to be republished upon receipt of that report (Rule 48.2(g))

## GAPFILL IMPROVEMENT WITH LOW ETCH RATE DIELECTRIC LINERS

### CROSS-REFERENCES TO RELATED APPLICATIONS

5 [0001] This application claims the benefit of U.S. Provisional Application No. 61/106,076 by Kwon et al, filed October 16, 2008 and titled "GAPFILL IMPROVEMENT WITH HIGH LOW ETCH RATE DIELECTRIC LINERS". This application is related to U.S. Pat. App. Ser. No. 11/765,257 and U.S. Pat. Prov. App. Ser. No. 61/042,638, both titled "BORON NITRIDE AND BORON NITRIDE-DERIVED MATERIALS DEPOSITION METHOD."

10 The entire contents of all three applications are herein incorporated by reference for all purposes.

### FIELD

[0002] This application relates to manufacturing technology solutions involving equipment, processes, and materials used in the deposition, patterning, and treatment of thin-films and 15 coatings, with representative examples including (but not limited to) applications involving: semiconductor and dielectric materials and devices, silicon-based wafers and flat panel displays (such as TFTs).

### BACKGROUND

[0003] Increasing the density of integrated circuits can increase speed and enable new 20 applications. The increased density can increase undesirable electrical interactions between adjacent circuit elements and conducting lines. Unwanted interactions are typically prevented by providing trenches that are filled with electrically insulating material to isolate the elements both physically and electrically. As circuit densities increase, however, the widths of these trenches decrease, increasing their aspect ratios and making it progressively 25 more difficult to fill the trenches without leaving voids. A trench which is not completely filled is undesirable since the degree of isolation may be compromised, thus limiting the maximum operational frequency or otherwise adversely affecting operation of the integrated circuit.

[0004] Common techniques that are used in such gapfill applications are chemical-vapor deposition ("CVD") techniques. Conventional thermal CVD processes supply reactive gases to the substrate surface where heat-induced chemical reactions take place to produce a desired film. Plasma-enhanced CVD ("PECVD") techniques promote excitation and/or 5 dissociation of the reactant gases by the application of radio-frequency ("RF") energy to a reaction zone near the substrate surface creating a plasma. The high reactivity of the species in the plasma reduces the energy required for a chemical reaction to take place, and thus lowers the temperature required for such CVD processes when compared with conventional thermal CVD processes. These advantages may be further exploited by high-density-plasma 10 ("HDP") CVD techniques, in which a dense plasma is formed at low vacuum pressures so that ionized reactants form a greater percentage of the total reactant population. While each of these techniques falls broadly under the umbrella of "CVD techniques," each of them has characteristic properties that make them more or less suitable for certain specific applications.

[0005] In some instances where trenches have a large aspect ratio and narrow width, 15 trenches have been filled with each of these CVD techniques using a "dep/etch/dep" process involving sequentially depositing material, etching some of it back, and depositing additional material. The etching step acts to reshape the partially filled trench, opening it so that more material can be deposited before it closes up and leaves an interior void. The etching step can penetrate through deposited material and damage underlying layers especially near the tops of 20 trenches or vias. In the case of shallow trench isolation (STI) the underlying semiconductor and/or protective silicon nitride barrier layer may be damaged which can cause device instability. Device reliability is generally at risk when the etching step is allowed to remove too much material.

#### BRIEF SUMMARY

[0006] A method of filling a trench is described and includes depositing a dielectric liner 25 with a high ratio of silicon oxide to dielectric liner etch rate in fluorine-containing etch chemistries. Silicon oxide is deposited within the trench and etched to reopen or widen a gap near the top of the trench. The dielectric liner protects the underlying substrate during the etch process so the gap can be made wider. Silicon oxide is deposited within the trench again 30 to substantially fill the trench.

[0007] In one embodiment, a method of depositing dielectric material in a trench in a semiconductor substrate includes forming a liner layer containing boron nitride over bottom

and sidewall surfaces of the trench and depositing the dielectric material containing silicon oxide over the liner layer such that the dielectric material at least partially fills the trench. The method further includes etching a portion of the deposited dielectric material with an etchant, removing the dielectric material at a higher etch rate than the liner layer.

5 [0008] In another embodiment, a method of removing a void formed in a dielectric material that fills a trench in a semiconductor substrate includes etching a top portion of the dielectric material to expose an opening in the void, in which the etching also exposes a portion of a liner layer comprising boron nitride that was covered by the dielectric material. The method further includes depositing additional dielectric material into the exposed void to remove the

10 void by filling it with the additional dielectric material.

15 [0009] In yet another embodiment, a method of depositing a film to fill a gap in a surface of a substrate includes forming a dielectric liner on the surface of the substrate, in which a silicon oxide to dielectric liner etch ratio is greater than about 50. The method further includes depositing a first layer of dielectric on the dielectric liner, etching the surface of the substrate and depositing a second layer of dielectric to substantially fill the gap.

20 [0010] Additional embodiments and features are set forth in part in the description that follows, and in part will become apparent to those skilled in the art upon examination of the specification or may be learned by the practice of the disclosed embodiments. The features and advantages of the disclosed embodiments may be realized and attained by means of the instrumentalities, combinations, and methods described in the specification.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0011] A further understanding of the nature and advantages of the disclosed embodiments may be realized by reference to the remaining portions of the specification and the drawings.

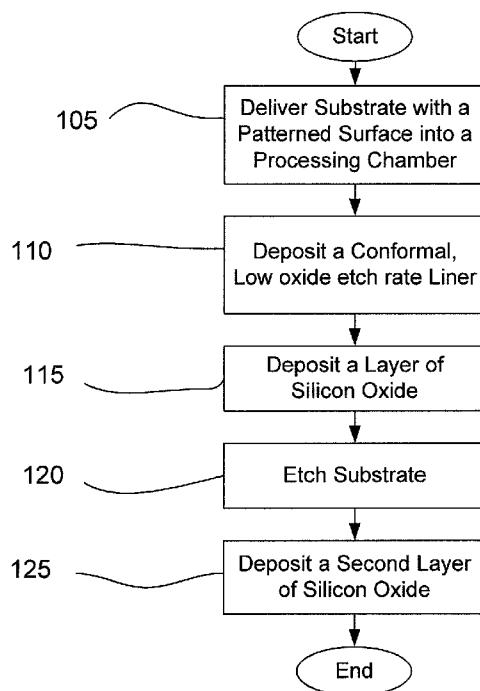

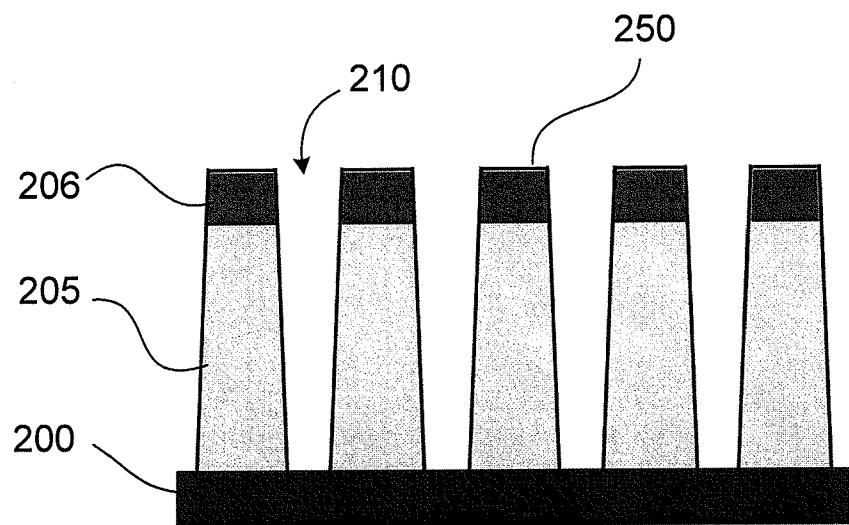

25 [0012] FIG. 1 is a flow chart of a silicon oxide gapfill deposition process according to disclosed embodiments.

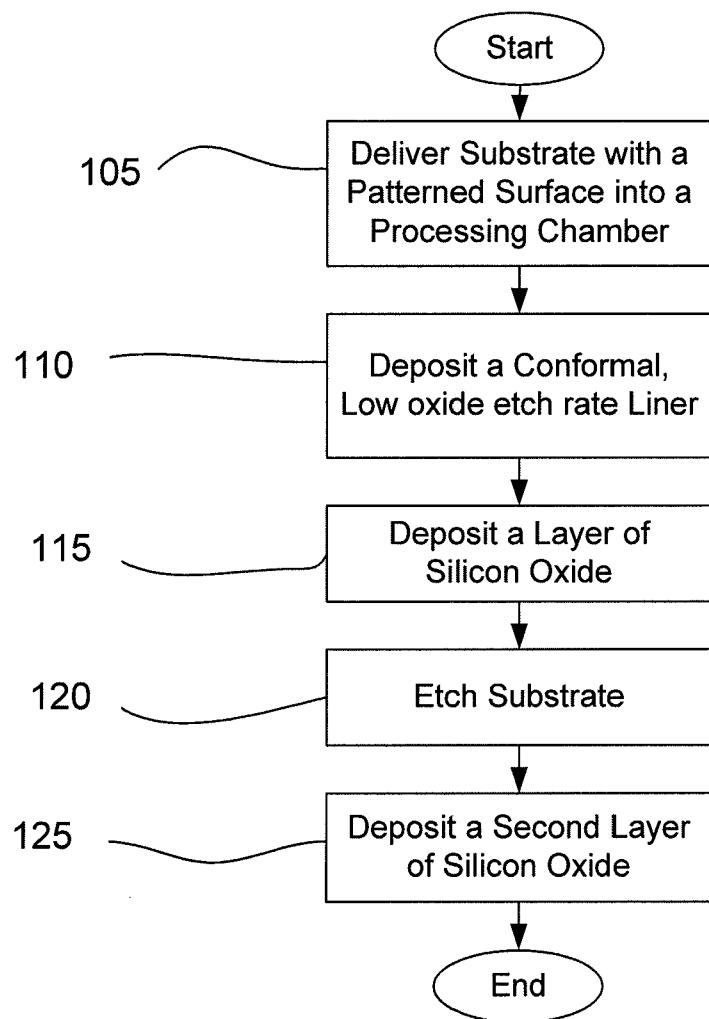

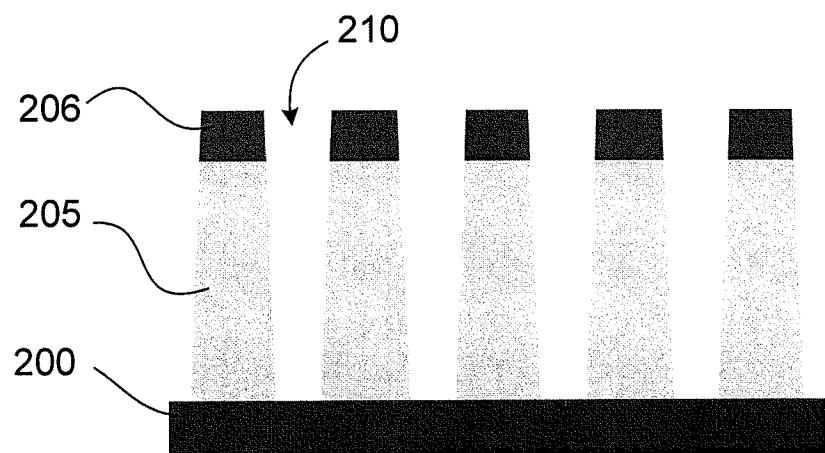

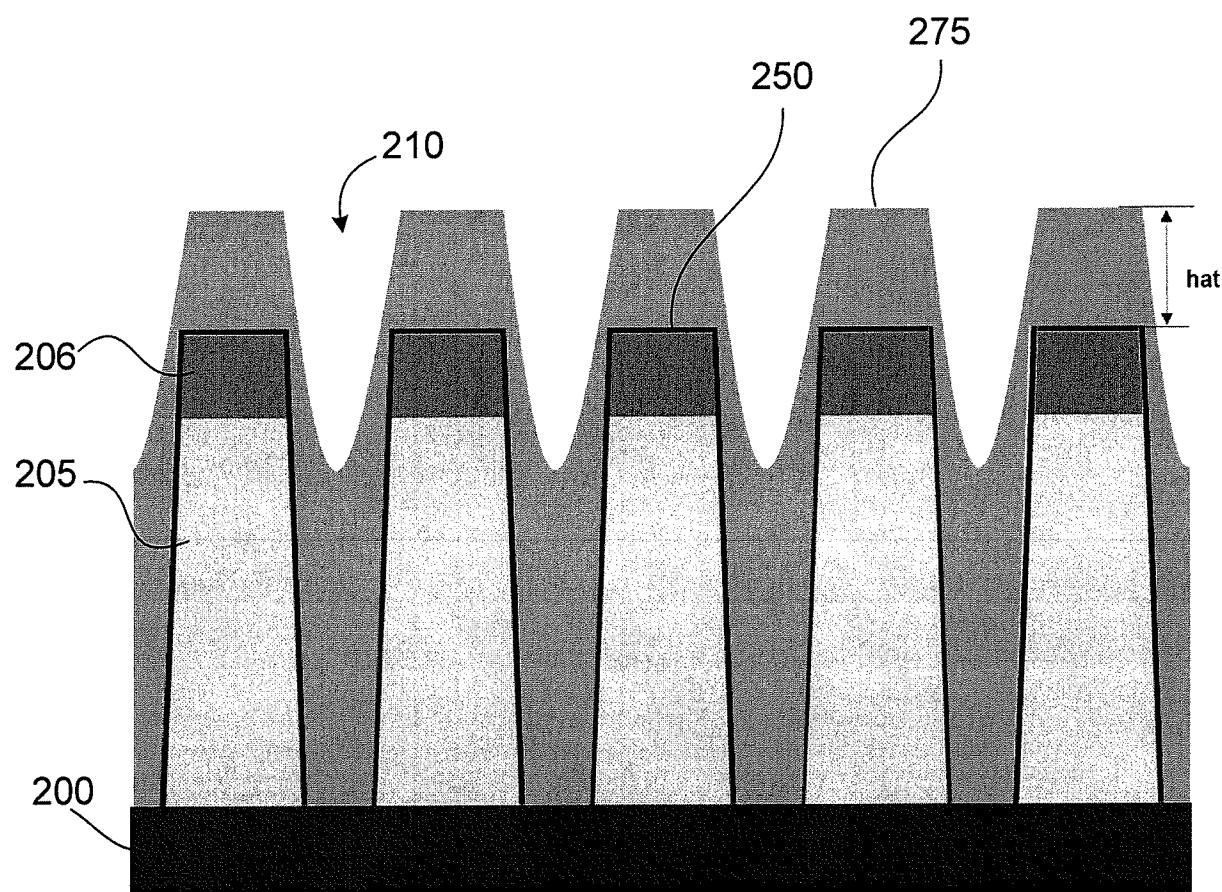

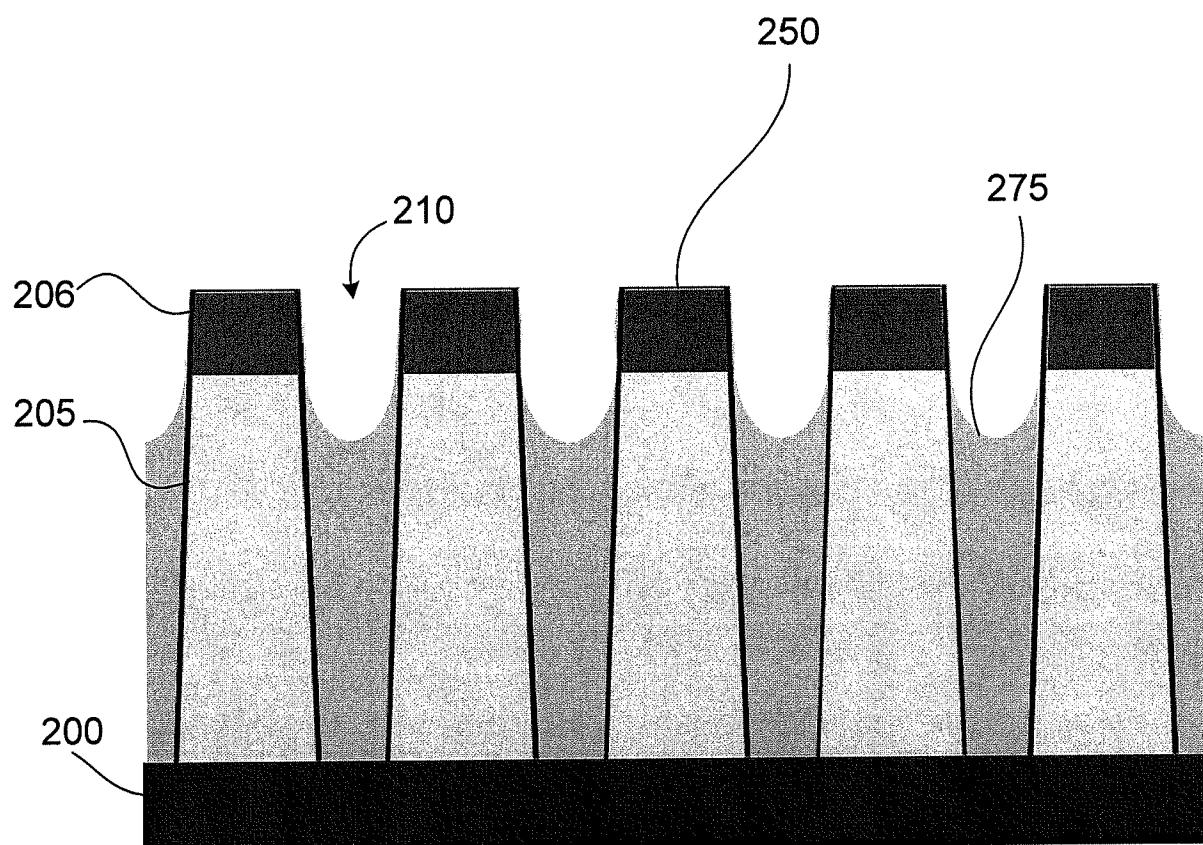

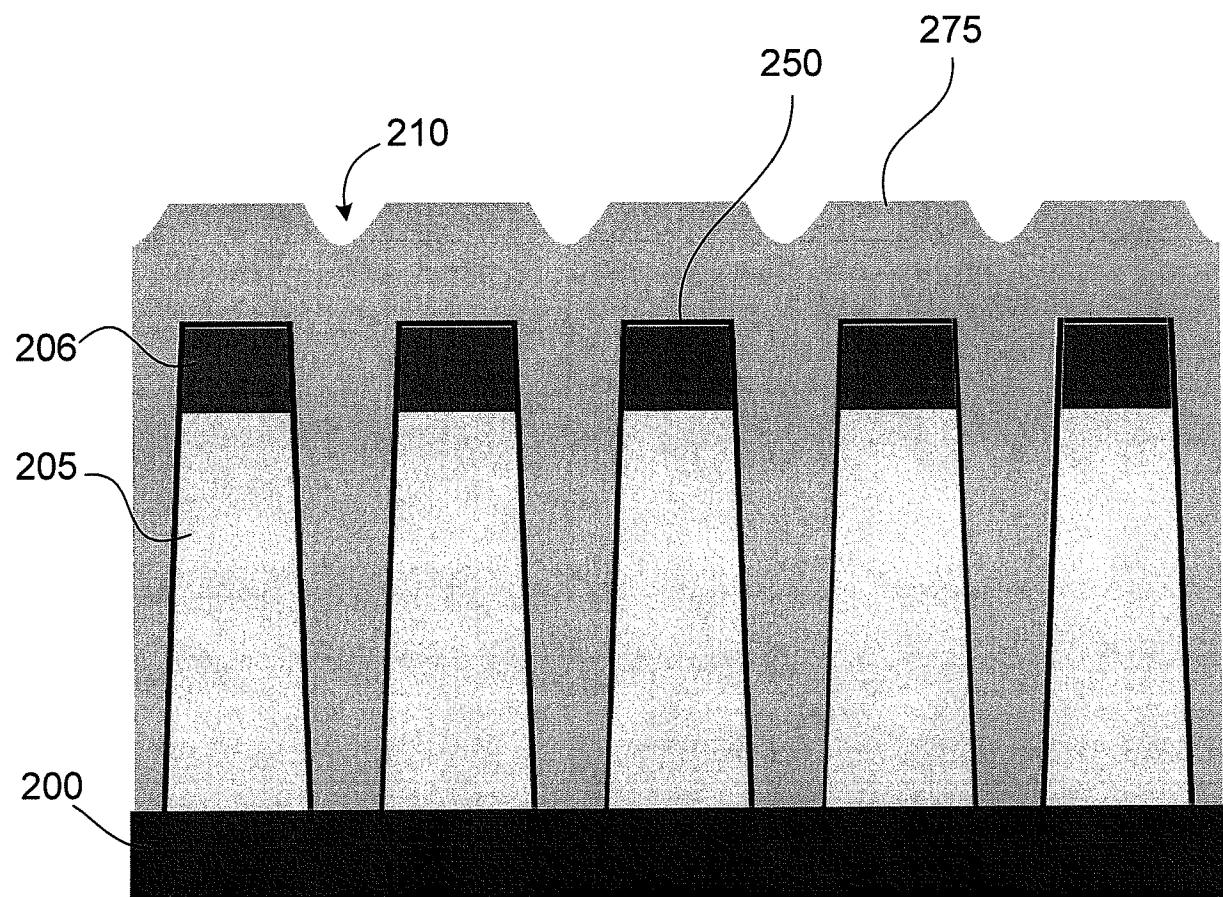

[0013] FIG. 2A-E are cross-sectional views of features on a substrate during a deposition process according to disclosed embodiments.

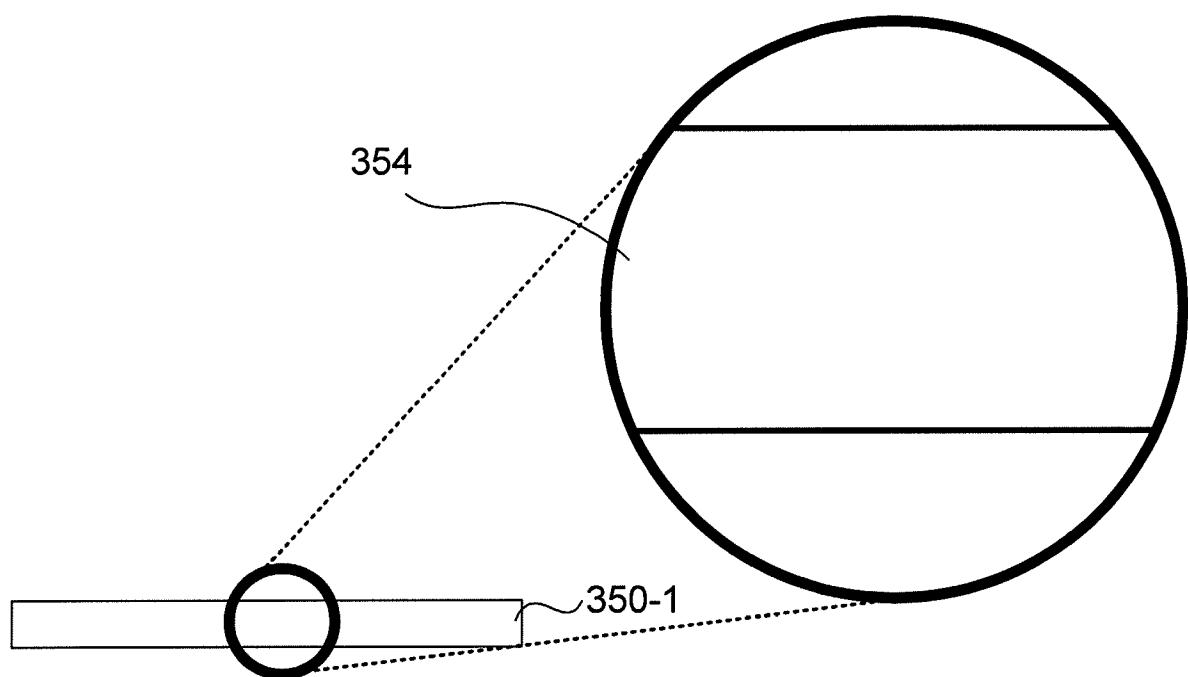

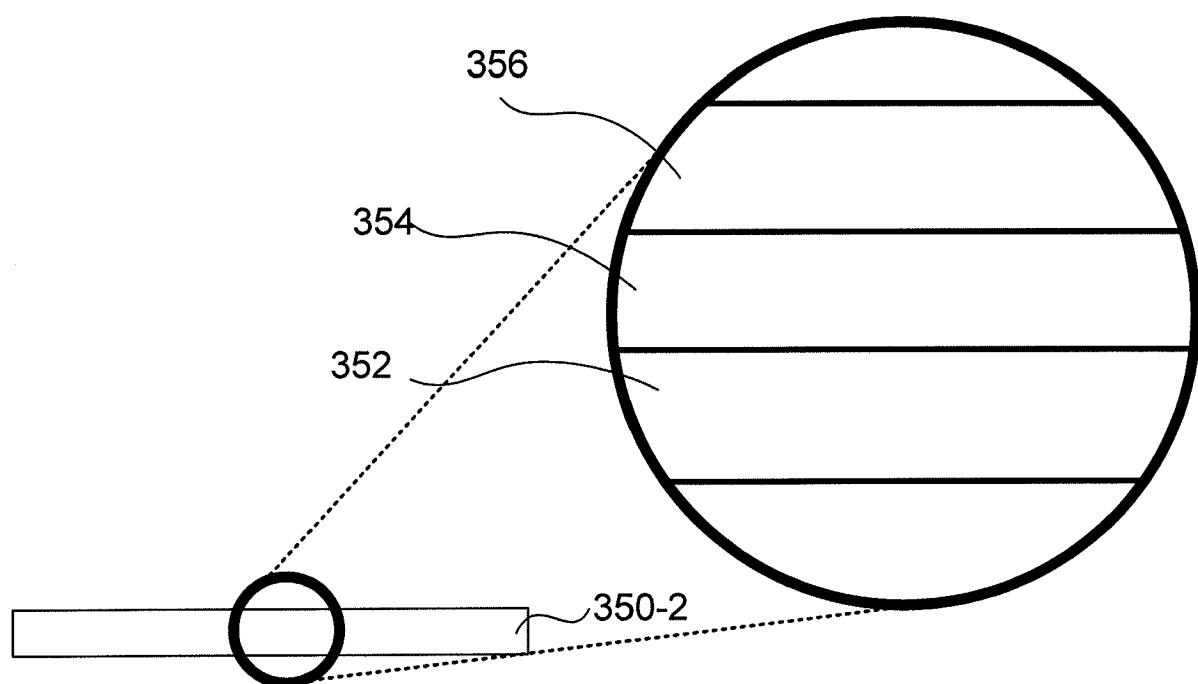

[0014] FIG. 3A-B are cross-sectional views of a barrier layer according to disclosed embodiments.

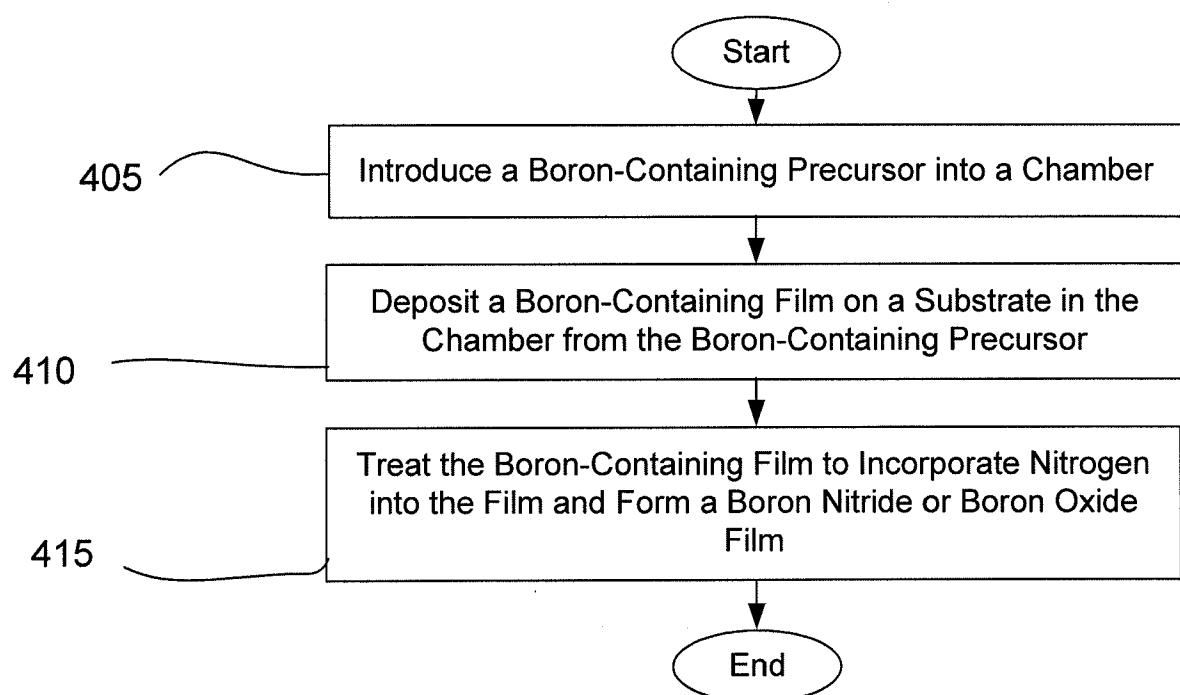

30 [0015] FIG. 4 is a flow chart of a method of forming boron nitride and boron oxide films.

[0016] In the appended figures, similar components and/or features may have the same reference label. Further, various components of the same type may be distinguished by following the reference label by a dash and a second label that distinguishes among the similar components. If only the first reference label is used in the specification, the 5 description is applicable to any one of the similar components having the same first reference label irrespective of the second reference label.

#### DETAILED DESCRIPTION

[0017] A method of filling a trench is described and includes depositing a dielectric liner 10 with a high ratio of silicon oxide to dielectric liner etch rate in fluorine-containing etch chemistries. Silicon oxide is deposited within the trench and etched to reopen or widen a gap near the top of the trench. The dielectric liner protects the underlying substrate during the etch process so the gap can be made wider. Silicon oxide is deposited within the trench again to fill the trench.

[0018] Embodiments of the invention are directed to methods of depositing a film to fill a trench in a surface of a substrate. For trenches of a given width, embodiments use a multistep deposition and etching process in which the etching process occurs between deposition 15 processes to widen or reopen a gap within the film. A dielectric liner layer having a low HF etch rate relative to silicon oxide is deposited conformally on a trench in the surface of the substrate and followed by a silicon oxide dep/etch/dep sequence which represents the order of 20 the silicon oxide processing steps in the sequence. The improved protection of surface features provided by the dielectric liner layer enables even higher aspect ratio trenches to be filled without voids before damage is done to the walls of the trench which can ultimately impact device operation. In particular, the embodiments of the invention may be used for 25 filling trenches below or about 45 nm wide and are suitable for a variety of different gapfill applications, e.g. shallow-trench-isolation.

[0019] In order to better understand and appreciate the invention, reference is now made to FIG. 1 and FIG. 2 which are a flow chart of a silicon oxide gapfill deposition process and cross-sectional views according to disclosed embodiments. The process begins when a 30 substrate 200 with a trench 210 on the surface is transferred into a processing chamber (Step 105 and FIG. 2A). The trench may be created by the presence of two walls of homogeneous material or, as shown, may be formed from walls of different materials 205, 206. In some

cases the walls are formed in the support substrate material itself. A thin conformal liner layer of a material, such as boron nitride, with a relatively low etch rate is deposited on the substrate (Step 110 resulting in FIG. 2B). The thin conformal liner 250 is thin compared to the width of the trench 210. A material with a relatively low etch rate, as used herein, 5 describes a material which etches more slowly than common silicon nitride in a fluorine-based etch process.

**[0020]** Following the deposition of the liner 250, the process of filling the trench 210 begins with depositing a layer of silicon oxide (Step 115 resulting in FIG. 2C). The layer of silicon oxide 275 fills a portion of the trench 210. The thickness of the layer of silicon oxide 10 275 may grow more quickly near the top of the trench 210 than the sides or the bottom. This can result in a narrowed gap above the trench 210 or even a closed void (not shown) in the trench 210. A closed void which is left in the trench and incorporated into a completed device or integrated circuit may compromise device performance or affect yield.

**[0021]** The deposition process is stopped and the substrate is etched back (Step 120 15 resulting in FIG. 2D) in order to reduce the formation of voids in the trench 210 during a subsequent deposition of material. In embodiments, the liner is boron nitride which exhibits a lower etch rate than silicon nitride for a same or similar fluorine-based etch process. Silicon nitride is a common alternative liner material. The lower etch rate of liners according to disclosed embodiments may allow the etch process to continue longer so the trench 210 is 20 more accessible. Alternatively or in combination, the lower etch rate of a liner allows the etch process to be made more aggressive at removing both liner and silicon oxide. Such a modification may result from a change in etch plasma parameters, a change in fluorine chemistry or other etch process parameters known to those of skill in the art. A longer and/or more aggressive etch may remove relatively more silicon oxide without damaging the liner or 25 top sidewall material 205, 206 to the point where performance of a device is compromised. The etch process may involve fluorine-containing gases with or without a plasma. The etch may remove more material from high points of the silicon oxide layer 275 and less from the bottom of the trench 210 to improve the gapfill of the next step. A second deposition of silicon oxide onto the etched substrate then fills the trench 210 between the two sidewalls 30 (Step 125 resulting in FIG. 2E).

**[0022]** Though the exemplary process represented by FIGS. 1 and 2 shows a process involving two depositions surrounding one etch (referred to succinctly as a "dep/etch/dep"),

the process may involve any number of etch processes with a deposition preceding and following each etch (e.g. a dep/etch/dep/etch/dep). A neighboring pair of deposition and etch processes may not border one another. In practice, there may be a gap between the pair of processes and, in some cases, the wafer may be removed from one processing chamber and transferred to another between the two processes.

5 [0023] A single layer liner 350-1 of relatively low etch rate material, such as boron nitride, is shown in FIG. 3A in cross-section. A magnified cross-sectional view of the liner is also shown indicating one layer of material 354. The chemical composition of the single layer liner is different from a typical liner material and the associated etch rate is lower. When 10 introduced into a process flow there is some chance that material (e.g. boron) may leach out of the single layer liner and detrimentally affect device performance or the process flow. Silicon nitride is known to be a capable barrier to diffusion of material either leaching into or out of the underlying portion of the substrate. Liners according to disclosed embodiments 15 may provide similar utility as a barrier layer in many applications. In other applications which might be sensitive to boron diffusion, one or more silicon nitride liners may be integrated into the process flow of FIG. 1 in order to avoid or suppress the diffusion of material from these new liners into the region above or below the liner.

10 [0024] In order to reduce diffusion into the region below the liner, a layer of silicon nitride may be deposited between Step 105 and Step 110. A step of depositing a layer of silicon 20 nitride may also be inserted between Step 110 and Step 115 to reduce diffusion of chemicals from the new liner material into the region above the liner. These inserted layers of silicon nitride may be generally referred to herein as barrier layers or diffusion barrier layers and may be made of other materials than silicon nitride. Thus in embodiments, composite layers including bilayers and trilayers may be formed for use as liners before silicon oxide 25 deposition. At least one of the layers in a composite layer may exhibit a relatively low etch rate relative to prior art silicon nitride layers according to embodiments of the invention.

FIG. 3B is a cross-sectional view of trilayer liner 350-2. A magnified cross-sectional view of the liner is also shown indicating three layers of material including a bottom layer of silicon nitride 352, boron nitride 354 and a top layer of silicon nitride 356.

30 [0025] Referring now to the dep/etch/dep sequence for filling a trench, the two deposition techniques of a given sequence may be the same deposition techniques or recipes. However, they may be distinct from one another. Representative oxide deposition methods are CVD,

HDP-CVD, SACVD, eHARP, HTUSG and O<sub>3</sub>-TEOS. Flowable techniques such as spin-on glass (SOG) may have improved gapfill capabilities but may still benefit from process sequences according to disclosed embodiments depending on the viscosity and other SOG process parameters.

5 [0026] Methods according to disclosed embodiments provide utility for a wide variety of fluorine-containing dry etch and wet etch processes. The etch ratios for two representative fluorine-containing dry-etch processes are shown in Table I. The ratios of the oxide etch rate to silicon nitride etch rate using the two fluorine etch processes are shown in one column. Similarly, silicon oxide to boron nitride etch rate ratios for the two fluorine etches are shown

10 in the last column. Since silicon oxide etches so much more quickly than boron nitride in an oxide etch, a portion of a liner made from boron nitride can remain when at least a portion of a silicon nitride liner of similar thickness would have been removed by the same oxide etch process. These two fluorine etch processes involve two precursors, NH<sub>3</sub> and NF<sub>3</sub>, and "Etch 1" involves a higher NF<sub>3</sub> concentration than "Etch 2" in order to increase the etch rate of

15 silicon oxide.

**Table I: Etch Ratios Relative to Silicon Oxide**

|        | Silicon Nitride | Boron Nitride |

|--------|-----------------|---------------|

| Etch 1 | 19.9            | 147           |

| Etch 2 | 39.2            | 126           |

20 [0027] The dielectric liners disclosed may be single layers of a relatively low etch rate material or multilayers combining silicon nitride with such single layers. Dielectric liners may be less than 10 nm, less than 5 nm, less than 2 nm or less than 1 nm thick in different

25 embodiments. These thicknesses include the thickness(es) of any barrier layer(s) included in composite liner layers. Composite liner layers are made from at least or about 25%, at least or about 50% or at least or about 75% low etch rate material in different embodiments.

[0028] In order to facilitate a comparison between silicon oxide, silicon nitride and

25 dielectric liners according to embodiments, a reference etch is chosen to be a room temperature 1% HF aqueous solution. Silicon oxide to dielectric liner etch ratios, unless otherwise noted, will be given here with reference to this reference etch. The ratio of the silicon oxide etch rate to a silicon nitride liner etch rate may be between 1 and 50. With regard to the present invention, the ratio of silicon oxide etch rate to dielectric liner etch rate

may be greater than or about 50, greater than or about 75 or greater than or about 100 in different embodiments. With regard to a composite liner layer, the ratio of etch rates is calculated using the etch rate of the relatively low etch rate layer within the composite liner layer.

5 [0029] Relatively low etch rate materials, according to disclosed embodiments, are not limited to boron nitride layers. Included in the disclosed embodiments are other materials which provide similar utility. Similar deposition methods may be used to form liners comprising boron and/or carbon and displaying similar silicon oxide to dielectric liner etch ratios. Liners may have an atomic concentration of boron which is greater than or about 5%,

10 greater than or about 10% or greater than or about 20% in different embodiments. Alternatively or in combination with boron concentrations, liners may have an atomic concentration of carbon which is greater than or about 5%, greater than or about 10% or greater than or about 20% in different embodiments. Higher boron and/or carbon concentrations correlate with a lower HF etch rate. Exemplary films are boron nitride (BN),

15 boron oxide (B<sub>2</sub>O<sub>3</sub>), silicon carbide (SiC), boron carbide(BC), carbon nitride (CN), silicon boron nitride (SiBN), boron silicon oxide (BSi<sub>x</sub>O<sub>y</sub>), phosphorus boron nitride (PBN), silicon carbon nitride (SiCN) and boron carbon silicon nitride (BCSiN) films.

20 [0030] An exemplary method of depositing a boron-containing liner layer will be described while referring to the flow chart of Figure 4. The example will focus on methods of

25 depositing boron nitride and boron oxide. As shown in step 405, a boron-containing precursor is introduced into a chamber. In step 410, a boron-containing film is deposited on a substrate in the chamber from the boron-containing precursor. Then, in step 415, the boron-containing film is treated to modify the film composition (e.g., to increase the nitrogen or oxygen content of the film). Treating the boron-containing film comprises exposing the

25 boron-containing film to a nitrogen-containing or oxygen-containing precursor.

30 [0031] Returning to step 405, the chamber into which the boron-containing precursor is introduced may be any chemical vapor deposition chamber or a plasma-enhanced chemical vapor deposition chamber. Examples of chambers that may be used include the PRODUCER® SE and PRODUCER® GT PECVD chambers, both of which are available

herein are provided for a 300 mm PRODUCER® SE chamber with two isolated processing

regions, with one substrate per processing region. Thus, the flow rates experienced per each substrate processing region and substrate are half of the flow rates into the chamber.

[0032] The substrate on which the boron-containing film is deposited may be a silicon, silicon-containing, or glass substrate. The substrate may be a bare substrate or have one or 5 more layers of material deposited thereon and/or features formed therein.

[0033] The boron-containing precursor may be diborane ( $B_2H_6$ ), borazine ( $B_3N_3H_6$ ), or an alkyl-substituted derivative of borazine. The boron-containing precursor may be introduced into the chamber at a flow rate between about 5 sccm and about 50 slm, such as between about 10 sccm and about 1 slm. Typically, the boron-containing precursor is introduced into 10 the chamber with nitrogen ( $N_2$ ), hydrogen ( $H_2$ ), argon (Ar) or a combination thereof as a dilution gas. The dilution gas may be introduced into the chamber at a flow rate between about 5 sccm and about 50 slm, such as between about 1 slm and about 10 slm.

[0034] In embodiments, a boron-containing film may be formed in Step 415 of Figure 4 by introducing a nitrogen-containing compound and/or an oxygen-containing film. Examples of 15 nitrogen-containing compounds that may be used include ammonia ( $NH_3$ ), hydrazine ( $N_2H_4$ ). Examples of oxygen-containing compounds include oxygen ( $O_2$ ), nitric oxide (NO), nitrous oxide ( $N_2O$ ), carbon dioxide ( $CO_2$ ), and water ( $H_2O$ ). Other compounds may be used as well including silicon-containing compounds, carbon-containing compounds, phosphorous-containing compounds etc. Combinations of compounds may also be used. In some 20 instances these compounds may be present while the boron-containing precursor is in the chamber (not shown in Figure 4). Alternatively, the compound may be introduced into the chamber before or after the introduction of the boron-containing precursor. Examples of silicon-containing compounds that may be used include silane, trisilylamine (TSA), trimethylsilane (TMS), and silazanes, such as hexamethylcyclotrisilazane (HMCTZ). 25 Examples of carbon-containing compounds that may be used include hydrocarbon compounds having the general formula  $C_xH_y$ , such as alkanes, alkenes, and alkynes. An example of a phosphorous-containing compound that may be used is phosphine ( $PH_3$ ).

[0035] The boron-containing film may be deposited on the substrate in the chamber from the boron-containing precursor in the presence or absence of a plasma in the chamber.

30 [0036] For deposition of the boron-containing film in the absence of a plasma in the chamber, the temperature of a substrate support in the chamber may be set to between about 100°C and about 1000°C, e.g., between about 300°C and about 500°C, and the pressure in the

chamber may be between about 10 mTorr and about 760 Torr, e.g., between about 2 Torr and about 10 Torr, during the deposition. A combination of boron-containing, nitrogen-containing, carbon-containing, oxygen-containing and silicon-containing compounds may be introduced in the chamber at the same time at a flow rate between about 5 sccm and about 50 slm, such as between 10 sccm and about 1 slm.

[0037] For deposition of the boron-containing film in the presence of a plasma in the chamber, the temperature of a substrate support in the chamber may be set to between about 100°C and about 1000°C, e.g., between about 300°C and about 500°C, and the pressure in the chamber may be between about 10 mTorr and about 760 Torr, e.g., between about 2 Torr and about 10 Torr, during the deposition. The plasma may be provided by RF power delivered to a showerhead electrode and/or a substrate support electrode of the chamber. The RF power may be provided at a power level between about 2 W and about 5000 W, such as between about 30 W and about 1000 W, at a single low frequency of between about 100 kHz up to about 1 MHz, e.g., about 300 kHz to about 400 kHz, or at a power level between about 2 W and about 5000 W, such as between about 30 W and about 1000 W, at a single high frequency of greater than about 1 MHz, such as greater than about 1 MHz up to about 60 MHz, e.g., 13.6 MHz. Alternatively, the RF power may be provided at a mixed frequency including a first frequency between about 100 kHz up to about 1 MHz, e.g., about 300 kHz to about 400 kHz at a power level between about 2 W and about 5000 W, such as between about 30 W and about 1000 W, and a second frequency of greater than about 1 MHz, such as greater than about 1 MHz up to about 60 MHz, e.g., 13.6 MHz, at a power level between about 2 W and about 5000 W, such as between about 30 W and about 1000 W.

[0038] Returning to Figure 4, after the boron-containing film is deposited, the boron-containing film is treated to modify its composition by incorporating nitrogen or oxygen into the film and form a boron nitride or boron oxide film. The boron nitride or boron oxide film may have a thickness of between about 2 Å and about 5000 Å. The treatment is selected from the group consisting of a plasma process, an ultraviolet (UV) cure process, a thermal anneal process, and combinations thereof, and comprises exposing the boron-containing film to a nitrogen-containing precursor to incorporate nitrogen into the film and form the boron nitride film. The nitrogen-containing precursor may be nitrogen gas (N<sub>2</sub>), ammonia (NH<sub>3</sub>), or hydrazine (N<sub>2</sub>H<sub>4</sub>), for example. The nitrogen-containing precursor may be diluted with a dilution gas such as argon, helium, hydrogen, or xenon. Exposing the boron-containing film to a oxygen-containing precursor allows incorporation of oxygen in the film and formation of

a boron oxide film. The oxygen-containing precursor may be oxygen gas (O<sub>2</sub>), nitrous oxide (N<sub>2</sub>O) or carbon dioxide (CO<sub>2</sub>).

**[0039]** In embodiments in which the treatment comprises a plasma process, the plasma process may be performed in the same chamber in which the boron-containing film was

5 deposited or a different chamber. The plasma may be provided by RF power delivered to a showerhead electrode and/or a substrate support electrode of the chamber. The RF power may be provided at a power level between about 2 W and about 5000 W, such as between about 30 W and about 1000 W, at a single low frequency of between about 100 kHz up to about 1 MHz, e.g., about 300 kHz to about 400 kHz, or at a power level between about 2 W

10 and about 5000 W, such as between about 30 W and about 1000 W, at a single high frequency of greater than about 1 MHz, such as greater than about 1 MHz up to about 60 MHz, e.g., 13.6 MHz. Alternatively, the RF power may be provided at a mixed frequency including a first frequency between about 100 kHz up to about 1 MHz, e.g., about 300 kHz to about 400 kHz at a power level between about 2 W and about 5000 W, such as between about

15 30 W and about 1000 W, and a second frequency of greater than about 1 MHz, such as greater than about 1 MHz up to about 60 MHz, e.g., 13.6 MHz, at a power level between about 2 W and about 5000 W, such as between about 30 W and about 1000 W. The nitrogen-containing precursor may be introduced into the chamber at a flow rate of between about 5 sccm and about 50 slm, such as between about 100 sccm and about 500 sccm, during the

20 treatment. The nitrogen-containing precursor may be flowed into the chamber for a period of time, such as between about 1 second and about 2 hours, such as between about 1 second and about 60 seconds. The chamber pressure may be between about 10 mTorr and about 760 Torr, and the temperature of a substrate support in the chamber may be between about 20°C and about 1000°C during the treatment. Increased high frequency RF power, increased NH<sub>3</sub>

25 flow rates, and longer treatment times of the plasma process can be used to adjust the etch rate of the films.

**[0040]** In embodiments in which the treatment comprises a UV cure process, the UV cure process may be performed in the same chamber as the deposition chamber or in a chamber

30 which is part of an integrated tool that includes the deposition chamber in which the boron-containing film was deposited. For example, the UV cure process may be performed in a NANOCURE<sup>TM</sup> chamber that is part of a PRODUCER<sup>®</sup> platform that includes a PECVD chamber in which the boron-containing film is deposited.

[0041] Exemplary UV cure process conditions that may be used include a chamber pressure of between about 10 mTorr and about 760 Torr and a substrate support temperature of between about 20°C and about 1000°C. The nitrogen-containing precursor may be introduced into the chamber at a flow rate of between about 5 sccm and about 50 sccm during 5 the treatment. The nitrogen-containing precursor may be flowed into the chamber for a period of time such as between about 1 second and about 2 hours, such as between about 1 second and about 10 minutes. The UV radiation may be provided by any UV source, such as mercury microwave arc lamps, pulsed xenon flash lamps, or high-efficiency UV light emitting diode arrays. The UV radiation may have a wavelength of between about 170 nm and about 10 400 nm, for example. The treatment may comprise exposing the boron-containing film to between about 1 Watt/cm<sup>2</sup> and about 1000 Watts/cm<sup>2</sup> of ultraviolet radiation, and the ultraviolet radiation may provide a photon energy between about 0.5 eV and about 10 eV, such as between about 1 eV and about 6 eV.

[0042] Typically, the UV cure process removes hydrogen from the film, which is desirable 15 as hydrogen can diffuse through the film and into semiconducting regions of the substrate and degrade reliability of a device formed on the substrate. The UV cure process also typically increases the density of the film and reduces the etch rate.

[0043] In embodiments in which the treatment comprises a thermal process, the thermal 20 process may be performed in the same chamber in which the boron-containing film was deposited or a different chamber. The nitrogen-containing precursor may be introduced into the chamber at a flow rate of between about 5 sccm and about 50 slm, such as between about 10 sccm and about 1 slm, during the treatment. The nitrogen-containing precursor may be flowed into the chamber for a period of time such as between about 1 second and about 10 hours, such as between 10 seconds and about 20 minutes. The chamber pressure may be 25 between about 10 mTorr and about 760 Torr, and the temperature of a substrate support in the chamber may be between about 20°C and about 1000°C during the treatment.

[0044] While a substrate is exposed to the boron-containing precursor and the nitrogen-containing precursor sequentially in the embodiments described with respect to Figure 4, in alternative embodiments, a substrate is exposed to the boron-containing precursor and the 30 nitrogen-containing precursor (and/or an oxygen-containing) precursor simultaneously. Generally speaking, simultaneous exposure allows greater film growth rates and reduces the ability to control the thickness of thin films. In such embodiments, the boron-containing

precursor and the nitrogen-containing or oxygen-containing precursor are introduced into a chamber and then reacted to chemically vapor deposit a boron nitride or boron oxide film on a substrate in the chamber. Optionally, a silicon-containing compound, a carbon-containing compound, a phosphorous-containing compound, or combination thereof may also be introduced into the chamber at the same time to deposit a doped boron nitride film. The reaction of the boron-containing precursor, the nitrogen-containing or oxygen-containing precursor, and the optional other compounds may be performed in the presence or absence of a plasma in the chamber.

[0045] The ensuing discussion discusses specific process conditions for growing boron nitride as an exemplary low etch rate material. The boron-containing precursor and the nitrogen-containing precursor may be any of the precursors described above with respect to the embodiments of Figure 4. Similarly, the chamber and substrate may be any of the chambers and substrates, respectively, described above with respect to the embodiments of Figure 4.

[0046] The boron-containing precursor may be introduced into the chamber with nitrogen (N<sub>2</sub>), hydrogen (H<sub>2</sub>), argon (Ar) or a combination thereof as a dilution gas. The boron-containing precursor may be introduced into the chamber at a flow rate between about 5 sccm and about 50 slm, such as between about 10 sccm and about 1 slm. The nitrogen-containing precursor may be introduced into the chamber at a flow rate between about 5 sccm and about 50 slm, such as between about 10 sccm and about 1 slm. The dilution gas may be introduced into the chamber at a flow rate between about 5 sccm and about 50 slm, such as between about 1 slm and about 10 slm.

[0047] In embodiments in which the boron-containing precursor and the nitrogen-containing precursor are reacted in the presence of a plasma, a chamber pressure of between about 10 mTorr and about 760 Torr, e.g., between about 2 Torr and about 10 Torr, and a substrate support temperature of between about 100°C and about 1000°C, e.g., between about 300°C and about 500°C, may be used during the deposition. The spacing between a showerhead of the chamber and the substrate support may be between about 100 mils and about 10000 mils. The plasma may be provided by RF power delivered to a showerhead electrode and/or a substrate support electrode of the chamber. The RF power may be provided at a power level between about 2 W and about 5000 W, such as between about 30 W and about 1000 W, at a single low frequency of between about 100 kHz up to about 1

MHz, e.g., about 300 kHz to about 400 kHz, or at a power level between about 2 W and about 5000 W, such as between about 30 W and about 1000 W, at a single high frequency of greater than about 1 MHz, such as greater than about 1 MHz up to about 60 MHz, e.g., 13.6 MHz. Alternatively, the RF power may be provided at a mixed frequency including a first 5 frequency between about 100 kHz up to about 1 MHz, e.g., about 300 kHz to about 400 kHz at a power level between about 2 W and about 5000 W, such as between about 30 W and about 1000 W, and a second frequency of greater than about 1 MHz, such as greater than about 1 MHz up to about 60 MHz, e.g., 13.6 MHz, at a power level between about 2 W and about 5000 W, such as between about 30 W and about 1000 W.

10 [0048] Low dielectric etch rate materials other than boron nitride are also the subject of this patent as described earlier and set forth in the claims. In embodiments in which the boron-containing precursor and the nitrogen-containing, oxygen-containing, carbon-containing and/or silicon-containing precursor are reacted in the absence of a plasma, a chamber pressure of between about 10 mTorr and about 760 Torr and a substrate support temperature 15 of between about 100°C and about 1000°C may be used during the deposition. The spacing between a showerhead of the chamber and the substrate support may be between about 50 mils and about 5000 mils.

20 [0049] As used herein "substrate" may be a support substrate with or without layers formed thereon. The support substrate may be an insulator or a semiconductor of a variety of doping concentrations and profiles and may, for example, be a semiconductor substrate of the type used in the manufacture of integrated circuits. A gas in an "excited state" describes a gas wherein at least some of the gas molecules are in vibrationally-excited, dissociated and/or ionized states. A gas may be a combination of two or more gases. The term trench is used throughout with no implication that the etched geometry has a large horizontal aspect ratio. 25 Viewed from above the surface, trenches may appear circular, oval, polygonal, rectangular, or a variety of other shapes.

30 [0050] Having disclosed several embodiments, it will be recognized by those of skill in the art that various modifications, alternative constructions, and equivalents may be used without departing from the spirit of the disclosed embodiments. Additionally, a number of well known processes and elements have not been described in order to avoid unnecessarily obscuring the present invention. Accordingly, the above description should not be taken as limiting the scope of the invention.

**[0051]** Where a range of values is provided, it is understood that each intervening value, to the tenth of the unit of the lower limit unless the context clearly dictates otherwise, between the upper and lower limits of that range is also specifically disclosed. Each smaller range between any stated value or intervening value in a stated range and any other stated or 5 intervening value in that stated range is encompassed. The upper and lower limits of these smaller ranges may independently be included or excluded in the range, and each range where either, neither or both limits are included in the smaller ranges is also encompassed within the invention, subject to any specifically excluded limit in the stated range. Where the stated range includes one or both of the limits, ranges excluding either or both of those 10 included limits are also included.

**[0052]** As used herein and in the appended claims, the singular forms "a", "an", and "the" include plural referents unless the context clearly dictates otherwise. Thus, for example, reference to "a process" includes a plurality of such processes and reference to "the dielectric material" includes reference to one or more dielectric materials and equivalents thereof 15 known to those skilled in the art, and so forth.

**[0053]** Also, the words "comprise," "comprising," "include," "including," and "includes" when used in this specification and in the following claims are intended to specify the presence of stated features, integers, components, or steps, but they do not preclude the presence or addition of one or more other features, integers, components, steps, acts, or 20 groups.

WHAT IS CLAIMED IS:

- 1           1. A method of depositing dielectric material in a trench in a

2 semiconductor substrate, the method comprising:

- 3           forming a liner layer comprising boron nitride over bottom and sidewall

4 surfaces of the trench;

- 5           depositing the dielectric material comprising silicon oxide over the liner layer,

6 wherein the dielectric material at least partially fills the trench; and

- 7           etching a portion of the deposited dielectric material with an etchant, wherein

8 the etchant removes the dielectric material at a higher etch rate than the liner layer.

- 1           2. The method of claim 1, wherein the liner layer is a single layer

2 comprising boron nitride.

- 1           3. The method of claim 1, wherein the liner layer is a bilayer comprising

2 a silicon nitride layer and a boron nitride layer.

- 1           4. The method of claim 1, wherein the liner layer is a trilayer comprising

2 a boron nitride layer formed between a pair of silicon nitride layers.

- 1           5. The method of claim 1, wherein the step of etching a portion of the

2 deposited dielectric material exposes a void formed in the dielectric material in the trench.

- 1           6. The method of claim 5, wherein the method further comprises

2 depositing a second portion of the dielectric material in the trench, wherein the second

3 portion of dielectric material at least partially fills the exposed void.

- 1           7. The method of claim 1, wherein the step of etching a portion of the

2 deposited dielectric material widens a gap formed by the dielectric material in the trench.

- 1           8. The method of claim 1, wherein the step of etching a portion of the

2 deposited dielectric material involves a dry etch comprising reactive fluorine.

- 1           9. The method of claim 1, wherein the step of etching a portion of the

2 deposited dielectric material involves a Siconi etch process.

- 1           10. The method of claim 1, wherein the etchant comprises a reactive

2 fluorine species formed from nitrogen trifluoride (NF<sub>3</sub>).

1           11.    A method of removing a void formed in a dielectric material that fills a

2 trench in a semiconductor substrate, the method comprising:

3               etching a top portion of the dielectric material to expose an opening in the

4 void, wherein the etching also exposes a portion of a liner layer comprising boron nitride that

5 was covered by the dielectric material; and

6               depositing additional dielectric material into the exposed void to remove the

7 void by filling it with the additional dielectric material.

1           12.    A method of depositing a film to fill a gap in a surface of a substrate,

2 the method comprising:

3               forming a dielectric liner on the surface of the substrate, wherein a silicon

4 oxide to dielectric liner etch ratio is greater than about 50;

5               depositing a first layer of dielectric on the dielectric liner;

6               etching the surface of the substrate; and

7               depositing a second layer of dielectric to substantially fill the gap.

1           13.    The method of claim 12, wherein the oxide to dielectric liner etch ratio

2 is greater than about 75.

1           14.    The method of claim 12, wherein the oxide to dielectric liner etch ratio

2 is greater than about 100.

1           15.    The method of claim 12, wherein the dielectric liner comprises boron

2 nitride.

1           16.    The method of claim 12, wherein the dielectric liner has an atomic

2 concentration of boron which is greater than 5%.

1           17.    The method of claim 12, wherein the dielectric liner has an atomic

2 concentration of carbon which is greater than 5%.

1           18.    The method of claim 12, wherein the dielectric liner has an atomic

2 concentration of boron which is greater than 10%.

1           19.    The method of claim 12, wherein the dielectric liner has an atomic

2 concentration of carbon which is greater than 10%.

1                   20.     The method of claim 12, wherein the dielectric liner has an atomic

2 concentration of boron which is greater than 20%.

1                   21.     The method of claim 12, wherein the dielectric liner has an atomic

2 concentration of carbon which is greater than 20%.

1                   22.     The method of claim 12, wherein the dielectric liner comprises a

2 material selected from the group consisting of boron carbide, boron oxide, silicon carbide,

3 boron nitride, boron carbon nitride, phosphorous boron nitride, carbon nitride, silicon boron

4 nitride, boron silicon oxide and silicon carbon nitride.

1                   23.     The method of claim 12, further comprising a step of forming a layer

2 of silicon nitride before forming the conformal layer of boron nitride.

1                   24.     The method of claim 12, further comprising a step of forming a layer

2 of silicon nitride before depositing the first layer of dielectric.

1                   25.     The method of claim 12, further comprising a step of forming a first

2 layer of silicon nitride before forming the conformal layer of boron nitride and a second layer

3 of silicon nitride before depositing the first layer of dielectric.

1                   26.     The method of claim 12, wherein the step of etching the substrate

2 comprises dry etching the substrate in a process gas comprising NH<sub>3</sub> and NF<sub>3</sub>.

**FIG. 1**

**FIG. 2A**

**FIG. 2B**

**FIG. 2C**

**FIG. 2D**

**FIG. 2E**

**FIG. 3A**

**FIG. 3B**

**FIG. 4**