(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4124508号

(P4124508)

(45) 発行日 平成20年7月23日(2008.7.23)

(24) 登録日 平成20年5月16日(2008.5.16)

|               |                           |

|---------------|---------------------------|

| (51) Int.Cl.  | F 1                       |

| HO 1 L 21/316 | (2006.01) HO 1 L 21/316 X |

| HO 1 L 21/205 | (2006.01) HO 1 L 21/205   |

| HO 1 L 21/31  | (2006.01) HO 1 L 21/31 B  |

| HO 1 L 21/02  | (2006.01) HO 1 L 21/02 B  |

請求項の数 5 外国語出願 (全 7 頁)

|              |                         |           |                                                                                                            |

|--------------|-------------------------|-----------|------------------------------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願平10-67801             | (73) 特許権者 | 504199127<br>フリースケール セミコンダクター イン<br>コーポレイテッド<br>アメリカ合衆国 78735 テキサス州<br>オースティン ウィリアム キャノン<br>ドライブ ウエスト 6501 |

| (22) 出願日     | 平成10年3月2日(1998.3.2)     | (74) 代理人  | 100116322<br>弁理士 桑垣 衡                                                                                      |

| (65) 公開番号    | 特開平10-289906            | (72) 発明者  | マシュー・パスラック<br>アメリカ合衆国アリゾナ州チャンドラー、<br>ウエスト・リンダ・レーン5382                                                      |

| (43) 公開日     | 平成10年10月27日(1998.10.27) | (72) 発明者  | ジョナサン・ケイ・アプロクワ<br>アメリカ合衆国アリゾナ州テンピ、イース<br>ト・ランチ・ロード1963                                                     |

| 審査請求日        | 平成17年3月2日(2005.3.2)     |           |                                                                                                            |

| (31) 優先権主張番号 | 812950                  |           |                                                                                                            |

| (32) 優先日     | 平成9年3月4日(1997.3.4)      |           |                                                                                                            |

| (33) 優先権主張国  | 米国(US)                  |           |                                                                                                            |

最終頁に続く

(54) 【発明の名称】 化合物半導体ウエハの表面保護方法

## (57) 【特許請求の範囲】

## 【請求項1】

化合物半導体ウエハ構造の表面保護方法であって、

蒸着源の融点よりも高い融点を有し、蒸着源との共融合金を形成しない酸化物、または

蒸発源との共融温度を有するが蒸着源の蒸着温度よりも共融温度の方が高い酸化物からなる

酸化物坩堝に、結晶性  $Ga_2O_3$  からなる蒸着源を配置する工程と、

化合物半導体ウエハ構造(22)の表面(24)に前記結晶性  $Ga_2O_3$  蒸着源からの

酸化ガリウム分子を熱的に蒸着することによって、前記ウエハ構造の前記表面上に  $Ga_2O_3$  層(25)を形成する工程とを備える、表面保護方法。

## 【請求項2】

III-V族化合物成長チャンバ(35)および絶縁物蒸着チャンバ(38)に連結された搬送・装填モジュール(33)を備えたマルチ・ウエハ・エピタキシャル生産システム(30)における、半導体ウエハの表面保護方法であって、

蒸着源の融点よりも高い融点を有し、蒸着源との共融合金を形成しない酸化物、または

蒸発源との共融温度を有するが蒸着源の蒸着温度よりも共融温度の方が高い酸化物からなる

酸化物坩堝に、結晶性  $Ga_2O_3$  からなる蒸着源を配置する工程と、

前記搬送・装填モジュール(33)内に化合物半導体ウエハ(22)を配置する工程と、

前記マルチ・ウエハ生産システム(30)内の圧力を  $10^{-10}$  Torr に減圧する工程と、

10

20

前記化合物半導体ウエハ(22)を前記III-V族化合物成長チャンバ(35)に移動し、前記化合物半導体ウエハ(22)の表面上に、化合物半導体物質の層(23)をエピタキシャル成長させる工程と、

前記化合物半導体ウエハ(22)を前記搬送・装填モジュール(33)に移動し、次いで前記絶縁物蒸着チャンバ(38)に移動し、前記化合物半導体物質の層(23)上に結晶性 $\text{Ga}_2\text{O}_3$ 蒸着源からの酸化ガリウム分子を熱的に蒸着することにより、絶縁キャップ層(25)を形成する工程とを備える、表面保護方法。

【請求項3】

前記化合物半導体ウエハは、ガリウム砒素化合物半導体からなる、請求項2に記載の表面保護方法。

10

【請求項4】

前記酸化物坩堝を形成する酸化物は4eV以下のエネルギー・バンドギャップを有する、請求項1または2に記載の表面保護方法。

【請求項5】

前記酸化物坩堝は、 $\text{BeO}$ ,  $\text{ZrO}_2$ ,  $\text{HfO}_2$ ,  $\text{La}_2\text{O}_3$ ,  $\text{Al}_2\text{O}_3$ , または $\text{ThO}_2$ からなる、請求項1または2に記載の表面保護方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、III-Vウエハの生産に関し、更に特定すれば、III-V構造の表面保護に関するものである。

20

【0002】

【従来の技術】

従来技術におけるIII-Vエピタキシャル・ウエハの生産では、半導体層を用いてエピタキシャル構造を完成させる。例えば、 $\text{GaAs}$ ,  $\text{In}_{1-x}\text{Ga}_x\text{As}$ ,  $\text{Al}_{1-x}\text{Ga}_x\text{As}$ ,  $\text{InGaAsP}$ 等のような、種々の半導体最上層が、特定の素子/回路用途および半導体基板に応じて用いられている。従来技術のエピタキシャル・ウエハの生産では、半導体最上層を用いると、その結果制御不能かつ有害な電気的特性および化学的表面特性が発生する。電子および光電素子/回路処理は複雑化し、素子/回路性能に影響が及ぶ。複雑化および劣化の度合いは、特定の素子/回路処理および用途に左右される。例えば、ユニポーラ・トランジスタ素子/回路では、プラズマ露出、フェルミ・レベル・ピンニング(Fermi level pinning), ならびにゲート・ソースおよびゲート・ドレイン領域の不安定性によって、その生産性および性能の低下を招く。機能的かつ安定なMOSFET素子の製造は不可能であった。

30

【0003】

制御不能かつ有害な電気的特性および表面特性は、化学的表面反応によって自然酸化物およびダングリング・ボンド(dangling bond)が発生するために生ずる。一方、表面は熱力学的に不安定であり、フェルミ・レベル・ピンニング(pinned Fermi level)を呈する。即ち、 $10^3$  Langmuir ( $1\text{ Langmuir} = 10^{-6}\text{ Torr}$ )という低い圧力に表面を露出させた後に、 $\text{GaAs}$ 表面の高い反応性が、フェルミ・レベル・ピンニングおよび表面の不安定性を誘発する。空気(硫黄, セレニウム等)に露出した後に表面準備技法を実施することは、非効率的でありかつ不安定であることが証明されている。

40

【0004】

従来技術では、例えば、M. Passlack et al., Appl. Phys. Lett., vol 68, 1099 (1996), Appl. Phys. Lett., vol. 68, 3605 (1996), およびAppl. Phys. Lett., vol 69, 302, (1996), "Electron beam Deposition of gallium oxide thin films using a single purity crystal layer"と題し1995年9月19日に特許された米国特許番号第5,451,548号, "Gallium Oxide Coatings for Optoelectronic Devices Using Electron Beam Evaporation of a High Purity Single Crystal  $\text{Gd}_3\text{Ga}_5\text{O}_{12}$  Source"と題し1996年8月27日に特許された米国特許番号第5,550,089号において、超高真空

50

(UHV : ultra-high vacuum) を保持しながら、 $Gd_3Ga_5O_{12}$  の e - ビーム蒸着 (e-beam evaporation) を用いて、 $GaAs$  系半導体エピタキシャル層上に特定の絶縁キャップ層を現場において堆積すると、界面状態密度 (interface state density) が低い熱力学的に安定な III - V 表面 (界面) の製造が可能であることが報告されている。 $GaAs$  では、重要な要素には、 $GaAs$  表面の不純物への超低圧露出 (< 10 ないし 100 Langmuir) ならびに  $GaAs$  バルクおよび表面化学量論比の保存、 $GaAs$  表面酸化の完全な除外、ならびに  $GaAs$  および堆積される分子の界面原子に関連する特定の原子構造の必要性が含まれる。しかしながら、従来技術に記載されているプロセスは、dc 不安定性および低い信頼性に妨げられるために、製造は不可能である。

## 【0005】

10

したがって、これらの問題を克服する新しい製造方法を提供することができれば、非常に有利であろう。

## 【0006】

## 【発明が解決しようとする課題】

本発明の目的は、新規で改良された III - V エピタキシャル・ウエハ生産プロセスを提供することである。

## 【0007】

本発明の他の目的は、安定性および信頼性改善を図った新規で改良された III - V エピタキシャル・ウエハを提供することである。

## 【0008】

20

本発明の更に他の目的は、製造および使用が比較的簡単な、新規で改良された III - V ウエハを提供することである。

## 【0009】

## 【課題を解決するための手段】

上述のおよびその他の問題の少なくとも部分的な解決、ならびに上述のおよびその他の目的の実現は、本発明の化合物半導体ウエハ構造の表面保護方法において達成される。この方法は、表面を有する化合物半導体ウエハ構造を用意する段階と、ウエハ構造上で絶縁物質を熱的に蒸着させることにより、ウエハ構造の表面上に絶縁キャップ層を形成する段階とを含む。

## 【0010】

30

具体的な半導体生産プロセスでは、マルチ・ウエハ・エピタキシャル生産システムを用意する。このシステムは、III - V 族化合物成長チャンバおよび絶縁物蒸着チャンバが取り付けられた搬送・装填モジュールを含む。表面を有する化合物半導体ウエハをこの搬送・装填モジュール内に配置し、マルチ・ウエハ生産システム内の圧力を  $10^{-10}$  Torr に減圧する。化合物半導体ウエハを III - V 族化合物成長チャンバに移動し、化合物半導体物質の層を、化合物半導体ウエハの表面上にエピタキシャル成長させる。次に、マルチ・ウエハ生産システムから取り出すことなく、化合物半導体ウエハを搬送・装填モジュールに移動し、更に絶縁物蒸着チャンバに移動する。化合物半導体物質の層上に物質を熱的に蒸着することによって、絶縁キャップ層を形成する。

## 【0011】

40

## 【発明の実施の形態】

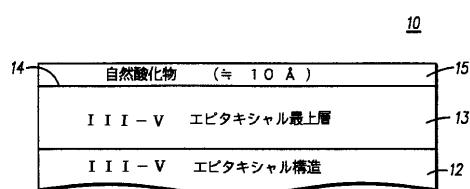

具体的に図 1 を参照すると、従来技術の III - V 化合物半導体ウエハ 10 が示されている。ウエハ 10 は、基板、およびその上面にエピタキシャル的に形成された 1 層以上の III - V 物質を含む。この開示の目的のために、基板およびその上に形成されたあらゆるエピタキシャル層のことを、単に化合物半導体ウエハ構造と呼ぶことにする。これは、図 1 では 12 で示されている。化合物半導体ウエハ構造 12 は、上面 14 のある最上層 13 を有する。化合物半導体ウエハ構造 12 または最上層 13 を周囲状態 (空気、処理環境等) に露出させると常に、自然酸化物の層 15 が表面上に形成される。通常、層 15 は非常に薄く、厚さは約 10 オングストローム程度である。最上層 13 および自然酸化物層 15 間の界面は、熱力学的に不安定であり、フェルミ・レベル・ピンニングを呈する。

50

## 【0012】

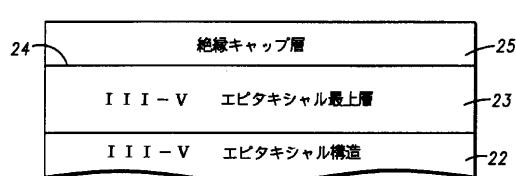

本発明にしたがって形成された化合物半導体ウエハ構造20を図2に示す。化合物半導体ウエハ構造20は、概略的に、基板、およびその表面上にエピタキシャル的に形成された1層以上のIII-V物質を含む。以降、この層を22で示すことにする。化合物半導体ウエハ構造20は、上面24のある最上層23を有する。勿論、特定用途によっては(または、化合物半導体ウエハ構造20のある部分では)、基板上にエピタキシャル層がない場合もあり、上面24が単に基板の上面となっている場合もあることは理解されよう。化合物半導体ウエハ構造20の表面24上に、絶縁キャップ層25を熱的に蒸着する。

## 【0013】

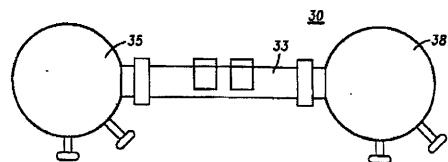

次に図3に移ると、マルチ・ウエハ・エピタキシャル生産システム30が示されている。これは、本発明による図2の化合物半導体ウエハ構造20を製造する際に用いられる。システム30は、搬送・装填モジュール33、この搬送・装填モジュール33に取り付けられたIII-V成長チャンバ35、および搬送・装填モジュール33に取り付けられた絶縁物蒸着チャンバ38を含む。各チャンバ35、38が搬送・装填モジュール33に取り付けられているので、ウエハ、チップ等は、システム30から取り出すことなく、各チャンバ内で処理することができる。したがって、一旦ウエハをシステム30に導入し真空状態としたなら、ウエハは、処理が完了するまで、環境には晒されない。

## 【0014】

したがって、本発明による化合物半導体ウエハ構造の表面を保護するプロセスの一例として、化合物半導体ウエハを搬送・装填モジュール33内に配置し、マルチ・ウエハ生産システム30内の圧力を $10^{-10}$  Torrに減圧する。次に、ウエハをIII-V族化合物成長チャンバ35に移動し、化合物半導体物質の1つ以上の層を、表面上にエピタキシャル成長させ、化合物半導体ウエハ構造(例えば、化合物半導体ウエハ構造20)を生産する。最上層23の成長の後、化合物半導体ウエハ構造20を搬送・装填モジュール33に移動し、次いで絶縁物蒸着チャンバ38に移動する。絶縁物蒸着チャンバ38内において、ウエハ構造20上に絶縁物質を熱的に蒸着することによって、化合物半導体ウエハ構造20の表面24上に、絶縁キャップ層25を形成する。

## 【0015】

本プロセスの好適実施例では、酸化物坩堝(oxide crucible)において蒸着源(evaporation source)を用い、流出セル(effusion cell)からのガリウム酸化物分子を熱的に蒸着することによって、ウエハ構造20の表面24上に、絶縁キャップ層25を熱的に蒸着する。蒸着源は、融点 $m_p$ を有する多結晶 $\text{Ga}_2\text{O}_3$ 、融点 $m_p$ を有する単結晶 $\text{Ga}_2\text{O}_3$ 、あるいは融点 $m_p$ を有する $\text{Ga}_2\text{O}_3$ 成分を含有する多結晶または単結晶物質の1つから選択する。蒸着源を含む酸化物坩堝は、融点 $m_p$ が蒸着源の融点よりも高くある( $m_p > m_p$ )とともに、蒸着源との共融合金(eutectic alloy)を形成しない酸化物からなる坩堝、または共融温度を有し蒸着源の蒸着温度よりも共融温度の方が高い酸化物からなる坩堝のいずれかから選択する。更に、酸化物坩堝は、比較的高いバンドギャップ、即ち、通常4 eVを有する物質で形成することが好ましい。

## 【0016】

ある特定例では、酸化物坩堝は、以下の物質の1つで形成する。 $\text{BeO}$ ( $m_p = 2507$ )、 $\text{ZrO}_2$ ( $m_p = 2710$ )、 $\text{HfO}_2$ ( $m_p = 2774$ )、 $\text{La}_2\text{O}_3$ ( $m_p = 2305$ )、 $\text{Al}_2\text{O}_3$ ( $m_p = 2050$ )、または $\text{ThO}_2$ ( $m_p = 3390$ )。上述の物質の1つを酸化物坩堝に使用する場合、蒸着源は、多結晶または単結晶 $\text{Ga}_2\text{O}_3$ 、あるいは $\text{Ga}_2\text{O}_3$ 成分を含有する多結晶または単結晶材料( $m_p = 1725$ )とする。他の特定例では、酸化物坩堝は、以下の材料の1つで形成する。 $\text{ZrO}_2$ ( $m_p = 2710$ )、 $\text{HfO}_2$ ( $m_p = 2774$ )、 $\text{La}_2\text{O}_3$ ( $m_p = 2305$ )、 $\text{Al}_2\text{O}_3$ ( $m_p = 2050$ )、または $\text{ThO}_2$ ( $m_p = 3390$ )。この場合、蒸着源は、 $\text{Gd}_3\text{Ga}_5\text{O}_{12}$ ( $m_p = 1700$ )および $\text{MgGa}_2\text{O}_4$ ( $m_p = 1700$ )の一方を含む。

## 【0017】

10

20

30

40

50

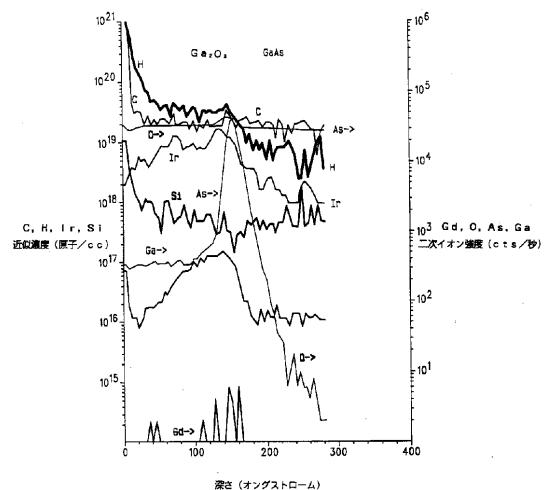

このようにして、絶縁キャップ層 25 を適所に配するまで、化合物半導体ウエハ構造 20 を周囲条件に露出することから保護する。図 3 のシステム 30 において絶縁キャップ層 25 を形成するので、構造即ちエピタキシャル層は、周囲条件には決して晒されることはなく、基板またはエピタキシャル層および絶縁キャップ層 25 間の界面は、熱力学的に安定であり、卓越した電気的特性を有する。GaAs 表面およびその上に堆積した酸化物層を有する化合物半導体ウエハ構造の特定例では、GaAs - Ga<sub>2</sub>O<sub>3</sub> 界面は、単一層急峻性(monolayer abruptness)を呈し、酸化物の表面荒さ (rms) は 2.5 オングス 10 ロームである。また、製造したウエハ全体にわたって界面状態密度には、卓越した均一性があることもわかった。界面状態密度は、全体として、従来技術の密度 ( $10^{10} \text{ cm}^{-2} \text{ eV}^{-1}$ ) に比肩し得るか、あるいはこれよりも優れている。更に、Gd<sub>3</sub>Ga<sub>5</sub>O<sub>12</sub>を蒸着源として用いた特定例では、Ga<sub>2</sub>O<sub>3</sub> 膜が含む Gd レベルは、図 4 のグラフに示すように、選択イオン質量分光分析 (SIMS: Selective Ion Mass Spectroscopy) の検出限界未満であることもわかっている。

#### 【0018】

開示したプロセスのウエハ構造上に熱的に蒸着した絶縁層は、従来技術のエピタキシャル生成物の露出した半導体表面に置き換わり、埋め込みエピタキシャル半導体表面は電気的および化学的に安定で、卓越した電気的特性を呈する。このように、新規な表面保護プロセスにしたがって製造した、改良された化合物半導体ウエハ構造は、以下の利点を有する。まず、半導体エピ層構造およびその中に形成される素子 / 回路の卓越した電気的および化学的特性、パシベーションならびに保護性能を有すること、半導体エピ層構造およびその中に形成される素子 / 回路の卓越した電子および化学表面特性の安定性、素子 / 回路処理の簡略化、素子 / 回路の再現性および信頼性向上が得られること、更に、電子的パシベーションの処理および保存の間半導体表面の重要な部分が露出されないことがあげられる。

#### 【0019】

これらの改良によって、dc 不安定性や低い信頼性のような従来技術の問題が本質的に解決即ち克服されるため、生産性の高いプロセスが得られる。

#### 【0020】

以上、本発明の特定実施例について示しかつ説明したが、更に別の変更や改良も当業者には想起されよう。したがって、本発明は、ここに示した特定形態には限定されないと理解されることを望み、本発明の精神および範囲から逸脱しない変更は全て特許請求の範囲に含まれることを意図するものである。

#### 【図面の簡単な説明】

【図 1】表面上に自然酸化物が形成されている、従来技術の化合物半導体基板の簡略断面図。

【図 2】本発明による、エピタキシャル層およびキャップ層を有する化合物半導体基板の簡略断面図。

【図 3】本発明にしたがって図 2 の構造を製造する際に利用するマルチ・ウエハ・エピタキシャル生産システムを示す図。

【図 4】Gd<sub>3</sub>Ga<sub>5</sub>O<sub>12</sub>を蒸着源とした場合の、Ga<sub>2</sub>O<sub>3</sub> 膜における近似濃度およびイオン強度を示すグラフ。

#### 【符号の説明】

- 1 0 I I I - V 化合物半導体ウエハ

- 1 2 化合物半導体ウエハ構造

- 1 3 最上層

- 1 4 上面

- 1 5 自然酸化物層

- 2 0 化合物半導体ウエハ構造

- 2 2 層

- 2 3 最上層

10

20

30

40

50

- 2 4 上面

2 5 絶縁キャップ層

3 0 マルチ・ウエハ・エピタキシャル生産システム

3 3 転送および装填モジュール

3 5 I I I - V 成長チャンバ

3 8 絶縁チャンバ

【図 1】

【図 2】

【図 3】

【図 4】

---

フロントページの続き

(72)発明者 ラビ・ドュルーパッド

アメリカ合衆国アリゾナ州テンピ、イースト・ジェミニ・ドライブ1854

(72)発明者 コレイ・ディー・オーバーガード

アメリカ合衆国アリゾナ州フェニックス、ウエスト・マルベリー・ドライブ2034

審査官 大塚 徹

(56)参考文献 特開平07-268609(JP,A)

特開平07-273405(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/316

H01L 21/205

H01L 21/31

H01L 21/02