(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2015-114652

(P2015-114652A)

(43) 公開日 平成27年6月22日(2015.6.22)

| (51) Int.Cl.                | F 1       | テーマコード (参考) |

|-----------------------------|-----------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 | K 3K107     |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 | 624B 5C080  |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 | 642A 5C380  |

|                             | G09G 3/20 | 612U        |

|                             | G09G 3/30 | J           |

審査請求 未請求 請求項の数 7 O L (全 20 頁) 最終頁に続く

|           |                              |          |                                        |

|-----------|------------------------------|----------|----------------------------------------|

| (21) 出願番号 | 特願2013-259168 (P2013-259168) | (71) 出願人 | 000201814<br>双葉電子工業株式会社<br>千葉県茂原市大芝629 |

| (22) 出願日  | 平成25年12月16日 (2013.12.16)     | (74) 代理人 | 100116942<br>弁理士 岩田 雅信                 |

|           |                              | (74) 代理人 | 100167704<br>弁理士 中川 裕人                 |

|           |                              | (74) 代理人 | 100114122<br>弁理士 鈴木 伸夫                 |

|           |                              | (74) 代理人 | 100086841<br>弁理士 脇 篤夫                  |

|           |                              | (72) 発明者 | 六車 雄<br>千葉県茂原市大芝629 双葉電子工業株式会社内        |

最終頁に続く

(54) 【発明の名称】表示駆動装置、表示駆動方法、表示装置

## (57) 【要約】

【課題】表示装置における表示ムラの改善

【解決手段】データ線と走査線の交差点に対応して画素が形成されている表示部に対する表示駆動のために、表示データのフレームを構成する各行について設定された電流階調値を記憶する電流設定部と、1フレーム内の各行の走査タイミング毎に、その行の電流階調値とされた定電流を生成する電流階調制御部と、データ線のそれに対して、表示データで規定される画素の階調値に応じた時間長だけ電流階調制御部からの定電流を供給するデータ線駆動部とを設ける。これによりデータ線に供給される定電流が走査線単位で可変制御されるようにする。

【選択図】図5

## 【特許請求の範囲】

## 【請求項 1】

列方向に並ぶ複数の画素に共通に接続されたデータ線と、行方向に並ぶ複数の画素に共通に接続された走査線とが、それぞれ複数配設され、前記データ線と前記走査線の各交差点に対応して画素が形成されている表示部に対して、表示データに基づく表示駆動を行う表示駆動装置であって、

表示データのフレームを構成する各行について設定された電流階調値を記憶する電流設定部と、

1フレーム内の各行の走査タイミング毎に、前記電流設定部に記憶された該当行の電流階調値とされた定電流を生成する電流階調制御部と、

前記データ線のそれぞれに対して、表示データで規定される画素の階調値に応じた時間長だけ、前記電流階調制御部からの定電流を供給するデータ線駆動部と、を備えた表示駆動装置。

## 【請求項 2】

前記電流階調制御部は、1フレーム内の各行の走査タイミング毎の定電流の電流階調値の切替を、各行の走査期間の間のプランギング期間において実行する

請求項1に記載の表示駆動装置。

## 【請求項 3】

前記電流設定部に記憶される電流階調値は、前記表示部で表示する表示データの切替に対応して書き換えられる

請求項1又は請求項2に記載の表示駆動装置。

## 【請求項 4】

前記電流設定部に記憶される電流階調値の書き換えは、フレーム開始タイミングで行われる

請求項1乃至請求項3のいずれかに記載の表示駆動装置。

## 【請求項 5】

前記電流階調制御部は、流れる電流値について異なる重み付けをされた複数のトランジスタのうちの1つ以上を、前記電流設定部に記憶された電流階調値に基づいて選択し、選択されたトランジスタの電流値の和に相当する電流値として、電流階調値に相当する定電流を生成する

請求項1乃至請求項4のいずれかに記載の表示駆動装置。

## 【請求項 6】

列方向に並ぶ複数の画素に共通に接続されたデータ線と、行方向に並ぶ複数の画素に共通に接続された走査線とが、それぞれ複数配設され、前記データ線と前記走査線の各交差点に対応して画素が形成されている表示部に対して、表示データに基づく表示駆動を行う表示駆動方法として、

表示データのフレームを構成する各行について設定された電流階調値を記憶し、

1フレーム内の各行の走査タイミング毎に、記憶された電流階調値のうちで該当行の電流階調値とされた定電流を生成し、

生成した定電流を、前記データ線のそれぞれに対して、表示データで規定される画素の階調値に応じた時間長だけ供給する

表示駆動方法。

## 【請求項 7】

列方向に並ぶ複数の画素に共通に接続されたデータ線と、行方向に並ぶ複数の画素に共通に接続された走査線とが、それぞれ複数配設され、前記データ線と前記走査線の各交差点に対応して画素が形成されている表示部と、

前記走査線に対して走査信号を与える走査線駆動部と、

表示データのフレームを構成する各行について設定された電流階調値を記憶する電流設定部と、

1フレーム内の各行の走査タイミング毎に、前記電流設定部に記憶された該当行の電流

10

20

30

40

50

階調値とされた定電流を生成する電流階調制御部と、

前記データ線のそれぞれに対して、表示データで規定される画素の階調値に応じた時間長だけ、前記電流階調制御部からの定電流を供給するデータ線駆動部と、を備えた表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は表示駆動装置、表示駆動方法、表示装置に関し、特にデータ線と走査線が複数配設され、データ線と前記走査線の各交差点に対応して画素が形成されている表示部の駆動技術に関する。

10

【先行技術文献】

【特許文献】

【0002】

【特許文献1】特開平9-232074号公報

【特許文献2】特開2004-309698号公報

【背景技術】

【0003】

画像を表示する表示パネルとして、OLED (Organic Light Emitting Diode: 有機発光ダイオード) を用いる表示装置、LCD (Liquid Crystal Display: 液晶ディスプレイ) を用いる表示装置等が知られている。多くの表示装置では、列方向に並ぶ複数の画素に共通に接続されたデータ線と、行方向に並ぶ複数の画素に共通に接続された走査線とがそれぞれ複数配設され、データ線と走査線の各交差点に対応して画素が形成されている表示部を有する。

20

そしていわゆる線順次走査の場合、走査線ドライバが順次走査線を選択していきながら、データ線ドライバが、各データ線に1ライン分のデータ線駆動信号を出力することで画素としての各ドットの表示が制御される。

【0004】

上記特許文献1には表示パネルの寄生容量による画素発光の立ち上がりの遅れを改善するために、走査が次の走査線に移る際に、すべての走査線を一旦リセット電位に接続する技術が開示されている。

30

上記特許文献2には、データ電極に表示信号を供給する際に、そのオーバーシュート、アンダーシュートを低減するための手法として、すべての電極をリセット電位に接続し、続いてプリセット電位に接続する技術が開示されている。

【発明の概要】

【発明が解決しようとする課題】

【0005】

ここで例えばパッシブ駆動OLED表示装置では、表示パネルが通常の方形ではないなどの事情で長さが異なる走査線が存在する場合や、各走査線で画素の点灯率が異なる場合(発光させる画素の数が異なる場合)に、部分的に本来の階調よりも高輝度或いは低輝度となることがある。これにより画面上に表示ムラが生じてしまう。

40

なおここでいう「点灯率」とは、各走査線の画素数のうちで発光させる画素数の割合の意味である。(点灯率 = 走査線上の発光画素数 / 走査線上の画素数)

そこで本発明では、これらの事情で生じる輝度変化を小さくし、輝度ムラ(表示ムラ)を低減することを目的とする。

【課題を解決するための手段】

【0006】

第1に、本発明に係る表示駆動装置は、列方向に並ぶ複数の画素に共通に接続されたデータ線と、行方向に並ぶ複数の画素に共通に接続された走査線とが、それぞれ複数配設され、前記データ線と前記走査線の各交差点に対応して画素が形成されている表示部に対して、表示データに基づく表示駆動を行う表示駆動装置であって、表示データのフレームを

50

構成する各行について設定された電流階調値を記憶する電流設定部と、1フレーム内の各行の走査タイミング毎に、前記電流設定部に記憶された該当行の電流階調値とされた定電流を生成する電流階調制御部と、前記データ線のそれぞれに対して、表示データで規定される画素の階調値に応じた時間長だけ、前記電流階調制御部からの定電流を供給するデータ線駆動部とを備えたものである。

このような表示駆動装置によって、データ線には階調値に応じた時間長だけ定電流が与えられる。定電流を与える時間によって画素の発光輝度を制御している。ここで、1ライン（本明細書で「ライン」とは走査線としての行や、或いは走査線とその走査線上に配列された画素を含む行を包括的に表す用語としている）上の非発光画素の数や発光階調の影響、或いは各走査線の長さの差により、部分的に本来の階調よりも高輝度或いは低輝度となり、表示ムラが生ずることがある。そこで各走査線の走査タイミング毎に、各データ線に与える定電流値を制御する。つまり1ラインの走査毎に定電流値を可変制御する。各ラインに応じた定電流値は、電流階調値として表示ムラを解消できる適切な値に設定して記憶しておく。

#### 【0007】

第2に、上記した本発明に係る表示駆動装置においては、前記電流階調制御部は、1フレーム内の各行の走査タイミング毎の定電流の電流階調値の切替を、各行の走査期間の間のブランкиング期間において実行することが望ましい。

ライン毎に定電流値を制御するわけであるが、その定電流値の切替をブランкиング期間で行うことで、定電流値の変動の影響を表示に及ぼさないようにできる。

#### 【0008】

第3に、上記した本発明に係る表示駆動装置においては、前記電流設定部に記憶される電流階調値は、前記表示部で表示する表示データの切替に対応して書き換えられることが望ましい。

1フレームにおける各ラインの点灯率は画像内容によって異なる。従って表示画像を切り換える場合に、それに応じて電流設定部に記憶される電流階調値も書き換えることが適切となる。

#### 【0009】

第4に、上記した本発明に係る表示駆動装置においては、前記電流設定部に記憶される電流階調値の書き換えは、フレーム開始タイミングで行われることが望ましい。表示画像の切替をフレーム開始タイミングで行うためである。

#### 【0010】

第5に、上記した本発明に係る表示駆動装置においては、前記電流階調制御部は、流れ電流値について異なる重み付けをされた複数のトランジスタのうちの1つ以上を、前記電流設定部に記憶された電流階調値に基づいて選択し、選択されたトランジスタの電流値の和に相当する電流値として、電流階調値に相当する定電流を生成することが望ましい。

これにより電流階調値に応じたトランジスタの選択により、電流階調値に応じた定電流駆動を行うことができる。

#### 【0011】

本発明に係る表示駆動方法は、表示データのフレームを構成する各行について設定された電流階調値を記憶し、1フレーム内の各行の走査タイミング毎に、記憶された電流階調値のうちで該当行の電流階調値とされた定電流を生成し、生成した定電流を、前記データ線のそれぞれに対して、表示データで規定される画素の階調値に応じた時間長だけ供給するものである。

即ち走査線の長さの差や走査線上の点灯率等の影響による輝度変化に対する表示ムラの補正を、データ線に与える定電流値の走査タイミング毎の調整によって実現する。

#### 【0012】

また本発明に係る表示装置は、列方向に並ぶ複数の画素に共通に接続されたデータ線と、行方向に並ぶ複数の画素に共通に接続された走査線とが、それぞれ複数配設され、前記データ線と前記走査線の各交差点に対応して画素が形成されている表示部と、前記走査線

に対して走査信号を与える走査線駆動部と、表示データのフレームを構成する各行について設定された電流階調値を記憶する電流設定部と、1フレーム内の各行の走査タイミング毎に、前記電流設定部に記憶された該当行の電流階調値とされた定電流を生成する電流階調制御部と、前記データ線のそれぞれに対して、表示データで規定される画素の階調値に応じた時間長だけ、前記電流階調制御部からの定電流を供給するデータ線駆動部とを備える。

即ち上述の表示駆動装置を備えた表示装置を構成する。

【発明の効果】

【0013】

本発明によれば、走査線の長さの差や走査線上の点灯率等の影響による輝度変化を、データ線に与える定電流値を走査タイミング毎に調整することで、表示ムラ（輝度ムラ）を低減し、もって表示品質を向上させることができる。

10

【図面の簡単な説明】

【0014】

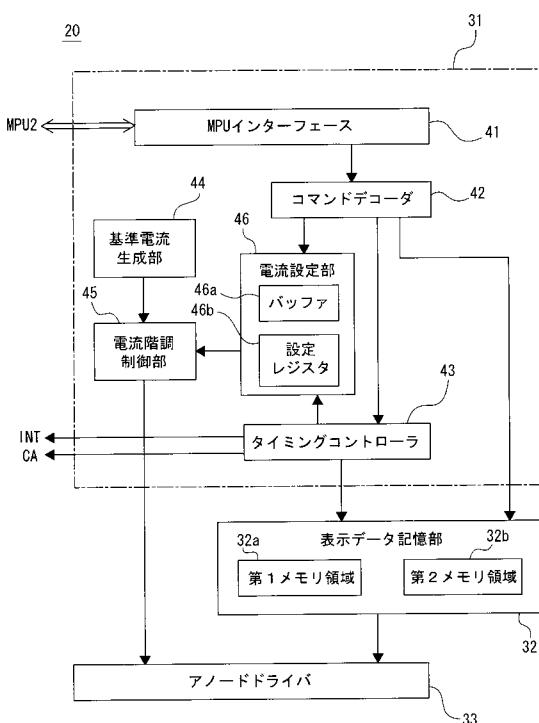

【図1】本発明の実施の形態の表示装置のブロック図である。

【図2】異形パネルでの輝度ムラの説明図である。

【図3】点灯率の差による輝度ムラの説明図である。

【図4】点灯率の差による輝度ムラの発生原因の説明図である。

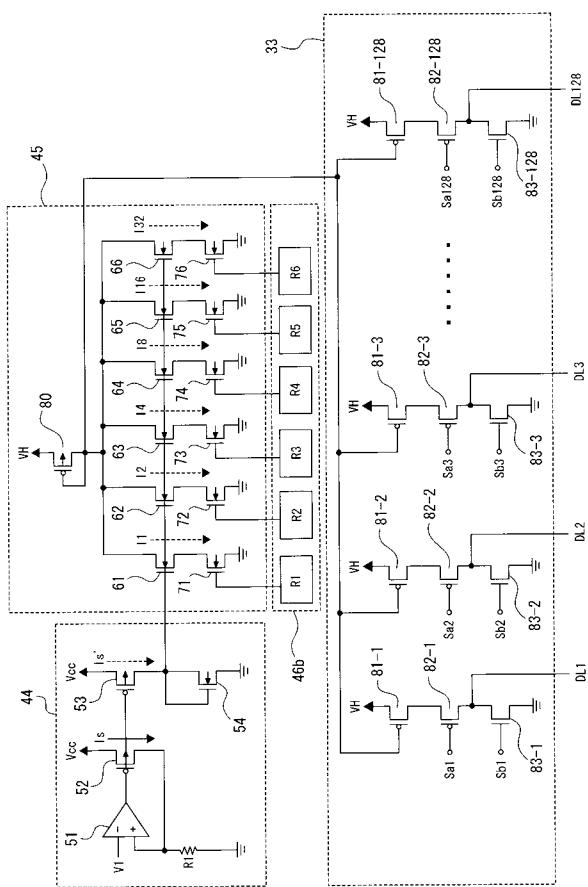

【図5】実施の形態のコントローラICのブロック図である。

【図6】実施の形態の電流階調値の説明図である。

20

【図7】実施の形態の定電流生成系の回路図である。

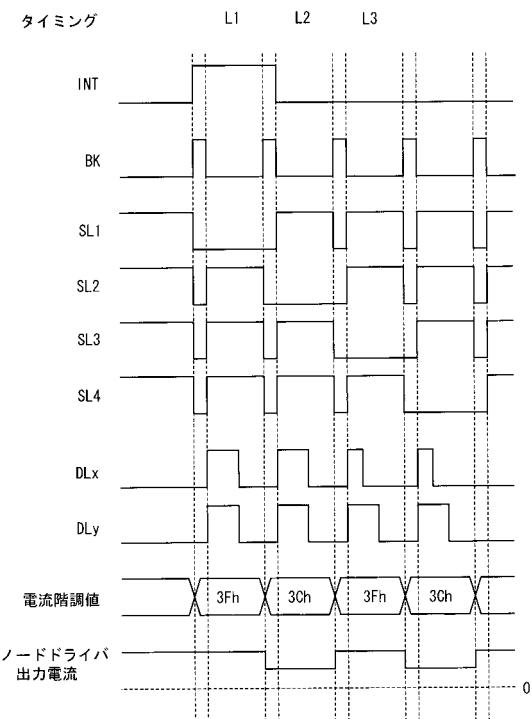

【図8】実施の形態の表示駆動動作波形の説明図である。

【図9】実施の形態の表示データに応じた電流階調値の説明図である。

【図10】実施の形態の表示データ切替動作の説明図である。

【図11】実施の形態の表示データ切替処理のフローチャートである。

【発明を実施するための形態】

【0015】

以下、本発明の実施の形態を次の順序で説明する。

30

<1. 実施の形態の表示装置>

<2. 表示上に発生する輝度変化の説明>

<3. 表示駆動装置の構成及び動作>

<4. 表示画像の切り替え>

<5. 実施の形態の効果及び変形例>

【0016】

<1. 実施の形態の表示装置>

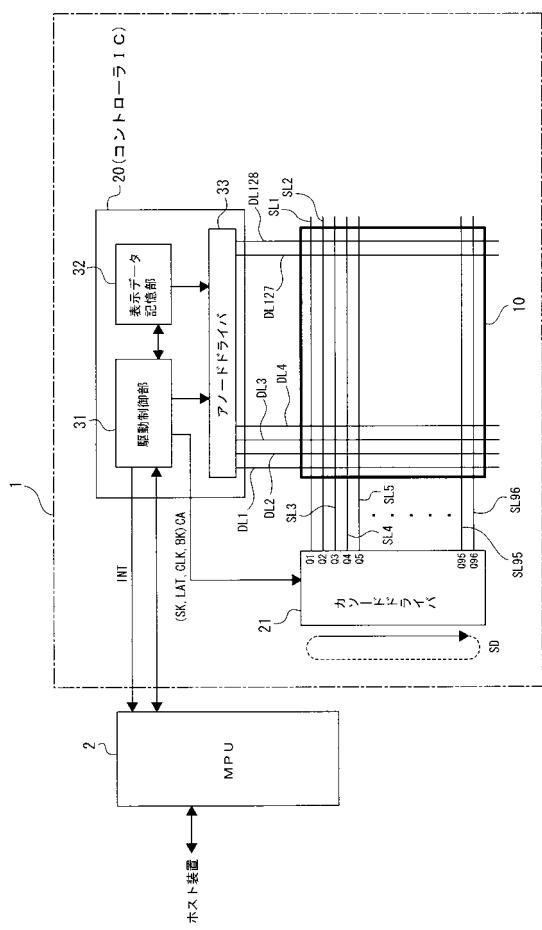

図1は実施の形態の表示装置1と、表示装置1の表示動作制御を行うMPU（Micro Processing Unit：演算装置）2を示している。

表示装置1は、表示画面を構成する表示部10と、コントローラIC（Integrated Circuit）20と、カソードドライバ21を有する。

表示装置1が本発明請求項の表示装置に相当する実施の形態である。またコントローラIC20が本発明請求項の表示駆動装置に相当する実施の形態である。

40

なお、この図1の例ではカソードドライバ21はコントローラIC20の外部の構成として示しているが、カソードドライバ21がコントローラIC20の内部に設けられる場合もある。

【0017】

表示部10は、データ線DL（DL1～DL128）と、走査線SL（SL1～SL96）とが、それぞれ複数配設され、データ線DLと走査線SLの各交差点に対応して画素が形成されている。即ち128本のデータ線DL1～DL128と、96本の走査線SL1～SL96に対応して、128個の画素が水平方向の1行（1ライン）に配置され、96個の画素が垂直方向の1列に配置される。

50

従って表示部10は、表示画像を構成する画素として $128 \times 96 = 12288$ 個の画素を有する。本実施の形態の場合、各画素はOLEDを用いた自発光素子として形成される。なお、もちろん画素数、データ線数、走査線数は一例に過ぎない。

#### 【0018】

128本のデータ線DL1～DL128のそれぞれは、表示部10の列方向（垂直方向）に並ぶ96個の画素に共通に接続されている。また96本の走査線SL1～SL96のそれぞれは、行方向（水平方向）に並ぶ128個の画素に共通に接続されている。

走査線SLで選択されたラインの128個の画素に、データ線DLから表示データ（階調値）に基づく発光駆動電流が与えられることで、当該ラインの各画素が、表示データに応じた輝度（階調）で発光駆動される。

10

#### 【0019】

この表示部10の表示駆動のためにコントローラIC20、カソードドライバ21が設けられる。

コントローラIC20は、駆動制御部31、表示データ記憶部32、アノードドライバ33を有する。アノードドライバ33は、データ線DL1～DL128を駆動する。

アノードドライバ33は、駆動制御部31から供給される定電流を、表示データ記憶部32に記憶された表示データの階調に応じた時間長だけデータ線DLに供給する。即ちアノードドライバ33はデータ線駆動部として機能する。

#### 【0020】

駆動制御部31は、MPU2との間でコマンドや表示データの通信を行い、コマンドに応じた表示動作を制御する。例えば駆動制御部31は、表示開始のコマンドを受信すると、それに応じてタイミング設定を行って、カソードドライバ21による走査線SLの走査を開始させる。またカソードドライバ21による走査に同期させてアノードドライバ33によるデータ線DLの駆動を実行させる。

20

アノードドライバ33によるデータ線DLの駆動に関しては、駆動制御部31は、MPU2から受信した表示データを表示データ記憶部32に記憶させると共に、上記の走査タイミングに合わせて、表示データをアノードドライバ33に転送させる。またデータ線駆動信号としての定電流を生成し、アノードドライバ33に供給する。

これに応じてアノードドライバ33が、各階調に応じた期間、データ線駆動信号としての定電流をデータ線DLに出力する。

30

このような制御により、選択されているライン、つまりカソードドライバ21から選択レベルの走査信号が与えられている1つの走査線SL上の各画素が発光駆動される。順次各ラインが発光駆動されていくことで、フレーム画像表示が実現される。

#### 【0021】

カソードドライバ21は、走査線SLの一端から走査信号を与える走査線駆動部として機能する。

このカソードドライバ21は、Q1出力端子～Q96出力端子が、それぞれ走査線SL1～SL96に接続された状態で配置されている。そして走査方向SDとして示すように、Q1出力端子からQ96出力端子に向かって選択レベルの走査信号を順次出力することで、走査線SL1～SL96を順次選択状態とする走査を行う。

40

#### 【0022】

このような走査を行うために駆動制御部31はカソードドライバ21に対してカソードドライバ制御信号CAを供給する。

カソードドライバ制御信号CAは走査の制御のための各種信号を包括的に示したものであり、本実施の形態の場合、スキャン信号SK、ラッチ信号LAT、クロック信号CLK、ブランкиング信号BKが含まれる。

詳述は避けるがカソードドライバ21は、図示しないシフトレジスタを内蔵し、このシフトレジスタはスキャン信号SKとして与えられる選択レベルの信号をクロック信号CLKに基いてQ1出力端子側からQ96出力端子側に向かうデータ転送を行う。このシフトレジスタの各段の出力がラッチ信号LATで図示しないラッチ回路にラッチされ、その

50

各ラッチ回路の出力が図示しないドライブ段の回路を介して、Q 1 出力端子～Q 9 6 出力端子から各走査線 S L 1～S L 9 6 に出力される。

このような動作によりカソードドライバ 2 1 は、走査線 S L 1～S L 9 6 を順次選択する走査を行うこととなる。

なおブランкиング信号 B K は、画素を発光駆動しないタイミングを規定する信号である。

#### 【0 0 2 3】

またコントローラ I C 2 0 の駆動制御部 3 1 は、フレーム開始信号 I N T を出力する。フレーム開始信号 I N T は、毎フレームで第 1 ラインの走査タイミングで発生される信号である。フレーム開始信号 I N T は駆動制御部 3 1 の内部で用いられる他、フレーム開始タイミングを示す信号として M P U 2 に供給される。

10

#### 【0 0 2 4】

< 2 . 表示上に発生する輝度変化の説明 >

本実施の形態では、表示上に発生する輝度ムラを解消するために、アノードドライバ 3 3 が各データ線 D L に与える定電流を、各ラインの走査タイミング毎に可変制御できるようしている。ここでは、まず表示上に発生する輝度ムラについて説明しておく。

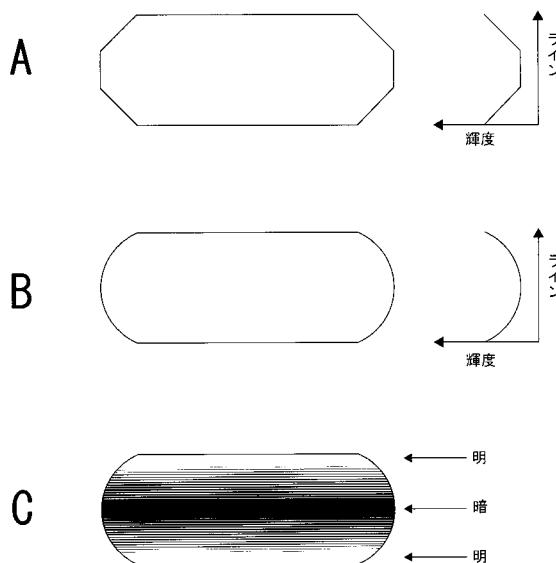

本実施の形態で対処する輝度ムラの原因は、大きく分けて異形パネルで生じる輝度ムラと、点灯率によって生じる輝度ムラがある。

#### 【0 0 2 5】

まず異形パネルの場合を図 2 で説明する。図 2 A、図 2 B は、表示部 1 0 を通常の長方形ではない異形のパネルとした場合の形状例を示している。ここでは八角形パネルや長円形パネルを例示している。図示は省略するが、円形パネル、橢円形パネル、或いは他の多角形パネルなどももちろん想定される。

20

例えばこれらのような異形パネルの場合、各走査線 S L の長さとして差が生ずる。走査線 S L は、長いほど容量負荷が大きく、また配線抵抗も高い。データ線 D L に供給された電流は画素を介して走査線 S L に流れるため、画素に与えられる電流が走査線 S L の長さの影響を受ける。

結果としては図 2 A、図 2 B の右側に示すように、全面を同一輝度の駆動条件で駆動したとしても、走査線 S L が短い領域ほど輝度が高く、走査線 S L が長い領域ほど輝度が低くなる。図 2 C には模式的に輝度ムラが生じている状況を示している。

30

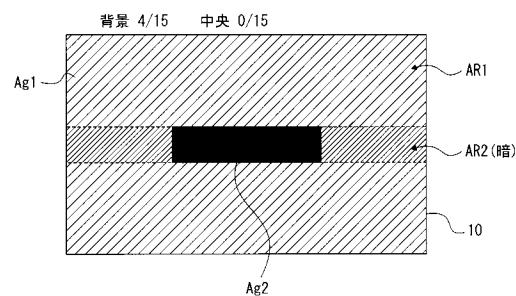

#### 【0 0 2 6】

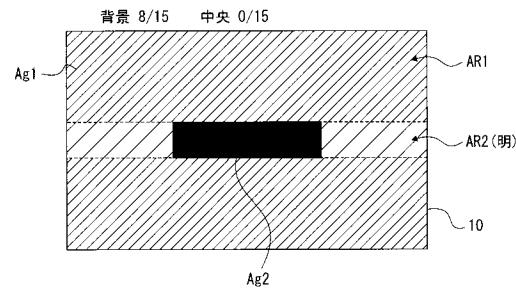

次に通常の長方形状の表示パネルでも生ずる点灯率の差による輝度ムラを図 3、図 4 で説明する。

図 3 A は表示部 1 0 の表示画面の様子を示している。この例は、背景領域 A g 1 の輝度を 4 / 1 5 階調とし、中央領域 A g 2 の輝度を 0 / 1 5 階調（非点灯）とする表示を行っている状態である。つまり中央領域 A g 2 を通るラインは、走査線上の全画素のうち点灯画素数が少なくなっている（点灯率が低い）。なお輝度の階調は例えば 0 / 1 5（非発光）から 1 5 / 1 5（最大輝度発光）までの 1 6 階調であるとする。

例えばこのように中央領域 A g 2 を非点灯画素とし、その周囲の背景領域 A g 1 を比較的低い階調の輝度とした場合に、図中の背景領域 A g 1 内である領域 A R 1 と領域 A R 2 の輝度が異なる状態となる現象が生ずる。即ち破線で示す範囲の領域 A R 2（中央領域 A g 2 の左右の領域）の輝度が他の背景部分よりも若干暗くなつて、輝度ムラが生じてしまう。

40

#### 【0 0 2 7】

また図 3 B は、背景領域 A g 1 の輝度を 8 / 1 5 階調とし、中央領域 A g 2 の輝度を 0 / 1 5 階調（非点灯）とする表示を行っている状態である。上記図 3 A と同じく中央領域 A g を通るラインは点灯率が低い。

例えばこのように中央領域 A g 2 を非点灯画素とし、その周囲の背景領域 A g 1 を比較的高い階調の輝度とした場合に、背景領域 A g 1 内である領域 A R 1 と領域 A R 2 の輝度が異なる状態となる。この場合は、破線で示す範囲の領域 A R 2（中央領域 A g 2 の左右

50

の領域)の輝度が他の背景部分よりも若干明るくなつて、輝度ムラが生じてしまう。

【0028】

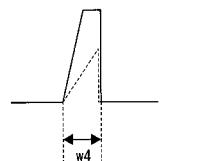

これらの輝度ムラの原因は次のように考えられる。

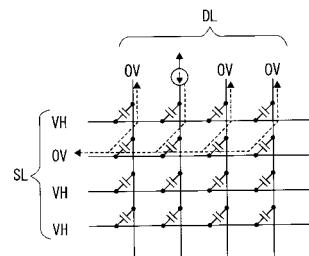

図4Cは、点灯率が高いラインのモデルであり、ここでは全データ線DLに発光駆動電流が与えられている状態を示している。電圧VHの走査線SLは非選択状態であり、0Vとされた走査線SLが選択中のラインとなる。この場合、各データ線に与えられた電流は、破線で示すように選択中の走査線SLに流れる。

【0029】

図4Dは点灯率が低いラインのモデルとして、一部のデータ線DLに電流が与えられ、他のデータ線は0V(例えば接地)とされている状態を示している。

この場合、点灯画素に対応するデータ線DLに与えられる電流は、破線で示すように選択中の走査線SLだけでなく、非点灯画素に対応するデータ線DLにも流れる。このためコンデンサの記号で示す各画素の容量成分のうち、非点灯画素の寄生容量に対する充電も行われることになり負荷が重くなる結果、発光駆動電流の立ち上がりが遅れるという事象が発生する。

【0030】

以上を踏まえて考えると、図3Aのように背景領域Ag1の輝度が比較的低い場合、領域AR1における画素に対する発光駆動電流は図4Aの実線、領域AR2における画素に対する発光駆動電流は図4Aの破線のようになる。

つまり点灯率が高いラインの点灯画素に対する発光駆動電流は立ち上がりが早くなり、点灯率が低いラインの点灯画素に対する発光駆動電流は立ち上がりが遅くなる。

ここで定電流印加の時間長w4は、例えば4/15階調としての長さである。この波形からわかるように領域AR2の画素に対する発光駆動電流は十分に立ち上がらず、この結果、当該領域の輝度が低下する。

【0031】

一方、図3Bのように背景領域Ag1の輝度が比較的高い場合、領域AR1における画素に対する発光駆動電流は図4Bの実線、領域AR2における画素に対する発光駆動電流は図4Bの破線のようになる。

つまり点灯率が高いラインの点灯画素に対する発光駆動電流は早く立ち上がって、例えば8/15階調に相当する時間長w8だけ定電流を維持する。点灯率が低いラインの点灯画素に対する発光駆動電流は、上記図3Aの場合と同様に立ち上がりが遅いのであるが、電流供給時間長が長くなると、定電流値以上にオーバーシュートしてしまう現象が生じている。このオーバーシュートにより当該領域の輝度が高くなる。

【0032】

以上のように、走査線の長さの差や点灯率の差によって輝度ムラが生ずる。本実施の形態では、これらに対応して各走査線SLの走査タイミング毎にデータ線DLに与える定電流値を制御するものである。

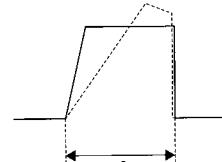

【0033】

<3.表示駆動装置の構成及び動作>

以下、データ線DLに対する定電流駆動制御について詳細に説明する。

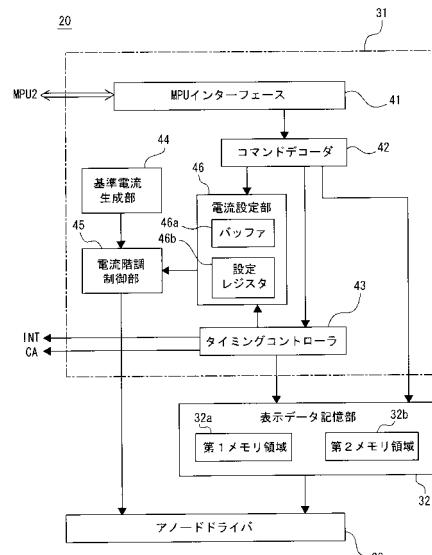

図5は、表示駆動装置として機能するコントローラIC20の内部を示しているが、特に駆動制御部31内を詳細に示したものである。

駆動制御部31内には、MPUインターフェース41、コマンドデコーダ42、タイミングコントローラ43、基準電流生成部44、電流階調制御部45、電流設定部46が設けられる。

【0034】

MPUインターフェース41は、上述したMPU2との間の各種通信を行うインターフェース回路部である。具体的には表示データやコマンド信号の送受信がMPUインターフェース41とMPU2の間で行われる。

コマンドデコーダ42は、MPU2から送信されてきたコマンド信号等を図示しない内

部レジスタに取り込むと共に、コマンド信号のデコードを行う。そしてコマンドデコーダ42は、取り込んだコマンド信号の内容に応じた動作を実行させるべく、タイミングコントローラ43に必要な通知を行う。またコマンドデコーダ42は取り込んだ表示データを表示データ記憶部32に記憶させる。

#### 【0035】

なお、表示データ記憶部32には、例えばそれぞれ1フレーム分の表示データの記憶領域として第1メモリ領域32a、第2メモリ領域32bが用意されている。

本実施の形態では、表示部10に、1フレームの静止画データを切り換えて表示していくことを想定する。即ちMPU2から供給された静止画としての1フレームの表示データは、例えば第1メモリ領域32aに格納された状態で、その表示データに基づく表示が実行される。

その後、表示内容を切り換える際には、切替タイミングに先立って、次の表示データが第2メモリ領域32bに記憶されていく。そして切替タイミングで、第2メモリ領域32bの表示データが表示対象のデータとして使用されて表示駆動が行われる。

さらにその後、表示内容を切り換える際には、切替タイミングに先立って、次の表示データが第1メモリ領域32aに記憶され、所定のタイミングで表示対象が第1メモリ領域32aの表示データに変更される。

このように第1メモリ領域32a、第2メモリ領域32bが交互に使用されることで、MPU2からの表示データの転送時間によらず、実際の表示上での表示内容の切替が時間遅れなくスムースに行われる。

#### 【0036】

タイミングコントローラ43は、表示部10の走査線SL、データ線DLの駆動タイミングを設定する。

即ちタイミングコントローラ43は上述したカソードドライバ制御信号CAを出力して、カソードドライバ21によるライン走査を実行させる。

またタイミングコントローラ43はアノードドライバ33に対しての表示データ記憶部32からの表示データの転送制御を行い、アノードドライバ33が各走査タイミングでの各データ線DL1～DL128に定電流を供給する時間長が、表示データの該当画素の階調に応じた時間長となるようとする。

またタイミングコントローラ43はフレーム開始信号INTを生成する。

#### 【0037】

基準電流生成部44は、データ線駆動信号の電流値の基準となる基準電流を生成する。

電流階調制御部45は、基準電流生成部44で生成された基準電流を、設定された電流階調値に調整する。特に本実施の形態では、電流階調制御部45による基準電流の調整によって、各走査線SL1～SL96の走査タイミング毎に、各データ線DL1～DL128に与える定電流値を変更制御することが可能とされている。

#### 【0038】

電流階調制御部45による定電流値の調整は、電流設定部46に記憶された電流階調値に基づいて行われる。

電流設定部46の設定レジスタ46bには各走査線SL1～SL96のそれぞれについての電流階調値が記憶されている。

#### 【0039】

図6に設定レジスタ46bに記憶される電流階調値の例を示す。なお設定レジスタ46bに実際に記憶されるのは図6におけるレジスタの値R1～R6であり、タイミングと電流階調値は説明のために示しているものである。タイミングL1～L96とは、走査線SL1～SL96の各走査タイミングのことである。

電流階調値の設定として、タイミングL1～L96の各ラインの走査タイミング毎の電流階調値が示される。例えばタイミングL1の電流階調値が3Fh（“h”を付した数字は16進表記：（ ）内は10進表記）、タイミングL2の電流階調値が3Ch・・・などとされる。各タイミングの電流階調値の6ビットは、レジスタR1～R6に1ビットづ

つ記憶される。即ち、6ビットの電流階調値におけるビット0がレジスタR1に、ビット1がレジスタR2に、・・・ビット5がレジスタR6にそれぞれ記憶される。

なおレジスタR1～R6の各値は1ビットで、設定レジスタ46bにはタイミングL1～L96の各走査タイミングに対応する値が記憶される。

図5の電流設定部46の設定レジスタ46b全体としては、 $96 \times 6 = 576$ ビットを、1つの表示データに対する電流階調値として記憶することになる。

#### 【0040】

なお電流設定部46におけるバッファ46aは、設定レジスタ46bの電流階調値を書き換える際に、MPU2から提供される新たな電流階調値を一時保存するために用いられるもので、設定レジスタ46bと同じく $96 \times 6 = 576$ ビットの領域が用意される。

10

#### 【0041】

電流階調制御部45は、各走査線SL1～SL96の走査タイミング毎に、設定レジスタ46bに記憶された該当ラインの電流階調値に相当する電流値の定電流を得る。そしてその定電流をアノードドライバ33に供給する。

アノードドライバ33は、このような定電流を、各データ線DL1～DL128に対して、表示データに示されるそれぞれの画素の階調値に従った時間長だけ供給する。

#### 【0042】

図7で、基準電流生成部44、電流階調制御部45、及びアノードドライバ33の回路構成例を説明する。

基準電流生成部44は差動アンプ51、PチャネルのFET(Field Effect Transistor)52, 53、NチャネルのFET54、及び抵抗R1を有する。

20

差動アンプ51の反転入力には所定電圧V1が印加され、非反転入力は抵抗R1を介して接地されている。差動アンプ51の出力端はFET52のゲートに接続され、FET52のソースは電圧Vccに接続され、FET52のドレインは差動アンプ51の非反転入力に接続される。この構成により、FET52のソース-ドレイン間に基準電流Isが流れる。

#### 【0043】

FET53はゲートがFET52のゲートに接続され、ソースが電圧Vccに接続され、ドレインがFET54のドレインとゲートに接続されている。この場合、FET52とFET53がカレントミラー構成を探るため、FET53に基準電流Isと同じ電流値の基準電流Is'が流れる。そしてFET53, 54が直列接続されていることで、基準電流Is'がFET54のドレイン-ソース間にも流れる。

30

#### 【0044】

電流階調制御部45は、NチャネルのFET61～66、同じくNチャネルのFET71～76、PチャネルのFET80を有する。

FET80のソースには電圧VHが印加され、FET80はドレインとソースが接続されるとともに、そのドレインはFET61～66の全てのドレインに接続される。FET61～66のソースは、それぞれFET71～76のドレインに接続される。

この場合に、上述の基準電流生成部44のFET54のゲートとドレインが接続され、この接続点に、FET61～66のゲートが接続されている構成により、FET54とFET61～66のそれぞれがカレントミラー構成を探る。

40

#### 【0045】

ここでFET61～66は、トランジスタサイズ(ゲート幅W)が異なる設計とされて、電流重み付け設定がされている。即ちFET61～66のそれぞれのゲート幅Wは、FET54のゲート幅の1倍、2倍、4倍、8倍、16倍、32倍とされ、これにより各FET61～66のドレイン-ソース電流の重み付けがなされている。

即ちFET61～66のドレイン-ソース電流をI1, I2, I4, I8, I16, I32とすると、 $I1 = Is'$ 、 $I2 = 2 \cdot Is'$ 、 $I4 = 4 \cdot Is'$ 、 $I8 = 8 \cdot Is'$ 、 $I16 = 16 \cdot Is'$ 、 $I32 = 32 \cdot Is'$ となる。

#### 【0046】

50

このようなFET61～66に対して、FET71～76はスイッチとして機能する。FET71～76のゲートには、それぞれ設定レジスタ46bのレジスタR1～R6の記憶値に応じた電圧が印加される。従ってFET71～76は図6に示した電流階調値“1”“0”によりオン／オフされる。

そしてFET71～76のうちでオンされたFETの系統で、FET61～66の重み付けされたドレイン・ソース電流が流れる。FET80に流れる電流は、それらの電流の和としての電流値となる。

#### 【0047】

図6の例に沿って述べると、タイミングL1の期間は、レジスタR1～R6における“111111”の値によってFET71～76が制御される。この場合FET71～76は全てオンとなり、FET80のソース・ドレイン電流はI1+I2+I4+I8+I16+I32で階調値63の電流値となる。10

またタイミングL2の期間は、レジスタR1～R6における“001111”の値によってFET71～76が制御される。この場合FET71、72はオフ、FET73～76は全てオンとなり、FET80のソース・ドレイン電流はI4+I8+I16+I32で階調値60の電流値となる。

#### 【0048】

アノードドライバ33には、各データ線DL1～DL128に対応してそれぞれ、PチャネルのFET81(81-1～81-128), 82(82-1～82-128)とNチャネルのFET83(83-1～83-128)によるデータ線駆動回路が形成されている。なお、表示データに対応する階調制御(定電流の出力時間長制御)のための信号Sa, Sbを生成する回路構成は図示を省略している。20

FET81のソースには電圧VHが印加され、ドレインはFET82のソースに接続される。またFET82のドレインとFET83のドレインが接続されている。FET83のソースは接地されている。

FET82, 83の接続点が、データ線DL(DL1～DL128)に接続される。

#### 【0049】

この場合に、上述の電流階調制御部45におけるFET80はゲートとドレインが接続され、この接続点に、FET81-1～81-128の各ゲートが接続されている構成により、FET80と各FET81-1～81-128のそれぞれがカレントミラー構成を採る。従って各データ線DL1～DL128についてのデータ線駆動回路には、上述のFET80のソース・ドレイン電流と同じ電流値の定電流が流れる構成となっている。30

#### 【0050】

ここでFET82-1～82-128は、それぞれ信号Sa(Sa1～Sa128)によってオン／オフされる。またFET83-1～83-128は、それぞれ信号Sb(Sb1～Sb128)によってオン／オフされる。信号Sa, Sbは表示データによる画素の階調に応じた時間長だけ定電流を出力するための制御信号であり、表示データ(各画素データ)に応じて時間長設定されたパルス信号である。

信号Sa, SbによってFET82がオン、FET83がオフされると、FET82のドレイン電流がデータ線DLに供給される。

また信号Sa, SbによってFET82がオフ、FET83がオンされると、データ線DLが接地されることとなる。

従って表示データに基づいて信号Sa, Sbが生成され、FET82, 83が制御されることで、表示データで示される階調値に応じた時間長だけ、データ線DLに、電流階調制御部45で電流値の調整された定電流が供給される。

#### 【0051】

このような構成により、各走査線SL1～SL96の走査タイミング毎に電流値が調整されたデータ線駆動が実現される。

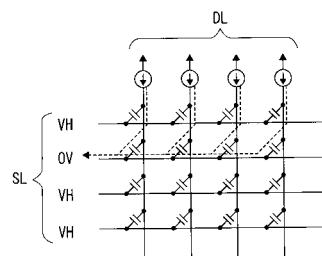

図8に動作波形を示す。フレーム開始信号INTは、フレームの先頭ライン(走査線SL1の走査タイミング)でハイレベル(Hレベル)とされる。

10

20

30

40

50

プランキング信号 B K は、各走査線 S L 1 ~ S L 9 6 の走査期間の間の期間で H レベルとされる。このプランキング信号の H レベル期間が、画素を発光駆動しないプランキング期間となる。プランキング期間中、全ての走査線 S L はロウレベル ( L レベル ) とされ、全てのデータ線 D L は接地される。

#### 【 0 0 5 2 】

この図 8 では、走査線 S L 1 ~ S L 9 6 のうちで走査線 S L 1 ~ S L 4 と、データ線 D L 1 ~ D L 1 2 8 のうちの或るデータ線 D L x , D L y を例示している。

走査線 S L 1 ~ S L 4 ・・・ は、フレーム開始タイミングから順次選択状態とされる ( L レベルが選択レベル )。例えばタイミング L 1 は走査線 S L 1 の走査タイミング、タイミング L 2 は走査線 S L 2 の走査タイミングとなる。

なおプランキング期間は全走査線 S L が L レベルとされる例で示しているが、プランキング期間に全走査線 S L を H レベルに固定する駆動方式もある。

データ線 D L x , D L y は、各走査タイミングで、それぞれ該当ラインの画素の階調値に応じた時間長だけ、定電流出力を行う。図 8 のデータ線 D L x , D L y の H レベル期間は、定電流出力されている期間を示す。

#### 【 0 0 5 3 】

ここで、上述の図 6 の例のように電流階調値が設定されているとすると、アノードドライバ 3 3 からのデータ線 D L 1 ~ D L 1 2 8 への定電流出力は、図 8 のアノードドライバ出力電流として示すように、タイミング L 1 では 3 F h 階調の電流値、タイミング L 2 では 3 C h 階調の電流値、タイミング L 3 では 3 F h 階調の電流値・・・ というように可変制御される。

#### 【 0 0 5 4 】

このようにデータ線 D L の電流値が走査タイミング毎に制御されることで、図 2 又は図 3 , 図 4 で説明した輝度ムラを低減又は解消できる。

即ち異型パネルとして形成されて走査線 S L の長さに差がある場合、長い走査線 S L の走査タイミングでは高めの電流階調値とし、短い走査線 S L の走査タイミングでは低めの電流階調値とすることで、データ線 D L の電流値によって図 2 C に示したような輝度ムラを解消する方向の輝度補正を行うことができる。

また画面内容に応じての各ラインでの点灯率の差に起因して輝度ムラが生ずる場合に関しては、点灯率の差や、階調値に応じて、各ラインの走査タイミングに適切な電流階調値を設定する。例えば図 3 A の例の場合は、領域 A R 2 の画素が属するラインは輝度が低下する状況になるため、電流階調値を高くする。一方図 3 B の例の場合は、領域 A R 2 の画素が属するラインは輝度が上昇する状況になるため、電流階調値を低くする。このように画面内容に応じて各ラインの走査タイミングでのデータ線 D L の電流値を調整することで、輝度ムラを解消する方向の輝度補正を行うことができる。

#### 【 0 0 5 5 】

なお図 8 の波形に示されるように、アノードドライバ 3 3 が出力する定電流値の切り替えは、プランキング信号 B K で規定されるプランキング期間に行なうようにしている。プランキング期間は、全ての走査線 S L が L レベルにリセットされる。またプランキング期間はアノードドライバ 3 3 からデータ線 D L への定電流供給も行われない。即ちプランキング期間では、図 7 の回路において F E T 8 2 はオフ、F E T 8 3 はオンとなるように信号 S a , S b が生成されている。

#### 【 0 0 5 6 】

電流階調制御部 4 5 の F E T 7 1 ~ 7 6 のゲートに与えられる電流階調値の切り替えは、このようなプランキング信号 B K のタイミングで行われるようにする。

走査線 S L がリセット状態でデータ線 D L に電流供給がオフとされるプランキング期間は、画面表示のための発光を行っていない期間である。このようなプランキング期間に定電流値の切り替えを行うことで、切り替え動作が表示画像品質に影響を与えないようにすることができる。例えば電流値の切り替え時の過渡的な電流変動が表示画像品質を低下させないようにしている。

10

20

30

40

50

## 【0057】

<4. 表示画像の切り替え>

ところで、異型パネルの走査線長の差に起因する輝度ムラに関しては、設定レジスタ46bに記憶する電流階調値は固定的でよい。即ち、設定レジスタ46bに記憶する例えは6ビット×96ライン分の電流階調値は書き換える必要はない。

しかし、点灯率の差による輝度ムラは、画像内容により、ライン毎の適切な電流階調値が異なるものとなるため、表示データの切り替えに応じて設定レジスタ46bの電流階調値の書き換えを行うことが必要である。

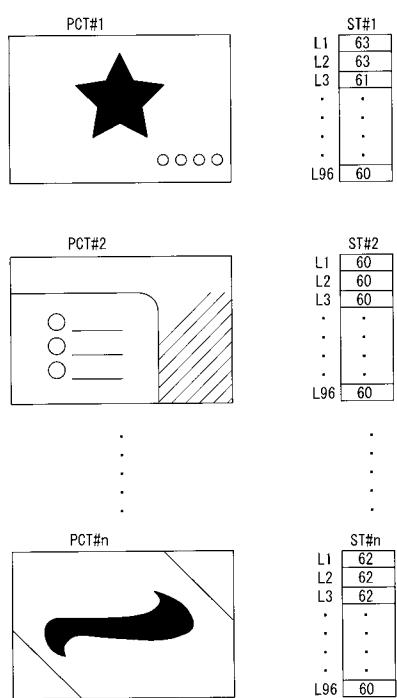

例えば実施の形態の表示装置は、図9に示す画像PCT#1～PCT#nのn種類の画像の表示が想定されているとする。MPU2は、これらの画像PCT#1～PCT#nとしての表示データを選択してコントローラIC20に供給し、表示動作を実行させる。

## 【0058】

この場合、例えばMPU2は、画像PCT#1～PCT#nに応じた電流階調値ST#1～ST#nを保持しておく。電流階調値ST#1～ST#nとしてのライン毎の各値自体は、画像PCT#1～PCT#nの応じて適切な値を予め設定しておき、MPU2に、その電流階調値ST1～ST#nを記憶させておけばよい。

MPU2は、表示画像を切り替えるときには、電流階調値も切り替えるようにコントローラIC20に指示する。例えば画像PCT#2を表示させるために、画像PCT#2の表示データをコントローラIC20に転送する際には、電流階調値ST#2も転送する。このようにすることで、コントローラIC20内で、画像内容に応じて適切に輝度ムラを低減又は解消できる定電流値可変制御が可能となる。

## 【0059】

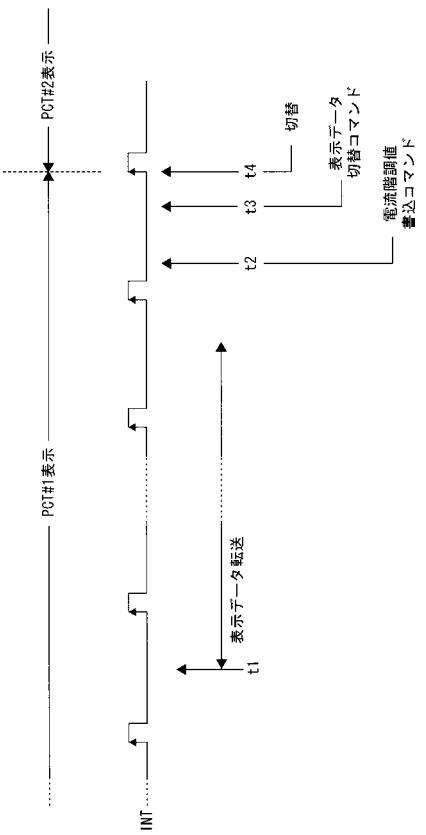

表示画像の切換の際の動作を図10、図11で説明する。

図10は表示画像切換の際のMPU2とコントローラIC20のやりとりを模式的に示している。例えば現在、画像PCT#1の表示を行っており、これを画像PCT#2の表示に切り替えるとする。

実際の切り替えタイミングは時点t4である。これより前の時点では、フレーム開始信号INTのタイミングで開始される各フレームで画像PCT#1の表示が行われている。

この場合MPU2は、切り替えタイミングの時点t4に先だって、或る時点t1から画像PCT#2の表示データの転送を行う。表示データのデータ量が多いためである。

コントローラIC20の駆動制御部31では、コマンドデコーダ42が転送してきた表示データを取り込み、これを表示データ記憶部32に記憶させる。このとき、例えばその時点で画像PCT#1の表示データが第1メモリ領域32aに格納され、これに応じてアノードドライバ33が動作しているとすると、今回転送してきた表示データは第2メモリ領域32bに格納していく。これにより或る画像の表示継続中に次の表示データの取り込みが可能となる。

## 【0060】

表示画像切換の直前のフレーム期間では、まず時点t2にMPU2は電流階調値書込コマンドを送信する。このときMPU2は画像PCT#2に対応する電流階調値ST#2も送信する。電流階調値は6×96ビットであり、さほどのデータサイズではないため、特に事前に転送しておく必要はない。

駆動制御部31では、コマンドデコーダ42が当該コマンドに応じて、電流階調値ST#2を電流設定部46に書き込む。但しこの場合、バッファ46aに書き込むようにする。またコマンドデコーダ42から、タイミングコントローラ43に当該コマンド受信が通知される。

続いて時点t3にMPU2は表示データ切替コマンドを送信する。コマンドデコーダ42はこれを受信・デコードし、タイミングコントローラ43に通知する。

## 【0061】

実際の表示データ切替はフレーム開始タイミングに行うため、タイミングコントローラ43は当該表示データ切替コマンドの直後のフレーム開始信号INTのタイミングまで待

10

20

30

40

50

機する。そして受信していた表示データ切替コマンドに対応する処理として、フレーム開始信号がLレベルからHレベルになるタイミング(時点  $t_4$ )に、表示データ記憶部32からアノードドライバ33への表示データの転送元を、第1メモリ領域32aから第2メモリ領域32bに切り替えるように制御する。またこの時点でタイミングコントローラ43は、受信していた電流階調値書き込みコマンドに対応する処理として、電流設定部46に対して、バッファ46aに格納していた電流階調値ST#2を設定レジスタ46bに書き込むように制御する。

【0062】

このような処理により時点  $t_4$  以降のフレームでは、画像PCT#2の表示が実行され、またその際に各走査線SLの走査タイミング毎に、電流階調値ST#2に応じたデータ線DLの電流値制御が行われる。もちろん電流階調値ST#2は、画像PCT#2に対応してライン毎の電流階調値を設定したものであるため、表示上で輝度ムラは低減又は解消されたものとなる。

10

【0063】

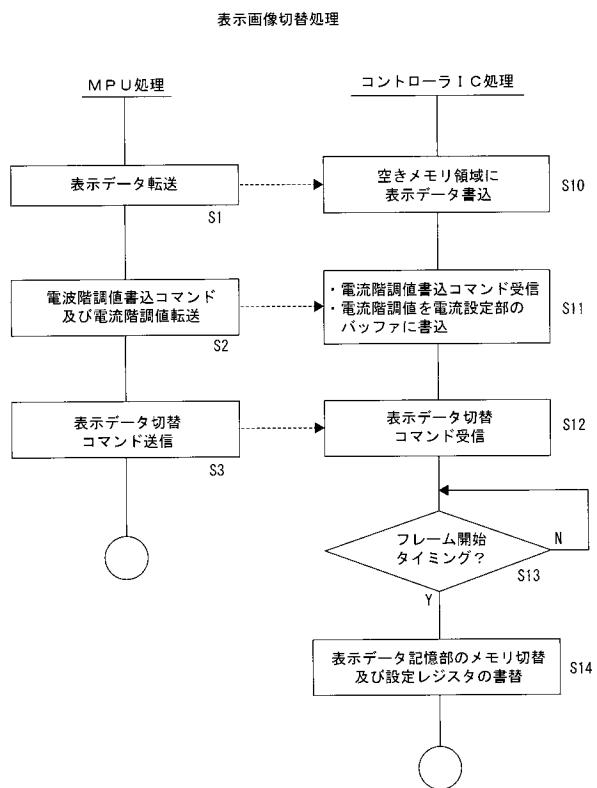

図11は以上の動作のためのMPU2の処理とコントローラIC20の処理を示したものである。

表示画像切替を行う場合、MPU2はステップS1で次の画像の表示データの転送を行う。コントローラIC20側では、ステップS10で転送されてくる表示データを、表示データ記憶部32における第1, 第2メモリ領域32a, 32bのうちの空いている方に格納させていく。

20

【0064】

表示データの転送が完了したら、MPU2はステップS2として電流階調値書き込みコマンドと電流階調値を転送する。コントローラIC20はステップS11で電流階調値書き込みコマンドを受信するとともに、転送されてきた電流階調値を電流設定部46のバッファ46aに書き込む。

さらに同じフレーム期間内にMPU2はステップS3として表示データ切替コマンドを送信する。コントローラIC20では、ステップS12で表示データ切替コマンドを受信する。

【0065】

そしてコントローラIC20は、ステップS13としてフレーム開始タイミングを待機する。フレーム開始タイミングとなったらステップS14で、表示データ切替コマンドと電流階調値書き込みコマンドに応じた処理を実行する。即ち上述のように表示データ記憶部32からアノードドライバ33への表示データの転送元を、第1メモリ領域32aと第2メモリ領域32bの間で切り替え、また電流設定部46のバッファ46aに格納した電流階調値を設定レジスタ46bに書き込むように制御する。

30

【0066】

<5. 実施の形態の効果及び変形例>

以上のとおり実施の形態では、表示駆動装置としてのコントローラIC20は、列方向に並ぶ複数の画素に共通に接続されたデータ線DLと、行方向に並ぶ複数の画素に共通に接続された走査線SLとが、それぞれ複数配設され、データ線DLと走査線SLの各交差点に対応して画素が形成されている表示部10に対して、表示データに基づく表示駆動を行う。このようなコントローラIC20には、表示データのフレームを構成する各行について設定された電流階調値を記憶する電流設定部46と、1フレーム内の各行の走査タイミング毎に、電流設定部46に記憶された該当行の電流階調値とされた定電流を生成する電流階調制御部45と、データ線DLのそれぞれに対して、表示データで規定される画素の階調値に応じた時間長だけ、電流階調制御部45からの定電流を供給するアノードドライバ33(データ線駆動部)を備えている。

40

このような構成により、各走査線SLの走査タイミング毎に各データ線DLに与える定電流値を制御する。従って各ラインについての定電流値が、電流階調値として表示ムラを解消できる適切な値に設定されて記憶されていることで、ライン毎の点灯率や発光階調の

50

影響による輝度ムラ、或いは異型パネルにおける各走査線 S L の長さの差による輝度ムラを解消又は低減することができる。もって表示画像の品質を向上させることができる。

なお、異型パネルの場合に、各ラインの点灯率の差によって生じる輝度ムラの補正も、このような手法で実現できることはいうまでもない。画像毎に電流階調値が設定されればよく、通常の長方形パネルの場合と同様に考えることができる。

#### 【0067】

また電流階調制御部 45 は、1 フレーム内の各行の走査タイミング毎の定電流の電流階調値の切替を、各行の走査期間の間のブランкиング期間において実行している。これによって、データ線 D L 上の定電流値の変動の影響を表示画像に及ぼさないようにでき、高品質な画像を維持できる。

10

#### 【0068】

また電流設定部 46 ( 設定レジスタ 46 b ) に記憶される電流階調値は、表示部 10 で表示する表示データの切替に対応して書き換えられるようにしている。1 フレームにおける各ラインの点灯率は画像によって異なり、画像内容によって、適切に輝度ムラを補正するための各ラインの最適な電流階調値は異なる。そこで表示する画像に応じて電流階調値を用意しておき、表示データの切替に対応して電流階調値も書き換えることで、常に適切な輝度ムラの補正が実現できる。

またこの場合に、電流階調値の書き換えは、フレーム開始タイミングで行われるようにしている。表示画像の切替をフレーム開始タイミングで行うため、同時に書き換えることが輝度ムラの補正効果を得るために最適となる。

20

#### 【0069】

また電流階調制御部 45 は、図 7 に示したように電流値について異なる重み付けをされた複数のトランジスタ ( F E T 6 1 ~ 6 6 ) のうちの 1 つ以上を、電流設定部 46 ( 設定レジスタ 46 b におけるレジスタ R 1 ~ R 6 ) に記憶された電流階調値に基づいて選択し、選択されたトランジスタの電流値の和に相当する電流値 ( F E T 8 0 のドレイン - ソース電流値 ) として、電流階調値に相当する定電流を生成している。このような電流階調値に応じたトランジスタの選択により、電流階調値に応じた定電流を容易に発生させることができ、本実施の形態のデータ線駆動に適している。

#### 【0070】

またこのようなコントローラ I C 20 を有する実施の形態の表示装置 1 は、輝度ムラが低減又は解消された高品質な表示を実現する表示装置となる。

30

#### 【0071】

以上、実施の形態について説明したが、本発明の表示装置や表示駆動装置、表示駆動方法は実施の形態に限定されず多様な変形例が考えられる。

電流階調値を記憶する設定レジスタ 46 b は、実際のハードウェア形態としてレジスタ構成が用いられてもよいが、D - R A M ( Dynamic Random Access Memory ) 、 S - R A M ( Static Random Access Memory ) 、フラッシュメモリなどのメモリが用いられてもよい。また異型パネル対応のために電流階調値の書き換えが必要ない場合、設定レジスタ 46 b の機能を R O M ( Read Only Memory ) により実現してもよい。

40

#### 【0072】

図 9 で説明した各種の画像 P C T # 1 ~ P C T # n に応じた電流階調値 S T # 1 ~ S T # n は M P U 2 が記憶し、必要に応じてコントローラ I C 20 に転送するものとしたが、電流階調値 S T # 1 ~ S T # n をコントローラ I C 20 が内部に記憶しておいてもよい。その場合、コントローラ I C 20 は表示データの切替に応じて電流階調値を選択して設定レジスタ 46 b に書き込むようにする。

#### 【0073】

また本発明は O L E D を用いる表示装置だけでなく、他の種の表示装置でも適用可能である。特に電流駆動による自発光素子を用いた表示装置に好適である。

#### 【符号の説明】

#### 【0074】

50

- 1 ... 表示装置

2 ... MPU

1 0 ... 表示部

2 0 ... コントローラ I C

2 1 ... カソードドライバ

3 1 ... 駆動制御部

3 2 ... 表示データ記憶部

3 3 ... アノードドライバ

4 3 ... タイミングコントローラ

4 4 ... 基準電流生成部

4 5 ... 電流階調制御部

4 6 ... 電流設定部

4 6 b ... 設定レジスタ

10

【図1】

【図2】

【図3】

A

B

【図5】

【図4】

A

B

C

D

【図6】

| タイミング | 電流階調値    | レジスタの値 |    |    |    |    |    |

|-------|----------|--------|----|----|----|----|----|

|       |          | R1     | R2 | R3 | R4 | R5 | R6 |

| L1    | 3Fh (63) | 1      | 1  | 1  | 1  | 1  | 1  |

| L2    | 3Ch (60) | 0      | 0  | 1  | 1  | 1  | 1  |

| L3    | 3Fh (63) | 1      | 1  | 1  | 1  | 1  | 1  |

| L4    | 3Ch (60) | 0      | 0  | 1  | 1  | 1  | 1  |

| :     | :        | :      | :  | :  | :  | :  | :  |

| L96   | 3Fh (63) | 1      | 1  | 1  | 1  | 1  | 1  |

【図7】

【 図 8 】

【図9】

【 図 1 0 】

【図 11】

## フロントページの続き

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|--------------|---------|--------------|

|              | G 0 9 G | 3/20 6 1 2 T |

|              | G 0 9 G | 3/20 6 2 3 D |

|              | G 0 9 G | 3/20 6 2 3 C |

|              | G 0 9 G | 3/20 6 3 1 V |

|              | H 0 5 B | 33/14 A      |

(72)発明者 杉本 照和

千葉県茂原市大芝 6 2 9 双葉電子工業株式会社内

(72)発明者 川名 啓資

千葉県茂原市大芝 6 2 9 双葉電子工業株式会社内

(72)発明者 神山 幸夫

千葉県茂原市大芝 6 2 9 双葉電子工業株式会社内

(72)発明者 岩田 和弘

千葉県茂原市大芝 6 2 9 双葉電子工業株式会社内

F ターム(参考) 3K107 AA01 BB01 CC33 HH04

5C080 AA06 BB05 DD05 EE01 EE28 FF07 HH09 JJ01 JJ02 JJ04

JJ07

5C380 AA01 AB05 AB50 BA19 BA20 BA31 BA45 BB01 BB02 BC02

CA08 CA13 CB01 CE19 CE21 CF02 CF05 CF06 CF07 CF09

CF22 CF26 CF28 CF41 CF62 CF64 DA02 DA08 DA32 DA33

DA35 DA41 DA46 DA49