(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5575378号

(P5575378)

(45) 発行日 平成26年8月20日(2014.8.20)

(24) 登録日 平成26年7月11日(2014.7.11)

(51) Int.CI.

H01L 33/38 (2010.01)

F 1

H01L 33/00 210

請求項の数 25 (全 12 頁)

(21) 出願番号 特願2008-188716 (P2008-188716)

(22) 出願日 平成20年7月22日 (2008.7.22)

(65) 公開番号 特開2009-188370 (P2009-188370A)

(43) 公開日 平成21年8月20日 (2009.8.20)

審査請求日 平成23年7月22日 (2011.7.22)

(31) 優先権主張番号 10-2008-0010784

(32) 優先日 平成20年2月1日 (2008.2.1)

(33) 優先権主張国 韓国 (KR)

前置審査

(73) 特許権者 506029004

ソウル バイオシス カンパニー リミテッド

SEOUL VIOSYS CO., LTD.

大韓民国 425-851 キョンギード

アンサンーシ ダンウォン-グ ウォン

シードン 727-5 ブロック 1-3

6

(74) 代理人 110000408

特許業務法人高橋・林アンドパートナーズ

最終頁に続く

(54) 【発明の名称】発光ダイオード及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に n 型半導体層を形成する段階と；

前記 n 型半導体層上に活性層を形成する段階と；

前記活性層上に p 型半導体層を形成する段階と；

エッチング面が傾斜面に形成されるように前記 n 型半導体層をエッチングする段階と；

前記 p 型半導体層上に p - 電極を形成する段階と；

エッチングされた前記 n 型半導体層と p - 電極が形成されていない前記 p 型半導体層の一部にかけて n - 電極を形成する段階と；

を含む発光ダイオードの製造方法であり、

前記発光ダイオードの製造方法は、前記 n - 電極が形成される前に、n - 電極が形成される n 型半導体層、活性層を含む傾斜面、p 型半導体層の一部に、前記 n - 電極が形成される前記 n 型半導体層、前記活性層を含む前記傾斜面、前記 p 型半導体層の一部にプラズマ表面処理を行い表面に、絶縁膜を形成する段階をさらに含み、

前記発光ダイオードに逆方向に静電気が印加された場合、前記発光ダイオードの接触電位差によって形成される内部抵抗よりも、前記エッチングされた前記 n 型半導体層および p - 型半導体層の一部にかけて形成された前記 n - 電極と前記 p 型半導体層との間の電気抵抗が小さくなり、

前記発光ダイオードの製造方法は、前記 n - 電極を形成する段階以後に、前記 p - 電極上に反射板を形成し、前記反射板と前記 n - 電極をサブマウントに付着してフリップチップ

10

20

形態で構成することをさらに含むことを特徴とする発光ダイオードの製造方法。

【請求項 2】

前記エッチング段階は、加熱によって円形に再形成化(thermal reflow)されたフォトレジストをエッチングマスクとして用いて乾式エッチングすることで、エッチング面が傾斜面に形成されることを特徴とする請求項1に記載の発光ダイオードの製造方法。

【請求項 3】

前記n-電極が形成される前に、プラズマ処理を通して半導体層の電気的特性を変化させるプラズマ処理段階をさらに含むことを特徴とする請求項1に記載の発光ダイオードの製造方法。

10

【請求項 4】

前記プラズマ処理する段階後に、前記n-電極が形成されるn型半導体層、活性層を含む傾斜面、p型半導体層の一部に絶縁膜を形成する段階をさらに含むことを特徴とする請求項3に記載の発光ダイオードの製造方法。

【請求項 5】

前記n型半導体層、前記活性層及び前記p型半導体層は、窒化物系半導体で構成されることを特徴とする請求項1に記載の発光ダイオードの製造方法。

20

【請求項 6】

前記プラズマ処理段階のガスは、N、NO、NH、He、Ne、Arからなるグループから選択された何れか一つまたは二つ以上の組み合わせで構成されたことを特徴とする請求項3に記載の発光ダイオードの製造方法。

【請求項 7】

前記プラズマ処理段階中に印加されるプラズマパワーによって、表面処理された半導体層の電気特性が変わることを特徴とする請求項3に記載の発光ダイオードの製造方法。

【請求項 8】

前記プラズマ処理段階中のプラズマ処理時間によって、表面処理された半導体層の電気特性が変わることを特徴とする請求項3に記載の発光ダイオードの製造方法。

30

【請求項 9】

前記プラズマ処理段階中に印加されるプラズマパワーと処理時間によって、表面処理された半導体層の電気特性が変わることを特徴とする請求項3に記載の発光ダイオードの製造方法。

【請求項 10】

前記n-電極は、Ti、Al、Pt、Pd、Au、Cr、Fe、Cu、Moを含むグループから選択された何れか一つまたは二つ以上の組み合わせであることを特徴とする請求項1に記載の発光ダイオードの製造方法。

【請求項 11】

前記n-電極の形成によって、前記活性層と並列に接続される電流通路を形成することを特徴とする請求項1に記載の発光ダイオードの製造方法。

【請求項 12】

半導体層と接触される前記n-電極の接触面積の大きさを変化させ、前記n-電極と半導体層との接触抵抗を変化させる段階をさらに含むことを特徴とする請求項1に記載の発光ダイオードの製造方法。

40

【請求項 13】

基板と；

前記基板上に形成されたn型半導体層と；

前記n型半導体層上に形成された活性層と；

前記活性層上に形成されたp型半導体層と；

前記p型半導体層上に形成されたp-電極と；

エッチングで露出された前記n型半導体層と前記p型半導体層の一部にかけて形成され、前記n型半導体層、前記活性層を含む前記傾斜面、前記p型半導体層の一部にプラズマ

50

表面処理を行い形成された絶縁膜を介したn-電極と；を含むことを特徴とする発光ダイオードであり、

前記発光ダイオードに逆方向に静電気が印加された場合、前記発光ダイオードの接触電位差によって形成される内部抵抗よりも、前記エッチングされた前記n型半導体層およびp型半導体層の一部にかけて形成された前記n-電極と前記p型半導体層との間の電気抵抗が小さくなることを特徴とする発光ダイオード。

**【請求項14】**

前記露出されたn型半導体層と前記p型半導体層は、エッチング傾斜面を有し、前記傾斜面に活性層が露出されたことを特徴とする請求項13に記載の発光ダイオード。 10

**【請求項15】**

前記n-電極は、プラズマ処理され、電気的特性が変化された半導体層上に形成されたことを特徴とする請求項13に記載の発光ダイオード。

**【請求項16】**

前記n-電極は、n型半導体層、活性層を含む傾斜面、p型半導体層の一部の間に絶縁膜を含むことを特徴とする請求項13に記載の発光ダイオード。

**【請求項17】**

前記n型半導体層、前記活性層及び前記p型半導体層は、窒化物系半導体であることを特徴とする請求項13に記載の発光ダイオード。 20

**【請求項18】**

前記プラズマ処理のガスは、N、NO、NH、He、Ne、Arからなるグループから選択された何れか一つまたは二つ以上の組み合わせであることを特徴とする請求項15に記載の発光ダイオード。

**【請求項19】**

前記プラズマ処理は、プラズマパワーによって表面処理された半導体層の電気特性が変わることを特徴とする請求項15に記載の発光ダイオード。

**【請求項20】**

前記プラズマ処理は、プラズマ処理時間によって表面処理された半導体層の電気特性が変わることを特徴とする請求項15に記載の発光ダイオード。 30

**【請求項21】**

前記プラズマ処理は、プラズマパワーと処理時間によって表面処理された半導体層の電気特性が変わることを特徴とする請求項15に記載の発光ダイオード。

**【請求項22】**

前記n-電極は、Ti、Al、Pt、Pd、Au、Cr、Fe、Cu、Moを含むグループから選択された何れか一つまたは二つ以上の組み合わせで構成されることを特徴とする請求項13に記載の発光ダイオード。

**【請求項23】**

前記n-電極の形成によって、前記活性層と並列に接続される電流通路が形成されることを特徴とする請求項13に記載の発光ダイオード。

**【請求項24】**

前記p-電極上に反射板をさらに含み、前記反射板と前記n-電極をサブマウントに付着することを特徴とする請求項17に記載の発光ダイオード。 40

**【請求項25】**

半導体層と接触される前記n-電極の接触面積の大きさによって、前記n-電極と半導体層との接触抵抗が決定されることを特徴とする請求項13に記載の発光ダイオード。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、高い静電気放電衝撃に対する保護機能が強化された発光ダイオードに関するもので、発光ダイオードの活性層と電気的に並列に接続される漏洩電流通路を設置し、静 50

電気が発光ダイオードに印加されるとき、並列に接続された漏洩電流通路を通して静電気をバイパス（bypassing）することで、発光ダイオード活性層を保護し、静電気に対する高い信頼性を有する発光ダイオードに関するものである。

#### 【背景技術】

##### 【0002】

発光ダイオードは、活性層に順方向に注入される電流を光に変換する素子である。インジウムリン（InP）、ガリウム砒素（GaAs）、ガリウムリン（GaP）などの化合物半導体が赤外線及び赤色などの光を放出する発光ダイオードの材料として使用されており、紫外線、青色及び緑色の光を放出する発光ダイオードの材料として、窒化ガリウム（GaN）系列の化合物半導体が開発されて使用されている。10

##### 【0003】

一般的に、GaN系列の化合物半導体は、結晶欠陥の発生を減らすために、類似した結晶構造及び格子常数を有するサファイア基板上にエピタキシャル成長される。サファイアが絶縁物質であるので、発光ダイオードの各電極パッドは、エピ層の成長面上に形成される。しかしながら、サファイアなどの絶縁物質の基板を使用する場合、外部から流入した静電気による静電放電を防止することが難しいので、ダイオードの損傷が容易に誘発され、素子の信頼性を低下させる。したがって、発光ダイオードをパッケージするとき、静電放電を防止するために別個のツェナーダイオードを発光ダイオードと一緒に装着して使用する。20

##### 【0004】

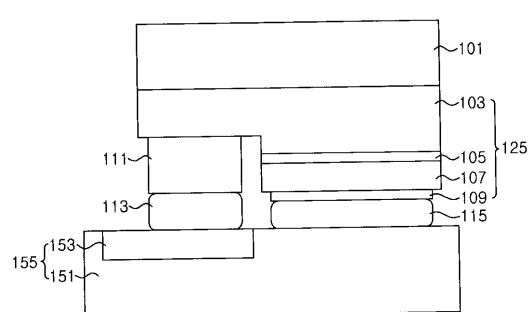

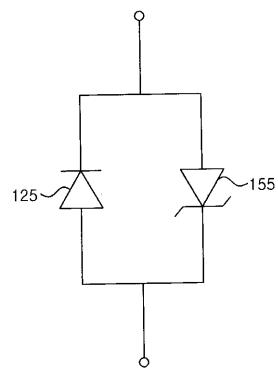

図1Aは、ESD損傷を防止するために、サブマウント内にツェナーダイオードを形成したフリップチップLEDの構成を概略的に示した断面図で、図1Bは、これに対する等価回路図である。図1Aを参照すると、半導体発光素子は、LED125と、LED125と並列に連結されてサブマウント151に形成されるツェナーダイオード155とを含む。LED125は、サファイア基板101上に順次的に積層されたn型半導体層（例えばn-GaN）103と、活性層105と、p型半導体層（例えば、p-GaN）107と、n型半導体層103上に積層されるn-電極111と、p型半導体層107上に積層されるp-電極109とを含む。ツェナーダイオード155は、例えば、n型シリコン基板などのサブマウント151の一部分にp型シリコン領域153を形成するために、例えば、p型イオン注入によって形成される。LED125のn-電極111が第1導電性バンプ113を通してp型シリコン領域153に連結され、p-電極109が第2導電性バンプ115を通してn型シリコン基板などのサブマウント151に連結されることで、フリップチップボンディングが行われる。図1Aに示した半導体発光素子の入出力端子（図示せず）を通してESD電圧が印加されると、ほとんどの放電電流は、LED125に並列に連結されるツェナーダイオード155を通して流れることによって、予期していなかったESD電圧の印加からLED125を保護することができる。30

##### 【0005】

図1Aに示した半導体発光素子の場合、サブマウントにツェナーダイオードを製作するために高価のイオン注入工程を実施するか、または、制御に困難さがある拡散工程を含むようになり、サブマウント製造工程が複雑になるだけでなく、それによって費用が増加するという問題点があった。40

##### 【0006】

上記のような問題点をフリップチップLEDに対して記述したが、一般的な表面放出LEDにツェナーダイオードを結合してパッケージングする場合にも、ツェナーダイオードを実装する工程の追加によって発光ダイオードパッケージ工程数及び製造費用が増加するだけでなく、パッケージング内のLEDとツェナーダイオードの空間配置に問題が発生しうる。

#### 【発明の開示】

##### 【発明が解決しようとする課題】

##### 【0007】

10

20

30

40

50

本発明は、ツェナーダイオードの利用なしにも外部から流入可能な静電気から発光ダイオードを保護するためになされたもので、発光ダイオードの活性層と並列に接続される電流通路を提供することを目的とする。

#### 【0008】

本発明の他の目的は、発光ダイオードの製造時に電極位置を変更することで、簡単に発光ダイオードの活性層と並列に接続される電流通路を提供し、電極が形成される部分の半導体表面抵抗と接触面積を変更することで、発光ダイオードの最適な駆動条件と静電気にに対する信頼性を同時に確保することにある。

#### 【課題を解決するための手段】

#### 【0009】

10

上記のような技術的課題を解決するための本発明の発光ダイオードは、基板、n型窒化物層、活性層、p型窒化物、エッチングによってオープンされたn型窒化物層でp型窒化物層の一部分上に延長形成されるn-電極を含むことで、発光ダイオードの活性層と並列関係にある電流通路を形成することを特徴とする。

#### 【0010】

発光ダイオード動作と静電気に対する信頼性を同時に維持するために、プラズマ表面処理を通して前記p型窒化物層の一部分の表面抵抗を変更し、前記n-電極と接触されるp型窒化物層の面積を変更することで、発光ダイオードの活性層と並列に形成される電流通路の電気抵抗を制御することを特徴とする。

#### 【発明の効果】

20

#### 【0011】

本発明は、別途のツェナーダイオードを使用せずに電流通路を発光ダイオードの活性層と並列に設置することで、発光素子を作成するためのパッケージ工程数及び製造費用を減少できるとともに、外部から流入した静電気による静電放電を防止し、逆電流によるダイオードの損傷を防止できるので、発光素子の信頼性を向上させることができる。

#### 【0012】

また、プラズマ表面処理及び接触面積の変更によって前記電流通路の電気抵抗を変更することができ、高い静電気放電特性を有するとともに、正常的な発光ダイオードの動作が可能になる。

#### 【発明を実施するための最良の形態】

30

#### 【0013】

このような技術的課題を達成するための本発明の一側面によると、サファイア基板上にn型半導体層を形成する段階と、前記n型半導体層上に活性層を形成する段階と、前記活性層上にp型半導体層を形成する段階と、エッチングによって前記n型半導体層の一部を除去してオープンする段階と、前記p型半導体層上にp-電極を形成する段階と、オープンされた前記n型半導体層と前記p-電極が形成されていないp型半導体層の一部にかけてn-電極を形成する段階とから構成される、活性層と並列に接続される電流通路を有する発光ダイオードの製造方法を提供する。

#### 【0014】

40

前記エッチングによってn型半導体層の一部を除去してオープンする段階は、フォトレジストによってパターンを形成する段階と、加熱によってフォトレジストパターンを再形成化(thermal reflow)する段階と、円形に再形成化されたフォトレジストパターンをエッチングマスクとして用いて乾式エッチングによってn型半導体層の一部を除去し、活性層を含むエッチング面を傾斜面に形成する段階とをさらに含むことができる。

#### 【0015】

前記エッチングによってn型半導体層の一部を除去した後、オープンされたn型半導体層、エッチング面によって露出された側面活性層、p-電極が形成されていないp型半導体層上にプラズマ処理を実施する段階をさらに含むことができる。

#### 【0016】

50

前記 n - 電極を形成する段階は、前記 n - 電極と接触される前記 n 型半導体層の接触面積の大きさを変更する段階と、前記 n - 電極と接触される前記 p 型半導体層の接触面積の大きさを変更する段階とをさらに含むことができる。

#### 【 0 0 1 7 】

また、サファイア基板上に n 型半導体層を形成する段階と、前記 n 型半導体層上に活性層を形成する段階と、前記活性層上に p 型半導体層を形成する段階と、エッティングによって前記 n 型半導体層の一部を除去してオープンする段階と、前記 p 型半導体上に p - 電極を形成する段階と、前記 p - 電極上に反射板を形成する段階と、オープンされた前記 n 型半導体層と前記 p - 電極が形成されていない前記 p 型半導体層の一部にかけて n - 電極を形成する段階とを経て完成された発光ダイオードの n - 電極と p - 電極をサブマウントに付着し、フリップチップ形態の発光ダイオードに製作することができる。 10

#### 【 0 0 1 8 】

本発明の他の側面によると、サファイア基板上に p 型半導体層を形成する段階と、前記 p 型半導体層上に活性層を形成する段階と、前記活性層上に n 型半導体層を形成する段階と、エッティングによって前記 p 型半導体層の一部を除去してオープンする段階と、前記 n 型半導体層上に n - 電極を形成する段階と、オープンされた前記 p 型半導体層と前記 n - 電極が形成されていない前記 n 型半導体層の一部にかけて p - 電極を形成する段階とから構成される活性層と並列に接続される電流通路を有する発光ダイオードの製造方法を提供する。

#### 【 0 0 1 9 】

前記エッティングによって前記 p 型半導体層の一部を除去してオープンする段階は、フォトレジストによってパターンを形成する段階と、加熱によって前記フォトレジストパターンを再形成化する段階と、円形に再形成化されたフォトレジストパターンをエッティングマスクとして用いて乾式エッティングによって p 型半導体層の一部を除去し、活性層を含むエッティング面を傾斜面に形成する段階とをさらに含むことができる。 20

#### 【 0 0 2 0 】

前記エッティングによって前記 p 型半導体層の一部を除去した後、オープンされた前記 p 型半導体層、エッティング面によって露出された側面活性層、前記 n - 電極が形成されていない n 型半導体層上にプラズマ処理を実施する段階をさらに含むことができる。

#### 【 0 0 2 1 】

前記 p - 電極を形成する段階は、前記 p - 電極と接触される前記 p 型半導体層の接触面積の大きさを変更する段階と、前記 p - 電極と接触される前記 n 型半導体層の接触面積の大きさを変更する段階とをさらに含むことができる。 30

#### 【 0 0 2 2 】

また、サファイア基板上に p 型半導体層を形成する段階と、前記 p 型半導体層上に活性層を形成する段階と、前記活性層上に n 型半導体層を形成する段階と、エッティングによって前記 p 型半導体層の一部を除去してオープンする段階と、前記 n 型半導体層上に n - 電極を形成する段階と、前記 n - 電極上に反射板を形成する段階と、オープンされた前記 p 型半導体と前記 n - 電極が形成されていない前記 n 型半導体層の一部にかけて p - 電極を形成する段階とを経て完成された発光ダイオードの n - 電極と p - 電極をサブマウントに付着し、フリップチップ形態の発光ダイオードに製作することができる。 40

#### 【 0 0 2 3 】

本発明の他の側面によると、発光ダイオードは、サファイア基板上に形成された n 型半導体層と、前記 n 型半導体層上に形成された活性層と、前記活性層上に形成された p 型半導体層と、 p 型半導体層上に形成された p - 電極と、エッティングによってオープンされた n 型半導体層と p - 電極が形成されていない p 型半導体層にかけて形成された n - 電極とを含むことで、活性層と並列に接続される電流通路を有する発光ダイオードを提供する。

#### 【 0 0 2 4 】

前記 n - 電極は、 n 型半導体層と p 型半導体層との間の傾斜したエッティング面を含み、 n 型半導体層と p - 電極が形成されていない p 型半導体層にかけて形成される。 50

前記 n - 電極は、 n 型半導体層、エッティング面によって露出された側面活性層、 p - 電極が形成されていない p 型半導体層上に、接触面の電気抵抗が変形されるようにプラズマ処理によって形成される。

#### 【 0025 】

前記 n - 電極は、 n - 電極と接触される n 型半導体層の接触面積の大きさを変更し、 n - 電極と接触される p 型半導体層の接触面積の大きさを変更することで形成される。

前記活性層と並列に接続される電流通路を有する発光ダイオードの n - 電極及び p - 電極をサブマウントに付着し、フリップチップ形態の発光ダイオードを提供することができる。

#### 【 0026 】

本発明の他の側面によると、発光ダイオードは、サファイア基板上に形成された p 型半導体層と、前記 p 型半導体層上に形成された活性層と、前記活性層上に形成された n 型半導体層と、前記 n 型半導体層上に形成された n - 電極と、エッティングによってオープンされた前記 p 型半導体層と前記 n - 電極が形成されていない前記 n 型半導体層にかけて形成された p - 電極とを含むことで、活性層と並列に接続される電流通路を有する発光ダイオードを提供する。

#### 【 0027 】

前記 p - 電極は、前記 p 型半導体層と前記 n 型半導体層との間の傾斜したエッティング面を含み、前記 p 型半導体層と前記 n - 電極が形成されていない n 型半導体層にかけて形成される。

10

#### 【 0028 】

前記 p - 電極は、 p 型半導体層、エッティング面によって露出された側面活性層、 n - 電極が形成されていない n 型半導体層上に、接触面の電気抵抗が変形されるようにプラズマ処理によって形成される。

#### 【 0029 】

前記 p - 電極は、 p - 電極と接触される p 型半導体層の接触面積の大きさを変更し、 p - 電極と接触される n 型半導体層の接触面積大きさを変更することで形成される。

前記活性層と並列に接続される電流通路を有する発光ダイオードの n - 電極及び p - 電極をサブマウントに付着し、フリップチップ形態の発光ダイオードを提供することができる。

20

#### 【 0030 】

以下、添付した図面を参照して本発明の実施例を詳細に説明する。以下で紹介される実施例は、当業者に本発明の思想を充分に伝達するための例として提供するものである。したがって、本発明は、以下で説明される実施例に限定されることなく、他の形態で具体化されることもある。そして、各図面において、構成要素の幅、長さ、厚さなどは、便宜のために誇張されて表現される。明細書の全体にかけて、同一の参照番号は同一の構成要素を示している。

30

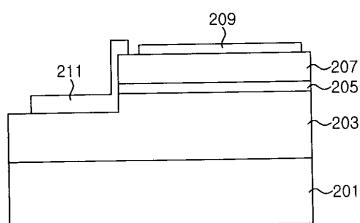

#### 【 0031 】

図 2 は、本発明の一実施例に係る発光ダイオードを説明するための断面図である。

図 2 を参照すると、サファイア基板 201 上に n 型窒化物層 203 、活性層 205 、 p 型窒化物層 207 、 p - 電極 209 から構成された発光ダイオードにおいて、露出された n 型窒化物層と p - 電極が形成されていない p 型窒化物層上にかけて n - 電極 211 が形成される ( p 型パッドは図示せず。)。

40

#### 【 0032 】

前記 n - 電極 211 は、 n 型窒化物層 207 と p 型窒化物層 209 の一部にかけて形成されることで、発光ダイオードの活性層 205 と電気的に並列に接続された電流通路を有するようになる。

#### 【 0033 】

発光ダイオードに逆方向に静電気が印加された場合、発光ダイオードの接触電位差によつて形成される内部抵抗よりも並列に接続された電流通路の電気抵抗が小さく設計されて

50

おり、印加された静電気は、並列に接続された電流通路を通して流れるようになり、発光ダイオードの活性層を効果的に保護できるようになる。

#### 【0034】

n-電極211の形成前に、プラズマ表面処理を通してn-電極が形成される窒化物層に対する電気抵抗を変形することができ、特に、p型窒化物層に対するプラズマ表面処理は、電気抵抗を急速に増加させることができる。

#### 【0035】

プラズマ表面処理は、RIE、ICP、ECRなどのプラズマを発生可能な全ての真空チャンバーで行うことができ、プラズマガスは、N、NO、NH、He、Ne、Arからなるグループから選択された何れか一つまたは二つ以上の組み合わせで構成され、プラズマ発生のために1W乃至200W範囲のパワーが印加され、10分以下の時間で窒化物層をプラズマ処理することができる。10

#### 【0036】

特に、活性層を下部に置いているp型窒化物層209の表面プラズマ処理においては、プラズマ処理による活性層の損傷を防止するために、窒素プラズマを25Wのパワーで60秒未満に処理し、p型窒化物層209表面のみにプラズマ処理を実施することが好ましい。

#### 【0037】

プラズマ処理時、プラズマ発生パワーと時間に比例して窒化物半導体の電気抵抗が増加することを確認したし、プラズマ処理された窒化物層上に接触される前記n-電極211は、窒化物半導体の接触面で接触抵抗が増加するので、露出されたn型窒化物層203とp-電極が形成されていないp型窒化物層207上にかけて形成されたn-電極211によって発生する電流通路の電気特性を制御できるようになる。20

#### 【0038】

したがって、発光ダイオードの活性層と並列に接続される電流通路を通して流れる漏洩電流を防止しながら、素子の電気的駆動特性を正常的に維持させるとともに、外部から流入可能な静電気に対してバイパスを提供することで、静電気に対して高い信頼性を有する発光ダイオードを提供するようになる。

#### 【0039】

窒化物半導体に対するプラズマ処理の代わりに、n-電極と接触されるn型窒化物層、活性層を含むメサ側面、p型窒化物層上にSiO<sub>2</sub>膜またはSiN膜などの絶縁体を挿入することによっても、窒化物層に接触されるn-電極の接触抵抗を変化させることができる。30

#### 【0040】

プラズマ処理後に、n-電極と接触されるn型窒化物層、活性層を含むメサ側面、p型窒化物層上にSiO<sub>2</sub>膜またはSiN膜などの絶縁体を追加的に挿入することによっても、窒化物層に接触されるn-電極の接触抵抗を変化させることができる。

#### 【0041】

また、n-電極が形成される接触面に対するプラズマ処理と一緒に、窒化物層と接触するn-電極の面積を変化させることで接触抵抗を変形することができ、特に、p型窒化物と接触される接触面積の変化は、接触抵抗変化に多くの影響を及ぼすようになる。40

#### 【0042】

窒化物層と接触されるn-電極の面積を減少させることで電極の接触抵抗が増加するので、露出されたn型窒化物層203とp-電極が形成されていないp型窒化物層207上にかけて形成されたn-電極211によって発生する電流通路の電気特性を制御できるようになる。

#### 【0043】

前記p-電極209は、酸化伝導膜またはNi/Auなどの透明金属膜で形成され、n-電極211は、Ti、Al、Pt、Pd、Au、Cr、Fe、Cu、Moを含むグループから選択された何れか一つまたは二つ以上の組み合わせで具現される。50

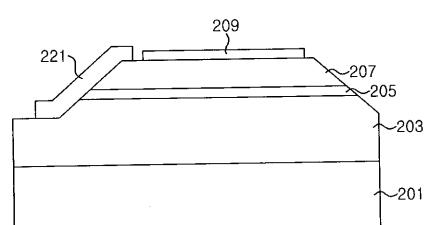

## 【0044】

図3は、本発明の一実施例に係る発光ダイオードを説明するための断面図である。

図3を参照すると、サファイア基板201上にn型窒化物層203、活性層205、p型窒化物層207、p-電極209で構成された発光ダイオード構造が開示されており( p型パッドは図示せず)、エッティングによってn型窒化物層207を露出させるとき、加熱によって円形に再形成されたフォトレジストをエッティングマスクとして用いて乾式エッティングさせることで、図3のように傾斜型メサ構造を有する発光ダイオードを製作できるようになる。

## 【0045】

n-電極221は、露出されたn型窒化物層203とp-電極が形成されていないp型窒化物層207上にかけて形成される。 10

前記p-電極209は、酸化伝導膜またはNi/Auなどの透明金属膜で形成され、n-電極221は、Ti、Al、Pt、Au、Cr、Fe、Cu、Moを含むグループから選択された何れか一つまたは二つ以上の組み合わせで具現される。

## 【0046】

前記n-電極221は、n型窒化物層207とp型窒化物層209の一部にかけて形成されることで、発光ダイオードの活性層205と電気的に並列に接続された電流通路を有するようになる。

## 【0047】

n-電極221の形成前に、プラズマ表面処理を通してn-電極が形成される窒化物層に対する電気抵抗を変形することができ、特に、p型窒化物層に対するプラズマ表面処理は、電気抵抗を急速に増加させることができる。 20

## 【0048】

プラズマ表面処理は、RIE、ICP、ECRなどのプラズマを発生可能な全ての真空チャンバーで行うことができ、プラズマガスは、N、NO、NH、He、Ne、Arからなるグループから選択された何れか一つまたは二つ以上の組み合わせで構成され、プラズマ発生のために1W乃至200W範囲のパワーが印加され、10分以下の時間で窒化物層をプラズマ処理することができる。

## 【0049】

特に、活性層を下部に置いているp型窒化物層209の表面プラズマ処理においては、プラズマ処理による活性層の損傷を防止するために、窒素プラズマを25Wのパワーで60秒未満に処理し、p型窒化物層209表面のみにプラズマ処理を実施することが好ましい。 30

## 【0050】

プラズマ処理時、プラズマ発生パワーと時間に比例して窒化物半導体の電気抵抗が増加することを確認したし、プラズマ処理された窒化物層上に接触される前記n-電極221は、窒化物半導体の接触面で接触抵抗が増加するので、露出されたn型窒化物層203とp-電極が形成されていないp型窒化物層207上にかけて形成されたn-電極221によって発生する電流通路の電気特性を制御できるようになる。

## 【0051】

したがって、発光ダイオードの活性層と並列に接続される電流通路を通して流れる漏洩電流を防止しながら、素子の電気的駆動特性を正常的に維持させるとともに、外部から流入可能な静電気に対してバイパスを提供することで、静電気に対して高い信頼性を有する発光ダイオードを提供するようになる。 40

## 【0052】

窒化物半導体に対するプラズマ処理の代わりに、n-電極と接触されるn型窒化物層、活性層を含むメサ側面、p型窒化物層上にSiO<sub>2</sub>膜またはSiN膜などの絶縁体を挿入することによっても、窒化物層に接触されるn-電極の接触抵抗を変化させることができる。

## 【0053】

プラズマ処理後に、n-電極と接触されるn型窒化物層、活性層を含むメサ側面、p型窒化物層上にSiO<sub>2</sub>膜またはSiN膜などの絶縁体を追加的に挿入することによっても、窒化物層に接触されるn-電極の接触抵抗を変化させることができる。

#### 【0054】

また、n-電極が形成される接触面に対するプラズマ処理と一緒に、窒化物層と接触するn-電極の面積を変化させることで接触抵抗を変形することができ、特に、p型窒化物と接触される接触面積の変化は、接触抵抗変化に多くの影響を及ぼすようになる。

#### 【0055】

窒化物層と接触されるn-電極の面積を減少させることで電極の接触抵抗が増加するので、露出されたn型窒化物層203とp-電極が形成されていないp型窒化物層207上にかけて形成されたn-電極221によって発生する電流通路の電気特性を制御できるようになる。10

#### 【0056】

特に、図3に示すように、傾斜型メサ構造の発光ダイオードは、活性層が素子の上面に露出されており、プラズマ処理時、垂直型メサ構造に比べて効果的に活性層の露出面を絶縁化することで、n-電極との直接的な電気的接触を防止することができ、長時間の間素子を駆動するときに素子の信頼性を増進させることができ、露出されたn型窒化物層203とp-電極が形成されていないp型窒化物層207上にかけて形成されたn-電極221が緩慢な傾斜度を有するエッティング面上に形成されることで、電極形成時のステップカバレッジ問題を解消することができ、フリップチップ形態で素子を製作する場合に光抽出効率を増加させることで、発光効率をより一層改善させることができる。20

#### 【0057】

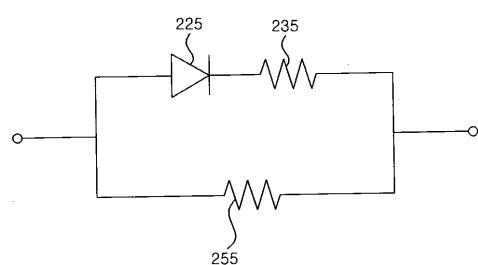

図4は、図2及び図3の発光ダイオードの等価回路図である。

図4を参照すると、発光ダイオード225に直列に接続された抵抗235は、発光ダイオード活性層の接合電位差を含む内部抵抗と半導体-金属間の接触抵抗を全て含む抵抗成分を示したもので、発光ダイオード225と並列に接続された抵抗255は、露出されたn型窒化物層203とp-電極が形成されていないp型窒化物層207上にかけて接触されたn-電極211または221によって形成される電流通路の抵抗に該当する。

#### 【0058】

前記電流通路の抵抗255は、窒化物半導体層に対するプラズマ処理と接触される電極面の大きさによって決定され、前記電流通路抵抗255の大きさ変化によって、製作された発光ダイオード駆動の電気的特性と静電気放電限界が決定される。30

#### 【0059】

図2及び図3に開示された発光ダイオードは、n-電極が素子の左側面のみに形成された場合を記載しているが、素子の左側だけでなく、右側にも対称的な構造でn-電極を形成することができ、素子を完全に取り囲む形態でn-電極を形成することもできる。図2及び図3では、サファイア上にn型窒化物層、活性層、p型窒化物層が順次形成された窒化物発光ダイオードに対して説明したが、サファイア上にp型窒化物層、活性層、n型窒化物層が積層された窒化物発光ダイオードも本発明の同一の技術的思想に基づいて具体化されることは自明である。40

#### 【図面の簡単な説明】

#### 【0060】

【図1A】一般的なフリップチップ形態の発光ダイオードの断面図である。

【図1B】図1Aのフリップチップ形態の発光ダイオードの等価回路図である。

【図2】本発明の一実施例に係る発光ダイオードの断面図である。

【図3】本発明の他の実施例に係る発光ダイオードの断面図である。

【図4】図2及び図3の発光ダイオードの断面図である。

#### 【符号の説明】

#### 【0061】

101, 201...基板、103, 203...n型半導体層、105, 205...活性層、1

50

07, 207...p型半導体層、109, 209...p-電極、111, 211, 221...n-電極、125, 225...発光ダイオード、155...ツエナーダイオード、235, 255...抵抗。

【図1A】

【図1B】

【図2】

【図3】

【図4】

---

フロントページの続き

(72)発明者 ユン ヨジン

大韓民国 425-851 ギヨンギ - ド アンサン - シ ダンウォン - グ ウォンシ - ドン 7

27-5 ブロック 1-35

審査官 佐藤 俊彦

(56)参考文献 特開2002-043633 (JP, A)

特開2002-261326 (JP, A)

特開2003-347589 (JP, A)

特開2007-157850 (JP, A)

特開平10-223930 (JP, A)

特開2007-080899 (JP, A)

特開2006-324511 (JP, A)

特開2005-039197 (JP, A)

特開昭62-036827 (JP, A)

特開平07-066280 (JP, A)

特開2006-245232 (JP, A)

特開2007-173349 (JP, A)

特開2007-227820 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 33/00 - 33/64