(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6316959号

(P6316959)

(45) 発行日 平成30年4月25日(2018.4.25)

(24) 登録日 平成30年4月6日(2018.4.6)

|                |           |        |            |

|----------------|-----------|--------|------------|

| (51) Int.Cl.   | F 1       |        |            |

| HO 1 L 21/8234 | (2006.01) | HO 1 L | 27/088 C   |

| HO 1 L 27/088  | (2006.01) | HO 1 L | 29/78 301G |

| HO 1 L 21/336  | (2006.01) | HO 1 L | 29/78 301F |

| HO 1 L 29/78   | (2006.01) | HO 1 L | 29/78 301C |

| HO 1 L 21/28   | (2006.01) | HO 1 L | 21/28 E    |

請求項の数 8 (全 18 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2016-530238 (P2016-530238)  |

| (86) (22) 出願日 | 平成26年10月24日(2014.10.24)       |

| (65) 公表番号     | 特表2016-540378 (P2016-540378A) |

| (43) 公表日      | 平成28年12月22日(2016.12.22)       |

| (86) 國際出願番号   | PCT/US2014/062276             |

| (87) 國際公開番号   | W02015/076978                 |

| (87) 國際公開日    | 平成27年5月28日(2015.5.28)         |

| 審査請求日         | 平成29年8月8日(2017.8.8)           |

| (31) 優先権主張番号  | 61/908,007                    |

| (32) 優先日      | 平成25年11月22日(2013.11.22)       |

| (33) 優先権主張国   | 米国(US)                        |

| (31) 優先権主張番号  | 14/283,168                    |

| (32) 優先日      | 平成26年5月20日(2014.5.20)         |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

最終頁に続く

|           |                                                                                        |

|-----------|----------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サン デイエゴ モアハウス ドラ<br>イブ 5775 |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                                 |

| (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                                 |

| (72) 発明者  | スタンリー・スンチュル・ソン<br>アメリカ合衆国・カリフォルニア・921<br>21-1714 サン・ディエゴ・モアハ<br>ウス・ドライブ・5775           |

(54) 【発明の名称】ゲートパターニングのためのリソグラフィマージプロセス

## (57) 【特許請求の範囲】

## 【請求項 1】

ダイ上で複数のデバイスを作製するための方法であって、

自己整合ダブルパターニング(SADP)プロセスを用いて、第1のゲート長とコンタクトポリシリコンピッチ(CPP)とを有する、複数の第1のゲートを作成するために第1の領域をパターニングするステップであって、前記CPPが単一パターンリソグラフィ限界よりも小さい、パターニングするステップと、

リソエッチャリソエッチ(LEE)セルスワッププロセスによって前記第1の領域をパターニングして、前記複数の第1のゲートのいくつかの代わりに配置される一組の第2のゲートを作製するステップであって、前記第2の一組のゲートは第2のゲート長及び前記CPPを有し、前記第2のゲート長は前記第1のゲート長と異なるステップとを備える、方法。

## 【請求項 2】

前記セルスワッププロセスが、前記SADPプロセスによって形成されるゲート間で実行される第2のリソグラフィプロセスである、請求項1に記載の方法。

## 【請求項 3】

前記複数のデバイスが、モバイル電話、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、コンピュータ、ハンドヘルドパーソナル通信システム(PCS)ユニット、ポータブルデータユニット、および/または固定位置データユニットに組み込まれる、請求項1に記載の方法。

## 【請求項 4】

第1の領域内に第1のゲート長とコンタクトポリシリコンピッチ（CPP）とを有する、複数の第1のゲート長デバイスであって、前記CPPが単一パターンリソグラフィ限界よりも小さい、複数の第1のゲート長デバイスと、

前記第1の領域内の前記複数の第1のゲート長デバイスのいくつかの代わりに配置された一組の第2のゲート長デバイスであって、前記一組の第2のゲート長デバイスは第2のゲート長及び前記CPPを有し、前記第2のゲート長が前記第1のゲート長とは異なる、一組の第2のゲート長デバイスと

を有し、

前記CPPは40nm～80nmの範囲であり、

10

前記第1のゲート長及び前記第2のゲート長は10nm～30nmの範囲である、装置。

## 【請求項 5】

第3のゲート長を有する第3のゲート長デバイスをさらに含む、請求項4に記載の装置。

## 【請求項 6】

モバイル電話、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、コンピュータ、ハンドヘルドパーソナル通信システム（PCS）ユニット、ポータブルデータユニット、および／または固定位置データユニットに組み込まれる、請求項4に記載の装置。

20

## 【請求項 7】

ダイ上で複数のデバイスを作製するための方法であって、

自己整合ダブルパターニング（SADP）プロセスを用いて、第1のゲート長とコンタクトポリシリコンピッチ（CPP）とを有する、複数の第1のゲートを作成するために第1の領域をパターニングするステップであって、前記CPPが単一パターンリソグラフィ限界よりも小さい、パターニングするステップと、

リソエッチャリソエッチ（LEE）セルスワッププロセスによって前記第1の領域をパターニングして、前記複数の第1のゲートのいくつかの代わりに配置される一組の第2のゲートを作製するステップであって、前記第2の一組のゲートは第2のゲート長及び前記CPPを有し、前記第2のゲート長は前記第1のゲート長と異なるステップとを備える、方法。

30

## 【請求項 8】

前記複数のデバイスが、モバイル電話、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、コンピュータ、ハンドヘルドパーソナル通信システム（PCS）ユニット、ポータブルデータユニット、および／または固定位置データユニットに組み込まれる、請求項7に記載の方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

関連出願の相互参照

40

本出願は、その開示の全体が参照により本明細書に明示的に組み込まれている、2013年11月22日に出願した、「MERGING LITHOGRAPHY PROCESS FOR GATE PATTERNING」という名称の米国仮特許出願第61/908,007号の、米国特許法第119（e）条に基づく利益を主張するものである。

## 【0002】

本開示の態様は、半導体デバイスに関し、より詳細には、電界効果トランジスタ（FET）構造内のゲート長さおよびゲート間隔を削減することに関する。

## 【背景技術】

## 【0003】

50

半導体デバイスのサイズが削減するにつれて、デバイス用のパターンを作製する能力はより困難になる。10ナノメートル(nm)のコンタクトポリシリコン(PO)ピッチ(CPP: contacted polysilicon(PO) pitch)デバイスの場合、そのデバイスサイズを達成するために、複数のパターニングステップを使用することができます。たとえば、関連技術方法は、より小さなピッチサイズを達成するためにインターリープまたは交互絡合されたより大きなピッチパターンを使用するリソエッチャリソエッチ(LELE:litho-etch litho-etch)として知られている。それでもなお、LELEは、より大きなラインエッジ粗さ(LER)、より大きなゲート間間隔変動、およびより大きな限界寸法変動によって依然として制限される。

## 【0004】

10

別の関連技術方法は、ゲート長(Lg)を定義するために、マンドレル上に堆積されたスペーサを使用する自己整合ダブルパターニング(SADP:self-aligned double patterning)である。SADPはLELEよりも良好な限界寸法均一性を有するが、SADP生成デバイスにおいて異なるゲート長を生成するため、追加のマスクが使用される。これは、より大きな集積回路に関するSADPプロセスの有用性を制限する。

## 【発明の概要】

## 【課題を解決するための手段】

## 【0005】

20

ダイ上でデバイスを作製するための方法は、第1のプロセスを用いて、第1のゲート長と第1のコンタクトポリシリコンピッチ(CPP)とを有する第1のゲートを作成するために第1の領域をパターニングするステップを含み得る。第1のCPPは単一パターンリソグラフィ限界よりも小さい。本方法はまた、第2のプロセスを用いて、第2のゲート長または第2のCPPを有する第2のゲートを作成するために第1の領域をパターニングするステップを含む。第2のCPPは単一パターンリソグラフィ限界よりも小さい。第2のゲート長は第1のゲート長とは異なる。

## 【0006】

装置は、第1の領域内に第1のゲート長と第1のコンタクトポリシリコンピッチ(CPP)とを有する第1のゲート長デバイスを含み得る。第1のCPPは単一パターンリソグラフィ限界よりも小さい。本装置はまた、第2のゲート長または第2のCPPを有する第1の領域内の少なくとも1つの第2のゲート長デバイスを含む。第2のCPPは単一パターンリソグラフィ限界よりも小さい。第2のゲート長は第1のゲート長とは異なっている。

## 【0007】

30

装置は、第1の領域内で第1のゲート長と第1のコンタクトポリシリコンピッチ(CPP)とを有する、電流を選択的に伝導するため第1の手段を含み得る。第1のCPPは単一パターンリソグラフィ限界よりも小さい。本装置はまた、第2のゲート長または第2のCPPを有する少なくとも1つの第2のゲート長デバイスを有する、電流を選択的に伝導するための第2の手段を含む。第2のCPPは単一パターンリソグラフィ限界よりも小さい。第2のゲート長は第1のゲート長とは異なっている。

## 【0008】

40

上記は、続く詳細な説明をよりよく理解することができるよう、本開示の特徴および技術的利点について、かなり大まかに概説したものである。本開示のさらなる特徴および利点について、以下で説明する。本開示は、本開示と同じ目的を果たすための他の構造を修正または設計する基礎として容易に利用できることを、当業者には理解されたい。そのような等価な構造(construction)が、添付の特許請求の範囲に記載の本開示の教示から逸脱しないことも、当業者には理解されたい。本開示の特徴になると考えられる新規な特徴は、本開示の構成(organization)と動作方法の両方について、さらなる目的および利点とともに、以下の説明を添付の図と併せ検討することからよりよく理解されるであろう。しかしながら、図の各々は、例示および説明を目的として提

50

供されているに過ぎず、本開示の制限を定めるものではないことを、明確に理解されたい。

【0009】

本開示のより完全な理解が得られるように、ここで、以下の説明を添付の図面と併せて参照する。

【図面の簡単な説明】

【0010】

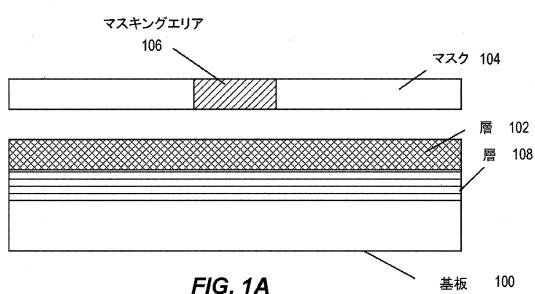

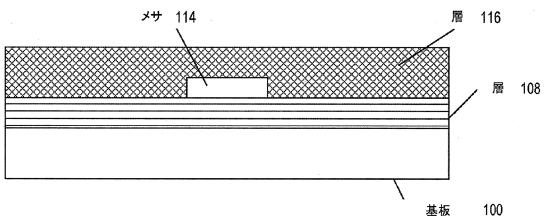

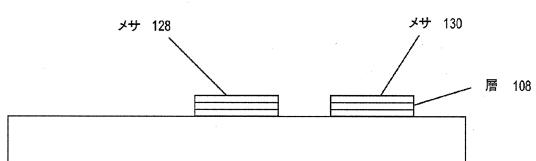

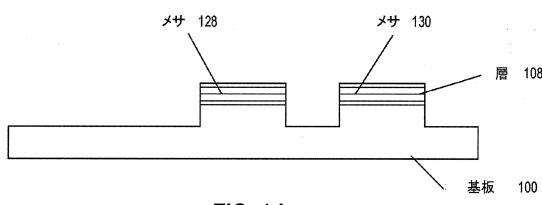

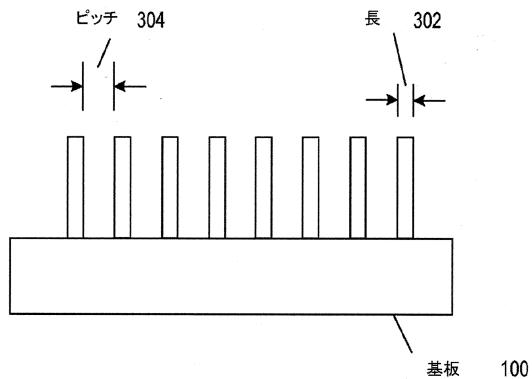

【図1A】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

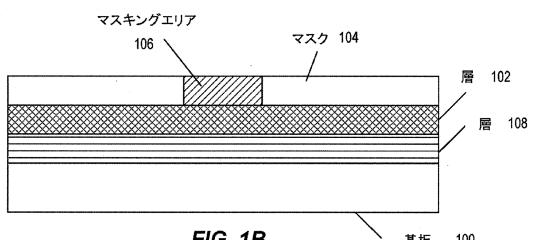

【図1B】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

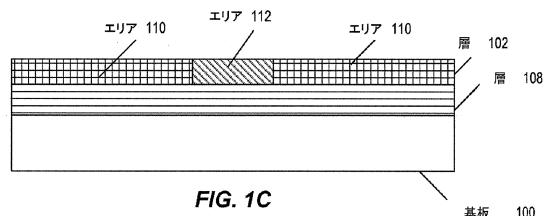

【図1C】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

10

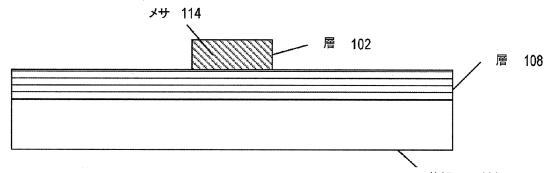

【図1D】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

【図1E】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

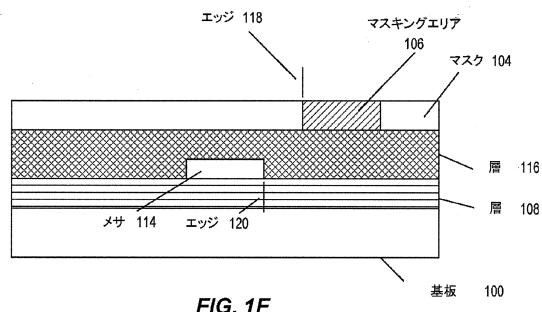

【図1F】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

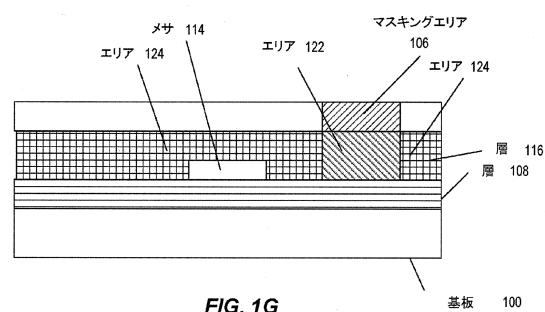

【図1G】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

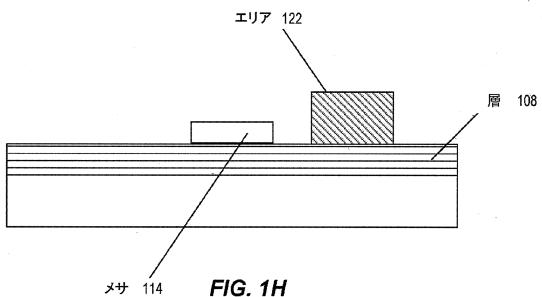

【図1H】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

【図1I】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

【図1J】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

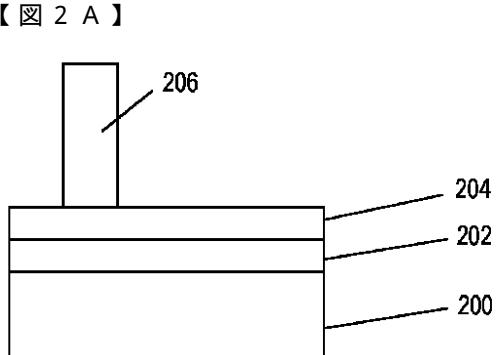

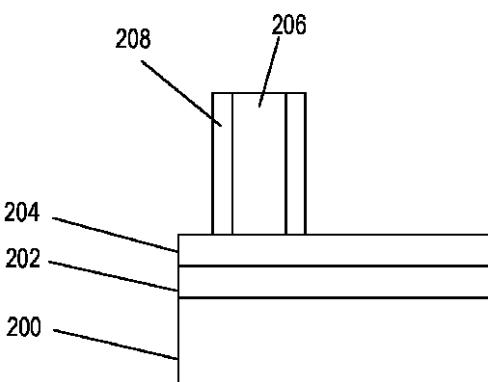

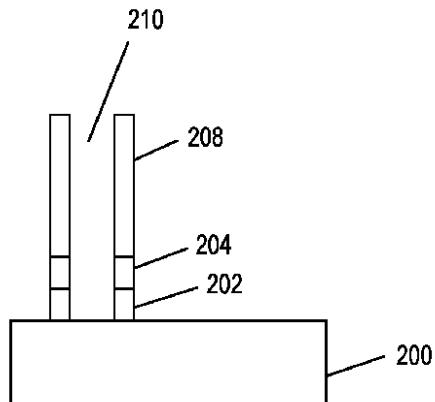

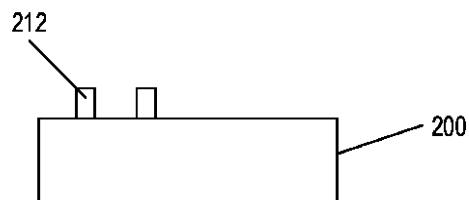

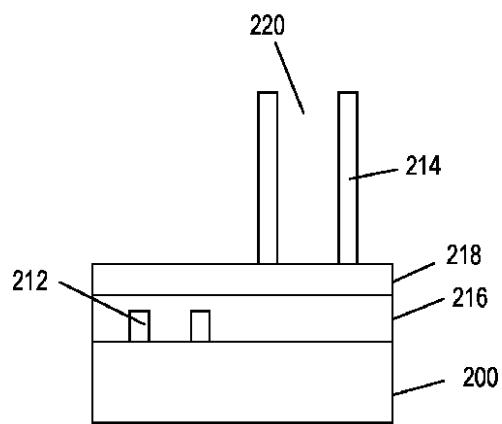

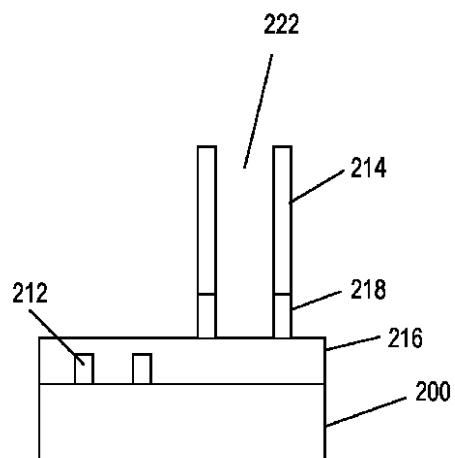

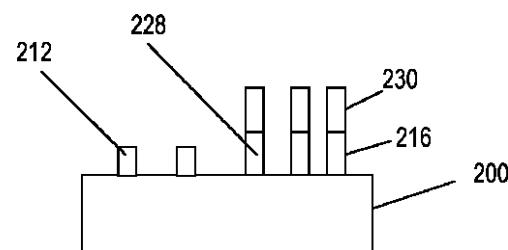

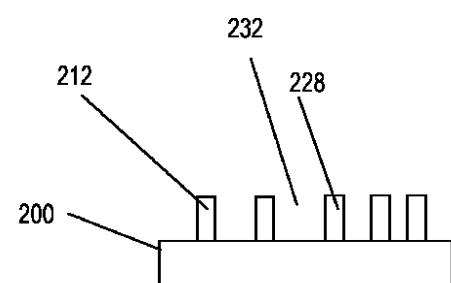

【図2A】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

【図2B】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

20

【図2C】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

【図2D】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

【図2E】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

【図2F】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

【図2G】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

30

【図2H】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

【図2I】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

【図2J】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

【図2K】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

【図2L】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

40

【図2M】本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す図である。

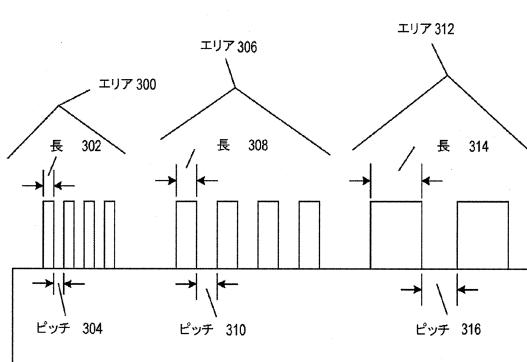

【図3A】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

【図3B】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

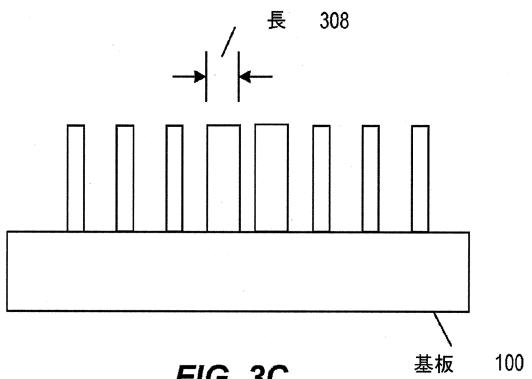

【図3C】本開示の1つまたは複数の態様による半導体デバイスの側面図である。

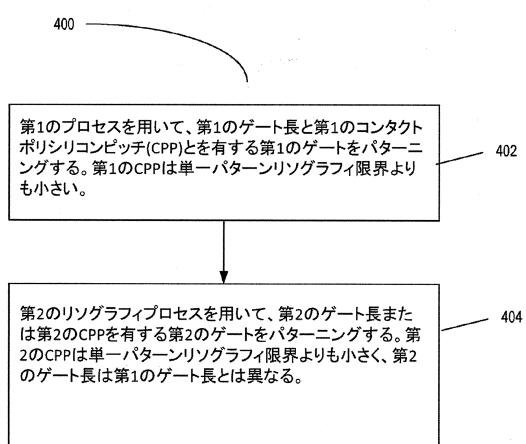

【図4】本開示の一態様によるデバイスを作製するための方法を示すプロセスフロー図である。

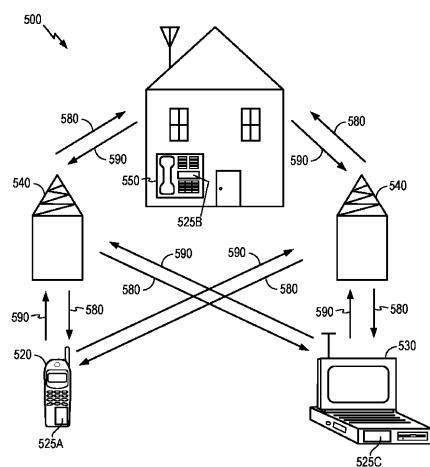

【図5】本開示の一態様が有利に採用され得る例示的なワイヤレス通信システムを示すブロック図である。

50

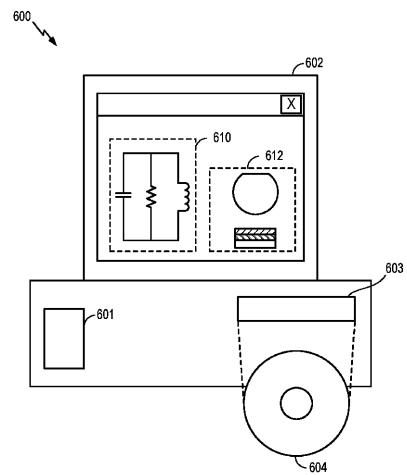

【図6】本開示の一態様による、半導体構成要素の回路設計、レイアウト設計、および論理設計に使用される設計用ワークステーションを示すブロック図である。

【発明を実施するための形態】

【0011】

添付の図面に関して以下に記載する詳細な説明は、様々な構成の説明として意図されており、本明細書で説明する概念が実践され得る構成のみを表すことは意図されていない。詳細な説明は、様々な概念の完全な理解を与える目的で特定の詳細を含む。しかしながら、これらの概念がこれらの具体的な詳細なしに実践され得ることが、当業者には明らかであろう。場合によっては、そのような概念を曖昧にすることを回避するために、よく知られている構造および構成要素がブロック図の形態で示されている。本明細書の説明では、「および／または」という用語の使用は、「包含的論理和」を表すことを意図し、「または」という用語の使用は、「排他的論理和」を表すことを意図する。

10

【0012】

10 (10) ナノメートル (nm) のコンタクトポリシリコン (PO) ピッチ (CPP) ジオメトリは、デバイスのパターニング用に 64 (64) nm ベースジオメトリを使用することができる。デバイス内にこのサイズのベースジオメトリを作成するために、193 インターリーブダブルパターニング (interleaved double patterning) がしばしば使用される。2つの方法がデバイス内にベースジオメトリを作成し得る。第1のリソグラフィプロセス、すなわち、リソエッチリソエッチ (LELE) は、128 (128) nm 特徴のサイズを 64 nm 特徴のサイズに削減するために、その上でインターリーブされた（たとえば、オーバーレイされた）128 nm ピッチパターンを使用する。マスクを重複させることによって、128 nm 特徴は、64 nm ベース CPP に達するために半分に切断され得る。第2のリソグラフィプロセス、すなわち、自己整合ダブルパターニング (SADP) は、ゲート長 (Lg) を定義するために、ダミーマンドレルパターン上に堆積されたスペーサを使用する。これは、FinFET デバイス内にフィン構造を作成するのと同様である。

20

【0013】

本開示の一態様は、SADP と LELE とをマージし、回路またはデバイス内に複数のゲート長を可能にすることである。SADP の使用は、より密な限界寸法 (CD) 制御とより少ない変動とを実現するが、単一のゲート長だけを可能にする。本開示の一態様では、SADP プロセスに関して 1 つのマスクが使用される。LELE の使用は、同じデバイス内に複数のゲート長とフレキシブルな CPP とを可能にする。本開示の一態様では、LELE の使用は 2 つのマスクを使用する。SADP と LELE の両方に関する切断パターンはまた、本開示の一態様では、単一のマスクを使用し、これは 4 つのマスクプロセスを可能にする。

30

【0014】

本開示の一態様では、SADP の使用は、より小さな CPP においてより小さなゲート長を可能にする。SADP を LELE と組み合わせることによって、より小さな、場合によっては、最小の CPP において複数のゲート長が可能にされる。さらに、LELE は、入出力 (I/O) デバイスおよびアナログデバイスに関して、より大きな CPP においてより大きなゲート長をやはり可能にする。

40

【0015】

図1A～図1J は、本開示の 1 つまたは複数の態様による半導体デバイスの側面図を示す。図1A～図1J では、概して LELE プロセスを示す。図1A は、層102 および層108 を有する基板100 を示す。層102 および108 は、ハードマスク層、フォトマスク層であり得るか、またはシリコン酸化物、ポリシリコン、もしくは他の材料の層であり得る。マスキングエリア106 を有するマスク104 も図1A に示す。図1B では、マスク104 は、層102 をパターニングするために、層102 および基板100 に近接して配置される。

【0016】

50

図1Cは、マスキングエリア106によって遮断されなかった、層102のエリア110と、マスキングエリア106によって遮断されたエリア112とを有する層102を示す。図1A～図1Cは、本開示のLELEプロセスの「第1のリソグラフィ」すなわち「第1のリソ」部分について説明する。図1Dは、デバイス全体の設計に応じて、層102の一部であり得るか、または別の層の一部であり得る、メサ114を示す。図1Dは、本開示のLELEプロセスの「第1のエッチ」について説明する。

#### 【0017】

図1Eは、フォトレジストであり得るか、または、シリコン、シリコン酸化物、ポリシリコン、もしくは他の材料であり得る、別の層116を示す。図1Fは、マスキングエリア106のエッジ118がメサ114のエッジ120からオフセットされるマスク104を示す。図1Gは、エリア122はマスキングエリア106を使用して遮断されるが、エリア124は遮断されない状態にとどまる、層116の露出部を示す。図1Hは、層108上のエリア122およびメサ114を示す。図1E～図1Hは、本開示のLELEプロセスの「第2のリソグラフィ」部分について説明する。

#### 【0018】

図1Iは、メサ114およびエリア122の下にあったメサ128ならびにメサ130を作成するための、層108の部分のエッチングまたは除去を示す。図1Jは、メサ128および130が基板100の部分を保護するためのマスクとして機能する、基板100のエッチングを示す。図1H～図1Jは、本開示のLELEプロセスの「第2のエッチ」部分について説明する。

#### 【0019】

マスキングエリア106を配置することによって、メサ128および130の幅、ならびに、したがって、デバイス内の基板100または他の層上に作成される特徴は、LELEプロセスにおいて、第1のリソグラフィと第2のリソグラフィとの間のマスキングエリア106を「インターリープすること」によって作成される。しかしながら、(マスキングエリア106によって定義される)エリア122はメサ130が別のメサ128または別のデバイスにどの程度近いかを制限するが、これは、エリア122がエリア122の下に何らかのエッチングまたは他の処理が発生するのを妨げるためである。これは、基板100上のデバイスのゲート間隔を制限する。言い換えると、第1の領域内でLELEプロセスを実行することができ、第2の領域内でSADPプロセスを実行することができる。さらに、LELEプロセスは、SADPプロセスによって生成される特徴間またはゲート間で実行され得る。

#### 【0020】

図2A～図2Mは、本開示の1つまたは複数の態様による半導体デバイスを作製するためのプロセスを示す。

#### 【0021】

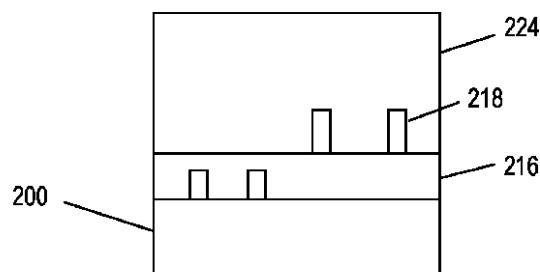

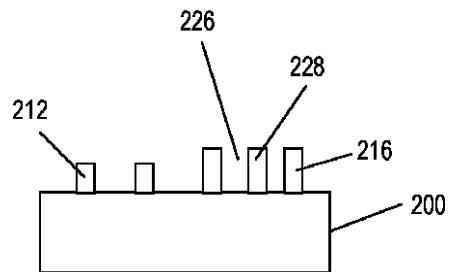

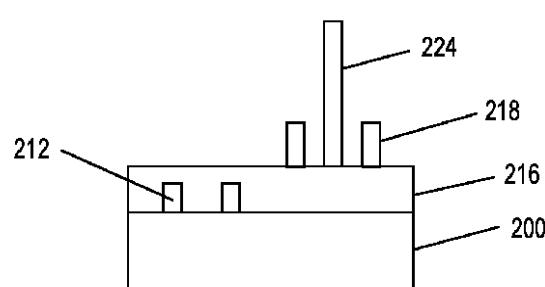

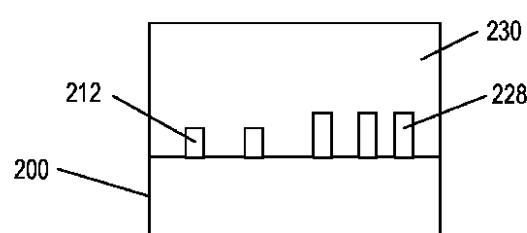

図2Aは、SADPマスクの使用を示す。ハードマスク層202および204を有する基板200を示し、ハードマスク層204上にマンドレル206を堆積させる。図2Bは、マンドレル206上のスペーサ層208の堆積を示す。図2Cは、マンドレル206のエッチング210と、ハードマスク層202および204とを示す。スペーサ層208の厚さは、SADPプロセスにおいてゲート長を定義する。図2Dは、スペーサ層208とハードマスク層204とが除去され、基板200上にゲート長パターン212が残されることを示す。図2Eは、フォトレジスト(PR)層214、およびハードマスク層216、218の堆積を示す。図2Fでは、第2のマスクが適用され、フォトレジスト層214が露出する。図2Gでは、第2のマスクが適用され、フォトレジスト層214が露出する。

#### 【0022】

本開示では、SADPマスクは、基板200の第1の領域内に第1のゲートのパターンを作成し、基板200の第1の領域内でLELEパターンが実行される。したがって、本開示の一態様では、SADPデバイスおよびLELEデバイスは、基板200の第1の領域内で互いにインターリープされ得るか、または互いに隣接し得る。

10

20

30

40

50

## 【0023】

さらに、第1の領域内のSADPパターンは、第1のゲート長と第1のコンタクトポリシリコンピッチ(CPP)とを作成する。第1のCPPは、単一パターンリソグラフィ限界よりも小さい場合がある。第1の領域内のLELEパターンは、第2のゲート長または第2のCPPを作成し、この場合、第2のCPPはやはり単一パターンリソグラフィ限界よりも小さい。第2のゲート長は第1のゲート長とは異なる場合がある。限定ではなく、一例として、第1のCPPおよび第2のCPPは40ナノメートルから80ナノメートルにわたる場合があるのに対して、第1のゲート長および第2のゲート長は10ナノメートルから30ナノメートルにわたる場合がある。

## 【0024】

10

図2Gは、エッチ222によるハードマスク層除去を示す。図2Hは、第2のフォトレジスト224適用を示す。図2Iは、第3のマスク、第2のフォトレジスト224をパターンングする第2のLELEパターンの使用を示す。図2Jは、第2のLELEパターンに基づいて、ゲート長パターン228を作成するための、ハードマスク層216のエッチ226を示す。図2Kは、別のフォトレジスト230堆積を示す。図2Lは切断マスクのパターンングを示す。図2Mは、本開示の一態様による、基板200内にゲート長パターン212および228を作成するための、基板200内へのエッチング232を示す。

## 【0025】

図3Aは、本開示の1つまたは複数の態様による半導体デバイスの側面図を示す。エリア300は、改善された限界次元均一性を有し、デバイス間のピッチ変動がより少ない、より小さなピッチ(CPP)304におけるSADPパターンゲート長302を示す。エリア306は、より小さなCPPであり得るか、またはエリア300におけるのと同じCPP310であり得る第2のピッチ(CPP)310におけるLELEパターンゲート長308を示す。エリア312は、図1A～図1Jに関して説明したLELEプロセスを使用して作られることが可能な、より大きなピッチ(CPP)316におけるより大きなゲート長314を示す。

20

## 【0026】

図3Bは、本開示の1つまたは複数の態様による半導体デバイスの側面図を示す。複数のデバイスは、最初に、より小さなピッチ(CPP)304においてSADPパターンゲート長302で形成される。図3Cで、基板100上の同じ領域またはエリア内でLELEセルスワップが実行される。本開示のこの態様では、SADPパターンゲート長302よりも大きいLELEパターンゲート長308を有するLELEパターンデバイスの対を作製するために、LELEセルスワッププロセスが実行される。LELEパターンゲート長デバイスに関するピッチは、ピッチ304と同じであり得る。

30

## 【0027】

図4は、本開示の一態様によるデバイスを作製するための方法400を示すプロセスフロー図である。ブロック402で、第1のリソグラフィプロセスを用いて、第1のゲート長と第1のコンタクトポリシリコンピッチ(CPP)とを有する、少なくとも1つの第1のゲートをパターンングする。第1のCPPは単一パターンリソグラフィ限界よりも小さい。たとえば、図1A～図1Jに示すようにSADPを使用して第1のゲートをパターンングする。ブロック404で、第2のリソグラフィプロセスを用いて、第2のゲート長または第2のCPPを有する第2のゲートがパターンングされる。第2のCPPは単一パターンリソグラフィ限界よりも小さく、第2のゲート長は第1のゲート長とは異なる。たとえば、第2のゲートは、図2A～図2MのLELEプロセスを使用してパターンングされる。

40

## 【0028】

本開示のさらなる態様によれば、半導体装置について説明される。一構成では、本装置は、第1のゲート長と第1のコンタクトポリシリコンピッチ(CPP)とを有する、電流を選択的に伝導するため第1の手段を含む。第1の手段は、図3のエリア300で説明したSADPプロセスを使用して作られたトランジスタであり得る。本装置はまた、第2の

50

ゲート長または第2のCPPを有する、少なくとも1つの第2のゲート長デバイスを有する電流を選択的に伝導するための第2の手段を含む。第2の手段は、図3のエリア306またはエリア312で説明したLELEプロセスを使用して作られたトランジスタであり得る。別の態様では、前述の手段は、前述の手段によって具陳された機能を実行するよう構成された任意のモジュールまたは任意の装置であり得る。

【0029】

図5は、本開示の一態様が有利に採用され得る例示的なワイヤレス通信システム500を示すブロック図である。説明のために、図5は、3つの遠隔ユニット520、530、および550と、2つの基地局540とを示す。ワイヤレス通信システムは、より多くの遠隔ユニットおよび基地局を有し得ることを理解されよう。遠隔ユニット520、530および550は、I Cデバイス525A、525Cおよび525Bを含み、これらは開示するデバイスを含む。基地局、スイッチングデバイス、ネットワーク機器などの他のデバイスも、開示するデバイスを含み得ることを認識されよう。図5は、基地局540から遠隔ユニット520、530、および550への順方向リンク信号580、ならびに遠隔ユニット520、530、および550から基地局540への逆方向リンク信号590を示す。

10

【0030】

図5では、遠隔ユニット520はモバイル電話として示され、遠隔ユニット530はポータブルコンピュータとして示され、遠隔ユニット550は、ワイヤレスローカルループシステムにおける固定位置遠隔ユニットとして示されている。たとえば、遠隔ユニットは、モバイル電話、ハンドヘルドパーソナル通信システム(PCS)ユニット、携帯情報端末などのポータブルデータユニット、GPS対応デバイス、ナビゲーションデバイス、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、検針機器などの固定位置データユニット、またはデータもしくはコンピュータ命令を記憶する、もしくは取り出す他のデバイス、あるいはそれらの組合せとすることができます。図5は本開示の態様による遠隔ユニットを示すが、本開示は、これらの示された例示的なユニットに限定されない。本開示の態様は、開示したデバイスを含む多くのデバイスにおいて、適切に採用され得る。

20

【0031】

図6は、上記で開示したデバイスなどの半導体構成要素の回路設計、レイアウト設計、および論理設計に使用される設計用ワークステーションを示すブロック図である。設計用ワークステーション600は、オペレーティングシステムソフトウェア、サポートファイル、およびCadenceやOrCADなどの設計ソフトウェアを収容するハードディスク601を含む。設計用ワークステーション600はまた、本開示の一態様によるデバイスなど、回路610または半導体構成要素612の設計を容易にするために、ディスプレイ602を含む。記憶媒体604は、回路610または半導体構成要素612の設計を有形に記憶するために提供される。回路610または半導体構成要素612の設計は、GDSIIまたはGERBERなどのファイルフォーマットにおいて記憶媒体604に記憶され得る。記憶媒体604は、CD-ROM、DVD、ハードディスク、フラッシュメモリ、または他の適切なデバイスであり得る。さらに、設計用ワークステーション600は、記憶媒体604からの入力を受け入れるか、または記憶媒体604への出力を書き込むための駆動装置603を含む。

30

【0032】

記憶媒体604上に記録されるデータは、論理回路構成、フォトリソグラフィマスク用のパターンデータ、または電子ビームリソグラフィなどの連続描画ツール用のマスクパターンデータを指定することができる。データはさらに、論理シミュレーションに関連するタイミングダイアグラムまたはネット回路などの論理検証データをさらに含み得る。記憶媒体604にデータを提供すると、半導体ウエハを設計するためのプロセス数を削減させることによって、回路610または半導体構成要素612の設計が容易になる。

40

【0033】

50

ファームウェアおよび／またはソフトウェアによる実装の場合、本明細書において説明した機能を実行するモジュール（たとえば手続き、関数など）を用いて、方法を実装することができる。本明細書において説明した方法を実装する際に、命令を有形に具現化する機械可読媒体を使用することができる。たとえば、ソフトウェアコードをメモリに記憶させ、プロセッサユニットによって実行することができる。メモリは、プロセッサユニット内またはプロセッサユニットの外部に実装されていてよい。本明細書では、「メモリ」という用語は、長期メモリ、短期メモリ、揮発性メモリ、不揮発性メモリ、または他のメモリのタイプを指し、特定のタイプのメモリもしくは特定の数のメモリ、またはメモリが格納される媒体のタイプに限定すべきではない。

## 【0034】

10

機能は、ファームウェアおよび／またはソフトウェアとして実装する場合、1つもしくは複数の命令またはコードとしてコンピュータ可読媒体上に記憶させることができる。例として、データ構造を符号化したコンピュータ可読媒体、およびコンピュータプログラムを符号化したコンピュータ可読媒体がある。コンピュータ可読媒体は、物理的なコンピュータ記憶媒体を含む。記憶媒体は、コンピュータがアクセスすることのできる利用可能な媒体とすることができます。限定ではなく、例として、そのようなコンピュータ可読媒体は、RAM、ROM、EEPROM、CD-ROMもしくは他の光ディスクストレージ、磁気ディスクストレージもしくは他の磁気記憶デバイス、または、所望のプログラムコードを命令もしくはデータ構造の形で記憶するのに使用することができ、かつコンピュータによってアクセスされ得る他の媒体を含むことができ、本明細書で使用されるディスク（disk および disc）は、コンパクトディスク（disc）（CD）、レーザディスク（disc）、光ディスク（disc）、デジタル多用途ディスク（disc）（DVD）、フロッピーディスク（disk）、およびBlu-ray（登録商標）ディスク（disc）を含み、ディスク（disk）は通常、データを磁気的に再生するが、ディスク（disc）はデータをレーザによって光学的に再生する。上記のものの組合せも、コンピュータ可読媒体の範囲内に含まれるべきである。

20

## 【0035】

30

コンピュータ可読媒体におけるストレージに加えて、命令および／またはデータは、通信装置内に含まれる伝送媒体における信号として提供することができる。たとえば、通信装置は、命令およびデータを示す信号を有するトランシーバを含むことができる。命令およびデータは、1つまたは複数のプロセッサに、特許請求の範囲において概説される機能を実装させるように構成される。

## 【0036】

40

以上、本開示およびその利点について詳細に説明してきたが、添付の特許請求の範囲によって定められる本開示の技術から逸脱することなく、本明細書において様々な変更、置換、および改変を行えることを理解されたい。たとえば、「上」および「下」などの関係性の用語が、基板または電子デバイスに関して使用される。当然、基板または電子デバイスが反転した場合、上は下に、下は上になる。加えて、横向きの場合、上および下は、基板または電子デバイスの側面を指す場合がある。さらに、本出願の範囲は、本明細書で説明したプロセス、機械、製造、組成物、手段、方法、およびステップの特定の構成に限定されることは意図されない。当業者が本開示から容易に諒解するように、本明細書で説明した対応する構成と実質的に同じ機能を実行するか、もしくは実質的に同じ結果を実現する、現存するもしくは今後開発されるプロセス、機械、製造、組成物、手段、方法、またはステップが、本開示に従って利用され得る。したがって、添付の特許請求の範囲は、そのようなプロセス、機械、製造、組成物、手段、方法、またはステップをそれらの範囲内に含むものとする。

## 【0037】

本明細書で本開示に関連して説明された様々な例示的論理ブロック、モジュール、回路、およびアルゴリズムステップが、電子ハードウェア、コンピュータソフトウェア、または両方の組合せとして実装され得ることを当業者ならさらに理解されよう。ハードウェア

50

とソフトウェアのこの互換性を明確に示すために、様々な例示的構成要素、ブロック、モジュール、回路、およびステップが、上記ではその機能に関して一般的に説明された。そのような機能がハードウェアとして実装されるか、それともソフトウェアとして実装されるかは、特定の応用分野およびシステム全体に対して課される設計制限に依存する。当業者は、説明された機能を各々の特定の応用分野について様々な方式で実装し得るが、そのような実装判断は、本開示の範囲からの逸脱を引き起こすと解釈されるべきではない。

#### 【0038】

本明細書の開示に関連して説明した様々な例示的論理ブロック、モジュール、および回路は、本明細書で説明した機能を実施するように設計された汎用プロセッサ、デジタル信号プロセッサ (D S P)、特定用途向け集積回路 (A S I C)、フィールドプログラマブルゲートアレイ (F P G A) もしくは他のプログラマブル論理デバイス、ディスクリートゲートもしくはトランジスタロジック、ディスクリートハードウェア構成要素、またはそれらの任意の組合せとともに実装あるいは実施され得る。汎用プロセッサはマイクロプロセッサでよいが、別の方法として、プロセッサは、任意の従来型プロセッサ、コントローラ、マイクロコントローラまたはステートマシンでよい。プロセッサはまた、コンピューティングデバイスの組合せ、たとえば、D S Pとマイクロプロセッサとの組合せ、複数のマイクロプロセッサ、D S Pコアと連携する1つもしくは複数のマイクロプロセッサ、または任意の他のそのような構成として実装され得る。

#### 【0039】

本開示に関連して説明した方法またはアルゴリズムのステップは、ハードウェアで直接的に、プロセッサによって実行されるソフトウェアモジュールで、またはその2つの組合せで実施され得る。ソフトウェアモジュールは、R A M、フラッシュメモリ、R O M、E P R O M、E E P R O M、レジスタ、ハードディスク、リムーバブルディスク、C D - R O M、または当技術分野で知られている任意の他の形態の記憶媒体に常駐することができる。例示的記憶媒体がプロセッサに結合され、プロセッサが記憶媒体から情報を読み取ること、および記憶媒体に情報を書き込むことができるようになる。代替案では、記憶媒体は、プロセッサに一体とされ得る。プロセッサおよび記憶媒体は、A S I C内に存在し得る。A S I Cは、ユーザ端末内に存在し得る。代替として、プロセッサおよび記憶媒体は、ユーザ端末内にディスクリート構成要素として存在し得る。

#### 【0040】

1つまたは複数の例示的設計では、説明される機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組合せで実装され得る。ソフトウェアで実装される場合、機能は、コンピュータ可読記憶媒体上に1つもしくは複数の命令またはコードとして格納あるいは送信され得る。コンピュータ可読媒体は、コンピュータ記憶媒体と、コンピュータプログラムの1つの場所から別の場所への転送を容易にする任意の媒体を含む通信媒体との両方を含む。記憶媒体は、汎用または特殊用途コンピュータによってアクセスされ得る任意の使用可能な媒体であってもよい。限定ではなく例として、そのようなコンピュータ可読媒体は、R A M、R O M、E E P R O M、C D - R O M、もしくは他の光ディスクストレージ、磁気ディスクストレージもしくは他の磁気記憶デバイス、あるいは命令またはデータ構造の形態の規定のプログラムコード手段を搬送もしくは格納するために使用され得、汎用もしくは専用コンピュータ、または汎用もしくは専用プロセッサによってアクセスされ得る任意の他の媒体を含み得る。また、任意の接続が適切にコンピュータ可読媒体と呼ばれる。たとえば、ソフトウェアが、同軸ケーブル、光ファイバケーブル、ツイストペア、デジタル加入者線 (「D S L」)、もしくは赤外線、無線、およびマイクロ波などのワイヤレス技術を使用してウェブサイト、サーバ、または他の遠隔ソースから送信される場合、同軸ケーブル、光ファイバケーブル、ツイストペア、D S L、または赤外線、無線、およびマイクロ波などのワイヤレス技術は、媒体の定義に含まれる。本明細書で使用する場合、ディスク (d i s k) およびディスク (d i s c) は、コンパクトディスク (d i s c) (C D)、レーザディスク (d i s c)、光ディスク (d i s c)、デジタル多用途ディスク (d i s c) (D V D)、フロッピーディスク (d i s k) お

10

20

30

40

50

およびBlue-ray(登録商標)ディスク(disc)を含み、ディスク(disk)は、通常、データを磁気的に再生し、ディスク(disc)は、データをレーザで光学的に再生する。上記のものの組合せも、コンピュータ可読媒体の範囲内に含まれるべきである。

【0041】

本開示の前述の説明は、いかなる当業者も本開示を作製または使用できるようにするために提供される。本開示に対する様々な修正形態が当業者には容易に明らかとなり、本明細書で定義する一般原理は、本開示の趣旨または範囲から逸脱することなく、他の変形形態に適用され得る。したがって、本開示は、本明細書で説明する例および設計に限定されるものではなく、本明細書で開示する原理および新規の特徴に合致する最も広い範囲を与えられるべきである。

10

【符号の説明】

【0042】

|     |              |    |

|-----|--------------|----|

| 100 | 基板           |    |

| 102 | 層            |    |

| 104 | マスク          |    |

| 106 | マスキングエリア     |    |

| 108 | 層            |    |

| 110 | エリア          | 20 |

| 112 | エリア          |    |

| 114 | メサ           |    |

| 116 | 層            |    |

| 118 | エッジ          |    |

| 120 | エッジ          |    |

| 122 | エリア          |    |

| 124 | エリア          |    |

| 128 | メサ           |    |

| 130 | メサ           |    |

| 200 | 基板           |    |

| 202 | ハードマスク層      | 30 |

| 204 | ハードマスク層      |    |

| 206 | マンドレル        |    |

| 208 | スペーサ層        |    |

| 210 | エッチング        |    |

| 212 | ゲート長パターン     |    |

| 214 | フォトレジスト(PR)層 |    |

| 216 | ハードマスク層      |    |

| 218 | ハードマスク層      |    |

| 220 | 露出すなわちパターニング |    |

| 222 | エッチ          | 40 |

| 224 | 第2のフォトレジスト   |    |

| 226 | エッチ          |    |

| 228 | ゲート長パターン     |    |

| 230 | フォトレジスト      |    |

| 232 | エッチング        |    |

| 300 | エリア          |    |

| 302 | SADPパターンゲート長 |    |

| 304 | ピッチ(CPP)     |    |

| 306 | エリア          |    |

| 308 | LELEパターンゲート長 | 50 |

|         |                    |    |

|---------|--------------------|----|

| 3 1 0   | 第 2 のピッチ ( C P P ) |    |

| 3 1 2   | エリア                |    |

| 3 1 4   | ゲート長               |    |

| 3 1 6   | ピッチ ( C P P )      |    |

| 4 0 0   | 方法                 |    |

| 5 0 0   | ワイヤレス通信システム        |    |

| 5 2 0   | 遠隔ユニット             |    |

| 5 2 5 A | I C デバイス           | 10 |

| 5 2 5 B | I C デバイス           |    |

| 5 2 5 C | I C デバイス           |    |

| 5 3 0   | 遠隔ユニット             |    |

| 5 4 0   | 基地局                |    |

| 5 5 0   | 遠隔ユニット             |    |

| 5 8 0   | 順方向リンク信号           |    |

| 5 9 0   | 逆方向リンク信号           |    |

| 6 0 0   | 設計用ワークステーション       |    |

| 6 0 1   | ハードディスク            |    |

| 6 0 2   | ディスプレイ             |    |

| 6 0 3   | 駆動装置               |    |

| 6 0 4   | 記憶媒体               | 20 |

| 6 1 0   | 回路                 |    |

| 6 1 2   | 半導体構成要素            |    |

【図 1 A】

【図 1 B】

【図 1 C】

FIG. 1C

【図 1 D】

FIG. 1D

【図 1 E】

FIG. 1E

【図 1 F】

FIG. 1F

【図 1 H】

FIG. 1H

【図 1 G】

FIG. 1G

【図 1 I】

FIG. 1I

【図 1 J】

FIG. 1J

【図 2 A】

FIG. 2A

FIG. 2B

【図 2 C】

**FIG. 2C**

【図 2 D】

**FIG. 2D**

【図 2 F】

**FIG. 2F**

【図 2 G】

**FIG. 2G**

【図 2 H】

FIG. 2H

【図 2 J】

FIG. 2J

【図 2 I】

FIG. 2I

【図 2 K】

FIG. 2K

【図 2 L】

FIG. 2L

【図 3 A】

FIG. 3A

【図 2 M】

FIG. 2M

【図3B】

FIG. 3B

【図3C】

FIG. 3C

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

---

フロントページの続き

(51)Int.Cl. F I

G 03 F 7/20 (2006.01) G 03 F 7/20 521

(72)発明者 ジョンゼ・ワン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 チョ・フェイ・イエブ

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

審査官 市川 武宜

(56)参考文献 米国特許出願公開第2011/0156755(US, A1)

米国特許出願公開第2012/0180016(US, A1)

国際公開第2012/097101(WO, A1)

特開2013-149983(JP, A)

米国特許出願公開第2005/0153562(US, A1)

米国特許出願公開第2013/0089984(US, A1)

特開2012-169426(JP, A)

米国特許出願公開第2012/0164837(US, A1)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/8234

G 03 F 7/20

H 01 L 21/28

H 01 L 21/336

H 01 L 27/088

H 01 L 29/78