(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-182426

(P2012-182426A)

(43) 公開日 平成24年9月20日(2012.9.20)

(51) Int.Cl.

H01L 27/14 (2006.01)

H01L 27/146 (2006.01)

F 1

H01L 27/14

H01L 27/14D

A

テーマコード(参考)

4M118

審査請求 未請求 請求項の数 12 O L (全 29 頁)

(21) 出願番号 特願2011-223291 (P2011-223291)

(22) 出願日 平成23年10月7日 (2011.10.7)

(31) 優先権主張番号 特願2011-26347 (P2011-26347)

(32) 優先日 平成23年2月9日 (2011.2.9)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 滝本 俊介

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 岡部 剛士

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】 固体撮像装置、固体撮像装置を用いた撮像システム及び固体撮像装置の製造方法

## (57) 【要約】

【課題】 導波路を有する固体撮像装置において、反射防止膜の光学特性の低下を抑制する。

【解決手段】 半導体基板に配された光電変換部と、光電変換部の上に配された反射防止として機能する第1の絶縁膜と、光電変換部に対応して第1の絶縁膜の上に配された第2の絶縁膜と、第2の絶縁膜の上に底面が配されたコアと、クラッドとを有する導波路と、を有する固体撮像装置の製造方法において、光電変換部の上部に配された部材の一部を異方性のエッチングにて除去し開口を形成することでクラッドを構成する工程と、開口にコアを形成する工程と、を有し、開口を形成する工程において、部材がエッチングされる速度よりも第2の絶縁膜がエッチングされる速度が低い条件で、部材がエッチングされる。

【選択図】 図6

**【特許請求の範囲】****【請求項 1】**

半導体基板に配された光電変換部と、

前記光電変換部の上に配された反射防止として機能する第1の絶縁膜と、

前記光電変換部に対応して前記第1の絶縁膜の上に配された第2の絶縁膜と、

前記第2の絶縁膜の上に底面が配されたコアと、クラッドとを有する導波路と、

を有する固体撮像装置の製造方法において、

前記光電変換部の上部に配された部材の一部をエッティングにて除去し開口を形成することで前記クラッドを構成する工程と、

前記開口にコアを形成する工程と、を有し、

前記開口を形成する工程において、前記部材がエッティングされる速度よりも前記第2の絶縁膜がエッティングされる速度が低い条件で、前記部材がエッティングされることを特徴とする固体撮像装置の製造方法。

**【請求項 2】**

前記第1の絶縁膜は、多層の反射防止膜である請求項1に記載の固体撮像装置の製造方法。

**【請求項 3】**

前記第1の絶縁膜は、窒化シリコンからなる絶縁膜と、前記窒化シリコンからなる絶縁膜の上に配された酸化シリコンからなる絶縁膜とを含む請求項1あるいは2のいずれか1項に記載の固体撮像装置の製造方法。

**【請求項 4】**

前記半導体基板には、前記光電変換部の信号電荷を転送するゲート電極を有し、

前記第1の絶縁膜は、前記光電変換部の上から前記ゲート電極の上に延在していることを特徴とする請求項1乃至3のいずれか1項に記載の固体撮像装置の製造方法。

**【請求項 5】**

前記コアと前記第2の絶縁膜とが同一の材料からなることを特徴とする請求項1乃至4のいずれか1項に記載の固体撮像装置の製造方法。

**【請求項 6】**

半導体基板に配された複数の光電変換部と、

前記複数の光電変換部の上に配置された反射防止膜として機能する第1の絶縁膜と、

前記第1の絶縁膜の上に、前記複数の光電変換部に対応して設けられた、エッティングス

トップ膜として機能する複数の第2の絶縁膜と、

底面が前記第2の絶縁膜と接し、前記第2の絶縁膜と同一の材料からなるコアと、クラ

ッドとを有する複数の導波路と、を有する固体撮像装置。

**【請求項 7】**

半導体基板に配された複数の光電変換部と、

前記複数の光電変換部の上に配置された反射防止膜として機能する第1の絶縁膜と、

前記第1の絶縁膜の上に、前記複数の光電変換部に対応して設けられた複数の第2の絶

縁膜と、

底面が前記第2の絶縁膜と接し、前記第2の絶縁膜と同じ材料からなるコアと、クラッ

ドとを有する複数の導波路と、

を有する固体撮像装置。

**【請求項 8】**

前記複数の第2の絶縁膜は、前記複数の光電変換部と1対1で対応して設けられていることを特徴とする請求項7に記載の固体撮像装置。

**【請求項 9】**

前記複数の光電変換部の信号電荷を転送する複数のゲート電極を有し、

前記第1の絶縁膜が前記ゲート電極を覆って延在していることを特徴とする請求項7あるいは8のいずれか1項に記載の固体撮像装置。

**【請求項 10】**

10

20

30

40

50

前記第1の絶縁膜は、窒化シリコンからなる絶縁膜と、前記窒化シリコンからなる絶縁膜の上に配された酸化シリコンからなる絶縁膜とを含み、

前記第2の絶縁膜は、窒化シリコンからなる請求項7乃至9のいずれか1項に記載の固体撮像装置。

【請求項11】

前記ゲート電極の上面よりも前記第2の絶縁膜の上面は前記半導体基板の近くに配置されている請求項9に記載の固体撮像装置。

【請求項12】

請求項6乃至11のいずれか1項に記載の固体撮像装置と、

前記固体撮像装置からの電気信号を処理する信号処理装置と、を有する撮像システム。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は固体撮像装置、固体撮像装置を用いた撮像システム及び固体撮像装置の製造方法に関する。

【背景技術】

【0002】

近年、光電変換部に入射する光量を増やすため、導波路を有する固体撮像装置が提案されている。特許文献1には、導波路を有する固体撮像装置において、導波路を形成する際のエッチングストップ膜と、受光部上の反射防止膜とを兼ねることが記載されている。

20

【0003】

また、特許文献2には、コンタクト用の開口を形成するためのエッチングにおける、エッティングストップ膜を画素部に設けることが開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2006-191000号公報

【特許文献2】特開2008-041726号公報

【発明の概要】

【発明が解決しようとする課題】

30

【0005】

特許文献1の導波路を形成する際のエッティングストップ膜は、その一部がエッティングされて膜厚が変わってしまう、又はエッティングのダメージを受ける可能性がある。このため、反射防止膜としての光学特性が低下してしまう可能性がある。

【0006】

また、特許文献2では、画素部以外の領域におけるコンタクト用の開口を形成するためのエッティングにおけるエッティングストップ膜については考慮されていない。エッティングの際にダメージが生じると、ノイズが生じてしまい、画像の品質が低下する可能性がある。

本発明は上記の課題の少なくとも一つを解決することを目的とする。

【課題を解決するための手段】

【0007】

本発明の固体撮像装置の製造方法は、半導体基板に配された光電変換部と、前記光電変換部の上に配された反射防止として機能する第1の絶縁膜と、前記光電変換部に対応して前記第1の絶縁膜の上に配された第2の絶縁膜と、前記第2の絶縁膜の上に底面が配されたコアと、クラッドとを有する導波路と、を有する固体撮像装置の製造方法において、前記光電変換部の上部に配された部材の一部をエッティングにて除去し開口を形成することで前記クラッドを構成する工程と、前記開口にコアを形成する工程と、を有し、前記開口を形成する工程において、前記部材がエッティングされる速度よりも前記第2の絶縁膜がエッティングされる速度が低い条件で、前記部材がエッティングされる。

【0008】

40

50

本発明の固体撮像装置は、半導体基板に配された複数の光電変換部と、前記複数の光電変換部の上に配置された反射防止膜として機能する第1の絶縁膜と、前記第1の絶縁膜の上に、前記複数の光電変換部に対応して設けられた複数の第2の絶縁膜と、底面が前記第2の絶縁膜と接し、前記第2の絶縁膜と同じ材料からなるコアと、クラッドとを有する複数の導波路と、を有する。

【発明の効果】

【0009】

本発明の固体撮像装置の製造方法によって、例えば、導波路を有する固体撮像装置において、反射防止膜の光学特性の低下を抑制することが可能となる。

【図面の簡単な説明】

【0010】

【図1】実施例1の固体撮像装置の画素セルの回路図。

【図2】実施例1の固体撮像装置の画素セルの平面レイアウトを示す図。

【図3】実施例1の固体撮像装置の製造方法を示す図。

【図4】実施例1の固体撮像装置の製造方法を示す図。

【図5】実施例1の固体撮像装置の製造方法を示す図。

【図6】実施例1の固体撮像装置の断面模式図。

【図7】実施例1を説明する平面レイアウトを示す模式図。

【図8】実施例1の変形例を説明する平面レイアウトを示す模式図。

【図9】実施例2の固体撮像装置の断面模式図。

【図10】固体撮像装置及び撮像システムを説明するブロック図。

【図11】実施例4の固体撮像装置の製造方法を示す図。

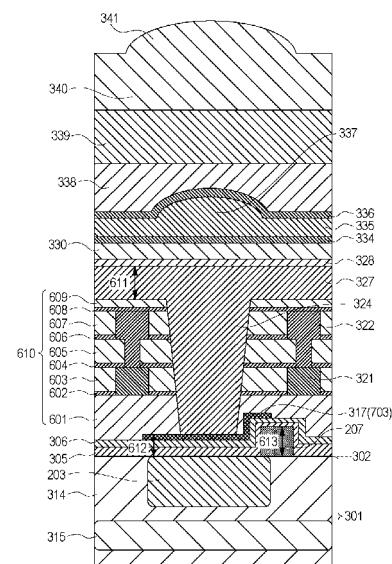

【図12】実施例5の固体撮像装置の断面模式図。

【図13】実施例5の固体撮像装置の製造方法を示す図。

【図14】実施例6の固体撮像装置の断面模式図。

【図15】実施例7の固体撮像装置の断面模式図。

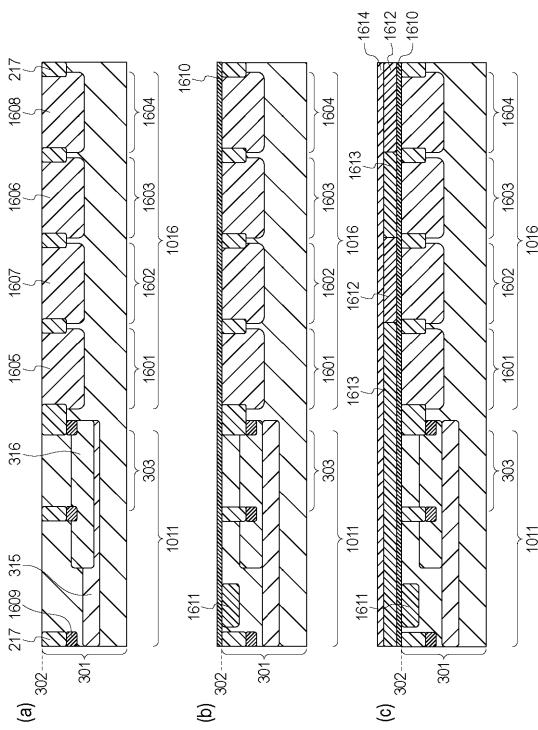

【図16】実施例8の固体撮像装置の製造方法を示す断面模式図。

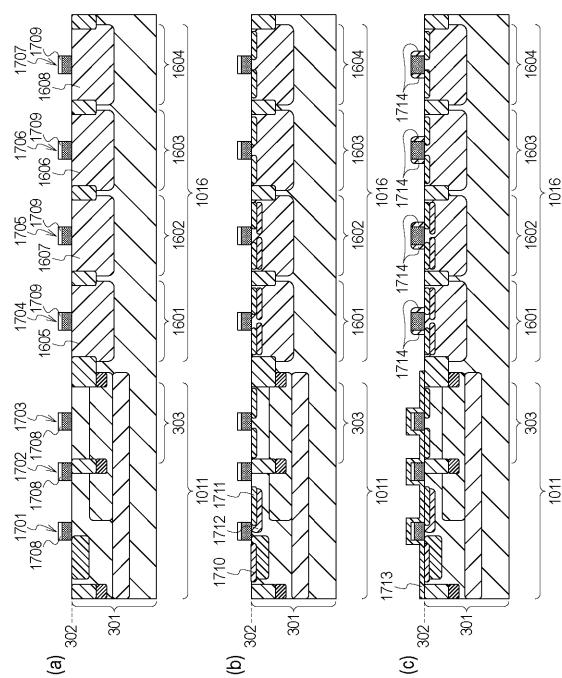

【図17】実施例8の固体撮像装置の製造方法を示す断面模式図。

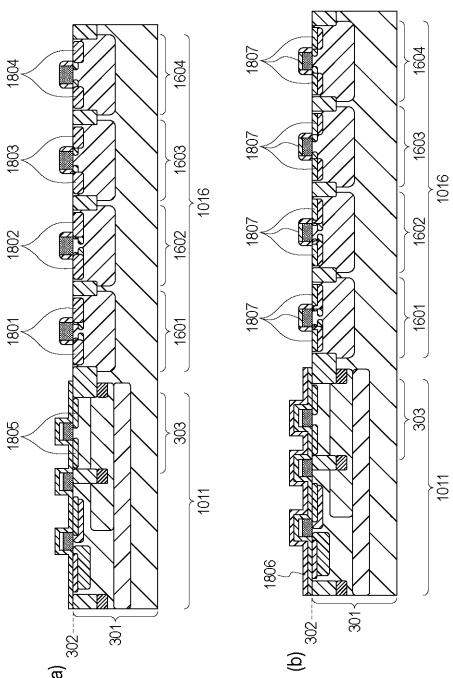

【図18】実施例8の固体撮像装置の製造方法を示す断面模式図。

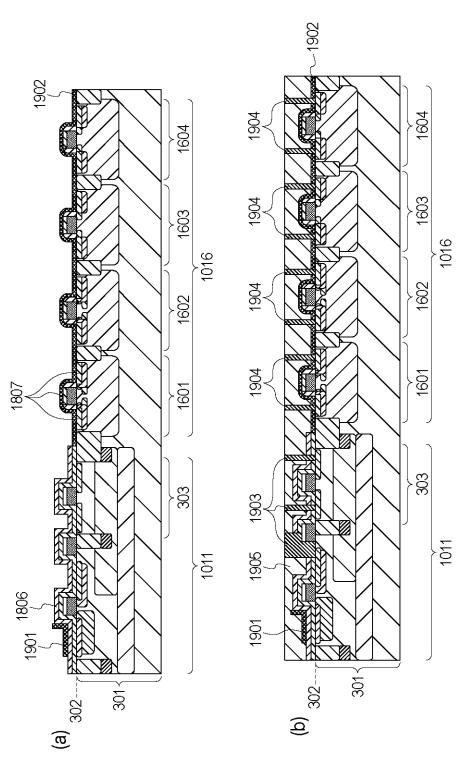

【図19】実施例8の固体撮像装置の製造方法を示す断面模式図。

【図20】実施例8の固体撮像装置を説明するための断面模式図。

【図21】実施例9の固体撮像装置を説明するための断面模式図。

【発明を実施するための形態】

【0011】

本発明は、例えば、半導体基板に配された光電変換部と、第1の絶縁膜と、第2の絶縁膜と、導波路と、を有する固体撮像装置の製造方法に関する。第1の絶縁膜は、光電変換部の上に配された反射防止として機能する。第2の絶縁膜は、光電変換部に対応して前記第1の絶縁膜の上に配されている。そして、導波路は、第2の絶縁膜の上に底面が配されたコアと、クラッドとを有する。ここで、固体撮像装置の製造方法は、光電変換部の上部に配された部材の一部をエッチングにて除去し開口を形成することでクラッドを構成する工程と、開口にコアを形成する工程と、を有する。そして、開口を形成する工程において、部材がエッチングされる速度よりも第2の絶縁膜がエッチングされる速度が低い条件で、部材がエッチングされる。このような製造方法によって、反射防止膜の光学特性の低下を抑制することが可能となる。

【0012】

また、固体撮像装置は、半導体基板に配された複数の光電変換部と、複数の光電変換部の上に配置された反射防止膜として機能する第1の絶縁膜と、第1の絶縁膜の上に、複数の光電変換部に対応して設けられた複数の第2の絶縁膜と、を有する。そして、更に、固体撮像装置は、底面が前記第2の絶縁膜と接し、前記第2の絶縁膜と同じ材料からなるコアと、クラッドとを有する複数の導波路を有する。このような構成によって、固体撮像装

10

20

30

40

50

置の感度を向上することが可能となる。

【0013】

以下、図面を用いて本発明の実施例を説明する。ここで、一般的な半導体装置、及び製造方法に準ずる箇所については、詳細な記載を省略する。また、窒化シリコンの屈折率は酸化シリコンの屈折率よりも高く、酸窒化シリコンの屈折率はそれらの間の値になるものとする。例えば、窒化シリコンの屈折率は約1.75～2.34であり、酸化シリコンの屈折率は約1.35～1.54であるとする。また、例えば可視光の波長は、約360～830nmの範囲であるとする（岩波 理化学辞典 第5版）。

【0014】

また、開口とは、複数の層間絶縁膜を貫通する場合あるいは貫通しない場合（凹部）のいずれの場合も含み、孔とも言える。開口を用いる構成として、実施例では導波路の構成を説明するが、限定されない。また、本発明は半導体装置一般に適用可能である。また、エッチング選択比とは、ある部材のエッチングされる速度に対する別の部材のエッチングされる速度の比であり、大きいほど別の部材のみがエッチングされる。エッチング選択比が小さいほど、ある部材もエッチングされることを示す。同じ材料とは、主成分が同一材料からなるものであり、例えば、窒化シリコンという材料においては、窒素の含有量が異なる場合も同じ材料とみなす。

【実施例1】

【0015】

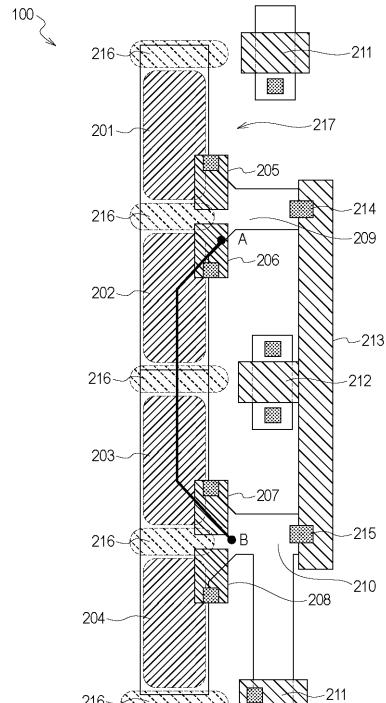

本実施例の固体撮像装置について、図1～図7、及び図10を用いて説明する。まず、図1、図2、図7及び図10を用いて、本実施例の固体撮像装置について説明する。

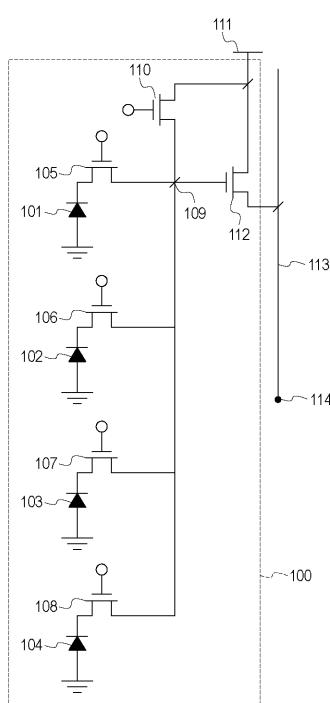

【0016】

図1は、本実施例の固体撮像装置の画素セルの回路図である。画素セル100は、4つのフォトダイオード（以下PDとする）101～104と、4つの転送トランジスタ105～108と、1つのリセットトランジスタ110と、1つの増幅トランジスタ112とを有する。そして、フローティングディフュージョンノード（以下FDノードとする）109を有する。ここで、信号電荷は電子であり、トランジスタがN型である場合について説明する。

【0017】

4つのPD101～104は、アノードがグランドに接続されており、入射光をその光量に応じた電荷に光電変換して蓄積する。4つの転送トランジスタ105～108は、それぞれ対応する4つのPD101～104にて発生した信号電荷をFDノード109に転送する転送手段として機能する。具体的には、第1のPD101と第1の転送トランジスタ105のソースが接続し、第2のPD102と第2の転送トランジスタ106のソースが接続している。そして、第3のPD103と第3の転送トランジスタ107のソースが接続し、第4のPD104と第4の転送トランジスタ108のソースが接続している。第1～第4の転送トランジスタ105～108のドレインが1つに接続しており、FDノード109を構成している。増幅トランジスタ112は、そのゲート電極がFDノード109に接続され、ドレインが電源供給線111に接続され、ソースが出力信号線113に接続されており、FDノード109の電位に基づく信号が出力信号線113に出力される。リセットトランジスタ110は、FDノード109に接続され、FDノード109の電位を任意の電位にリセットする。同時に、転送トランジスタ105～108を導通させることにより、PD101～104もリセット可能である。電源供給線111は少なくとも2つの電位を有し、FDノード109の電位を2つの値に設定することで、出力信号線113への信号の出力を行うことが出来る。なお、出力信号線には複数の画素セルが接続されているものとする。また、端子114は後述の読み出し回路に接続されている。

【0018】

少なくとも1つの光電変換部を含む繰り返し単位を画素とする、図1においては、画素セル100は4つの画素を含む。画素セル100が含む構成は、PDが4つの場合に限らず、また選択トランジスタや容量などを有していてもよい。光電変換部としてフォトダ

10

20

30

40

50

イオードを例に挙げたが、フォトゲートなどでもよい。

【0019】

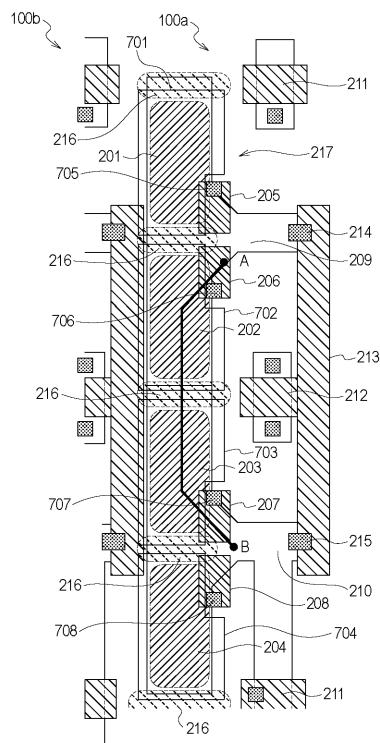

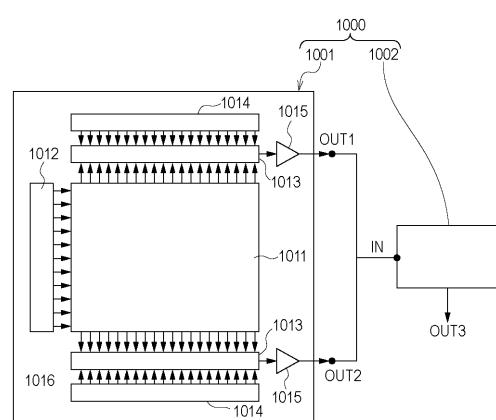

図10は、固体撮像装置及び撮像システムの概略構成を示す図である。図10において、固体撮像装置1001は、画素部1011と、垂直走査回路1012と、2つの読み出し回路1013と、2つの水平走査回路1014と、2つの出力アンプ1015を備えている。画素部1011以外の領域を周辺回路部1016と称する。

【0020】

図10において、画素部1011には、図1に示した複数の画素セルが2次元状に配列されて構成される。つまり、画素部1011には複数の画素が配列されている。各画素セルは、複数の画素を含んで構成される。読み出し回路1013は、例えば、列アンプ、CDS回路、加算回路等を含み、垂直走査回路1012によって選択された行の画素から垂直信号線を介して読み出された信号に対して増幅、加算等を行う。列アンプ、CDS回路、加算回路等は、例えば、画素列又は複数の画素列毎に配置される。水平走査回路1014は、読み出し回路1013の信号を順番に読み出すための信号を生成する。出力アンプ1015は、水平走査回路1014によって選択された列の信号を増幅して出力する。以上の構成は、固体撮像装置の一つの構成例に過ぎず、本実施形態は、これに限定されるものではない。例えば、読み出し回路1013と水平走査回路1014と出力アンプ1015とは、2系統の出力経路を構成するため、画素部1011を挟んで上下に1つずつ配置されている。しかし、出力経路は3つ以上設けられていてもよい。

【0021】

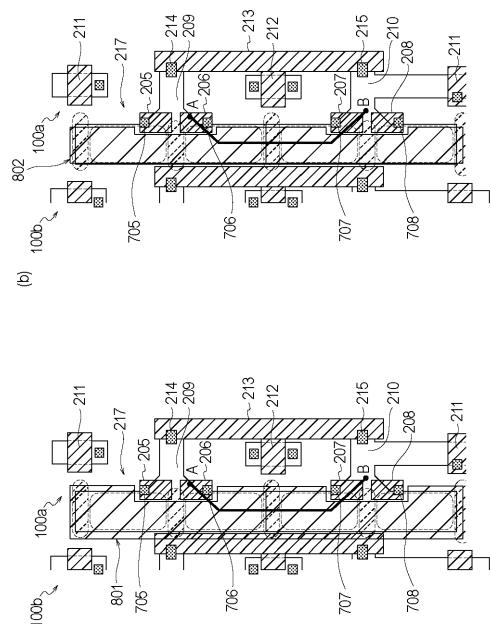

次に、図2を用いて、図1に対応した平面レイアウトを説明する。図2は、平面レイアウトを説明する模式図であり、半導体基板の正面に任意の構成の外縁を投影した図である。図2において、第1～第4のPD201～204が配置されている。ここでは、簡単のためにPDの一部である電荷蓄積領域(N型半導体領域)の部分を示している。第1～第4のPD201～204に対応して第1～第4の転送トランジスタのゲート電極205～208が配置されている。そして、第1の転送トランジスタのドレインと第2の転送トランジスタのドレインは共通の領域からなり、第1のフローティングディフュージョン領域209(以下、第1のFD領域)である。第3の転送トランジスタのドレインと第4の転送トランジスタのドレインは共通の領域からなり、第2のフローティングディフュージョン領域210(以下、第2のFD領域)である。この第1のFD領域209と第2のFD領域210と増幅トランジスタのゲート電極212とを接続配線213が接続している。増幅トランジスタのゲート電極212と接続配線213とは一体となっている。第1のFD領域209と接続配線213とをシェアードコンタクト214が接続し、第2のFD領域210と接続配線213とはシェアードコンタクト215とで接続されている。シェアードコンタクトとは、半導体領域同士、半導体領域とゲート電極との間、あるいはゲート電極同士を、配線層を介することなく接続するコンタクトのことである。また、図2においては、第2のFD領域210がリセットトランジスタのソースあるいはドレインと共通の領域となっている。211はリセットトランジスタのゲート電極である。

【0022】

ここで、図2において、PDとトランジスタのソース・ドレイン及びチャネルとなる領域とが形成された領域は活性領域であり、その他の領域は素子分離領域217となっている。また、活性領域のPDとPDの間や転送トランジスタのゲート電極とゲート電極との間には、半導体領域である信号電荷に対するポテンシャルバリア216が配置されている。ポテンシャルバリア216はPDとPDとの間の信号電荷の行き来を抑制する、素子分離領域としての機能を有する。

【0023】

ここで、図7を用いて、エッチングストップ膜について説明する。図7は図2に対応した平面レイアウトを説明する模式図である。図7では、画素セル100aと隣接する画素セル100bの一部が示されている。図7では、図2の平面レイアウトにエッチングストップ膜として機能する絶縁膜701～704が配置されている。絶縁膜701～704は

10

20

30

40

50

、電荷蓄積領域と1対1で配置されている。絶縁膜701～704は、例えば、窒化シリコンからなる。絶縁膜701～704は光電変換部の受光面よりも平面的に面積が大きく、絶縁膜701～704の外縁が光電変換部である電荷蓄積領域201～204に可能な限り重ならないように配置されている。これは、絶縁膜701～704をパターニングによって形成する際のエッチング等のダメージが電荷蓄積領域201～204に与えられるのを防ぐためである。よって、図7において絶縁膜701～704は、各転送トランジスタのゲート電極205～208と、隣接する画素セル100bの接続配線213の上に重なるように配置されている。後に説明する開口を形成するエッチングの際に、ゲート電極や配線にダメージを与えないためである。

## 【0024】

また、絶縁膜701～704は、ゲート電極205～208の上に配置されるコンタクト705～708や、他のトランジスタのコンタクトが配置される領域と重ならないように配置される。これは、コンタクト705～708や他のトランジスタのコンタクトを形成する際に、製造を簡易にするための構成である。

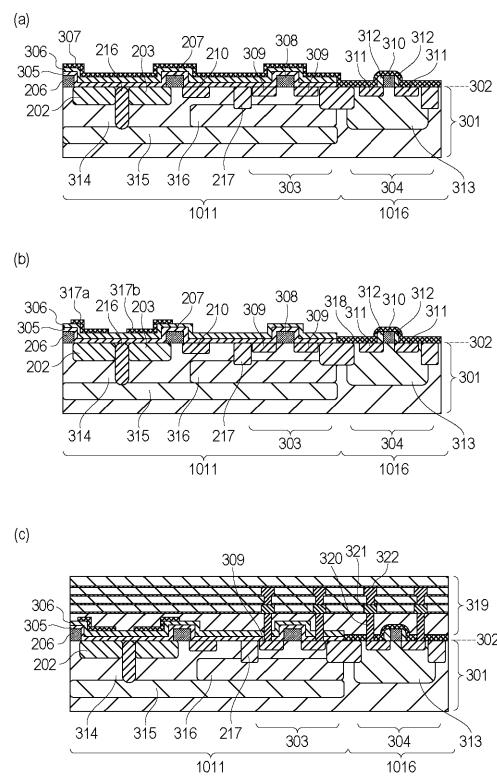

## 【0025】

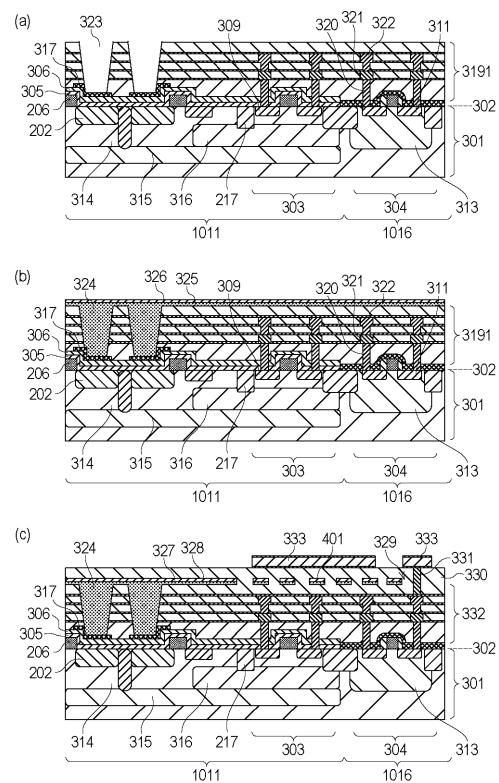

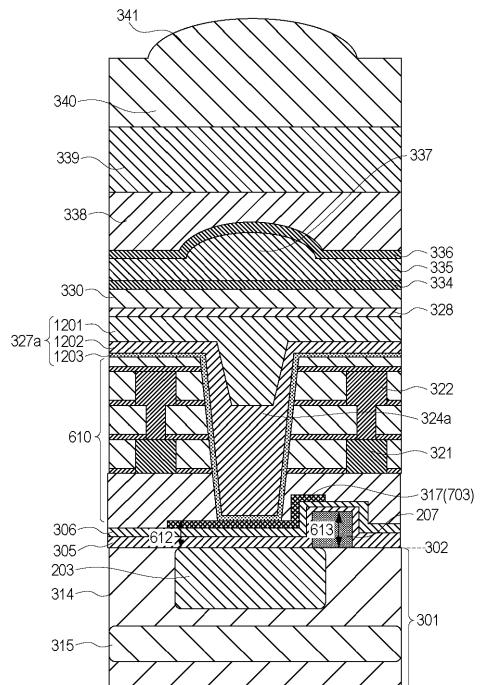

このような固体撮像装置の製造方法について、図3～図5を用いて説明する。図3～図5は、製造方法の工程を説明する図2のA B線における断面模式図である。具体的には、図3～図5は、図2のA B線における画素セルの第2、第3のPDの断面と、画素セルの任意のトランジスタ303と、周辺回路部の任意のトランジスタ304とを示している。上述の構成については同一の符号を付し、説明を省略する。また、一般の半導体技術によって形成可能な構成については、その詳細な説明を省略する。

## 【0026】

まず、図3(a)を用いて、素子が配置された半導体基板を準備する工程を説明する。まず、準備する半導体基板31は、シリコンからなり、主面302を有する。そして、半導体基板301には、2つのPDの電荷蓄積領域202、203と、画素セルのトランジスタ303と、周辺回路部のトランジスタ304とが設けられている。図3(a)において、画素部のトランジスタ303はN型のソース・ドレイン領域309とゲート電極308とを有する。電荷蓄積領域202、203の下部にはN型半導体領域314が設けられている。このN型半導体領域314は電荷蓄積領域よりも不純物濃度が低く、電荷蓄積領域と共に光電変換部の一部を構成する。N型半導体領域314の下部には、光電変換部の一部として機能するP型半導体領域315が配置されている。そして、トランジスタ303のソース・ドレイン領域309と第2のFD領域210の下部にはP型半導体領域316が配置されている。周辺回路部のトランジスタ304は、CMOS回路を構成するトランジスタが配置されるが、本実施形態においては、N型のトランジスタのみを示している。周辺回路部のトランジスタ304は、P型の半導体領域313に配されたN型のソース・ドレイン領域311と、ソース・ドレイン領域の間であって半導体基板の主面302上のゲート電極310とを有する。このような素子を有する半導体基板301を準備する。なお、これらの素子の製造方法については、公知の半導体の製造方法で製造可能であるため、詳細については省略する。また、図中においてゲート絶縁膜については省略している。

## 【0027】

そして、図3(a)においては、素子上に絶縁膜を形成する工程を示している。画素部1011には、酸化シリコンからなる絶縁膜(不図示)と、窒化シリコンからなる絶縁膜305と、酸化シリコンからなる絶縁膜306とが主面302側からこの順に積層して配置されている。これらの膜はプラズマ化学気相成長(Chemical Vapour Deposition、以下CVD)によって形成されうる。

## 【0028】

そして、トランジスタ304は、そのゲート電極10の側壁にサイドスペーサー312を有し、ソース・ドレイン領域311はLDD構造(Lightly Doped Drain構造、不図示)を有する。サイドスペーサー312は、酸化シリコンと、窒化シリ

10

20

30

40

50

コンと、酸化シリコンとの積層膜からなる。これらの膜はプラズマCVD法によって形成されうる。そして、サイドスペーサー312を構成する膜は、画素部1011に形成される絶縁膜(不図示)と、絶縁膜305と、絶縁膜306と同一の膜から形成されうる。

#### 【0029】

そして、図3(a)において、画素部1011と周辺回路部1016に渡って窒化シリコンからなる絶縁膜307を、例えは低圧プラズマCVD法(LP-CVD法)によって堆積する。ここで、絶縁膜307を形成する前に、画素部1011と周辺回路部1016に渡って酸化シリコンからなる膜(不図示)をプラズマCVD法によって堆積しておいてもよい。これは、周辺回路部のトランジスタ304のソース・ドレイン領域311において半導体基板の主面302が露出しないようにするためである。

10

#### 【0030】

図3(b)において、画素部1011と周辺回路部1016に形成されている絶縁膜307を、公知のリソグラフィ技術及びエッティング技術によって、所望の形状にパターニングし、絶縁膜317と絶縁膜318とを形成する。ここで、絶縁膜317は、電荷蓄積領域202、203の上、すなわち光電変換部の上から転送トランジスタのゲート電極の一部上に延在して設けられる。絶縁膜317及び絶縁膜318の上面はゲート電極の形状を踏襲した形状を有する。この図3(a)及び図3(b)の工程は、図7に示した絶縁膜701~704が形成される工程であり、図3(b)の絶縁膜317aは図7の絶縁膜702に対応し、図3(b)の絶縁膜317bは図7の絶縁膜703に対応する。画素部1011の他の領域においては、図3(a)の絶縁膜307はエッティングによって除去されている。周辺回路部1016において図3(a)の絶縁膜307はエッティングされることなく、絶縁膜318となる。

20

#### 【0031】

次に、図3(c)において、図3(b)の構成上に、複数の層間絶縁膜319と、コンタクト320と、第1の配線層321と、ビアを含む第2の配線層322とを形成する。コンタクトや配線層の配線は複数配置されている。複数の層間絶縁膜319は、酸化シリコンからなる絶縁膜と窒化シリコンからなる絶縁膜とが交互に積層されている。酸化シリコンからなる複数の絶縁膜は、プラズマCVD法によって、約120nm~1000nmの膜厚にそれぞれが形成される。窒化シリコンからなる複数の絶縁膜は、プラズマCVD法によって、約10nm~200nmの膜厚にそれぞれが形成される。よって、複数の層間絶縁膜319の大部分は酸化シリコンである。窒化シリコンからなる複数の絶縁膜は、配線層やビアを形成する際のエッティングトップ膜や配線層を構成する金属の拡散防止膜として機能する。複数の層間絶縁膜319は後に導波路のクラッドとなる部材である。

30

#### 【0032】

コンタクト320は主にタングステンからなり、バリアメタルを有する。コンタクト320を形成するには、酸化シリコンからなる絶縁膜(不図示)と絶縁膜305と絶縁膜306とをプラズマエッティングによって除去してコンタクトホールを形成する工程が必要である。しかし、ここで、絶縁膜317が絶縁膜307の状態で配置されていた場合には、絶縁膜307(窒化シリコン)、絶縁膜306(酸化シリコン)、絶縁膜305(窒化シリコン)、酸化シリコン(不図示)の順にエッティングを行わなくてならない。この場合には、エッティング条件の切り替えやエッティング停止条件の設定が困難になってしまう。絶縁膜317を用いた場合には、絶縁膜305をエッティングストップ膜として機能させる条件でエッティングを行い、条件の切り替えが1回で済むため、コンタクトの形成が容易である。

40

#### 【0033】

第1の配線層321、ビアと一体形成された第2の配線層322は、主に銅を主成分とする。第1の配線層321はシングルダマシン法によって形成された構造を有し、第2の配線層322はデュアルダマシン法によって形成された、ビアと配線層とが一体の導電体によって形成された構造を有する。コンタクト、ビア及び配線層はそれぞれバリアメタルを有している。これらの製造方法については、公知の製造方法によって形成可能であるた

50

め説明を省略する。なお、第1、第2の配線層はダマシン法ではなく、パターニングによって形成されていてもよい。

【0034】

ここで、図3(c)において、窒化シリコンからなる複数の絶縁膜のうち、第1及び第2の配線層の上面と接して配置される絶縁膜は、金属、すなわち銅の拡散防止膜として機能する。一方、第1、第2の配線層の下面側に配置される絶縁膜は、第1、第2の配線層をダマシン法で形成する際のエッティングストップ膜として機能する。拡散防止膜として機能する絶縁膜よりもエッティングストップ膜として機能する絶縁膜の膜厚は薄い。ダマシン法では、絶縁膜に配線用の溝あるいは配線及びビア用の溝を形成する工程があり、この溝を形成する際のエッティングにおいて、溝の形状制御のためエッティングストップ膜があることが好ましい。よって、第1、第2の配線層の下面側にエッティングストップ膜として機能する絶縁膜が配置されている。なお、配置されるエッティングストップ膜は溝を形成する際に除去されるため、エッティングストップ膜の下面は第1、第2の配線層の下面と一致あるいは第1、第2の配線層の下面よりも上部に配置されることになる。なお、図3(c)までの構成が形成されたウエハを入手し、以下に示す開口を形成する工程を行ってもよい。

【0035】

次に、図3(c)の複数の層間絶縁膜319に開口323を形成し図4(a)の構成を形成する。複数の層間絶縁膜319の上に、光電変換部に対応して領域に開口を有するフォトレジストパターン(不図示)が形成され、それをマスクとしてエッティングが行われる。エッティングは、異方性のエッティング、例えば、プラズマエッティングである。エッティング処理が行われ、絶縁膜317が露出するまで複数の層間絶縁膜が除去される。ここで、絶縁膜317は、エッティング時における光電変換部へのプラズマダメージを低減するための膜であり、また、エッティングストップ膜としても機能する。そして、半導体基板の主面302との間の酸化シリコンからなる絶縁膜(不図示)と、絶縁膜305と、絶縁膜306とは、半導体基板に入射すべき光に対する反射防止膜として機能する。ここで、この多層の反射防止膜の性能は絶縁膜306の膜厚が重要となる。絶縁膜306において、絶縁膜305と絶縁膜317(すなわち導波路の下面)との間で多重反射が生じ、反射を低減する機能を有するためである。絶縁膜317がエッティングストップ膜として機能することで、絶縁膜306の膜厚が所望の値に維持され、設計通りの反射防止膜の性能を得ることが可能となる。なお、複数の層間絶縁膜の一部を除去する際のエッティングによって絶縁膜317の膜厚が変化しても、高屈折率部材324と一体となっているため影響は小さい。

【0036】

次に、図4(a)の開口323に、複数の層間絶縁膜3191よりも屈折率の高い透明材料を埋め込み、導波路のコアを形成する。ここでは、複数の層間絶縁膜3191を構成する主な材料である酸化シリコンよりも屈折率の高い窒化シリコンを用いて埋め込みを行う。具体的には、高密度プラズマCVD法(High Density Plasma-CVD法)によって、窒化シリコンを全面に堆積し、開口323に窒化シリコンを埋め込む。そして、開口323の以外の複数の層間絶縁膜3191の上などの不要な部分に形成された窒化シリコンを、化学機械研磨法(Chemical Mechanical Polishing、以下CMP法)あるいはプラズマエッティングによって除去する。この除去工程によって、窒化シリコンの表面は平坦化され、開口323に高屈折率部材324を形成する。つまり、導波路は、複数の層間絶縁膜3191と高屈折率部材324によって構成される。複数の層間絶縁膜3191は導波路のクラッドであり、高屈折率部材が導波路のコアである。

【0037】

なお、本実施形態においては、CMP法を行い除去及び平坦化を行う。この時、複数の層間絶縁膜3191の上部に配置された窒化シリコンを全て除去せずに、絶縁膜325を形成する。絶縁膜325は、高屈折率部材324の上から複数の層間絶縁膜3191の上面に渡って延在する厚さ約100nm~500nmの層である。これは、配線層へのダメージを抑制するためである。そして、絶縁膜325の上面に酸窒化シリコンからなる絶縁

膜326を形成する。絶縁膜326はプラズマCVD法によって、約50nm～150nmの膜厚で形成される。

【0038】

図4(b)の構造のあとに、図4(c)に示すように、絶縁膜325及び絶縁膜326の任意の領域の少なくとも一部を除去する。本実施形態では、周辺回路部1016における、後にピアを形成する領域と、その他の領域の一部をエッティングによって除去する。これは、屈折率の高い膜は応力が高いため、半導体基板の全面に形成してしまうと半導体基板のそりや屈折率の高い膜の剥がれが生じてしまうためである。また、ピアを形成する領域を除去し開口329を形成することで、後の工程においてエッティングを容易にすることが可能である。また、その他の領域の一部以外を残してパターン401を形成することで、その後の平坦性を確保することが可能となる。絶縁膜325及び絶縁膜326は、画素部1011の絶縁膜327と、絶縁膜328となる。その後、開口329を埋め、絶縁膜327及び絶縁膜328を覆うように、絶縁膜330となる絶縁膜を形成する。絶縁膜330となる絶縁膜は、例えば酸化シリコンからなり、プラズマCVD法によって形成される。そして、絶縁膜330となる絶縁膜と第2の配線層322の上に配置された複数の層間絶縁膜319の一部とを貫通するピア331を形成する。ピア331が形成され、絶縁膜330と複数の層間絶縁膜332とが形成される。ピア331は例えばタンゲステンからなり、チタンや窒化チタンのバリアメタルを有する。ピア331の上部に第3の配線層333が形成され、図4(c)の構成が得られる。第3の配線層333は、例えばアルミニウムを主成分とする導電体からなり、パターニングによって形成される。ここで、第3の配線層333は、遮光膜としても機能し得る。

10

20

30

40

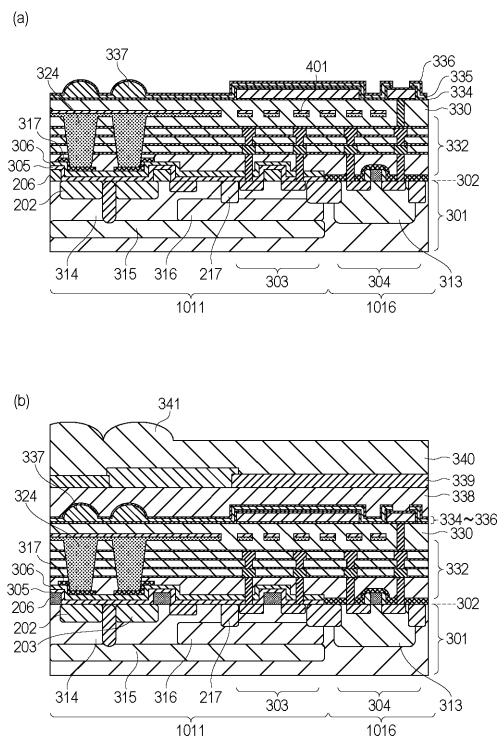

【0039】

次に、図4(c)の構成において、絶縁膜334となる絶縁膜と絶縁膜335となる絶縁膜をこの順に形成する。ここで、絶縁膜334となる絶縁膜はプラズマCVD法によって形成される酸窒化シリコンであり、絶縁膜335となる絶縁膜はプラズマCVD法によって形成される窒化シリコンである。そして、絶縁膜335となる絶縁膜上にレンズ形状のフォトトレジストを形成し、それをマスクとしてエッティングを行うことで、絶縁膜335となる絶縁膜にレンズ形状を転写する。その後、レンズ形状の絶縁膜の上に絶縁膜336となる絶縁膜を形成する。絶縁膜336となる絶縁膜はプラズマCVD法によって形成される酸窒化シリコンである。そして、外部電極パッドに対応する領域において、3層の絶縁膜を除去することで、絶縁膜334～336の構成が得られ、図5(a)の構成が得られる。ここで、絶縁膜335は層内レンズ337を有するレンズ層であり、絶縁膜334と絶縁膜336とは絶縁膜335の反射防止として機能しうる。

【0040】

図5(a)の工程の後に、樹脂からなる平坦化層338と、複数の色に対応したカラーフィルタを含むカラーフィルタ層339と、マイクロレンズ341を含むマイクロレンズ層340とをこの順に形成し、図5(b)の構成が得られる。以上のように図3～図5のフローによって、固体撮像装置を形成することが可能である。なお、図3～図5において、半導体基板301は正面側の一部を示したものであり、3板用あるいは白黒用の固体撮像装置の場合には、カラーフィルタは形成しなくてもよい。

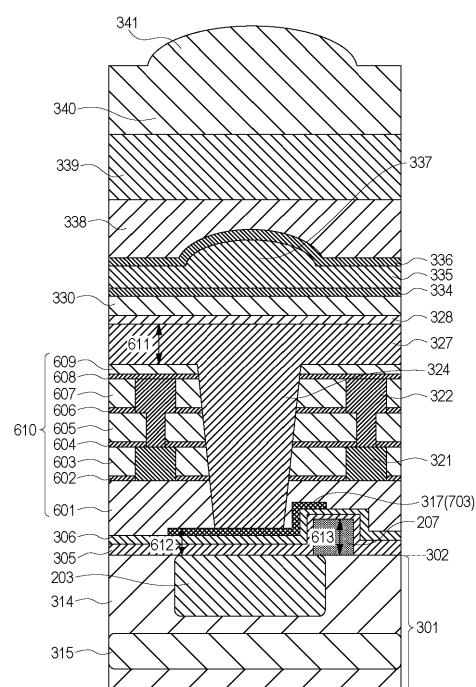

【0041】

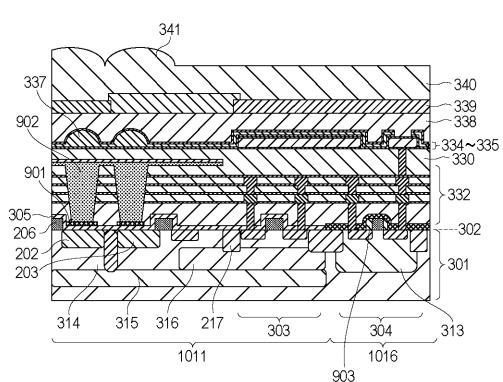

次に、絶縁膜317について図6を用いて詳細に説明する。図6は図5(b)に示す固体撮像装置の拡大図である。図5(b)と共に構成については同一の符号を付し、説明を省略する。なお、図5(b)の複数の層間絶縁膜332は複数の層間絶縁膜610に対応し、複数の層間絶縁膜610は、絶縁膜601～609を有する。絶縁膜601、603、605、607、609は酸化シリコンからなる絶縁膜であり、絶縁膜602、604、606、608は窒化シリコンからなる絶縁膜である。絶縁膜604と絶縁膜608は配線層の金属の拡散防止膜として機能しうる。絶縁膜602と絶縁膜606は配線層を形成する際のエッティングストップ膜として機能しうる。絶縁膜604と絶縁膜608は、絶縁膜602及び絶縁膜606よりも厚い。

50

## 【0042】

図6において、図7の絶縁膜703に対応する絶縁膜317(703)は、上述のように窒化シリコンからなる。ここで、高屈折率部材324は窒化シリコンからなるため、絶縁膜317と高屈折率部材324とは同一の材料からなる。このような構成によって、絶縁膜317と高屈折率部材324との界面における反射が生じにくい。この絶縁膜317と半導体基板の正面302との間には、酸化シリコンからなる絶縁膜(不図示)と、絶縁膜305と、絶縁膜306とが半導体基板の正面302側からこの順に積層されている。ここで、絶縁膜(不図示)の膜厚は約5~20nm、絶縁膜305の膜厚は約30~100nm、絶縁膜306の膜厚は約50~150nm、絶縁膜317の膜厚は30~100nmである。絶縁膜317は可能であれば、 $\lambda/2n$ ( $\lambda$ :入射する光の波長、n:屈折率)であることが望まれる。

10

## 【0043】

なお、ここで絶縁膜703が半導体基板の正面302の全面(コンタクトのプラグが配置される部分を除く)に渡って形成された場合においても、エッチングストップ膜として機能し、反射防止膜へのダメージを抑制することが可能である。しかし、絶縁膜を半導体基板の正面302の全体に形成する場合に比べて、本実施例の形状にすることで感度が向上する。具体的には、例えば、感度の高い450~630nmの波長領域において、絶縁膜703が半導体基板の正面302の全面に渡って形成された場合に比べて、本実施例の絶縁膜703の形状は1~5%程度、感度が向上する。これは、全面に渡って形成された絶縁膜の場合には、導波路によって集められた光が広がってしまうため、と考えられる。クラッドである絶縁膜に比べて高い屈折率を有する絶縁膜703が全面に配置されていると、絶縁膜703近傍のクラッドの屈折率が実行的に高まるため、光が広がってしまう。また、ある光電変換部の上から隣接する光電変換部へ連続した1つの絶縁膜が配置される場合には、隣接する光電変換部に光が混入してしまう可能性がある。よって、絶縁膜703は可能な限り、各光電変換部に対応して分離されていることが望まれる。

20

## 【0044】

また、図6において、絶縁膜327の膜厚611は、0より厚く、 $\lambda/n$ 以下( $\lambda$ :入射光の波長、n:絶縁膜327の屈折率)である。絶縁膜327は導波路のクラッドである複数の層間絶縁膜610の上に配され、導波路の高屈折率部材324の上から隣接する導波路の高屈折率部材324へ延在している。この時、導波路に斜めに入射した光が絶縁膜327を隣接する導波路に入射してしまう可能性がある。このような光の混入を低減するために、膜厚611は、0より厚く、 $\lambda/n$ 以下であることが望ましい。なお、特に吸収されにくい波長の長い光、例えば赤に対応する光の伝搬を低減することが望ましい。例えば、赤のカラーフィルタの分光透過率のピーク波長を元に設定することが可能である。なお、下限は平坦化処理の際のプロセスマージンが取れる範囲で設定可能である。また、下限は絶縁膜327を保護膜として使用可能な範囲で設定してもよい。

30

## 【0045】

更に、図6において、光電変換部の上部の絶縁膜305、306、317の膜厚は、ゲート電極613の厚みよりも薄いことが好ましい。すなわち、正面302から光電変換部の上の絶縁膜317の上面までの距離612よりも、正面302からゲート電極の上面613までの距離613の方が大きくなっている。この構成によって、導波路を光電変換部の近傍に設けることが可能となり、導波路の下面から光が出射する際に光が広がることを抑制することが可能である。つまり、感度を向上させることが可能となる。

40

## 【0046】

図6では、絶縁膜305と、絶縁膜305と接して配される絶縁膜306と、絶縁膜306と接して配される317とを光電変換部の上からこの順に形成している。この時、絶縁膜を形成する間にその上面を平坦化するが入らないため、容易に膜厚を制御することが可能となる。

## 【0047】

以上のように、本実施例の絶縁膜701~704を設けることで、導波路を有しつつ、

50

反射を低減した構成を提供することが可能となる。よまた、固体撮像装置の感度を向上させることが可能となる。

#### 【0048】

次に、図8を用いて、図7の絶縁膜701～704の変形例について説明する。図8(a)及び図8(b)は、それぞれが図7に対応した平面レイアウトを示す図である。図8(a)及び図8(b)において、図7と共通の構成については同一の符号を付し、説明を省略する。

#### 【0049】

図8(a)では、図7の絶縁膜701～704が一体の絶縁膜801となっている。このように、エッチングストップ膜として機能する絶縁膜は、各光電変換部において別個の絶縁膜でなくてもよい。このような構成によって、反射防止膜の機能の低下を抑制することが可能である。また、各PDへのエッチングダメージを低減しつつ、コンタクト形成時の工程を容易にすることが可能である。なお、上述したように、図7のように各光電変換部に別個の絶縁膜が配置されていた方が、隣接画素への光の伝搬を低減することが可能であり、また感度の向上が可能となる。

10

#### 【0050】

また、図8(b)では、図7の絶縁膜701～704が一体の絶縁膜802となっており、またその面積が異なる。ここでは、絶縁膜802の外縁が各PDの電荷蓄積領域201～204に重なる領域を有する。また、絶縁膜802が転送トランジスタのゲート電極205～208及び接続配線213の上部に延在していない。このような構成においても、反射防止膜の機能の低下を抑制することが可能である。また、コンタクト形成時の工程を容易にすることが可能である。また、図7のように絶縁膜802が各PDに対応して分離していてもよい。上述したように、図7のように各光電変換部に別個の絶縁膜が配置されていた方が、感度が向上する。

20

#### 【0051】

また、絶縁膜701～704の面積は、開口323の底面の面積より大きく、光電変換部の受光面の面積よりも小さくてよい。このような構成によって、開口323を形成する際のエッチングダメージを低減しつつ、光の広がりを抑制し感度を向上させることが可能となる。

30

#### 【実施例2】

#### 【0052】

本実施例について、図9を用いて説明する。図9は図5(b)に対応した固体撮像装置の断面模式図であり、図5(b)と共に構成には同一の符号を付して説明を省略する。本実施例は、実施例1の絶縁膜306が配置されていない点、及び実施例1の絶縁膜317の形状が異なる絶縁膜901である点で相違する。

#### 【0053】

図9において、電荷蓄積領域202及び203の上部には、酸化シリコンからなる絶縁膜(不図示)と、絶縁膜305と、絶縁膜901とが主面302側からこの順に配置されている。絶縁膜901は図5(b)の絶縁膜317に対応する。絶縁膜901はゲート電極の上部に延在していない。また、絶縁膜901は同じ窒化シリコンからなる絶縁膜305の上に接して形成されている。このような構成によって、実施例1に比べて、高屈折率部材902を半導体基板の主面302のより近くまで配置することが可能となる。

40

#### 【0054】

なお、周辺回路部1016において、トランジスタのサイドウォール903は酸化シリコン(不図示)と窒化シリコンとからなる。このサイドウォールは、画素部1011における酸化シリコン(不図示)及び絶縁膜305の積層膜と同一の膜から形成される。

#### 【0055】

このような構成においても、絶縁膜901を設けることで反射防止膜の光学特性の低下を抑制することが可能である。また、絶縁膜901が各光電変換部に配置されることで、感度が向上する。更には、絶縁膜901が光電変換部の上にのみ配置されているため、コ

50

ンタクトも容易に形成可能である。

【実施例3】

【0056】

本実施例では、図10を用いて撮像システムの構成を説明する。図10は固体撮像装置及び撮像システムのブロック図である。撮像システム1000は、固体撮像装置1001と、固体撮像装置1001から出力された電気信号が入力され、当該電気信号を処理する信号処理装置1002とを備える。具体的には、電気信号が固体撮像装置1001のOUT1、2から出力され、信号処理装置1002のINに入力される。信号処理装置1002のOUT3からは、電気信号を処理した結果に応じて、画像信号や駆動信号、制御信号が出力される。電気信号としては、電流信号であってもよいし電圧信号でもよく、また、アナログ信号であってもよいしデジタル信号であってもよい。固体撮像装置1001はイメージセンサー、焦点検出用のセンサー、測光用のセンサーであってもよく、用途は任意である。このような撮像システムを有することで、好適な画像信号、あるいは制御に利用可能な制御信号が得られる。

10

【実施例4】

【0057】

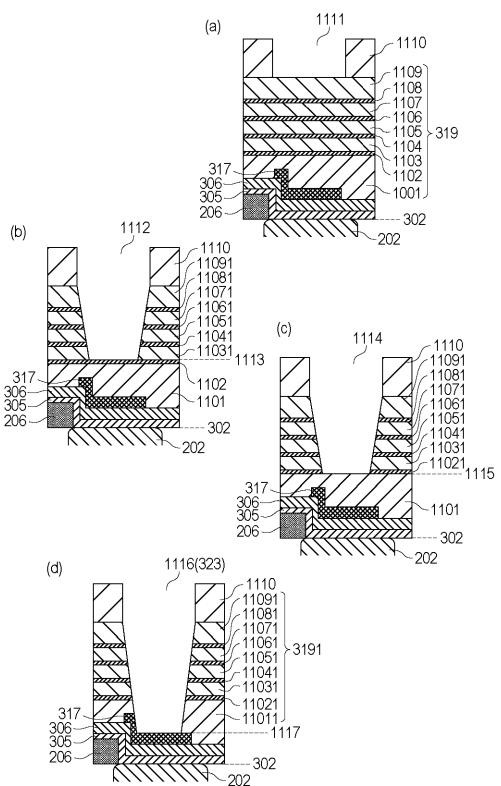

本実施例は、実施例1とは複数の層間絶縁膜の開口を形成する工程が異なる。図11を用いて開口を形成する工程について説明する。図11は、図3(c)から図4(a)の間の工程を詳細に示した断面模式図であり、第2のPDに相当する部分を拡大したものである。他の図面と同一の符号を付した構成については、説明を省略する。

20

【0058】

図11(a)に示すように、配線及び複数の層間絶縁膜を形成する工程の後に、マスクを形成する。ここで、複数の層間絶縁膜319は、少なくとも2種類の材料からなる絶縁膜が交互に積層した構成を有している。具体的には、少なくとも第1の絶縁膜となる部材と、それと異なる材料からなる第2の絶縁膜となる部材と、第3の絶縁膜となる部材と、第3の絶縁膜と異なる材料からなる第4の絶縁膜となる部材とをこの順に積層した構成を有している。図11(a)においては、酸化シリコンからなる絶縁膜1101、1103、1105、1107、1109と、窒化シリコンからなる絶縁膜1102、1104、1106、1108とを交互に積層した構成を有している。なお、絶縁膜1101～1109は図6の絶縁膜601～609と対応している。これらは、第1の絶縁膜となる部材として絶縁膜1101、第2の絶縁膜となる部材として絶縁膜1102、第3の絶縁膜となる部材として絶縁膜1103、第4の絶縁膜となる部材として絶縁膜1104とする。

30

【0059】

図11(a)の複数の層間絶縁膜319を形成した後に、その最上層である絶縁膜1109の上部に、光電変換部に対応して開口1111を有するマスク1110を形成する。マスク1110はフォトトレジストからなり、フォトリソグラフィー技術によって形成可能である。

【0060】

次に、エッチングを行い開口1111に対応する複数の層間絶縁膜を除去する。まず、絶縁膜1109からエッチングを行う。エッチングは例えば異方性エッチングである。この除去工程において、第3の絶縁膜と第4の絶縁膜に対して、第3の絶縁膜と第4の絶縁膜のエッチングの速度がほぼ等しい条件、すなわちそれらが共にエッチングされる条件でエッチング処理を行う。そして、少なくとも第3の絶縁膜と第4の絶縁膜の開口1111に対応する部分を除去する(第1の除去工程)。第1の除去工程は、マスクの開口部分における第3の絶縁膜と第4の絶縁膜を除去し、第2の絶縁膜が露出あるいは一部が除去されるまで行う。つまり、絶縁膜1103～1109を連続してエッチングする。ここで、第3の絶縁膜となる部材である絶縁膜1103の一部が除去された時点でエッチングを停止あるいは切り替える。このタイミングは第3の絶縁膜となる部材が除去されなければよく、第2の絶縁膜となる部材がエッチングされていてもよい。このエッチングを停止するタイミングは、プラズマの発光強度をモニタし、第3の絶縁膜の除去に起因する発光強度

40

50

が低下を検知することや時間で設定することが可能である。酸化シリコンの絶縁膜と窒化シリコンの絶縁膜とを同時にエッティング可能な条件とは、例えば、 $\text{CHF}_3$ 等の水素含有フッ化炭素系と $\text{C}_4\text{F}_8$ 等のフッ化炭素系の混合ガスと、酸素と、アルゴン等の不活性ガスとを用いたプラズマエッティングである。絶縁膜1103～1109は開口を有する絶縁膜11031～11091となる(図11(b))。開口1112は各絶縁膜にそれぞれ設けられた開口が連通したものである。開口1112の底面は面1113の高さにある。

#### 【0061】

各絶縁膜に対してエッティング条件を変えた場合には、エッティング条件が異なることに起因して、開口形成のテーオー角度が変化し、その結果、開口の側面において、各絶縁膜に対応した凹凸が生じる可能性がある。よって、本実施例の方法によれば、条件を一定にして連続してエッティングを行うことが可能であるため、開口の側面がなめらかに形成される。また、このような第1の除去工程を行うことで、各絶縁膜に対してエッティング条件を変えてエッティングを行う場合に比べて、条件を一定にしてエッティングを行うことが可能であるため、エッティングにかかる時間を削減することが可能である。

10

#### 【0062】

そして、図11(c)に示すように、露出した第2の絶縁膜となる部材をその下層の第1の絶縁膜となる部材よりも優先的にエッティングを行う条件で、すなわち選択比が高い条件で、第2の絶縁膜を除去する第2の除去工程を行う。言い換えれば、第2の絶縁膜となる部材のエッティングされる速度が第1の絶縁膜となる部材のエッティングされる速度よりも速い条件である。この時のエッティング条件は、例えば、 $\text{CH}_2\text{F}_2$ 等の水素含有フッ化炭素系のガスと、酸素と、アルゴン等の不活性ガスとを用いたプラズマエッティングを行うことで満たされる。図11(c)に示すように、絶縁膜1102のマスク1110に対応した部分が除去され、開口を有する絶縁膜11021となる。ここで、絶縁膜1101は絶縁膜1102を除去する際のエッティングトップ膜として機能しうる。ここで、開口1114の底面は、絶縁膜1101の上面である面1115の高さにある。

20

#### 【0063】

このような第2の除去工程を行うことで、第1の絶縁膜となる部材によってエッティングの進行が低減するため、上述の第1の除去工程によって生じうるウエハ面内におけるグローバルなエッティングばらつきが吸収される。

30

#### 【0064】

最後に、図11(d)に示すように、図11(c)で露出した第1の絶縁膜となる部材を絶縁膜317よりも優先的に除去する条件でエッティングを行う第3の除去工程を行う。つまり、絶縁膜317がエッティングされる速度よりも第1の絶縁膜となる部材がエッティングされる速度が速い条件で、つまり絶縁膜317に対する第1の絶縁膜のエッティング選択比が高い条件で、エッティングが行われる。例えば、 $\text{C}_4\text{F}_6$ 等のフッ化炭素系のガスと、酸素と、アルゴン等の不活性ガスとを用いた異方性のプラズマエッティングである。図11(d)に示すように、絶縁膜1101のマスク1110に対応した部分が除去され、開口を有する絶縁膜11011となる。なお、他の実施例と同様に、絶縁膜317は、絶縁膜1101を除去する際のエッティングトップ膜として機能しうる。続いて、マスク1110が除去される。そして、開口1116、すなわち図4(a)の開口323を有する複数の層間絶縁膜3191が形成される。引き続き、図4(b)に示すような開口の埋め込み工程が行われる。開口1116の底面は面1117の高さに配置される。

40

#### 【0065】

本実施例のような開口の形成方法を有することで、形状が制御された開口を形成することが可能であり、ウエハ面内におけるエッティングばらつきを低減することが可能となる。また、エッティングのダメージも低減可能である。

#### 【実施例5】

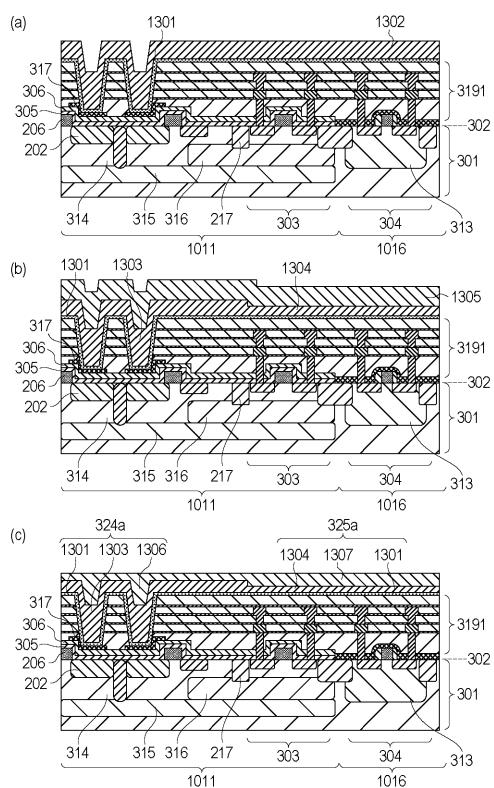

#### 【0066】

本実施例は、実施例1とは高屈折率部材324と絶縁膜327を形成する工程が異なる。図12及び図13を用いて説明する。図12は、図6に対応する断面模式図であり、図

50

6 の高屈折率部材 3 2 4 と絶縁膜 3 2 7 が、高屈折率部材 3 2 4 a と絶縁膜 3 2 7 a となっている。図 1 3 は図 1 2 の構成を形成するときの製造方法を説明する断面模式図であり、図 4 ( b ) の工程の変形例となっている。図 6 、図 4 ( b ) 及び他の図面と同一の符号を付した構成については、説明を省略する。

#### 【 0 0 6 7 】

図 1 2 では、高屈折率部材 3 2 4 a 及び絶縁膜 3 2 7 a は、それぞれ第 1 部材 1 2 0 3 、第 2 部材 1 2 0 2 、第 3 部材 1 2 0 1 の 3 つからなる。いずれの部材も窒化シリコンからなり、形成方法、あるいはタイミングが異なるものである。図 1 3 を用いて詳述する。

#### 【 0 0 6 8 】

図 1 3 ( a ) では、図 4 ( a ) の構成に、第 1 部材となる絶縁膜 1 3 0 1 を形成し、続いて第 2 部材となる絶縁膜 1 3 0 2 を形成している。第 2 の部材を形成する第 2 の工程は、第 1 の部材を形成する第 1 の工程と比較して、成膜効果に対するスパッタ効果の割合が高い条件で行う。絶縁膜 1 3 0 1 及び絶縁膜 1 3 0 2 は画素部 1 0 1 1 から周辺回路部 1 0 1 6 に渡って形成されている。ここで、絶縁膜 1 3 0 1 は、成膜効果とスパッタ効果を有する高密度プラズマ C V D 法において、上部電極のみに高周波パワーを供給し、成膜効果を高めた条件で形成される。絶縁膜 1 3 0 2 は、高密度プラズマ C V D 法において、上部電極及び下部電極の両方に高周波パワーを供給し、スパッタ効果を高めた条件で形成される。このような条件によって、絶縁膜 1 3 0 1 は開口の側壁との密着性が高く、絶縁膜 1 3 0 2 は開口の埋め込み性が高く、すなわちボイドの発生を低減可能である。また、絶縁膜 1 3 0 2 は絶縁膜 1 3 0 1 に比べて応力が小さいため、ウエハの変形の発生を低減することが可能である。なお、下部電極の高周波パワーは 0 W ~ 5 0 0 0 W であり、上部電極の高周波パワーは 1 0 0 0 ~ 7 0 0 0 W である。ここでは、絶縁膜 1 3 0 1 形成時の下部電極の高周波パワーは 0 W としているが、絶縁膜 1 3 0 2 形成時に比べて絶縁膜 1 3 0 1 形成時の上部電極に対する下部電極の高周波パワーの割合が低ければよい。また、シリコン含有ガスと、窒素ガスと、窒素含有ガスと、不活性ガスを含む混合ガスを用いる。シリコン含有ガスとはシラン、T E O S 、トリメチルシラン、テトラメチルシラン等であり、窒素含有ガスとはアンモニア等であり、不活性ガスとはアルゴンやヘリウム等である。ここでは、絶縁膜 1 3 0 1 及び絶縁膜 1 3 0 2 のいずれにおいてもシラン、窒素、アンモニア、アルゴンの混合ガスを使用している。絶縁膜 1 3 0 1 形成時の混合ガス中の不活性ガスの比率を絶縁膜 1 3 0 2 形成時に比べて小さくしてもよい。高密度プラズマ C V D 法において、成膜効果とスパッタ効果は高周波パワー、混合ガスの比率などで適宜調整可能である。なお、出来上がった高屈折部材として第 1 の部材、第 2 の部材とは一体の構成であってもよい。また、第 1 の工程と第 2 の工程との間に、上部電極に対する下部電極の高周波パワーの割合が第 1 の工程と第 2 の工程の間の値を有する第 3 の工程を有していてよい。つまり、第 1 の工程と第 2 の工程とを切り替える際には、間に第 3 の工程を有するなど、連続的な条件で切り替えてよい。

#### 【 0 0 6 9 】

図 1 3 ( b ) では、絶縁膜 1 3 0 2 の周辺回路部 1 0 1 6 に対応する領域を厚さ方向に一部除去し、絶縁膜 1 3 0 3 及び絶縁膜 1 3 0 4 とする。除去は、例えば、画素部 1 0 1 1 をマスクで覆い、異方性のプラズマエッチングを行うことでなされる。そして、第 3 部材となる絶縁膜 1 3 0 5 を形成する。絶縁膜 1 3 0 5 は画素部 1 0 1 1 から周辺回路部 1 0 1 6 に渡って形成されている。この絶縁膜 1 3 0 5 は絶縁膜 1 3 0 2 と同様な条件で形成される。

#### 【 0 0 7 0 】

そして、図 1 3 ( c ) に示すように、絶縁膜 1 3 0 5 の上面を例えば C M P 法によって平坦化し、余分な絶縁膜を除去し、絶縁膜 1 3 0 6 及び絶縁膜 1 3 0 7 とする。そして、第 1 ~ 第 3 の部材からなる高屈折率部材 3 2 4 a と絶縁膜 3 2 5 a を形成する。なお、図 1 2 の第 1 部材 1 2 0 3 は絶縁膜 1 3 0 1 、図 1 2 の第 2 部材 1 2 0 2 は絶縁膜 1 3 0 3 及び絶縁膜 1 3 0 4 、図 1 2 の第 3 の部材 1 3 0 1 は絶縁膜 1 3 0 6 及び絶縁膜 1 3 0 7 である。

10

20

30

40

50

## 【0071】

このような形成方法によって、開口の側壁との密着性が高く、高屈折率部材におけるボイドの発生を低減することが可能である。

## 【0072】

なお、本実施例においては、高密度プラズマCVD法によって第1～第3の部材を形成する際に、部材となる膜の成膜速度が、以下の関係を満たすような条件で行われる。それは、図4(a)における開口323の側面から正面302に平行な方向への成膜速度に対して、図4(a)における開口323の底面から正面302に垂直な上方向への成膜速度が1.5倍以上10倍以下となるような条件である。このような条件によって、ボイドが形成されることなく、導波路を形成することが可能となる。

10

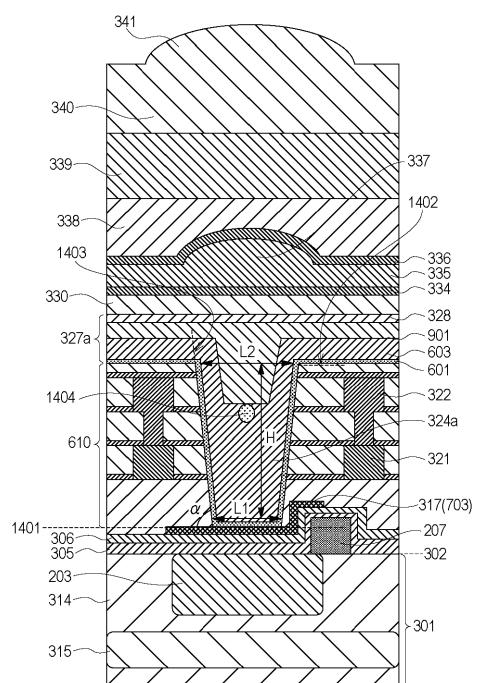

## 【実施例6】

## 【0073】

本実施例では、図14を用いて導波路の高屈折率部材の形状について説明する。図14は、図12に対応する断面模式図であり、図12及び他の図面と同一の符号を付した構成については、説明を省略する。

## 【0074】

図14において、導波路の高屈折率部材324aの形状、すなわち図4(a)の開口323は、底面と上面と側面とを有する。底面を含む面を面1401とし、上面を含む面を面1402とし、側面を含む面を面1403とする。面1401と面1402は、光電変換部の受光面を含む、半導体基板の正面302と平行である。底面のもっとも広い幅L1と、上面のもっとも広い幅L2と、面1401と面1402との間、すなわち上面と底面とを結ぶ線分を高さHとし、面1403と面1401となす角を角度 $\theta$ とする。高さHは正面302に垂直である。ここで、高屈折率部材324aの形状は、 $L_1 < L_2$ であり、 $H / L_2 = 2.72 \pm 0.8^\circ < \theta < 90^\circ$ を満たす。このような関係によって、高屈折率部材324aをボイドなく形成することが可能となる。

20

## 【0075】

また、ここで、マイクロレンズ341と層内レンズ334とで構成されるレンズ系における焦点1404は、高さHと高さ(H/2)との間に配置される。このような配置によって、高屈折率部材に確実に光が集光される、また、波動光学的に高屈折率部材に集光されるため、感度が向上する。

30

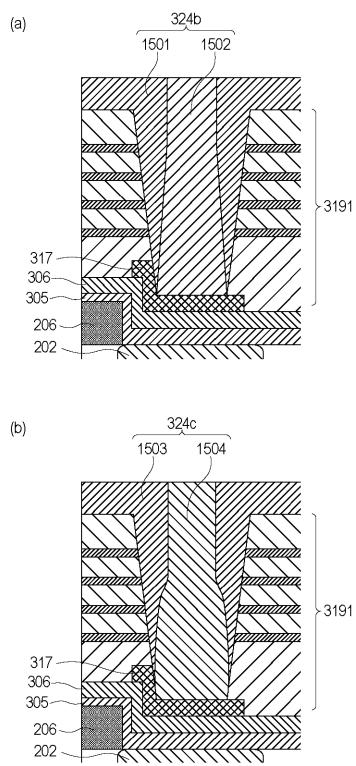

## 【実施例7】

## 【0076】

本実施例では、図15を用いて導波路の高屈折率部材の形状について説明する。図15は、図6に対応する断面模式図であり、図6及び他の図面と同一の符号を付した構成については、説明を省略する。

## 【0077】

図15(a)において、高屈折率部材324bは、第1の領域1501と第2の領域1502とを有する。図15(b)において、高屈折率部材324cは、第1の領域1503と第2の領域1504とを有する。それぞれ、第1の領域1501、1503は開口323の側壁を囲む。第2の領域1502、1504は、第1の領域1501、1503にそれぞれ囲まれている。第2の領域1502、1504は高屈折率部材の上面に比べて下面における面積(正面302に平行な面における)が大きい。すなわち、第1の領域は光導波路の上部において、膜厚が厚くなっている。また、第1の領域1501、1503の屈折率は第2の領域1502、1504の屈折率に比べて高い。光は屈折率の高い領域に集まる性質を有しているため、このような構成によって、導波路に入射した光が第1の領域に集まり、また、斜め方向から入射した光が集まり、感度が向上する。また、第1の領域によって第2の領域が囲まれていることで、開口の側壁を伝搬してきた光が効率よく高屈折率部材の中心に伝搬され、感度が向上する。

40

## 【実施例8】

## 【0078】

50

本実施例は、実施例1と同様に導波路を有する場合の固体撮像装置に関する。しかし、本実施例では、実施例1と周辺回路部が異なる使用電圧のトランジスタを有する構成が少なくとも異なる。具体的には、周辺回路部が、例えば使用電圧が3.3Vや2.5Vの高電圧用のトランジスタと、例えば使用電圧が1.8Vや1.0Vの低電圧用のトランジスタとを有する。以下、本実施例について、図16～図19を用い製造方法を説明し、図20を用い構造を説明する。ここで、図16～図19において、他の実施例と同様な構成については、同一の符号を付し、説明を省略する。また、図16～図19において、互いの図面の符号は相互に参照できるものとする。

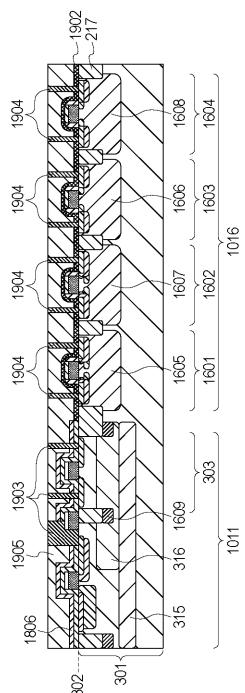

#### 【0079】

まず、図16(a)は、画素部1011と周辺回路部1016とを示している。周辺回路部1016は、低電圧用N型トランジスタ形成領域1601と、低電圧用P型トランジスタ形成領域1602と、高電圧用N型トランジスタ形成領域1603と、高電圧用P型トランジスタ形成領域1604とを含む。

10

#### 【0080】

画素部1011と周辺回路部1016に素子分離、ここではSTI(Shallow trench isolation)構造を有する素子分離を形成する。素子分離形成時には、画素部においてのみ、素子分離の界面における欠陥からのノイズを低減するための半導体領域1609を形成する。ここでは、信号電荷が少数キャリアとなる導電型の半導体領域を形成すればよく、本実施例においては、P型の半導体領域を形成している。その後、周辺回路部に、P型ウエル1605と、P型ウエル1606と、N型ウエル1607と、N型ウエル1608とを形成する。後に、P型ウエル1605には低電圧用のN型トランジスタが形成され、P型ウエル1606には高電圧用のN型トランジスタが形成される。N型ウエル1607には低電圧用のP型トランジスタが形成され、N型ウエル1608には高電圧用のP型トランジスタが形成される。その後、画素部1011のP型半導体領域315やP型半導体領域316が形成される。

20

#### 【0081】

次に、後に光電変換部の電荷蓄積領域となるN型半導体領域1611を形成する。そして、半導体基板301の主面302にゲート絶縁膜1610を形成する(図16(b))。ゲート絶縁膜1610は、熱酸化によって形成された酸化シリコンからなる膜や、その膜をプラズマ窒化した酸窒化シリコンからなる膜や、窒化シリコンを堆積した膜などを使いことが出来る。本実施例では、ゲート絶縁膜1610は酸窒化シリコンからなるものとする。酸窒化シリコンからなるゲート絶縁膜1610とすることで、不純物がゲート電極などから半導体基板に混入することを低減することが出来る。ここで、ゲート絶縁膜1610は複数の膜厚を有することが出来る。ここでは、ゲート絶縁膜1610は、画素部1011と、高電圧用N型トランジスタ形成領域1603と、高電圧用P型トランジスタ形成領域1604において、第1膜厚を有する。また、低電圧用N型トランジスタ形成領域1601と、低電圧用P型トランジスタ形成領域1602においては、ゲート絶縁膜1610は第2膜厚を有する。ここで、第1膜厚は第2膜厚よりも厚い。ゲート絶縁膜1610が第1膜厚を有する領域に配される回路は、ゲート絶縁膜1610が第2膜厚を有する領域に配される回路よりも、信号が高電圧、いわゆる大きな振幅で駆動するためである。そして、PDの上に延在するゲート絶縁膜は第1膜厚を有する。PDへのダメージを低減するためである。

30

#### 【0082】

そして、ゲート絶縁膜1610の上に、ゲート電極となる材料膜を形成する。ここで、材料膜はポリシリコン膜とするが他の材料でもよい。本実施例では、イオン注入によって材料膜に不純物イオンを注入し、P型ポリシリコン膜1612とN型ポリシリコン膜1613とを形成する。P型トランジスタを形成する領域に位置するポリシリコンをP型ポリシリコン膜1612とし、N型トランジスタを形成する領域に位置するポリシリコンをN型ポリシリコン膜1613とする。周辺回路部1016のトランジスタの特性向上のため、表面チャネル型にする場合には、このようなN型及びP型のポリシリコン膜を使い分け

40

50

ることが好ましい。そして、両ポリシリコン膜を覆う絶縁膜 1614 を形成する（図 16（c））。絶縁膜 1614 は、酸化シリコンからなる膜である。その他、絶縁膜 1614 の材料として、窒化シリコン等の材料を用いることが出来る。

#### 【0083】

そして、絶縁膜 1614 の上にフォトレジストパターン（不図示）を形成し、絶縁膜 1614 をエッチングすることで、絶縁部材を形成する。絶縁部材は、画素部 1011 に設けられた第 1 絶縁部材 1708 と、周辺回路部 1016 に設けられた第 2 絶縁部材 1709 とを有する。フォトレジストパターン（不図示）を除去した後、第 1 絶縁部材 1708 と第 2 絶縁部材 1709 とをマスクとして、P 型ポリシリコン膜 1612 と N 型ポリシリコン膜 1613 とをエッチングする。そして、ゲート電極 1701～ゲート電極 1707 を形成する（図 17（a））。図 17（a）において、画素部 1011 には、転送トランジスタのゲート電極 1701 と、増幅トランジスタのゲート電極 1702 と、画素セルの任意のトランジスタのゲート電極 1703 が形成される。ここで、正確には、増幅トランジスタのゲート電極 1702 はゲート電極が配線として延在している部分を示している。図 17（a）において、周辺回路部 1016 には、低電圧用 N 型トランジスタのゲート電極 1704 と、低電圧用 P 型トランジスタ 1705 と、高電圧用 N 型トランジスタのゲート電極 1706 と、高電圧用 P 型トランジスタのゲート電極 1707 とが形成される。第 1 部材 1708 とゲート電極は 1 対 1 で対応し、第 1 絶縁部材 1708 の側面は対応するゲート電極の側面と同一面を構成することが望ましい。第 2 絶縁部材 1709 とゲート電極も 1 対 1 で対応し、第 2 絶縁部材 1709 の側面は対応するゲート電極の側面と同一面を構成することが望ましい。ここで、画素部 1011 においてゲート電極の上に第 1 絶縁部材 1708 を有することで、後のイオン注入工程においてゲート電極にイオンが注入されることを低減することが可能となるため、ゲート電極の性能のばらつきが低減可能である。ここで、図 17（a）ではゲート絶縁膜は省略しているが、主面 302 上に存在している。図 17（b）から図 19（b）までにおいてもゲート絶縁膜については同様に省略している。

#### 【0084】

次に、図 17（b）に示すように、各トランジスタのソース領域及びドレイン領域を構成するための半導体領域を形成する。転送トランジスタにおいては、ドレイン領域である FD 領域 1711 を形成する。ここで、FD 領域 1711 と PD の電荷蓄積領域 1611 との間に P 型半導体領域 1712 を形成する。この P 型半導体領域 1712 は転送トランジスタの動作を可能とするためのポテンシャルバリアとして機能する。また、P 型半導体領域 1712 はいわゆるパンチスルーストップの機能を有している。そして、電荷蓄積領域 1611 の上を覆うように P 型半導体領域 1710 を形成する。P 型半導体領域 1710 は、半導体基板 301 の表面にて生じる暗電流から電荷蓄積領域 1611 を保護する表面保護領域としての機能を有する。他のトランジスタにおいては、この図 17（b）においてはソース領域及びドレイン領域の一部となる半導体領域を形成している。この半導体領域は、完成後のトランジスタのソース領域及びドレイン領域の少なくともいずれかが有する低不純物濃度を有する半導体領域である。また、低電圧用のトランジスタにおいてはパンチスルー低減のためのソース領域及びドレイン領域とは逆導電型で、ソース領域及びドレイン領域が形成される領域の下に半導体領域を更に形成する。各トランジスタのソース領域及びドレイン領域の一部となる半導体領域の導電型は N 型トランジスタの場合には N 型であり、P 型トランジスタの場合には P 型である。これら各半導体領域は、例えばイオン注入によって形成可能であり、詳細な説明は省略する。この時、低電圧用と高電圧用のトランジスタで、信頼性向上のため、ソース領域及びドレイン領域の一部となる半導体領域の濃度を変えることが好ましい。

#### 【0085】

そして、図 17（c）に示すような絶縁膜 1713 とスペーサー 1714 を形成する。絶縁膜 1713 は画素部 1011 にのみに形成される。絶縁膜 1713 は PD の反射防止膜として機能できるように、その材料及び厚みが設定される。スペーサー 1714 は周辺

10

20

30

40

50

回路部 1016 の各トランジスタのゲート電極の側壁に形成されている。絶縁膜 1713 は酸化シリコンの膜の上に窒化シリコンの膜が積層した構造を有し、スペーサー 1714 は酸化シリコンの膜の上に窒化シリコンの膜が積層した構造となっている。なお、スペーサー 1714 は窒化シリコンの部材とゲート電極との間に酸化シリコンの部材があるともいえる。これらは、正面 302 の上のゲート絶縁膜とゲート電極と第 1 絶縁部材 1708 と第 2 絶縁部材 1709 を覆うように、すなわち図 17 (b) の状態で酸化シリコンからなる膜を CVD 法で形成した後、CVD 法で窒化シリコンからなる膜を形成する。その後、画素部 1011 を覆うフォトレジストパターンを形成する。そして、フォトレジストパターンをマスクとして画素部 1011 及び周辺回路部 1016 に渡って異方性のエッチングを行い、周辺回路部 1016 の酸化シリコンからなる膜と窒化シリコンからなる膜とを除去する。周辺回路部 1016 の各ゲート電極の側面に接して、酸化シリコンからなる膜と窒化シリコンからなる膜とからなるスペーサー 1714 が形成され、図 17 (c) の構成となる。ここで、絶縁膜 1713 とスペーサー 1714 とを同一膜から形成するため、工程を削減することが可能となる。また、スペーサー 1714 のみを形成する場合には、PD の上に形成されたスペーサー用の絶縁膜をエッチングすることになるため、PD にエッチングダメージが生じうる。しかし、絶縁膜 1713 とスペーサー 1714 とを同一膜から形成するため、PD へのダメージの発生を抑制可能である。

10

## 【0086】

図 18 (a) では、周辺回路部 1016 の各トランジスタのソース領域及びドレイン領域の一部を形成する。高電圧用の N 型トランジスタのゲート電極と、高電圧用の N 型トランジスタのソース領域及びドレイン領域が形成される領域とを露出させるフォトレジストパターンを形成する。同時に、低電圧用の N 型トランジスタのゲート電極と、低電圧用の N 型トランジスタのソース領域及びドレイン領域が形成される領域とが露出させるフォトレジストパターンを形成する。その後、ソース領域及びドレイン領域 1803 とソース領域及びドレイン領域 1804 を形成するための N 型の不純物となるイオン注入を行う。そして、高電圧用の P 型トランジスタのゲート電極と、高電圧用の P 型トランジスタのソース領域及びドレイン領域が形成される領域とを露出させるフォトレジストパターンを形成する。同時に、低電圧用の P 型トランジスタのゲート電極と、低電圧用の P 型トランジスタのソース領域及びドレイン領域とが形成される領域とが露出させるフォトレジストパターンを形成する。その後、ソース領域及びドレイン領域 1802 とソース領域及びドレイン領域 1804 を形成するための P 型の不純物となるイオン注入を行う。この工程によって、図 17 (b) において形成されたソース領域及びドレイン領域を形成する半導体領域よりも不純物濃度が高い半導体領域を形成する。これら半導体領域によって、LDD 構造 (Lightly Doped Drain 構造) を有するトランジスタが形成される。ここで、画素部 1011 のトランジスタは、本工程で形成される不純物濃度が高い半導体領域を有さない。このような構成によって、例えば増幅トランジスタのダイナミックレンジが向上する。

20

30

## 【0087】

そして、画素部 1011 を覆う絶縁膜 1806 を形成する。この絶縁膜 1806 は、例えば酸化シリコンからなる膜である。画素部 1011 及び周辺回路部 1016 を覆うように CVD 法により酸化シリコンからなる膜が形成され、主に画素部 1011 を覆うフォトレジストパターンを形成する。フォトレジストパターンをマスクとして、酸化シリコンからなる膜に対して異方性エッチングを行い、フォトレジストパターンで覆われていない酸化シリコンからなる膜の一部を除去する。ここで、フォトレジストパターンは、シリサイドを設けない領域を覆うように、すなわち酸化シリコンからなる膜がシリサイドを設けない領域に残るように、設けられる。この時、フォトレジストパターンで覆われていない領域においては、例えば周辺回路部 1016 のソース領域及びドレイン領域とゲート電極は露出している。

40

## 【0088】

絶縁膜 1806 が形成された後、シリサイド領域 1807 が形成される。シリサイド領

50

域 1807 は、例えばコバルトシリサイドからなる。シリサイド領域は、タングステンシリサイド、チタンシリサイド等の任意の材料から形成可能である。シリサイド領域 1807 は、まず、画素部 1011 においては絶縁膜 1806 を覆うように、周辺回路部 1016 においてはソース領域及びドレイン領域とゲート電極とを覆うように、コバルトからなる金属膜が形成される。金属膜は例えばスパッタ法などで形成可能である。金属膜が形成された後、金属とシリコン（ポリシリコンを含む）とが反応するように熱処理を行い、シリサイドを形成する。ここで、周辺回路部 1016 においてはソース領域及びドレイン領域とゲート電極は、先の絶縁膜 1806 を形成する際にその表面が露出しているため、金属膜がそれらと接するように形成可能である。熱処理後、未反応の金属をエッチングにより除去し、図 18 (b) の構成を得る。画素部 1011 にはシリサイド領域が形成されていない。このような構成によって、コバルト等の金属の拡散が低減され、P D でのリークや P D の信号へのノイズ（いわゆる白傷）を低減することが可能となる。なお、画素部 1011 の任意の構成にシリサイド領域を設けてもよく、周辺回路部 1016 の任意の構成にシリサイド領域を設けないようにしてもよい。

10

## 【0089】

次に、図 19 (a) に示すような絶縁膜 1901 と絶縁膜 1902 とを形成する。絶縁膜 1901 と絶縁膜 1902 は、酸化シリコンからなる膜と、その上に設けられた窒化シリコンからなる膜の積層膜である。絶縁膜 1901 は、実施例 1 等と同様に P D に対応して形成される。絶縁膜 1902 は、周辺回路部 1016 のトランジスタを覆うように形成され、シリサイド領域を覆うように形成される。絶縁膜 1902 は、後にコンタクトホール形成時のエッチングストップとして機能させることも可能である。ここで、絶縁膜 1901 をゲート電極を覆うように形成する。この構成によって、後の工程におけるエッチングによってゲート電極が削られてしまうことを抑制することが出来る。また、絶縁膜 1901 と絶縁膜 1902 とを同一膜から形成することで、工程の削減が可能であり、また、別の膜から形成する場合に比べてダメージを低減することが出来る。

20

## 【0090】

そして、図 19 (b) に示すような絶縁膜 1905 となる膜を形成し、絶縁膜 1905 となる膜に対してエッチングを行い、絶縁膜 1905 となる膜の一部を除去してコンタクトホールを形成する。各コンタクトホールにプラグとなる金属を設け、図 19 (b) に示す構成が得られる。ここで、絶縁膜 1905 は、例えば C V D 法によって形成される酸化シリコンからなる膜である。画素部 1011 のプラグ 1903 と周辺回路部 1016 のプラグ 1904 は、例えば、バリアメタルとなるチタン及び窒化チタンとタングステンとかなる。ここで、コンタクトホールを形成する際のエッチングにおいて、画素部 1011 の絶縁膜 1713 と周辺回路部 1016 の絶縁膜 1807 とがエッチングストップとして機能する。それは、エッチングの際に、絶縁膜 1905 となる酸化シリコンからなる膜のエッチング速度が、絶縁膜 1713 及び絶縁膜 1807 の窒化シリコンからなる膜とのエッチング速度よりも速くなるような条件でエッチングを行う。絶縁膜 1713 及び絶縁膜 1807 が露出した時点でエッチング条件を切り替え、絶縁膜 1713 及び絶縁膜 1807 を除去する。このようなコンタクトホールの形成方法によって、半導体基板 301 へのダメージを低減することが出来る。

30

## 【0091】

ここで、画素部 1011 のエッチングストップとして機能する膜と、周辺回路部 1016 のエッチングストップとして機能する膜とは別の膜を設けている。このように別の膜とすることで、画素部 1011 と周辺回路部 1016 の膜厚を独立で設定可能であり、光学特性と電気特性の両立が可能となる。

40

## 【0092】

また、絶縁膜 1902 は画素部 1011 のプラグ 1903 に接さないように配置される。画素部 1011 のプラグ 1903 が形成される領域において、画素部 1011 のエッチングストップとして機能する絶縁膜 1713 の上に絶縁膜 1902 を設けると、エッチングストップとして機能する膜が 2 層存在してしまう。このような構成では、エッチングの

50

条件の切り替えが増加し、また、コンタクトホールの形状の制御が困難となる。更に、2層が積層してしまう領域があるとそれらを覆う絶縁膜1905の厚みが増大してしまう。よって、画素部1011のプラグ1903に接さないように絶縁膜1902が配置されることで、固体撮像装置の特性を向上させることが可能となる。

【0093】

この後は、一般的な半導体プロセスにより配線等を形成し、実施例1等に示す導波路を形成し、カラーフィルタ等を形成することにより固体撮像装置が完成する。

【0094】

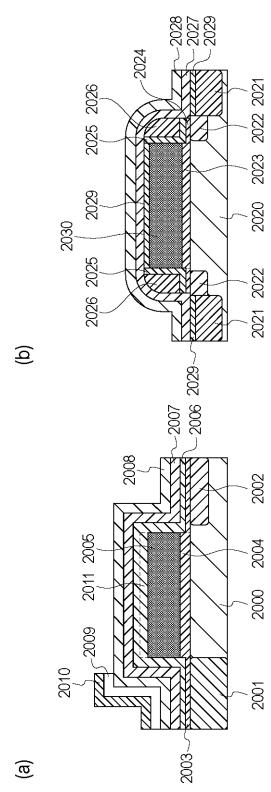

このような製造方法で形成した固体撮像装置のトランジスタの構造について、図20を用いて説明する。画素部のトランジスタの例として転送トランジスタを、周辺回路部のトランジスタの例として高耐圧用のN型トランジスタを示す。図20(a)は転送トランジスタのゲート電極近傍の拡大模式図であり、図20(b)は高耐圧用のN型トランジスタのゲート電極近傍の拡大模式図である。図2(a)及び図2(b)はそれぞれ図19(a)で示した状態に対応している。

10

【0095】

図20(a)において、N型半導体領域2000と、電荷蓄積領域2001と、FD領域2002とは図19(a)の半導体基板301に含まれる。半導体基板を覆うようにして設けられたゲート絶縁膜2004とゲート絶縁膜延在部2003とが設けられている。

【0096】

ゲート絶縁膜延在部2003は、ゲート電極2005の下から電荷蓄積領域2001及びFD領域2002の上に延在した部分を示している。ゲート絶縁膜2004はゲート絶縁膜延在部2003より厚いが、適宜変更可能である。酸化シリコンからなる絶縁膜2006が、ゲート電極2005と、電荷蓄積領域2001と、FD領域2002とを覆っている。第1絶縁部材2011と絶縁膜2006とは、共に酸化シリコンからなる。絶縁膜2006の上に、ゲート電極2005と、電荷蓄積領域2001と、FD領域2002とを覆い、窒化シリコンからなる絶縁膜2007が設けられている。PDである電荷蓄積領域2001と窒化シリコンからなる絶縁膜2007との間に酸化シリコンからなる絶縁膜2006を設けたことで、暗電流の抑制が可能となる。更に、酸化シリコンからなる絶縁膜2008が、絶縁膜2007の上でゲート電極2005と、電荷蓄積領域2001と、FD領域2002とを覆うように設けられている。そして、絶縁膜2008の上で、電荷蓄積領域2001に対応する部分にのみ、酸化シリコンからなる絶縁膜2009と窒化シリコンからなる絶縁膜2010とが設けられている。絶縁膜2010は絶縁膜2009の上に設けられている。ここで、図20(a)の構成と図16～図19の構成との対応は次のようになる。絶縁膜2006は絶縁膜1713に、絶縁膜2006及び絶縁膜2007は絶縁膜1713に、第1絶縁部材2011は第1絶縁部材1708に、絶縁膜2008は絶縁膜1806に、絶縁膜2009及び絶縁膜2010は絶縁膜1901に、対応する。ここで、絶縁膜2006と第1絶縁部材2011と酸化シリコンからなり、一体の膜のようにみなせる。PDの上からゲート電極の上に延在する酸化シリコン膜がゲート電極の上で厚みを増すような構成となっている。

20

【0097】

一方、図20(b)においては、P型半導体領域2020と、ソース領域及びドレイン領域となるN型半導体領域2021と、ソース領域及びドレイン領域の一部を構成しN型半導体領域2021よりも不純物濃度が低いN型半導体領域2022とが示されている。これらは、図19(a)の半導体基板301に含まれている。半導体基板を覆うようにして設けられたゲート絶縁膜2023とゲート絶縁膜延在部2024とが設けられている。ゲート絶縁膜延在部2024は、ゲート電極2030の下からN型半導体領域2022の上に延在した部分を示している。ゲート絶縁膜2023はゲート絶縁膜延在部2024より厚いが、適宜変更可能である。ゲート電極2030とN型半導体領域2021の上にはシリサイド領域2029が設けられている。酸化シリコンからなる絶縁膜2025と窒化シリコンからなる絶縁膜2026とが、サイドスペーサーを構成している。サイドスペー

30

40

50

サーは、ゲート電極 2030 の側面に接し、N型半導体領域 2022 の上に設けられている。絶縁膜 2026 とゲート電極 2030との間には絶縁膜 2025 が配置している。窒化シリコンからなる膜とゲート電極や半導体領域との間に酸化シリコンからなる膜を設けることで、トランジスタの信頼性の低下を抑制可能である。N型半導体領域 2021 とサイドスペーサーとゲート電極 2030 とを覆って酸化シリコンからなる絶縁膜 2027 と窒化シリコンからなる絶縁膜 2028 とが設けられている。絶縁膜 2028 は絶縁膜 2027 の上に設けられている。N型半導体領域 2021 と窒化シリコンからなる膜との間に酸化シリコンからなる膜が設けられていることで、半導体基板の正面 302 と窒化シリコンからなる膜とが接さないため、暗電流の発生を低減可能である。ここで、図 20 (b) の構成と図 16 ~ 図 19 の構成との対応は次のようになる。絶縁膜 2025 及び絶縁膜 2026 はサイドスペーサー 1714 に、絶縁膜 2027 及び絶縁膜 2028 は絶縁膜 1902 に、対応する。

10

## 【0098】

そして、図 16 ~ 図 19 で説明してきたように、図 20 (a) 及び図 20 (b) において、絶縁膜 2006 と絶縁膜 2025 とは同一の膜から形成され、絶縁膜 2007 と絶縁膜 2026 とは同一の膜から形成される。また、図 20 (a) 及び図 20 (b) において、絶縁膜 2009 と絶縁膜 2027 とは同一の膜から形成され、絶縁膜 2010 と絶縁膜 2028 とは同一の膜から形成される。このような形成方法によって、膜を形成する工程の回数を減らすことができ、また、膜を形成する際の熱による不純物拡散が低減可能となる。

20

## 【0099】

また、窒化シリコンからなる絶縁膜 2007 と絶縁膜 2028 はコンタクトホール形成時のエッチングストップ膜として機能可能である。ここで、絶縁膜 2007 は、図 19 (b) にあるように、プラグ 1903 に接して、画素部 1011 のプラグ 1903 以外を覆っている。また、絶縁膜 2028 は、プラグ 1904 に接して、周辺回路部 1016 のプラグ 1904 以外を覆っている。絶縁膜 2028 は、画素部 1011 に設けられていてもよいが、画素部 1011 のプラグ 1903 が形成されうる部分には設けられないことが望ましい。それは、窒化シリコンからなる膜が積層されてしまい、プラグ 1903 のコンタクトホール形成時のエッチングが煩雑なものとなってしまうためである。なお、本実施例の絶縁膜の構造によれば、画素部 1011 及び周辺回路部 1016 において、半導体基板の上に、半導体基板側から酸化シリコンからなる膜、窒化シリコンからなる膜、酸化シリコンからなる膜の順に設けられている。このような構成によって、画素部 1011 と周辺回路部 1016 とでコンタクトホール形成のためのエッチングを同時にを行うことが可能である。しかし、コンタクトホールを形成する際には、画素部 1011 のプラグ 1903 のためのコンタクトホールと、周辺回路部 1016 のプラグ 1904 のためのコンタクトホールとは、別の工程で形成することが好ましい。より正しくは、周辺回路部 1016 のプラグ 1904 のためのコンタクトホール形成時に、画素部 1011 のプラグ 1903 のためのコンタクトホールが形成されていないか、コンタクトホールがプラグあるいはフォトレジストマスクで埋められていることが望ましい。つまり、周辺回路部 1016 のプラグ 1904 のためのコンタクトホール形成時に、シリサイド領域がない部分が露出していないことが望ましい。例えば、プラグ 1903 のためのコンタクトホールを形成し、プラグ 1903 を形成した後、プラグ 1904 のためのコンタクトホールを形成し、プラグ 1904 を形成する。同じ工程で行うと、シリサイド領域を露出することになる周辺回路部 1016 のプラグ 1904 のためのコンタクトホール形成時に、シリサイド領域がない部分の半導体基板の正面 302 を露出させることになってしまう。この場合には、コンタクトホール形成のエッチングによってシリサイド領域の金属が飛散し、シリサイド領域がない部分が金属によって汚染される可能性があるためである。

30

## 【0100】

本実施例では、シリサイド領域を周辺回路部のトランジスタのゲート電極とソース領域とドレイン領域に設けているが、いずれか 1 つでもよい。また、画素部の任意のトランジ

40

50

スタに設けてもよい。

【 0 1 0 1 】

また、本実施例では、実施例1と同様に導波路を設けた場合の固体撮像装置について説明したが、図21に示すように、絶縁膜1901を設けず、導波路を設けない構成にも適用可能である。

【 0 1 0 2 】

以上、説明したように、本発明の構成によって、反射防止膜の性能を低下させることなく導波路が形成可能である。また、光電変換部に対応した絶縁膜を有することで、導波路の下面からの光の広がりを抑制し、集光効率を向上することが可能である。また、本発明の構成によって、周辺回路部におけるコンタクトホール形成時のダメージが低減可能であり、高品位な固体撮像装置を提供することが可能となる。なお、これら実施例は適宜変更可能であり、例えば、反射防止膜が各光電変換部に 1 対 1 で形成されていてもよい。また、それぞれの実施例は適宜組み合わせ可能である。

## 【符号の説明】

【 0 1 0 3 】

- |       |        |

|-------|--------|

| 2 0 3 | 電荷蓄積領域 |

| 2 0 7 | ゲート電極  |

| 6 1 0 | 複数の絶縁膜 |

| 3 2 4 | 高屈折率部材 |

| 3 0 5 | 絶縁膜    |

| 3 0 5 | 絶縁膜    |

| 3 1 7 | 絶縁膜    |

【 义 1 】

【図2】

【図3】

【図4】

【図5】

【図6】

【 図 7 】

【 図 8 】

【 図 9 】

【 図 1 0 】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

【 图 1 4 】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

---

フロントページの続き

(72)発明者 鈴木 健太郎

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 碓井 崇

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 加藤 太朗

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 下津佐 峰生

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

F ターム(参考) 4M118 BA14 CA02 CA18 CA32 CA34 EA01 EA14 FA06 FA33 GA09

GC07 GD04 GD07 GD11