(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4336115号

(P4336115)

(45) 発行日 平成21年9月30日(2009.9.30)

(24) 登録日 平成21年7月3日(2009.7.3)

(51) Int.Cl.

F 1

G 11 B 20/14 (2006.01)

G 11 B 7/005 (2006.01)G 11 B 20/14 351 A

G 11 B 7/005 Z

請求項の数 9 (全 11 頁)

(21) 出願番号 特願2003-20726 (P2003-20726)

(22) 出願日 平成15年1月29日 (2003.1.29)

(65) 公開番号 特開2004-127474 (P2004-127474A)

(43) 公開日 平成16年4月22日 (2004.4.22)

審査請求日 平成15年1月29日 (2003.1.29)

審判番号 不服2006-14808 (P2006-14808/J1)

審判請求日 平成18年7月10日 (2006.7.10)

(31) 優先権主張番号 091123157

(32) 優先日 平成14年10月4日 (2002.10.4)

(33) 優先権主張国 台湾(TW)

(73) 特許権者 500067499

聯發科技股份有限公司

台灣新竹市新竹科學園區篤行一路 1 號

(74) 代理人 100082304

弁理士 竹本 松司

(74) 代理人 100088351

弁理士 杉山 秀雄

(74) 代理人 100093425

弁理士 湯田 浩一

(74) 代理人 100102495

弁理士 魚住 高博

(74) 代理人 100112302

弁理士 手島 直彦

(72) 発明者 侯 坤穎

台灣雲林縣北港鎮公館里大同路82號

最終頁に続く

(54) 【発明の名称】 B C A 信号のサンプリングクロックジェネレータ

## (57) 【特許請求の範囲】

## 【請求項 1】

B C A 信号のサンプリングクロックジェネレータにおいて、光ディスクの回転速度に正比例する速度指示信号を受け取り、並びに各速度指示信号周期に対応する参考クロックを計数して計数値を発生する周波数カウンタと、該周波数カウンタの計数値を受け取り、並びに設定値で分割して周波数分割値を発生する分割器と、

該参考クロック、B C A 再生信号及び該周波数分割値を受け取り、サンプリングクロックを発生し、該周波数分割値を除数として該参考クロックに対する周波数分割を行い、且つ該B C A 再生信号に基づきサンプリングクロックの位相調整を行う可変除数周波数分割器と、

を具え、

前記速度指示信号がディスクドライブの主軸モータ回転速度の速度指示信号或いはその整数倍周波数信号とされたことを特徴とする、B C A 信号のサンプリングクロックジェネレータ。

## 【請求項 2】

請求項 1 に記載のB C A 信号のサンプリングクロックジェネレータにおいて、前記可変除数周波数分割器が、

B C A 再生信号に基づきクリア信号を発生するカウンタクリア信号ジェネレータと、

参考クロックと周波数分割値を受け取り計数値を出力し、該クリア信号が有効である時

10

20

に計数値をクリアするカウンタと、

該計数値を受け取り、該計数値が設定値に等しい時にサンプリングクロックのサンプリングパルスを発生するパルスジェネレータと、

を具えたことを特徴とする、BCA信号のサンプリングクロックジェネレータ。

#### 【請求項3】

請求項2に記載のBCA信号のサンプリングクロックジェネレータにおいて、前記カウンタクリア信号ジェネレータが、BCA再生信号の上昇縁にある時にクリア信号をある時間有効とする、BCA信号のサンプリングクロックジェネレータ。

#### 【請求項4】

BCA信号のサンプリングクロックジェネレータにおいて、

10

参考クロックを受け取り、並びに該参考クロックを設定値で分割した後に計数クロックを発生する周波数分割器と、

光ディスクの回転速度に正比例する速度指示信号を受け取り、並びに各速度指示信号周期に対応する前述の計数クロックのパルス数を計数して周波数分割値を発生する周波数カウンタと、

該参考クロック、BCA再生信号及び該周波数分割値を受け取り、サンプリングクロックを発生し、該周波数分割値を除数として該参考クロックに対する周波数分割を行い、且つ該BCA再生信号に基づきサンプリングクロックの位相調整を行う可変除数周波数分割器と、

を具えたことを特徴とする、BCA信号のサンプリングクロックジェネレータ。

20

#### 【請求項5】

請求項4に記載のBCA信号のサンプリングクロックジェネレータにおいて、前記速度指示信号がディスクドライブの主軸モータ回転速度の速度指示信号或いはその整数倍周波数信号とされたことを特徴とする、BCA信号のサンプリングクロックジェネレータ。

#### 【請求項6】

請求項4に記載のBCA信号のサンプリングクロックジェネレータにおいて、前記可変除数周波数分割器が、

BCA再生信号に基づきクリア信号を発生するカウンタクリア信号ジェネレータと、

参考クロックと周波数分割値を受け取り計数値を出力し、該クリア信号が有効である時に計数値をクリアするカウンタと、

30

該計数値を受け取り、該計数値が設定値に等しい時にサンプリングクロックのサンプリングパルスを発生するパルスジェネレータと、

を具えたことを特徴とする、BCA信号のサンプリングクロックジェネレータ。

#### 【請求項7】

請求項6に記載のBCA信号のサンプリングクロックジェネレータにおいて、前記カウンタクリア信号ジェネレータが、BCA再生信号の上昇縁にある時にクリア信号をある時間有効とする、BCA信号のサンプリングクロックジェネレータ。

#### 【請求項8】

BCA信号のサンプリングクロックジェネレータにおいて、

40

光ディスクの回転速度に正比例する速度指示信号を受け取り、並びに各速度指示信号周期の対応する計数クロックのパルス数を計数し、並びに周波数分割値を出力する周波数カウンタと、

参考クロック、BCA再生信号及び前述の周波数分割値を受け取り、サンプリングクロックを発生し、該周波数分割値を除数として前述の参考クロックに対して周波数分割を行い、且つBCA再生信号に基づきサンプリングクロックの位相調整を行う可変除数周波数分割器と、

を具えたことを特徴とする、BCA信号のサンプリングクロックジェネレータ。

#### 【請求項9】

請求項8に記載のBCA信号のサンプリングクロックジェネレータにおいて、前記速度指示信号がディスクドライブの主軸モータ回転速度指示信号或いはその整数倍周波数信号

50

とされたことを特徴とする、BCA信号のサンプリングクロックジェネレータ。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は BCA 信号のサンプリングクロックジェネレータに係り、特に、主軸モータの速度指示信号を利用してサンプリングクロックを発生する BCA 信号のサンプリングクロックジェネレータに関する。

【0002】

【従来の技術】

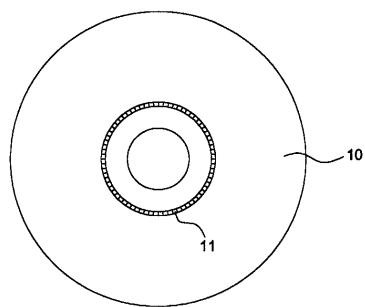

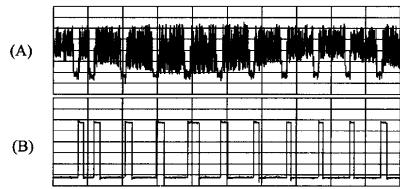

現在ディジタルオーディオビデオディスク (Digital Video Disc / Digital Versatile Disc ; DVD) には、読み取り専用の DVD-ROM (Read Only Memory)、一次書き込み可能な DVD-R (Recordable)、及び乱アクセス式の DVD-RAM (Random Access Memory) がある。DVD-ROM の発展において、この光ディスクは BCA (Burst Cutting Area) をデータ記録に供し、これにより各光ディスクに個別データが表示される。図 1 に示されるように、光ディスク 10 の BCA 11 はディスクの中心より起算して 22.3 (+0/-0.4) mm から 23.5 ± 0.5 mm 位置までである。各 BCA データビットは二つの BCA チャネルビットをエンコードしてなる。チャネルビット「10」はデータビット「0」を代表し、チャネルビット「01」はデータビット「1」を代表する。BCA のデータ記録方法は、レーザービームを輻射方向で該 BCA の一部エリアの反射層 (reflection film) を除去するものである。反射層除去の長さと間隔はチャネルビットを RZ (Return to Zero) 変調により制御される。もとの BCA にはすでにダミーピットストリング (Dummy Bit String) が存在し、ゆえに光学ヘッドが BCA データを読み取る時、得られる RF (radio frequency) 信号からは BCA のストライプ (stripe) 信号が除かれているほか、高周波ピットストリング信号が含まれ、これは図 2 の (A) に示されるとおりである。その後、BCA 信号再生装置で RF 信号を処理して BCA 再生信号を発生し、これは図 2 の (B) に示されるとおりである。

【0003】

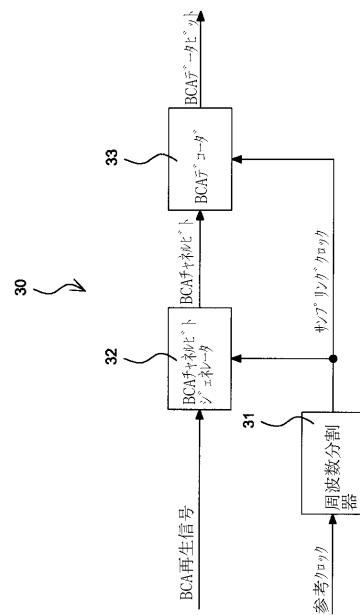

図 3 は周知の BCA データビットの取得装置のブロック図である。図 3 に示されるように、該 BCA データビット取得装置 30 は、まず BCA チャネルビットジェネレータ 32 が、サンプリングクロックに基づき BCA 再生信号をサンプリングした後、RZ 復調 (Demodulation) により BCA チャネルビットを発生し、さらに BCA デコーダ 33 でデコードして BCA データビットを得る。サンプリングクロック発生の方式は、参考クロックを周波数分割器 31 で周波数分割して発生する方式である。しかし、このような方式は光ディスクの回転速度が一定の設定値に符合するように確定させる必要がある。もし光ディスクの回転速度が設計値と異なると、BCA 再生信号の周波数が光ディスクの回転速度により改変するため、BCA チャネルビットジェネレータ 32 がサンプリングクロックに基づいて正確に BCA 再生信号に対するサンプリングを行えなくなる。

【0004】

位相ロック回路 (Phase locked loop; PLL) により BCA 再生信号に基づきサンプリングクロックを発生することはできるが、しかし、PLL の設計は比較的複雑であり、且つコストが比較的高い。このほか、周知のディスク再生装置には、エッジインターバル (edge interval) を計算する方法によりサンプリングクロックを発生する方法を採用したものもあるが、この方法は実施するために必要なファームウェア (firmware) 或いは回路が多過ぎ、コストが高い (例えば特許文献 1)。

【0005】

【特許文献 1】

米国特許第 6 0 3 4 9 3 4 号明細書

【0006】

10

20

30

40

50

**【発明が解決しようとする課題】**

上述の問題を鑑み、本発明の目的は、主軸モータの速度指示信号を利用してサンプリングクロックを発生するB C A信号のサンプリングクロックジェネレータを提供することとする。

**【0007】**

本発明のサンプリングクロックジェネレータは、ディスクの回転速度に基づきサンプリングクロックの周波数を動態調整する。該サンプリングクロックジェネレータは主軸モータの速度指示信号を受け取り各速度指示信号周期が対応する参考クロックのパルス数を計数し、並びに計数値を発生する周波数カウンタと、周波数カウンタの計数値を受け取り設定値で周波数分割した後に周波数分割値を発生する分割器と、参考クロック、B C A再生信号及び周波数分割値を受け取り、並びに該周波数分割値を除数として参考クロックに対して周波数分割を行い、且つ該B C A再生信号で位相調整することでサンプリングクロックを発生する可変除数周波数分割器と、を具えている。

10

**【0008】****【課題を解決するための手段】**

請求項1の発明は、B C A信号のサンプリングクロックジェネレータにおいて、光ディスクの回転速度に正比例する速度指示信号を受け取り、並びに各速度指示信号周期に対応する参考クロックを計数して計数値を発生する周波数カウンタと、

該周波数カウンタの計数値を受け取り、並びに設定値で分割して周波数分割値を発生する分割器と、

20

該参考クロック、B C A再生信号及び該周波数分割値を受け取り、サンプリングクロックを発生し、該周波数分割値を除数として該参考クロックに対する周波数分割を行い、且つ該B C A再生信号に基づきサンプリングクロックの位相調整を行う可変除数周波数分割器と、

を具え、

前記速度指示信号がディスクドライブの主軸モータ回転速度の速度指示信号或いはその整数倍周波数信号とされたことを特徴とする、B C A信号のサンプリングクロックジェネレータとしている。

請求項2の発明は、請求項1に記載のB C A信号のサンプリングクロックジェネレータにおいて、前記可変除数周波数分割器が、

30

B C A再生信号に基づきクリア信号を発生するカウンタクリア信号ジェネレータと、

参考クロックと周波数分割値を受け取り計数値を出力し、該クリア信号が有効である時に計数値をクリアするカウンタと、

該計数値を受け取り、該計数値が設定値に等しい時にサンプリングクロックのサンプリングパルスを発生するパルスジェネレータと、

を具えたことを特徴とする、B C A信号のサンプリングクロックジェネレータとしている。

請求項3の発明は、請求項2に記載のB C A信号のサンプリングクロックジェネレータにおいて、前記カウンタクリア信号ジェネレータが、B C A再生信号の上昇縁にある時にクリア信号を有効とする、B C A信号のサンプリングクロックジェネレータとしている。

40

請求項4の発明は、B C A信号のサンプリングクロックジェネレータにおいて、

参考クロックを受け取り、並びに該参考クロックを設定値で分割した後に計数クロックを発生する周波数分割器と、

光ディスクの回転速度に正比例する速度指示信号を受け取り、並びに各速度指示信号周期に対応する前述の計数クロックのパルス数を計数して周波数分割値を発生する周波数カウンタと、

該参考クロック、B C A再生信号及び該周波数分割値を受け取り、サンプリングクロックを発生し、該周波数分割値を除数として該参考クロックに対する周波数分割を行い、且つ該B C A再生信号に基づきサンプリングクロックの位相調整を行う可変除数周波数分割

50

器と、

を具えたことを特徴とする、BCA信号のサンプリングクロックジェネレータとしている。

請求項5の発明は、請求項4に記載のBCA信号のサンプリングクロックジェネレータにおいて、前記速度指示信号がディスクドライブの主軸モータ回転速度の速度指示信号或いはその整数倍周波数信号とされたことを特徴とする、BCA信号のサンプリングクロックジェネレータとしている。

請求項6の発明は、請求項4に記載のBCA信号のサンプリングクロックジェネレータにおいて、前記可変除数周波数分割器が、

BCA再生信号に基づきクリア信号を発生するカウンタクリア信号ジェネレータと、

参考クロックと周波数分割値を受け取り計数値を出力し、該クリア信号が有効である時に計数値をクリアするカウンタと、

該計数値を受け取り、該計数値が設定値に等しい時にサンプリングクロックのサンプリングパルスを発生するパルスジェネレータと、

を具えたことを特徴とする、BCA信号のサンプリングクロックジェネレータとしている。

請求項7の発明は、請求項6に記載のBCA信号のサンプリングクロックジェネレータにおいて、前記カウンタクリア信号ジェネレータが、BCA再生信号の上昇縁にある時にクリア信号をある時間有効とする、BCA信号のサンプリングクロックジェネレータとしている。

請求項8の発明は、BCA信号のサンプリングクロックジェネレータにおいて、

光ディスクの回転速度に正比例する速度指示信号を受け取り、並びに各速度指示信号周期の対応する計数クロックのパルス数を計数し、並びに周波数分割値を出力する周波数カウンタと、

参考クロック、BCA再生信号及び前述の周波数分割値を受け取り、サンプリングクロックを発生し、該周波数分割値を除数として前述の参考クロックに対して周波数分割を行い、且つBCA再生信号に基づきサンプリングクロックの位相調整を行う可変除数周波数分割器と、

を具えたことを特徴とする、BCA信号のサンプリングクロックジェネレータとしている。

請求項9の発明は、請求項8に記載のBCA信号のサンプリングクロックジェネレータにおいて、前記速度指示信号がディスクドライブの主軸モータ回転速度指示信号或いはその整数倍周波数信号とされたことを特徴とする、BCA信号のサンプリングクロックジェネレータとしている。

#### 【0009】

#### 【発明の実施の形態】

本発明はBCA信号のサンプリングクロックジェネレータを提供し、それはディスクの回転速度に基づきサンプリングクロックの周波数を動態調整する。該サンプリングクロックジェネレータは主軸モータの速度指示信号を受け取り各速度指示信号周期が対応する参考クロックのパルス数を計数し、並びに計数値を発生する周波数カウンタと、周波数カウンタの計数値を受け取り設定値で周波数分割した後に周波数分割値を発生する分割器と、参考クロック、BCA再生信号及び周波数分割値を受け取り、並びに該周波数分割値を除数として参考クロックに対して周波数分割を行い、且つ該BCA再生信号で位相調整することでサンプリングクロックを発生する可変除数周波数分割器と、を具えている。

#### 【0010】

#### 【実施例】

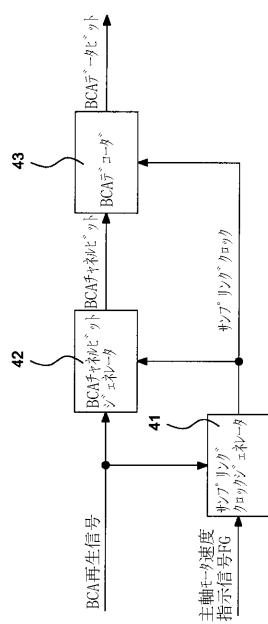

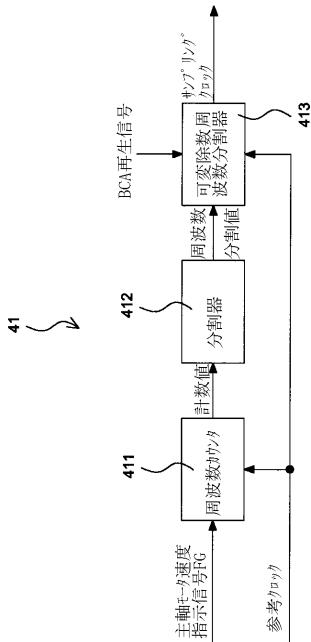

図4は本発明のBCA信号のサンプリングクロックジェネレータの実施構造を示す。本発明のBCA信号のサンプリングクロックジェネレータ41は、主軸モータ速度指示信号FGとBCA再生信号によりBCA信号のサンプリングクロックを発生する。このBCA信号のサンプリングクロックはBCAチャネルビットジェネレータ42とBCAデコーダ4

10

20

30

40

50

3に提供され、BCAチャネルビットジェネレータ42が正確なBCAチャネルビットをサンプリングできるようにし、BCAデコーダ43が正確なBCAデータビットにデコードできるようにする。

#### 【0011】

BCA規格(specification)に基づき、ディスク回転速度が毎分1440回転(1440rpm, 24Hz)の時、BCAチャネルビットの速度(channel bit rate)は $1/(8.89\text{ us})$ であり、即ち112.49KHzである。しかし、ディスク回転速度に変化がある時、BCAチャネルビットの速度もまた変化する。例えばディスク回転速度が毎分1300回転(1300rpm, 21.67Hz)の時、BCAチャネルビットの速度は $1/(9.85\text{ us})$ 、即ち、101.55KHzとなる。これにより、固定周波数のサンプリングクロックによりBCAチャネルビットのデータをキャプチャする時、ディスクが標準回転速度の時に正確にBCAチャネルビットのデータを取得できるが、ディスクが標準回転速度から大きく離れると、錯誤のBCAチャネルビットのデータが発生しうる。

#### 【0012】

仮に主軸モータ速度指示信号FGの周期(period)が $1/(24^*N)$ であり、そのうちNは異なる主軸モータ設計時の整数値、例えば3、4、5、6等であるとすると、各主軸モータ速度指示信号FGの周期は約 $(4678/N)$ 個のBCAチャネルビット、即ち $1/(24^*N)/(8.89 \times 10^{-6})$ を有する。主軸モータ速度指示信号FGの周波数とBCAチャネルビットの速度は正比例し、ゆえにただ主軸モータ速度指示信号FGの周波数を計算し、並びに $(4678/N)$ の関係に基づき、正確な周波数のBCA信号のサンプリングクロックを発生することができる。

#### 【0013】

図5は本発明のBCA信号のサンプリングクロックジェネレータ41の第1実施例のプロック図である。該サンプリングクロックジェネレータ41は周波数カウンタ411、分割器412、及び可変除数周波数分割器413を具えている。本発明は参考クロックを基準クロックとしてサンプリングクロックを発生し、これにより該参考クロックの周波数は主軸モータ速度指示信号FGの周波数より高くなればならず、またサンプリングクロックの周波数より高くなればならず、例えば参考クロックの周波数は33MHzとされうる。まず、周波数カウンタ411を利用して主軸モータ速度指示信号FGと参考クロックを受け取り、並びに主軸モータ速度指示信号FGの各周期が対応する参考クロックのパルス数を計算する。例えば、ディスク回転速度が1440rpmであり、N値が4の時、計数値は約343.75Kとされる。その後、分割器412を利用し計数値を等比例縮小し、周波数分割値を発生する。例えば、該分割器の除数は $(4678/N)$ 程度の範囲に設定可能で、即ち主軸モータ速度指示信号FGの周波数のBCAチャネルビットの速度の関係値付近、例えば1196とする。こうして、本実施例中、分割器412の出力する周波数分割値は約287となる。最後に、可変除数周波数分割器413を利用して参考クロックを分割値で分割し、サンプリングクロックを発生する。このサンプリングクロックの周波数は本実施例では約115KHzとされ、これは必要なサンプリングクロックの周波数112.5Kとの差が5%に満たない。この5%に満たない周波数の差は、周波数可変除数周波数分割器の設計を透過して位相調整することにより、チャネルビットの正確なサンプリングに影響を与えないものとされる。

#### 【0014】

且つ本発明のサンプリングクロックジェネレータはディスク回転速度に変化が発生した時、主軸モータ速度指示信号FGの周波数もまたこれに伴い変更するため、該サンプリングクロックの周波数もまたこれに伴い等比例で変更する。例えば、ディスク回転速度が1300rpmに下がる時、その変化率は10.3%である。この時、本実施例の計数値は約381Kに変わり、周波数分割値は318に変わり、サンプリングクロックの周波数は103.8KHzに代わる。これにより、サンプリングクロックの周波数もまた10.3%下がり、ゆえにシステムが回転速度に対応する正確なサンプリングクロックの周波数を発

10

20

30

40

50

生することができる。

**【0015】**

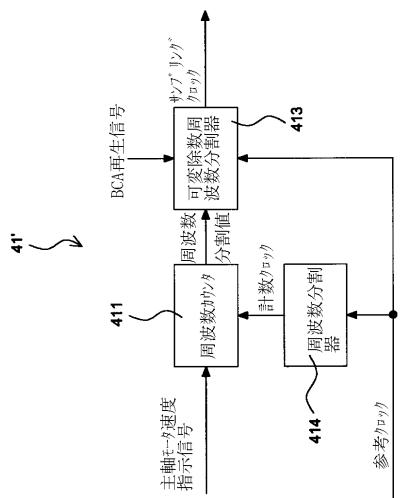

図6は本発明のBCA信号のサンプリングクロックジェネレータの第2実施例のブロック図である。第1実施例のサンプリングクロックジェネレータ41は周波数カウンタを利用して計数値を発生した後、さらに設定値で周波数分割して周波数分割値を発生したが、第2実施例のサンプリングクロックジェネレータ41'はまず参考クロックを周波数分割した後に計数クロックを発生し、更に周波数カウンタを利用して周波数分割値を発生する。このサンプリングクロックジェネレータ41'は、周波数分割器414、周波数カウンタ411、及び可変除数周波数分割器413を具えている。本発明は参考クロックを基準クロックとしてサンプリングクロックを発生し、これにより該参考クロックの周波数は主軸モータ速度指示信号FGの主軸モータ速度指示信号FGの周波数より高くなればならず、またサンプリングクロックの周波数より高くなればならず、例えば参考クロックの周波数は33MHzとされうる。まず、サンプリングクロックジェネレータ41'は、周波数分割器414を利用し、参考クロックを周波数分割し、計数クロックを発生する。該周波数分割器414の除数(4687/N)程度の範囲に設定され得て、すなわち、主軸モータ速度指示信号FGの周波数のBCAチャネルビットの速度の関係値付近、例えば1196とされる。これにより、周波数分割器414の発生する計数クロックの周波数は27.59KHzとなる。その後、周波数カウンタ411を利用し主軸モータ速度指示信号FGと計数クロックを受け取り、並びに主軸モータ速度指示信号FGの各周期の対応する計数クロックのパルス数を計算し、周波数分割値を発生する。例えば、ディスク回転速度が1440rpmであり、且つN値が4である時、周波数分割値は約287となる。最後に、可変除数周波数分割器413を利用し参考クロックを周波数分割値に基づき周波数分割し、サンプリングクロックを発生する。このサンプリングクロックの周波数は本実施例では約115KHzである。これにより、本実施例の発生するサンプリングクロックの周波数と必要なサンプリングクロックの周波数112.5KHzの差は5%に満たず、この5%に満たない周波数の差は、周波数可変除数周波数分割器の設計を透過して位相調整することにより、チャネルビットの正確なサンプリングに影響を与えないものとされる。当然、もしシステムが二種類の異なる周波数の参考クロックを提供できれば、周波数分割器414は省略可能である。例えば、システムは一つの計数クロックと一つの参考クロックを提供し且つ参考クロックの周波数が計数クロックの周波数の整数倍であるものとされる。

**【0016】**

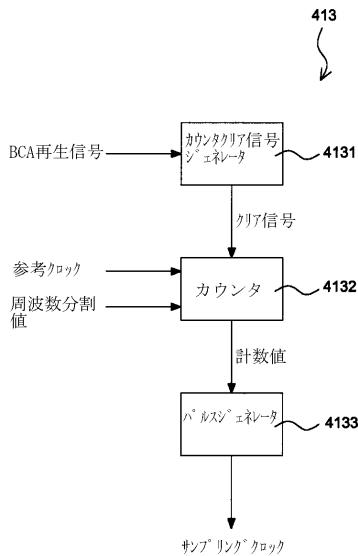

図7は可変除数周波数分割器のブロック図である。図示されるように、可変除数周波数分割器413は、カウンタクリア信号ジェネレータ4131、カウンタ4132、及びパルス発生器4133を具えている。該可変除数周波数分割器413はBCA再生信号を利用してサンプリングクロックの位相を調整し、発生するサンプリングクロックに良好なサンプリング位相を具備させ、且つサンプリングクロックの僅かな周波数誤差を補償できる。この可変除数周波数分割器413はカウンタクリア信号ジェネレータ4131を利用し、BCA再生信号に基づいてクリア信号を発生し、例えば、各BCA再生信号の上昇縁で一つのクリア信号のパルスを発生する。カウンタ4132は参考クロックと周波数分割値を受け取った後、計数値を発生し、並びに計数値が周波数分割値に等しい時は0にリセットされ並びに新たに計数し、或いは、クリア信号のパルスを受け取って0にリセットされ並びに新たに計数する。パルスジェネレータ4133はカウンタ4132の計数値を受け取り、並びに計数値がAに等しい時は、一つのサンプリングクロックのパルスを発生する。該サンプリングクロックのパルス幅は必要に応じて設計できる。例えば、該パルスジェネレータ4133は計数値がAとA+Bの間の時、出力信号がハイとなり、その他の時間ではローとなる。

**【0017】**

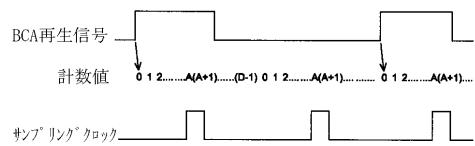

図8はBCA再生信号、計数値とサンプリングクロックのパルスの表示図である。図示されるように、BCA再生信号の上昇縁の時、計数値は0にクリアされる。その後、計数値がAの時、サンプリングクロックは一つのパルスを発生する。続いて、計数値がDとなる

10

20

30

40

50

時（Dは周波数分割値）、カウンタは0にリセットされ、並びに新たに計数する。可変除数周波数分割器413はBCA再生信号により位相調整するため、周波数分割値に僅かな誤差があっても、サンプリングクロックの発生に影響を与えることはない。

#### 【0018】

以上の実施例の説明は、本発明の実施範囲を限定するものではなく、本発明に基づきなしうる細部の修飾或いは改変は、いずれも本発明の請求範囲に属するものとする。

#### 【0019】

##### 【発明の効果】

本発明は、主軸モータの速度指示信号を利用してサンプリングクロックを発生するBCA信号のサンプリングクロックジェネレータを提供している。

10

##### 【図面の簡単な説明】

【図1】周知の光ディスクのBCA信号の表示図である。

【図2】光ディスクよりキャプチャされるRF信号（A）とBCA信号再生装置でRF信号を処理して発生するBCA再生信号（B）の表示図である。

【図3】周知のBCA信号の取得プロック図である。

【図4】本発明のBCA信号のサンプリングクロックジェネレータの実施構造図である。

【図5】本発明のBCA信号のサンプリングクロックジェネレータの第1実施例のプロック図である。

【図6】本発明のBCA信号のサンプリングクロックジェネレータの第2実施例のプロック図である。

20

【図7】本発明のBCA信号のサンプリングクロックジェネレータの可変除数周波数分割器のプロック図である。

【図8】本発明のBCA信号、計数値とサンプリングクロックのパルス表示図である。

##### 【符号の説明】

41、41' サンプリングクロックジェネレータ

411 周波数カウンタ

412 分割器

413 可変除数周波数分割器

4131 カウンタクリア信号ジェネレータ

4132 カウンタ

30

4133 パルスジェネレータ

414 周波数分割器

42 BCAチャネルビットジェネレータ

43 BCAデコーダ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(72)発明者 謝 坤宏

台湾高雄市前鎮區長江街65號14F

合議体

審判長 山田 洋一

審判官 関谷 隆一

審判官 横尾 俊一

(56)参考文献 特開平5-36207(JP,A)

特開2002-93059(JP,A)

特開昭53-111267(JP,A)

(58)調査した分野(Int.Cl., DB名)

G11B20/10

G11B20/14

H03L7/00-7/26