(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-38954

(P2004-38954A)

(43) 公開日 平成16年2月5日(2004.2.5)

(51) Int.CI.<sup>7</sup>

F 1

テーマコード(参考)

**G06F 11/18**

G06F 11/18

310C

5B034

**G06F 11/16**

G06F 11/16

310E

5B048

**G06F 11/22**

G06F 11/22

310B

審査請求 未請求 請求項の数 8 O.L. (全 8 頁)

(21) 出願番号 特願2003-161724 (P2003-161724)

(22) 出願日 平成15年6月6日 (2003.6.6)

(31) 優先権主張番号 10/183,560

(32) 優先日 平成14年6月28日 (2002.6.28)

(33) 優先権主張国 米国(US)

(71) 出願人 503003854

ヒューレット-パッカード デベロップメント カンパニー エル.ピー.

アメリカ合衆国 テキサス州 77070

ヒューストン 20555 ステイト

ハイウェイ 249

(74) 代理人 100081721

弁理士 岡田 次生

(74) 代理人 100105393

弁理士 伏見 直哉

(74) 代理人 100111969

弁理士 平野 ゆかり

最終頁に続く

(54) 【発明の名称】マイクロプロセッサのエラーをテストする方法および装置

## (57) 【要約】

【課題】ロックステップ性能をテストする装置および対応する方法を提供する。

【解決手段】装置は、ロックステップモードで動作する2つ以上のプロセッサを備え、プロセッサはそれぞれ、コードシーケンスを実行するプロセッサロジックと、コードシーケンスによって参照されるプロセッサ固有資源と、プログラム可能事象の発生に基づいて信号をアサートする状態マシンと、アサートされた信号を供給する出力と、を備える。装置はまた、2つ以上のプロセッサそれぞれの出力を読み取り比較するように動作可能なロックステップロジックブロックも備える。コードシーケンスの実行に基づくプロセッサ出力は、2つ以上のプロセッサそれぞれの出力を読み取り比較するように動作可能なロックステップロジックに提供される。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

マルチプロセッサ環境においてロックステップ機能をテストする装置であって、ロックステップモードで動作する2つ以上のプロセッサを有し、該2つ以上のプロセッサはそれぞれ、

コードシーケンスを実行するプロセッサロジックであって、同一のコードシーケンスが前記2つ以上のプロセッサそれぞれのプロセッサロジックによって実行される、プロセッサロジックと、

プログラム可能事象の発生に基づいて信号をアサートする状態マシンと、

前記アサートされた信号を供給する出力と、

を有し、装置はまた、

前記2つ以上のプロセッサそれぞれの前記出力を読み出して比較するように動作可能なロックステップロジックブロックを有する装置。

**【請求項 2】**

前記状態マシンは、カウントダウンタイムおよびプログラム可能レジスタアレイのうちの一方を含む請求項1記載の装置。

**【請求項 3】**

前記アサートされる信号はテストマシンチェックを含む請求項1記載の装置。

**【請求項 4】**

前記2つ以上のプロセッサはプロセッサ固有資源をさらに有し、該プロセッサ固有資源は、前記プログラム可能事象を実行して前記状態マシンに前記信号をアサートさせる請求項1記載の装置。

**【請求項 5】**

マイクロプロセッサにおいてエラーをテストする方法であって、

プログラム可能事象の発生に基づいて状態マシンを制御するようにプロセッサ固有資源をプログラムするステップと、

前記プログラム可能事象発生時にテスト信号をアサートするステップと、

前記アサートされたテスト信号を読み出すステップと、

前記アサートされたテスト信号を読み出した後にロックステップロジックをオフにし、それによって2つ以上のプロセッサのロックステップ動作が停止するステップと、

を含む方法。

**【請求項 6】**

前記状態マシンは、カウントダウンタイムおよびプログラム可能レジスタアレイのうちの一方を含む請求項5記載の方法。

**【請求項 7】**

前記アサートされる信号はテストマシンチェックを含む請求項5記載の方法。

**【請求項 8】**

前記プロセッサ固有資源は、前記プログラム可能事象を実行して前記状態マシンに前記信号をアサートさせる請求項5記載の方法。

**【発明の詳細な説明】****【0001】****【発明の属する技術分野】**

本発明は、ロックステッププロセッサを使用するコンピュータシステムでのエラーテストに関する。

**【0002】****【従来の技術】**

シリコンデバイスは、コンピュータシステムにおけるマイクロプロセッサを含め、宇宙線や粒子によってもたらされるエラー等の「ソフトエラー」の影響をますます受けやすくなっている。宇宙線および粒子の衝突は、マイクロプロセッサ内のノードの状態を変化させ、「ソフトエラー」を発生させる。ソフトエラーは一時的なものであり、コンピュー

10

20

30

40

50

タシステムの他の部分にとっては不可視であり得る。多くのコンピュータシステム、特にマイクロプロセッサは、信頼性の向上のために、ソフトエラーを検出して修正するハードウェアを備えている。従来技術によるマイクロプロセッサは、マイクロプロセッサのエラー検出 / エラー修正ハードウェアをテストするために、マイクロプロセッサにおける各種アレイ内のエラー（パリティ）ビットを初期化する能力を備えている。

#### 【0003】

コンピュータシステムの信頼性をさらに強化するために、ロックステップコアまたはFRC (Functional Reliability Check : 機能信頼性チェック) と呼ばれる技法が使用され、2つ以上のマイクロプロセッサまたはマイクロプロセッサコアがマスター / チェッカペアで動作し、2つ以上のコアの出力が常に比較される。出力の差はいずれも、おそらくソフトエラー状態を含むエラー状態を指示示す。しかし、ソフトエラーは一時的なものであるため、ソフトエラーの検出および修正に使用されるハードウェアは、シリコンにおいて確認することが難しい。

#### 【0004】

##### 【発明が解決しようとする課題】

本発明の目的は、ロックステップ性能をテストする装置および対応する方法を提供することである。

#### 【0005】

##### 【課題を解決するための手段】

高度なマルチコアプロセッサーーキテクチャでは、ロックステッププロセッサの動作をテストする装置および対応する方法が用いられる。実施形態において、装置は、ロックステップモードで動作する2つ以上のプロセッサを備え、2つ以上のプロセッサはそれぞれ、コードシーケンスを実行するプロセッサロジックであって、同一のコードシーケンスが2つ以上のプロセッサそれぞれのプロセッサロジックによって実行されるプロセッサロジックと、コードシーケンスによって参照されるプロセッサ固有資源と、プログラム可能事象の発生に基づいて信号をアサートする状態マシンと、アサートされた信号を供給する出力と、を備える。装置はまた、2つ以上のプロセッサそれぞれの出力を読み取り比較するように動作可能なロックステップロジックブロックも備える。コードシーケンスの実行に基づくプロセッサ出力は、2つ以上のプロセッサそれぞれの出力を読み取り比較するように動作可能なロックステップロジックに提供される。

#### 【0006】

詳細な説明では、同様の符号が同様の要素を指す添付図面を参照する。

#### 【0007】

##### 【発明の実施の形態】

チップ設計プロセス中にロックステップ機能性をテストする装置および対応する方法を開示する。ロックステッププロセスは、定義上、同一のコードストリームを実行し、同一の出力を生成する。プロセッサに組み込まれた、または他の方法でプロセッサに組み合わされたロックステップロジックを使用して、ロックステッププロセッサの出力の差を検出する。出力の差は、プロセッサのうちの少なくとも1つのプロセッサがエラー状態にあることを示し、ロックステップの損失につながり得る。個々のプロセッサへの直接アクセスなしで（たとえば、テストポートを経由して）は、チップ設計者（またはテスト作成者）は、テストのためにロックステップを損失させる差（たとえば、エラー状況）を、1つまたは複数のロックステッププロセッサに挿入することができない。ロックステップロジックの様々な機構をテストするために、本明細書に記載の装置および方法を使用して、ロックステップロジックによって検出されるであろうエラーを起こすことができる。

#### 【0008】

適正なロックステップ機能性を確認するテストプロセスの一環として、チップ設計者は、ロックステップ回復プロセス、すなわちロックステップを損失した2つ以上のプロセッサをロックステップ動作モードに復帰させるプロセスもテストする。開示する装置および対応する方法は、この特定の態様のロックステップ機能性をテストするように設計される。

さらに、本装置および本方法は、テスト結果の再現性を考慮する。

#### 【0009】

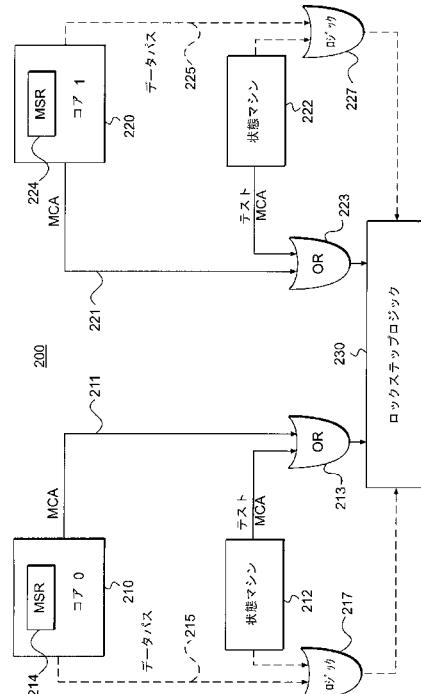

図1は、ロックステップエラーを注入し、ロックステップの損失からの適正回復をテストする能力を含む、エラーを注入しロックステップ機能をテストすることができるシリコンデバッグ環境200を示す。図1では、プロセッサコア210が、エラー信号バス211およびORゲート213を通してロックステップロジックブロック230に接続される。プロセッサコア210は、データバス215と、ORゲート、XORゲート、マルチプレクサ、またはある他のロジック要素であることができるロジック要素217を通してロックステップロジック230に接続される。プロセッサコア210とロックステップで動作するプロセッサコア220もまた、エラー通知バス221およびORゲート223、またデータバス225およびロジック要素227を使用してロックステップロジックブロック230に接続される。ORゲート213には状態マシン212も接続され、ORゲート223には状態マシン222が接続される。10

#### 【0010】

プロセッサコア210は、読み出し専用マシン固有レジスタ(Machine Specific Register: MSR)214等のプロセッサ固有資源を備えることができる。MSR214は、プロセッサコア210のアドレス(core\_id)等、プロセッサコア210に固有のデータを含むことができる。同様に、プロセッサコア220も、MSR214と同じ機能を実行するMSR224を備えることができる。エラー信号バス211および221、ならびにバス上のハードウェア(ORゲート213および223、ならびに状態マシン212および222)は、テストマシンチェックアサート(Machine Check Assertion: MCA)信号を含む、またはデータバス211および221のうちの一方におけるビットを変更する、エラーの注入に使用される。20

#### 【0011】

状態マシン212および222は、プログラム可能であればよく、タイマ/カウンタ、プログラム可能レジスタアレイ、または他の適したハードウェアデバイス(図1に示さず)であることができる。状態マシン212および222は、設定サイクル数に従って動作することができ、各動作サイクルにつき値が減分され、そして値がゼロまたは他のプログラム可能な値に達すると、その時点でテストMCA信号が注入される。ハードウェア(ORゲート、データバス、および状態マシン)を使用して、チップ設計者は、再現性のある事象を決定論的に発生させることができ、シリコンデバッグ環境におけるプロセッサコアの確認を行うことができる。プロセッサコア210および220、ならびに関連する上記ハードウェアは、単一のシリコンチップ(図示せず)上に実装することができ、エラーを注入しロックステップ機能性をテストする装置が、この関連するハードウェアを備える。30

#### 【0012】

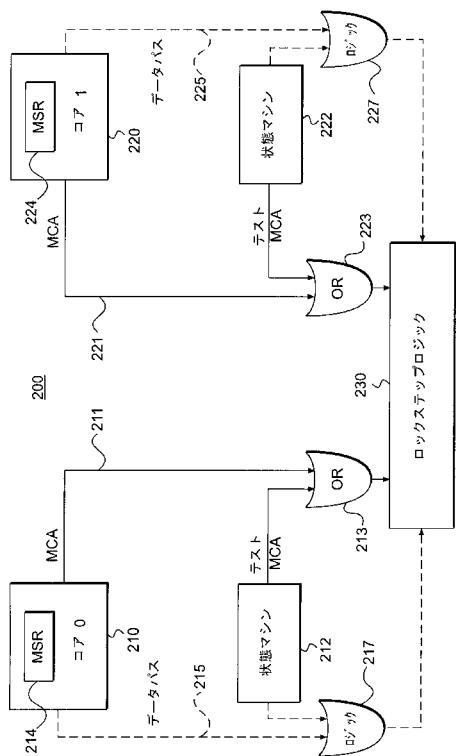

図2A～図2Cは、図1の環境200において使用可能な様々な状態マシンを示す。図2Aは、テストMCA信号またはエラーテスト信号の一度だけのアサートを供給するカウントダウンタイマ250を示す。カウントダウンタイマ250は、減分器251、値レジスタ253、および比較器255を備える。比較器255は、クロックサイクルごとに、またはある他の規定された周期で値レジスタ253から値を読み出す。減分器251は、クロックサイクルごとに1だけ(またはある他の量)値レジスタ253の値を減分する。比較器255は、特定のクロックサイクルで読み出された値を設定値、たとえば0等と比較する。読み出された値が設定値に達すると、カウントタ250が、テストMCA信号をアサートするように、関連するロジックハードウェアに信号を送る。40

#### 【0013】

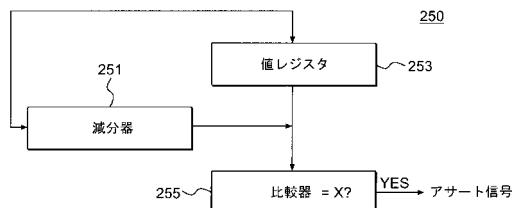

図2Bは、これもまたテストMCA信号の一度だけのアサートを供給するタイマ260を示す。タイマ260は、クロックサイクルごとに、またはある他の周期で1だけ、またはある他の値だけカウントアップするタイマ値レジスタ261と、プログラム可能値レジスタ263と、を備え、タイマ値レジスタ261および値レジスタ263は双方とも比較器50

265に接続される。比較器265は、レジスタ261および263の値を常に読み出し、2つの値が等しくなったときにMCA信号を供給する。

【0014】

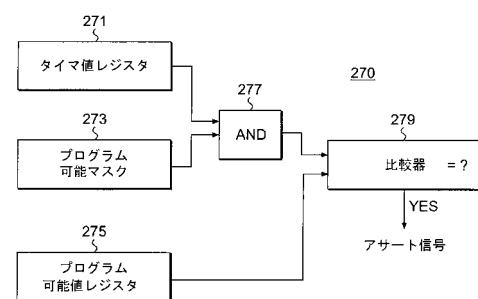

図2Cは、テストMCA信号のアサートを供給する代替のタイマ270を示す。タイマ270は、タイマ値レジスタ271、プログラム可能マスクレジスタ273、およびプログラム可能値レジスタ275を備える。レジスタ271および273は、ANDゲート277に接続される。ANDゲート277の出力は、比較器279に接続される。比較器279は、ANDゲートの出力がプログラム可能値レジスタ275の値と整合したときに、テストMCA信号を送る。

【0015】

図2A～図2Cに示す様々な状態マシンは、テストMCA信号のアサートを制御するために使用することのできるデバイスの例にすぎない。

【0016】

プロセッサコア210および220に関連する状態マシンは、1つの状態マシンのみがロックステップロジックブロック230への信号をアサートするように制御することができる。チップ設計者がロックステップの損失（または他のエラー）をテストしたい場合、たとえば、プロセッサコア210および関連するテストハードウェアは、アサートされたMCA信号のソースとなるように制御することができる。この場合、チップ設計者は、ロックステップの損失をテストし、プロセッサコア210の検出されたエラーに基づいて、続けて回復を開始するよう要求することができる。したがって、プロセッサコア210に関連する状態マシンのみが、テストMCA信号をアサートするように制御される。テストMCA信号がアサートされると、ロックステップロジックブロック230がオフになり、プロセッサコア220が非保護モードで実行される。次いで、ロックステップ損失からの回復をプロセッサコア220から開始することができる。チップ設計者は、テストMCA信号を双方のプロセッサコア210および220からアサートするよう要求することもできる。

【0017】

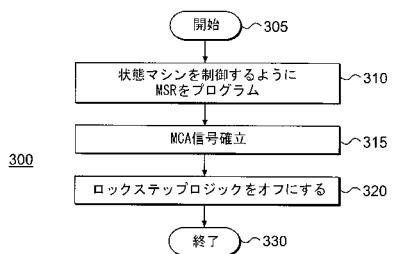

図3は、図1の装置のテスト動作300を示すフローチャートである。動作300はブロック305において始まる。ブロック310において、チップ設計者がコアシーケンスをロードして、コアプロセッサ210および220に関連するMSRのうちの一方または双方をプログラムする。たとえば、テストMCA信号を開始するように状態マシン212を制御することができる。ブロック315において、プログラムされたMSRが状態マシン212を制御してテストMCA信号をアサートさせる。ブロック320において、テストロジックが、アサートされたテストMCA信号を状態マシン212から受け取ってオフになり、プロセッサ210および220のロックステップ動作が終了する。その後、プロセッサ210および220は、ロックステップ動作が回復するまで独立モードで動作する。次いで、動作300はブロック330において終了する。

【0018】

本明細書に使用する用語および説明は例示としてのみ記載され、制限を意味するものではない。当業者は、特記されない限りすべての用語をそれぞれの可能な限り最も広い意味で理解すべきである併記の特許請求の範囲およびその等価物において規定される本発明の精神および範囲内で多くの変形が可能なことを認めよう。

【図面の簡単な説明】

【図1】ロックステップマイクロプロセッサを含むマイクロプロセッサの適正動作を確認するために、事象を決定論的に発生させることができる装置を示すシリコンデバッグ環境の論理図。

【図2A】マシンチェックおよび他のエラーをアサートするために、図1の環境において使用可能なユーザプログラム可能デバイスを示す図。

【図2B】マシンチェックおよび他のエラーをアサートするために、図1の環境において使用可能なユーザプログラム可能デバイスを示す図。

10

20

30

40

50

【図2C】マシンチェックおよび他のエラーをアサートするために、図1の環境において使用可能なユーザプログラム可能デバイスを示す図。

【図3】図1の装置の動作のフローチャート。

【図1】

【図2A】

【図2B】

【図2C】

【図3】

## フロントページの続き

(72)発明者 ケヴィン・デイヴィッド・サフォード

アメリカ合衆国80528コロラド州フォート・コリンズ、ツイン・ヘロン・コート 3183

(72)発明者 ジェレミー・ピー・ペットシンガー

アメリカ合衆国80525コロラド州フォート・コリンズ、サンリーフ・コート 2212

(72)発明者 カール・ピー・ブルメル

アメリカ合衆国60614イリノイ州シカゴ、ウェスト・ウェブスター 339、ナンバー 8

F ターム(参考) 5B034 AA02 DD03

5B048 AA14 DD05