(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-104102

(P2004-104102A)

(43) 公開日 平成16年4月2日(2004.4.2)

(51) Int.Cl.<sup>7</sup>

H01L 23/12

F 1

H01L 23/12 501P

H01L 23/12 501C

テーマコード(参考)

審査請求 未請求 請求項の数 18 O L (全 11 頁)

(21) 出願番号 特願2003-284994 (P2003-284994)

(22) 出願日 平成15年8月1日 (2003.8.1)

(31) 優先権主張番号 特願2002-240778 (P2002-240778)

(32) 優先日 平成14年8月21日 (2002.8.21)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100090387

弁理士 布施 行夫

(74) 代理人 100090398

弁理士 大渕 美千栄

(72) 発明者 山口 浩司

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

(54) 【発明の名称】半導体装置及びその製造方法、回路基板並びに電子機器

## (57) 【要約】

【課題】 本発明の目的は、外部端子の接続不良を減らすことにある。

【解決手段】 半導体装置は、集積回路12が形成されて内部に電気的に接続された配線14と配線14に形成された電極16とを有する半導体基板10と、半導体基板10上に形成された樹脂層20と、電極16に電気的に接続されてなる再配置配線22と、再配置配線22上に形成されて樹脂層20にて支持されてなる複数の外部端子24と、電極16に電気的に接続されずに樹脂層20にて支持されてなる複数のダミー端子26と、を含む。

。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

集積回路が形成され、内部に電気的に接続された配線と前記配線に形成された電極とを有する半導体基板と、

前記半導体基板上に形成された樹脂層と、

前記電極に電気的に接続されてなる再配置配線と、

前記再配置配線上に形成され、前記樹脂層にて支持されてなる複数の外部端子と、

前記電極に電気的に接続されずに前記樹脂層にて支持されてなる複数のダミー端子と、

を含む半導体装置。

**【請求項 2】**

10

請求項 1 記載の半導体装置において、

前記樹脂層の上面は、端部に位置する第 1 の領域と、前記第 1 の領域よりも中央に近い第 2 の領域と、を有し、

前記ダミー端子は、前記第 1 の領域に設けられ、

前記外部端子は、前記第 2 の領域に設けられてなる半導体装置。

**【請求項 3】**

20

請求項 2 記載の半導体装置において、

前記樹脂層の前記上面は、矩形をなし、

前記ダミー端子は、前記矩形の少なくとも対角線上の一対の角部に設けられてなる半導体装置。

**【請求項 4】**

請求項 2 記載の半導体装置において、

前記樹脂層の前記上面は、長形状をなし、

前記ダミー端子は、前記長形状の長手方向の両端部に設けられてなる半導体装置。

**【請求項 5】**

請求項 1 から請求項 4 のいずれかに記載の半導体装置において、

2 つ以上の前記ダミー端子が隣接するように配置されてなる半導体装置。

**【請求項 6】**

30

請求項 1 から請求項 5 のいずれかに記載の半導体装置において、

それぞれの前記ダミー端子は、それぞれの前記外部端子とは異なる材料で形成されてなる半導体装置。

**【請求項 7】**

請求項 1 から請求項 6 のいずれかに記載の半導体装置において、

それぞれの前記ダミー端子は、樹脂からなる中央部と、ハンダからなる表面層と、を有するように形成されてなる半導体装置。

**【請求項 8】**

請求項 1 から請求項 7 のいずれかに記載の半導体装置において、

それぞれの前記ダミー端子は、いずれの前記外部端子よりも大きい半導体装置。

**【請求項 9】**

40

請求項 1 から請求項 8 のいずれかに記載の半導体装置において、

前記外部端子及び前記ダミー端子の下方に形成されてなる導電膜をさらに有する半導体装置。

**【請求項 10】**

50

請求項 9 記載の半導体装置において、

前記導電膜は、前記半導体基板上であって前記樹脂層の下に形成されてなる半導体装置

**【請求項 11】**

請求項 9 又は請求項 10 記載の半導体装置において、

前記導電膜は、前記集積回路が形成された領域を覆うように形成されてなる半導体装置

。

## 【請求項 1 2】

請求項 9 又は請求項 1 0 記載の半導体装置において、

前記導電膜は、相互に間隔があくように複数の部分に分割されてなる半導体装置。

## 【請求項 1 3】

請求項 1 2 記載の半導体装置において、

前記導電膜を構成する前記複数の部分が形成された領域内に、前記集積回路が形成されてなる半導体装置。

## 【請求項 1 4】

請求項 9 から請求項 1 3 のいずれかに記載の半導体装置において、

前記導電膜は、前記電極に電気的に接続されないように、前記ダミー端子に電気的に接続されてなる半導体装置。 10

## 【請求項 1 5】

半導体チップが表面実装されたインターポーヴ基板と、

前記インターポーヴ基板の裏面に設けられた配線層と、

前記インターポーヴ基板の裏面に設けられ、前記インターポーヴ基板の最外周端部に配置されたダミーバンプと、

前記インターポーヴ基板の前記ダミーバンプよりも内側に配置され、前記配線層に接続された外部端子と、

前記インターポーヴ基板に設けられた、前記半導体チップと前記配線層とを接続するスルーホールと、

を含む半導体装置。 20

## 【請求項 1 6】

請求項 1 から請求項 1 5 のいずれかに記載の半導体装置が実装されてなる回路基板。

## 【請求項 1 7】

請求項 1 から請求項 1 5 のいずれかに記載の半導体装置を有する電子機器。

## 【請求項 1 8】

集積回路が形成されて内部に電気的に接続された配線と前記配線に形成された電極とを有する半導体基板上に樹脂層を形成すること、

前記電極に電気的に接続されるように、再配置配線を形成すること、

前記再配置配線上に、前記樹脂層にて支持されるように複数の外部端子を形成すること、及び、 30

前記電極に電気的に接続されずに前記樹脂層にて支持されるように複数のダミー端子を形成すること、

を含む半導体装置の製造方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0 0 0 1】

本発明は、半導体装置及びその製造方法、回路基板並びに電子機器に関する。

## 【背景技術】

## 【0 0 0 2】

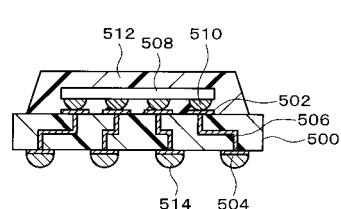

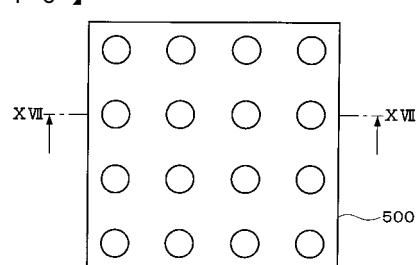

図 1 6 は、従来のボールグリッドアレイパッケージの概略構成を示す平面図、図 1 7 は、図 1 6 に示すボールグリッドアレイパッケージの XVII - XVII 線断面図である。 40

## 【0 0 0 3】

従来のボールグリッドアレイでは、フルグリッド配列または千鳥配列などで、外部端子となるハンダボールの配置が行なわれていた。インターポーヴ 5 0 0 の両面には配線 5 0 2, 5 0 4 がそれぞれ形成され、配線 5 0 2, 5 0 4 は、インターポーヴ 5 0 0 に形成されたスルーホール 5 0 6 を介して接続されている。そして、インターポーヴ 5 0 0 の表面には I C チップ 5 0 8 が実装され、I C チップ 5 0 8 は、バンプ 5 1 0 を介して配線 5 0 2 と接続されるとともに、モールド樹脂 5 1 2 により封止されている。また、インターポーヴ 5 0 0 の裏面には、ハンダボール 5 1 4 がフルグリッド状に配置され、ハンダボール 50

514は配線504に接続されている。

【0004】

従来のボールグリッドアレイでは、インターポーナ500をマザーボード上に実装すると、インターポーナ500の収縮によってハンダボール514に力が加えられる。特に、インターポーナ500の端部に近いハンダボール514に大きな力が加えられていた。インターポーナ500のサイズが大きい場合には、ハンダボール514の接続不良を防止することが難しかった。

【0005】

本発明の目的は、外部端子の接続不良を減らすことがある。

【発明の開示】

【課題を解決するための手段】

【0006】

(1) 本発明に係る半導体装置は、集積回路が形成され、内部に電気的に接続された配線と前記配線に形成された電極とを有する半導体基板と、

前記半導体基板上に形成された樹脂層と、

前記電極に電気的に接続されてなる再配置配線と、

前記再配置配線上に形成され、前記樹脂層にて支持されてなる複数の外部端子と、

前記電極に電気的に接続されずに前記樹脂層にて支持されてなる複数のダミー端子と、

を含む。本発明によれば、半導体装置をマザーボード等に接合したときに、ダミー端子によって接合強度が高められるので、外部端子の電気的な接続不良を減らすことができる。

(2) この半導体装置において、

前記樹脂層の上面は、端部に位置する第1の領域と、前記第1の領域よりも中央に近い第2の領域と、を有し、

前記ダミー端子は、前記第1の領域に設けられ、

前記外部端子は、前記第2の領域に設けられてもよい。

(3) この半導体装置において、

前記樹脂層の前記上面は、矩形をなし、

前記ダミー端子は、前記矩形の少なくとも対角線上の一対の角部に設けられてもよい。

(4) この半導体装置において、

前記樹脂層の前記上面は、長形状をなし、

前記ダミー端子は、前記長形状の長手方向の両端部に設けられてもよい。

(5) この半導体装置において、

2つ以上の前記ダミー端子が隣接するように配置されていてもよい。

(6) この半導体装置において、

それぞれの前記ダミー端子は、それぞれの前記外部端子とは異なる材料で形成されていてもよい。

(7) この半導体装置において、

それぞれの前記ダミー端子は、樹脂からなる中央部と、ハンダからなる表面層と、を有するように形成されていてもよい。

(8) この半導体装置において、

それぞれの前記ダミー端子は、いずれの前記外部端子よりも大きい%。

(9) この半導体装置は、

前記外部端子及び前記ダミー端子の下方に形成されてなる導電膜をさらに有してもよい。

(10) この半導体装置において、

前記導電膜は、前記半導体基板上であって前記樹脂層の下に形成されていてもよい。

(11) この半導体装置において、

前記導電膜は、前記集積回路が形成された領域を覆うように形成されていてもよい。

10

20

30

40

50

(12) この半導体装置において、

前記導電膜は、相互に間隔があくように複数の部分に分割されていてもよい。

(13) この半導体装置において、

前記導電膜を構成する前記複数の部分が形成された領域内に、前記集積回路が形成されていてもよい。

(14) この半導体装置において、

前記導電膜は、前記電極に電気的に接続されないように、前記ダミー端子に電気的に接続されていてもよい。

(15) 本発明に係る半導体装置は、半導体チップが表面実装されたインターポーヴ基板と、

前記インターポーヴ基板の裏面に設けられた配線層と、

前記インターポーヴ基板の裏面に設けられ、前記インターポーヴ基板の最外周端部に配置されたダミーバンプと、

前記インターポーヴ基板の前記ダミーバンプよりも内側に配置され、前記配線層に接続された外部端子と、

前記インターポーヴ基板に設けられた、前記半導体チップと前記配線層とを接続するスルーホールと、

を含む。本発明によれば、接続不良の頻度が大きい領域にハンダボールを配置する必要がなく、半導体装置をマザーボード上に実装したときに、ハンダボールの接続状態をダミーバンプで補強することが可能となる。このため、インターポーヴ基板が大型化しても、工程数を増加させることなくハンダボールの接続不良を低減することが可能となり、スルーブラッドの低下を抑制しつつ、二次実装時の信頼性を向上させることができる。

(16) 本発明に係る回路基板は、上記半導体装置が実装されてなる。

(17) 本発明に係る電子機器は、上記半導体装置を有する。

(18) 本発明に係る半導体装置の製造方法は、集積回路が形成されて内部に電気的に接続された配線と前記配線に形成された電極とを有する半導体基板上に樹脂層を形成すること、

前記電極に電気的に接続されるように、再配置配線を形成すること、

前記再配置配線上に、前記樹脂層にて支持されるように複数の外部端子を形成すること、及び、

前記電極に電気的に接続されずに前記樹脂層にて支持されるように複数のダミー端子を形成すること、

を含む。本発明によれば、半導体装置をマザーボード等に接合したときに、ダミー端子によって接合強度が高められるので、外部端子の電気的な接続不良を減らすことができる。

【発明を実施するための最良の形態】

【0007】

以下、本発明の実施の形態を、図面を参照して説明する。

【0008】

(第1の実施の形態)

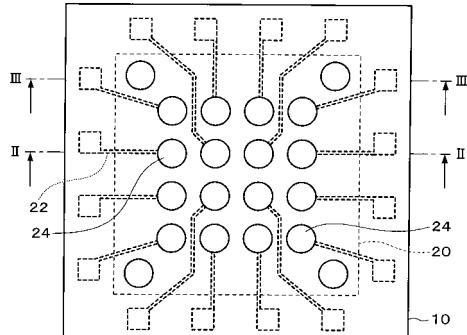

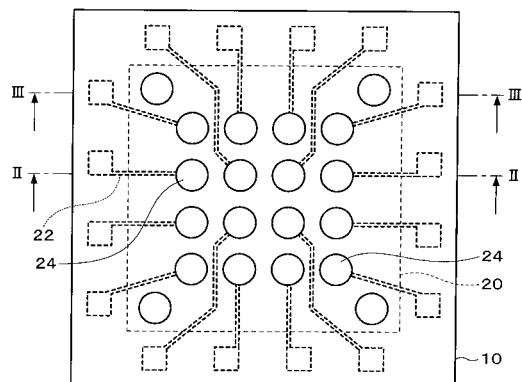

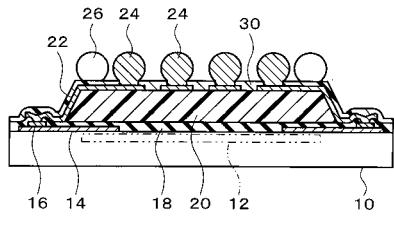

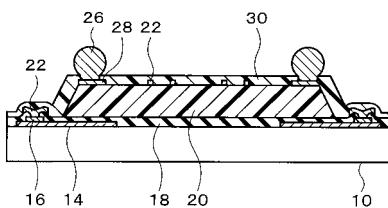

図1は、本発明の第1の実施の形態に係る半導体装置を説明する図である。図2は、図1に示す半導体装置のII-II線断面図であり、図3は、図1に示す半導体装置のIII-III線断面図である。半導体装置は、半導体基板10を有する。図1に示す半導体基板10は半導体チップであるが、半導体ウエハを使用してもよい。半導体基板10には、集積回路12が形成されている。半導体チップには、1つの集積回路12が形成され、半導体ウエハには、複数の集積回路12が形成される。集積回路12が形成された領域を能動領域といふことができる。

【0009】

半導体基板10は、内部に電気的に接続された複数の配線(又は配線層)14を有する。複数の配線14は、集積回路12(又は能動領域)に電気的に接続された配線を含む。

複数の配線 14 は、電気的に、集積回路 12 に接続されずに半導体基板 10 の内部に接続された配線を含んでもよい。配線 14 には、電極（パッド）16 が形成されている。

【0010】

半導体基板 10 は、パッシベーション膜 18 を有していてもよい。パッシベーション膜 18 は、樹脂膜、シリコン酸化膜、シリコン窒化膜のいずれであってもよい。パッシベーション膜 18 は、シリコン酸化膜のように透明であってもよいし、不透明であってもよい。パッシベーション膜 18 は、各電極 16 の一部（例えば中央部のみ）を除いて形成されてもよい。パッシベーション膜 18 は、配線 14 を覆っており、集積回路 12（又は能動領域）の全体を覆っていてもよい。

【0011】

半導体基板 10 には、樹脂層 20 が形成されている。樹脂層 20 は、半導体基板 10 の一部（例えばパッシベーション膜 18 の一部）が露出するように形成されている。樹脂層 20 は、電気的絶縁層である。樹脂層 20 は、導電性粒子を含まない。樹脂層 20 は、応力緩和機能を有してもよい。樹脂層 20 は、ポリイミド樹脂、シリコーン変性ポリイミド樹脂、エポキシ樹脂、シリコーン変性エポキシ樹脂、ベンゾシクロブテン（B C B；benzocyclobutene）、ポリベンゾオキサゾール（P B O；polybenzoxazole）等で形成されてもよい。樹脂層 20 は、遮光性を有する材料から形成されてもよい。樹脂層 20 は、電極 16 の上方を避けて形成されている。樹脂層 20 の少なくとも一部は、集積回路 12（又は能動領域）の上方に形成されてもよい。

【0012】

半導体装置は、電極 16 に電気的に接続された再配置配線 22 を有する。再配置配線 22 は、その一部が電極 16 とオーバーラップするように形成されている。再配置配線 22 は、樹脂層 20 上に（例えばその上面に）至るように形成されている。再配置配線 22 は、パッシベーション膜 18 上を通ってもよい。再配置配線 22 は、例えば、Ti W スパッタ配線層、Cu スパッタ配線層およびCu メッキ配線層の3層構造から構成することができる。

【0013】

再配置配線 22 上には、複数の外部端子（例えばハンダボール）24 が設けられている。外部端子 24 は、軟ろう（soft solder）又は硬ろう（hard solder）のいずれで形成してもよい。軟ろうとして、鉛を含まないハンダ（以下、鉛フリーハンダという。）を使用してもよい。鉛フリーハンダとして、スズ-銀（Sn-Ag）系、スズ-ビスマス（Sn-Bi）系、スズ-亜鉛（Sn-Zn）系、あるいはスズ-銅（Sn-Cu）系の合金を使用してもよいし、これらの合金に、さらに銀、ビスマス、亜鉛、銅のうち少なくとも1つを添加してもよい。外部端子 24 は、樹脂層 20 の上方に形成されており、樹脂層 20 にて支持されている。したがって、外部端子 24 に加えられた外力の一部が、樹脂層 20 にて吸収される。

【0014】

半導体装置は、複数のダミー端子 26 を有する。ダミー端子 26 は、電極 16 に電気的に接続されないようになっている。ダミー端子 26 は、外部端子 24 に電気的に接続されないようになっている。ダミー端子 26 は、樹脂層 20 にて支持されてなる。例えば、樹脂層 20 上に形成されたパッド 28 上にダミー端子 26 を設けてもよい。

【0015】

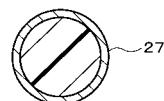

ダミー端子 26 は、外部端子 24 と同じ材料（例えばハンダ）で形成してもよいし、異なる材料（例えば樹脂）で形成して、ダミー端子 26 と外部端子 24 の性質（弾力性・接着力等）を異ならせててもよい。例えば、ダミー端子 26 を接着剤により構成すれば、ダミー端子 26 を押し潰しながらマザーボードに接着することができる。これにより、ダミー端子 26 の大きさのバラツキを吸収することが可能となる。あるいは、変形例として、図4に示すダミー端子 27 は、樹脂からなる中央部と、ハンダからなる表面層と、を有する。これによれば、ダミー端子 26 が弾性変形し易くなり、外力が加わった場合においても、ダミー端子 26 をマザーボードの配線パターンから外れにくくすることが可能となる。

10

20

30

40

50

また、表面層をハンダで形成することにより、ダミー端子 26 の接続を外部端子 24 の接続とともに一括して行うことができる。

【0016】

樹脂層 20 の上面が矩形をなしている場合、ダミー端子 26 は、矩形の少なくとも対角線上の一対の角部に設けてもよい。樹脂層 20 の上面は、端部に位置する第 1 の領域と、第 1 の領域よりも中央に近い第 2 の領域と、に分けることができる。その場合、ダミー端子 26 を第 1 の領域に設け、外部端子 24 を第 2 の領域に設けてもよい。本実施の形態によれば、半導体装置をマザーボード等に接合したときに、ダミー端子 26 によって接合強度が高められるので、外部端子 24 の電気的な接続不良を減らすことができる。

【0017】

半導体装置は、第 2 の樹脂層（ソルダレジスト等の保護層）30 を有していてもよい。第 2 の樹脂層 30 は、樹脂層 20 上に形成されている。第 2 の樹脂層 30 は、再配置配線 22 の外部端子 24 を設ける部分（例えばランド）を避けて、再配置配線 22 を覆うように形成されている。第 2 の樹脂層 30 には、樹脂層 20 上において再配置配線 22 を露出させる開口が形成されている。外部端子 24 は、第 2 の樹脂層 30 に形成された開口を介して再配置配線 22 と接続されている。第 2 の樹脂層 30 は、外部端子 24 の少なくとも根本部分に接触している。第 2 の樹脂層 30 は、電極 16 を覆っていてもよい。

【0018】

本実施の形態に係る半導体装置の製造方法では、半導体基板 10 として、半導体ウエハを使用する。半導体基板 10 上に（例えばパッシベーション膜 18 上に）、樹脂層 20 を形成する。樹脂層 20 の形成プロセスは、半導体基板 10 に樹脂前駆体（例えば熱硬化性樹脂前駆体）を塗布すること、あるいは、半導体基板 10 上で樹脂前駆体をスピンドルコートによって拡げて、樹脂前駆体層を形成することを含んでもよい。放射線（光線（紫外線、可視光線）、X 線、電子線）に感応する性質を有する放射線感応性樹脂前駆体を使用して、連続的又は一体的な樹脂前駆体層を形成し、これをパターニングしてもよい。パターニングにはリソグラフィを適用する。あるいは、印刷（例えばスクリーン印刷）によって、樹脂層 20 を形成してもよい。樹脂層 20 は、複数層になるように形成してもよいし、1 層になるように形成しもよい。樹脂層 20 は、電極 16 上を避けるように形成する。樹脂層 20 は、半導体基板 10 の切断領域を避けるように形成してもよい。

【0019】

電極 16 に電気的に接続されるように、再配置配線 22 を形成する。樹脂層 20 上に至るよう再配置配線 22 を形成する。再配置配線 22 は、電極 16 上を通るように形成する。再配置配線 22 は、樹脂層 20 の側面を通ってもよい。再配置配線 22 は、ランド（ラインよりも幅の広い部分）を有するように形成してもよい。ランドは、その上に外部端子 24 を設けるためのものである。再配置配線 22 は、1 層で形成してもよいし、複数層で形成してもよい。例えば、スパッタリングにより、TiW スパッタ膜およびCuスパッタ膜を順次積層した後、メッキレジスト膜を形成する。そして、フォトリソグラフィー技術を用いることにより、再配置配線 22 に対応する開口をメッキレジスト膜に形成し、この開口を介して電解銅メッキを行うことにより、Cu メッキ配線層を形成する。そして、メッキレジスト膜を除去し、Cu メッキ配線層をマスクとして、Cuスパッタ膜およびTiWスパッタ膜を順次エッチングすることにより、Cuスパッタ配線層およびTiWスパッタ配線層を形成し、再配置配線 22 を形成することができる。

【0020】

樹脂層 20 上に第 2 の樹脂層 30 を形成してもよい。第 2 の樹脂層 30 には、樹脂層 20 の内容が該当してもよい。あるいは、第 2 の樹脂層 30 はソルダレジストであってもよい。第 2 の樹脂層 30 は、再配置配線 22 の一部（例えばランドの中央部）を除いた残りの部分を覆うように形成する。第 2 の樹脂層 30 は、半導体基板 10 の切断領域が露出するように形成してもよい。

【0021】

再配置配線 22 上に、樹脂層 20 にて支持されるように外部端子 24 を形成する。外部

10

20

30

40

50

端子 24 の形成には、周知の方法を適用することができる。また、樹脂層 20 にて支持されないようにダミー端子 26 を形成する。樹脂層 20 上にパッド 28 を形成し、その上にダミー端子 26 を形成してもよい。

【0022】

必要に応じて、第 2 の樹脂層 30 上に、図示しない第 3 の樹脂層を形成してもよい。第 3 の樹脂層には、樹脂層 20 の内容が該当してもよい。第 3 の樹脂層は、外部端子 24 の上端部を除く部分を覆うように設ける。こうすることで、外部端子 24 に加えられる外力によって生じる応力を分散することができる。あるいは、外部端子 24 と再配置配線 22 との接合を補強することができる。第 3 の樹脂層は、半導体基板 10 の全体を覆うように形成した後にパターニングしてもよい。第 3 の樹脂層を、外部端子 24 が覆われるように設けた後、外部端子 24 の上端部から第 3 の樹脂層を除去してもよい。パターニングには、リソグラフィを適用することができる。あるいは、レーザの使用又はアッシングによって、第 3 の樹脂層の一部を除去してもよい。

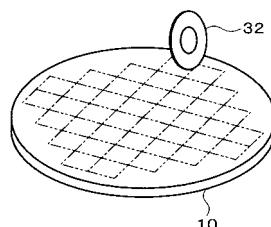

【0023】

図 5 に示すように、半導体基板 10 を切断（例えば、スクライビング又はダイシング）してもよい。半導体基板 10 の切断領域に樹脂層 20 及び第 2 の樹脂層 30 を設けないようにはすれば、樹脂を切断しないのでカッタ（又はブレード）32 の目詰まりを防止することができる。こうして、半導体装置を得ることができる。

【0024】

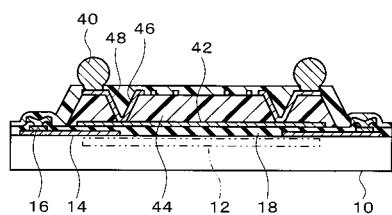

（第 2 の実施の形態）

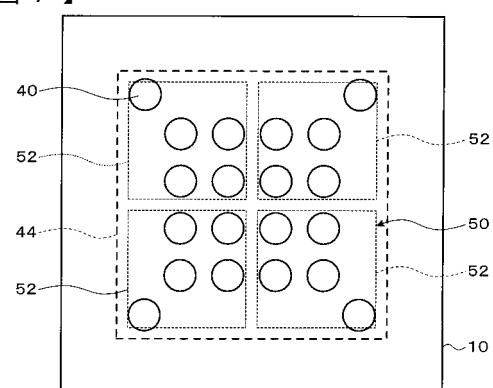

図 6 は、本発明の第 2 の実施の形態に係る半導体装置を説明する図である。本実施の形態では、外部端子（図示せず）及びダミー端子 40 の下方に導電膜 42 が形成されている。図 6 に示す導電膜 42 は、半導体基板 10 上（例えばパッシベーション膜 18 上）であって樹脂層 44 の下に形成されているが、樹脂層 44 の内部に導電膜 42 を設けてもよい。導電膜 42 は、集積回路 12（例えば能動素子が形成された領域）を覆うように形成してもよい。こうすることで、集積回路 12 に対して電磁波のシールド効果を得ることができる。

【0025】

変形例として、図 7 に示すように、導電膜 50 を、相互に間隔があくように複数の部分 52 に分割してもよい。導電膜 50 を分割することで、導電膜 50 の内部応力が半導体基板 10 に与える影響を小さくすることができる。また、複数の部分 52 が形成された領域（複数の部分 52 及び隣同士の部分 52 間の隙間の合計領域）内に集積回路 12（例えば能動素子が形成された領域）が位置するように、導電膜 50 を形成する。こうすることで、集積回路 12 に対して電磁波のシールド効果を得ることができる。

【0026】

図 6 及び図 7 のいずれの例でも、導電膜 42（又は 50）は、電極 16 に電気的に接続されないように、ダミー端子 40 に電気的に接続されている。詳しくは、樹脂層 44 に導電膜 42（又は 50）の一部とオーバーラップするように貫通穴 46 が形成されている。導電膜 42（又は 50）上から、貫通穴 46 の内面を通って、樹脂層 44 の上面に至るよう、再配置配線 48 が形成されている。樹脂層 44 に支持されるように、再配置配線 48 上にダミー端子 40 が形成されている。ダミー端子 40 を構成する材料は、外部端子 24（図 2 参照）に使用できる材料から選択することができる。ダミー端子 40 を介して、導電膜 42（又は 50）を GND に電気的に接続すれば、電磁波のシールド効果が高められる。

【0027】

その他の構成及び製造方法は、第 1 の実施の形態で説明した内容が該当する。また、本実施の形態でも、第 1 の実施の形態で説明した効果を達成することができる。

【0028】

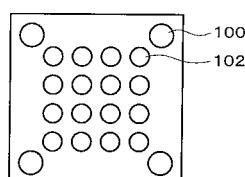

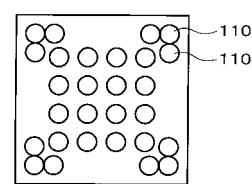

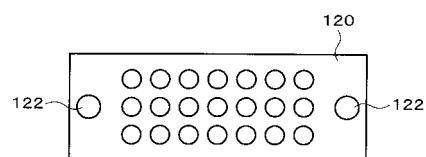

図 8～図 10 は、ダミー端子の変形例を説明する図であり、第 1 及び第 2 の実施の形態に適用することができる。図 8 に示すように、ダミー端子 100 を、全ての外部端子 22

10

20

30

40

50

よりも大きくなるように構成してもよい。これにより、ダミー端子 100 の接着力を増大させることができるとなる。図 9 に示すように、2 つ以上のダミー端子 110 を、隣接するように配置してもよい。2 つ以上のダミー端子 110 を溶融して一体化してもよい。これにより、ダミー端子 110 の大きさを変更することなく、その接着力を増大させることができるとなる。図 10 に示すように、樹脂層 120 が長形状（例えば長方形又は橢円形状）をなす場合、ダミー端子 122 を、長形状の長手方向の両端部に設けてもよい。

#### 【0029】

##### （第 3 の実施の形態）

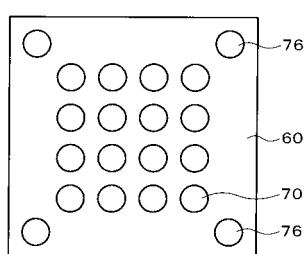

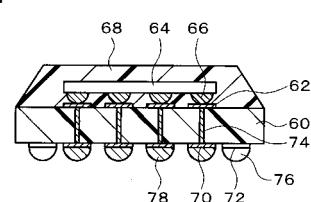

図 11 は、本発明の第 3 の実施の形態に係る半導体装置を説明する断面図であり、図 12 は、その底面図である。インターポーザ基板 60 には、その表面に配線層 62 が形成されている。インターポーザ基板 60 には、その表面に、半導体チップ（例えば IC チップ）64 が実装（例えば表面実装）されている。半導体チップ 64 は、バンプ 66 を介して配線層 62 と接続されるとともに、モールド樹脂 68 により封止されている。

#### 【0030】

インターポーザ基板 60 の裏面には配線層 70 およびランド 72 が形成されている。配線層 62, 70 は、インターポーザ基板 60 に形成されたスルーホール 74 を介して接続されている。ランド 72 は、インターポーザ基板 60 の最外周端部に配置されている。ランド 72 上には、ダミーバンプ（又はダミーボール）76 が形成されている。ダミーバンプ 76 は、インターポーザ基板 60 の最外周端部に配置されている。インターポーザ基板 60 のダミーバンプ 76 よりも内側には、外部端子（例えばハンダボール）78 が配置され、外部端子 78 は、配線層 70 に接続されている。

#### 【0031】

本実施の形態によれば、インターポーザ基板 60 の最外周端部（接続不良の頻度が大きい領域）に外部端子 78 が配置されることを防止することができる。また、インターポーザ基板 60 をマザーボード上に実装した後に、外部端子 78 の接続状態をダミーバンプ 76 で補強することができる。このため、半導体装置が大型化した場合においても、実装時の工程数を増加させることなく、例えば表面実装時に、外部端子 78 の接続不良を低減することができる。スループットの低下を抑制しつつ、ボールグリッドアレイが適用された半導体装置の二次実装時の信頼性を向上させることができる。

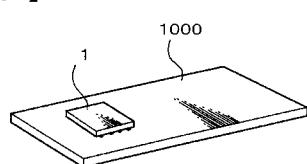

#### 【0032】

図 13 には、上述した実施の形態で説明した半導体装置 1 が実装された回路基板 100 が示されている。この半導体装置を有する電子機器として、図 14 にはノート型パソコンコンピュータ 2000 が示され、図 15 には携帯電話 3000 が示されている。

#### 【0033】

本発明は、上述した実施の形態に限定されるものではなく、種々の変形が可能である。例えば、本発明は、実施の形態で説明した構成と実質的に同一の構成（例えば、機能、方法及び結果が同一の構成、あるいは目的及び結果が同一の構成）を含む。また、本発明は、実施の形態で説明した構成の本質的でない部分を置き換えた構成を含む。また、本発明は、実施の形態で説明した構成と同一の作用効果を奏する構成又は同一の目的を達成することができる構成を含む。また、本発明は、実施の形態で説明した構成に公知技術を付加した構成を含む。

#### 【図面の簡単な説明】

#### 【0034】

【図 1】図 1 は、本発明の第 1 の実施の形態に係る半導体装置を説明する図である。

【図 2】図 2 は、図 1 に示す半導体装置の II-II 線断面図である。

【図 3】図 3 は、図 1 に示す半導体装置の III-III 線断面図である。

【図 4】図 4 は、ダミー端子の変形例を説明する図である。

【図 5】図 5 は、本発明の第 1 の実施の形態に係る半導体装置の製造方法を説明する図である。

【図 6】図 6 は、本発明の第 2 の実施の形態に係る半導体装置を説明する図である。

10

20

30

40

50

【図7】図7は、本発明の第2の実施の形態に係る半導体装置の変形例を説明する図である。

【図8】図8は、ダミー端子の変形例を説明する図である。

【図9】図9は、ダミー端子の変形例を説明する図である。

【図10】図10は、ダミー端子の変形例を説明する図である。

【図11】図11は、本発明の第3の実施の形態に係る半導体装置の断面図である。

【図12】図12は、本発明の第3の実施の形態に係る半導体装置の底面図である。

【図13】図13は、本実施の形態に係る半導体装置が実装された回路基板を示す図である。

【図14】図14は、本実施の形態に係る半導体装置を有する電子機器を示す図である。 10

【図15】図15は、本実施の形態に係る半導体装置を有する電子機器を示す図である。

【図16】図16は、従来のボールグリッドアレイパッケージの概略構成を示す平面図である。

【図17】図17は、図16に示すボールグリッドアレイパッケージのXVII-XVII線断面図である。

【符号の説明】

【0035】

10 ... 半導体基板 12 ... 集積回路 14 ... 配線 16 ... 電極 18 ... パッシベーション

ン膜 20 ... 樹脂層 22 ... 再配置配線 22 ... 外部端子 24 ... 外部端子 26 ... ダミー端子

-端子 27 ... ダミー端子 28 ... パッド 30 ... 第2の樹脂層 40 ... ダミー端子 42 ... 導電膜

2 ... 導電膜 44 ... 樹脂層 46 ... 貫通穴 48 ... 再配置配線 50 ... 導電膜 52 ... 部

分 60 ... インターポーヴ基板 62 ... 配線層 64 ... 半導体チップ 66 ... バンプ 68 ... モールド樹脂

70 ... 配線層 72 ... ランド 74 ... スルーホール 76 ... ダミーバンプ 78 ... 外部端子

【図1】

【図2】

【図3】

【図4】

【図5】

【図 6】

【図 7】

【図 8】

【図 12】

【図 13】

【図 14】

【図 9】

【図 10】

【図 11】

【図 15】

【図 16】

【図 17】