# (19) 대한민국특허청(KR)

# (12) 공개특허공보(A)

(51) 국제특허분류(Int. Cl.)

*G06F* 12/08 (2006.01) *G06F* 12/00 (2006.01) *G06F* 13/16 (2006.01)

(21) 출원번호 10-2011-0120920

(22) 출원일자 **2011년11월18일** 심사청구일자 **2011년11월18일**

(30) 우선권주장

12/950,293 2010년11월19일 미국(US)

(11) 공개번호 10-2012-0054549

(43) 공개일자 2012년05월30일

(71) 출원인

애플 인크.

미합중국 95014 캘리포니아 쿠퍼티노 인피니트 루프 1

(72) 발명자

브라트, 조세프 피.

미국 95014 캘리포니아주 쿠퍼티노 엠/에스 74-3에스오씨 인피니트 루프 1

홀랜드, 피터 에프.

미국 95014 캘리포니아주 쿠퍼티노 엠/에스 74-3에스오씨 인피니트 루프 1

(74) 대리인

백만기, 양영준

전체 청구항 수 : 총 18 항

#### (54) 발명의 명칭 디스플레이 파이프 내에서의 스트리밍 변환

#### (57) 요 약

실시예에서, 디스플레이 파이프는 그 디스플레이 파이프가 디스플레이를 위해 판독하고 있는 이미지들에 대응하는 하나 이상의 변환 유닛을 포함한다. 각각의 변환 유닛은 이미지 데이터 페치들에 앞서 변환들을 프리페치하도록 구성될 수 있으며, 이것은 (적어도 대부분의 경우에서) 디스플레이 파이프에서의 변환 미스들을 방지할 수 있다. 변환 유닛들은 FIFO(first-in, first-out) 방식으로 변환들을 유지할 수 있고, 디스플레이 파이프 페치 하드웨어는 주어진 변환 또는 변환이 더 이상 필요하지 않을 때 변환 유닛에게 통보할 수 있다. 변환유닛은 식별된 변환들을 무효화하고, 가장 최근에 프리페치된 가상 페이지에 인접한 가상 페이지들을 위한 추가의 변환을 프리페치할 수 있다.

#### 대 표 도 - 도1

## 특허청구의 범위

#### 청구항 1

변환 유닛(translation unit)으로서,

복수의 엔트리를 포함하는 메모리 - 각각의 엔트리는 이미지 데이터의 소스 버퍼 내의 다른 가상 페이지에 대한 변화을 저장하도록 구성됨 -; 및

상기 메모리에 연결된 제어 회로

를 포함하고,

상기 제어 회로는 처리가 완료된 상기 소스 버퍼 내의 하나 이상의 가상 페이지를 식별하는 표시를 수신하도록 연결되고, 상기 제어 회로는 상기 표시에 의해 나타내어지는 상기 하나 이상의 가상 페이지에 대한 변환들을 상기 메모리로부터 페기하고, 상기 소스 버퍼 내의 다른 가상 페이지들에 대한 추가의 변환들을 프리페치 (prefetch)하도록 구성되며, 상기 다른 가상 페이지들은 소스 버퍼 내의 제2 가상 페이지에 인접한 제1 가상 페이지를 포함하고, 상기 제2 가상 페이지에 대한 변환은 상기 메모리 내에 저장된 변환들 중 가장 최근에 페치된 변환인 변환 유닛.

#### 청구항 2

제1항에 있어서,

상기 제어 회로는, 처리가 상기 소스 버퍼로부터의 이미지 데이터의 처리를 시작하고 있음을 나타내는 시작 표시를 수신하도록 연결되고, 상기 변환 유닛은 상기 시작 표시에 응답하여 변환들의 메모리를 클리어하도록 구성되는 변환 유닛.

# 청구항 3

제2항에 있어서.

상기 제어 회로는 상기 소스 버퍼로부터 다수의 연속적인 가상 페이지들에 대한 변환들을 프리페치하도록 구성되고, 그 개수는 상기 메모리 내의 상기 복수의 엔트리의 개수와 동일한 변환 유닛.

### 청구항 4

제3항에 있어서,

상기 개수는 상기 소스 버퍼의 행 내의 가상 페이지들의 개수의 2배인 변환 유닛.

## 청구항 5

디스플레이 파이프로서,

복수의 이미지 처리 파이프라인 - 상기 복수의 이미지 처리 파이프라인 중의 각각의 이미지 처리 파이프라인은 그 이미지 처리 파이프라인에 대하여 이미지 데이터를 페치하도록 구성된 페치/메모리 관리 유닛을 포함하고, 상기 페치/메모리 관리 유닛은 상기 이미지 데이터의 어드레스들을 변환하기 위해 복수의 변환을 프리페치하도록 구성된 변환 유닛을 포함하며, 상기 복수의 변환은 페치되고 있는 이미지 내의 적어도 2행의 타일을 변환함 -; 및

상기 복수의 변환에 대한 프리페치 동작들 및 상기 이미지 데이터에 대한 페치 동작들을 메모리에 송신하도록 구성된, 상기 복수의 이미지 처리 파이프라인에 연결된 호스트 인터페이스

를 포함하는 디스플레이 파이프.

#### 청구항 6

제5항에 있어서,

상기 복수의 이미지 처리 파이프라인은 정적 이미지를 페치하도록 구성된 적어도 하나의 사용자 인터페이스

유닛을 포함하는 디스플레이 파이프.

#### 청구항 7

제6항에 있어서,

상기 복수의 이미지 처리 파이프라인은 비디오 시퀀스의 프레임들을 폐치하도록 구성된 적어도 하나의 비디오 파이프라인을 포함하는 디스플레이 파이프.

#### 청구항 8

제7항에 있어서,

상기 적어도 하나의 비디오 파이프라인은 복수의 페치/메모리 관리 유닛을 포함하고, 상기 복수의 페치/메모리 관리 유닛 각각은 다른 이미지 평면에 대응하는 디스플레이 파이프.

#### 청구항 9

메모리 제어기에 인터페이스하도록 구성된 포트 인터페이스 유닛;

이미지 프로세서;

상기 이미지 프로세서에 연결되고, 상기 이미지 프로세서에 대하여 최근에 사용된 변환들을 캐싱하도록 구성된 변환 유닛 - 상기 변환 유닛은 상기 이미지 프로세서로부터 메모리 동작들을 수신하고, 상기 메모리 동작들 내의 가상 어드레스들을 변환하도록 연결되고, 상기 변환 유닛은 상기 메모리 동작들을 변환된 어드레스들과 함께 상기 포트 인터페이스 유닛에 송신하도록 구성됨 -; 및

디스플레이를 위한 이미지 데이터를 페치하기 위해 상기 포트 인터페이스 유닛에 연결된 디스플레이 파이프 - 상기 디스플레이 파이프는 이미지 데이터를 저장하는 복수의 가상 페이지에 대한 변환들을 프리페치하도록 구성된 하나 이상의 스트리밍 변환 유닛을 포함하고, 상기 스트리밍 변환 유닛들은 상기 디스플레이 파이프가처리를 완료한 가상 페이지들의 변환들을 페기하고 하나 이상의 추가의 변환을 프리페치하도록 구성되며, 상기 디스플레이 파이프는 상기 이미지 데이터에 대한 페치 요청들 및 변환 데이터를 판독하기 위한 요청들을 송신하기 위해 상기 포트 인터페이스 유닛에 연결됨 -

를 포함하는 장치.

## 청구항 10

제9항에 있어서.

상기 변환 유닛은, 상기 변환 유닛에서의 미스(miss)에 응답하여, 상기 미스에 대한 변환을 페치하고, 상기 변환을 캐싱하도록 구성되는 장치.

#### 청구항 11

제9항에 있어서,

상기 추가의 변환들은 상기 스트리밍 변환 유닛 내에서 가장 최근에 프리페치된 변환에 연속하는 장치.

#### 청구항 12

제9항에 있어서,

주어진 스트리밍 변환 유닛에 의해 프리페치된 상기 복수의 가상 페이지는 처리 중인 소스 이미지 내의 적어도 2행의 가상 페이지들을 포함하는 장치.

#### 청구항 13

제9항에 있어서,

상기 이미지 데이터는 이미지 데이터의 타일들로서 배열되고, 상기 복수의 가상 페이지 중의 각각의 가상 페이지는 하나의 타일을 저장하는 장치.

#### 청구항 14

디스플레이를 위해 이미지 데이터를 처리하도록 구성된 디스플레이 파이프 내에 복수의 변환을 프리페치하는 단계 - 상기 복수의 변환은 상기 이미지 데이터를 포함하는 소스 버퍼 내의 가상 페이지들에 대한 것임 -:

상기 복수의 변환 중 하나 이상의 변환에 대하여 처리가 완료되었다는 표시를 수신하는 단계; 및

하나 이상의 추가의 변환을 프리페치하는 단계 - 상기 추가의 변환들 중 제1 변환은 메모리 내의 페이지 테이블에서 상기 복수의 변환 중 가장 최근에 페치된 변환에 인접한 것임 -

를 포함하는 방법.

#### 청구항 15

제14항에 있어서,

상기 하나 이상의 추가의 변환은 적어도 2개의 변환이고, 상기 적어도 2개의 변환은 상기 메모리 내의 페이지 테이블 내에서 연속하는 것인 방법.

#### 청구항 16

제15항에 있어서.

상기 복수의 변환은 상기 메모리 내의 페이지 테이블 내에서 연속하는 것인 방법.

#### 청구항 17

제14항에 있어서,

상기 복수의 변환의 개수는 적어도 상기 소스 버퍼 내의 2행의 가상 페이지들을 프리페치하기에 충분한 것인 방법.

#### 청구항 18

제14항에 있어서.

상기 디스플레이 파이프가 상기 소스 버퍼의 처리를 시작하고 있음을 나타내는 시작 표시를 수신하는 단계; 및

상기 시작 표시에 응답하여, 상기 디스플레이 파이프 내에서 변환 유닛으로부터의 변환들을 클리어하고, 상기 복수의 변환을 프리페치하는 단계

를 더 포함하는 방법.

## 명 세 서

## 기 술 분 야

[0001] 본 발명은 가상 메모리 시스템들의 분야에 관한 것이다.

#### 배경기술

[0002]

가상 메모리 시스템들은 컴퓨팅 시스템들 내에서 다양한 이유로 인해 구현된다. 예를 들어, 가상 메모리는 더 작은 물리적 메모리를 구현하면서도, 소프트웨어 프로세스가 이용할 수 있는 더 큰 가상 메모리 공간을 만들기 위해 이용될 수 있다. 디스크 드라이브와 같은 비휘발성 저장소는 현재 이용되지 않고 있는 가상 메모리 공간으로부터의 데이터를 저장할 수 있다. 가상 메모리는 동일한 시스템 상에서 실행되고 있는 상이한 소프트웨어 프로세스들을 고립시켜서, 한 프로세스가 다른 프로세스에 속한 데이터를 액세스할 수 없게 하기 위해 이용될 수 있다. 가상 메모리는, 제어 소프트웨어(예를 들어, 운영 체제, 하이퍼바이저와 같은 가상 머신모니터(VMM), 또는 기타 권한있는 소프트웨어)가 물리적 메모리 내의 데이터를 재배치(relocate)하면서도 프로세스에게는 가상 메모리 공간 내에서 어드레스되는 연속적인 메모리로서 보이게 하는 것을 허용하기 위해서도 이용될 수 있다. 따라서, 데이터는 물리적인 메모리 공간 내의 어디에서든, 이용가능한 메모리에 할당될수 있다. 물리적 메모리가 프로세스들 간에서 공유되므로, 물리적 메모리 내에서 데이터를 재배치하는 능력

은 제어 소프트웨어의 부담을 덜어준다.

- [0003] 전형적으로, 제어 소프트웨어는 가상 어드레스들로부터, 그 가상 어드레스들에 대해 할당된 메모리 위치들의 물리적 어드레스들로의 변환들(translations)을 준비한다. 변환 정보는 메모리 내의 하나 이상의 페이지 테이블 내에 저장되고, 시스템 내의 변환 하드웨어는 가상 어드레스들을 물리적 어드레스들로 변환하기 위해 변환 정보를 캐싱한다. 변환은 페이지 입도(page granularity)로 수행된다. 즉, 가상 메모리 시스템 내의 페이지 경계에 정렬되는 한 블록의 가상 어드레스들은 모두 동일한 변환에 의해 메모리 내의 한 물리적 페이지로 변환된다. 페이지 크기는 달라질 수 있다(예를 들어, 4 킬로바이트, 8 킬로바이트, 또는 일부 경우에서는 몇 메가바이트로 훨씬 더 크게). 일부 시스템들은, 주어진 시점에서 모든 페이지들이 선택된 크기를 갖도록 프로그램적으로 선택가능하든, 아니면 상이한 페이지 크기들에 동시에 지원되도록 페이지별로 가변적이든 간에, 가변 페이지 크기를 지원한다. 주어진 가상 페이지를 위한 물리적 페이지 어드레스를 지정하는 변환 정보는 그 가상 페이지에 대한 변환이라고 칭해진다. 변환은 물리적 페이지를 식별하는 물리적 페이지 번호를 포함하며, 유효 비트, 캐시 속성 등과 같은 다양한 속성 비트들을 포함할 수 있다. 가상 페이지는 가상 어드레스 공간 내의 페이지 정렬된 페이지 크기의 블록(page-aligned, page-sized block)이며, 마찬가지로, 물리적 페이지는 물리적 어드레스 공간 내의 페이지 정렬된 페이지 크기의 블록(page-sized block)이며, 마찬가지로, 물리적 페이지는 물리적 어드레스 공간 내의 페이지 정렬된 페이지 크기의 블록이다.

- [0004] 변환들의 캐성은 (캐성된 변환들을 통해 물리적 어드레스로 변환되는) 가상 어드레스를 이용하여 메모리를 액세스하는 처리를 가속화한다. 그러나, 캐시들은 유한하고, 따라서 때로는 메모리로부터 변환 하드웨어로 변환이 페치(fetch)될 것을 요구하는 미스들(misses)이 존재한다. 다양한 구현들에서, 하드웨어가 메모리로부터 미스된 변환을 판독할 수 있고, 또는 소프트웨어가 변환을 하드웨어 내로 로딩할 수 있다. 어느 경우에서 든, 변환 미스가 발생할 때, 메모리 액세스의 레이턴시(latency)가 증가된다.

## 발명의 내용

### 과제의 해결 수단

- [0005] 실시예에서, 디스플레이 파이프는 그 디스플레이 파이프가 디스플레이를 위해 판독하고 있는 이미지들에 대응하는 하나 이상의 변환 유닛을 포함한다. 각각의 변환 유닛은 이미지 데이터 페치에 앞서 변환들을 프리페치 (prefetch)하도록 구성될 수 있고, 이것은 (적어도 대부분의 경우에서) 디스플레이 파이프 내에서의 변환 미스들을 방지할 수 있다. 변환 유닛들은 FIFO(first-in, first-out) 방식으로 변환들을 유지할 수 있으며, 디스플레이 파이프 페치 하드웨어는 주어진 변환 또는 변환들이 더 이상 필요하지 않을 때 변환 유닛에게 알릴수 있다. 변환 유닛은 식별된 변환을 무효화하고, 가상 최근에 프리페치된 가상 페이지와 연속하는 가상 페이지들에 대한 추가의 변환들을 프리페치할 수 있다.

- [0006] 실시예에서, 위에서 설명된 프리페치 변환 유닛들의 포함은, 보다 더 복잡한 변환 유닛을 디스플레이 파이프들이 이용하는 메모리에 대한 동일한 포트를 공유하는 이미지 프로세서에 전용으로 하는 것을 허용할 수 있다. 디스플레이 파이프로부터의 경합은 보다 더 복잡한 변환 유닛으로부터 제거될 수 있으므로, 이미지 프로세서로부터의 보다 더 많은 랜덤-액세스 메모리 요청들이 보다 더 복잡한 변환 유닛 내에서 히트할 가능성이 높아질 수 있고, 이것은 이미지 프로세서에 대한 미스 레이트도 물론 감소시킬 수 있다.

#### 도면의 간단한 설명

[0007] 이하의 상세한 설명은 이하에 간단하게 설명되는 첨부 도면들을 참조한다.

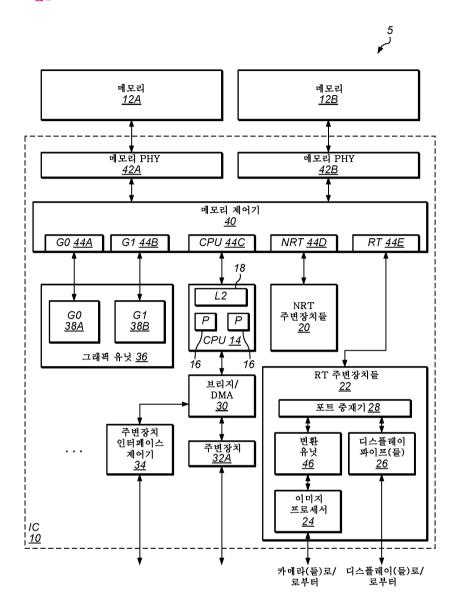

도 1은 집적 회로의 일 실시예의 블록도이다.

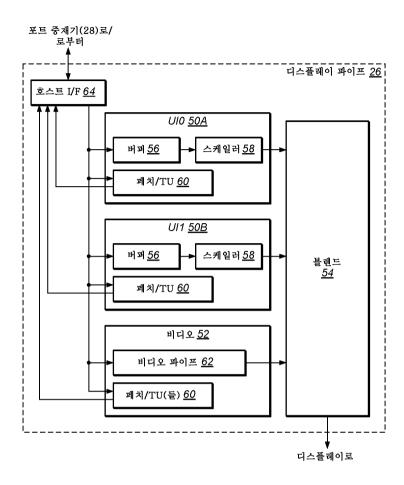

도 2는 도 1에 도시된 디스플레이 파이프의 일 실시예의 블록도이다.

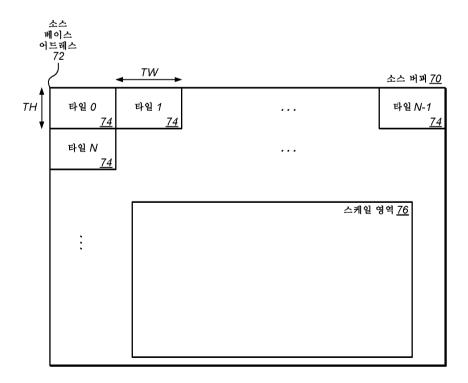

도 3은 소스 버퍼의 일 실시예의 블록도이다.

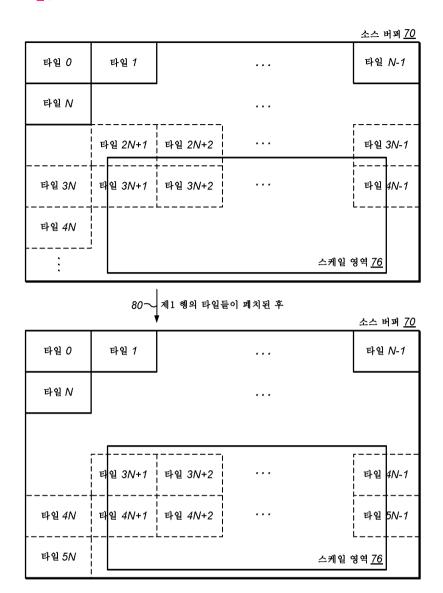

도 4는 디스플레이 파이프 내의 메모리 관리 유닛(MMU)에서 유효할 수 있는 변환들의 예의 블록도이다.

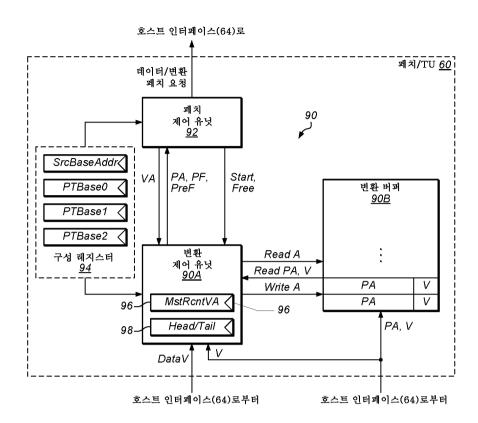

도 5는 도 2에 도시된 페치/MMU 유닛의 일 실시예의 블록도이다.

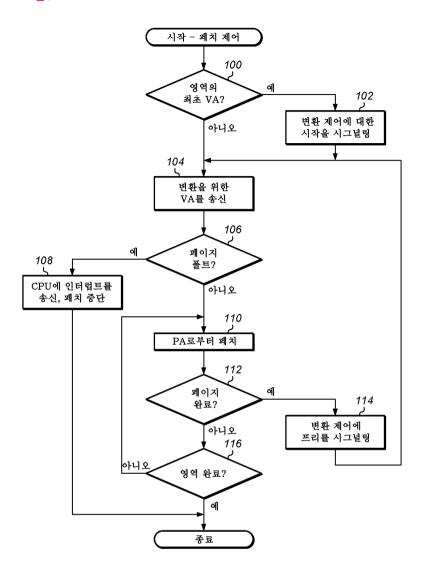

도 6은 도 5에 도시된 폐치 제어 유닛의 일 실시예의 동작을 나타낸 흐름도이다.

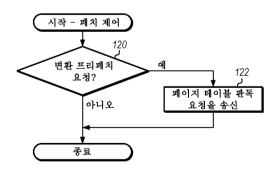

도 7은 도 5에 도시된 페치 제어 유닛의 일 실시예의 추가의 동작을 나타낸 흐름도이다.

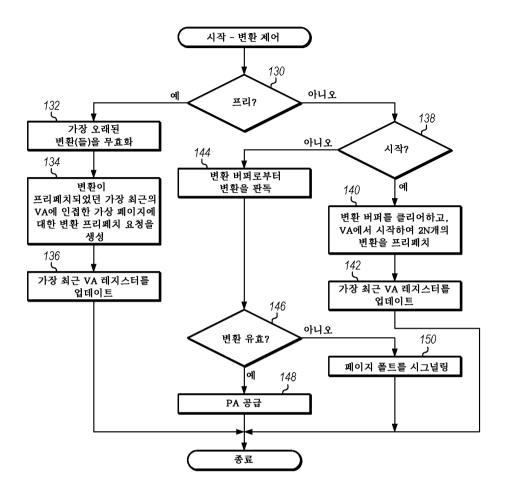

도 8은 도 5에 도시된 변환 제어 유닛의 일 실시예의 동작을 나타낸 흐름도이다.

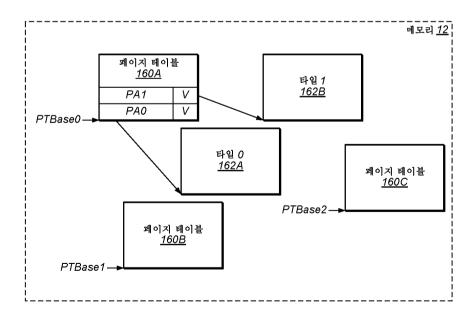

도 9는 소스 버퍼의 타일들 및 변환 테이블들을 저장하는 메모리의 일 실시예의 블록도이다.

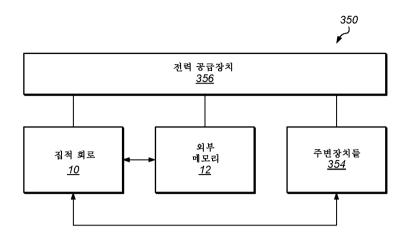

도 10은 시스템의 일 실시예의 블록도이다.

본 발명은 다양한 수정 및 대안적인 형태들을 허용하지만, 그들의 구체적인 실시예들이 도면들에 예시로서 도시되어 있고 여기에 상세하게 설명될 것이다. 그러나, 도면들 및 그에 대한 상세한 설명은 본 발명을 개시된 특정한 형태로 제한하도록 의도된 것이 아니며, 반대로, 첨부된 청구항들에 의해 정의된 대로의 본 발명의 취지 및 범위 내에 드는 모든 수정, 균등물 및 대안들을 포함하도록 의도됨을 이해해야 한다. 여기에서 이용되는 제목들은 오직 체계화를 위한 것이며, 설명의 범위를 제한하기 위해 이용되도록 의도된 것이 아니다. 본출원 전체에서 이용될 때, "~수 있다(may)"는 용어는 필수적이라는 의미(mandatory sense)(즉, 반드시 그러해야 함을 의미함)가 아니라, 허용적인 의미(permissive sense)(즉, ~일 가능성을 가짐을 의미함)로 이용된 것이다. 마찬가지로, "포함한다(include, including, includes)"는 용어는 그에 제한된다는 것이 아니라 포함한다는 것을 의미한다.

다양한 유닛, 회로 또는 기타 컴포넌트들이 태스크 또는 태스크들을 수행"하도록 구성되는(configured to)" 것으로서 설명될 수 있다. 그러한 맥락들에서, "~하도록 구성된다"는 것은 동작 동안 태스크 또는 태스크들을 수행하는 "회로망을 갖는다"는 것을 일반적으로 의미하는, 구조에 대한 폭넓은 기재이다. 통상적으로 그러하듯이, 유닛/회로/컴포넌트는 그 유닛/회로/컴포넌트가 현재 온(on) 상태가 아니더라도 태스크를 수행하도록 구성될 수 있다. 일반적으로, "~하도록 구성된"에 대응하는 구조를 형성하는 회로망은 동작을 구현하는 하드웨어 회로를 포함할 수 있다. 마찬가지로, 설명에서의 편의를 위하여, 다양한 유닛/회로/컴포넌트가 태스크 또는 태스크들을 수행하는 것으로서 설명될 수 있다. 그러한 설명은 "~하도록 구성된"이라는 구문을 포함하는 것으로서 해석되어야 한다. 하나 이상의 태스크를 수행하도록 구성된 유닛/회로/컴포넌트에 관한 기재는 그 유닛/회로/컴포넌트에 대하여 35 U.S.C. § 112의 6항의 해석을 적용하도록 명시적으로 의도된 것이아니다.

#### 발명을 실시하기 위한 구체적인 내용

[0008]

이제, 도 1을 보면, 시스템(5)의 일 실시예의 블록도가 도시되어 있다. 도 1의 실시예에서, 시스템(5)은 외 부 메모리들(12A-12B)에 연결된 집적 회로(IC)(10)를 포함한다. 도시된 실시예에서, 집적 회로(10)는 하나 이상의 프로세서(16) 및 레벨 2(L2) 캐시(18)를 포함하는 중앙 처리 유닛(CPU) 블록(14)을 포함한다. 다른 실시예들은 L2 캐시(18)를 포함하지 않을 수도 있고/거나 추가 레벨들의 캐시를 포함할 수도 있다. 추가적으 로, 둘보다 많은 프로세서(16)를 포함하는 실시예 및 단 하나의 프로세서(16)만을 포함하는 실시예가 고려된 다. 집적 회로(10)는 하나 이상의 비-실시간(non-real time, NRT) 주변장치(20)의 집합, 및 하나 이상의 실 시간(real time, RT) 주변장치(22)의 집합을 더 포함한다. 도시된 실시예에서, RT 주변장치들은 이미지 프로 세서(24), 하나 이상의 디스플레이 파이프(26), 변환 유닛(46) 및 포트 중재자(port arbiter)(28)를 포함한다. 다른 실시예들은 더 많거나 더 적은 이미지 프로세서(24), 더 많거나 더 적은 디스플레이 파이프 (26), 및/또는 요구되는 대로의 임의의 추가의 실시간 주변장치들을 포함할 수 있다. 이미지 프로세서(24)는 시스템(5) 내의 하나 이상의 카메라로부터 이미지 데이터를 수신하도록 연결될 수 있다. 마찬가지로, 디스플 레이 파이프들(26)은 시스템 내의 하나 이상의 디스플레이를 제어하는 하나 이상의 디스플레이 제어기(도시되 지 않음)에 연결될 수 있다. 이미지 프로세서(24)는 변환 유닛(46)에 연결될 수 있고, 그것은 포트 중재자 (28)에 더 연결될 수 있다. 포트 중재자(28)는 디스플레이 파이프들(26)에도 물론 연결될 수 있다. 도시된 실시예에서, CPU 블록(14)은 하나 이상의 주변 장치(32) 및/또는 하나 이상의 주변장치 인터페이스 제어기 (34)에 연결될 수 있는 브리지/DMA(direct memory access) 제어기(30)에 연결된다. 다양한 실시예들에서, 주 변 장치들(32) 및 주변장치 인터페이스 제어기들(34)의 개수는 0으로부터 임의의 원하는 수로 변화할 수 있다. 도 1에 도시된 시스템(5)은 GO(38A) 및 G1(38B)과 같은 하나 이상의 그래픽 제어기를 포함하는 그래픽 유닛(36)을 더 포함한다. 다른 실시예들에서, 그래픽 유닛마다의 그래픽 제어기의 개수 및 그래픽 유닛들의 개수는 달라질 수 있다. 도 1에 도시되어 있는 바와 같이, 시스템(5)은 하나 이상의 메모리 물리 인터페이스 회로(PHY)(42A-42B)에 연결된 메모리 제어기(40)를 포함한다. 메모리 PHY(42A-42B)는 집적 회로(10)의 핀들 상에서 메모리들(12A-12B)에 통신하도록 구성된다. 메모리 제어기(40)는 또한 포트들(44A-44E)의 집합을 포 함한다. 포트들(44A-44B)은 각각 그래픽 제어기(38A-38B)에 연결된다. CPU 블록(14)은 포트(44C)에 연결된 다. NRT 주변장치들(20) 및 RT 주변장치들(22)은 각각 포트들(44D-44E)에 연결된다. 다른 실시예들에서, 메 모리 제어기들의 수와 마찬가지로, 메모리 제어기(40) 내에 포함된 포트들의 수는 달라질 수 있다. 다른 실 시예들에서, 메모리 PHY(42A-42B) 및 대응하는 메모리(12A-12B)의 개수는 하나이거나 둘보다 많을 수 있다.

- [0009] 일 실시예에서, 각각의 포트(44A-44E)는 특정 타입의 트래픽에 연관될 수 있다. 예를 들어, 일 실시예에서, 트래픽 타입들은 RT 트래픽, NRT 트래픽 및 그래픽 트래픽을 포함할 수 있다. 다른 실시예들은, 상기 트래픽 타입들에 더하여, 그를 대신하여, 또는 그들의 부분집합에 더하여, 다른 트래픽 타입들을 포함할 수 있다. 트래픽의 각 타입은 (예를 들어, 요구조건들 및 행동에 관련하여) 서로 다르게 특징지어질 수 있으며, 메모리 컨트롤러는 특징들에 기초하여 더 높은 성능을 제공하기 위해 트래픽 타입들을 서로 다르게 다룰 수 있다. 예를 들어, RT 트래픽은 특정한 시간량 내에서의 각각의 메모리 동작의 서비스를 요구한다. 동작의 레이턴시 가 특정한 시간량을 초과하는 경우, RT 주변장치 내에서 에러있는 동작이 발생할 수 있다. 예를 들어, 이미 지 프로세서(24) 내에서 이미지 데이터가 상실될 수 있으며, 또는 디스플레이 파이프들(26)이 연결되어 있는 디스플레이들 상의 디스플레이된 이미지가 시각적으로 왜곡될 수 있다. RT 트래픽은 예를 들어 등시성인 것 으로서 특징지어질 수 있다. 반면에, 그래픽 트래픽은 비교적 높은 대역폭일 수 있지만, 레이턴시에 민감하 지 않다. 프로세서들(16)로부터 오는 것과 같은 NRT 트래픽은 성능상의 이유로 레이턴시에 더 민감하지만, 더 높은 레이턴시 동안 살아남는다. 즉, NRT 트래픽은 일반적으로 그 NRT 트래픽을 생성한 장치들에서의 에 러있는 동작을 유발하지 않고서, 임의의 레이턴시에서 서비스될 수 있다. 마찬가지로, 레이턴시에 덜 민감하 지만 대역폭이 더 높은 그래픽 트래픽은 일반적으로 임의의 레이턴시에서 서비스될 수 있다. 다른 NRT 트래 픽은 비교적 낮은 대역폭이지만 일반적으로 적정한 레이턴시에서 서비스될 수 있는 오디오 트래픽을 포함할 수 있다. 대부분의 주변장치 트래픽은 또한 NRT일 수 있다(예를 들어, 자기, 광학 또는 고체상태 저장소와 같은 저장 장치들로의 트래픽). 상이한 트래픽 타입들에 연관된 포트들(44A-44E)을 제공함으로써, 메모리 제 어기(40)는 상이한 트래픽 타입들에 병렬로 노출될 수 있다.

- [0010] 앞에서 언급된 바와 같이, RT 주변장치들(22)은 이미지 프로세서(24) 및 디스플레이 파이프들(26)을 포함할 수 있다. 디스플레이 파이프들(26)은 하나 이상의 이미지 프레임을 페치하고, 그 프레임들을 블렌딩하여 디스플레이 이미지를 생성하기 위한 회로망을 포함할 수 있다. 디스플레이 파이프들(26)은 하나 이상의 비디오 파이프라인을 더 포함할 수 있고, 비디오 프레임들은 비디오 프레임 레이트에서의 디스플레이를 위해 프레임들을 생성하기 위해 (비교적) 정적인 이미지 프레임들과 블렌딩될 수 있다. 디스플레이 파이프들(26)의 결과는 디스플레이 스크린 상에 디스플레이될 픽셀들의 스트림일 수 있다. 픽셀 값들은 디스플레이 스크린 상에서의 디스플레이를 위해 디스플레이 제어기에 송신될 수 있다. 이미지 프로세서(24)는 카메라 데이터를 수신하고, 그 데이터를 처리하여 메모리 내에 저장될 이미지로 할 수 있다.

- [0011] 디스플레이 파이프들(26) 및 이미지 프로세서(24) 둘 다는 가상 어드레스 공간에서 동작할 수 있으며, 따라서 메모리 동작들에 대한 물리적 어드레스들을 생성하여 메모리를 판독하거나 기입하기 위해 변환들을 이용할 수 있다. 이미지 프로세서(24)는 어느 정도 랜덤한 액세스 메모리 패턴을 가질 수 있으며, 따라서 변환을 위해 변환 유닛(46)에 의존할 수 있다. 변환 유닛(46)은 각 변환을 그 변환이 다른 캐싱된 변환들에 관련하여 얼마나 자주 이용되는지에 기초하여 소정 기간 동안 캐싱하는 TLB(translation lookaside buffer)를 이용할 수 있다. 예를 들어, TLB는 세트 연관(set associative) 또는 완전 연관(fully associative) 구성을 이용할 수 있으며, LRU(least recently used) 타입 알고리즘은 세트 내의 (또는 완전 연관 구성에서의 TLB에 걸친) 변환들 간에서 변환들의 이용의 신근성(recency)의 순위를 정하기 위해 이용될 수 있다. LRU 타입 알고리즘들은 예를 들어, 트루(true) LRU, 의사(pseudo) LRU, MRU(most recently used) 등을 포함할 수 있다. 또한, TLB 내에서의 용량 미스들(capacity misses)의 영향을 감소시키기 위해, 상당히 큰 TLB가 구현될 수 있다.

- [0012] 한편, 디스플레이 파이프들(26)의 액세스 패턴들은 상당히 규칙적일 수 있다. 예를 들어, 각각의 소스 이미지를 위한 이미지 데이터는 가상 어드레스 공간 내의 연속적인 메모리 위치들에 저장될 수 있다. 따라서, 디스플레이 파이프들은 가상 페이지로부터의 소스 이미지 데이터의 처리를 시작할 수 있으며, 후속하는 가상 페이지들이 그 가상 페이지에 연속할 수 있다. 즉, 가상 페이지 번호들은 번호순이며, 이미지 데이터가 페치됨에 따라 페이지마다 1씩 증가 또는 감소한다. 마찬가지로, 변환들은 메모리 내의 주어진 페이지 테이블 내에서 서로에 연속할 수 있다(예를 들어, 페이지 테이블 내의 연속적인 엔트리들은 서로에 대해 수치적으로 하나 많거나 하나 적은 가상 페이지 번호들을 변환할 수 있다). 일부 실시예들에서 하나보다 많은 페이지 테이블 이 이용될 수 있고, 따라서 페이지 테이블의 마지막 엔트리가 다음 페이지 테이블의 처음 엔트리에 연속하지 않을 수 있지만, 대부분의 변환들은 페이지 테이블들 내에서 연속적일 수 있다. 달리 보면, 이미지 데이터를 저장하는 가상 페이지들은 가상 어드레스 공간 내에서 서로에 인접할 수 있다. 즉, 가상 어드레스 공간 내의 인접하는 가상 페이지들 사이에 개재되는 페이지들이 존재하지 않을 수 있다.

- [0013] 디스플레이 파이프들(26)은 디스플레이 파이프들이 이미지 데이터를 판독하기에 앞서 변환들을 프리페치하는 변환 유닛들을 구현할 수 있다. 프리페치는 소스 이미지의 처리가 시작되어야 할 때 개시될 수 있으며, 변환

유닛은 변환 유닛 내의 변환 메모리를 채우기에 충분한 연속적인 변환들을 프리페치할 수 있다. 디스플레이 파이프들 내의 페치 회로망은 가상 페이지들 내의 데이터의 처리가 완료될 때 변환 유닛에게 알릴 수 있고, 변환 유닛은 대응하는 변환을 무효화하고, 추가의 변환들을 프리페치할 수 있다. 따라서, 초기의 프리페치가 완료되고 나면, 각각의 가상 페이지를 위한 변환은 디스플레이 파이프들(26)이 그 가상 페이지로부터의 페치를 시작함에 따라 변환 유닛 내에서 더 빈번하게 이용가능할 수 있다. 또한, 디스플레이 파이프들(26)로부터의 변환 유닛(46)에 대한 경합은 프리페치 변환 유닛들에게 유리하도록 제거될 수 있다. 디스플레이 파이프들 내의 변환 유닛들은 연속적인 가상 페이지들의 집합에 대한 변환을 페치하므로, 그들은 "스트리밍 변환 유닛들"로서 칭해질 수 있다.

- [0014] 일반적으로, 디스플레이 파이프들(26)은 비교적 정적인 프레임들을 페치하도록 구성된 하나 이상의 사용자 인터페이스 유닛들을 포함할 수 있다. 즉, 정적인 프레임 내의 소스 이미지는 비디오 시퀀스의 일부분이 아니다. 정적 프레임이 변경될 수 있긴 하지만, 그것은 비디오 시퀀스에 대응하는 비디오 프레임 레이트에 따라변하고 있지는 않다. 디스플레이 파이프들(26)은 비디오 프레임들을 페치하도록 구성된 하나 이상의 비디오 파이프라인을 더 포함할 수 있다. 이러한 다양한 파이프라인들(예를 들어, 사용자 인터페이스 유닛들 및 비디오 파이프라인들)은 일반적으로 "이미지 처리 파이프라인들"이라고 청해질 수 있다.

- [0015] 메모리 제어기(40)로 되돌아가면, 일반적으로, 포트는 하나 이상의 소스와 통신하기 위한 메모리 제어기(40) 상의 통신 포인트일 수 있다. 일부 경우들에서, 포트는 소스에 전용일 수 있다(예를 들어, 포트(44A-44B)는 각각 그래픽 제어기(38A-38B)에 전용일 수 있다). 다른 경우들에서, 포트는 복수의 소스 간에 공유될 수 있 다(예를 들어, 프로세서들(16)은 CPU 포트(44C)를 공유할 수 있고, NRT 주변장치들(20)은 NRT 포트(44D)를 공 유할 수 있고, 디스플레이 파이프들(26) 및 이미지 프로세서들(24)과 같은 RT 주변장치들(22)은 RT 포트(44 E)를 공유할 수 있다.) 포트는 하나 이상의 소스와 통신하기 위해 단일 인터페이스에 연결될 수 있다. 따라 서, 소스들이 인터페이스를 공유하는 경우, 소스들 간에서의 선택을 위해, 인터페이스의 소스 측에 중재자가 존재할 수 있다. 예를 들어, L2 캐시(18)는 메모리 제어기(40)에 대하여 CPU 포트(44C)를 위한 중재자로서 기능할 수 있다. 포트 중재자(28)는 RT 포트(44E)를 위한 중재자로서 기능할 수 있고, 유사한 포트 중재자 (도시되지 않음)가 NRT 포트(44D)를 위한 중재자일 수 있다. 포트 상의 단일 소스, 또는 포트 상의 소스들의 조합이 에이전트라고 칭해질 수 있다. 각각의 포트(44A-44E)는 자신의 개별 에이전트와 통신하기 위해 인터 페이스에 연결된다. 인터페이스는 임의의 유형의 통신 매체(예를 들어, 버스, 포인트-대-포인트 접속 등)일 수 있으며, 임의의 프로토콜을 구현할 수 있다. 일부 실시예들에서, 포트들(44A-44E)은 모두 동일한 인터페 이스 및 프로토콜을 구현할 수 있다. 다른 실시예들에서, 상이한 포트들은 상이한 인터페이스들 및/또는 프 로토콜들을 구현할 수 있다. 또 다른 실시예들에서, 메모리 제어기(40)는 단일 포트를 가질 수 있다(singleported).

- [0016] 실시예에서, 각각의 소스는 그 소스에 의해 송신되는 각각의 메모리 동작에 QoS(quality of service) 매개변수를 할당할 수 있다. QoS 매개변수는 메모리 동작에 대해 요청된 서비스 레벨을 식별할 수 있다. 더 높은 서비스 레벨을 요청하는 QoS 매개변수 값을 갖는 메모리 동작들은 더 낮은 서비스 레벨을 요청하는 메모리 동작들보다 우선권을 제공받을 수 있다. 각각의 메모리 동작은 플로우 ID(FID)를 포함할 수 있다. FID는 메모리 동작들의 플로우의 일부분으로서 메모리 동작을 식별할 수 있다. 메모리 동작들의 플로우는 일반적으로 관련될 수 있는 반면, 상이한 플로우들로부터의 메모리 동작들은 동일한 소스로부터 온 것일지라 해도 관련되지 않을 수 있다. FID의 일부분(예를 들어, 소스 필드)은 소스를 식별할 수 있고, FID의 나머지는 플로우를 식별할 수 있다(예를 들어, 플로우 필드). 따라서, FID는 트랜잭션 ID와 유사할 수 있고, 일부 소스들은 단순히 트랜잭션 ID를 FID로서 송신할 수 있다. 그러한 경우에서, 트랜잭션 ID의 소스 필드는 FID의 소스 필드일 수 있고, 트랜잭션 ID의 시퀀스 번호(동일 소스로부터의 트랜잭션들 간에서 트랜잭션을 식별함)는 FID의 플로우 필드일 수 있다. 일부 실시예들에서, 상이한 트래픽 타입들은 QoS 매개변수들의 상이한 정의들을 가질 수 있다.

- [0017] 메모리 제어기(40)는 각각의 포트(44A-44E) 상에서 수신된 QoS 매개변수들을 처리하도록 구성될 수 있고, 포트를 상에서 수신된 메모리 동작들을, 그 포트로부터의 다른 메모리 동작들에 관하여, 그리고 다른 포트들 상에서 수신된 다른 메모리 동작들에 관하여 스케줄링하기 위해, 상대적인 QoS 매개변수 값들을 이용할 수 있다. 더 구체적으로, 메모리 제어기(40)는 QoS 매개변수들의 상이한 집합들로부터 도출된 QoS 매개변수들을 비교하도록 구성될 수 있고(예를 들어, RT QoS 매개변수들과 NRT QoS 매개변수들), 그 QoS 매개변수들에 기초하여 스케줄링 결정을 내리도록 구성될 수 있다.

- [0018] 일부 실시예들에서, 메모리 제어기(40)는 계류중인 메모리 동작들을 위하여 QoS 레벨을 업그레이드하도록 구

성될 수 있다. 다양한 업그레이드 메커니즘이 지원될 수 있다. 예를 들어, 메모리 제어기(40)는 동일한 플로우로부터 더 높은 QoS 레벨을 지정하는 QoS 매개변수를 갖는 다른 메모리 동작들을 수신한 것에 응답하여, 그 플로우의 계류 중인 메모리 동작들을 위한 QoS 레벨을 업그레이드하도록 구성될 수 있다. 이러한 형태의 QoS 업그레이드는, 정상적인 메모리 동작 송신 방법을 이용하여 송신되는 QoS 매개변수들이 동일한 플로우 내의 메모리 동작들을 위한 암시적인 업그레이드 요청으로서 기능할 수 있기 때문에, 대역내 업그레이드(inband upgrade)라고 칭해질 수 있다. 메모리 제어기(40)는 더 높은 QoS 레벨을 지정하는 새롭게 수신된 메모리 동작과 동일한 포트 또는 소스로부터의 것이지만 동일한 플로우는 아닌 계류중인 메모리 동작들을 푸시하도록 구성될 수 있다. 다른 예로서, 메모리 제어기(40)는 하나 이상의 에이전트로부터의 측과대 인터페이스 (sideband interface)에 연결되도록 구성될 수 있으며, 측과대 인터페이스 상에서 업그레이드 요청을 수신한 것에 응답하여 QoS 레벨들을 업그레이드할 수 있다. 다른 예에서, 메모리 제어기(40)는 계류중인 메모리 동작들의 상대적인 에이지(age)를 추적하도록 구성될 수 있다. 메모리 제어기(40)는 소정 에이지들에서의 오래된 예모리 동작들의 QoS 레벨을 업그레이드하도록 구성될 수 있다. 업그레이드가 발생하는 에이지들은 오래된 메모리 동작의 현재의 QoS 매개변수에 의존할 수 있다.

- [0019] 메모리 제어기(40)는 포트들에서 수신된 각각의 메모리 동작에 의해 어드레싱되는 메모리 채널을 결정하도록 구성될 수 있고, 대응하는 채널 상에서 메모리 동작들을 메모리(12A-12B)에 송신하도록 구성될 수 있다. 채널들의 개수, 및 채널들로의 어드레스들의 맵핑은 다양한 실시예들에서 달라질 수 있으며, 메모리 제어기 내에 프로그래밍가능할 수 있다. 메모리 제어기는 채널 내로 송신되는 메모리 동작들의 순서를 결정하기 위해, 동일 채널에 맵핑되는 메모리 동작들의 QoS 매개변수들을 이용할 수 있다.

- [0020] 프로세서들(16)은 임의의 명령어 세트 아키텍처를 구현할 수 있으며, 그 명령어 세트 아키텍처 내에 정의된 명령어들을 실행하도록 구성될 수 있다. 프로세서들(16)은 스칼라(scalar), 수퍼스칼라(superscalar), 파이 프라인(pipelined), 수퍼파이프라인(superpipelined), 아웃-오브-오더(out of order), 인-오더(in order), 스페큘레이티브(speculative), 논-스페큘레이티브(non-speculative) 등, 또는 그들의 조합을 포함하는 임의의 마이크로아키텍처를 이용할 수 있다. 프로세서들(16)은 회로망을 포함할 수 있고, 선택적으로는 마이크로코딩 기술들을 구현할 수 있다. 프로세서들(16)은 하나 이상의 레벨 1 캐시를 포함할 수 있고, 따라서 캐시(18)는 L2 캐시이다. 다른 실시예들은 프로세서들(16) 내에 복수 레벨의 캐시들을 포함할 수 있고, 캐시(18)는 계층구조 내에서 다음의 하위 레벨일 수 있다. 캐시(18)는 임의의 크기 및 임의의 구성(세트 연관, 직접 사상(direct mapped) 등)을 이용할 수 있다.

- [0021] 그래픽 제어기(38A-38B)는 임의의 그래픽 처리 회로망일 수 있다. 일반적으로, 그래픽 제어기(38A-38B)는 프레임 버퍼 내에 디스플레이될 개체들을 렌더링하도록 구성될 수 있다. 그래픽 제어기(38A-38B)는 그래픽 동작의 일부 또는 전부, 및/또는 일부 그래픽 동작들의 하드웨어 가속을 수행하기 위해 그래픽 소프트웨어를 실행할 수 있는 그래픽 프로세서들을 포함할 수 있다. 하드웨어 가속 및 소프트웨어 구현의 양은 실시예마다달라질 수 있다.

- [0022] NRT 주변장치들(20)은 성능 및/또는 대역폭을 이유로, 메모리(12A-12B)에의 독립적인 액세스를 제공받는 임의의 비-실시간 주변장치들을 포함할 수 있다. 즉, NRT 주변장치들(20)에 의한 액세스는 CPU 블록(14)에 독립적이며, CPU 블록 메모리 동작들과 병렬로 진행할 수 있다. 주변장치들(32) 및/또는 주변장치 인터페이스 제어기(34)에 의해 제어되는 주변장치 인터페이스에 연결된 주변장치들과 같은 다른 주변장치들도 비-실시간 주변장치일 수 있지만, 메모리에의 독립적인 액세스를 요구하지 않을 수 있다. NRT 주변장치들(20)의 다양한실시예들은 비디오 인코더 및 디코더, 스케일러(scaler)/로테이터(rotator) 회로망, 및 이미지 압축 및/또는압축해제 회로망 등을 포함할 수 있다.

- [0023] 브리지/DMA 제어기(30)는 주변장치(들)(32) 및 주변장치 인터페이스 제어기(들)(34)를 메모리 공간에 브리지하기 위한 회로망을 포함할 수 있다. 도시된 실시예에서, 브리지/DMA 제어기(30)는 주변장치들/주변장치 인터페이스 제어기들로부터의 메모리 동작들을 CPU 블록(14)을 통해 메모리 제어기(40)에 브리정할 수 있다. CPU 블록(14)은 또한 브리정된 메모리 동작들과 프로세서들(16)/L2 캐시(18)로부터의 메모리 동작들 간의 일관성(coherence)을 유지할 수 있다. 또한, L2 캐시(18)는 브리정된 메모리 동작들과, CPU 인터페이스 상에서 CPU 포트(44C)에 송신될 프로세서들(16)로부터의 메모리 동작들을 중재할 수 있다. 브리지/DMA 제어기(30)는 메모리로 및 메모리로부터 데이터의 블록들을 전송하기 위해, 주변장치들(32) 및 주변장치 인터페이스 제어기들(34)을 대신하여 DMA 동작을 제공할 수 있다. 더 구체적으로, DMA 제어기는 주변장치들(32) 및 주변장치인터페이스 제어기들(34)을 대신하여 메모리 제어기(40)를 통해 메모리(12A-12B)로의 및 그로부터의 전송을수행하도록 구성될 수 있다. DMA 제어기는 DMA 동작들을 수행하기 위해 프로세서들(16)에 의해 프로그래밍가

능할 수 있다. 예를 들어, DMA 제어기는 디스크립터들을 통해 프로그래밍가능할 수 있다. 디스크립터들은 DMA 전송을 기술하는, 메모리(12A-12B) 내에 저장된 데이터 구조들일 수 있다(예를 들어, 소스 및 목적지 어드레스, 크기 등). 대안적으로, DMA 제어기는 DMA 제어기 내의 레지스터들(도시되지 않음)을 통해 프로그래밍가능할 수 있다.

- [0024] 주변장치들(32)은 집적 회로(10) 상에 포함된 임의의 요구되는 입력/출력 장치들 또는 다른 하드웨어 장치들 을 포함할 수 있다. 예를 들어, 주변장치들(32)은 이터넷 MAC(media access controller)과 같은 하나 이상의 네트워킹 MAC 또는 WiFi(wireless fidelity) 제어기와 같은 네트워킹 주변장치들을 포함할 수 있다. 다양한 오디오 처리 장치들을 포함하는 오디오 유닛이 주변장치들(32) 내에 포함될 수 있다. 하나 이상의 디지털 신호 프로세서들은 주변장치들(32) 내에 포함될 수 있다. 주변장치들(32)은 타이머, 온-칩 시크릿 메모리, 암호화 엔진 등, 또는 그들의 임의의 조합과 같은 임의의 다른 요구되는 기능들을 포함할 수 있다.

- [0025] 주변장치 인터페이스 제어기들(34)은 임의의 유형의 주변장치 인터페이스를 위한 임의의 제어기들을 포함할 수 있다. 예를 들어, 주변장치 인터페이스 제어기들은 USB(universal serial bus) 제어기, PCIe(peripheral component interconnect express) 제어기, 플래시 메모리 인터페이스, 범용 입력/출력(I/0) 핀들 등과 같은 다양한 인터페이스 제어기들을 포함할 수 있다.

- [0026] 메모리들(12A-12B)은 DRAM(dynamic random access memory), SDRAM(synchronous DRAM), 더블 데이터 레이트 (DDR, DDR2, DDR3 등) SDRAM(mDDR3 등과 같은 SDRAM의 모바일 버전들, 및/또는 LPDDR2 등과 같은 SDRAM들의 저전력 버전들을 포함함), RAMBUS DRAM(RDRAM), 정적 RAM(SRAM) 등과 같은 임의의 유형의 메모리일 수 있다. 하나 이상의 메모리 장치는 회로 보드 상에 연결되어, SIMM(single inline memory modules), DIMM(dual inline memory modules) 등과 같은 메모리 모듈들을 형성할 수 있다. 대안적으로, 장치들에는 칩-온-칩 구성 (chip-on-chip configuration), 패키지-온-패키지 구성(package-on-package configuration) 또는 멀티칩 모듈 구성(multi-chip module configuration)으로 집적 회로(10)가 탑재될 수 있다.

- [0027] 메모리 PHY(42A-42B)는 메모리(12A-12B)에 대한 하위 레벨의 물리 인터페이스를 관리할 수 있다. 예를 들어, 메모리 PHY(42A-42B)는 동기 DRAM 메모리 등에의 적절한 클럭킹을 위해, 신호들의 타이밍을 담당할 수 있다. 일 실시예에서, 메모리 PHY(42A-42B)는 집적 회로(10) 내에 공급되는 클럭에 고정(lock)되도록 구성될 수 있으며, 메모리(12)에 의해 이용되는 클럭을 생성하도록 구성될 수 있다.

- [0028] 다른 실시예들은 도 1에 도시된 컴포넌트들 및/또는 다른 컴포넌트들의 부분집합 또는 확대집합을 포함하는, 컴포넌트들의 다른 조합들을 포함할 수 있음에 유의해야 한다. 주어진 컴포넌트의 한 인스턴스가 도 1에 도 시되어 있을 수 있긴 하지만, 다른 실시예들은 그 주어진 컴포넌트의 하나 이상의 인스턴스를 포함할 수 있다. 마찬가지로, 본 상세한 설명의 전반에 걸쳐서, 주어진 컴포넌트의 단 하나의 인스턴스가 도시되어 있 더라도 하나 이상의 인스턴스가 포함될 수 있고/거나, 복수의 인스턴스가 도시되어 있더라도 단 하나의 인스 턴스를 포함하는 실시예들이 이용될 수 있다.

- [0029] 이제 도 2를 보면, 디스플레이 파이프(26)의 일 실시예의 블록도가 도시되어 있다. 복수의 디스플레이(디스 플레이 제어기들(도시되지 않음)에 의해 제어될 수 있거나, 또는 대응하는 디스플레이 파이프(26)에 의해 직 접 제어될 수 있음)에의 연결을 위한 디스플레이 파이프(26)의 복수의 인스턴스가 존재할 수 있다. 도 2에 도시된 바와 같이, 디스플레이 파이프(26)는 하나 이상의 사용자 인터페이스(UI) 유닛을 포함할 수 있는데, 본 경우에서는 2개가 UIO(50A) 및 UIO(50B)로서 도시되어 있다. 블렌드 유닛(blend unit)(54)과 함께, 비디 오 유닛(52)과 같은 하나 이상의 비디오 유닛도 포함될 수 있다. 호스트 인터페이스 유닛(호스트 I/F)(64)도 포함될 수 있다. 각각의 사용자 인터페이스 유닛(50A-50B)은 버퍼(56), 스케일러(58), 및 페치/변환 유닛(페 치/TU)(60)의 인스턴스들을 포함할 수 있다. 버퍼(56)는 호스트 인터페이스 유닛(64)으로부터 이미지 데이터 를 수신하고, 스케일러(58)에 데이터를 제공하도록 연결될 수 있다. 스케일러(58)는 블렌딩을 위한 알파값과 함께 픽셀들을 블렌드 유닛(54)에 출력하도록 구성될 수 있다. 페치/TU(60)는 호스트 인터페이스 유닛(64)으 로부터 변환 데이터를 수신하고, 포트 중재기(28)로의 (그리고, 궁극적으로는 메모리 제어기(40)로의) 송신을 위해, 메모리 동작들을 호스트 인터페이스 유닛(64)에 제공하도록 연결된다. 비디오 유닛(52)은 비디오 파이 프(62) 및 하나 이상의 페치/TU(60)를 포함할 수 있다. 예를 들어, 비디오 유닛(52)은 비디오 시퀀스 내의 각각의 이미지 평면에 대한 페치/TU(60)를 포함할 수 있다. 다양한 이미지 평면들이 비디오 이미지를 기술할 수 있다. 예를 들어, 이미지 평면들은 컬러 평면들일 수 있다(예를 들어, 적색, 녹색, 청색 또는 Y, Cr, Cb). 비디오 유닛(52) 내의 페치/TU(들)(60)는 메모리 동작들을 호스트 인터페이스 유닛(64)에 제공하고, 그 로부터 변환 데이터를 수신하도록 연결될 수 있다. 비디오 파이프(62)는 호스트 인터페이스 유닛(64)으로부

터 비디오 이미지 데이터를 수신하도록 연결될 수 있다.

- [0030] 페치/TU들(60) 각각은 대응하는 이미지 처리 파이프라인(50A-50B 또는 52)에 대하여 소스 이미지 데이터를 페치하도록 구성될 수 있다. 소스 이미지들은 가상으로 어드레싱될 수 있으며, 페치/TU들(60)은 데이터를 판독하기 위한 메모리 동작들을 위해 가상 어드레스들을 물리적 어드레스들로 변환하기 위해, 변환 유닛들을 포함할 수 있다. 페치/TU들(60)은 또한 디스플레이될 소스 이미지의 초기화에 응답하여, 그리고 소스 이미지의하나 이상의 가상 페이지 내의 데이터의 처리 완료에 응답하여, 메모리로부터 변환들을 프리페치하기 위해 메모리 판독 동작들을 생성하도록 구성될 수 있다. 변환 판독 동작들 및 이미지 데이터 페치 판독 동작들은 페치/TU들(60)에 의해 호스트 인터페이스 유닛(64)에 송신될 수 있고, 호스트 인터페이스 유닛은 동작들을 포트중재기(28)에 송신할 수 있다. 데이터가 판독 동작을 위해 반환될 때, 호스트 인터페이스 유닛(64)은 수신측파이프라인(50A-50B 또는 52)을 위해 데이터를 태그할 수 있고, 데이터가 변환 데이터인지 이미지 데이터인지를 나타낼 수 있다. 그 다음, 수신측 유닛은 데이터를 적절한 대로 페치/TU(60) 또는 이미지 처리 파이프라인에 캡처할 수 있다.

- [0031] 일반적으로, 이미지 데이터는 디스플레이될 소스 이미지를 기술할 수 있다. 실시예에서, 사용자 인터페이스 이미지를 위한 이미지 데이터는 블렌딩을 위한 알파값 및 픽셀 데이터를 포함할 수 있다. 픽셀 데이터는 각 픽셀을 위한 컬러를 기술할 수 있다. 픽셀 데이터는 버퍼(56) 내에 저장될 수 있고, 선택적으로는 스케일러 (58)에 의해 스케일링될 수 있다. 스케일 계수(scale factors)는 사용자 인터페이스 유닛(50A-50B) 내에 프로그래밍될 수 있고, 또는 이미지 데이터 내에 제공될 수 있다. 스케일링된 픽셀들은 알파값들과 함께, 출력 픽셀들로서 블렌드 유닛(54)에 제공될 수 있다. 실시예에서, 사용자 인터페이스 유닛(50A-50B)은 소스 이미지 내의 프로그래밍가능한 액티브 영역들을 지원할 수 있다. 액티브 영역들은 소스 이미지 중에서 디스플레이될 부분들만을 정의할 수 있다. 실시예에서, 사용자 인터페이스 유닛들(50A-50B)은 액티브 영역들 내의 데이터만을 페치하도록 구성될 수 있다. 액티브 영역들 밖에서는, 제로의 알파값을 갖는 더미 데이터가 픽셀 데이터로서 전달될 수 있다.

- [0032] 실시예들에서, 비디오 파이프(62)는 YCbCr 포맷일 수 있는 페치된 비디오 프레임 데이터/정보를 메모리로부터 수신할 수 있으며, 랜덤한 노이즈를 데이터에 삽입하고(디더(dither)), 선택적으로 데이터를 수직 및 수평 방향 중 하나 또는 둘 다에서 스케일링하고, 사용자 인터페이스 유닛(50A-50B)으로부터의 다른 이미지 데이터와의 블렌딩을 위해 데이터를 RGB 컬러 공간으로 변환할 수 있다.

- [0033] 블렌드 유닛(54)은 사용자 인터페이스 유닛(50A-50B) 및 비디오 유닛(52)으로부터 픽셀들의 프레임을 수신할 수 있고, 그들을 레이어별로(layer by layer) 함께 블렌딩하도록 구성될 수 있다. 최종의 결과적인 픽셀들은 출력 FIFO 내에 큐잉될 수 있으며, 디스플레이 제어기에 의해 페치될 수 있다. 블렌드 유닛(54) 내의 최하위 레벨 레이어는 백그라운드 컬러로서 정의될 수 있다. 레이어 1은 레이어 0과 블렌딩될 수 있다. 다음 레이어인 레이어 2는 블렌딩된 레이어 0 및 1과 블렌딩되는 식으로, 모든 레이어가 블렌딩될 때까지 계속될 수 있다.

- [0034] 도 3은 디스플레이 파이프(26)를 위한 가상 어드레스 공간 내의 소스 버퍼(70)를 도시하는 블록도이다. 소스 버퍼(70)는 소스 베이스 어드레스(72)에 의해 가상 어드레스 공간 내에 위치가 찾아질 수 있다. 도시된 실시예에서, 소스 버퍼(70)는 이미지 타일들(74)의 세트로서 구성될 수 있다. 다른 실시예들에서, 소스 버퍼(70)는 스캔 라인들로 구성될 수 있고, 또는 스캔 라인과 타일 구성 간에서 선택하도록 프로그래밍될 수 있다. 타일 구성에서, 타일 내의 픽셀들은 다음 타일로 가기 전에 연속적인 가상 메모리 위치들에 저장된다. 다음 타일은 소스 버퍼(70)의 폭의 끝(예를 들어, 도 3의 타일 N-1)에 도달하여, 다음 타일이 다음 행의 타일들 중의 처음 타일(예를 들어, 도 3의 타일 N)이기 전까지는 수평방향으로 다음으로 인접한 타일일 수 있다. 스캔라인 구성에서, 소스 버퍼(70)의 폭에 걸친 픽셀들의 행은 다음 행으로 가기 전에 연속적인 메모리 위치들에 저장된다. 타일 구성은, 예를 들어 이미지가 압축될 수 있거나, 또는 압축된 이미지로부터 압축해제되는 경우에 이용될 수 있다. 많은 압축 알고리즘이 예를 들어 타일들을 비교하고, 한 타일과 다음 타일 간의 차이를 저장함으로써 작동한다.

- [0035] 도 3에 도시된 것과 같은 타일 구성에서, 하나 이상의 타일이 각각의 가상 페이지에 저장될 수 있다. 타일의 크기는 타일 폭(TW) 및 타일 높이(TH)의 항으로 측정될 수 있다. 실시예에서, 타일 폭은 바이트로 측정되고, 타일 높이는 픽셀들의 행으로 측정된다. 일례에서, 타일 폭은 256 바이트일 수 있고, 타일 높이는 16행일 수 있지만, 다른 예들에서는, 이들 중 하나 또는 둘 다에서 더 큰 크기 및 더 작은 크기가 이용될 수 있다. 예에서, 각각의 타일은 하나의 4 킬로바이트 페이지이고, 따라서 가상 페이지 크기가 4 킬로바이트인 경우, 각 각의 타일은 하나의 변환에 대응한다. 다른 실시예들에서, 가상 페이지는 복수의 타일을 포함할 수 있고, 또

는 한 타일이 복수의 페이지에 걸쳐 확장할 수 있다.

- [0036] 소스 버퍼(70) 내에서, 스케일 영역(76)이 정의될 수 있다. 스케일 영역(76)은 디스플레이될 소스 이미지일 수 있다. 소스 버퍼(70)는 시스템 내에서 지원되는 최대 크기의 이미지일 수 있고, 이미지들은 최대 이하의 임의의 크기를 가질 수 있다. 스케일 영역은, 소스 이미지가 위에서 논의된 바와 같이 이미지 처리 파이프라 인들 내의 스케일러들에 의해 스케일렁될 수 있기 때문에 그와 같이 청해진다. 소스 영역(76)의 위치 및 크기에 더하여, 소스 베이스 어드레스(72)도 이미지 처리 파이프라인 내에 프로그래밍될 수 있다.

- [0037] 도 3에 도시되어 있는 바와 같이, 소스 버퍼(70)의 폭에 걸친 타일들의 수는 N일 수 있으며, N은 정수이다. 예를 들어, 실시예에서, 소스 버퍼(70)는 4 킬로바이트 폭일 수 있고, 타일 폭이 256 바이트라면, N은 16일 수 있다. 다른 실시예들에서는 다른 폭들이 이용될 수 있다.

- [0038] 도 4는 스케일 영역(76)의 페치가 개시될 때의 소스 버퍼(70) 및 스케일 영역(76)을 도시한 것이다. 페치/TU(60)는 페치될 스케일 영역(76)의 제1 픽셀을 포함하는 타일로부터 시작하여, 처음의 2N개의 변환을 프리페치할 수 있다. 도 4의 예에서, 초기 타일은 타일 2N+1이고, 따라서 처음의 2N개의 타일의 마지막 타일(및 변환)은 타일 4N이다. 초기에 프리페치되는 변환들을 나타내기 위해, 이러한 타일들은 도 4에서 점선으로 도시된다. 도 4는 또한, 제1 행의 타일들이 완료된 후에(화살표(80)), 처리에서의 나중 시점에서의 소스 버퍼(70) 및 스케일 영역(76)을 나타낸다. 이 시점에서, 페치/TU(60)는 타일들 2N+1 내지 3N-1 내의 픽셀들의 페치를 완료하였다. 따라서, 이 변환들은 타일 3N을 위한 변환과 함께 무효화되었다. 따라서, 타일 4N+1 내지타일 5N을 위한 새로운 변환들이 프리페치되었다.

- [0039] 페치/TU(60)는 페치/TU(60)의 페치들과 타일들 간의 미스매치를 허용하기 위해, 2N개의 변환들을 프리페치하 도록 구성될 수 있다(여기에서, N은 소스 버퍼(70)의 폭에 걸친 타일들의 수임). 예를 들어, 실시예에서, 페치/TU(60)는 소스 버퍼(70)로부터 한번에 5라인을 페치하도록 구성될 수 있다. 따라서, 임의의 주어진 지점에서, 페치들은 2행의 타일들을 동시에 포함할 수 있다. 현재 행의 마지막 타일이 완전하게 페치되고 나면, 그 행의 변환들이 페기될 수 있고, 다음의 2행을 위한 변환들이 변환들의 프리페칭을 통해 이용가능(또는 거의 이용가능)할 수 있다. 따라서, 많은 경우들에서, 이미지 데이터 페치들은 어떠한 변환 미스도 경험하지 않을 수 있다.

- [0040] 도 4의 예에서, 각 행 내의 제1 타일은 이용되지 않음에 유의해야 한다. 즉, 이미지 처리 파이프라인들은 스케일 영역(76) 내의 데이터만을 페치할 수 있다. 따라서, 각 행 내의 제1 타일을 위한 변환들은 필요하지 않을 수 있다. 일반적으로, 소스 버퍼(70) 및 스케일 영역(76)의 정의에 따라, 각 행 내에는 필요하지 않은 하나 이상의 변환이 존재할 수 있다. 일부 실시예들에서, 페치/TU(60)는 이용되지 않을 타일들을 위한 변환들을 페치하는 것을 회피할 수 있다. 다른 실시예들에서, (미사용 변환들을 페치하기 위한 추가 대역폭의 양이비교적 작을 수 있으므로) 페치/TU(60)는 단순히 각각의 변환을 페치할 수 있다.

- [0041] 도 5는 페치/TU(60)의 일 실시예의 블록도이다. 도 5의 실시예에서, 페치/TU(60)는 변환 유닛(90)(변환 제어 유닛(90A) 및 변환 버퍼 메모리(90B)를 포함), 페치 제어 유닛(92), 및 구성 레지스터들(94)의 세트를 포함한다. 페치 제어 유닛(92) 및 변환 제어 유닛(90A)은 구성 레지스터들(94)에 연결될 수 있다. 페치 제어 유닛(90A)은 호스트 인터페이스 유닛(64) 및 변환 제어 유닛(90A)에 더 연결될 수 있다. 변환 제어 유닛(90A)은 변환 버퍼 메모리(90B)에 연결될 수 있고, 변환 제어 유닛(90A) 및 변환 버퍼 메모리(90B) 둘 다가 호스트 인터페이스 유닛(64)으로부터 데이터를 수신하도록 연결될 수 있다.

- [0042] 일반적으로, 폐치 제어 유닛(92)은 (변환 제어 유닛(90A)을 대신하여) 변환 데이터 폐치 동작들 및 이미지 데이터 폐치 메모리 동작들을 위한 폐치 요청들을 생성하도록 구성될 수 있다. 다른 실시예들에서, 폐치 제어 유닛(90A)은 호스트 인터페이스 유닛(64)으로의 별도의 접속을 통해 변환 데이터 폐치 요청들을 송신할 수 있다. 폐치 제어 유닛(92)이 이미지 데이터를 폐치할 때, 폐치 제어 유닛(92)은 가상 폐이지 어드레스들(도 5의 VA)을 변환 제어 유닛(90A)에 송신하도록 구성될 수 있다. 변환 제어 유닛(90A)은 변환 버퍼 메모리(90B)로부터 대응하는 엔트리를 판독하도록 구성될 수 있고(도 5의 Read A), 메모리는 대응하는 엔트리로부터의 물리적 어드레스 및 유효 비트를 반환할 수 있다(도 5의 Read PA). 변환 제어 유닛(90A)은 변환이 유효하다는 것을 검사하도록 구성될 수 있고, 폐치 제어 유닛(92)에게, 변환이 유효하지 않은 경우에는 폐이지 폴트 (page fault, PF)를, 또는 변환이 유효한 경우에는 물리적 어드레스(PA)를 반환할 수 있다. 다른 실시예들에서, 권한 제어(permission controls)와 같은 추가의 변환 속성들도 체크될 수 있고, 변환이 유효하지 않거나 속성들이 액세스를 허가하지 않는 경우에는 페이지 폴트가 시그널링될 수 있다.

- [0043] 또한, 페치 제어 유닛(92)이 새로운 소스 이미지의 페치를 시작하고 있을 때, 페치 제어 유닛(92)은 초기 가

상 어드레스를 송신하도록 구성될 수 있고, 새로운 소스 이미지의 시작을 시그널링할 수 있다(도 5의 start). 새로운 소스 이미지의 시작에 응답하여, 변환 제어 유닛(90A)은 변환 버퍼(90B)를 클리어하고, 초기 가상 어드레스를 위한 변환에서 시작하여, 변환들을 위한 프리페치들을 시작할 수 있다. 페치 제어 유닛(92)은 주어진 가상 페이지로부터의 데이터의 페치 완료를 나타내는 프리(free) 표시(도 5의 Free)를 송신하도록 더 구성될 수 있다. 변환 제어 유닛(90A)은 변환 버퍼 메모리(90B) 내의 대응하는 변환들을 무효화하고, 가상 최근에 페치된 가상 어드레스에 연속하는 추가의 변환들을 프리페치하도록 구성될 수 있다. 변환 제어 유닛(90A)은 추가의 변환 프리페치들을 생성하기 위하여, 그를 위한 변환이 프리페치되었던 가장 최근의 가상 어드레스를 저장하도록 구성될 수 있다(MstRcntVA 레지스터(96)). 일 실시예에서, 프리 표시는 가장 오래된 것부터한번에 하나씩 변환들을 프리로 하기 위해 어써트될 수 있는 신호일 수 있다. 다른 실시예에서, 프리 표시는 프리인 가장 오래된 변환의 개수의 카운트일 수 있다. 또 다른 실시예들에서, 프리로 된 페이지들의 가상 어드레스들이 공급될 수 있다.

- [0044] 일 실시예에서, 변환 제어 유닛(90A)은 변환 버퍼 메모리(90B)를 FIFO 버퍼로서 관리하도록 구성될 수 있다. 따라서, 메모리(90B)에의 헤드 포인터 및 테일 포인터가 유지될 수 있다(예를 들어, 레지스터(98) 내에). 변환 제어 유닛(90A)은 메모리(90B)를 채우기 위해 프리페치들을 생성하도록 구성될 수 있다(도 5의 Pref). 프리페치 데이터가 호스트 인터페이스 유닛(64)에 의해 반환될 때, 변환 제어 유닛(90A)은 변환 버퍼 메모리 (90B)를 업데이트하기 위해 기입 어드레스를 생성하도록 구성될 수 있다(도 5의 Write A).

- [0045] 변환 버퍼 메모리(90B)는 일반적으로 엔트리들의 세트로 구성된 임의의 유형의 메모리를 포함할 수 있다(예를 들어, 랜덤 액세스 메모리, 플롭(flops) 또는 레지스터들의 세트 등). 각각의 엔트리는 변환을 저장할 수 있다(예를 들어, 도시된 실시예에서는 PA 및 유효 비트, 다른 실시예들에서는 아마도 다른 속성들). 따라서, 실시예에서, 변환 버퍼(90B)는 2N개의 엔트리를 포함할 수 있다. 일부 실시예들에서, 변환의 가상 페이지 번호도 엔트리 내에 저장될 수 있고, 페치 제어 유닛(92)으로부터의 가상 어드레스는 히트(hit)를 검출하기 위해 메모리(90B)에 대하여 캠될(cammed) 수 있다(또는 히트일 것으로 예상되는 엔트리가 판독될 수 있고, 가상 어드레스는 그 엔트리로부터의 가상 페이지 번호와 비교될 수 있다).

- [0046] 구성 레지스터들(94)은 페치/TU(60) 내에 다양한 프로그래밍가능한 값들을 저장할 수 있다. 예를 들어, 소스베이스 어드레스(72)(가상 어드레스)가 레지스터들(94) 내에 저장될 수 있다. 하나 이상의 페이지 테이블 베이스 어드레스들(물리적 어드레스들)도 물론 레지스터(94) 내에 저장될 수 있다. 각각의 페이지 테이블 베이스 어드레스는 메모리 내에서 페이지 테이블의 위치를 찾을 수 있다. 예를 들어, 도 5의 실시예에서는 3개의페이지 테이블 베이스 어드레스, 즉 페이지 테이블 베이스 제로(PTBase0), PTBase1 및 PTBase2가 지원된다.페치/TU(60)에 의해 지원되는 페이지 테이블들의 수는 소스 버퍼(70)의 지원되는 최대 크기에 기초할 수 있다. 예를 들어, 각각의 페이지 테이블은 한 페이지 크기일 수 있으며, 지정된 수의 변환을 저장할 수 있다. 따라서, 가능한 최대 소스 버퍼(70)에 의해 커버될 수 있는 페이지들의 수를 한 페이지 테이블 내에 저장될 수 있는 변환들의 수로 나눈 것은, 페치/TU(60)에 의해 지원되는 페이지 테이블들의 수를 나타낼 수 있다. 다른 실시예들은 페이지 테이블 베이스 어드레스들의 최대 수보다 적게 지원할 수 있으며, 레지스터들 (94)은 소스 이미지가 처리될 때 업데이트될 수 있다.

- [0047] 변환 제어 유닛(90A)은 호스트 인터페이스(64)에 의해 공급되는 변환 데이터의 유효 비트를, 변환 데이터가 제공되고 있다는 표시와 함께 수신하도록 연결될 수 있다(Data V). 변환 제어 유닛(90A)은 변환이 제공되고 있음을 검출할 수 있고, 그에 응답하여 변환 메모리(90B)를 업데이트할 수 있다.

- [0048] 도 6은 페치 제어 유닛(92)의 일 실시예의 특정 동작들의 흐름도이다. 도 6에서는 이해를 쉽게 하기 위해 블록들이 특정한 순서로 도시되어 있지만, 다른 순서들도 이용될 수 있다. 블록들은 페치 제어 유닛(92) 내의 조합 로직(combinatorial logic)에서 병렬로 수행될 수 있다. 블록들, 블록들의 조합들, 및/또는 전체로서의 흐름도는 복수의 클럭 사이클에 걸쳐 파이프라인될 수 있다. 페치 제어 유닛(92)은 도 6에 도시된 동작을 구현하도록 구성될 수 있다.

- [0049] 페치 제어 유닛(92)이 스케일 영역(76) 내의 초기의 가상 어드레스(예를 들어, 소스 이미지의 제1 픽셀 또는 타일, 판정 블록(100)에서 "예" 분기)를 페치하려고 준비하고 있는 동안, 페치 제어 유닛(92)은 변환 제어 유닛(90A)에 시작을 시그널링하도록 구성될 수 있다(블록(102)). 페치 제어 유닛(92)은 초기 가상 어드레스를 변환을 위해 변환 제어 유닛(90A)에 송신하도록 구성될 수 있다(블록(104)). 가상 어드레스가 초기 가상 어드레스가 아닌 경우, 시작은 시그널링되지 않을 수 있지만, 가상 어드레스는 여전히 변환을 위해 송신될 수 있다(판정 블록(100)의 "아니오" 분기 및 블록(104)).

- [0050] 변환이 페이지 폴트로 귀결되는 경우(가상 어드레스에 응답하여 변환 제어 유닛(90A)에 의해 페치 제어 유닛 (92)에 시그널링됨, 판정 블록(106)의 "예" 분기), 페치 제어 유닛(92)은 프로세서들(16) 중 하나에 인터럽트를 송신하도록 구성될 수 있으며 (블록(108)), 데이터 페치를 중단할 수 있다. 페치 제어 유닛(92)은 성공적으로 변환되지 않은 가상 어드레스를 저장하기 위해 레지스터를 포함할 수 있다. 대안적으로, 변환 제어 유닛(90A)이 레지스터를 포함할 수 있거나, 레지스터(96) 내의 가장 최근의 VA를 폴트인 가상 어드레스로 덮어쓰도록 구성될 수 있다.

- [0051] 변환이 페이지 폴트로 귀결되지 않는 경우 (판정 블록(106)의 "아니오" 분기), 페치 제어 유닛(92)은 변환 제어 유닛(90A)으로부터 물리적 어드레스(PA)를 수신할 수 있고, 그 PA를 이용하여 페치 요청을 송신하도록 구성될 수 있다(블록(110)). 일부 실시예들에서, 페치 제어 유닛(92)은 변환으로부터의 PA를 보유하도록 구성될 수 있고, 페치 제어 유닛(92)이 페이지의 끝에 도달할 때까지 물리적 페이지 내의 페치들을 생성할 수 있다. 다른 실시예들에서, 페치 제어 유닛(92)은 매번 물리적 페이지 내의 페치에 대해 변환을 다시 판독할 수 있다.

- [0052] 페치 제어 유닛(92)은 페치들이 물리적 페이지의 끝에 도달한 때를 검출하도록 구성될 수 있고 (판정 블록 (112)의 "예" 분기), 변환 제어 유닛(90A)이 대응하는 변환을 무효화하고 새로운 변환을 프리페치하도록 변환 제어 유닛(90A)에 프리를 시그널링할 수 있다(블록(114)). 다른 실시예에서, 페치 제어 유닛(92)은 복수의 페이지에 대해 프리를 시그널링하기 전에 복수의 프리 페이지를 축적할 수 있다. 또 다른 실시예에서, 변환 제어 유닛(90A)은 다른 변환 프리페치 요청을 발행하기 전에 복수의 프리를 축적할 수 있다. 또한, 페치 제어 유닛(92)은 변환 및 페치 생성을 위해 다른 VA를 발행하도록 구성될 수 있다(블록(104)).

- [0053] 페치 제어 유닛(92)은 스케일 영역(76)의 페치가 완료되지 않은 경우 (판정 블록(116)의 "아니오" 분기), PA 로부터 추가의 페치들을 생성하도록 구성될 수 있다(블록(110)).

- [0054] 도 7은 페치 제어 유닛(92)의 일 실시예의 소정의 추가 동작을 도시한 흐름도이다. 도 7에서는, 이해를 쉽게하기 위해 블록들이 특정한 순서로 도시되었지만, 다른 순서들이 이용될 수 있다. 블록들은 페치 제어 유닛(92) 내에서 결합 로직에서 병렬로 수행될 수 있다. 블록들, 블록들의 조합, 및/또는 전체로서의 흐름도는 복수의 클럭 사이클에 걸쳐 파이프라인될 수 있다. 페치 제어 유닛(92)은 도 7에 도시된 동작을 구현하도록 구성될 수 있다. 변환 프리페치 요청을 수신한 것에 응답하여 (판정 블록(120)의 "예" 분기), 페치 제어 유닛(92)은 하나 이상의 페이지 테이블 엔트리를 판독하기 위한 페이지 테이블 판독 요청을 송신하도록 구성될 수 있다(블록(122)). 페이지 테이블 엔트리들은 변환 제어 유닛(90A)에 의해 프리페치된 가장 최근의 가상 어드레스에 다음으로 연속하는 가상 페이지에 대응하는 페이지 테이블 엔트리를 포함할 수 있다. 추가의 페이지 테이블 엔트리들도 물론 판독될 수 있다. 일 실시예에서, 연속적인 가상 어드레스들은 페이지 테이블들 내의 연속적인 페이지 테이블 엔트리들을 어드레싱할 수 있다. 따라서, 복수의 페이지 테이블 엔트리를 한번에 프리페치하는 것은, 가까운 장래에 변환 유닛(90)이 필요로 할 수 있는 복수의 변환을 프리페치할 수 있다.

- [0055] 다음으로 도 8을 보면, 변환 제어 유닛(90A)의 일 실시예의 특정한 동작을 설명하는 흐름도가 도시되어 있다. 도 8에서는, 이해를 쉽게 하기 위해 블록들이 특정한 순서로 도시되었지만, 다른 순서들이 이용될 수 있다. 블록들은 변환 제어 유닛(90A) 내에서 결합 로직에서 병렬로 수행될 수 있다. 블록들, 블록들의 조합, 및/또는 전체로서의 흐름도는 복수의 클럭 사이클에 걸쳐 파이프라인될 수 있다. 변환 제어 유닛(90A)은 도 8에 도시된 동작을 구현하도록 구성될 수 있다.

- [0056] 변환 제어 유닛(90A)이 페치 제어 유닛(92)으로부터 프리 표시를 수신하는 경우 (판정 블록(130)의 "예"분기), 변환 제어 유닛(90A)은 변환 버퍼(90B) 내의 하나 이상의 변환을 무효화하도록 구성될 수 있다(블록(132)). 예를 들어, 실시예에서, 변환 제어 유닛(90A)은 변환 버퍼(90B)를 FIFO로서 관리하도록 구성될 수 있다. 그러한 실시예에서, 버퍼 내의 가장 오래된 변환들은 FIFO의 테일 포인터에 있을 수 있다. 변환 제어 유닛(90A)은 그를 위한 변환이 프리페치되었던 가장 최근의 가상 페이지에 인접한(또는 그에 연속하는) 가상 페이지에 대한 변환 프리페치 요청을 생성하도록 구성될 수 있다(블록(134)). 위에서 논의된 바와 같이, 가장 최근의 가상 어드레스는 레지스터(96) 내에 있을 수 있다. 얼마나 많은 페이지가 프리인지에 따라 하나이상의 프리페치가 생성될 수 있다. 일반적으로, 변환 제어 유닛(90A)은 변환 버퍼(90B)를 채우기에 충분한 변환들을 프리페치하도록 구성될 수 있다. 변환 제어 유닛(90A)은 또한 레지스터(96) 내의 가장 최근의 가상 어드레스를 업데이트하도록 구성될 수 있다(블록(136)). 실시예에서, 변환 제어 유닛(90A)은 복수의 변환 프리페치가 발행될 준비가 될 때까지 변환 프리페치 요청들의 발행을 지연하도록 구성될 수 있다.

- [0057] 페치 제어 유닛(92)으로부터 가상 어드레스와 함께 시작 표시를 수신한 것에 응답하여(판정 블록(138)에서 "예"분기), 변환 제어 유닛(90A)은 변환 버퍼(90B)를 클리어하고, 가상 어드레스에서 시작하여 2N개의 변환을 프리페치하도록 구성될 수 있다(여기에서, N은 행 내의 타일들의 수 또는 행 내의 픽셀 블록들의 수임)(블록(140)). 또한, 변환 제어 유닛(90A)은 가장 최근 VA 레지스터(96)를 2N개의 변환 중 마지막 것에 대응하는 VA로 업데이트하도록 구성될 수 있다(블록(142)).

- [0058] 그렇지 않으면, 시작 표시가 제공되지 않은 변환 요청에 응답하여 (판정 블록(138)에서 "아니오" 분기), 변환 제어 유닛(90A)은 변환 버퍼로부터 VA를 위한 대응하는 변환을 판독하도록 구성될 수 있다(블록(144)). 변환 이 유효한 경우(판정 블록(146)에서 "예" 분기), 변환 제어 유닛(90A)은 대응하는 변환으로부터의 PA를 폐치 제어 유닛(92)에 공급하도록 구성될 수 있다(블록(148)). 변환이 유효하지 않은 경우(판정 블록(146)에서 "아니오" 분기). 변환 제어 유닛(90A)은 폐치 제어 유닛(92)에 페이지 폴트를 시그널링하도록 구성될 수 있다(블록(150)).

- [0059] 일부 실시예들에서, 변환 유닛(90)에 의해 이용되는 변환들은 유효 비트에 더하여 하나 이상의 보호/제어 속성을 포함할 수 있음에 유의해야 한다. 예를 들어, 그러한 속성들은 판독 권한 및 기입 권한을 포함할 수 있다. 판독 권한이 제공되지 않는 경우, 변환은 판독되도록 허가되지 않을 수 있다. 권한들은 권한 레벨(privilege level)에 기초할 수 있다. 속성들의 임의의 집합이 제공되고 체크될 수 있다. 체크에 통과하는 경우, PA가 공급될 수 있다. 체크에 실패하는 경우, 페이지 폴트가 시그널링될 수 있다.

- [0060] 다음으로 도 9로 가면, 메모리(12)(도 1의 실시예에서의 메모리(12A-12B)에 걸쳐 이어질 수 있음)의 일 실시 예의 블록도가 도시되어 있다. 메모리(12)는 다양한 페이지 테이블(160A-160C)을 저장할 수 있고, 그들 각각은 개별 페이지 테이블 베이스 어드레스(도 9의 PTBaseO, PTBaseO) 및 PTBaseO)에 의해 찾아질 수 있다. 각각의 페이지 테이블(160A-160B)은 변환 엔트리들의 집합을 포함할 수 있으며, 이들 각각은 본 실시예에서 메모리(12) 내의 타일의 위치를 찾을 수 있다. 따라서, 물리적 어드레스 PAO는 타일 0(162A)의 위치를 찾을 수 있고, PA2는 타일 1(162B)의 위치를 찾을 수 있는 등이다. (예를 들어, 본 실시예에서는 타일들인) 소스 버퍼(70) 내의 페이지들의 연속적인 VA들은 주어진 페이지 테이블(160A-160C) 내의 연속적인 변환들에 의해 변환될 수 있다. 페이지 테이블(160A-160B) 내의 마지막 변환이 페치될 때, 다음의 연속적인 변환은 각각 다음페이지 테이블(160B-160C) 내의 처음 변환일 수 있다.

- [0061] 이제 도 10을 보면, 시스템(350)의 일 실시예의 블록도가 도시되어 있다. 도시된 실시예에서, 시스템(350)은 외부 메모리(12)(예를 들어, 도 1의 메모리(12A-12B))에 연결된 집적 회로(10)의 적어도 하나의 인스턴스를 포함한다. 집적 회로(10)는 하나 이상의 주변장치(354) 및 외부 메모리(12)에 연결된다. 또한, 집적 회로 (10)에의 공급 전압과 메모리(12) 및/또는 주변장치들(354)에의 하나 이상의 공급 전압을 공급하는 전원(356)이 제공된다. 일부 실시예들에서, 집적 회로(10)의 둘 이상의 인스턴스가 포함될 수 있다(둘 이상의 외부 메모리(12)도 포함될 수 있음).

- [0062] 주변장치들(354)은 시스템(350)의 유형에 의존하여 임의의 요구되는 회로망을 포함할 수 있다. 예를 들어, 일 실시예에서, 시스템(350)은 이동 장치(예를 들어, PDA(personal digital assistant), 스마트폰 등)일 수 있으며, 주변장치들(354)은 wifi, 블루투스, 셀룰러, GPS(global positioning system) 등과 같은 다양한 유형의 무선 통신을 위한 장치들을 포함할 수 있다. 주변장치들(354)은 RAM 저장소, 고체 상태 저장소, 또는 디스크 저장소를 포함하는 추가의 저장소도 포함할 수 있다. 주변장치들(354)은 터치 디스플레이 스크린 또는 멀티터치 디스플레이 스크린, 키보드 또는 다른 입력 장치들, 마이크로폰, 스피커 등을 포함하는 디스플레이 스크린과 같은 사용자 인터페이스 장치들을 포함할 수 있다. 다른 실시예들에서, 시스템(350)은 임의의 유형의 컴퓨팅 시스템(예를 들어, 데스크탑 개인용 컴퓨터, 랩탑, 워크스테이션, 넷탑 등)일 수 있다.

- [0063] 본 기술분야에 숙련된 자들에게 있어서, 위의 명세서를 완전히 알게 되면, 다수의 변형 및 수정이 분명해질 것이다. 이하의 청구항들은 그러한 모든 변형 및 수정을 포괄하는 것으로 해석되도록 의도된 것이다.