(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2025-35397

(P2025-35397A)

(43)公開日 令和7年3月13日(2025.3.13)

## (51)国際特許分類

H 05 K 3/46 (2006.01)

H 01 L 23/12 (2006.01)

F I

H 05 K 3/46

H 05 K 3/46

H 01 L 23/12

Q

B

Bテーマコード(参考)

5 E 3 1 6

審査請求 未請求 請求項の数 10 O L (全27頁)

(21)出願番号 特願2023-142412(P2023-142412)

(22)出願日 令和5年9月1日(2023.9.1)(71)出願人 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74)代理人 110002147

弁理士法人酒井国際特許事務所

(72)発明者 小林 慶裕

長野県長野市小島田町80番地 新光電

気工業株式会社内

F ターム(参考) 5E316 AA22 AA32 AA43 CC08

CC09 CC10 CC32 DD17

DD24 EE01 FF04 GG15

GG17 GG28 HH01 JJ02

JJ13

## (54)【発明の名称】 配線基板、積層型配線基板及び配線基板の製造方法

## (57)【要約】

【課題】半導体素子からのノイズの拡散を抑制すること

。

【解決手段】配線基板は、第1配線構造体と、第2配線構造体とを有する。第1配線構造体は、半導体素子の搭載面及び搭載面とは反対側の裏面を有する。第2配線構造体は、第1配線構造体の裏面に形成される。第2配線構造体は、補強絶縁層と、キャビティと、電子部品と、充填樹脂層とを有する。補強絶縁層は、第1配線構造体の裏面に形成される。キャビティは、補強絶縁層を第1配線構造体の裏面の方向へ切り欠いて形成される。電子部品は、キャビティ内に位置する。充填樹脂層は、キャビティ内に充填され、電子部品を被覆する。

【選択図】図2

実施形態に係る第1配線基板の構成を示す図

**【特許請求の範囲】****【請求項 1】**

半導体素子の搭載面及び前記搭載面とは反対側の裏面を有する第1配線構造体と、前記第1配線構造体の前記裏面に形成された第2配線構造体とを有し、前記第2配線構造体は、前記第1配線構造体の前記裏面に形成された補強絶縁層と、前記補強絶縁層を前記第1配線構造体の前記裏面の方向へ切り欠いて形成されたキャビティと、前記キャビティ内に位置する電子部品と、前記キャビティ内に充填され、前記電子部品を被覆する充填樹脂層とを有することを特徴とする配線基板。

10

**【請求項 2】**

前記電子部品は、前記補強絶縁層を前記第1配線構造体の前記裏面まで切り欠いて形成された前記キャビティ内に位置するとともに、前記第1配線構造体の前記裏面上に固定されることを特徴とする請求項1に記載の配線基板。

20

**【請求項 3】**

前記電子部品は、前記補強絶縁層を前記第1配線構造体の前記裏面に到達しない位置まで切り欠いて形成された前記キャビティ内に位置するとともに、前記キャビティの底面を形成する前記補強絶縁層上に固定されることを特徴とする請求項1に記載の配線基板。

20

**【請求項 4】**

前記第2配線構造体は、複数の前記電子部品を有し、複数の前記電子部品は、前記補強絶縁層を前記第1配線構造体の前記裏面の方向へ切り欠いて形成された複数の前記キャビティ内にそれぞれ位置し、前記充填樹脂層は、複数の前記キャビティ内に充填され、複数の前記電子部品を被覆することを特徴とする請求項1に記載の配線基板。

30

**【請求項 5】**

前記第2配線構造体の厚さは、前記第1配線構造体の厚さ以上であることを特徴とする請求項1に記載の配線基板。

**【請求項 6】**

支持体をさらに有し、前記第1配線構造体は、前記搭載面が前記支持体側に向けられた状態で前記支持体上に形成されることを特徴とする請求項1に記載の配線基板。

40

**【請求項 7】**

配線基板が他の配線基板に積層された積層型配線基板であって、前記配線基板は、半導体素子の搭載面及び前記搭載面とは反対側の裏面を有する第1配線構造体と、前記第1配線構造体の前記裏面に形成された第2配線構造体とを有し、前記第2配線構造体は、前記第1配線構造体の前記裏面に形成された補強絶縁層と、前記補強絶縁層を前記第1配線構造体の前記裏面の方向へ切り欠いて形成されたキャビティと、前記キャビティ内に位置する電子部品と、

50

前記キャビティ内に充填され、前記電子部品を被覆する充填樹脂層とを有することを特徴とする積層型配線基板。

【請求項 8】

前記充填樹脂層の前記第1配線構造体とは反対側に位置する反対面に電極パッドが設けられており、

前記他の配線基板の表面に他の電極パッドが設けられており、

前記電極パッドと前記他の電極パッドとが電気的に接続され、前記配線基板が前記他の配線基板に積層されていることを特徴とする請求項7に記載の積層型配線基板。

【請求項 9】

半導体素子の搭載面及び前記搭載面とは反対側の裏面を有する第1配線構造体を形成する工程と、

前記第1配線構造体の前記裏面に第2配線構造体を形成する工程とを有し、

前記第2配線構造体を形成する工程は、

前記第1配線構造体の前記裏面に補強絶縁層を形成し、

前記補強絶縁層を前記第1配線構造体の前記裏面の方向へ切り欠いてキャビティを形成し、

形成された前記キャビティ内に電子部品を配置し、

前記キャビティ内に、前記電子部品を被覆する充填樹脂を充填することを特徴とする配線基板の製造方法。

20

【請求項 10】

前記第1配線構造体を形成する工程において、

支持体を用意し、

前記支持体上に、前記搭載面が前記支持体に接するように、前記第1配線構造体を形成することを特徴とする請求項9に記載の配線基板の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、配線基板、積層型配線基板及び配線基板の製造方法に関する。

30

【背景技術】

【0002】

従来、例えば主基板上に、微細配線を有する中継基板を積層した積層型配線基板が知られている。このような積層型配線基板では、中継基板上に半導体素子が搭載されるとともに、主基板上であって中継基板の周囲に、例えばキャパシタ等の電子部品が搭載されることがある。主基板上に搭載される電子部品は、中継基板上に搭載される半導体素子から発生するノイズを低減する機能を有する。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2001-144207号公報

40

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記の積層型配線基板においては、半導体素子からのノイズが拡散する可能性があるという問題がある。具体的には、中継基板上に搭載される半導体素子と主基板上に搭載される電子部品とが中継基板の配線及び主基板の配線を介して接続されるため、半導体素子と電子部品との間の配線の長さが大きくなり、かかる配線のインダクタンスが増加する。この結果、半導体素子からのノイズが電子部品において十分に低減されず、半導体素子の周囲に拡散する恐れがある。

【0005】

50

開示の技術は、上記に鑑みてなされたものであって、半導体素子からのノイズの拡散を抑制することができる配線基板、積層型配線基板及び配線基板の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0006】

本願の開示する配線基板は、一つの態様において、第1配線構造体と、第2配線構造体とを有する。第1配線構造体は、半導体素子の搭載面及び搭載面とは反対側の裏面を有する。第2配線構造体は、第1配線構造体の裏面に形成される。第2配線構造体は、補強絶縁層と、キャビティと、電子部品と、充填樹脂層とを有する。補強絶縁層は、第1配線構造体の裏面に形成される。キャビティは、補強絶縁層を第1配線構造体の裏面の方向へ切り欠いて形成される。電子部品は、キャビティ内に位置する。充填樹脂層は、キャビティ内に充填され、電子部品を被覆する。

10

【発明の効果】

【0007】

本願の開示する配線基板の一つの態様によれば、半導体素子からのノイズの拡散を抑制することができる、という効果を奏する。

【図面の簡単な説明】

【0008】

【図1】図1は、実施形態に係る基板の構造を示す図である。

20

【図2】図2は、実施形態に係る第1配線基板の構成を示す図である。

【図3】図3は、実施形態に係る第1配線基板の製造方法を示すフロー図である。

【図4】図4は、ガラス支持体の具体例を示す図である。

【図5】図5は、シード層形成工程の具体例を示す図である。

【図6】図6は、レジスト層形成工程の具体例を示す図である。

【図7】図7は、電極パッド形成工程の具体例を示す図である。

【図8】図8は、レジスト層除去工程の具体例を示す図である。

【図9】図9は、シード層除去工程の具体例を示す図である。

【図10】図10は、絶縁層形成工程の具体例を示す図である。

【図11】図11は、シード層形成工程の具体例を示す図である。

30

【図12】図12は、レジスト層形成工程の具体例を示す図である。

【図13】図13は、電解銅めっき工程の具体例を示す図である。

【図14】図14は、レジスト層除去工程の具体例を示す図である。

【図15】図15は、シード層除去工程の具体例を示す図である。

【図16】図16は、はんだ付加工工程の具体例を示す図である。

【図17】図17は、接着層形成工程の具体例を示す図である。

【図18】図18は、実施形態に係る基板の製造方法を示すフロー図である。

【図19】図19は、第1配線基板搭載工程の具体例を示す図である。

【図20】図20は、ガラス支持体剥離工程の具体例を示す図である。

【図21】図21は、半導体装置の構成例を示す図である。

【図22】図22は、実施形態に係る第2配線構造体の形成方法を示すフロー図である。

40

【図23】図23は、補強絶縁層形成工程の具体例を示す図である。

【図24】図24は、ビアホール形成工程の具体例を示す図である。

【図25】図25は、シード層形成工程の具体例を示す図である。

【図26】図26は、レジスト層形成工程の具体例を示す図である。

【図27】図27は、電解銅めっき工程の具体例を示す図である。

【図28】図28は、レジスト層除去工程の具体例を示す図である。

【図29】図29は、シード層除去工程の具体例を示す図である。

【図30】図30は、キャビティ形成工程の具体例を示す図である。

【図31】図31は、電子部品配置工程の具体例を示す図である。

【図32】図32は、電子部品埋め込み工程の具体例を示す図である。

50

【図33】図33は、ビアホール形成工程の具合例を示す図である。

【図34】図34は、実施形態の変形例1に係る第1配線基板の構成を示す図である。

【図35】図35は、キャビティ形成工程の具体例を示す図である。

【図36】図36は、電子部品配置工程の具体例を示す図である。

【図37】図37は、実施形態の変形例2に係る第1配線基板の構成を示す図である。

【図38】図38は、実施形態の変形例3に係る第1配線基板の構成を示す図である。

【図39】図39は、キャビティ形成工程の具体例を示す図である。

【図40】図40は、電子部品配置工程の具体例を示す図である。

【図41】図41は、実施形態の変形例4に係る第1配線基板の構成を示す図である。

【図42】図42は、凹部形成工程の具体例を示す図である。

【図43】図43は、電子部品配置工程の具体例を示す図である。

【発明を実施するための形態】

【0009】

以下に、本願の開示する配線基板、積層型配線基板及び配線基板の製造方法の実施形態を図面に基づいて詳細に説明する。なお、この実施形態により開示技術が限定されるものではない。

【0010】

(実施形態)

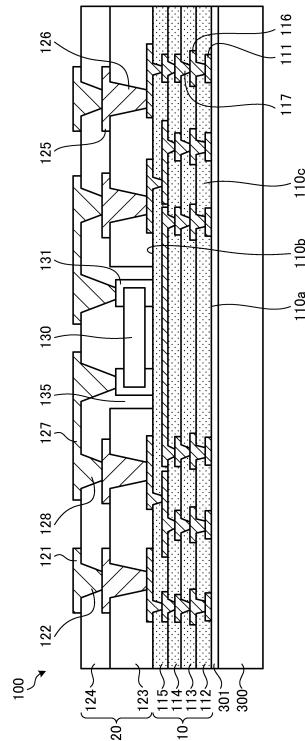

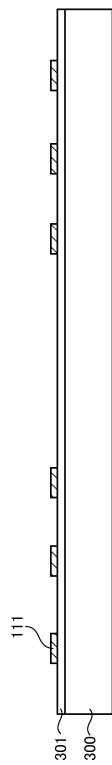

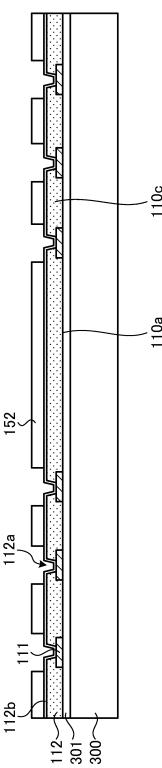

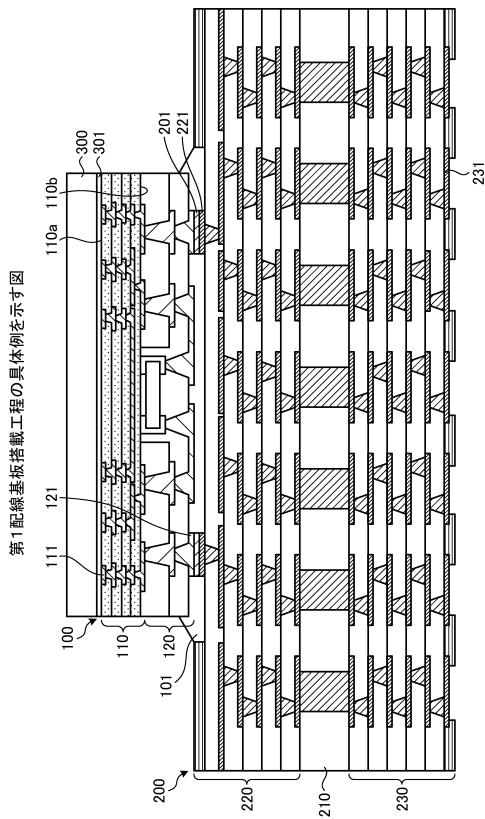

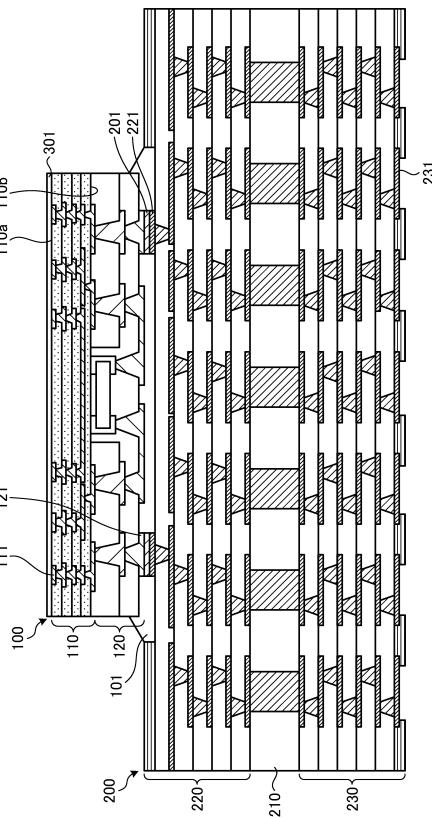

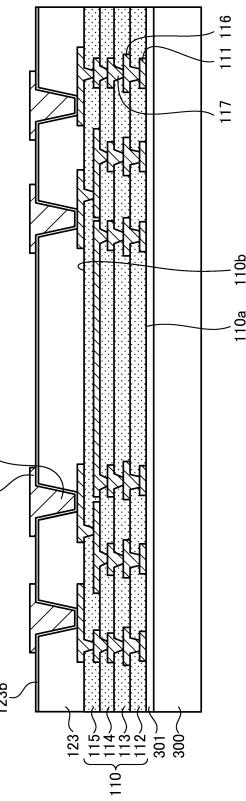

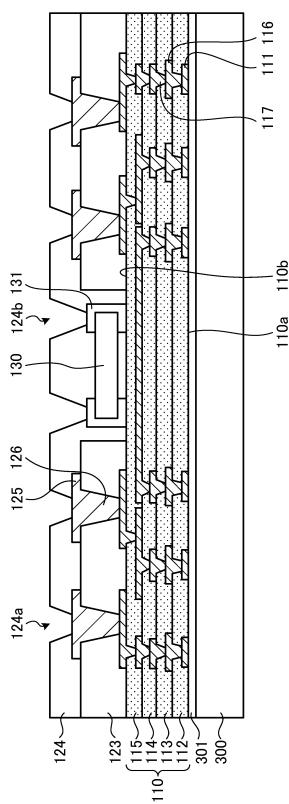

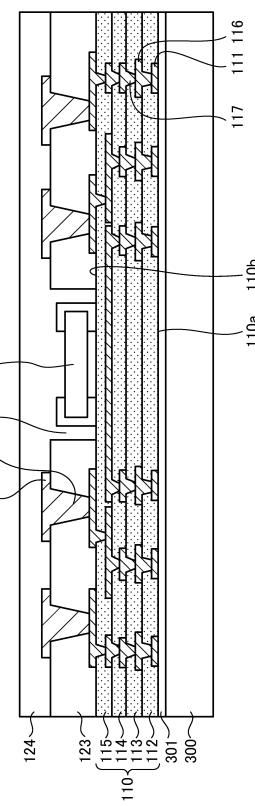

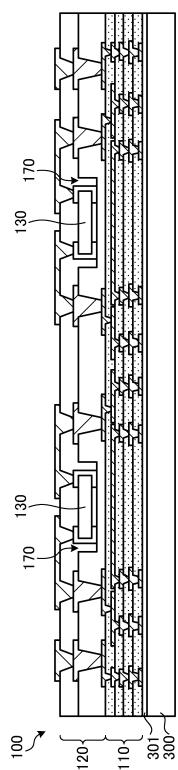

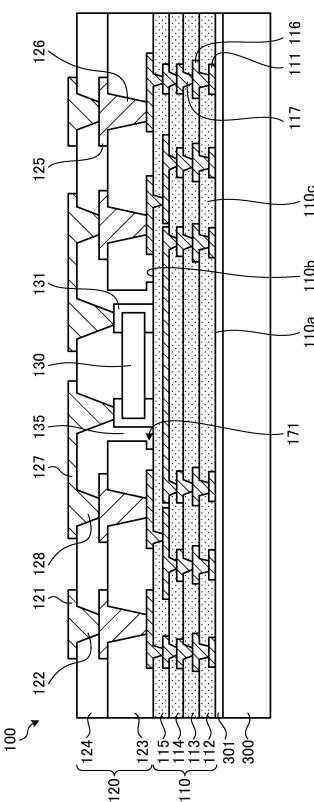

図1は、実施形態に係る基板の構造を示す図である。図1においては、実施形態に係る基板の断面を模式的に示している。図1に示す基板は、第1配線基板100が第2配線基板200に積層されてなる積層型配線基板である。以下の説明においては、図1の第2配線基板200から第1配線基板100へ向かう方向が上であり、第1配線基板100から第2配線基板200へ向かう方向が下であるものとする。しかしながら、第1配線基板100及び第2配線基板200は、例えば上下反転して製造及び使用されても良く、任意の姿勢で製造及び使用されて良い。

【0011】

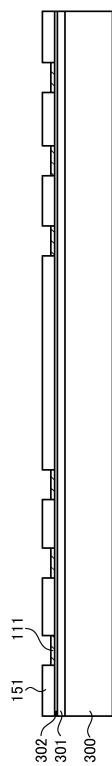

第1配線基板100は、複数の薄膜層が積層された第1配線構造体110と、基層となる第2配線構造体120とを有する中継基板である。第1配線構造体110の上面110aには、電極パッド111が形成される。電極パッド111は、例えば銅などの導電体により形成され、第1配線基板100に半導体素子が接合される際の接続端子となる。すなわち、第1配線基板100に半導体素子が接合される際には、第1配線構造体110の上面110aに半導体素子が搭載され、電極パッド111と半導体素子の電極とがはんだにより接合される。また、第2配線構造体120の下面には、電極パッド121が形成される。電極パッド121は、例えば銅などの導電体により形成され、第1配線基板100が第2配線基板200に接合される際の接続端子となる。また、電極パッド121は、第2配線構造体120内部の配線層及びビアを介して第1配線構造体110の配線と接続される。

【0012】

第2配線基板200は、コア層210と、コア層210の上面に積層されたビルドアップ層220と、コア層210の下面に積層されたビルドアップ層230とを有する主基板である。ビルドアップ層220の上面には、電極パッド221が形成され、ビルドアップ層230の下面には、電極パッド231が形成される。電極パッド221は、例えば銅などの導電体により形成され、第2配線基板200が第1配線基板100に接合される際の接続端子となる。電極パッド231は、例えば銅などの導電体により形成され、第2配線基板200がマザーボード等の外部部品に接合される際の接続端子となる。また、コア層210の内部、ビルドアップ層220の内部及びビルドアップ層230の内部には、電極パッド221と電極パッド231とを電気的に接続する配線が形成される。

【0013】

第1配線基板100は、第2配線基板200に搭載される。すなわち、第1配線基板100の接続端子である電極パッド121と第2配線基板200の接続端子である電極パッ

10

20

30

40

50

ド 2 2 1 とが、はんだ 2 0 1 により接合されている。そして、第 1 配線基板 1 0 0 の下面（つまり、第 2 配線構造体 1 2 0 の下面）と第 2 配線基板 2 0 0 の上面との間に接着層 1 0 1 が形成される。接着層 1 0 1 は、第 1 配線基板 1 0 0 の側面の一部を被覆した状態で第 1 配線基板 1 0 0 と第 2 配線基板 2 0 0 とを接着する。

【 0 0 1 4 】

このように接着層 1 0 1 及びはんだ 2 0 1 によって接合される第 1 配線基板 1 0 0 と第 2 配線基板 2 0 0 とは、別々に製造される。第 1 配線基板 1 0 0 は、例えばガラスを材料とする支持体上で製造される。すなわち、ガラス支持体上で第 1 配線構造体 1 1 0 の上面 1 1 0 a がガラス支持体側に向けられた状態で第 1 配線構造体 1 1 0 が形成され且つ第 1 配線構造体 1 1 0 の下面 1 1 0 b に第 2 配線構造体 1 2 0 が積層されることにより第 1 配線基板 1 0 0 が作製される。そして、ガラス支持体上で作製された第 1 配線基板 1 0 0 と第 2 配線基板 2 0 0 とが接着層 1 0 1 及びはんだ 2 0 1 によって接合されると、第 1 配線基板 1 0 0 からガラス支持体が剥離される。

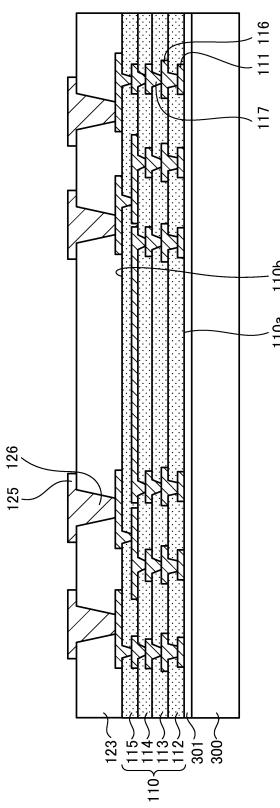

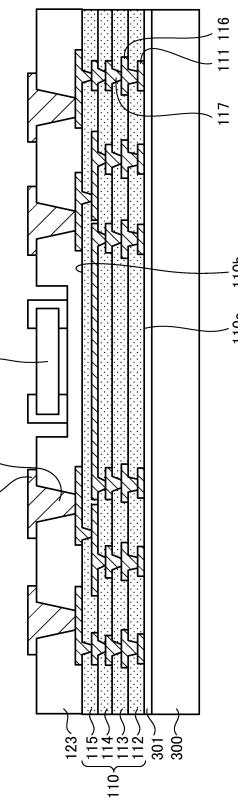

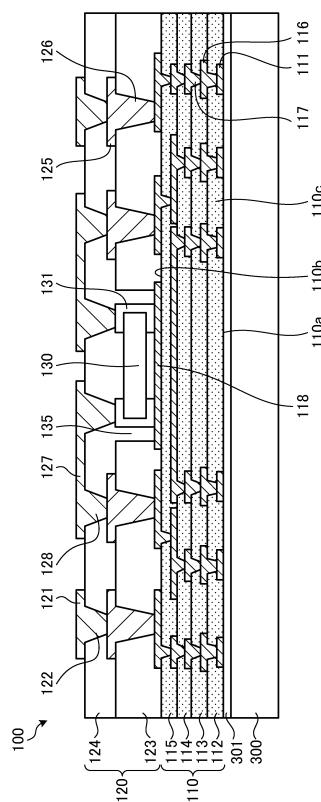

【 0 0 1 5 】

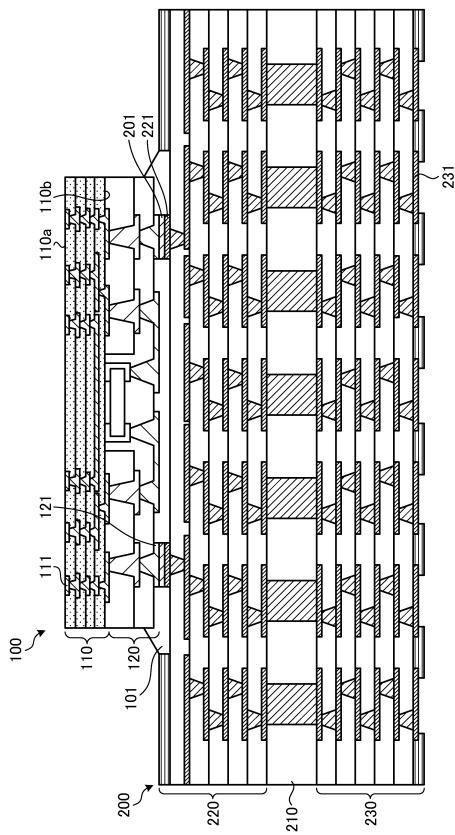

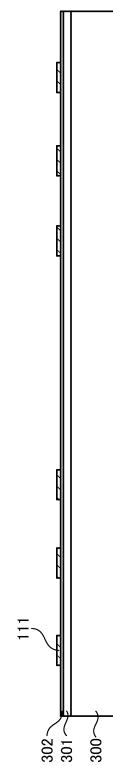

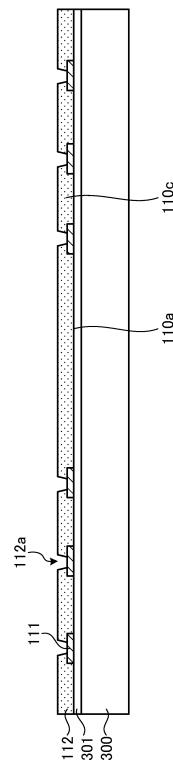

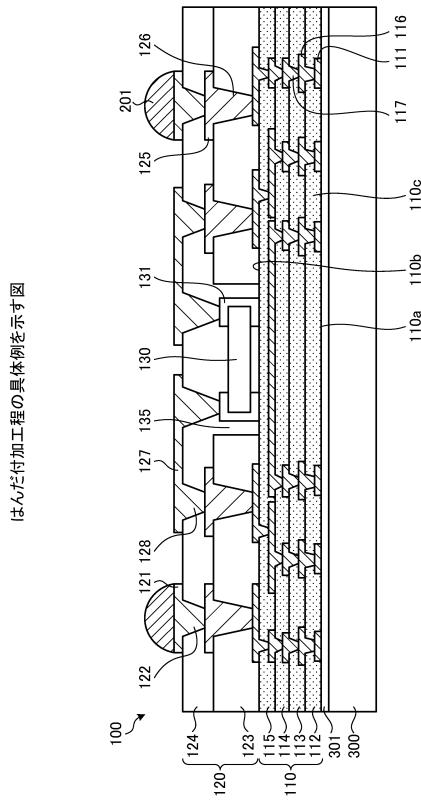

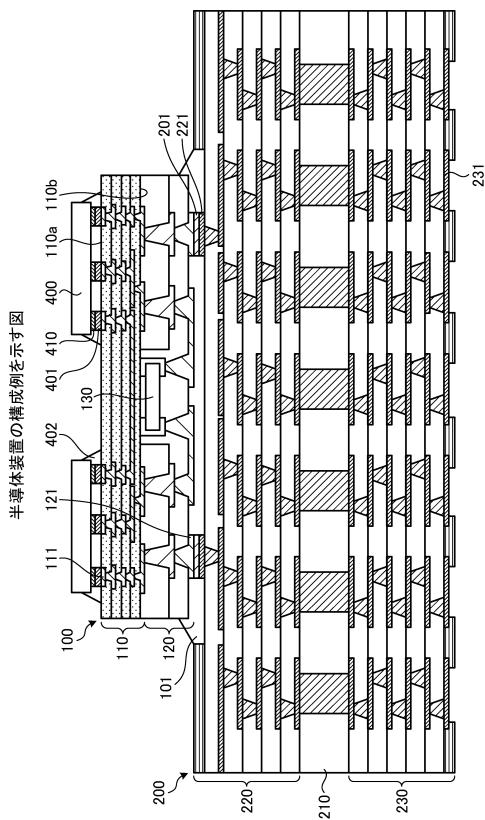

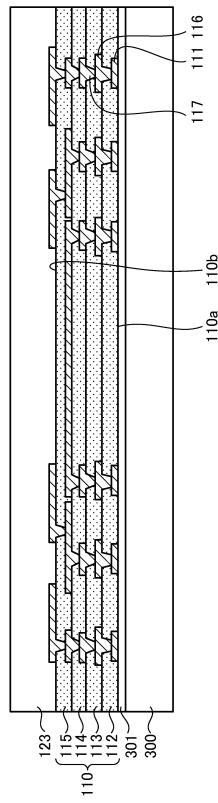

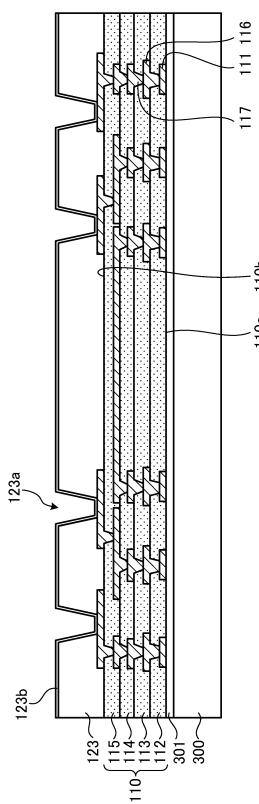

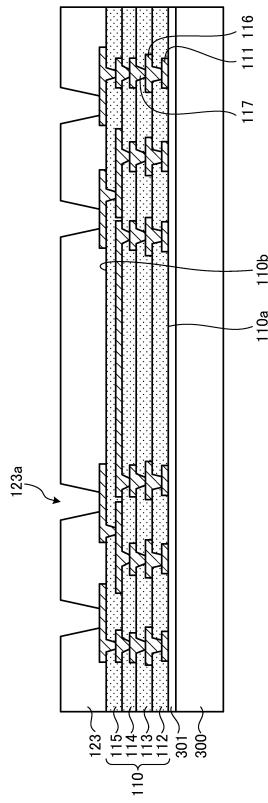

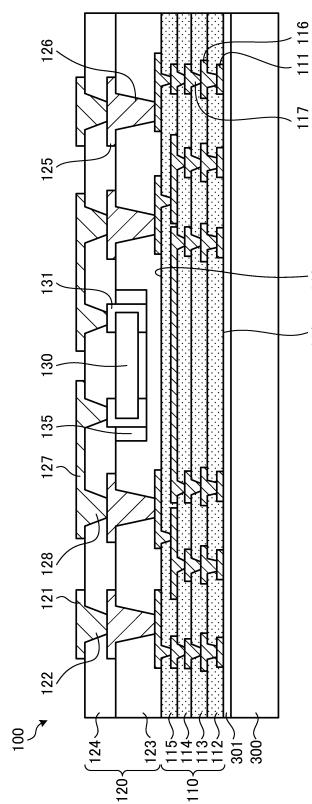

ここで、図 2 を参照して、第 1 配線基板 1 0 0 を製造する過程で形成される中間構造体の構成を説明する。図 2 は、実施形態に係る第 1 配線基板 1 0 0 の構成を示す図である。図 2 に示す第 1 配線基板 1 0 0 の中間構造体は、ガラス支持体 3 0 0 と、ガラス支持体 3 0 0 の上方に形成される第 1 配線構造体 1 1 0 と、第 1 配線構造体 1 1 0 の下面 1 1 0 b に積層される第 2 配線構造体 1 2 0 とを有する。第 1 配線構造体 1 1 0 及び第 2 配線構造体 1 2 0 は、ガラス支持体 3 0 0 上で上下反転して作成される。そして、第 2 配線構造体 1 2 0 には、電子部品 1 3 0 が埋設されている。

【 0 0 1 6 】

ガラス支持体 3 0 0 は、上面が平坦な支持体であり、この上面に剥離層 3 0 1 が形成されている。剥離層 3 0 1 としては、例えば、シリコーン系又はアクリル系の粘着性材料が用いられる。ガラス支持体 3 0 0 が剥離層 3 0 1 から剥離されることにより、第 1 配線基板 1 0 0 が得られる。ガラス支持体 3 0 0 は、例えばガラス支持体 3 0 0 上で作製された第 1 配線基板 1 0 0 と第 2 配線基板 2 0 0 とが接着層 1 0 1 及びはんだ 2 0 1 によって接合された後に、剥離層 3 0 1 から剥離される。なお、ガラス支持体 3 0 0 以外の支持体が用いられても良く、かかる支持体の材質としては、金属、シリコン、セラミック等が用いられても良い。

【 0 0 1 7 】

第 1 配線構造体 1 1 0 は、第 1 薄膜層 1 1 2 、第 2 薄膜層 1 1 3 、第 3 薄膜層 1 1 4 及び第 4 薄膜層 1 1 5 を有する、例えば厚さ 3 0 ~ 5 0  $\mu\text{m}$  程度の構造体である。ここでは、ガラス支持体 3 0 0 の上面に 4 層の薄膜層が積層されて第 1 配線構造体 1 1 0 が形成されるものとしたが、ガラス支持体 3 0 0 の上面に積層される薄膜層は 4 層でなくても良い。第 1 ~ 4 薄膜層 1 1 2 ~ 1 1 5 は、それぞれ絶縁層 1 1 0 c 上に微細配線を含む配線層 1 1 6 が形成されて構成される薄膜層である。第 1 ~ 4 薄膜層 1 1 2 ~ 1 1 5 の配線層 1 1 6 は、それぞれ絶縁層 1 1 0 c を貫通するビア 1 1 7 によって接続される。ビア 1 1 7 は、電極パッド 1 1 1 側の径が、電極パッド 1 2 1 側の径より小さい、円錐台形状に形成される。

【 0 0 1 8 】

第 1 ~ 4 薄膜層 1 1 2 ~ 1 1 5 の絶縁層 1 1 0 c は、例えば感光性の絶縁性樹脂を用いて形成される。それぞれの絶縁層 1 1 0 c の上方に微細な配線層 1 1 6 が形成される際には、絶縁層 1 1 0 c の上面にレジストが形成されてパターニング及び電解銅めっきが施される。

【 0 0 1 9 】

最下層の第 1 薄膜層 1 1 2 には、電極パッド 1 1 1 が埋設される。電極パッド 1 1 1 は、例えば銅などの導電体により形成され、第 1 配線基板 1 0 0 に半導体素子が接合される際の接続端子として用いられる。第 1 薄膜層 1 1 2 のガラス支持体 3 0 0 の上面側に位置する表面（下面）は、半導体素子の搭載面である第 1 配線構造体 1 1 0 の上面 1 1 0 a を

10

20

30

40

50

形成し、この第1配線構造体110の上面110aにおいては、電極パッド111が第1薄膜層112から露出する。電極パッド111は、第1薄膜層112の絶縁層110cを貫通するビア117によって第2薄膜層113の配線層116と接続される。

【0020】

第2配線構造体120は、補強絶縁層123及び充填樹脂層124を有する、例えば厚さ50～100μm程度の構造体である。補強絶縁層123は、ガラス繊維等の補強部材に絶縁性樹脂を含浸させて形成される。補強絶縁層123に補強部材が含まれることで、第2配線構造体120の剛性が第1配線構造体110の剛性よりも大きくなり、第1配線基板100の強度が向上する。補強絶縁層123の補強部材に含浸される絶縁性樹脂は、例えばエポキシ樹脂又はポリイミド樹脂等の熱硬化により硬化する樹脂である。補強絶縁層123の表面には、配線層125が形成される。配線層125は、補強絶縁層123を貫通するビア126によって第1配線構造体110の配線と接続される。ビア126は、電極パッド111側の径が、電極パッド121側の径より小さい、円錐台形状に形成される。補強絶縁層123には、電子部品130が埋設される。補強絶縁層123には、電子部品130を収容するためのキャビティが形成される。

10

【0021】

充填樹脂層124は、後述する電子部品埋め込み工程において、キャビティ内に充填される充填樹脂135と連続して形成される層である。充填樹脂層124の表面には、電極パッド121及び配線127が形成される。電極パッド121は、例えば銅などの導電体により形成され、第1配線基板100が第2配線基板200に接合される際の接続端子となる。配線127は、例えば銅などの導電体により形成され、電子部品130の入出力信号を伝送するための伝送配線となる。充填樹脂層124には、電子部品埋め込み工程の後にビア122、128が形成され、充填樹脂層124の表面の電極パッド121又は配線127と補強絶縁層123の表面の配線層125又は電子部品130の電極131とが接続される。ビア122、128は、電極パッド111側の径が、電極パッド121側の径より小さい、円錐台形状に形成される。充填樹脂層124は、補強絶縁層123と同様の補強部材及び絶縁性樹脂を用いて形成されてもよい。

20

【0022】

電子部品130は、例えばキャパシタ等の電子部品であり、第1配線構造体110の上面110aに搭載される半導体素子から発生するノイズを低減する機能を有する。電子部品130は、補強絶縁層123内に埋設される。すなわち、電子部品130の周囲に充填樹脂135が充填されることにより、電子部品130が第2配線構造体120に埋め込まれている。

30

【0023】

このように、実施形態では、電子部品130が第2配線構造体120に埋め込まれため、第1配線構造体110の上面110aに搭載される半導体素子と電子部品130とが中継基板である第1配線基板100の配線のみを介して接続される。すなわち、半導体素子と電子部品130とが、第1配線基板100の電極パッド111、配線層116、ビア117、配線層125、ビア126、配線127及びビア128を介して接続される。これにより、半導体素子と主基板上に搭載される電子部品とが中継基板の配線及び主基板の配線を介して接続される構造と比較して、半導体素子と電子部品130との間の配線の長さを小さくすることができ、かかる配線のインダクタンスを減少させることができる。結果として、半導体素子からのノイズを電子部品130において効率的に低減することができることから、半導体素子からのノイズの拡散を抑制することができる。

40

【0024】

また、実施形態では、電子部品130が補強部材を含む第2配線構造体120に埋め込まれる。このため、電子部品130に付与される応力に対する耐性を向上することができ、電子部品130の損傷の可能性を低減することができる。

【0025】

また、実施形態では、第2配線構造体120の厚さが第1配線構造体110以上である

50

。このため、第2配線構造体120に埋め込まれる電子部品130の部品サイズの制約を少なくすることができる。

【0026】

また、実施形態では、第1配線構造体110が、半導体素子の搭載面である上面110aがガラス支持体300側に向けられた状態でガラス支持体300上に形成される。このため、第1配線基板100の強度が増加し、第1配線基板100のハンドリング性が向上する。

【0027】

なお、図2に示すガラス支持体300は、第1配線基板100と第2配線基板200とが接合された後に、第1配線基板100から剥離されるが、ガラス支持体300を剥離するタイミングはこれに限られない。例えば、図2に示すガラス支持体300上に第1配線基板100が作成された段階において、ガラス支持体300が剥離されてもよい。

【0028】

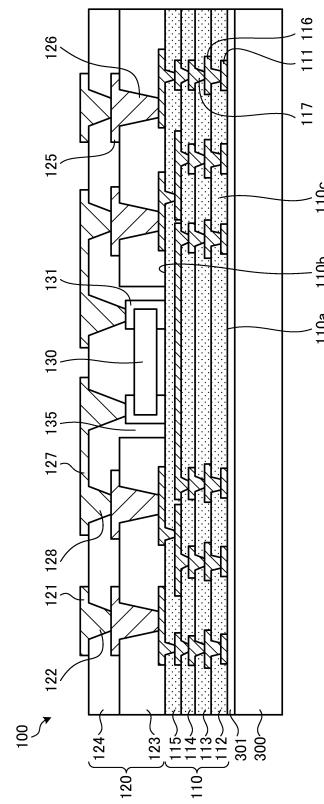

次に、図2に示す第1配線基板100を製造する製造方法について、図3に示すフロー図を参照しながら具体的に説明する。図3は、実施形態に係る第1配線基板100の製造方法を示すフロー図である。

【0029】

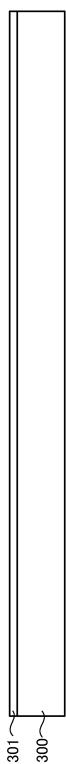

まず、第1配線基板100を製造する支持体となるガラス支持体300が準備される(ステップS101)。具体的には、例えば図4に示すように、ガラス支持体300の平坦な上面に、剥離層301が形成される。図4は、ガラス支持体300の具体例を示す図である。なお、ガラス支持体300以外の支持体が用いられても良く、かかる支持体の材質としては、金属、シリコン、セラミック等が用いられても良い。

【0030】

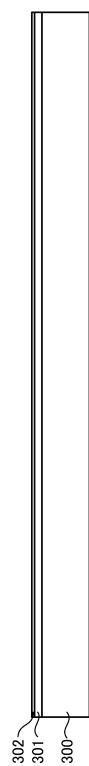

そして、例えば図5に示すように、ガラス支持体300の剥離層301の上面に、例えば銅のスパッタリングによってシード層302が形成される(ステップS102)。図5は、シード層形成工程の具体例を示す図である。

【0031】

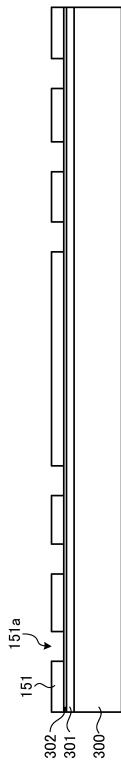

そして、例えば図6に示すように、シード層302上に開口部151aを有するレジスト層151が形成される(ステップS103)。レジスト層151は、例えばドライフィルムレジストを用いて形成されており、開口部151aは、例えばフォトリソグラフィ又はレーザ加工によって形成することが可能である。図6は、レジスト層形成工程の具体例を示す図である。

【0032】

レジスト層151が形成されると、シード層302から給電を行う電解銅めっきによって電極パッド111が形成される(ステップS104)。具体的には、例えば図7に示すように、レジスト層151の開口部151aにおいて露出するシード層302上に電極パッド111が形成される。図7は、電極パッド形成工程の具体例を示す図である。

【0033】

続いて、例えば図8に示すように、レジスト層151が除去される(ステップS105)。図8は、レジスト層除去工程の具体例を示す図である。レジスト層151の除去には、例えば苛性ソーダやアミン系のアルカリ剥離液が用いられる。

【0034】

レジスト層151が除去されると、フラッシュエッティングによりシード層302の不要な部分が除去される(ステップS106)。具体的には、シード層302を溶解するエッティング液によって、電極パッド111に接することなく露出するシード層302が溶解され、例えば図9に示すように、電極パッド111に接する部分以外では剥離層301が露出する。図9は、シード層除去工程の具体例を示す図である。なお、電極パッド111に接するシード層302は、フラッシュエッティング後も残存するが、図9においては図示を省略している。

【0035】

10

20

30

40

50

シード層 302 が除去されると、剥離層 301 上に、第 1 配線構造体 110 が形成される。まず、剥離層 301 上に、電極パッド 111 を被覆するように第 1 薄膜層 112 の絶縁層 110c が形成される（ステップ S107）。絶縁層 110c は、感光性の絶縁性樹脂を用いて形成され、フォトリソグラフィによってビアホールが形成される。具体的には、例えば図 10 に示すように、電極パッド 111 に対応する位置において、第 1 薄膜層 112 の絶縁層 110c に電極パッド 111 の上面を露出させるビアホール 112a が形成される。図 10 は、絶縁層形成工程の具体例を示す図である。第 1 薄膜層 112 のガラス支持体 300 の上面側に位置する表面（下面）は、半導体素子の搭載面である第 1 配線構造体 110 の上面 110a を形成し、この第 1 配線構造体 110 の上面 110a においては、電極パッド 111 が第 1 薄膜層 112 から露出する。

10

#### 【0036】

そして、第 1 薄膜層 112 の絶縁層 110c の表面に、例えば銅のスパッタリングによってシード層が形成される（ステップ S108）。すなわち、例えば図 11 に示すように、ビアホール 112a に露出する電極パッド 111 の表面と、ビアホール 112a 内壁を含む第 1 薄膜層 112 の絶縁層 110c の表面を被覆するシード層 112b が形成される。図 11 は、シード層形成工程の具体例を示す図である。

#### 【0037】

シード層 112b が形成されると、シード層 112b 上に、第 1 薄膜層 112 の配線層 116 を形成するためのレジスト層が形成される（ステップ S109）。すなわち、例えば図 12 に示すように、シード層 112b 上に、露光・現像を用いたパターニングによって微細配線の配線パターン形成部分に開口を設けたレジスト層 152 が形成される。図 12 は、レジスト層形成工程の具体例を示す図である。

20

#### 【0038】

レジスト層 152 が形成されると、レジスト層 152 の開口から露出するシード層 112b 上に、例えばシード層 112b から給電する電解銅めっきによって第 1 薄膜層 112 の配線層 116 及びビア 117 が形成される（ステップ S110）。具体的には、例えば図 13 に示すように、ビアホール 112a に電解銅が充填されてビア 117 が形成されるとともに、微細配線を有する配線層 116 が形成される。図 13 は、電解銅めっき工程の具体例を示す図である。

30

#### 【0039】

電解銅めっきによって第 1 薄膜層 112 の配線層 116 及びビア 117 が形成されると、例えば図 14 に示すように、レジスト層 152 が除去される（ステップ S111）。図 14 は、レジスト層除去工程の具体例を示す図である。レジスト層 152 の除去には、例えば苛性ソーダやアミン系のアルカリ剥離液が用いられる。

#### 【0040】

レジスト層 152 が除去されると、フラッシュエッチングによりシード層 112b の不要な部分が除去され（ステップ S112）、第 1 配線構造体 110 の第 1 薄膜層 112 が完成する。すなわち、例えば図 15 に示すように、配線層 116 及びビア 117 に接する部分以外のシード層 112b が除去され、絶縁層 110c、配線層 116 及びビア 117 を有する第 1 薄膜層 112 が剥離層 301 上に積層される。図 15 は、シード層除去工程の具体例を示す図である。なお、配線層 116 及びビア 117 に接するシード層 112b は、フラッシュエッチング後も残存するが、図 15 においては図示を省略している。

40

#### 【0041】

第 1 配線構造体 110 を形成する薄膜層は、複数積層されても良いため、薄膜層の積層が完了したか否かによって工程が終了するか否かが判定される（ステップ S113）。薄膜層の積層が完了していなければ（ステップ S113 N o）、上記の第 1 薄膜層 112 の形成と同様の工程が繰り返され、第 2 薄膜層 113 以降が形成される。

#### 【0042】

一方、薄膜層の積層が完了していれば（ステップ S113 Y e s）、第 1 配線構造体 110 が完成したことになり、第 1 配線構造体 110 の下面 110b に第 2 配線構造体 12

50

0が形成される（ステップS114）。すなわち、補強絶縁層123及び充填樹脂層124が第1配線構造体110の下面110b上に順に積層され、配線層125、電極パッド121及び配線127を有するとともに電子部品130が埋め込まれた第2配線構造体120が形成される。第2配線構造体120の形成工程については、後に詳述する。

#### 【0043】

第2配線構造体120が形成されると、図2に示した中間構造体が得られる。すなわち、ガラス支持体300上に第1配線構造体110及び第2配線構造体120が形成された中間構造体が形成される。第1配線構造体110及び第2配線構造体120は、第1配線基板100を構成する。

#### 【0044】

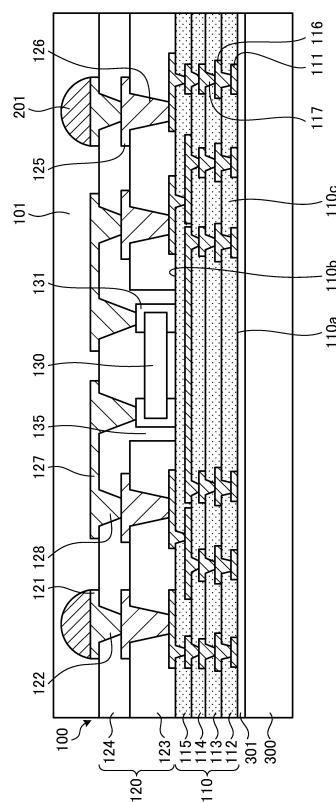

続いて、第1配線基板100を第2配線基板200に接合するために、例えば図16に示すように、第1配線基板100の電極パッド121にはんだ201が付加される（ステップS115）。図16は、はんだ付加工工程の具体例を示す図である。

#### 【0045】

第1配線基板100の電極パッド121にはんだ201が付加されると、例えば図16に示すように、電極パッド121が位置する第2配線構造体120の下面に、電極パッド121及びはんだ201を被覆する接着層101が形成される（ステップS116）。図17は、接着層形成工程の具体例を示す図である。

#### 【0046】

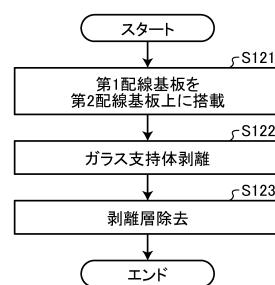

次に、図1に示す基板を製造する製造方法について、図18に示すフロー図を参照しながら具体的に説明する。図18は、実施形態に係る基板の製造方法を示すフロー図である。

#### 【0047】

まず、ガラス支持体300上で作製された第1配線基板100が接着層101を介して第2配線基板200上に搭載される（ステップS121）。具体的には、例えば図19に示すように、第1配線基板100の電極パッド121と第2配線基板200の電極パッド221とがはんだ201を介して接続するように、接着層101によって、第1配線基板100と第2配線基板200とが接着される。図19は、第1配線基板搭載工程の具体例を示す図である。

#### 【0048】

第1配線基板100と第2配線基板200とが接着層101及びはんだ201によって接合されると、例えば図20に示すように、第1配線基板100の剥離層301からガラス支持体300が剥離される（ステップS122）。図20は、ガラス支持体剥離工程の具体例を示す図である。

#### 【0049】

そして、剥離層301が除去されることにより（ステップS123）、図1に示した第1配線基板100と第2配線基板200とが積層されてなる積層型配線基板が完成する。

#### 【0050】

図1に示す積層型配線基板は、例えば半導体チップ等の半導体素子を搭載する半導体装置に利用することができる。具体的には、例えば図21に示すように、第1配線基板100の上面110aに半導体チップ400が搭載される。図21は、半導体装置の構成例を示す図である。半導体チップ400の電極410と第1配線基板100の電極パッド111とがはんだ401によって接合される。そして、電極410と電極パッド111との接合部は、アンダーフィル樹脂402によって封止される。これにより、中継基板である第1配線基板100上面にアンダーフィル樹脂402を介して半導体チップ400が搭載された半導体装置が得られる。

#### 【0051】

このような半導体装置においては、電子部品130が第2配線構造体120に埋め込まれている。このため、第1配線構造体110の上面110aに搭載される半導体チップ400と電子部品130とが中継基板である第1配線基板100の配線のみを介して接続さ

10

20

30

40

50

れる。すなわち、半導体チップ400と電子部品130とが、第1配線基板100の電極パッド111、配線層116、ビア117、配線層125、ビア126、配線127及びビア128を介して接続される。これにより、半導体チップ400と主基板上に搭載される電子部品とが中継基板の配線及び主基板の配線を介して接続される構造と比較して、半導体チップ400と電子部品130との間の配線の長さを小さくすることができ、かかる配線のインダクタンスを減少させることができる。結果として、半導体チップ400からのノイズを電子部品130において効率的に低減することができることから、半導体チップ400からのノイズの拡散を抑制することができる。

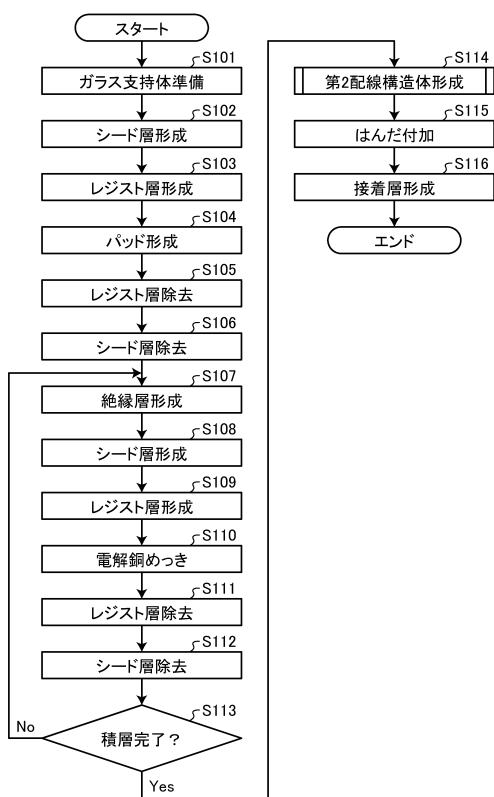

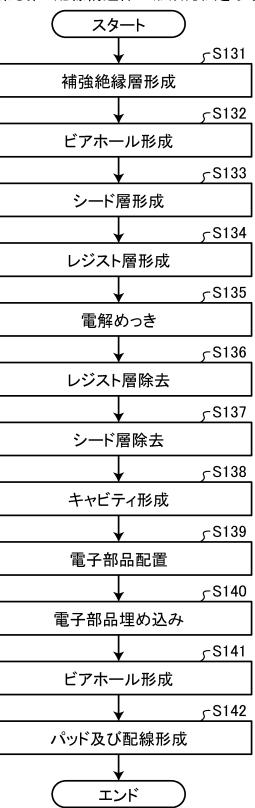

#### 【0052】

次に、第1配線基板100の第2配線構造体120の形成工程について、図22に示すフロー図を参照しながら具体的に説明する。図22は、実施形態に係る第2配線構造体120の形成方法を示すフロー図である。図22に示す第2配線構造体120の形成工程は、図3のステップS114に相当する。

#### 【0053】

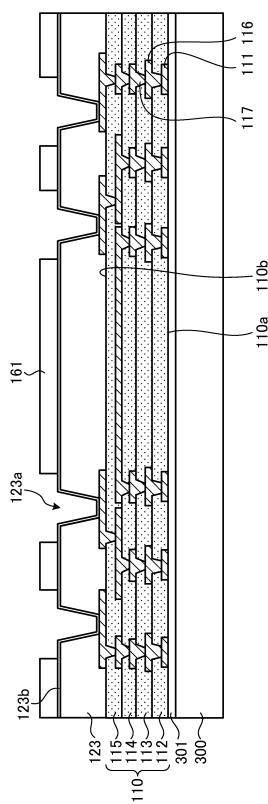

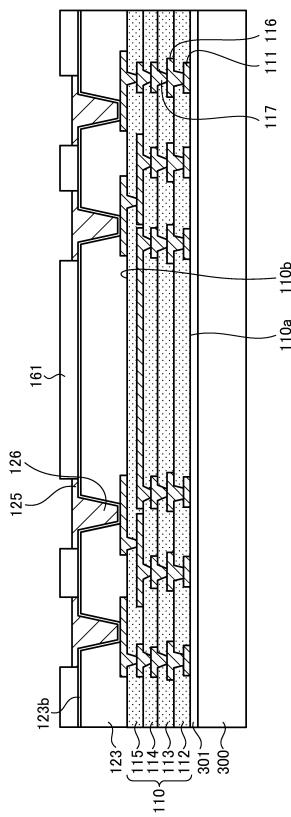

まず、第1配線構造体110の下面110bに、第1配線構造体110の最表層の配線層116を被覆する補強絶縁層123が形成される(ステップS131)。すなわち、例えば図23に示すように、第1配線構造体110の下面110bに未硬化状態の補強絶縁層123が積層され、補強絶縁層123によって配線層116が被覆される。第1配線構造体110の下面110bに形成された補強絶縁層123は熱硬化される。図23は、補強絶縁層形成工程の具体例を示す図である。

#### 【0054】

そして、補強絶縁層123にビアホールが形成される(ステップS132)。具体的には、例えば図24に示すように、補強絶縁層123を貫通し第1配線構造体110の最表層の配線層116の表面を露出させるビアホール123aが形成される。図24は、ビアホール形成工程の具体例を示す図である。ビアホール123aは、例えばレーザ加工によって形成することが可能である。レーザ加工によって発生する絶縁性樹脂の残渣物(スミア)は、デスマニア処理によって除去される。

#### 【0055】

ビアホール123aが形成されると、補強絶縁層123の表面に、例えば銅のスパッタリングによってシード層が形成される(ステップS133)。すなわち、例えば図25に示すように、ビアホール123aに露出する配線層116の表面と、ビアホール123a内壁を含む補強絶縁層123の表面を被覆するシード層123bが形成される。図25は、シード層形成工程の具体例を示す図である。

#### 【0056】

シード層123bが形成されると、シード層123b上に、配線層125を形成するためのレジスト層が形成される(ステップS134)。すなわち、例えば図26に示すように、シード層123b上に、露光・現像を用いたパターニングによって配線パターン形成部分に開口を設けたレジスト層161が形成される。図26は、レジスト層形成工程の具体例を示す図である。

#### 【0057】

レジスト層161が形成されると、レジスト層161の開口から露出するシード層123b上に、例えばシード層123bから給電を行う電解銅めっきによって配線層125及びビア126が形成される(ステップS135)。具体的には、例えば図27に示すように、ビアホール123aに電解銅めっきが充填されビア126が形成されるとともに、所定の配線パターンを有する配線層125が形成される。図27は、電解銅めっき工程の具体例を示す図である。配線層125及びビア126は、補強絶縁層123のうち電子部品130が収容される予定の領域には、配置されない。図27の例では、補強絶縁層123の中央付近の領域に電子部品130が収容される予定であるため、この領域には配線層125及びビア126が配置されていない。

#### 【0058】

10

20

30

40

50

電解銅めっきによって配線層 125 及びビア 126 が形成されると、例えば図 28 に示すように、レジスト層 161 が除去される（ステップ S136）。図 28 は、レジスト層除去工程の具体例を示す図である。レジスト層 161 の除去には、例えば苛性ソーダやアミン系のアルカリ剥離液が用いられる。

【0059】

レジスト層 161 が除去されると、フラッシュエッティングによりシード層 123b の不要な部分が除去される（ステップ S137）。具体的には、配線層 125 及びビア 126 に接することなく露出するシード層 123b が除去され、例えば図 29 に示すように、配線層 125 及びビア 126 に接する部分以外では補強絶縁層 123 が露出する。図 29 は、シード層除去工程の具体例を示す図である。なお、配線層 125 及びビア 126 に接するシード層 123b は、フラッシュエッティング後も残存するが、図 29 においては図示を省略している。

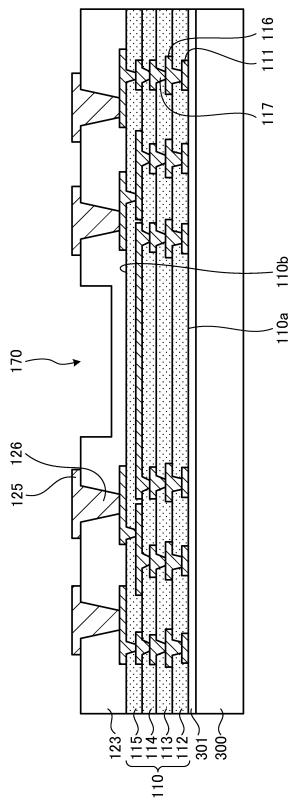

【0060】

シード層 123b が除去されると、補強絶縁層 123 のうち電子部品 130 が収容される予定の領域に、キャビティが形成される（ステップ S138）。具体的には、例えば図 30 に示すように、補強絶縁層 123 が第 1 配線構造体 110 の下面 110b の方向へ切り欠かれてキャビティ 170 が形成される。図 30 は、キャビティ形成工程の具体例を示す図である。キャビティ形成工程は、例えば CO2 レーザを用いたレーザ加工を行うことにより実現可能である。補強絶縁層 123 が第 1 配線構造体 110 の下面 110b まで切り欠かれることにより、キャビティ 170 の底面には、第 1 配線構造体 110 の下面 110b が露出する。

【0061】

そして、キャビティ 170 内に電子部品 130 が配置される（ステップ S139）。具体的には、例えば図 31 に示すように、キャビティ 170 内の第 1 配線構造体 110 の下面 110b 上に、半硬化状態の接着材（不図示）によって電子部品 130 が仮接着される。図 31 は、電子部品配置工程の具体例を示す図である。

【0062】

キャビティ 170 内に電子部品 130 が配置されると、充填樹脂 135 がキャビティ 170 内に充填され、電子部品 130 が埋め込まれる（ステップ S140）。すなわち、例えば図 32 に示すように、キャビティ 170 内に充填樹脂 135 が充填されるとともに、電子部品 130 の上方に伸展する充填樹脂層 124 が形成される。これにより、電子部品 130 が補強絶縁層 123 内に埋設される。図 32 は、電子部品埋め込み工程の具体例を示す図である。キャビティ 170 内に充填樹脂 135 が充填され充填樹脂層 124 が形成されると、これらの樹脂が熱硬化される。同時に、電子部品 130 を仮接着する接着剤も熱硬化され、電子部品 130 がキャビティ 170 内の第 1 配線構造体 110 の下面 110b 上に固定される。電子部品 130 が第 1 配線構造体 110 の下面 110b 上に固定されることにより、電子部品 130 から発生する熱が第 1 配線構造体 110 の配線層 116 を伝導して第 1 配線構造体 110 の外部に効率的に放熱される。

【0063】

そして、充填樹脂層 124 にビアホールが形成される（ステップ S141）。具体的には、例えば図 33 に示すように、充填樹脂層 124 を貫通し補強絶縁層 123 の表面の配線層 125 を露出させるビアホール 124a と、充填樹脂層 124 を貫通し電子部品 130 の電極 131 を露出させるビアホール 124b とが形成される。図 33 は、ビアホール形成工程の具体例を示す図である。ビアホール 124a、124b は、例えばレーザ加工によって形成することが可能である。

【0064】

ビアホール 124a、124b が形成された位置には、充填樹脂層 124 の表面の電極パッド 121 及び配線 127 が形成される（ステップ S142）。電極パッド 121 及び配線 127 の形成は、例えば SAP (Semi Additive Process) により行われる。電極パッド 121 及び配線 127 とともにビア 122、128 が形成され、充填樹脂層 12

4の表面の電極パッド121又は配線127と補強絶縁層123の表面の配線層125又は電子部品130の電極131とが接続される。これにより、電子部品130が埋め込まれた第2配線構造体120が完成する。

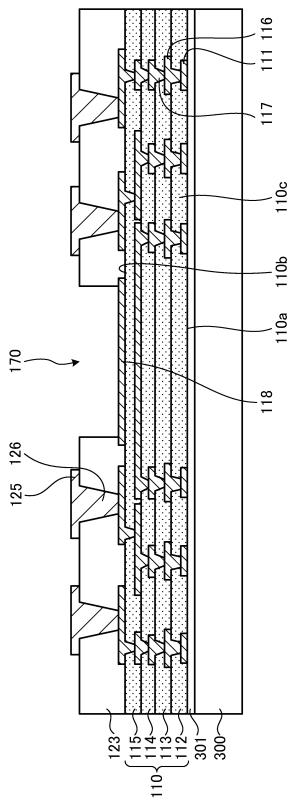

#### 【0065】

次に、実施形態の各種変形例について、図34～図43を参照しながら説明する。なお、以下に示す各種変形例では、実施形態と同一の部位には同一の符号を付することにより重複する説明を省略することがある。

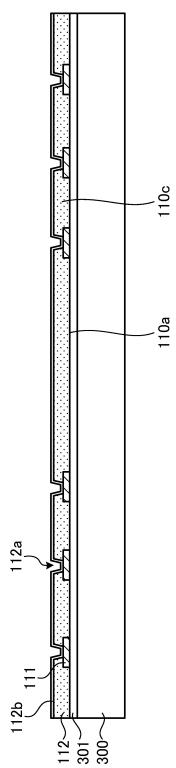

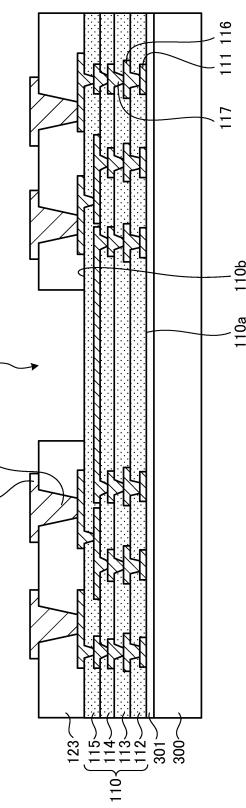

#### 【0066】

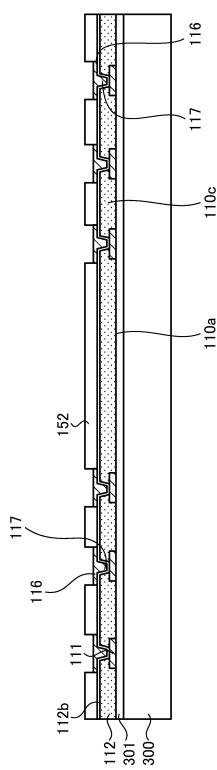

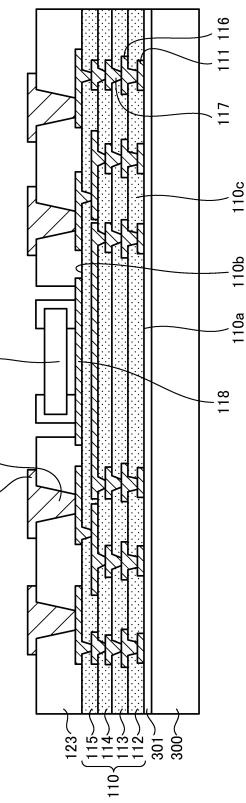

図34は、実施形態の変形例1に係る第1配線基板100の構成を示す図である。変形例1に係る第1配線基板100では、補強絶縁層123内に埋設される電子部品130の固定様式が上述の実施形態と異なる。

10

#### 【0067】

具体的には、変形例1では、補強絶縁層123のキャビティが第1配線構造体110の下面110bまで貫通しておらず、キャビティの底面が補強絶縁層123によって形成される。そして、電子部品130は、キャビティの底面を形成する補強絶縁層123上に固定される。

20

#### 【0068】

変形例1では、電子部品130がキャビティの底面を形成する補強絶縁層123上に固定されることにより、電子部品130と第1配線構造体110の下面110bとの間に補強絶縁層123を介在させることができる。このため、電子部品130に付与される応力に対する耐性をより向上することができ、電子部品130の損傷の可能性をより低減することができる。

20

#### 【0069】

続いて、実施形態の変形例1に係る第1配線基板100を製造する製造方法について、図35及び図36を参照しながら具体的に説明する。変形例1に係る第1配線基板100を製造する製造方法では、第2配線構造体120の形成工程におけるキャビティ形成工程（図22のステップS138）及び電子部品配置工程（図22のステップS139）が実施形態と異なる。図35は、キャビティ形成工程の具体例を示す図である。図36は、電子部品配置工程の具体例を示す図である。

30

#### 【0070】

シード層123bが除去されると、補強絶縁層123のうち電子部品130が収容される予定の領域に、キャビティが形成される。具体的には、例えば図35に示すように、補強絶縁層123が第1配線構造体110の下面110bに到達しない位置まで切り欠かれてキャビティ170が形成される。キャビティ170の底面は、補強絶縁層123によって形成される。

30

#### 【0071】

そして、キャビティ170内に電子部品130が配置される。具体的には、例えば図36に示すように、キャビティ170の底面に位置する補強絶縁層123上に、半硬化状態の接着材（不図示）によって電子部品130が仮接着される。そして、後の電子部品埋め込み工程において、充填樹脂層124の熱硬化と同時に、電子部品130を仮接着する接着剤も熱硬化され、電子部品130がキャビティ170の底面に位置する補強絶縁層123上に固定される。電子部品130がキャビティ170の底面に位置する補強絶縁層123上に固定されることにより、電子部品130と第1配線構造体110の下面110bとの間に補強絶縁層123が介在し、電子部品130に付与される応力に対する耐性がより向上する。この後、図22のステップ140以降の工程が施され、変形例1の第1配線基板100が完成する。

40

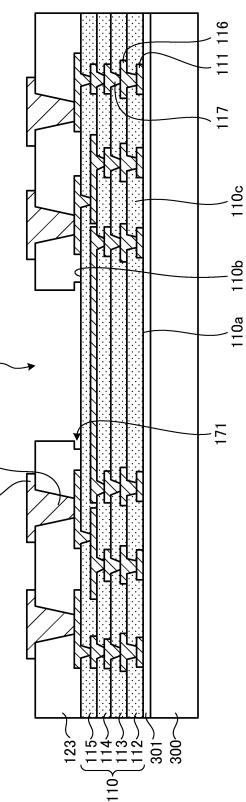

#### 【0072】

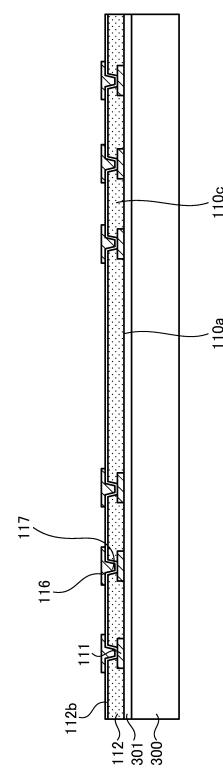

図37は、実施形態の変形例2に係る第1配線基板100の構成を示す図である。実施形態の変形例2に係る第1配線基板100では、第2配線構造体120に複数の電子部品130が埋め込まれる点が上述の変形例1と異なる。

50

## 【0073】

具体的には、変形例2では、第2配線構造体120の補強絶縁層123に複数のキャビティ170が形成され、複数の電子部品130が複数のキャビティ170内にそれぞれ位置する。そして、第2配線構造体120の充填樹脂層124が、複数のキャビティ170内に充填され、複数の電子部品130を被覆する。これにより、複数の電子部品130が第2配線構造体120に埋め込まれる。

## 【0074】

このように、変形例2では、複数の電子部品130が第2配線構造体120に埋め込まれるため、半導体素子からのノイズを複数の電子部品130において効率的に低減することができるところから、半導体素子からのノイズの拡散をより抑制することができる。

10

## 【0075】

図38は、実施形態の変形例3に係る第1配線基板100の構成を示す図である。変形例3に係る第1配線基板100では、補強絶縁層123内に埋設される電子部品130の固定様が上述の実施形態と異なる。

## 【0076】

具体的には、変形例3では、第1配線構造体110の最表層の配線層116にパッド118が形成されるとともに、補強絶縁層123のキャビティがパッド118まで到達している。なお、パッド118は、配線層116の形成時に、パッド118の形状に対応する開口を有するレジストを用いることにより、形成することが可能である。そして、電子部品130は、補強絶縁層123のキャビティの底面から露出するパッド118上に固定される。

20

## 【0077】

変形例3では、電子部品130が配線層116のパッド118上に固定されることにより、電子部品130から発生する熱が第1配線構造体110の配線層116を伝導して第1配線構造体110の外部に効率的に放熱される。

## 【0078】

続いて、実施形態の変形例3に係る第1配線基板100を製造する製造方法について、図39及び図40を参照しながら具体的に説明する。変形例3に係る第1配線基板100を製造する製造方法では、第2配線構造体120の形成工程におけるキャビティ形成工程(図22のステップS138)及び電子部品配置工程(図22のステップS139)が実施形態と異なる。図39は、キャビティ形成工程の具体例を示す図である。図40は、電子部品配置工程の具体例を示す図である。なお、図39において、キャビティ形成工程を形成する工程を行う前に、第1配線構造体110の最表層の配線層116には、パッド118が形成されているものとする。

30

## 【0079】

シード層123bが除去されると、補強絶縁層123のうち電子部品130が収容される予定の領域に、キャビティが形成される。具体的には、例えば図39に示すように、補強絶縁層123がパッド118まで切り欠かれてキャビティ170が形成される。キャビティ形成工程は、例えばCO2レーザを用いたレーザ加工を行うことにより実現可能である。レーザ加工においてはパッド118がレーザ光に対するストップ層として機能するため、底面が平坦なキャビティ170が得られる。キャビティ170の底面には、パッド118が露出する。パッド118は、キャビティ170の底面の平面形状よりもサイズが大きい平面形状(例えば、長方形)を有する。したがって、パッド118の側面は、キャビティ170の側面よりも外側に位置している。

40

## 【0080】

そして、キャビティ170内に電子部品130が配置される。具体的には、例えば図40に示すように、キャビティ170の底面に位置するパッド118上に、半硬化状態の接着材(不図示)によって電子部品130が仮接着される。そして、後の電子部品埋め込み工程において、充填樹脂層124の熱硬化と同時に、電子部品130を仮接着する接着剤も熱硬化され、電子部品130がキャビティ170の底面に位置するパッド118上に固

50

定される。電子部品 130 が配線層 116 のパッド 118 上に固定されることにより、電子部品 130 から発生する熱が第 1 配線構造体 110 の配線層 116 を伝導して第 1 配線構造体 110 の外部に効率的に放熱される。この後、図 22 のステップ 140 以降の工程が施され、変形例 3 の第 1 配線基板 100 が完成する。

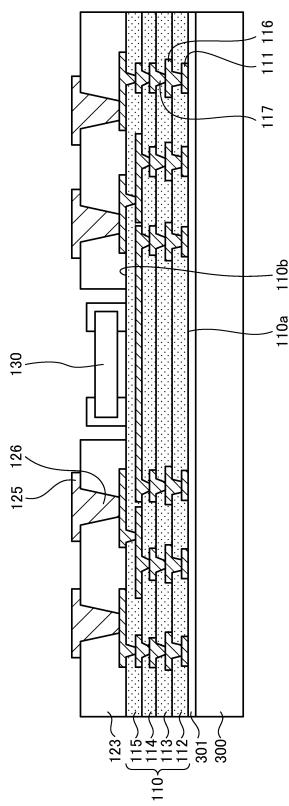

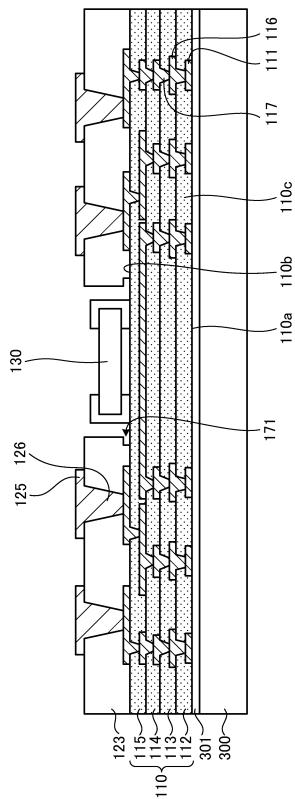

【0081】

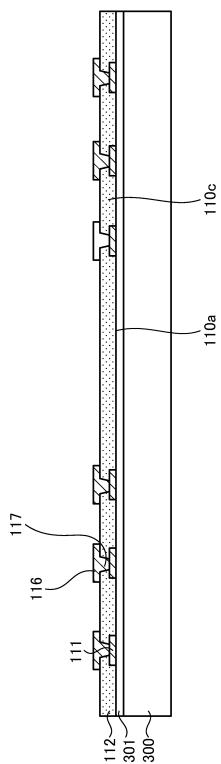

図 41 は、実施形態の変形例 4 に係る第 1 配線基板 100 の構成を示す図である。変形例 4 に係る第 1 配線基板 100 では、補強絶縁層 123 のキャビティの構造及び充填樹脂層 124 の構造が上述の実施形態と異なる。

【0082】

具体的には、変形例 4 では、補強絶縁層 123 のキャビティの側面が、キャビティの底面に隣接する位置に凹部 171 を有する。そして、充填樹脂層 124 の一部がキャビティの凹部 171 に格納される。

【0083】

変形例 4 では、充填樹脂層 124 の一部がキャビティの凹部 171 に格納されることにより、アンカー効果によって充填樹脂層 124 と補強絶縁層 123 のキャビティとの密着性を向上することができる。

【0084】

続いて、実施形態の変形例 4 に係る第 1 配線基板 100 を製造する製造方法について、図 42 及び図 43 を参照しながら具体的に説明する。変形例 4 に係る第 1 配線基板 100 を製造する製造方法では、キャビティ形成工程と電子部品配置工程との間に、凹部形成工程を含む点が変形例 3 と異なる。さらに、変形例 4 に係る第 1 配線基板 100 を製造する製造方法では、電子部品配置工程が変形例 3 と異なる。図 42 は、凹部形成工程の具体例を示す図である。図 43 は、電子部品配置工程の具体例を示す図である。

【0085】

補強絶縁層 123 にパッド 118 まで到達するキャビティ 170 が形成されると（図 39 参照）、キャビティ 170 の側面に凹部 171 が形成される。具体的には、パッド 118 がエッティングにより除去されることにより、例えば図 42 に示すように、キャビティ 170 の側面に凹部 171 が形成される。キャビティ 170 の底面には、第 1 配線構造体 110 の下面 110b が露出する。

【0086】

そして、キャビティ 170 内に電子部品 130 が配置される。具体的には、例えば図 43 に示すように、キャビティ 170 内の第 1 配線構造体 110 の下面 110b 上に、半硬化状態の接着材（不図示）によって電子部品 130 が仮接着される。そして、後の電子部品埋め込み工程において、充填樹脂層 124 の熱硬化と同時に、電子部品 130 を仮接着する接着剤も熱硬化され、電子部品 130 がキャビティ 170 内の第 1 配線構造体 110 の下面 110b 上に固定される。また、電子部品埋め込み工程において、充填樹脂層 124 の一部がキャビティの凹部 171 に格納されることにより、アンカー効果によって充填樹脂層 124 と補強絶縁層 123 のキャビティ 170 との密着性を向上することができる。この後、図 22 のステップ 140 以降の工程が施され、変形例 4 の第 1 配線基板 100 が完成する。

【0087】

以上のように、実施形態に係る配線基板（一例として、第 1 配線基板 100）は、第 1 配線構造体（一例として、第 1 配線構造体 110）と、第 2 配線構造体（一例として、第 2 配線構造体 120）とを有する。第 1 配線構造体は、半導体素子の搭載面（一例として、上面 110a）及び搭載面とは反対側の裏面（一例として、下面 110b）を有する。第 2 配線構造体は、第 1 配線構造体の裏面に形成される。第 2 配線構造体は、補強絶縁層（一例として、補強絶縁層 123）と、電子部品（一例として、電子部品 130）と、充填樹脂層（一例として、充填樹脂層 124）とを有する。補強絶縁層は、第 1 配線構造体の裏面に形成される。電子部品は、補強絶縁層を第 1 配線構造体の裏面の方向へ切り欠いて形成されたキャビティ（一例として、キャビティ 170）内に位置する。充填樹脂層は

10

20

30

40

50

、キャビティ内に充填され、電子部品を被覆する。これにより、半導体素子からのノイズの拡散を抑制することができる。

【符号の説明】

【0088】

100 第1配線基板

110 第1配線構造体

110a 上面

110b 下面

112 第1薄膜層

113 第2薄膜層

114 第3薄膜層

115 第4薄膜層

116 配線層

120 第2配線構造体

123 補強絶縁層

124 充填樹脂層

130 電子部品

170 キャビティ

200 第2配線基板

300 ガラス支持体

10

20

30

40

50

実施形態に係る基板の構造を示す図

実施形態に係る第1配線基板の構成を示す図

【図面】

【図1】

【図2】

【図3】

実施形態に係る第1配線基板の製造方法を示すフロー図

【図4】

ガラス支持体の具体例を示す図

10

20

30

40

【図5】

シード層形成工程の具体例を示す図

【図6】

レジスト層形成工程の具体例を示す図

50

【図7】

電極ハンド形成工程の具体例を示す図

【図9】

シード層除去工程の具体例を示す図

【図8】

レジスト層除去工程の具体例を示す図

【図10】

絶縁層形成工程の具体例を示す図

10

20

30

40

50

【 図 1 1 】

### シートド層形成工程の具体例を示す図

【 図 1 2 】

## レジスト層形成工程の具体例を示す図

【 図 1 3 】

図2-1-2 電解銅めつき工程の具体例を示す

【 図 1 4 】

### ジスト層除去工程の具体例を示す図

【図15】

シード層除去工程の具体例を示す図

【図16】

10

20

30

40

【図17】

接着層形成工程の具体例を示す図

【図18】

実施形態に係る基板の製造方法を示すフロー図

50

【図 19】

第1配線基板搭載工程の具体例を示す図

【図 20】

10

20

30

40

【図 21】

半導体装置の構成例を示す図

【図 22】

実施形態に係る第2配線構造体の形成方法を示すフロー図

50

【図 2 3】

補強絶縁層形成工程の具体例を示す図

【図 2 5】

シート層形成工程の具体例を示す図

【図 2 4】

ビアホール形成工程の具体例を示す図

【図 2 6】

レジスト層形成工程の具体例を示す図

10

20

30

40

50

【図 2 7】

電解鍍めつき工程の具体例を示す図

【図 2 8】

レジスト層除去工程の具体例を示す図

【図 2 9】

シード層除去工程の具体例を示す図

【図 3 0】

キャビティ形成工程の具体例を示す図

10

20

30

40

50

【図 3 1】

電子部品配置工程の具体例を示す図

【図 3 3】

ピアホール形成工程の具体例を示す図

【図 3 2】

電子部品埋め込み工程の具体例を示す図

【図 3 4】

実施形態の変形例1に係る第1配線基板の構成を示す図

10

20

30

40

50

【図 3 5】

キャビティ形成工程の具体例を示す図

【図 3 7】

実施形態の変形例2に係る第1配線基板の構成を示す図

【図 3 6】

電子部品配置工程の具体例を示す図

10

20

30

40

【図 3 8】

実施形態の変形例3に係る第1配線基板の構成を示す図

50

【図39】

## キャビティ形成工程の具体例を示す図

【 図 4 1 】

実施形態の変形例4に係る第1配線基板の構成を示す図

【図40】

## 電子部品配置工程の具体例を示す図

【 図 4 2 】

## 凹部形成工程の具体例を示す図

【 図 4 3 】

## 電子部品配置工程の具体例を示す図

10

20

30

40

50