(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5493009号

(P5493009)

(45) 発行日 平成26年5月14日(2014.5.14)

(24) 登録日 平成26年3月7日(2014.3.7)

(51) Int.Cl.

F 1

H01L 21/027 (2006.01)

H01L 21/30 514 A

H01L 27/11 (2006.01)

H01L 21/30 570

H01L 21/8244 (2006.01)

H01L 27/10 381

請求項の数 18 (全 24 頁)

(21) 出願番号 特願2012-538886 (P2012-538886)

(86) (22) 出願日 平成22年11月9日 (2010.11.9)

(65) 公表番号 特表2013-511153 (P2013-511153A)

(43) 公表日 平成25年3月28日 (2013.3.28)

(86) 國際出願番号 PCT/US2010/055977

(87) 國際公開番号 WO2011/059961

(87) 國際公開日 平成23年5月19日 (2011.5.19)

審査請求日 平成25年10月15日 (2013.10.15)

(31) 優先権主張番号 12/617,429

(32) 優先日 平成21年11月12日 (2009.11.12)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVICES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンノイベイル、ビィ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・プレイス、メイル・ストップ

・68 (番地なし)

(74) 代理人 100108833

弁理士 早川 裕司

(74) 代理人 100111615

弁理士 佐野 良太

最終頁に続く

(54) 【発明の名称】設計規則違反を低減するために多重露光及び遮断マスクの手法を用いる半導体デバイス製造

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体デバイス構造上にデバイス特徴部を作製する方法であって、

第1の要素フォトリソグラフィマスクによって規定されるネガティブなフォトレジスト特徴部の第1のパターンであって、先端・先端間及び先端・線間の設計規則違反が無い、

ネガティブなフォトレジスト特徴部の第1のパターンを前記半導体デバイス構造の目標材質の上に作製することと、

第2の要素フォトリソグラフィマスクによって規定されるネガティブなフォトレジスト特徴部の第2のパターンであって、先端・先端間及び先端・線間の設計規則違反が無い、

ネガティブなフォトレジスト特徴部の第2のパターンであって、ネガティブなフォトレジスト特徴部の前記第1のパターンと共に、ネガティブなフォトレジスト特徴部の、先端・先端間及び先端・線間の設計規則違反の無い結合されたパターンを形成する、ネガティブなフォトレジスト特徴部の第2のパターンを前記目標材質の上に作製することと、

ネガティブなフォトレジスト特徴部の前記結合されたパターンをエッチングマスクとして用いて前記目標材質を選択的にエッチングすることによって前記目標材質内に凹部線パターンを形成することと、

前記目標材質を選択的にエッチングした後に、前記凹部線パターンの指定された区画と交差し且つ当該区画を覆う、ポジティブなフォトレジスト特徴部の第3のパターンであって、先端・先端間及び先端・線間の設計規則違反が無い、ポジティブなフォトレジスト特徴部の第3のパターンを形成することと、を備える方法。

**【請求項 2】**

前記目標材質は第 2 の材質の層の上に形成され、

前記目標材質を選択的にエッチングすることは、前記第 2 の材質の一部を露出させ、

ポジティブなフォトレジスト特徴部の前記第 3 のパターンは前記第 2 の材質の露出させられた部分上に形成される請求項 1 の方法。

**【請求項 3】**

前記目標材質及びポジティブなフォトレジスト特徴部の前記第 3 のパターンを第 2 のエッチングマスクとして用いて前記第 2 の材質を選択的にエッチングすることによって前記第 2 の材質内に溝を形成することを更に備える請求項 2 の方法。

**【請求項 4】**

前記溝を電気伝導性材質で少なくとも部分的に埋めることを更に備える請求項 3 の方法

。

**【請求項 5】**

前記溝の少なくとも 1 つは二方向的である請求項 3 の方法。

**【請求項 6】**

半導体デバイスを製造する方法であって、

半導体材質の層及び半導体材質の前記層の上の絶縁材質の層を備える半導体デバイス構造を提供することと、

絶縁材質の前記層の上にハードマスク材質の層を形成することと、

第 1 のフォトリソグラフィマスクを用いて形成される第 1 のネガティブなフォトレジスト特徴部と、第 2 のフォトリソグラフィマスクを用いて形成される第 2 のネガティブなフォトレジスト特徴部とを備える、ネガティブなフォトレジスト特徴部の結合されたパターンをハードマスク材質(408)の前記層の上に作製することであって、前記第 1 のネガティブなフォトレジスト特徴部、前記第 2 のネガティブなフォトレジスト特徴部及びネガティブなフォトレジスト特徴部の前記結合されたパターンの各々は、先端・先端間及び先端・線間の設計規則違反が無いことと、

ネガティブなフォトレジスト特徴部の前記結合されたパターンをエッチングマスクとして用いてハードマスク材質の前記層を選択的にエッチングすることによってポジティブハードマスクパターン及びネガティブ凹部線パターンを前記ハードマスク材質内に規定することと、

ハードマスク材質の前記層を選択的にエッチングした後に、前記ネガティブ凹部線パターン内に規定される 1 つ以上の凹部線と交差し且つ当該凹部線を覆うポジティブなフォトレジスト特徴部のパターンであって、先端・先端間及び先端・線間の設計規則違反が無い、ポジティブなフォトレジスト特徴部のパターンを前記絶縁材質の上に作製することと、を備える方法。

**【請求項 7】**

前記ポジティブハードマスクパターン及び前記ポジティブなフォトレジスト特徴部を第 2 のエッチングマスクとして用いて前記絶縁材質を選択的にエッチングすることによって前記絶縁材質内に溝を形成することを更に備える請求項 6 の方法。

**【請求項 8】**

前記ポジティブハードマスクパターンを前記半導体デバイス構造から除去することと、

前記ポジティブなフォトレジスト特徴部を前記半導体デバイス構造から除去することと、を更に備える請求項 7 の方法。

**【請求項 9】**

前記溝内に電気伝導性材質を堆積させることを更に備える請求項 8 の方法。

**【請求項 10】**

前記溝の少なくとも 1 つは二方向的である請求項 7 の方法。

**【請求項 11】**

半導体デバイスを製造する方法であって、

半導体材質の層と、前記半導体材質の層の上の絶縁材質の層とを備える基板にハードマ

10

20

30

40

50

スク材質の層を形成することであって、前記ハードマスク材質の層を前記絶縁材質の層の上に形成することと、

ネガティブなフォトレジスト特徴部の、先端・先端間及び先端・線間の設計規則違反の無い結合されたパターンを前記ハードマスク材質の層の上に生成するために、多重露光フォトリソグラフィ手順を実行することと、

ネガティブなフォトレジスト特徴部の前記結合されたパターンによって規定される凹部線パターンを前記ハードマスク材質に形成することと、

前記凹部線パターンの指定された区画を、先端・先端間及び先端・線間の設計規則違反の無い、ポジティブなフォトレジスト特徴部の遮断パターンで覆うことと、

ポジティブなフォトレジスト特徴部の前記遮断パターンと、前記ハードマスク材質の前記凹部線パターンとによって規定される溝のパターンを前記絶縁材質に形成することと、

前記溝内に電気伝導性材質を堆積させることによって、半導体デバイス用の導電線を形成することと、を備える方法。

**【請求項 1 2】**

前記凹部線パターンを形成することは、ネガティブなフォトレジスト特徴部の前記結合されたパターンをエッチングマスクとして用いて、前記ハードマスク材質の層をエッチングすることを備える請求項 1 1 の方法。

**【請求項 1 3】**

前記溝のパターンを形成することは、ポジティブなフォトレジスト特徴部の前記遮断パターンと前記ハードマスク材質とをエッチングマスクとして用いて、前記絶縁材質の層をエッチングすることを備える請求項 1 1 の方法。

**【請求項 1 4】**

前記溝のパターンを形成することは、ポジティブなフォトレジスト特徴部の前記遮断パターンと前記ハードマスク材質とをエッチングマスクとして用いて、前記絶縁材質の層の下の絶縁材質の第 2 の層をエッチングすることを更に備える請求項 1 3 の方法。

**【請求項 1 5】**

前記溝のパターンを形成することは、前記半導体デバイスのトランジスタゲート構造で終了する少なくとも 1 つの溝を形成することを備える請求項 1 1 の方法。

**【請求項 1 6】**

前記溝のパターンを形成することは、前記半導体デバイスの活性トランジスタ領域で終了する少なくとも 1 つの溝を形成することを備える請求項 1 1 の方法。

**【請求項 1 7】**

前記溝のパターンを形成することは、前記絶縁材質の層の下の絶縁材質の第 2 の層で終了する少なくとも 1 つの溝を形成することを備える請求項 1 1 の方法。

**【請求項 1 8】**

前記凹部線パターンを形成することは、二方向的な凹部線のパターンを形成することを備える請求項 1 1 の方法。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

本出願の主題は、本出願と同時に出願された同時係属中の米国特許出願番号 1 2 / 6 1 7 , 4 2 1 の主題に関連している。

**【0 0 0 2】**

ここに説明される主題の実施形態は、概して半導体デバイス製造の技法及び技術(techniques and technologies)に関する。より特定的には、主題の実施形態は、半導体デバイスの製造に際しての設計規則違反を低減するためのフォトリソグラフィマスクの設計、作製、及び使用に関する。

**【背景技術】**

**【0 0 0 3】**

半導体産業は、より高い機能を達成し且つ製造コストを低減するために、より小さいチ

10

20

30

40

50

ツプ区域上のますます高密度になっている半導体デバイスで集積回路を製造することを目指している。大規模な集積化に対するこの要望は、回路寸法及びデバイス特徴部(circuit dimensions and device features)の継続的な縮小をもたらしてきた。電界効果トランジスタにおけるゲート長、及び導電線の幅、等の構造のサイズを低減する能力は、リソグラフィ性能によって推進される。

#### 【0004】

従来のフォトリソグラフィシステムでは、マスク又はレチクル(reticle)での透過又は反射を介して放射がもたらされて、半導体ウエハ上に像を形成する。一般に、像はウエハ上で結像し、フォトレジスト材質等の材質の層を露光してパターニングする。フォトレジスト材質は次いで、半導体ウエハの1つ以上の層におけるドープ領域、堆積領域、エッチング領域、又は他の構造及び特徴部を規定するために用いられる。フォトレジスト材質はまた、半導体デバイスの金属層に関連する導電線又は導電パッドを規定することもできる。更に、フォトレジスト材質は、分離領域、トランジスタゲート、又は他のトランジスタ構造及び要素を規定することができる。

#### 【0005】

極めて小型で且つ高密度にパッキングされた特徴部のフォトレジストパターンを形成するため、2つ以上のフォトリソグラフィサブプロセスを利用する多重露光/パターニングプロセスが用いられ得る。ある種類の二重露光プロセスは、第1のフォトレジストパターンを形成し、第1のフォトレジストパターンを用いてウエハをエッチングし、続いて第2のフォトレジストパターンを形成し、そして第2のフォトレジストパターンを用いてウエハをエッチングする。別の種類の二重露光プロセスは、第1のフォトレジストパターンを形成し、第1のフォトレジストパターンを第2のフォトレジスト層で被覆し、第2のフォトレジスト層を露光して現像し、次いでウエハをエッチングする。この二重露光プロセスは二重露光単一エッチングプロセスと称されることがある。

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

半導体産業において現在利用可能なフォトリソグラフィツールは、80ナノメートルの線解像度を達成することができる。より具体的には、193ナノメートル液浸ステッパー(immersion stepper)技術は、単一のマスク上で80ナノメートル程度の短いピッチを達成可能である。実際には、上述の二重露光/パターニングプロセスを用いて、80ナノメートル未満のピッチを有するデバイス特徴部が達成され得る。残念なことに、多重露光手順が用いられるとしても、ピッチ又は線分離の縮小化は、最終的には、フォトリソグラフィツールの実用上の実行能力によって制限される。従って、所望の半導体デバイス特徴部の実行可能性(viability)及び製造可能性をチェックするために、特定の設計規則が一般に用いられる。例えば、ローカル相互接続等の導電トレースの提案されたレイアウトにおいて、先端・先端間(tip-to-tip)及び/又は先端・線間(tip-line)での違反(violation)の可能性を識別するために、設計規則検査(design rule check) (DRC) 方法論が適用され得る。このように、提案されたレイアウトが特定のフォトリソグラフィツールに対しては短すぎる先端・先端間又は先端・線間の間隔を含む場合には、その提案されたレイアウトを用いて、幾つかの導電トレースを互いに短絡させることなしにデバイスを製造することは可能ではないかもしれない。

#### 【課題を解決するための手段】

#### 【0007】

半導体デバイス構造上にデバイス特徴部を作製する方法が提供される。方法は、フォトレジスト特徴部の第1のパターンを半導体デバイス構造の目標材質の上に作製することを含み、フォトレジスト特徴部の第1のパターンは、第1の要素フォトリソグラフィマスクによって規定される。方法はまた、フォトレジスト特徴部の第2のパターンを目標材質の上に作製し、フォトレジスト特徴部の第2のパターンは、第2の要素フォトリソグラフィマスクによって規定される。フォトレジスト特徴部の第1のパターン及びフォトレジスト

10

20

30

40

50

特徴部の第2のパターンは、協働してフォトレジスト特徴部の結合されたパターンを形成する。方法は、フォトレジスト特徴部の結合されたパターンをエッチングマスクとして用いて目標材質を選択的にエッチングすることによって継続する。これにより、目標材質内に凹部線パターンが形成される。方法は次いで、凹部線パターンの指定された区画を覆うフォトレジスト特徴部の第3のパターンを形成する。

#### 【0008】

半導体デバイスを製造する方法もまた提供される。この方法は、半導体材質の層及び半導体材質の層の上の絶縁材質の層を備える半導体デバイス構造を提供することによって開始する。方法は、絶縁材質の層の上にハードマスク材質の層を形成することと、フォトレジスト特徴部の結合されたパターンをハードマスク材質の層の上に作製することと、によって進行する。フォトレジスト特徴部の結合されたパターンは、第1のフォトリソグラフィマスクを用いて形成される第1のフォトレジスト特徴部と、第2のフォトリソグラフィマスクを用いて形成される第2のフォトレジスト特徴部と、を備える。方法は、フォトレジスト特徴部の結合されたパターンをエッチングマスクとして用いてハードマスク材質の層を選択的にエッチングすることによってポジティブハードマスクパターン及びネガティブ凹部線パターンをハードマスク材質内に規定することにより継続する。方法はまた、追加的フォトレジスト特徴部を絶縁材質の上に作製する。追加的なフォトレジスト特徴部は、ネガティブ凹部線パターン内に規定される1つ以上の凹部線と交差する。

#### 【0009】

半導体デバイスを製造する別 の方法が提供される。この方法は、半導体材質の層及び半導体材質の層の上の絶縁材質の層を備える基板上にハードマスク材質の層を形成し、ハードマスク材質の層は絶縁材質の層の上にある。方法は、多重露光フォトリソグラフィ手順を実行してハードマスク材質の層の上にフォトレジスト特徴部の結合されたパターンを作製することによって、及びハードマスク材質内に凹部線パターンを形成することによって、継続する。凹部線パターンは、フォトレジスト特徴部の結合されたパターンによって規定される。方法は次いで、凹部線パターンの指定された区画をフォトレジスト特徴部の遮断パターンで覆い、そして溝のパターンを絶縁材質内に形成する。溝のパターンは、フォトレジスト特徴部の遮断パターン及びハードマスク材質によって規定される。方法は次いで、電気伝導材質を溝内に堆積させることによって、半導体デバイスのための導電線をもたらす。

#### 【0010】

先端・先端間及び先端・線間の違反が低減された半導体デバイス特徴部のためのフォトリソグラフィマスクを作製する方法もまた提供される。この方法は、所望のマスクパターンを表す予備データを提供し、そして予備データを解析して所望のマスクパターン内における先端・先端間及び先端・線間の違反を識別する。方法は、識別された違反に従って予備データを修正して、修正されたマスクパターンを表す更新されたデータを取得し、修正されたマスクパターンには先端・先端間及び先端・線間の違反が無い。方法は次いで、更新されたデータを用いて、修正されたマスクパターンを有するフォトリソグラフィマスクを生成する。

#### 【0011】

設計規則違反が低減された半導体デバイス特徴部のためのフォトリソグラフィマスクを作製する別 の方法もまた提供される。この方法は、全体的なマスクパターンを表す予備データを提供し、予備データを処理して全体的なマスクパターンを複数の要素マスクパターンへと分解し、そして複数の要素マスクパターンに対して設計規則検査を実行して複数の要素マスクパターン内での先端・先端間及び先端・線間の違反を識別する。これにより、識別された違反がもたらされる。方法は、識別された違反に従って複数の要素マスクパターンの少なくとも1つを修正して要素マスクパターンの修正されたセットを取得することにより継続し、ここで要素マスクパターンの修正されたセットにおける各マスクパターンには先端・先端間及び先端・線間の違反が無い。方法は次いで、要素マスクパターンの修正されたセットのためのフォトリソグラフィマスクを生成する。

10

20

30

40

50

**【0012】**

設計規則違反が低減された半導体特徴部のためのフォトリソグラフィ方法もまた提供される。この方法は全体的なマスクパターンを提供することによって開始する。全体的なマスクパターンは、第1の要素マスクパターン及び第2の要素マスクパターンへと分解される。方法は、少なくとも第1の要素マスクパターン内における設計規則違反を識別して識別された違反をもたらすことによって継続する。方法は次いで、識別された違反に従って第1の要素マスクパターンを修正して修正された第1の要素マスクパターンを取得し、修正された第1の要素マスクパターンには設計規則違反が無い。方法はまた、識別された違反に従って遮断マスクパターンを生成し、遮断マスクパターンには設計規則違反が無く、そして方法は、修正された第1の要素マスクパターン、第2の要素マスクパターン、及び遮断マスクパターンに対応するフォトリソグラフィマスクを作製する。

**【0013】**

この概要は、詳細な説明において後で更に説明される概念の選択を単純化された形態で紹介するために設けられている。この概要是、特許請求の範囲に記載された主題の鍵となる特徴又は本質的な特徴を識別することを意図されていなければ、また特許請求の範囲に記載された主題の範囲を決定するための補助として用いられることも意図されていない。

**【図面の簡単な説明】****【0014】**

以下の図面と共に詳細な説明及び特許請求の範囲を考慮して参照することによって、主題のより完全な理解がもたらされるであろう。図面において同様の参照番号は全図を通して類似の要素を参照する。

**【0015】**

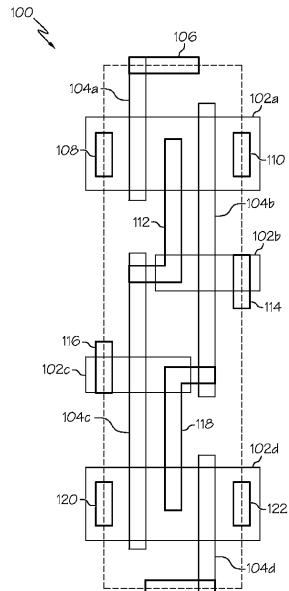

**【図1】**図1は二方向ローカル相互接続のレイアウトを示す例示的なスタティックランダムアクセスメモリ(SRAM)セルの平面図であって部分的な透視図である。

**【0016】**

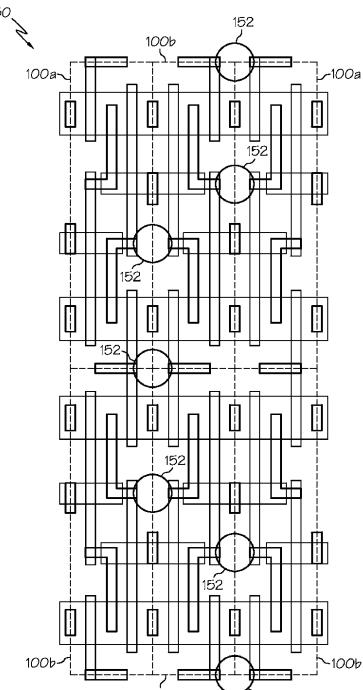

**【図2】**図2は図1に示されるSRAMセルに基づくSRAMセルの3×2アレイの平面図であって部分的な透視図である。

**【0017】**

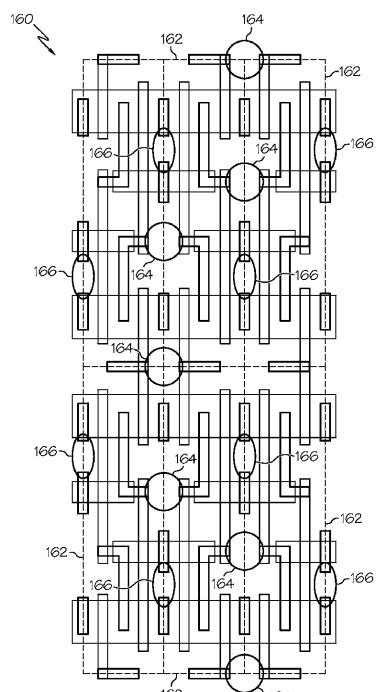

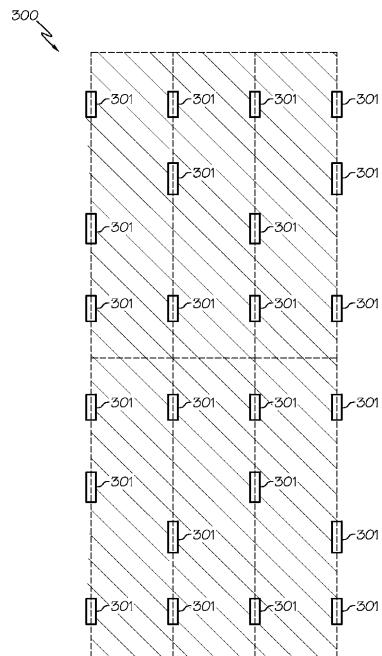

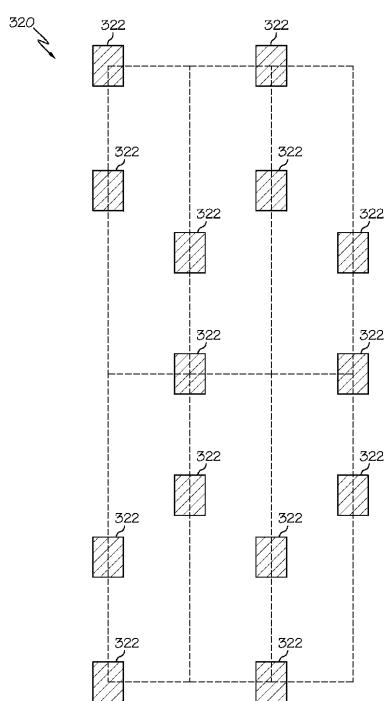

**【図3】**図3は代替的なSRAMセルレイアウトに基づくSRAMセルの3×2アレイの平面図であって部分的な透視図である。

**【0018】**

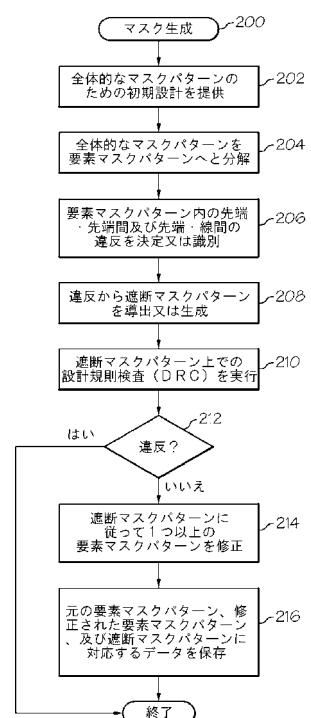

**【図4】**図4はマスク生成プロセスの例示的な実施形態を示すフローチャートである。

**【0019】**

**【図5】**図5は第1の要素マスクパターンの平面図である。

**【0020】**

**【図6】**図6は第2の要素マスクパターンの平面図である。

**【0021】**

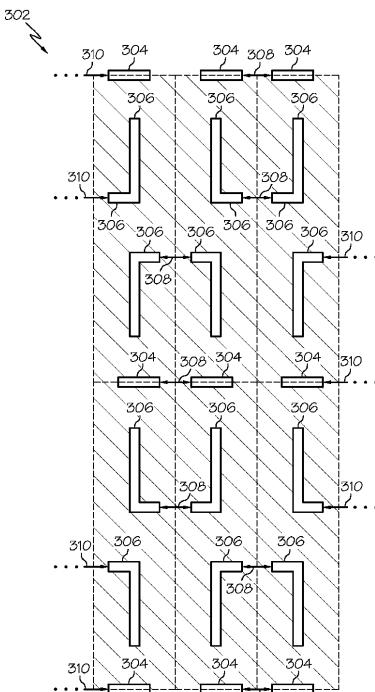

**【図7】**図7は遮断マスクパターンの平面図である。

**【0022】**

**【図8】**図8は図6に示される第2の要素マスクパターンの修正されたバージョンの平面図である。

**【0023】**

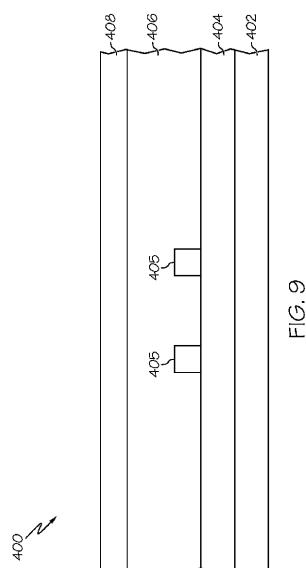

**【図9】**図9は例示的な製造プロセスに供される半導体デバイス構造を示す断面図(その1)である。

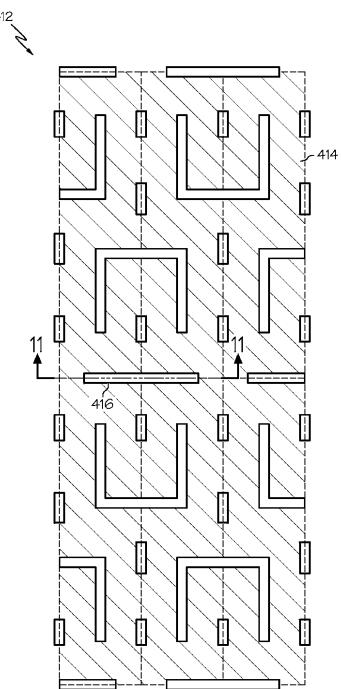

**【図10】**図10は例示的な製造プロセスに供される半導体デバイス構造を示す平面図(その1)である。

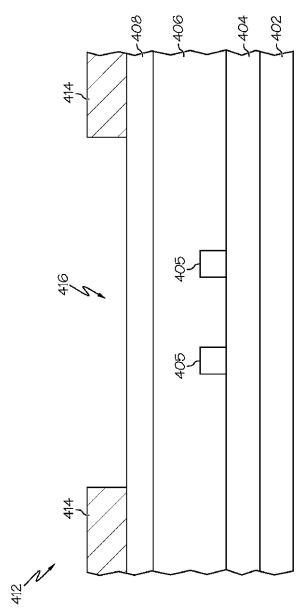

**【図11】**図11は例示的な製造プロセスに供される半導体デバイス構造を示す断面図(その2)である。

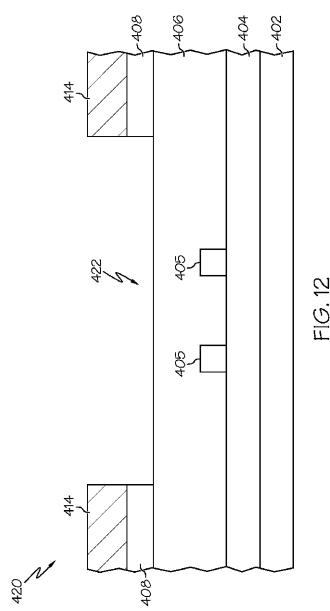

**【図12】**図12は例示的な製造プロセスに供される半導体デバイス構造を示す断面図(その3)である。

10

20

30

40

50

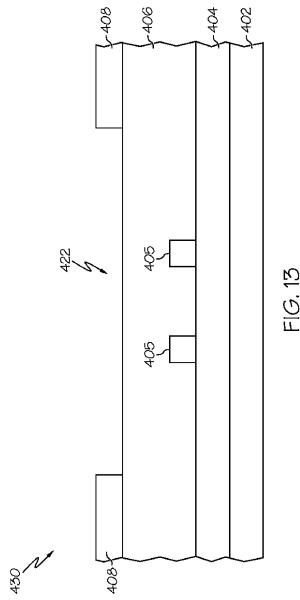

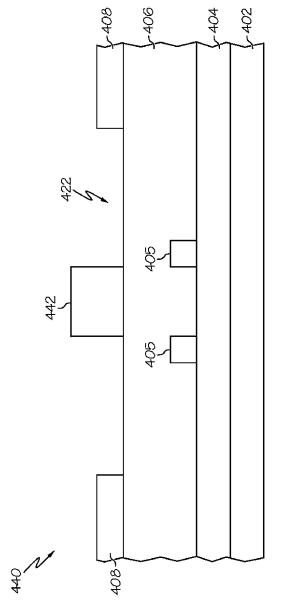

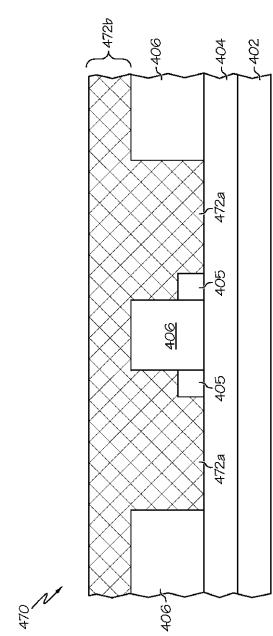

【図13】図13は例示的な製造プロセスに供される半導体デバイス構造を示す断面図（その4）である。

【図14】図14は例示的な製造プロセスに供される半導体デバイス構造を示す断面図（その5）である。

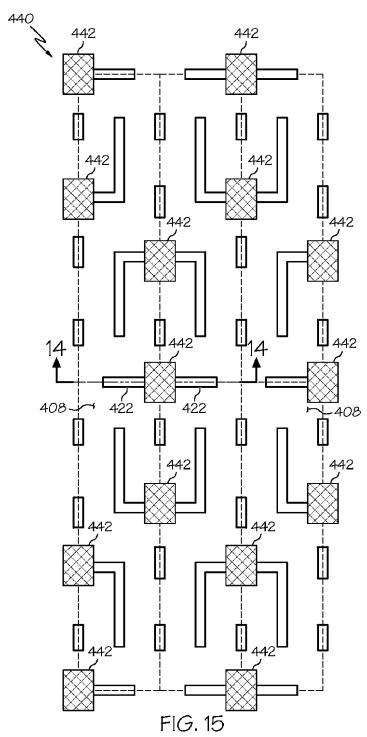

【図15】図15は例示的な製造プロセスに供される半導体デバイス構造を示す平面図（その2）である。

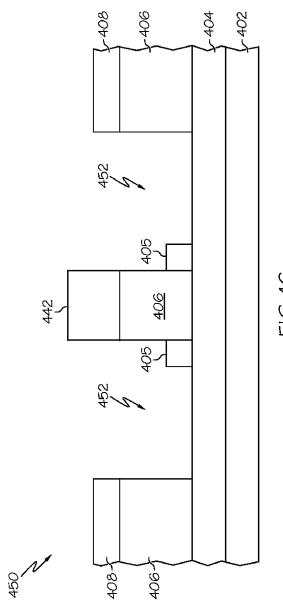

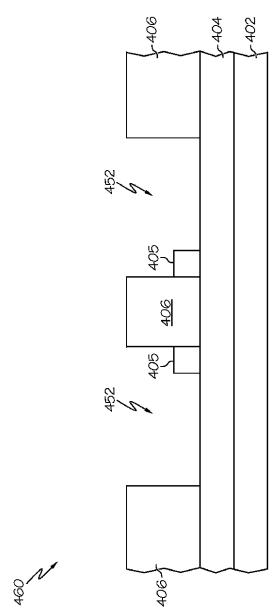

【図16】図16は例示的な製造プロセスに供される半導体デバイス構造を示す断面図（その6）である。

【図17】図17は例示的な製造プロセスに供される半導体デバイス構造を示す断面図（その7）である。10

【図18】図18は例示的な製造プロセスに供される半導体デバイス構造を示す断面図（その8）である。

【図19】図19は例示的な製造プロセスに供される半導体デバイス構造を示す断面図（その9）である。

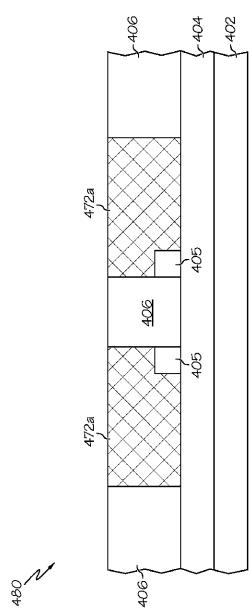

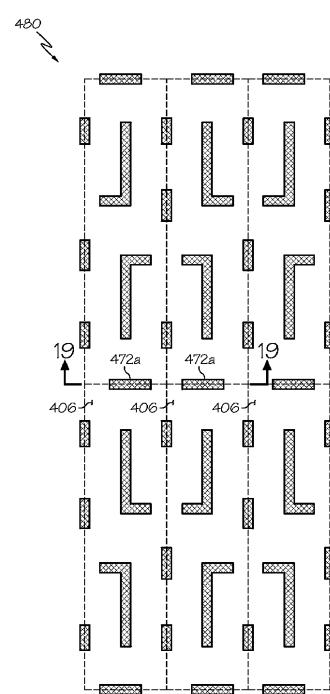

【図20】図20は例示的な製造プロセスに供される半導体デバイス構造を示す平面図（その3）である。

#### 【発明を実施するための形態】

##### 【0024】

以下の詳細な説明は、本来的に単なる例示であり、また主題の実施形態又は本出願及びそのような実施形態の使用を限定することを意図するものではない。ここで用いられる「例示的な」という語は、「例、事例、又は例証としての役目をする」を意味する。例示的なものとしてここで説明される任意の実装は、他の実装に対しても望ましいものとして又は有利であるものとして必ずしも解釈されない。更に、先の技術分野、背景技術、発明の概要、又は以下の詳細な説明において提示されるいかなる表現された又は暗示された理論によっても境界される意図はない。20

##### 【0025】

種々のコンピューティング要素又はデバイスによって実行され得る動作、処理タスク、及び機能の象徴的な表現を参照して、特定の技法及び技術がここに説明されるであろう。そのような動作、タスク、及び機能は、コンピュータ実行の、コンピュータ化された、ソフトウェア実装の、又はコンピュータ実装のものと称されることがある。実際には、1つ以上のプロセッサデバイスは、システムメモリ内のメモリロケーションでデータビットを表す電気的な信号を操作することによる他、信号の他の処理によって、説明される動作、タスク、及び機能を実施することができる。ここに説明される特定の方法は、ソフトウェア又はファームウェアにおいて実装される場合、種々のタスクを実行するコードセグメント又は命令によって表され得る。プログラム又はコードセグメントは、プロセッサ可読媒体内に記憶され得るし、あるいは搬送波において具現化されるコンピュータデータ信号によって伝送媒体又は通信バスを介して伝送され得る。この点において、「プロセッサ可読媒体」又は「機械可読媒体」は、情報を記憶し又は伝送することができる任意の媒体を含む。プロセッサ可読媒体の例は、限定はされないが、電子回路、半導体メモリデバイス、ROM、フラッシュメモリ、消去可能ROM(EROM)、フロッピー(登録商標)ディスク、CD-ROM、光ディスク、ハードディスク等を含む。30

##### 【0026】

半導体デバイスの製造の間にフォトリソグラフィ及び種々のフォトリソグラフィ技法が用いられる。そのような技法は半導体ウェハ上にフォトレジスト材質のパターンを形成するために用いることができ、この場合、そのようなパターンは、形成され、取り扱われ、又は処理されるべき特徴部、領域、及び／又は区域の境界を規定する。例えばフォトリソグラフィは、ローカル相互接続、能動半導体領域、ゲート構造、側壁スペーサ、エッチングマスク、イオン注入マスク等のレイアウトを規定するために用いられ得る。その際、典型的なフォトリソグラフィシステムは、放射源、光学系(例えばレンズ、ミラー、又は水等の液体)、マスク、及びフォトリソグラフィに供されるウェハのためのステージを使用40

する。そのようなフォトリソグラフィシステムは、マスク上で提供されるパターン又は像を目標材質又はウエハの表面へと転写するように構成される。

#### 【0027】

対象となるウエハの目標材質の上にフォトレジスト層が形成される。目標材質は、絶縁層、導電層、バリア層、又はエッチングされ、ドーピングされ、取り扱われ、処理され、若しくは層状にされるべき任意の目標材質であり得る。例えば目標材質は、限定はされないが、多結晶シリコン；シリサイド材質；シリコン窒化物材質等のハードマスク層；反射防止膜；又は任意の適切な導電性、半導電性、若しくは絶縁性の材質であってよい。フォトレジスト層は、リソグラフィ適用に適する種々のフォトレジスト材質、組成、又は化学薬品を備え得る。フォトレジスト層は、放射源から放射される電磁放射に応答して光化学反応を被り且つ電磁放射に対して十分な透明性を有してフォトレジスト層の有用なパターニングを可能にするように選択される。フォトレジスト層に適する材質は、特に、マトリックス材質又は樹脂、感光薬又は阻害剤、及び溶媒を含み得る。フォトレジスト層は、化学的に増幅された、ポジティブ又はネガティブトーンの、有機系のフォトレジストであってよい。フォトレジスト層はシリコン含有フォトレジストであってもよい。例えばフォトレジスト層は、限定はされないが、アクリレート系重合体、脂環式系重合体、又はフェノール性系重合体であってよい。

#### 【0028】

ここで説明される種々の実施形態のために、フォトレジスト材質の層は、任意の適切な技法、例えばスピンドルコートによる堆積を用いて、目標材質、又は半導体デバイス構造の層を覆うように形成され得る。所与のフォトレジスト層の厚みは、例えば真空紫外線（VUV）リソグラフィ、深紫外線（DUV）リソグラフィ、及び／又は超紫外線（EUV）リソグラフィ（例えば193nm、157nm、126nm、又は13.4nmの波長を有する露光光を用いる）用の特定のリソグラフィ技術に応じて選択される。その際、特定のフォトレジスト層は、15～1000nmの範囲内の厚みを有していてよく、望ましい厚みの範囲は50～500nmである。

#### 【0029】

フォトリソグラフィシステムによって用いられる光学系は、放射（即ちマスク上で提供されるパターン又は像によって修正される放射源からの放射）のパターンをフォトレジスト層上にフォーカスし且つ方向付けるように適切に構成される。特定の実施形態においては、マスクは、透明又は半透明な基板（例えばガラス又は石英）及びその上の不透明な又はパターニングされた層（クロム又はクロム酸化物から形成されていてよい）を含むバイナリマスクである。不透明層は、フォトレジスト層上に投影されるべき、所望の回路パターン、特徴部、又はデバイスに関連するパターン又は像をもたらす。代替的には、マスクは、減衰位相シフトマスク、交互位相シフトマスク、又は他の種類のマスクであってよい。

#### 【0030】

多くの半導体トランジスタ製造プロセスは、自己整合された特徴部(self-aligned features)、例えばコンタクトからゲートへの自己整合された特徴部及び／又はローカル相互接続からゲートへの自己整合された特徴部を必要としている。自己整合は、コンタクトからゲートへの短絡を回避し、また小ノード技術（例えば20nm以下の技術）でのチャネル長スケーリングを可能にするために利用される。ここに説明される技法及び技術は、自己整合される二方向ローカル相互接続を伴うプロセスフローを生かして、結果として、2つのフォトリソグラフィマスクを用いる従来のローカル相互接続パターニングされた解決法と比較して、より密接な先端・先端間及び先端・線間の間隔をもたらす。

#### 【0031】

現在のフォトリソグラフィツール（例えば193nm液浸ステッパー）を用い、よく知られた二重パターニング手法を用いて、80nmを下回るピッチを有するデバイス特徴部が作製され得る。しかし、二重パターニング技法で80nmを下回るピッチを達成する解決法は、各個別のフォトリソグラフィマスクに対する先端・先端間及び先端・線間の間隔要

10

20

30

40

50

求によって制限される。ここで用いられる「先端・先端間(tip-to-tip)」は、2つの隣接する特徴部の端又は先端(ends or tips)の間の距離又は長さを参照し、ここで端又は先端は一般的には同軸上で方向付けられている。ここで用いられる「先端・線間(tip-to-line)」は、1つの特徴部の端又は先端と別の特徴部の側縁(side edge)との間の距離又は長さを参照し、ここで第1の特徴部の端又は先端は一般的には第2の特徴部の側縁に対して直交して方向付けられている。先端・先端間及び先端・線間の違反に関連する制限に対処するために、3マスク手法がここに提供される。3マスク解決法は、2つのマスク(ハードマスク材質の二重バターニングのために用いられる)と共に、より小さい先端・先端間及び先端・線間の間隔を可能にする遮断マスク(blocking mask)を採用する。この3マスク手法は、例えばS R A Mピットセルを縮小化するために用いることができ、それにより、現時点では半導体デバイスの大量生産に対して準備が整っているとは全く言えないE U V技術を用いる必要性なしに、コスト効率的な解決法が可能になる。

#### 【0032】

ここに説明される技法は、半導体デバイス又はウエハ上の種々の特徴部、領域、要素、及び/又は構造を作製するために採用され得るが、以下に提示される例示的な実施形態は、S R A Mデバイスのための二方向ローカル相互接続パターンの形成に関連している。これらの例示的な実施形態は包括的なものではなく、また説明される主題の範囲又は応用を限定することも制限することも意図されていない。ローカル相互接続パターンは、従来の半導体デバイス製造技術を用いて縮小化することが比較的に困難であるという理由で、ここに言及されるものである。

#### 【0033】

図1は二方向ローカル相互接続のレイアウトを示す例示的な6TのS R A Mセル100の平面図であって部分的な透視図である。6Tセルが示されているが、ここに説明される技法及び概念は、4T、8T、10T等の他のS R A Mセルトポロジにも適用可能である。図1は、ここに提示される概念を最もよく表す単純化され且つ透視の方法でS R A Mセル100の特徴部を示している。また、S R A Mセル100の具体的なレイアウトは単に例示的なものであり、図示されるレイアウトは、説明される主題の範囲を限定し又は制限することを意図されていない。S R A Mセル100のこの実施形態は、4つの能動半導体領域102及び4つのゲート構造104を含み、これらは協働して6つのトランジスタデバイスを形成する。図1の視点からは直ちには明らかではないが、ゲート構造104は、よく理解されるように、能動半導体領域102の上に形成されている。ゲート構造104は、これらが全て一般的には同じ方向(図1における垂直方向)に向けられているという理由で、単方向的であると考えられる。

#### 【0034】

S R A Mセル100はまた複数のローカル相互接続を含み、これらはタンゲステン材質又は任意の適切な金属材質等の電気伝導性材質から形成される。この特定の実施形態は、ゲート構造104aに結合されるローカル相互接続106と、能動半導体領域102aに結合される2つのローカル相互接続108/110と、ゲート構造104c、能動半導体領域102b、及び能動半導体領域102aに結合される二方向ローカル相互接続112と、能動半導体領域102bに結合されるローカル相互接続114と、能動半導体領域102cに結合されるローカル相互接続116と、ゲート構造104b、能動半導体領域102c、及び能動半導体領域102dに結合される二方向ローカル相互接続118と、能動半導体領域102dに結合される2つのローカル相互接続120/122と、ゲート構造104dに結合されるローカル相互接続124と、を含む。図1の視点からは直ちには明らかではないが、ローカル相互接続は、能動半導体領域102の上で、ゲート構造104の上で、且つ/又は半導体基板の他の区域(図1においては、これらの他の区域は認識できるいかなるデバイス特徴部をも欠いている)の上で形成される。ローカル相互接続112及び118は、これらの各々が一般的には2つの異なる方向(図1における垂直方向及び水平方向)に向けられているという理由で、二方向的であると考えられる。S R A Mセル100の具体的な電気的結合及びはレイアウトは、6TのS R A Mセルの動作について

10

20

30

40

50

てよく知られている原理及び要求を満たすので、S R A Mセル1 0 0の動作についてはここでは詳しくは説明しない。

#### 【 0 0 3 5 】

実際上は、単一のS R A Mセルが単一の半導体基板上に幾つも作製されて、大きなメモリ容量を提供することになる。例えばS R A Mセル1 0 0は、単一の半導体デバイス構造上のS R A Mセルのアレイとして幾つも複製され得る。この点において、図2は、S R A Mセル1 0 0に基づくS R A Mセルの3×2アレイ1 5 0の平面図であって部分的な透視図である。S R A Mセルのアレイ1 5 0は、図1に示されるのと同じレイアウトを有する3つのS R A Mセル1 0 0 aと、図1に示されるレイアウトの鏡像レイアウトを有する3つのS R A Mセル1 0 0 bと、を含む。これにより、S R A Mセルのアレイ1 5 0内で隣接するセルは、特定の特徴部又は要素を共有することができる。例えば、隣接するセルは、特定の能動半導体領域及び／又は特定のローカル相互接続を共有し得る。10

#### 【 0 0 3 6 】

実際のS R A Mデバイスは数百万セルのアレイを用いているであろうし、製造業者はS R A Mデバイスの物理的サイズを低減する努力をしている。特定の設計規則（実用上の製造公差及び制限に基づく）は、幾つかの特徴部が縮小化され得る量を制限する。例えば設計規則は、特徴部が互いに短絡し又は結合すること（フォトリソグラフィツールの実用上の制限に起因し得る）を避けるために、隣接するマスク特徴部間の先端・先端間及び先端・線間の最小の間隔を決定する。従って、S R A Mデバイスに対して提案されるレイアウトが、潜在的な設計規則違反(design rule violations)（例えば先端・先端間又は先端・線間での違反）を含む場合には、そのレイアウトを製造することは実用的又は実現可能ではないであろう。この点に関して、図2は、S R A Mセルのアレイ1 5 0のための単一のフォトリソグラフィマスクに関連する幾つかの潜在的な先端・先端間違反1 5 2を識別している。図2において円で囲まれた領域は、これらの先端・先端間違反1 5 2に対応している。図2においては、全ての先端・先端間違反1 5 2は、水平に向かっているローカル相互接続特徴部に関係している。この例では、S R A Mセルのアレイ1 5 0は先端・線間違反を含まないが、ここに説明される手法は、先端・線間違反に対処するため、及び先端・先端間違反と先端・線間違反の任意の組み合わせに対処するために用いられ得る。20

#### 【 0 0 3 7 】

図3は、代替的なS R A Mセルレイアウトに基づくS R A Mセルの別の3×2アレイ1 6 0の平面図であって部分的な透視図である。S R A Mセルのアレイ1 6 0はS R A Mセル1 6 2の6つの反復（3つの鏡像バージョンを含む）を含む。S R A Mセルのアレイ1 6 0の全体的レイアウトは、図2に示されるS R A Mセルのアレイ1 5 0のレイアウトと一般的には同様である。しかし、S R A Mセルのアレイ1 5 0とは異なり、S R A Mセルのアレイ1 6 0は、垂直に向かわれる潜在的な先端・先端間違反を含む。このように、図3は、幾つかの垂直先端・先端間違反1 6 6に加えて幾つかの水平先端・先端間違反1 6 4を示している。特に、水平先端・先端間違反1 6 4は1つのフォトリソグラフィマスクに関連しており、一方、垂直先端・先端間違反は別のフォトリソグラフィマスクに関連している。この様子は後で詳細に説明される。30

#### 【 0 0 3 8 】

設計規則違反の存在により、従来の技法を用いて隣接するローカル相互接続特徴部の間での短絡をもたらすことなくS R A Mセルのアレイ1 5 0又はS R A Mセルのアレイ1 6 0を製造することは可能ではないであろう。以下に説明されるマスク生成及び半導体製造の技法及び技術は、多重パターニングフォトリソグラフィに際して用いられるマスクにおける潜在的な先端・先端間及び先端・線間の違反を解消することによって、この問題に対処し、そしてサブ8 0ナノメートル解像度での半導体デバイス（例えばS R A Mデバイス）の製造業者を支援する。40

#### 【 0 0 3 9 】

ここに説明される例示的な多重マスク解決法は、半導体デバイス構造上での多重パターニング手順に対して少なくとも2つのマスクを用いる。ハードマスク及びこれに続く遮断50

マスクの作製は、いかなるフォトリソグラフィマスクにも設計規則違反を導入することなしに、より密接した先端・先端間及び先端・線間の間隔を可能にする。この点に関し、図4は、半導体製造プロセスの間に用いられる一連のフォトリソグラフィマスクを作製するために実行され得るマスク生成プロセス200の例示的な実施形態を示している。プロセス200は、低減された設計規則違反（従来の手法に比べて）を伴う半導体デバイス特徴部のためにフォトリソグラフィマスクを作製する例示的な方法を代表する。プロセス200に関連して実行される種々のタスクは、ソフトウエア、ハードウエア、ファームウェア、又はそれらの任意の組み合わせによって実行されてよい。実際上は、プロセス200の一部は、1つ以上のコンピューティングデバイスによって、1つ以上のコンピュータシステムによって、又は実行されるときにホストコンピューティングデバイス若しくはプロセッサに、説明されるタスクを実施させるコンピュータ可読命令及び／若しくはプロセッサ実行可能命令を有する適切なソフトウェアプログラムを実行するように適切に構成される処理ハードウエアによって、実行されてよい。例えばプロセス200は、半導体デバイス設計、半導体デバイス設計に適する設計規則検査アプリケーション、等と共に用いられるのに適するコンピュータ支援設計アプリケーション内に組み込まれ又は統合化され得る。プロセス200は任意の数の追加的な又は代替的なタスクを含んでいてよく、図4に示されるタスクは図示される順序で実行される必要はなく、またプロセス200はここでは詳細に説明されない追加的な機能性を有するより包括的な手順又はプロセス内に組み込まれてよいことが理解されるべきである。更に、プロセス200の実施形態においては、図4に示される1つ以上のタスクが省略されてもよい（全体的な機能性が保たれる限り）。 10

#### 【0040】

プロセス200は、全体的な所望のマスクパターンのための初期設計を取得し、作成し、又は提供することによって開始してよい（タスク202）。特定のCAD展開においては、タスク202は所望のマスクパターンを表す予備データを提供してよく、ここでは、予備データは、全体的なマスクパターンによって規定される特徴部のレイアウト、寸法、配置、向き、及び相対的位置決めを示す（理解されるように、任意の適切な参照又は座標系を用いて）。この例は、図2に示されるSRAMセルのアレイ150のためのローカル相互接続の生成を意図している。従って、タスク202は、SRAMセル100（図1）の所望のローカル相互接続レイアウトを表すデータ及び／又はSRAMセルのアレイ150（図2）の相互接続レイアウトを表すデータを提供し、取得し、又は記憶する。 20

#### 【0041】

プロセス200のこの実施形態は、多重露光／パターニング手順（例えばリソ・リソ・エッチ（litho-litho-etch）（LLE）手順、リソ・エッチ・リソ・エッチ（LELE）手順、リソ・フリーズ・リソ・エッチ（litho-freeze-litho-etch）（LFFE）手順、等）を用いて全体的なマスクパターンが作製されることを前提としている。特定の実用上の実施形態においては、プロセス200は、LELEが多少はロバスト（robust）であり且つ確立された技術であるという理由で、LELE手順を採用している。従って、全体的なマスクパターンは、複数の異なる要素マスクパターンへと分解される（タスク204）。実際上は、タスク204は、全体的なマスクパターンを表している予備データを適切な方法で処理し又は解析して分解を行ってよい。任意の数の要素マスクパターンが生成され得るが、この例は、全体的なマスクパターンを第1の要素マスクパターン及び第2の要素マスクパターンへと分解する。プロセス200は、既存の又は従来の分解の技法、ソフトウエアアプリケーション、及び技術を活用してよい。従って、タスク204によって採用される具体的な分解技法はここでは詳述しない。 40

#### 【0042】

タスク204によって生成される例示的な要素マスクパターンが図5及び図6に示されており、ここで図5は第1の要素マスクパターン300の平面図であり、また図6は第2の要素マスクパターン302の平面図である。第1の要素マスクパターン300は、個々のSRAMセルの境界に位置する垂直に向かされた短いローカル相互接続を規定している。第1の要素マスクパターン300内のマスク特徴部301は、図2に示されるSRAM 50

セルのアレイ 150 内でも見出される。第 2 の要素マスクパターン 302 は、個々の S R A M セルの境界に位置する水平に向かされたローカル相互接続を規定するマスク特徴部 304 を含む。第 2 の要素マスクパターン 302 はまた、個々の S R A M セルの境界内に位置する二方向ローカル相互接続を規定するマスク特徴部 306 を含む。マスク特徴部 304 / 306 は、図 2 に示される S R A M セルのアレイ 150 内でも見出される。これら両マスクパターンの特徴部は、結果として得られる、半導体基板上に形成されるフォトレジスト材質のパターンが、マスク特徴部 301 / 304 / 306 に対応する輪郭を有する空間又は穴を含むことになるという理由で、「ネガティブ」である。つまり、図 5 及び図 6 においてマスク特徴部 301 / 304 / 306 が現れる場所ではどこでもフォトレジスト材質が欠如していることになる。

10

#### 【0043】

プロセス 200 は次いで、要素マスクパターン内の特定の設計規則違反を識別するために要素マスクパターンを解析することによって進行してよい(タスク 206)。現世代の 193 nm 液浸ステッパツールに対しては、約 90 ~ 112 nm 未満の先端・先端間又は先端・線間の間隔は、設計規則違反であると考えられる。実際上は、タスク 206 は、要素マスクパターン内における先端・先端間及び / 又は先端・線間の違反の存在を決定する適切な設計規則検査(design rule check) (D R C) 手順を伴っていてよい。従って、タスク 206 は、適切な D R C アプリケーション、プログラム、又はアルゴリズムを用いて要素マスクパターンを表すデータを解析する適切な処理ハードウェアによって実行されてよい。この例は、第 1 の要素マスクパターン 300 に先端・先端間又は先端・線間の違反が全くないことを前提としている。他方、この例は、タスク 206 が第 2 の要素マスクパターン 302 内で幾つかの先端・先端間違反を識別することを前提としている(第 2 の要素マスクパターン 302 内に先端・線間違反は無い)。図 6 においては、識別された違反 308 は両向き矢印によって表されている。図 6 はまた、矢印及び省略記号を用いて、幾つかの識別された違反 310 を示しており、即ちこれらの識別された違反 310 は、アレイの外側境界に位置し、また隣接するセルの存在下で生じる実際の違反を意図している。プロセス 200 は、全体のマスクパターンの特定のレイアウトに応じて、またタスク 204 が全体のマスクパターンをその要素マスクパターンへと分解する方法に応じて、要素マスクパターンの 1 つのみにおいて、要素マスクパターンの全てにおいて、又は要素マスクパターンの全てではないが幾つかにおいて、設計規則違反を見出し得ることが理解されるべきである。

20

#### 【0044】

特定の実施形態においては、タスク 206 は、例えば全体のマスクパターンに対して利用される同じ参照系、座標系、又は測定系を用いて、識別された違反の寸法、ロケーション、位置、及び / 又は配置を決定してよい。この情報は次いで、フォトリソグラフィ遮断マスクパターンを導き出し又は生成するために用いられ得る(タスク 208)。その際、遮断マスクパターンは、識別された違反の寸法から導き出され若しくは取得され又は識別された違反の寸法によって影響を受ける特徴部を有することになる。実際上は、タスク 208 は、識別された違反に従い遮断マスクデータを導き出す適切な処理ハードウェアによって実行されてよい。以下に更に詳細に説明されるように、遮断マスクパターンは、製造プロセスの間ににおける半導体デバイス上への特徴部の形成を選択的に遮断するために用いられる。図 7 は、タスク 208 の間に生成されることになる 1 つの例示的な遮断マスクパターン 320 の平面図である。タスク 208 は、所望のアレイ(図 7 に示されるような)に対応する遮断マスクパターンを生成可能であり、あるいは 1 つのセルのみに対応する遮断マスクパターンを生成可能であることが理解されるべきである。

30

#### 【0045】

遮断マスクパターン 320 は、識別された設計規則違反(図 6 参照)に対応するマスク特徴部 322 を含む。図 5 及び図 6 に示されるマスク特徴部 301 / 304 / 306 とは対照的に、遮断マスクパターン 320 上のマスク特徴部 322 は、結果として得られる、半導体基板上に形成されるフォトレジスト材質のパターンが、マスク特徴部 322 に対応

40

50

することになるという理由で、「ポジティブ」である。つまり、マスク特徴部 322 が存在する場所にはフォトレジスト材質が残っていることになる。各マスク特徴部 322 のロケーション及び幅は、そのそれぞれの設計規則違反のロケーション及び幅に基づいている。実際上は、マスク特徴部 322 の寸法は、識別された設計規則違反のそれぞれの寸法に等しくてよい。代替的には、マスク特徴部 322 は、プロセスばらつき及び／又は製造ツールの特性に対処する必要がある場合には、マスク特徴部 322 の寸法が、識別された設計規則違反のそれぞれの寸法と等しくないようにスケーリングされ得る。例えば、マスク特徴部 322 をそれらの対応する違反よりも僅かに大きく／小さくすることが望ましいかもしれない（実際上は、マスク特徴部 322 は典型的には拡大され、即ち対応する違反のサイズよりも僅かに大きい）。また、先端・先端間及び先端・線間の違反を考慮する場合、識別された違反は、典型的には 1 つの寸法、即ち 2 つの隣接する先端間の間隔又は先端と線の間の間隔を指定することになる。しかし、遮断マスクパターン 320 は、2 つの寸法によって規定されるマスク特徴部 322 を含んでいる。この例では、マスク特徴部 322 の水平寸法が、識別された違反の寸法に対応する。タスク 208 はまた、マスク特徴部 322 の垂直寸法を計算して、要素マスクパターン上で見出されるマスク特徴部との不所望な干渉を回避しており、その理由は後述の説明から明らかになる。

#### 【0046】

特定の実施形態においては、タスク 208 において生成された遮断マスクは、遮断マスクそれ自身内の設計規則違反をチェックするために、DRC 手順（タスク 210）に供される。従って、タスク 210 は、遮断マスク内での先端・先端間及び／又は先端・線間の任意の違反を識別するために適切な DRC アプリケーション、プログラム、又はアルゴリズムを用いて遮断マスクデータを解析する適切な処理ハードウェアによって実行され得る。遮断マスクが先端・先端間又は先端・線間の違反を含む場合（問い合わせタスク 212）には、プロセス 200 はエグジットしてよく、全体的なマスクパターンの再設計を開始してよく、全体的なマスクパターンを異なる方法で分解しようと試みてよく、あるいは適切と思われる他のアクションをとってよい。また、ここでは詳細には説明しないが、上述した技術及び手法を用いて 2 つ以上の遮断マスクパターンを生成し且つ使用することが望ましいであろうし又は必要であろう。例えば、いかなる違反をも伴わずに単一の遮断マスクパターンが生成され得ない場合には、多重遮断マスクパターンが用いられてよい。

#### 【0047】

遮断マスク上の DRC がクリーンであり遮断マスクに設計規則違反が無い場合には、遮断マスクパターン及び／又は識別された違反に従って少なくとも 1 つの要素マスクパターンを修正することによって、プロセス 200 は継続してよい（タスク 214）。タスク 214 は、実行されるときに、所望のマスクパターン（例えば図 6 に示される第 2 の要素マスクパターン 302）に対応する予備データを修正して、修正されたマスクパターンを表す更新されたデータを得ることになる。タスク 214 は、修正されたマスクパターンに先端・先端間及び先端・線間の違反等の設計規則違反が無いように実行される。このように、タスク 214 の間に実行される修正は、識別された違反の寸法及び／又は遮断マスクパターン内の特徴部の寸法によって影響されることになる。

#### 【0048】

プロセス 200 は、全体のマスクパターンの特定のレイアウトに応じて、またタスク 204 が全体のマスクパターンをその要素マスクパターンへと分解する方法に応じて、要素マスクパターンの 1 つのみを、要素マスクパターンの全てを、又は要素マスクパターンの全てではないが幾つかを、修正することができる。ここに説明される単純な例は、第 1 の要素マスクパターン 300（図 2）は修正されずにそのまま残り、そして第 2 の要素マスクパターン 302（図 3）のみが修正されることを前提としている。この点に関して、図 8 は第 2 の要素マスクパターン 302 の修正されたバージョンの平面図である。修正されたマスクパターン 340 の例示的な実施形態は、第 2 の要素マスクパターン 302 の全てのマスク特徴部に加えて、識別された違反 308 / 310 に対応する空間又は空隙を「埋める(fill in)」追加的なマスク特徴部を含む。従って、第 2 の要素マスクパターン 30

10

20

30

40

50

2のための予備データは、更新されたデータが、識別された違反308/310の代わりに規定される特徴部を有する第2の要素マスクパターン302の結合された又は融合されたバージョンを表すように、修正される。つまり、元の第2の要素マスクパターン302が処理されて、そして識別された違反308/310を、規定された特徴部で置換することによって、修正されたマスクパターン340へと変化させられる。

#### 【0049】

図8を参照すると、修正されたマスクパターン340は、第2の要素マスクパターン302内で見出される2つのマスク特徴部304を各々が包含する3つの結合されたマスク特徴部342を含む。特に、結合されたマスク特徴部342の各々は、先端・先端間又は先端・線間の違反を有していない单一且つ連続的な特徴部である。修正されたマスクパターン340はまた、第2の要素マスクパターン302内で見出される2つのマスク特徴部306を各々が包含する4つのU型の結合されたマスク特徴部344を含む。特に、U型の結合されたマスク特徴部344の各々は、先端・先端間又は先端・線間の違反を有していない单一且つ連続的な特徴部である。修正されたマスクパターン340はまた、3つの拡張されたマスク特徴部346を含み、それらの各々は、第2の要素マスクパターン302の境界の近くに位置するそれぞれのマスク特徴部304の拡張されたバージョンを表す。同様に、修正されたマスクパターン340は、4つの拡張されたL型のマスク特徴部348を含み、それらの各々は、第2の要素マスクパターン302の境界の近くに位置するそれぞれのマスク特徴部306の拡張されたバージョンを表す。修正されたマスクパターン340上の特徴部は、結果として得られる、半導体基板上に形成されるフォトトレジスト材質のパターンが、マスク特徴部342/344/346/348に対応する輪郭を有する空間又は穴を含むことになるという理由で、「ネガティブ」である。つまり、マスク特徴部342/344/346/348が存在する場所ではどこでもフォトトレジスト材質が欠如していることになる。修正されたマスクパターン340にはいかなる設計規則違反も無く、そして修正されたマスクパターン340上でのDRCはクリーンな結果を戻すことになる。

#### 【0050】

再び図4を参照すると、タスク214の実行は、要素マスクパターンの修正されたセットをもたらし、修正されたセットにおける各マスクパターンには先端・先端間及び先端・線間の違反が無い。プロセス200は次いで、複数の元の要素マスクパターン、单一又は複数の修正されたマスクパターン、及び单一又は複数の遮断マスクパターンに対するデータを保存する(タスク216)。このデータは次いで、单一又は複数の遮断マスクパターンのためのフォトリソグラフィマスク及び要素マスクパターンの修正されたセットのためのフォトリソグラフィマスクを生成/作製するために用いられ得る。この例では、3つの異なるフォトリソグラフィマスクが生成されることになり、即ち元の第1の要素マスクパターン300を規定するマスクと、修正されたマスクパターン340を規定するマスクと、遮断マスクパターン320を規定するマスクと、である。これらのマスクは次いで、半導体デバイス(例えばSRAMデバイス)の製造に際して特定の半導体デバイス特徴部を形成するために利用される。この点に関して、図9~20を参照して例示的な製造プロセスが説明される。

#### 【0051】

図9~20は、多重露光/パターニング製造プロセスに供される半導体デバイス構造の断面図及び平面図を含む。この製造プロセスは、デバイス特徴間での極めて密接した許容誤差及び/又は極めて狭い線幅を有する半導体デバイスを製造するために採用され得る。簡素化及び一貫性のために、この製造プロセスは、上述した3つのフォトリソグラフィマスク、即ち第1の要素マスク、修正されたマスク、及び遮断マスクを利用する。このように、ここに説明される例示的な製造プロセスは、SRAMデバイス構造上のデバイス特徴部を作製するために用いられ得る。

#### 【0052】

図9は目標材質が形成された後の例示的な半導体デバイス構造400を示している。ブ

10

20

30

40

50

ロセスのこの時点では、半導体デバイス構造 400 は、限定はされないが、半導体材質 402 の層と、半導体材質 402 の層の上の絶縁材質 404 の第 1 の層と、絶縁材質 404 の第 1 の層の上に形成される 2 つのゲート構造 405 と、絶縁材質 404 の第 1 の層の上でゲート構造 405 を覆う絶縁材質 406 の第 2 の層と、絶縁材質の第 2 の層の上のハードマスク材質 408 の層と、を含む。図 2 を参照すると、図 9 ~ 20 に含まれる断面図は 2 つのゲート構造に近接する先端・先端間ローカル相互接続領域に対応するが、ローカル相互接続の先端間には活性半導体領域は配置されていない。半導体デバイス構造 400 の断面構成は、ゲート構造を含まない領域、活性半導体領域を含む領域、等で異なるであろうことが理解されるべきである。

## 【0053】

10

半導体材質 402 は、望ましくは、半導体産業において典型的に用いられるようなシリコン材質、例えば比較的に純粋なシリコンの他、ゲルマニウム、炭素、等の他の元素が添加されたシリコンである。代替的には、半導体材質 402 は、ゲルマニウム、ガリウム砒素、等であってよい。半導体材質 402 は N 型又は P 型のいずれであってもよいが、典型的には、内部に形成される適切な型のウエルを伴う P 型である。半導体材質 402 はバルク半導体基板として提供されてよいし、あるいはサポート基板、サポート基板上の絶縁層、及び絶縁層上のシリコン材質の層を含むシリコン・オン・絶縁体 (SOI) 上で提供されてもよい。

## 【0054】

20

この実施形態では、絶縁材質 404 の第 1 の層は、半導体デバイス構造のための深い溝分離(shallow trench isolation) (STI) を表す。特定の実施形態においては、絶縁材質 404 の第 1 の層のために用いられる STI 材質は、オルトケイ酸テトラエチル(tetraethyl orthosilicate) (TEOS) 酸化物、高密度プラズマ酸化物、等の酸化物材質である。絶縁材質 406 の第 2 の層は、埋められてローカル相互接続の所望のパターンを作製する溝を形成するために用いられる。製造プロセスのこの時点では、絶縁材質 406 の第 2 の層はゲート構造 405 を密閉している(ゲート構造 405 は単純化してブロックとして図示されているが、実際にはゲート構造 405 の各々は、よく知られているように、種々の材質層の積層物として実現され得る)。実施形態に応じて、絶縁材質 406 の第 2 の層は、限定はされないが、TEOS 酸化物等の酸化物材質を含んでいてよい。半導体デバイス構造は、典型的には、絶縁材質 404 の第 1 の層と絶縁材質 406 の第 2 の層の間に、薄いコンタクトエッティング停止層(例えば窒化物層)を含むであろうことが理解されるべきである。この薄いコンタクトエッティング停止層は図 9 には図示されていない。典型的な実施形態においては、絶縁材質 406 の第 2 の層は、約 100 nm ~ 約 250 nm の範囲内の厚みを有しているが、必要に応じて他の厚みが用いられてもよい。

30

## 【0055】

ハードマスク材質 408 の層は、例えば、化学気相堆積 (CVD)、低圧 CVD (LPCVD)、プラズマ強化 CVD (PECVD)、大気圧 CVD (APCVD)、物理気相堆積 (PVD)、原子層堆積 (ALD) 等の適切な堆積技法を用いて絶縁材質 406 の第 2 の層の上に形成される。幾つかの実施形態においては、ハードマスク材質 408 の層を覆うように反射防止膜の層(図示せず)が形成されてもよい。種々の実施形態において、反射防止膜は、1 つ以上の有機底部反射防止膜(bottom anti-reflective coating) (BARC) 層、無機 BARC 層、及び有機・無機混成 BARC 層を含み得る。望ましい実施形態は CVD 材質を用いるが、代替的な実施形態においては、ハードマスク材質 408 は熱的に成長させられた材質であってもよい。実用上は、ハードマスク材質 408 は窒化物、望ましくはシリコン窒化物、等の誘電体材質であり、またハードマスク材質 408 は約 20 nm ~ 約 500 nm の典型的な厚みで形成されるが、実施形態に応じてこの典型的な範囲外の厚みであってもよい。ハードマスク材質 408 はまた、シリコンカーバイド、酸素ドープのシリコンカーバイド、窒素ドープのシリコンカーバイド、酸素ドープのシリコン窒化物、炭素ドープのシリコン窒化物、並びに酸素及び炭素ドープのシリコン窒化物の 1 つ以上を備えていてもよい。

40

50

## 【0056】

ハードマスク材質408の層を設けた後、製造プロセスは、適切なフォトリソグラフィマスクを用いて多重露光／パターニングフォトリソグラフィ手順を実行することによって継続してよい。この例では、半導体デバイス構造400上に初期フォトレジスト特徴部を形成するために、第1の要素マスクパターン300及び修正されたマスクパターン340に対応するマスクが用いられる。図10はハードマスク材質408の層の上のフォトレジスト材質414内に特徴部の組み合わされたパターンが形成された後の半導体デバイス構造412の平面図であり、図11は図10における11-11線から見た半導体デバイス構造412の断面図である。図11はフォトレジスト材質414内に形成されるネガティブマスク特徴部416を示している。図10に示されるように、このネガティブマスク特徴部416は、修正されたマスクパターンに関連する結合された水平特徴部の1つを表す。図10に示されるように、フォトレジスト材質414は、その内部に形成される複数のネガティブマスク特徴部を含む。上述した理由により、これらのフォトリソグラフィステップの結果として、先端・先端間及び先端・線間の設計規則違反の無いフォトレジスト特徴部の結合されたパターンがもたらされる。

## 【0057】

製造プロセスは次いで、フォトレジスト特徴部の結合されたパターンをエッチングマスクとして用いてハードマスク材質408の層を選択的にエッチングすることによって継続し得る。図12はハードマスク材質408の層がエッチングされた後の半導体デバイス構造420を示している。このステップで用いられるエッチング技法及びエッチング薬品は、ハードマスク材質408（例えば窒化物材質）の層が選択的に除去される一方で、フォトレジスト材質414及び下層の絶縁材質406の第2の層は無傷で残るように選択される。適切な化学的及び／又は物理的なエッチング技法並びにエッチング薬品が用いられてよく、これらは、限定はされないが、フッ素ベースのプラズマエッチング、反応性イオンエッチング、フッ素ベースの化学薬品エッチング、代替的にはアルゴン及び酸素を含む。このエッチングステップの結果、ハードマスク材質408の層内に凹部線パターン(recесs line pattern)422が形成される。この点において、残っているハードマスク材質408はポジティブハードマスクパターンに対応し、その中に規定されるネガティブ凹部線パターン422を伴っている。図12に示されるように、凹部線パターン422は、フォトレジスト材質414内に存在する特徴部を伴い自己整合の様態で形成される。つまり、凹部線パターン422は、フォトレジスト特徴部の結合されたパターンによって規定されることになる。その結果、凹部線パターン422の平面図は図10に示されるのと同じ概観を有することになり、また凹部線パターン422の少なくとも幾つかは二方向凹部線を含むことになる。

## 【0058】

製造プロセスは、ハードマスク材質408からフォトレジスト材質414を除去することによって継続し、結果として図13に示される半導体デバイス構造430をもたらす。凹部線パターン422は、フォトレジスト材質414の除去の後にもハードマスク材質408によって規定されたままである。その後、製造プロセスは、凹部線パターン422の指定された区画を覆うフォトレジスト特徴部の遮断パターンを形成する。図14はフォトレジスト特徴部の遮断パターン442の形成の後の半導体デバイス構造440の状態を示している。この例では、ハードマスクエッチングステップは第2の絶縁材質406の一部を露出させる一方で、第2の絶縁材質406の他の部分はフォトレジスト材質414によって保護され続けている。フォトレジスト特徴部の遮断パターン442は、図14に示されるように、第2の絶縁材質406の露出された部分の一部上に形成され、又は第2の絶縁材質406の露出された部分の一部の上にある。

## 【0059】

このフォトレジスト特徴部の遮断パターン442は、図7に示される遮断マスクパターン320に対応するフォトリソグラフィマスクを用いてフォトレジスト材質の層を露光することによって作製され得る。露光されたフォトレジスト材質が現像された後、残ってい

10

20

30

40

50

るフォトレジスト材質はフォトレジスト特徴部の遮断パターン442を表す。上述した理由により、フォトレジスト特徴部の遮断パターン442には、先端・先端間及び先端・線間の設計規則違反が無いはずである。図15はフォトレジスト特徴部の遮断パターン442の作製の後の半導体デバイス構造440の平面図である。図15は図14の視点を示す断面線14-14を含む。特に、フォトレジスト特徴部の遮断パターン442は多数の個別ブロックを含み、それらの各々は絶縁材質406の第2の層の上にある。また、フォトレジスト特徴部の遮断パターン442は、凹部線パターン422内に規定される1つ以上の凹部線と交差する。図15に示される実施形態では、ブロックは凹部線と重なり、また、先端・先端間の違反の次元に対して直交する方向において凹部線の境界を越えて延在している（隣接する特徴部を邪魔することなしに）。 10

#### 【0060】

製造プロセスは、ハードマスク材質408及びフォトレジスト特徴部の遮断パターン442をエッチングマスクとして用いて絶縁材質406の第2の層を選択的にエッチングすることによって進行してよい。図16は絶縁材質406の第2の層がエッチングされた後の半導体デバイス構造450を示している。このステップで用いられるエッチング技法及びエッチング薬品は、絶縁材質406（例えば酸化物）の第2の層が選択的に除去される一方で、ハードマスク材質408、フォトレジスト特徴部の遮断パターン442のために用いられるフォトレジスト材質、ゲート構造405、及び絶縁材質404の下層の第1の層が実質的に無傷で残るように選択される。図16に示される溝452は、それらが絶縁材質404の第1の層で又はその近傍で終了するように形成される。実際上は、このエッチングステップは、絶縁材質404の第1の層内に何らかの僅かな溝を形成することがあるが、これらの溝は、全体的な製造プロセス又は結果として得られるデバイスの性能に不利な影響を与えないように制御され得る。一例としては、適切なエッチング技法及びエッチング薬品は、限定はされないが、フッ素ベースの化学的エッチングを含む。このエッチングの結果、溝452のパターンが絶縁材質406の第2の層内に形成される。図16に示されるように、溝452のパターンは、ハードマスク材質408及びフォトレジスト特徴部の遮断パターン442を伴い自己整合の様態で形成される。つまり、溝452のパターンは、フォトレジスト特徴部の遮断パターン442及びハードマスク材質408によって規定されることになる。その結果、溝452のパターンの平面図は図15に示されるのと同じ概観を有することになり、また溝452のパターンにおける少なくとも1つの溝は二方向的になる。 20

#### 【0061】

特に、フォトレジスト特徴部の遮断パターン442は、修正されたマスクパターン340（図8）内で規定される特徴部の全てが実際に実現されることのないように、絶縁材質406の第2の層の区域を保護する。また、フォトレジスト特徴部の遮断パターン442は識別された違反308/310（図6）に基づいているので、結果として得られる溝452のパターンは、半導体デバイスのために元々設計された全体的なマスクパターンに対応する。 30

#### 【0062】

前述したように、図16の断面図は、下層の活性半導体領域を含まない半導体デバイス構造450のロケーションに対応している。下層の活性半導体領域を含む半導体デバイス構造450の区域に対しては、溝452のパターンは、基板の1つ以上の追加的な層又は領域（図16に示される断面以外の断面、例えば図16の紙面の更に向こう側又は手前側に位置しているであろう）内へと延びてよい。例えば、半導体デバイス構造450の特定の区域内では、少なくとも1つの溝は、ゲート構造が溝内に位置しないように形成され得る。更に別の例では、半導体デバイス構造450の特定の区域内では、少なくとも1つの溝が活性トランジスタ領域、例えばソース領域又はドレイン領域で終了するようにこれを形成する必要があるかもしれない。 40

#### 【0063】

製造プロセスは、フォトレジスト特徴部の遮断パターン442及びハードマスク材質4

08を除去することによって進行し、図17に示される半導体デバイス構造460を結果としてもらたす。実用上は、フォトレジスト特徴部の遮断パターン442は、例えば選択的ウエット化学エッチングを用いて除去され、またハードマスク材質408は、例えば選択的プラズマエッチング又は選択的化学エッチングを用いて除去される。用いられる具体的な材質に応じて、単一のエッチングプロセスを用いてフォトレジスト特徴部の遮断パターン442及びハードマスク材質408を除去することも可能であろう。

#### 【0064】

製造プロセスは、少なくとも部分的に溝を電気伝導性材質で埋めることによって継続する。特定の実施形態においては、溝は電気伝導性材質で完全に埋められる。実際には、製造プロセスは典型的には溝を「過充填し(overfill)」、絶縁材質406の第1の層の上に幾分かの過重荷(overburden)が結果としてもたらされることになる。結果として得られる半導体デバイス構造470が図18に示されている。図18に示されるように、溝は電気伝導性材質472aで埋められてしまっており、また電気伝導性材質472bが絶縁材質406の第1の層の上にも形成されている。更に、電気伝導性材質472aはゲート構造405の上でこれを覆っている（従って、ゲート構造405の電気伝導性要素、例えばシリサイドコンタクト領域、が電気伝導性材質472aに電気的に結合されることになる）。特定の実施形態においては、電気伝導性材質472は、例えばCVDプロセス、スパッタリングプロセス等を用いて堆積させられる金属材質（例えばタンクステン材質、銅材質、等）である。

#### 【0065】

電気伝導性材質472aが堆積させられた後、製造プロセスは電気伝導性材質472bの過重荷部分を除去し、その結果として図19に示される半導体デバイス構造480がもたらされる。電気伝導性材質472bの過重荷部分は、例えば絶縁材質406の第2の層の上面が露出させられた後に停止する化学的機械研磨手順を用いて除去される。従って、電気伝導性材質472aの露出された表面は、絶縁材質406の第2の層の露出させられた表面と共に実質的に平坦である。

#### 【0066】

半導体デバイス構造480上に結果として得られる電気伝導性材質472aのレイアウトは、半導体デバイスのための導電性ローカル相互接続の所望のパターンを表す。図20はローカル相互接続の作製の後の半導体デバイス構造480の平面図であり、ローカル相互接続は電気伝導性材質472を備えている。図20は図19の視点を表す断面線19-19を含む。特に、ローカル相互接続のパターンは、絶縁材質406の第2の層の区域によって囲まれる電気伝導性材質472の多数の区別可能なセグメント(distinct segments)を含む。図20に示されるローカル相互接続のパターンは、図2に示されるSRAMセルのアレイ150に用いられるものに対応する。

#### 【0067】

半導体デバイス構造480のためのローカル相互接続が作製された後、半導体デバイス又は基板上デバイスの製造を完了するために、任意の数の追加的なプロセスステップが行われ得る。これらのバックエンドプロセスステップはここでは詳述しない。

#### 【0068】

上述の詳細な説明においては少なくとも1つの例示的な実施形態が提示されたが、多数の変形が存在することが理解されるべきである。また、ここに説明される例示的な1つ以上の実施形態は、特許請求の範囲に記載された主題の範囲、応用、又は構成を限定することは決して意図されていないことが理解されるべきである。むしろ、上述の詳細な説明は、説明される1つ以上の実施形態を実装するのに役立つ指針を当業者に提供するはずである。特許請求の範囲によって規定される範囲から逸脱することなしに、要素の機能及び範囲において種々の変更がなされ得ることが理解されるべきであり、特許請求の範囲によって規定される範囲は、この特許出願の時点での既知の均等なもの及び予測可能な均等なものと含む。

10

20

30

40

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

FIG. 9

【図10】

FIG. 10

【図11】

FIG. 11

【図12】

FIG. 12

【図13】

【図14】

【図15】

【図16】

【図17】

FIG. 17

【図18】

FIG. 18

【図19】

FIG. 19

【図20】

FIG. 20

---

フロントページの続き

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 リチャード シュルツ

アメリカ合衆国、コロラド州 80526、フォート コリンズ、ウィッジン ストリート 42

43

審査官 新井 重雄

(56)参考文献 特開2008-153373(JP,A)

特開2006-294942(JP,A)

特開2004-247606(JP,A)

特開2002-182363(JP,A)

特開2010-118599(JP,A)

特開2005-259991(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/027

G03F 1/50

H01L 21/8244

H01L 27/11