(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-222299

(P2004-222299A)

(43) 公開日 平成16年8月5日(2004.8.5)

(51) Int.C1.<sup>7</sup>

H04L 29/14

H04B 1/38

F 1

H04L 13/00

H04B 1/38

315

テーマコード(参考)

5K011

5K035

審査請求 未請求 請求項の数 1 O L (全 11 頁)

(21) 出願番号 特願2004-7272 (P2004-7272)

(22) 出願日 平成16年1月14日 (2004.1.14)

(31) 優先権主張番号 10/346480

(32) 優先日 平成15年1月15日 (2003.1.15)

(33) 優先権主張国 米国(US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

AGILENT TECHNOLOGIE

S, INC.

アメリカ合衆国カリフォルニア州パロアル

ト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 100075513

弁理士 後藤 政喜

(74) 代理人 100084537

弁理士 松田 嘉夫

最終頁に続く

(54) 【発明の名称】トランシーバシステム

## (57) 【要約】

【課題】顧客又はエンドユーザによるアクセス又はその変更を防止しつつ、製造業者によるトランシーバ内の特定情報へのアクセスとその変更を許容できるようにする。

【解決手段】本発明のトランシーバシステムはホスト(110)と、前記ホスト(110)に接続されたトランシーバ(120)とを有し、前記トランシーバは、ホストから第1要求を受信するべく構成されると共に、前記トランシーバは、前記第1要求の受信に応答し、試験モード動作に入るべく構成されている。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

ホストと、

前記ホストに接続されたトランシーバと、を有し、

前記トランシーバは、前記ホストから第1要求を受信し、前記第1要求の受信に応答し試験モード動作に入ることを特徴とするトランシーバシステム。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、トランシーバに関し、更に詳しくは、試験モード動作を有するトランシーバ 10 とトランシーバシステムに関するものである。

**【背景技術】****【0002】**

トランシーバやその他の電子デバイスの場合、デバイスを適切に動作させるために、事前にデバイスの1つ又は複数の構成要素に対して較正又は調整機能を実行することが必要である。これらの較正又は調整機能を正しく実行しなければ、トランシーバが誤動作する可能性があるため、これらの較正及び調整機能は、通常、製造業者又は認可されたサービス技術者によって実行される。トランシーバの顧客又はその他のエンドユーザが、これらの較正又は調整機能にアクセスすることは、通常、許されてはいない。

**【0003】**

トランシーバ内に設置する前に、いくつかの構成要素に対して、これらの較正及び調整機能を実行可能なトランシーバも存在する。これらのトランシーバの場合、較正及び調整機能に使用する様々なパラメータや定数がトランシーバ内に保存されており、トランシーバに接続されたホストが、この情報にアクセスしたり、この情報を変更したりすることはできないようになっている。

**【0004】**

しかしながら、その他のトランシーバの場合には、較正及び調整機能に使用する様々なパラメータや定数に、ホストからアクセス可能であり、且つ／或いは、これらの情報をホストが変更することができる。これらの情報は、ホストからアクセス可能であってもよいが、製造業者としては、装置の動作を適切且つ安全なものにするべく、顧客又はエンドユーザによるトランシーバ内の情報へのアクセスとその変更の防止を望むであろう。 30

**【発明の開示】****【発明が解決しようとする課題】****【0005】**

従って、顧客又はエンドユーザによる情報へのアクセス又はその変更を防止しつつ、製造業者によるトランシーバ内の特定情報へのアクセスとその変更を許容できるようにすることが課題である。

**【課題を解決するための手段】****【0006】**

本発明では、ホストと、このホストに接続されたトランシーバと、を有するトランシーバシステムを提供するものであり、トランシーバは、ホストから要求を受信し、この要求の受信に応答して試験モード動作に入るべく構成されている。 40

**【発明を実施するための最良の形態】****【0007】**

好適な実施例に関する以下の詳細な説明においては、本明細書の一部を形成する添付の図面を参照しており、それらの図面には、例として、本発明を実施可能な特定の実施例が示されている。本発明の範囲を逸脱することなく、その他の実施例を利用することも可能であり、構造的又は論理的な変更を加えることも可能であることを理解されたい。従って、以下の詳細な説明は、限定を目的とするものとして解釈されることはならず、本発明の範囲は、添付の特許請求の範囲によって定義されるものである。 50

## 【0008】

本明細書においては、試験モード動作を有するトランシーバについて例示し説明する。トランシーバは、電源投入又はリセットに応答し、そのトランシーバに関連するすべての較正段階が完了しているかどうかを判定する。そして、すべての段階が完了していない場合には、トランシーバは試験モード動作に入り、ホストと共に較正段階を実行する。次いで、すべての段階が成功裏に完了した後に、トランシーバは顧客モード動作に入り、そのトランシーバのエンドユーザへの出荷準備が完了したことを示す。1つ又は複数の段階が成功裏に完了しない場合には、それらの段階を再試行すると共に／或いは、トランシーバに対して故障解析技法を適用することができる。ホストは、適切な要求をトランシーバに對して出すことにより、トランシーバを試験モード動作に再設定することができる。

10

## 【0009】

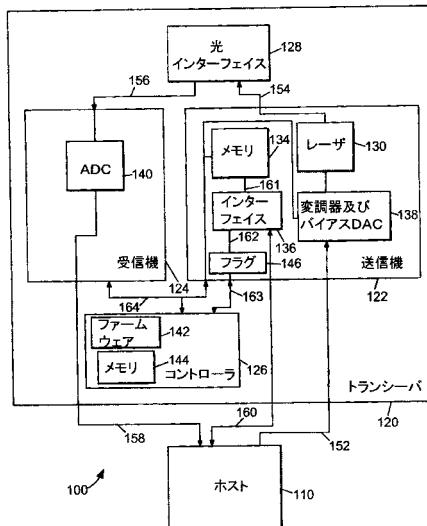

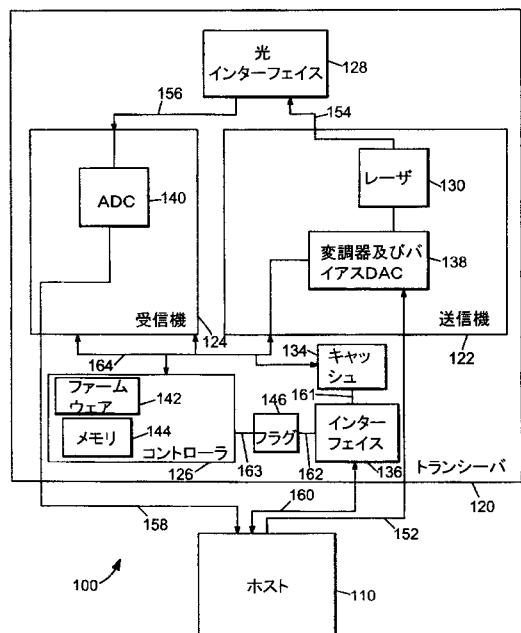

図1は、試験モード動作を有するトランシーバ120を含むトランシーバシステム100の実施例を示すロックダイアグラムである。図1に示されているように、トランシーバ120には、ホスト110が接続されている。トランシーバ120には、送信機122、受信機124、コントローラ126、及び光インターフェイス128が含まれている。送信機122には、レーザ130、メモリ134、インターフェイス136、変調器及びバイアスD/Aコンバータ(DAC)138、及びフラグ146が含まれている。受信機124には、A/Dコンバータ(ADC)140が含まれている。コントローラ126には、ファームウェア142とメモリ144が含まれている。

20

## 【0010】

ホスト110は、トランシーバ120と共に動作するべく構成された有線又は無線装置であれば、どのようなタイプのものであってもよい。ホスト110は、トランシーバ120の外付けになっている。このような装置の例には、試験システム、サーバーコンピュータシステム、パーソナルコンピュータシステム、ラップトップコンピュータシステム、携帯コンピュータシステム、携帯情報端末、及び携帯電話が含まれる。

## 【0011】

トランシーバ120は、以下に詳述するように、電気信号を送受信することによってホスト110と通信するべく構成された光トランシーバを備える。又、トランシーバ120は、光インターフェイス128を使用して光信号を送受信することにより、別の装置(図示されてはいない)とも通信する。光インターフェイス128は、ファイバチャネルインターフェイスやその他のタイプの光インターフェイスであってよい。

30

## 【0012】

一実施例においては、トランシーバ120は、SFF(Small Form Factor)委員会が規定する光トランシーバ用のデジタル診断監視インターフェイスに関するSFF-8472規格に準拠している。その他の実施例においては、トランシーバ120は、その他の規格に準拠したものであってよい。

40

## 【0013】

送信機122は、動作上、接続152を使用してホスト110からデジタル出力信号を受信するべく構成された光送信機を備える。変調器及びバイアスDAC138により、このデジタル出力信号がアナログ出力信号に変換され、このアナログ出力信号がレーザ130に供給される。これらのデジタル出力信号及びアナログ出力信号は、電気信号を含む。レーザ130は、このアナログ出力信号に応答して光出力信号を生成し、この光出力信号が接続154を使用して光インターフェイス128に供給される。

40

## 【0014】

受信機124は、接続156を使用して光インターフェイス128から光入力信号を受信するべく構成された光受信機を備える。A/Dコンバータ140により、この光入力信号がアナログ入力信号からデジタル入力信号に変換され、このデジタル入力信号が接続158によってホスト110に供給される。これらのデジタル出力信号及びアナログ出力信号は、電気信号を含む。

## 【0015】

50

トランシーバ120は、電気的接続160を使用してホスト110とも通信する。具体的には、トランシーバ120は、接続160を使用してホスト110から制御信号を受信する。更に、トランシーバ120は、接続160を使用してホスト110に情報を提供する。図1の実施例において、電気的接続160は、ホスト110を送信機122に接続しており、この接続は、[http://www.semiconductors.philips.com/acrobat/variables/I2C\\_BUS\\_SPECIFIC\\_ATION\\_3.pdf](http://www.semiconductors.philips.com/acrobat/variables/I2C_BUS_SPECIFIC_ATION_3.pdf)に存在するフィリップス半導体社(Philips Semiconductors)が提供するI2Cバス規格によって提供されるI2C接続であり、インターフェイス136は、I2Cバスインターフェイスから構成されている。更に、接続160及びインターフェイス136は、<http://www.atmel.com/atmel/acrobat/doc0180.pdf>に存在するアトメル社(ATMEL)が提供するATMEL AT24C01A/02/04データシートによって提供されるATMEL AT24C01A/02/04ファミリー構成要素用に定義された2線シリアルCMOS EEPROMプロトコルに準拠している。

#### 【0016】

インターフェイス136は、ハードウェア、或いはハードウェア及びソフトウェア構成要素の組み合わせを備え得る。メモリ134は、情報を保存するべく構成されたどのようなタイプの揮発性又は不揮発性メモリであってもよい。図1の実施例においては、メモリ134はSRAMで構成されている。

#### 【0017】

コントローラ126は、接続164を使用して送信機122及び受信機124に制御信号を供給すると共に、これらからフィードバック信号を受信する。図1の実施例においては、接続164は、[http://www.semiconductors.philips.com/acrobat/variables/I2C\\_BUS\\_SPECIFICATION\\_3.pdf](http://www.semiconductors.philips.com/acrobat/variables/I2C_BUS_SPECIFICATION_3.pdf)に存在するフィリップス半導体社(Philips Semiconductors)が提供するI2Cバス規格によって提供される内部I2C接続であり、コントローラ126はマスタとして機能し、送信機122及び受信機124はスレーブとして機能する。その他の実施例においては、接続164は、その他のどのようなタイプのシリアル又はパラレル接続であってもよい。

#### 【0018】

コントローラ126には、制御信号を生成しフィードバック信号を受信並びに処理するべくコントローラ126が実行可能なファームウェア142が含まれている。その他の実施例においては、コントローラ126は、本明細書で説明する機能を実行するべく、他のハードウェア及び/又はファームウェア又はソフトウェアの組み合わせを含むことができる。メモリ144は、レジスタ、フラッシュメモリ、RAM、又はEEPROMを含むどのようなタイプの揮発性及び不揮発性記憶装置、或いは、それらの組み合わせであってもよい。

#### 【0019】

トランシーバ120の動作モードには、試験モードと顧客モードという少なくとも2つのものが含まれている。いずれのモードにおいても、トランシーバ120は、ホスト110と共に動作する。試験モード動作においては、ホスト110は、トランシーバ120に対して較正段階を実行する。この較正段階には、トランシーバ120に情報を保存する段階と、送信機122、受信機124、及びトランシーバ120のその他の構成要素を較正及び又は調整する段階と、が含まれる。保存する情報には、製造情報、生産情報、装置情報、レビジョン情報、レーザ130の較正定数を含む送信機122の設定及びパラメータ、OMA(optical modulation amplitude)テーブルを含む受信機124の設定及びパラメータ、クロック情報、温度係数情報、温度/Vcc較正定数、及びEEPROM情報が含まれる。

#### 【0020】

試験モード動作においては、トランシーバ120は、トランシーバ120の構成要素に

10

20

30

40

50

対して自己試験を実行し、それぞれの構成要素の機能とレビジョン情報を検証することができる。更に、トランシーバ120は、レジスタの内容などの状態情報をトランシーバ120の構成要素からホスト110に供給する。更に、試験モード動作において、トランシーバ120は、内部監視タスクを実行可能である。

#### 【0021】

試験モード動作においては、トランシーバ120は、ホスト110からの要求に応答して較正段階を実行する。ホスト110は、インターフェイス136を使用し、較正段階に関連する要求をトランシーバ120に出す。この要求には、コマンド、アドレス、コマンドに関連する情報が含まれ、コントローラ126に関連する装置アドレスも含まれる。インターフェイス136は、接続161を使用し、この要求をメモリ134内に保存する。

10 この要求に応答し、インターフェイス136は、要求を受信したことをコントローラ126に通知するフラグ146を接続162を使用して設定する。コントローラ126は、接続163を使用して定期的にフラグ146をポーリングし、インターフェイス136によってフラグ146が設定されたと判定した際に、コントローラ126は、接続164を使用してメモリ134内の要求にアクセスする。

#### 【0022】

コントローラ126は、要求に関連する較正段階を実行することにより、その要求を処理する。そして、その較正段階が完了すると、コントローラ126は、その段階が実行されたことを示す標識をメモリ144に保存する。又、コントローラ126は、接続164を使用してメモリ134内に、この標識を保存し、接続163を使用してフラグ146をクリアすることにより、ホスト110に対しても標識を供給する。インターフェイス136は、フラグ146のクリアを検出するか、或いは、メモリ134への保存を監視することにより、メモリ134内の標識を検出する。この標識の検出に応答し、インターフェイス136は、標識をホスト110に供給する。ホスト110は、この標識をメモリ(図示されてはいない)に保存する。次いで、ホスト110は、更なる較正段階を上述のように同様に実行することができる。

#### 【0023】

コントローラ126は、較正段階を完了するごとに、コントローラ126が、メモリ144内の情報にアクセスし、すべての較正段階が完了しているかどうかを判定する。この情報には、それぞれの段階が成功裏に完了しているかどうかを示すそれぞれの較正段階に関連する標識が含まれている。ある段階が実行されていないか、或いは、成功裏に実行されていない場合には、コントローラ126は、トランシーバ120を試験モード動作に保持する。そして、すべての段階が成功裏に実行されている場合に、コントローラ126は、トランシーバ120を顧客モード動作に設定する。

#### 【0024】

ホスト110は、それぞれの較正段階ごとにトランシーバ120から受信する標識によっても、すべての較正段階が成功裏に完了したかどうかを判定することができる。この標識は、それぞれの較正段階が成功裏に完了したかどうか、並びにエラーが発生したかどうかを示している。又、ホスト110は、トランシーバ120を試験モード動作から離脱させる要求をトランシーバ120に出すこともできる。この試験モード離脱要求に応答し、トランシーバ120は、トランシーバ120に対して実行した較正段階の中のどれが成功裏に完了しなかったのかを示す標識を供給する(成功裏に完了しなかった較正段階が存在する場合)。1つ又は複数の較正段階が成功裏に完了しなかったと判定した場合には、ホスト110は、トランシーバ120に対して故障解析機能を実行することができる。すべての較正段階が成功裏に完了したと判定された場合には、ホスト110は、トランシーバ120の顧客又はエンドユーザに対する出荷準備が完了したと判定可能である。

#### 【0025】

顧客モード動作においては、トランシーバ120は、通常、ホスト110と共に動作する。具体的には、トランシーバ120は、ホスト110から電気信号を受信し、この電気信号を光信号に変換し、この光信号を光インターフェイス128を使用して別の装置(図

10

20

30

40

50

示されてはいない)に供給する。更に、トランシーバ120は、光インターフェイス128を介してその他の装置から光信号を受信し、この光信号を電気信号に変換し、この電気信号をホスト110に供給する。顧客モード動作では、いずれの時点においても、ホスト110は、試験モードの設定要求をトランシーバ120に対して出すことにより、トランシーバ120を試験モード動作に再設定することができる。

#### 【0026】

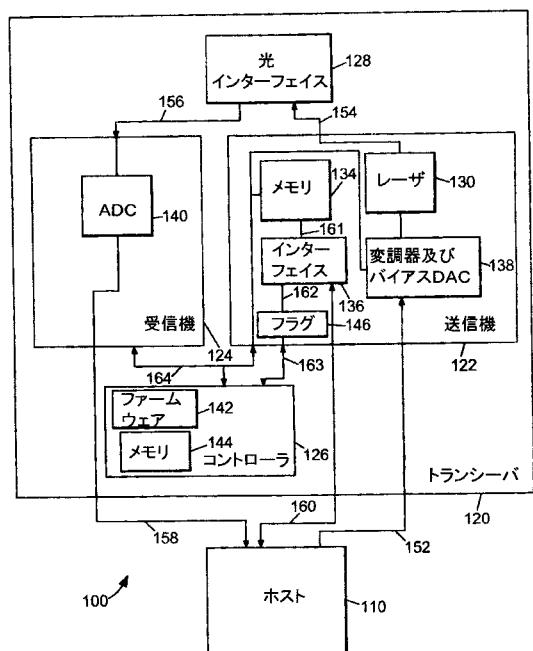

図2は、トランシーバの動作モードを変更する方法の実施例を示すフローチャートである。以下、図1を参照し、図2の方法の実施例について説明する。図2のブロック202に示されているように、コントローラ126は、トランシーバ120のすべての較正段階が完了しているかどうかを判定する。この判定は、トランシーバ120の電源投入(即ち、スイッチオン)又はリセットに応答して実行可能である。10

#### 【0027】

トランシーバ120のすべての較正段階が完了している場合には、トランシーバ120は、ブロック204に示されているように、顧客モード動作に入る。次いで、ブロック206に示されているように、ホスト110からの試験モード設定要求をコントローラ126が検出するかどうかを判定する。そして、コントローラ126が試験モード設定要求を検出した場合には、トランシーバは、ブロック208に示されているように、試験モード動作に入る。

#### 【0028】

トランシーバ120のすべての較正段階が完了していない場合には、トランシーバ120は、ブロック208に示されているように、試験モード動作に入る。次いで、ブロック210に示されているように、ホスト110からの要求をコントローラ126が検出しているかどうかを判定する。コントローラ126は、フラグ146をポーリングすることにより、要求を検出することができる。そして、コントローラ126がホスト110からの要求を検出していない場合には、この方法では、ブロック210の機能を再度反復実行する。コントローラ126がホスト110からの要求を検出している場合には、コントローラ126は、ブロック212に示されているように、その要求にアクセスする。コントローラ126は、メモリ134に存在する要求にアクセスする。そして、コントローラ126は、ブロック214に示されているように、その要求を処理する。20

#### 【0029】

ブロック216に示されているように、要求が成功裏に完了したかどうかを判定する。そして、要求が成功裏に完了しなかった場合には、コントローラ126は、ブロック218に示されているように、エラー標識をメモリ144内に保存する。又、コントローラ126は、ブロック220に示されているように、ホスト110に対してもエラー標識を供給する。このエラー標識は、メモリ134及びインターフェイス136を使用してホスト110に供給される。30

#### 【0030】

要求が成功裏に完了している場合には、コントローラ126は、ブロック222に示されているように、メモリ144内に成功標識を保存する。又、コントローラ126は、ブロック224に示されているように、ホスト110に対しても成功標識を供給する。この成功標識は、メモリ134及びインターフェイス136を使用してホスト110に供給される。40

#### 【0031】

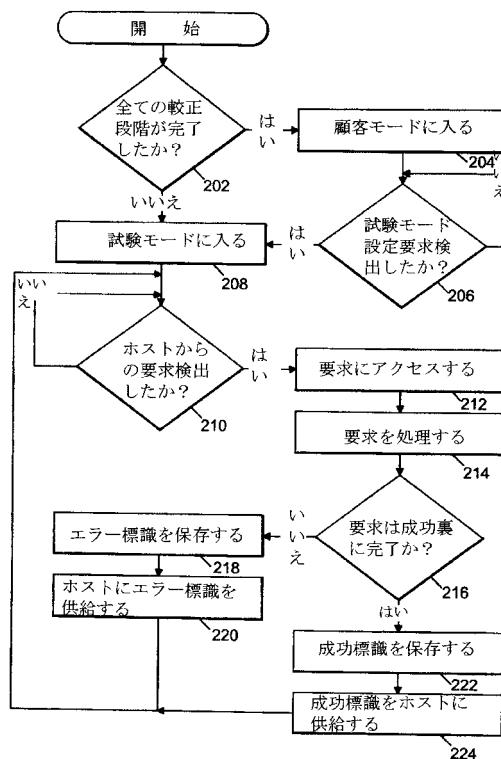

図3は、試験モード動作のトランシーバとやり取りする方法の実施例を示すフローチャートである。以下、図1を参照し、図3の方法の実施例について説明する。図3のブロック302に示されているように、ホスト110は、要求をトランシーバ120に対して出す。この要求は、較正段階の実行要求、又は試験モードの設定要求である。試験モードの設定要求により、トランシーバ120は試験モード動作に入り、較正段階の実行要求により、トランシーバ120に対してその較正段階が実行される。ブロック304に示されているように、ホスト110は、この要求に関連する標識を受信したかどうかを判定する。50

そして、ホスト 110 が、要求に関連する標識を受信していない場合には、ホスト 110 は、ブロック 306 に示されているように、トランシーバ 120 に関連するエラー状態を検出し、この方法は終了する。トランシーバ 120 は、較正段階の成功 / 不成功に關係なく、較正段階の実行に応答して標識を供給するように構成されているため、ホスト 110 が標識を受信しない場合には、エラー状態と見なすことができる。

#### 【0032】

ホスト 110 が要求に関連する標識を受信している場合には、ホスト 110 は、ブロック 308 に示されているように、この標識を保存する。次いで、ブロック 310 に示されているように、ホスト 110 は、実行を要する更なる較正段階が存在するかどうかを判定する。そして、実行を要する更なる較正段階が存在する場合には、この方法では、ブロック 302 の機能を反復実行する。実行を要する更なる較正段階が存在しない場合には、この方法は終了する。

10

20

30

40

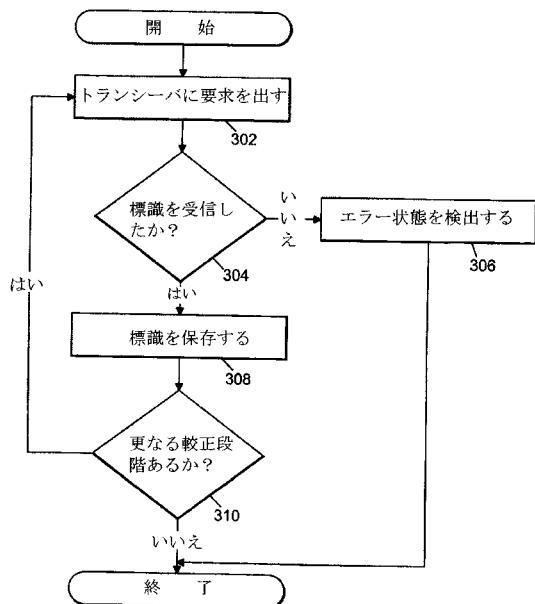

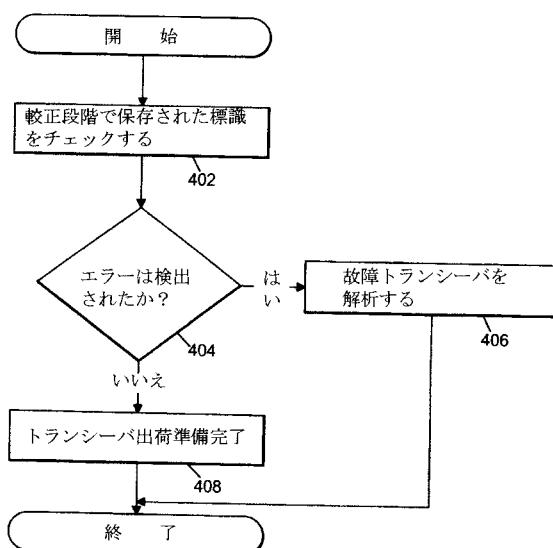

#### 【0033】

図 4 は、トランシーバの試験モード動作からエラーを検出する方法の実施例を示すフローチャートである。以下、図 1 を参照し、図 4 の方法の実施例について説明する。図 4 のブロック 402 に示されているように、ホスト 110 は、較正段階で保存された標識をチェックする。次いで、ブロック 404 に示されているように、ホスト 110 は、それらの標識を使用し、エラーが検出されているかどうかを判定する。そして、エラーが検出されている場合には、ホスト 110 は、ブロック 406 に示されているように、故障の発生したトランシーバ 120 を解析し、この方法は終了する。エラーが検出されていない場合には、ホスト 110 は、ブロック 308 に示されているように、トランシーバ 120 の出荷準備が完了したことを示す。

20

#### 【0034】

図 4 の別の実施例においては、ホスト 110 は、較正段階に関連する標識が保存された際に、即時にエラーを検出することができる。このエラーに応答し、ホスト 110 は、故障の修復を試みるか、或いは、故障の発生したトランシーバ 120 に対して 1 つ又は複数の故障解析機能を実行することができる。

#### 【0035】

図 5 は、試験モード動作を有するトランシーバを含むトランシーバシステムの別の実施例を示すブロックダイアグラムである。図 5 の実施例は、図 2 ~ 図 4 を参照して説明した図 1 の実施例と略同様に動作する。しかしながら、図 5 の場合には、キャッシュ 134 とインターフェイス 136 が送信機 122 には含まれていない。この実施例は、トランシーバ 120 のその他の部分又は構成要素にキャッシュ 134 とインターフェイス 136 を含むことができることを示すものである。

30

40

#### 【0036】

本明細書においては、好適な実施例を説明するべく、特定の実施例について例示し説明しているが、当業者であれば、本発明の範囲を逸脱することなく、同一の目的を実現するべく適合された様々な代替及び / 又は等価実施例により、これらの例示及び説明した特定の実施例を置換可能であることを理解するであろう。化学、機械、電気機械、電気、及びコンピュータ分野における知識を有する者であれば、本発明が、一部を下記するが、様々な実施態様で実施可能であることを容易に理解するであろう。本出願は、本明細書において説明した好適な実施例のあらゆる適合や変形を包含するものである。従って、本発明を限定するものは、特許請求の範囲及びその等価物のみである。

#### 【0037】

(実施態様 1) : ホスト (110) と、前記ホスト (110) に接続されたトランシーバ (120) と、を有し、前記トランシーバは、ホストから第 1 要求を受信するべく構成されると共に、前記トランシーバは、前記第 1 要求の受信に応答し、試験モード動作に入るべき構成されていることを特徴とするトランシーバシステム。

#### 【0038】

(実施態様 2) : 前記トランシーバが、前記試験モード動作に入る前に、顧客モード動

50

作で動作することを特徴とする実施態様 1 に記載のトランシーバシステム。

【0039】

(実施態様 3) : 前記トランシーバは、前記ホストから第 2 要求を受信するべく構成されると共に、前記トランシーバは、前記第 2 要求の受信に応答し、較正段階を実行するべく構成されていることを特徴とする実施態様 1 に記載のトランシーバシステム。

【0040】

(実施態様 4) : 前記較正段階が、前記ホストから受信した情報を前記トランシーバ内に保存する段階を有することを特徴とする実施態様 3 に記載のトランシーバシステム。

【0041】

(実施態様 5) : コントローラ(126)と、前記コントローラに接続され、第 1 情報を含む第 1 メモリ(144)と、を有し、前記コントローラは、前記第 1 情報にアクセスするべく構成されると共に、前記コントローラは、較正段階が完了していないことを示す前記第 1 情報に応答し、試験モード動作に入るべく構成されていることを特徴とするトランシーバ。10

【0042】

(実施態様 6) : 前記コントローラは、電源投入に応答し、前記第 1 情報にアクセスするべく構成されていることを特徴とする実施態様 5 に記載のトランシーバ。

【0043】

(実施態様 7) : 前記コントローラは、前記較正段階が完了していることを示す前記第 1 情報に応答し、顧客モード動作に入るべく構成されていることを特徴とする実施態様 5 に記載のトランシーバ。20

【0044】

(実施態様 8) : 前記コントローラは、前記較正段階に関連する要求をホスト(110)から受信するべく構成されると共に、前記コントローラは、前記要求の受信に応答し、前記第 1 較正段階を実行するべく構成されていることを特徴とする実施態様 5 に記載のトランシーバ。

【0045】

(実施態様 9) : 前記コントローラは、前記第 1 較正段階の実行に応答し、顧客モード動作に入るべく構成されていることを特徴とする実施態様 8 に記載のトランシーバ。

【0046】

(実施態様 10) : 前記コントローラは、前記較正段階に関連するエラーの検出に応答し、標識を前記ホストに供給するべく構成されていることを特徴とする実施態様 8 に記載のトランシーバ。30

【0047】

(実施態様 11) : 前記コントローラは、前記較正段階が成功裏に完了したことを検出した際に、標識を前記ホストに供給するべく構成されていることを特徴とする実施態様 8 に記載のトランシーバ。

【図面の簡単な説明】

【0048】

【図 1】試験モード動作を有するトランシーバを含むトランシーバシステムの実施例を示すプロック図である。40

【図 2】トランシーバの動作モードを変更する方法の実施例を示すフローチャートである。

【図 3】試験モード動作のトランシーバとやり取りする方法の実施例を示すフローチャートである。

【図 4】トランシーバの試験モード動作からエラーを検出する方法の実施例を示すフローチャートである。

【図 5】試験モード動作を有するトランシーバを含むトランシーバシステムの別の実施例を示すプロック図である。

【符号の説明】

50

【 0 0 4 9 】

1 1 0 ホスト

1 2 0 トランシーバ

1 2 6 コントローラ

1 4 4 第 1 メモリ

【 図 1 】

【 図 2 】

【図3】

【図4】

【図5】

---

フロントページの続き

(72)発明者 ケビン ライド ウルフ

アメリカ合衆国 カリフォルニア 93905 サリナス セイジ・コート 908

(72)発明者 アンジェリン ヤング ロドリゲス

アメリカ合衆国 カリフォルニア 94303 イースト・パロ・アルト クラーク・コート 9

40

(72)発明者 ピーター エイチ. マホワルド

アメリカ合衆国 カリフォルニア 94022 ロス・アルトス サン・ジュアン・コート 71

F ターム(参考) 5K011 EA00 GA00 JA03 KA00 LA07

5K035 AA07 BB01 DD02 GG01 HH01 HH07