(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-123771

(P2014-123771A)

(43) 公開日 平成26年7月3日(2014.7.3)

(51) Int.Cl.

**H01L 27/146 (2006.01)**

**H04N 5/369 (2011.01)**

**H04N 101/00 (2006.01)**

F 1

H01L 27/14

H04N 5/335 690

H04N 101:00

F

テーマコード(参考)

4M118

5C024

審査請求 有 請求項の数 1 O L (全 19 頁)

(21) 出願番号 特願2014-52329(P2014-52329)

(22) 出願日 平成26年3月14日(2014.3.14)

(62) 分割の表示 特願2011-547189(P2011-547189)

の分割

原出願日 平成21年12月26日(2009.12.26)

(71) 出願人 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100126240

弁理士 阿部 琢磨

(74) 代理人 100124442

弁理士 黒岩 創吾

(72) 発明者 遠藤 信之

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

(72) 発明者 板野 哲也

東京都大田区下丸子3丁目30番2号キヤ

ノン株式会社内

最終頁に続く

(54) 【発明の名称】 固体撮像装置および撮像システム

## (57) 【要約】

【課題】 光電変換素子の特性の低下を抑制しつつ、周辺回路部のトランジスタの動作を高速にすることが可能となる。

【解決手段】 本発明の固体撮像装置は、光電変換素子および転送トランジスタのゲート電極とを有する第1の基板と、周辺回路部を有する第2の基板とを積層して構成され、第1の基板には高融点金属化合物層が設けられておらず、第2の基板には高融点金属化合物層が配される。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

光電変換素子と前記光電変換素子からの電荷を転送するための転送トランジスタのゲート電極が配された第1の基板と、

前記光電変換素子にて生じた電荷に基づく信号を読み出すための周辺回路部が配された第2の基板とを積層した固体撮像装置において、

前記第2の基板に高融点金属化合物層が配され、

前記第1の基板には高融点金属化合物層が配されていない固体撮像装置。

**【請求項 2】**

前記第1の基板の上部に、アルミニウム配線あるいは銅配線からなる配線層が配され、10

前記第2の基板の上部に、アルミニウム配線あるいは銅配線からなる配線層が配されていることを特徴とする請求項1に記載の固体撮像装置。

**【請求項 3】**

前記第1の基板と前記第2の基板との間に、前記高融点金属に対する拡散防止膜を有する請求項1あるいは2のいずれかに記載の固体撮像装置。

**【請求項 4】**

前記転送トランジスタのゲート電極が配された前記第1の基板の正面と、前記周辺回路部のトランジスタが形成された前記第2の基板の正面と、を対向して積層した請求項1あるいは2のいずれかに記載の固体撮像装置。

**【請求項 5】**

前記第1の基板と前記第2の基板との間に、前記高融点金属に対する拡散防止膜を有する請求項4項に記載の固体撮像装置。20

**【請求項 6】**

前記第1の基板の上部に配線層と、層間絶縁膜とが配され、

前記高融点金属に対する拡散防止膜は、前記第1の基板に配された層間絶縁膜であることを特徴とする請求項5に記載の固体撮像装置。

**【請求項 7】**

前記第2の基板の上部に配線層と、層間絶縁膜とが配され、

前記高融点金属に対する拡散防止膜は、前記第2の基板に配された前記層間絶縁膜であることを特徴とする請求項5に記載の固体撮像装置。30

**【請求項 8】**

前記高融点金属に対する拡散防止膜は、前記第2の基板に配された高融点金属化合物層を有するトランジスタの前記高融点金属化合物層に接して配されていることを特徴とする請求項5に記載の固体撮像装置。

**【請求項 9】**

少なくとも前記第1の基板あるいは前記第2の基板の上部に銅配線からなる配線層が配され、

前記銅配線からなる配線層の上部に、銅に対する拡散防止膜が配され、

前記銅に対する拡散防止膜が、前記高融点金属に対する拡散防止膜を兼ねることを特徴とする請求項5に記載の固体撮像装置。40

**【請求項 10】**

前記転送トランジスタのゲート電極とが配された前記第1の基板の正面と、前記周辺回路部においてトランジスタが形成された前記第2の基板の正面と反対の面と、が対向して積層された請求項1あるいは2のいずれかに記載の固体撮像装置。

**【請求項 11】**

前記第1の基板と前記第2の基板との間に、前記高融点金属に対する拡散防止膜を有する請求項10項に記載の固体撮像装置。

**【請求項 12】**

前記第1の基板の上部に配線層と、前記配線層に接して配される層間絶縁膜とが配され、

前記高融点金属に対する拡散防止膜は、前記第1の基板に配された層間絶縁膜であることを特徴とする請求項11に記載の固体撮像装置。

【請求項13】

前記高融点金属に対する拡散防止膜は、前記第2の基板の裏面に接して配されていることを特徴とする請求項11に記載の固体撮像装置。

【請求項14】

少なくとも前記第1の基板の上部に銅配線からなる配線層が配され、

前記銅配線からなる配線層の上部に、銅に対する拡散防止膜が配され、

前記銅に対する拡散防止膜が、前記高融点金属に対する拡散防止膜を兼ねることを特徴とする請求項11に記載の固体撮像装置。 10

【請求項15】

前記第1の基板に、前記転送トランジスタのゲート電極によって前記光電変換素子からの前記電荷が転送されるフローティングディフュージョン領域とが配され、

前記第2の基板に、前記フローティングディフュージョン領域の電位に基づく信号が入力されるゲート電極を有する増幅トランジスタと、前記増幅トランジスタのゲート電極をリセット電位に設定するためのリセットトランジスタとが配され、前記第2の基板の上部には前記増幅トランジスタのゲート電極に基づく信号が出力される信号線とが配されることを特徴とする請求項1乃至14のいずれか1項に記載の固体撮像装置。

【請求項16】

前記第1の基板に、前記転送トランジスタのゲート電極によって前記光電変換素子からの前記電荷が転送されるフローティングディフュージョン領域と、前記フローティングディフュージョン領域の電位に基づく信号が入力されるゲート電極を有する増幅トランジスタと、前記増幅トランジスタのゲート電極をリセット電位に設定するためのリセットトランジスタとが配され、 20

前記第2の基板の上部に、前記増幅トランジスタのゲート電極に基づく信号が出力される信号線が配されることを特徴とする請求項1乃至14のいずれか1項に記載の固体撮像装置。

【請求項17】

請求項1乃至16のいずれか1項に記載の固体撮像装置と、

前記固体撮像装置から出力される信号を処理する信号処理部とを有する撮像システム。 30

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、裏面照射型の固体撮像装置に関する。

【背景技術】

【0002】

近年の固体撮像装置の高速化に伴い、トランジスタに高融点金属の半導体化合物層を設けた構成が提案されている。

【0003】

特許文献1には、光電変換部の受光部上には高融点金属の半導体化合物層を設けず、周辺回路部に高融点金属の半導体化合物層を設けた固体撮像装置が記載されている。 40

【0004】

特許文献2には、光電変換素子の感度を向上させるべく、光電変換素子や信号読み出し用の回路を設けた画素部を含む基板と、画素部の回路を駆動し読み出した信号を処理するための周辺回路を含む基板とを貼り合わせた裏面照射型の固体撮像装置が記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2001-111022号

10

20

30

40

50

【特許文献 2】特開 2009 - 170448 号

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献 1 に記載の周辺回路部に高融点金属の半導体化合物層を設けた構造では同一基板上に高融点金属が設けられるため、光電変換素子へ高融点金属が拡散してしまう可能性がある。光電変換素子の表面を絶縁膜で保護していたとしても、絶縁膜上に高融点金属を形成する工程などがあり絶縁膜中を拡散してしまう可能性がある。そして、光電変換素子が高融点金属によって汚染されることによってリーク電流が生じ、画像に白傷等が発生してしまう。また、特許文献 1 に記載の構成を形成するためには、同一基板上にて高融点金属の半導体化合物層の作り分けが必要であり、工程が煩雑であった。

10

【0007】

そこで、本発明では、簡易な構成で、白傷等の原因となる光電変換素子の特性の低下を抑制しつつ、周辺回路部に高融点金属化合物層を配置した固体撮像装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明の固体撮像装置は、光電変換素子と前記光電変換素子からの電荷を転送するためのゲート電極が配された第 1 の基板と、前記光電変換素子にて生じた電荷に基づく信号を読み出すための周辺回路部が配された第 2 の基板とを積層した固体撮像装置において、前記第 2 の基板に高融点金属化合物層が配され、前記第 1 の基板には高融点金属化合物層が配されていない。

20

【発明の効果】

【0009】

本発明は、簡易な構成で、光電変換素子の特性の低下を抑制しつつ、周辺回路部に高融点金属化合物層を配置した固体撮像装置を提供することが可能となる。

【図面の簡単な説明】

【0010】

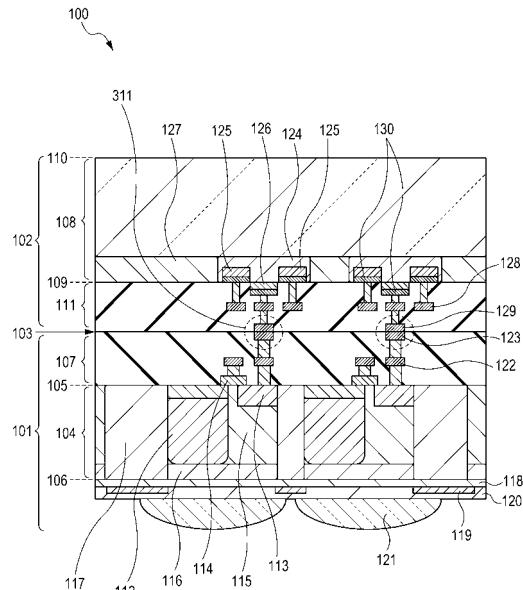

【図 1】実施例 1 を説明する固体撮像装置の断面図

30

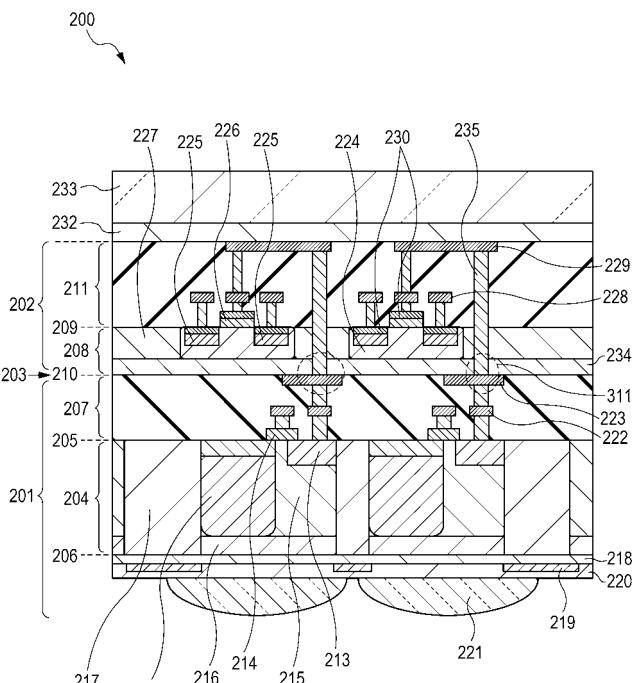

【図 2】実施例 2 を説明する固体撮像装置の断面図

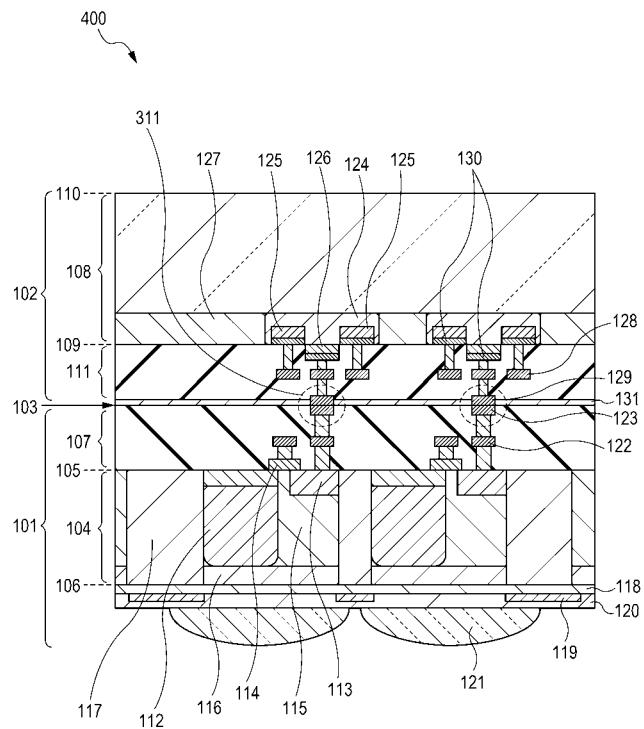

【図 3】実施例 3 を説明する固体撮像装置の断面図

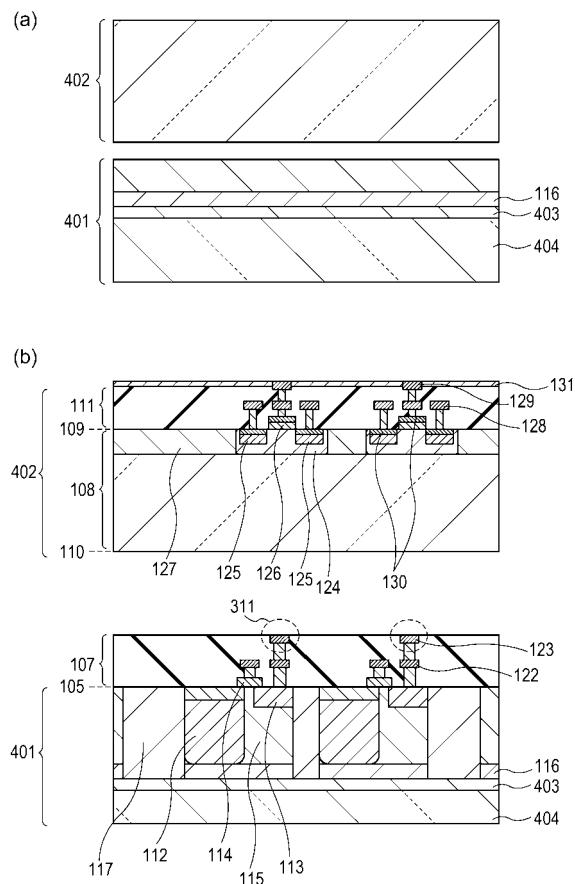

【図 4】実施例 3 の固体撮像装置の製造方法

【図 5】実施例 3 の固体撮像装置の製造方法

【図 6】実施例 5 を説明する固体撮像装置の断面図

【図 7】実施例 4 の固体撮像装置の製造方法

【図 8】実施例 4 の固体撮像装置の製造方法

【図 9】実施例 4 の固体撮像装置の製造方法

【図 10】実施例 5 の実施形態を説明する固体撮像装置の断面図

【図 11】実施例 6 の実施形態を説明する固体撮像装置の断面図

【図 12】本発明の固体撮像装置の回路の一例

40

【図 13】実施例 7 の撮像システムを説明するブロック図

【発明を実施するための形態】

【0011】

本発明の固体撮像装置は、光電変換素子および転送のためのゲート電極とを有する第 1 の基板と、周辺回路部を有する第 2 の基板とを積層して構成されている。そして、第 1 の基板には高融点金属化合物層が配されておらず、第 2 の基板には高融点金属化合物層が配される。このような構成によって、作り分けが容易であり、光電変換素子の特性の低下を抑制しつつ、周辺回路部のトランジスタの動作が高速になり、信号の読み出し動作を高速にすることが可能となる。

【0012】

50

以下、本発明について図面を用いて詳細に説明を行う。

**【実施例 1】**

**【0013】**

本発明の実施例 1 について、図 1 および図 12 を用いて説明する。

**【0014】**

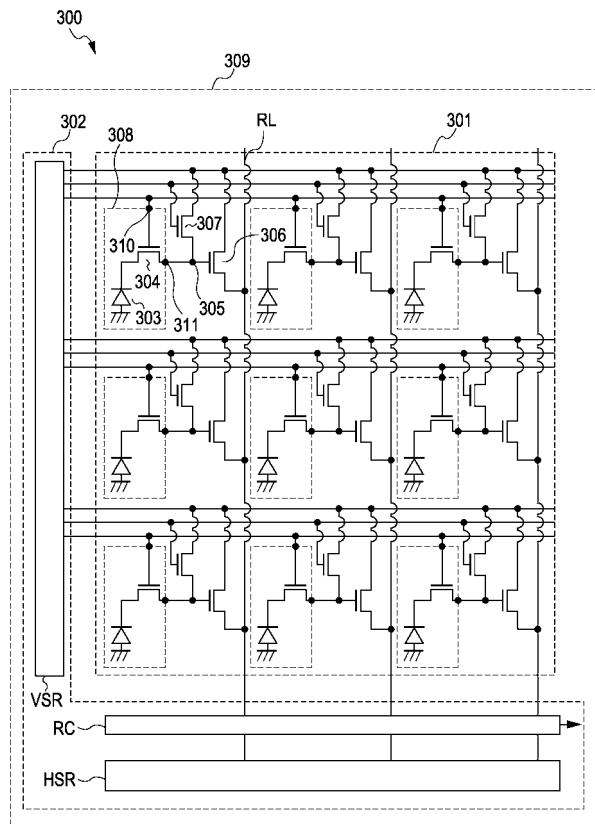

まず、図 12 を用いて実施例 1 の固体撮像装置の回路の一例を説明する。図 12 の固体撮像装置 300 は、複数の光電変換素子が配列した画素部 301 と、画素部 301 からの信号を読み出す駆動のための制御回路や読み出した信号を処理する信号処理回路を有する周辺回路部 302 とを有する。

**【0015】**

画素部 301 は、光電変換素子 303 と、転送トランジスタ 304 と、増幅トランジスタ 306 と、リセットトランジスタ 307 が複数配置されている。少なくとも 1 つの光電変換素子 303 を含む構成を画素とする。本実施例の 1 つの画素は、光電変換素子 303 と、転送トランジスタ 304 と、増幅トランジスタ 306 と、リセットトランジスタ 307 を含む。転送トランジスタ 304 のソースは光電変換素子 303 と接続しており、転送トランジスタ 304 のドレイン領域は増幅トランジスタ 306 のゲート電極と接続している。この増幅トランジスタ 306 のゲート電極と同一のノードをノード 305 とする。リセットトランジスタはノード 305 に接続し、ノード 305 の電位を任意の電位（例えば、リセット電位）に設定する。ここで、増幅トランジスタ 306 はソースフォロア回路の一部であり、ノード 305 の電位に応じた信号を信号線 RL に出力する。

10

20

**【0016】**

周辺回路部 302 は、画素部 301 のトランジスタのゲート電極へ制御信号を供給するための垂直走査回路 VSR を有する。また、周辺回路部 302 は、画素部 301 から出力された信号を保持し、増幅や加算や AD 変換などの信号処理回路を含む読み出し回路 RC を有する。そして、周辺回路部 302 は、読み出し回路 RC から信号を順次出力するタイミングを制御する制御回路の水平走査回路 HSR を有する。

30

**【0017】**

ここで、実施例 1 の固体撮像装置 300 は 2 つのチップが積層されることによって構成されている。2 つのチップとは、画素部 301 の光電変換素子 303 と、転送トランジスタ 304 とが配された第 1 のチップ 308 と、画素部 301 の増幅トランジスタ 306 と、リセットトランジスタ 307 と、周辺回路部 302 とが配された第 2 のチップ 309 である。このような構成において、第 2 のチップ 309 の周辺回路部 302 から第 1 のチップ 308 の転送トランジスタ 304 のゲート電極へと制御信号が接続部 310 を介して供給される。また、第 1 のチップ 308 の光電変換素子 303 にて生じた信号は転送トランジスタ 304 のドレイン領域に接続する接続部 311 を介して、ノード 305 に読み出される。このようにリセットトランジスタ 307 や増幅トランジスタ 306 を別のチップに設けることで、光電変換素子 303 の面積を大きくすることが可能となり感度の向上させることが可能となる。また、面積を同一とするならば、光電変換素子 303 を多く設けることが可能となり、多画素化が可能となる。

40

**【0018】**

次に、図 1 を用いて本実施例の固体撮像装置を説明する。図 1 は、図 12 の固体撮像装置 300 に対応した固体撮像装置 100 の断面図である。図 1 は、図 12 の光電変換素子 303、転送トランジスタ 304、増幅トランジスタ 306 に対応する断面図であり、その他の部分については記載を省略する。図 1 は 2 画素分の構成を示している。

40

**【0019】**

図 1において、第 1 のチップ 101 と、第 2 のチップ 102 と、第 1 のチップと第 2 のチップとの接合面 103 とが示されている。第 1 のチップ 101 は図 12 の第 1 のチップ 308 と、第 2 のチップ 102 は図 12 の第 2 のチップ 309 と対応している。

**【0020】**

第 1 のチップ 101 は第 1 の基板 104 を有する。第 1 の基板 104 において、トラン

50

ジスタが形成される面を正面 105 とし、その反対の面を裏面 106 とする。第 1 の基板 104 には、図 12 における光電変換素子 303、転送トランジスタ 304 を構成する部位が配されている。そして、第 1 のチップ 101 の第 1 の基板 104 の正面 105 側の上部には、例えばアルミニウムを主成分とした配線（アルミニウム配線）からなる第 1 の配線層 122 と第 2 の配線層 123 とを含む多層配線構造 107 を有する。ここでは、多層配線構造 107 の複数の層間絶縁膜を一体の絶縁膜として記載している。

#### 【0021】

第 2 のチップ 102 は第 2 の基板 108 を有する。第 2 の基板 108 において、トランジスタが形成される面を正面 109 とし、その反対の面を裏面 110 とする。第 2 の基板 108 の正面 109 の上部には、例えばアルミニウム配線からなる第 1 の配線層 128 と第 2 の配線層 129 とを含む多層配線構造 111 が形成されている。ここでも、多層配線構造 111 の複数の層間絶縁膜を一体の絶縁膜として示している。そして、第 2 の基板 108 には、図 12 における増幅トランジスタ 306 が配されている。なお、説明において、各チップにおいて、基板の正面から裏面に向う方向を下方向もしくは深い方向とし、裏面から正面に向う方向を上方向もしくは浅い方向とする。

10

#### 【0022】

ここで、本実施例の固体撮像装置においては、第 1 のチップ 101 と第 2 のチップ 102 のそれぞれの基板の正面 105 および正面 109 とが対向して積層されている。図 1 では、第 1 のチップ 101 と第 2 のチップ 102 の接続部の構成は、第 1 のチップ 101 のフローティングディフィュージョン領域（FD 領域）113 と第 2 のチップ 102 の増幅トランジスタのゲート電極 126 との接続のみ示している。具体的には、第 1 のチップ 101 の FD 領域 113 は多層配線構造 107、接続部 311、多層配線構造 111 を介して、増幅トランジスタのゲート電極 126 と接続している。なお、転送トランジスタのゲート電極 114 への制御信号を供給する図 12 に示す接続部 310 は図 1 においては不図示である。そして、本実施例の固体撮像装置においては、第 1 の基板 104 の裏面 106 側から光が入射する裏面入射型の固体撮像装置である。

20

#### 【0023】

各チップについて詳細に説明する。まず、第 1 のチップ 101 の第 1 の基板 104 には、ウェル 115 と、光電変換素子を形成する N 型の電荷蓄積領域 112 と、転送トランジスタを構成する、ゲート電極 114 が配されている。更に、光電変換素子を形成する P 型の表面保護層が電荷蓄積領域 112 の上部に配されている。更に、第 1 の基板 104 には、転送トランジスタのドレイン領域 113 と、素子分離領域 117 と、P 型の半導体領域 116 とが配されている。ウェル 115 は、トランジスタや光電変換素子が配される半導体領域であり、ここでは N 型でも P 型でもどちらでもよい。P 型の半導体領域 116 は、第 1 の基板 104 の裏面 106 のシリコンとシリコン酸化膜界面にて生じる暗電流の抑制が可能であり、また光電変換素子の一部としても機能可能である。電荷蓄積領域 112 は、光電変換素子にて生じた電荷（電子）を蓄積し、図 1 では転送トランジスタのゲート電極側に P 型の保護層を有している。素子分離領域 117 は、P 型の半導体領域からなり、図示していないが LOCOS 分離や STI 分離といった絶縁膜を含む素子分離構造を有していてもよい。転送トランジスタのドレイン領域 113 は FD 領域であり、図 12 のノード 305 を構成する。そして、第 1 のチップ 101 は、第 1 の基板 104 の裏面 106 側に、反射防止膜 118、遮光膜 119、平坦化層などを含むカラーフィルタ層 120、マイクロレンズ 121 を有する。

30

#### 【0024】

次に、第 2 のチップ 102 の第 2 の基板 108 には、ウェル 124 と、図 12 における増幅トランジスタ 306 を構成するソース領域およびドレイン領域 125 と、増幅トランジスタのゲート電極 126 と、素子分離領域 127 と、が配されている。ウェル 124 は P 型の半導体領域である。ここで、本実施例の固体撮像装置の第 2 のチップ 102 に配されたトランジスタ（図 12 の増幅トランジスタ 306）のソース領域およびドレイン領域 125 とゲート電極 126 とは高融点金属化合物層 130 を有する。また、同じく第 2 の

40

50

チップ 102 に配される図 12 の周辺回路部 302 を構成する領域にも高融点金属化合物を含むトランジスタが配される（不図示）。高融点金属化合物とは、例えば、半導体基板にシリコンを用いた場合には、高融点金属であるコバルトやチタンなどを用いたシリサイドである。

#### 【0025】

一方、第 1 の基板 104 のトランジスタなどには高融点金属化合物層は形成されておらず、第 1 の基板 104 の正面 105 の上部には、多層配線構造を構成する絶縁膜が配されている。このように、第 1 の基板 104 には高融点金属化合物層は形成されておらず、第 2 の基板に配された周辺回路部のトランジスタが高融点金属化合物を有することで、ノイズを低減しつつ、トランジスタの動作の高速化が可能となる。また、このような高融点金属化合物を有するトランジスタを第 2 のチップ 102 にのみ有することで、光電変換素子への高融点金属の混入を低減することが可能となり、高融点金属の混入によって生じるノイズを低減することが可能となる。また、同一基板上に高融点金属化合物を設ける領域と設けない領域とを作り分ける必要がないため高融点金属化合物が形成しないように保護する膜などが不要となり、すなわち各基板は簡易な構成となり、簡易な工程での製造が可能である。

#### 【0026】

なお、本実施例では光電変換素子に加えて FD 領域を第 1 の基板 104 に形成している。それは、光電変換素子で生じた信号電荷が保持される光電変換素子や FD 領域を構成する半導体領域に高融点金属化合物層を設けると、高融点金属が半導体領域に混入して生じたノイズが信号電荷に混入してしまうためである。なお、増幅トランジスタが第 1 の基板に配された場合には、増幅トランジスタに高融点金属化合物層は形成しない。

#### 【0027】

本実施形態では、各配線層はアルミニウム配線からなるとしたが、銅を主成分とした配線（銅配線）によって構成されていてもよい。銅配線の上部には銅に対する拡散防止膜が設けられていてもよく、銅に対する拡散防止膜はパターニングされていてもよい。

#### 【実施例 2】

#### 【0028】

本実施例の固体撮像装置を図 2 を用いて説明する。本実施例の固体撮像装置は、実施例 1 の固体撮像装置とは、図 12 に示すような回路は等しく、チップの積層構造が異なる。以下、回路については説明を省略し、図 2 に示す構成について説明を行う。

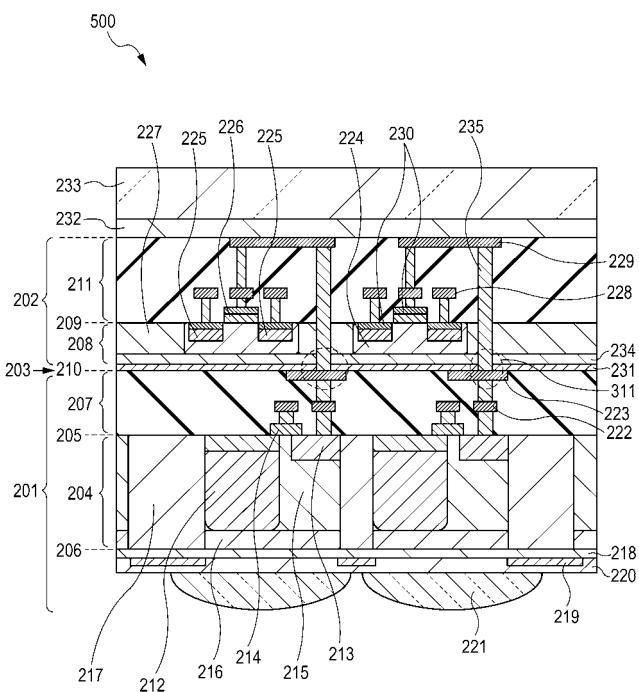

#### 【0029】

図 2 は、図 12 の回路に対応した固体撮像装置 200 の断面図である。図 2 は、図 12 の光電変換素子 303、転送トランジスタ 304、増幅トランジスタ 306 に対応する、2 画素分の断面図であり、その他の部分については記載を省略する。

#### 【0030】

図 2 には、第 1 のチップ 201 と、第 2 のチップ 202 と、第 1 のチップと第 2 のチップとの接合面 203 とが示されている。第 1 のチップ 201 は図 12 の第 1 のチップ 308 と、第 2 のチップ 202 は図 12 の第 2 のチップ 309 と対応している。

#### 【0031】

第 1 のチップ 201 は第 1 の基板 204 を有する。第 1 の基板 204 において、トランジスタが配される面を正面 205 とし、その反対の面を裏面 206 とする。第 1 の基板 204 には、図 12 における光電変換素子 303、転送トランジスタ 304 を構成する部位が配されている。そして、第 1 の基板 204 の正面 205 の上部には、アルミニウム配線からなる第 1 の配線層 222 と第 2 の配線層 223 とを含む多層配線構造 207 が配されている。ここでは、多層配線構造 207 の複数の層間絶縁膜を一体の絶縁膜として記載している。

#### 【0032】

第 2 のチップ 202 は第 2 の基板 208 を有する。第 2 の基板 208 において、トランジスタが形成される面を正面 209 とし、その反対の面を裏面 210 とする。第 2 の基板

10

20

30

40

50

208の正面209の上部には、アルミニウム配線からなる第1の配線層228と第2の配線層229とを含む多層配線構造211が配されている。ここでも、多層配線構造211の複数の層間絶縁膜を一体の絶縁膜として示している。そして、第2の基板208には、図12における増幅トランジスタ306を構成する部位が配されている。

#### 【0033】

ここで、本実施例の固体撮像装置においては、第1の基板204の正面205と第2の基板208の裏面210とが対向して積層されている。図2では、第1のチップ201と第2のチップ202の接続部の構成は、第1のチップ201のFD領域213と第2のチップ202の増幅トランジスタのゲート電極226との接続のみ示している。具体的には、第1のチップ201のFD領域213は、多層配線構造207、接続部311、多層配線構造211を介して、増幅トランジスタのゲート電極226と接続している。ここで、接続部311の一部を構成する、第2の基板208に関する貫通電極235が配されている。この貫通電極によって、FD領域213と増幅トランジスタのゲート電極226とが接続される。なお、転送トランジスタのゲート電極214への制御信号を供給する、図12における接続部310は図2においては不図示である。そして、本実施例の固体撮像装置においては、第1の基板204の裏面206側から光が入射する裏面入射型の固体撮像装置である。

10

#### 【0034】

次に、各チップについて詳細に説明する。第1のチップ201の第1の基板204には、ウエル215と、光電変換素子を形成するN型の電荷蓄積領域212と、転送トランジスタのゲート電極214とが配されている。更に、第1の基板204には転送トランジスタのドレイン領域213と、素子分離領域217と、P型の半導体領域216とが配されている。そして、第1のチップ201は、第1の基板204の裏面206側に、反射防止膜218、遮光膜219、平坦化層などを含むカラーフィルタ層220、マイクロレンズ221を有する。次に、第2のチップ202の第2の基板208には、ウエル224と、図12の増幅トランジスタ306を構成するソース領域、ドレイン領域225およびゲート電極226と、素子分離領域227と、が配されている。更に、第2の基板208の上部に第1の配線層228、第2の配線層229を有し、第2の基板208の最深部に絶縁層234を有する。これら第1のチップ201と第2のチップ202の構成について、実施例1と同様な構成については説明を省略する。

20

30

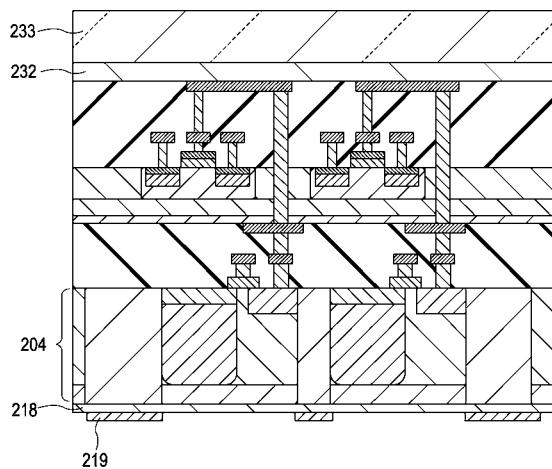

#### 【0035】

実施例2においては、更に、第2のチップ202の上部に接着層232と支持基板233とを有している。実施例2における絶縁層、接着層232、支持基板233については後述する。

#### 【0036】

ここで、本実施例の固体撮像装置の第2のチップ202に配されたトランジスタ(図12の増幅トランジスタ306)のソース領域およびドレイン領域225とゲート電極226とは高融点金属化合物層230を有する。また、同じく第2のチップ202に配される図12に示す周辺回路部302を構成する領域にも高融点金属化合物を含むトランジスタが配される(不図示)。高融点金属化合物とは、例えば、半導体基板にシリコンを用いた場合には、高融点金属であるコバルトやチタンなどを用いたシリサイドである。第2の基板に配された周辺回路部などのトランジスタが高融点金属化合物を有することで、トランジスタの動作の高速化が可能となる。また、このような高融点金属化合物を有するトランジスタを第2のチップ202にのみ有することで、第1のチップ201の光電変換素子の特性の低下を抑制しつつ、光電変換素子の高融点金属の混入を低減することが可能となる。また、同一基板上に高融点金属化合物を設ける領域と設けない領域とを作り分ける必要がないため高融点金属化合物が形成しないように保護する膜などが不要となり、すなわち各基板は簡易な構成となり、簡易な工程での製造が可能である。

40

#### 【実施例3】

#### 【0037】

50

本実施例の固体撮像装置を図3を用いて説明する。本実施例の固体撮像装置は、実施例1の固体撮像装置100に対応し、実施例1の固体撮像装置100に対して拡散防止膜を有する点が異なる。以下、図3に示す構成について説明を行う。なお、実施例1と等しい構成については説明を省略する。

#### 【0038】

図3の固体撮像装置400において、拡散防止膜131が第1のチップ101と第2のチップ102との間に配されている。このような拡散防止膜131を有することで、第2のチップに配された高融点金属化合物層の高融点金属が、多層配線構造111と107を拡散し、第1のチップの光電変換素子やFD領域を構成する半導体領域に混入することを抑制することが可能となる。従って、高融点金属が半導体領域に混入することによって生じる暗電流や(画像の)白傷の原因となるリーク電流の発生を、より抑制することが可能となる。

10

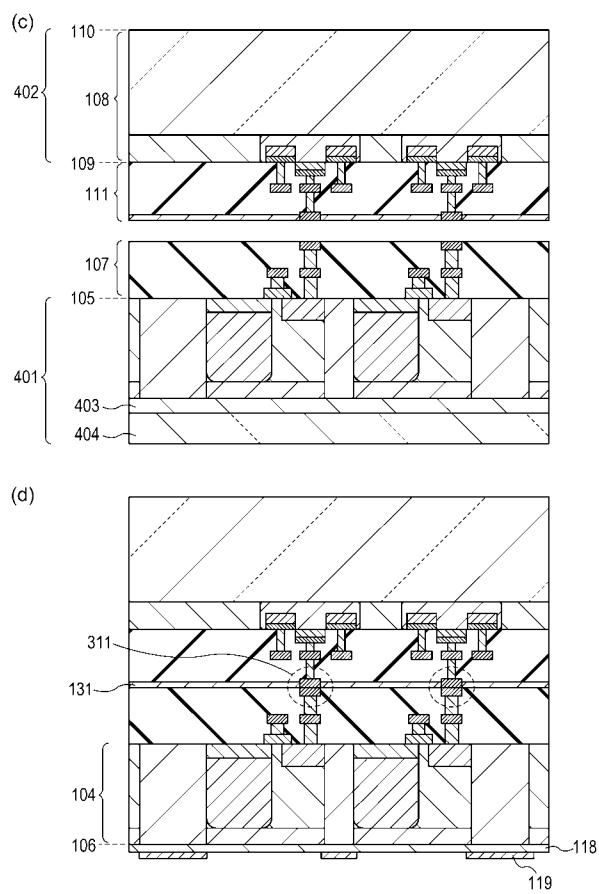

#### 【0039】

図3に示した固体撮像装置400の製造方法を図4および図5を用いて説明する。まず、図4(a)では、図3の第1の基板104となるフォトダイオード形成部材(以下PD形成部材)401と、図3の第2の基板108となる回路形成部材402とを準備する。これら部材は、例えばシリコン半導体基板であり、導電型は任意である。PD形成部材401は、P型半導体領域116と絶縁層403とを含む。このPD形成部材401は、SOI基板を使用しており、P型半導体領域116はイオン注入でもエピタキシャル成長によって形成されていてもよい。

20

#### 【0040】

次に、図4(b)に示すように、PD形成部材401に、電荷蓄積領域112や転送トランジスタのゲート電極114などの素子を形成する。そして、PD形成部材401の上部に多層配線構造107を形成する。多層配線構造107は、第1の配線層122および第2の配線層123を有する。第1の配線層122と第2の配線層123はそれぞれ複数の配線を含む。本実施例において各配線は、アルミニウム配線である。また、多層配線構造107は、配線同士を絶縁するための層間絶縁膜を有する。層間絶縁膜は、例えば、転送トランジスタのゲート電極と第1の配線層122との間や、第1の配線層122と第2の配線層123との間に配される。この多層配線構造107の形成には一般的な半導体プロセスが使用可能である。最後に、第2の配線層123を覆う層間絶縁膜を形成し、第2の配線層123の一部の配線が露出するように層間絶縁膜を除去する。露出した第2の配線層123は接続部311を構成する。PD形成部材401の転送トランジスタのゲート電極が配された面が、後の第1の基板104の正面105となる。

30

#### 【0041】

図4(c)においては、回路形成部材402に、ウエル124を形成し、増幅トランジスタ306を含むトランジスタ等の周辺回路部を形成する。その後、トランジスタのソース領域、ドレイン領域125およびゲート電極126など所望の位置に、高融点金属を堆積し、熱処理を行うことで高融点金属化合物層130を形成する。その後、回路形成部材402の上部に多層配線構造111を形成する。多層配線構造111は、第1の配線層128および第2の配線層129を有する。この多層配線構造111の構成や製造方法については、PD形成部材401の多層配線構造107と同様である。次に、第2の配線層129まで形成した後、第2の配線層129を覆う拡散防止膜131を形成する。拡散防止膜131はシリコンナイトライドやシリコンカーバイドなどで形成される。この拡散防止膜131は、高融点金属のPD形成部材401への拡散を抑制するための膜である。その後、接続部311を構成する第2の配線層129の一部の配線が露出するように拡散防止膜131を除去する。拡散防止膜の除去はエッティングやCMP技術を使用することが可能である。ここで、回路形成部材402は第2の基板108となる。第2の基板108の正面109が図4(c)に示すように定まる。

40

#### 【0042】

次に、図5(c)に示すように、PD形成部材401と回路形成部材402の基板の主

50

面（105、109）が互いに対向するように配置し、例えば、マイクロバンプによって接合する。

#### 【0043】

最後に、図5（d）に示したように、PD形成部材401の不要部分404および絶縁層403をCMPやエッティングなどによって除去し、PD形成部材401の薄膜化をはかり、第1の基板104を構成する。その後、第1の基板104の裏面106の上部にシリコンナイトライドなどからなる反射防止膜118を形成する。反射防止膜118の形成後に、反射防止膜118の上部に、タングステン膜を形成しパターニングをすることで、遮光膜119を形成する。その後、平坦化層やカラーフィルタ層120を形成し、マイクロレンズ121を形成する。このような製造方法によって、図3に示した固体撮像装置400を製造することが可能である。10

#### 【0044】

ここで、本実施例の構成によれば、多層配線構造107の層間絶縁膜を形成した後に、光電変換素子の欠陥回復を含む特性向上のための高温あるいは長時間の熱処理を行うことが可能となる。仮に、高融点金属化合物層を第1の基板が有している場合には、層間絶縁膜を形成する前に高融点金属の半導体化合物層を形成することになる。そして、層間絶縁膜を形成した後には、高融点金属の拡散などの問題により高温、長時間の熱処理を行うことが困難となってしまう。よって、本実施例の構成によれば、光電変換素子の欠陥回復のための熱処理を任意の工程で行うことが可能となるため、光電変換素子の特性の低下を抑制することが可能となる。20

#### 【0045】

また、好ましい形態として、FD領域に設けられたコンタクトの接続抵抗を向上させるために、プラグと接続する半導体領域にイオン注入および熱処理を行なうことが好ましい。しかし、先に述べたように、仮に、高融点金属化合物層を第1の基板が有している場合には、層間絶縁膜を形成した後に行われるコンタクト形成工程における熱処理を行うことが難しくなってしまう。よって、本実施例の構成によれば、周辺回路部に高融点金属化合物層を設けつつ、高融点金属化合物層を設けていないFD領域のコンタクトの形成工程において十分な熱処理を行なうことが可能となる。従って、FD領域での高融点金属の汚染を抑制しつつ、FD領域のコンタクトの接続を良好にすることが可能となる。30

#### 【0046】

以上述べてきたように、本実施例の固体撮像装置によれば、周辺回路部のトランジスタの動作が高速になり、信号の読み出し動作を高速にしつつ、更に、光電変換素子での暗電流の発生を抑制することが可能となる。

#### 【実施例4】

#### 【0047】

本実施例の固体撮像装置を図6を用いて説明する。本実施例の固体撮像装置500は、実施例2の固体撮像装置300に対応する構成であり、実施例2の固体撮像装置に比べて拡散防止膜を有する点が異なる。以下、図6に示す構成について説明を行う。なお、実施例2と等しい構成については説明を省略する。

#### 【0048】

図6の固体撮像装置500において、高融点金属に対する拡散防止膜231が第1のチップ201と第2のチップ202との間に配されている。拡散防止膜231を有することで、第2のチップに配された高融点金属化合物層の高融点金属が第1のチップの光電変換素子やFD領域を構成する半導体領域に混入することを、より抑制することが可能となる。よって、暗電流や（画像の）白傷の発生を抑制することが可能となる。なお、拡散防止膜231は、例えば、シリコンナイトライドやシリコンカーバイドからなる膜である。40

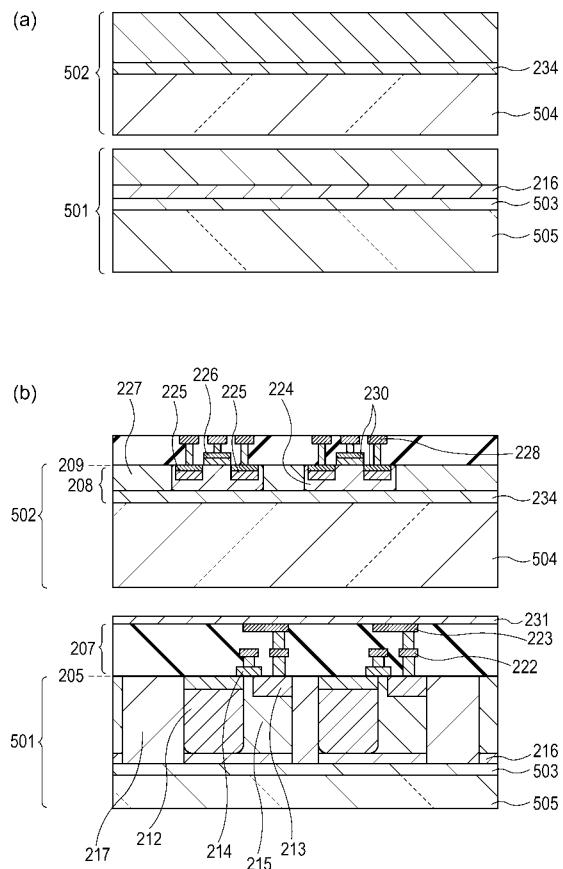

#### 【0049】

次に、図6に示した固体撮像装置500の製造方法を図7から図9を用いて説明する。まず、図7（a）において、図6の第1の基板204となるフォトダイオード形成基板（以下、PD形成部材）501と、図6の第2の基板208となる回路形成部材502とを

10

20

30

40

50

準備する。PD形成部材501は、P型半導体領域216と絶縁層503とが配されている。PD形成部材501は、SOI基板を使用しており、P型半導体領域216はイオン注入でもエピタキシャル成長によって形成されていてもよい。回路形成部材502は、SOI基板を使用し、絶縁層234が配されている。

#### 【0050】

次に、図7(b)のPD形成部材501において、ウエル215や電荷蓄積領域212や転送トランジスタのゲート電極214などの素子を形成する。そして、PD形成部材501の上部に多層配線構造207を形成する。多層配線構造207は、第1の配線層222および第2の配線層223を有する。多層配線構造207の構成や製造方法については、実施例3と同様であるため省略する。次に、第2の配線層223を覆う層間絶縁膜を形成し、第2の配線層223の配線が露出するように層間絶縁膜を除去する。第2の配線層223は接続部311を構成する。そして、第2の配線層223を覆う、シリコンナイトライドやシリコンカーバイドなどからなる拡散防止膜231を形成する。なお、第2の配線層223と拡散防止膜231との間に、第2の配線層223を覆う層間絶縁膜が配されているてもよい。

10

#### 【0051】

また、図7(b)の回路形成部材502において、ウエル224や増幅トランジスタを含むトランジスタを形成する。その後、トランジスタのソース領域、ドレイン領域およびゲート電極など所望の位置に、高融点金属を堆積し、熱処理を行うことで高融点金属化合物層230を形成する。その後、回路形成部材502の上部に多層配線構造211を形成する。多層配線構造211は第1の配線層228を有する。この第1の配線層228の構成や製造方法については、実施例3と同様である。

20

#### 【0052】

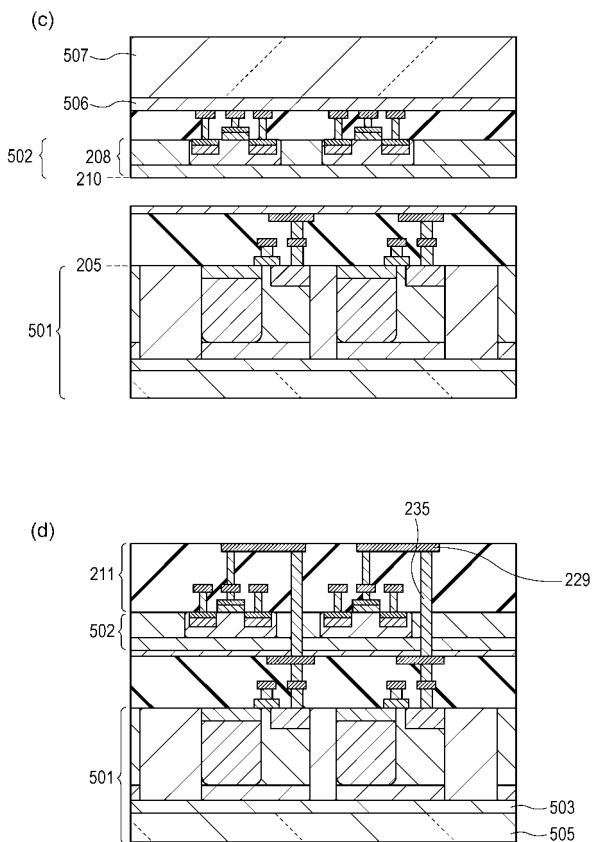

次に、図8(c)において、回路形成部材502の第1の配線層228の上部に接着層506と支持基板507を形成する。そして、回路形成部材502の不要部分504を研磨やエッティングによって除去し、第2の基板208を形成する。

#### 【0053】

図8(d)において、図6の第1の基板204となるPD形成部材501の正面205と第2の基板208の裏面210とが対向するように配置し、例えば、マイクロバンプによって接合する。その後、第1の接着層506と第1の支持基板507を除去する。そして、第2の基板208の第1の配線層228の上部に層間絶縁膜を形成し、第1の基板204との導通を取るための貫通電極235を形成する。この貫通電極235の製造方法については、一般的の半導体プロセスが利用できる。そして、貫通電極235を覆って、第2の配線層229を形成する。

30

#### 【0054】

次に、図9に示すように、第2の基板208の第2の配線層229の上部に接着層232と支持基板233を設ける。そして、PD形成部材501の不要部分505をエッティングやCMPなどによって除去し、第1の基板204が形成される。その後、第1の基板204の裏面206の上部に例えばシリコンナイトライドからなる反射防止膜218を形成する。その後、反射防止膜218の上部に例えばタンゲステンからなる遮光膜219を形成する。更に、遮光膜219の上部に平坦化層やカラーフィルタ層120を形成し、マイクロレンズ121を形成する。以上の製造方法によって、図6に示す固体撮像装置500が形成できる。

40

#### 【0055】

なお、本実施例の構成においても、光電変換素子やコンタクトの熱処理を任意の工程で行えるため、光電変換素子の特性の低下やコンタクトの接続抵抗の増大を抑制することが可能となる。

#### 【0056】

以上、述べてきたように、本実施例の固体撮像装置によれば、周辺回路部のトランジスタの動作が高速になり、信号の読み出し動作を高速にしつつ、更に、光電変換素子での暗

50

電流の発生を抑制することが可能となる。

**【実施例 5】**

**【0057】**

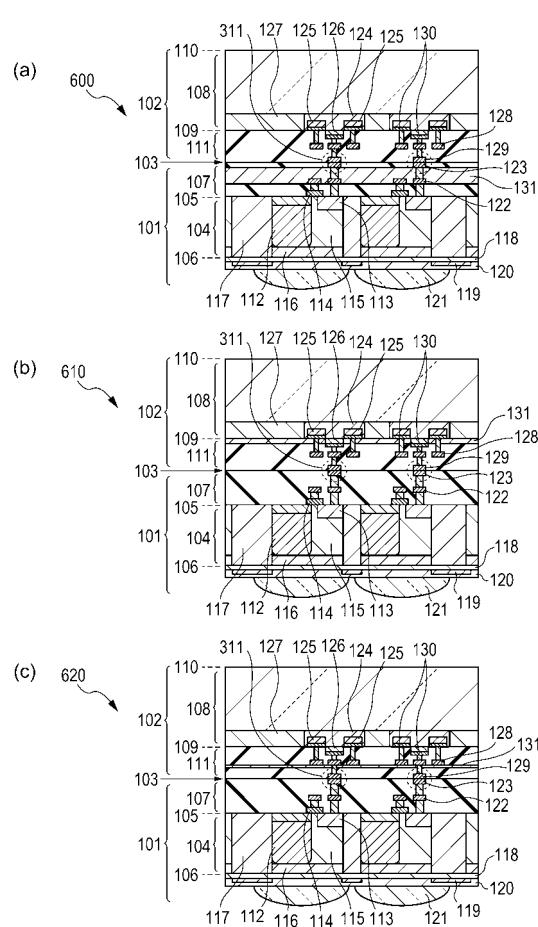

本実施例の固体撮像装置を、図10を用いて説明する。図10に示す本実施例の固体撮像装置600、610、620は、実施例3の固体撮像装置400に対応する構成であり、拡散防止膜131の配置の変形例を示す。以下、実施例3と等しい構成については説明を省略する。

**【0058】**

図10(a)に示す固体撮像装置600において、拡散防止膜131は、第1の基板104と第2の基板108との間に配され、更に、第1の基板104の上部に配された多層配線構造107に含まれる層間絶縁膜を兼ねている。このような構成によって、層間絶縁膜を形成する工程を削減することが可能となり、固体撮像装置の薄膜化が可能となる。また、固体撮像装置600は裏面照射型なので、例えばシリコンナイトライドからなる拡散防止膜131を光電変換素子の上部に全面に設けたとしても、層間絶縁膜として一般的なシリコン酸化膜と拡散防止膜131との屈折率差による反射等は生じない。よって、光学特性の低下を抑制しつつ、第2基板108からの高融点金属の拡散を抑制することが可能となる。なお、拡散防止膜131を層間絶縁膜として兼ねる構成は、図10(a)の構成に限らず、例えば、第2の基板108の上部に配される多層配線構造111中の層間絶縁膜であってもよい。

10

**【0059】**

次に、図10(b)に示す固体撮像装置610において、拡散防止膜131は、第1の基板104と第2の基板108との間に配される。そして、拡散防止膜131は、第2の基板108のソース領域およびドレイン領域125とゲート電極126上の高融点金属化合物層130に接して形成されている。このような構成にすることで、拡散防止膜131は第2の基板108のコンタクトホール形成時のエッチングストップ層としても使用することが可能となる。

20

**【0060】**

次に、図10(c)に示す固体撮像装置620において、拡散防止膜131は、第1の基板104と第2の基板108との間に配され、第2の基板108の第1の配線層228の上部に接して配されている。第1の配線層228は銅配線からなり、拡散防止膜131は銅に対する拡散防止膜としても機能する。このような構成を有することで、銅に対する拡散防止膜とを形成する工程が削減でき、また固体撮像装置の薄膜化が可能となる。なお、拡散防止膜131を銅に対する拡散防止膜と兼ねる構成は図10(c)の構成に限られない。例えば、第1の基板104の上部に配された多層配線構造107が銅配線で構成され、拡散防止膜131を各配線層に対して設けてもよい。

30

**【実施例 6】**

**【0061】**

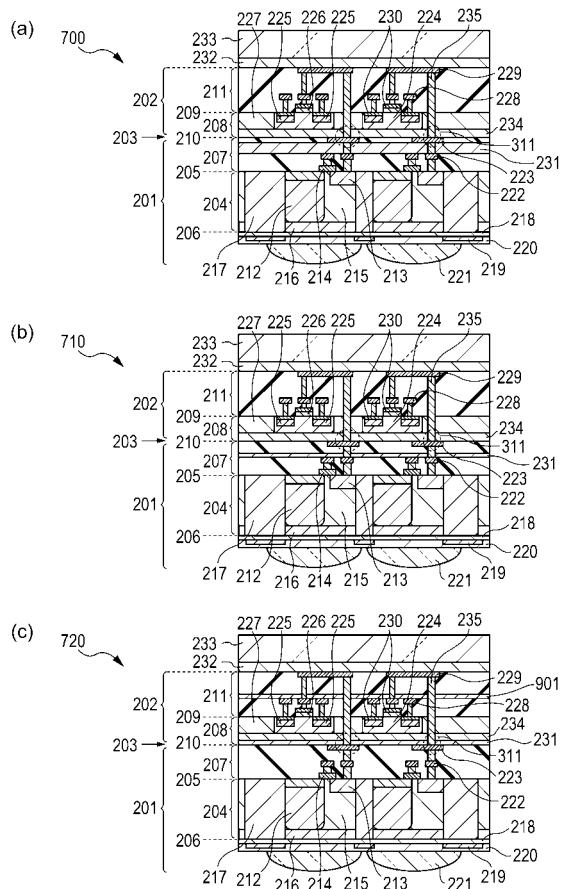

本実施例の固体撮像装置を、図11を用いて説明する。図11に示す本実施例の固体撮像装置700、710、720は、実施例4の固体撮像装置500に対応する構成であり、拡散防止膜231の配置の変形例を示す。以下、実施例4と等しい構成については説明を省略する。

40

**【0062】**

図11(a)に示す固体撮像装置700において、拡散防止膜231は、第1の基板204と第2の基板208との間に配され、更に、第1の基板204の上部に配された多層配線構造207に含まれる層間絶縁膜を兼ねている。このような構成によって、層間絶縁膜を形成する工程を削減することが可能となり、固体撮像装置の薄膜化が可能となる。また、固体撮像装置700は裏面照射型である。よって、例えばシリコンナイトライドからなる拡散防止膜231を光電変換素子の上部に全面に設けたとしても、層間絶縁膜として一般的なシリコン酸化膜と拡散防止膜231との屈折率差による入射光の反射について検討が不要である。よって、第2基板208からの高融点金属の拡散を抑制することが可能

50

となる。

### 【0063】

また、図11(b)に示す固体撮像装置710においては、拡散防止膜231は、第1の基板204と第2の基板208との間に配され、第1の基板208の第1の配線層222の上部に接して配されている。第1の配線層222は銅配線からなり、拡散防止膜231は銅に対する拡散防止膜としても機能する。このような構成を有することで、銅に対する拡散防止膜を形成する工程が削減でき、また固体撮像装置の薄膜化が可能となる。なお、拡散防止膜231を銅に対する拡散防止膜と兼ねる構成は図11(b)の構成に限られない。例えば、図11(c)に示すように、第1の基板204の上部に配された多層配線構造207のうち、第2の配線層223が銅配線で構成され、拡散防止膜231が第2の配線層223の上部に配されていてもよい。このとき、第1の配線層222の上部に拡散防止膜231が配されていてもよい。また、配線層間の容量を低減するために、第1の配線層222の上部には銅に対する拡散防止膜が配線の形状に沿ってパターニングされ、一部除去されていてもよい。また、図11(c)のように、第2の基板208の上部に配された多層配線構造211が銅配線によって構成されていてもよく、更に、銅の拡散防止膜901を有していてもよい。

10

### 【実施例7】

### 【0064】

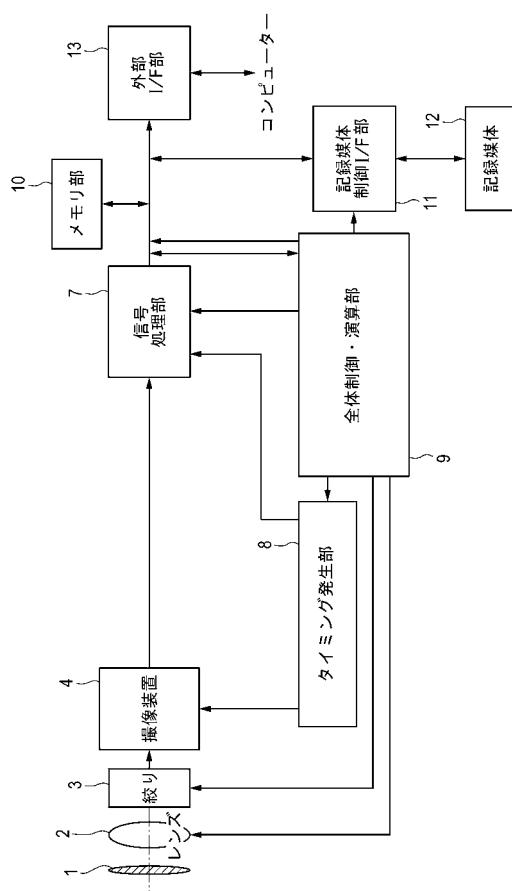

本実施例では、本発明の光電変換装置を撮像装置として撮像システムに適用した場合について詳述する。撮像システムとして、デジタルスチルカメラやデジタルカムコーダーなどがあげられる。図13に、撮像システムの例としてデジタルスチルカメラに光電変換装置を適用した場合のブロック図を示す。

20

### 【0065】

図13において、1はレンズの保護のためのバリア、2は被写体の光学像を撮像装置4に結像させるレンズ、3はレンズ2を通った光量を可変するための絞りである。4は上述の各実施例で説明した固体撮像装置である撮像装置である。撮像装置4は、レンズ2により結像された光学像を画像データとして変換する。ここで、撮像装置4にはA/D変換器が配され、具体的には第2のチップにA/D変換器が形成されている。7は撮像装置4より出力された撮像データに各種の補正やデータを圧縮する信号処理部である。そして、図13において、8は撮像装置4および信号処理部7に、各種タイミング信号を出力するタイミング発生部、9は各種演算とデジタルスチルカメラ全体を制御する全体制御・演算部である。10は画像データを一時的に記憶する為のメモリ部、11は記録媒体に記録または読み出しを行うためのインターフェース部、12は撮像データの記録または読み出しを行う為の半導体メモリ等の着脱可能な記録媒体である。そして、13は外部コンピュータ等と通信する為のインターフェース部である。ここで、タイミング信号などは撮像システムの外部から入力されてもよく、撮像システムは少なくとも撮像装置4と、撮像装置から出力された撮像信号を処理する信号処理部7とを有すればよい。本実施例では、撮像装置4にA/D変換器が設けられている場合を説明したが、撮像装置とA/D変換器とが別のチップであってもよい。また、撮像装置4に信号処理部7などが設けられていてよい。撮像装置4の第2のチップには高融点金属化合物層が形成されているため、信号処理などを高速に行うことが可能である。以上のように、本発明の光電変換装置を撮像システムに適用することが可能である。本発明の光電変換装置を撮像システムに適用することにより、高速な撮影が可能となる。

30

### 【0066】

以上述べてきたように、本発明の固体撮像装置によって、高速な動作が可能な固体撮像装置を提供することが可能となる。更に、拡散防止膜を設けることで、暗電流を低減することが可能となり、画像に白傷が生じることを抑制することが可能となる。各実施例は説明した構成に限定されず、また各実施例は適宜組み合わせ可能である。例えば、固体撮像装置は高融点金属に対する拡散防止膜を複数有していてもよい。

40

### 【0067】

50

なお、高融点金属化合物層は、トランジスタのソース領域、ドレイン領域およびゲート電極の他に、ウエルコンタクトなどの半導体領域に電位を供給する部分に形成されていてもよい。

#### 【産業上の利用可能性】

#### 【0068】

本発明は、デジタルスチルカメラやデジタルカムコーダーなどの撮像システムに用いられる固体撮像装置に適用可能である。

#### 【符号の説明】

#### 【0069】

- 101 第1のチップ

- 102 第2のチップ

- 103 接合面

- 104 第1の基板

- 107 多層配線構造

- 108 第2の基板

- 111 多層配線構造

- 112 光電変換素子

- 124 ウエル

- 125 ソース・ドレイン領域

- 126 増幅トランジスタのゲート電極

- 130 高融点金属化合物層

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【 図 8 】

【 9 】

【 囮 1 0 】

【 図 1 1 】

【 図 1 2 】

【図 1 3】

**【手続補正書】**

【提出日】平成26年4月14日(2014.4.14)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】****【特許請求の範囲】****【請求項1】**

光電変換素子と前記光電変換素子からの電荷を転送するための転送トランジスタのゲート電極が配された第1の基板と、

前記光電変換素子にて生じた電荷に基づく信号を読み出すための周辺回路部が配された第2の基板とを積層した固体撮像装置において、

前記第2の基板に高融点金属化合物層が配され、

前記第1の基板には高融点金属化合物層が配されていない固体撮像装置。

---

フロントページの続き

(72)発明者 山崎 和男

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 渡辺 杏平

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

(72)発明者 市川 武史

東京都大田区下丸子3丁目30番2号キヤノン株式会社内

F ターム(参考) 4M118 AB01 BA14 BA19 CA02 CA04 CA18 DD04 DD12 EA01 EA14

FA06 FA25 FA26 FA27 FA28 FA33 GA02 GC07 GD04 GD07

HA31

5C024 BX01 CX03 CY47 EX34 EX42 EX43 EX52 GX03 GX16 GX24

GY31 HX23 HX55