(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3965610号

(P3965610)

(45) 発行日 平成19年8月29日(2007.8.29)

(24) 登録日 平成19年6月8日(2007.6.8)

(51) Int.C1.

F 1

|            |           |            |      |

|------------|-----------|------------|------|

| HO1S 5/042 | (2006.01) | HO1S 5/042 | 612  |

| HO1L 21/28 | (2006.01) | HO1L 21/28 | 301B |

| HO1L 33/00 | (2006.01) | HO1L 33/00 | E    |

請求項の数 12 (全 16 頁)

(21) 出願番号 特願平9-207737

(22) 出願日 平成9年8月1日(1997.8.1)

(65) 公開番号 特開平11-54843

(43) 公開日 平成11年2月26日(1999.2.26)

審査請求日 平成16年6月11日(2004.6.11)

(73) 特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1番

1号

(74) 代理人 100072833

弁理士 柏谷 昭司

(74) 代理人 100075890

弁理士 渡邊 弘一

(74) 代理人 100105337

弁理士 真鍋 潔

(72) 発明者 副島 ▲玲▼子

神奈川県川崎市中原区上小田中4丁目1番

1号 富士通株式会社内

審査官 松崎 義邦

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

n型SiCからなる半導体層上にN<sub>i</sub>層、Ti層、ボンディングメタル層としてのAu層を順次積層させたことを特徴とする半導体装置。

## 【請求項2】

上記n型SiCが、発光半導体素子のn型半導体層を構成することを特徴とする請求項1記載の半導体装置。

## 【請求項3】

上記n型SiC上に設けた積層構造の最上層となるp型Al<sub>x</sub> In<sub>y</sub> Ga<sub>1-x-y</sub> N(但し、0<x<1, 0<y<1)を設けると共に、前記p型Al<sub>x</sub> In<sub>y</sub> Ga<sub>1-x-y</sub> Nに接するN<sub>i</sub>層を設け、前記N<sub>i</sub>層とボンディングメタル層としてのAu層との間にTi層を介在させることを特徴とする請求項1または2に記載の半導体装置。

## 【請求項4】

半導体層にN<sub>i</sub>層を堆積させたのち、アニール処理を施し、次いで、前記N<sub>i</sub>層上に、Ti層及びAu層を順次堆積させたことを特徴とする半導体装置の製造方法において、前記半導体層がp型Al<sub>x</sub> In<sub>y</sub> Ga<sub>1-x-y</sub> N(但し、0<x<1, 0<y<1)であり、且つ、前記アニール処理の温度が、800以下であることを特徴とする半導体装置の製造方法。

## 【請求項5】

上記p型Al<sub>x</sub> In<sub>y</sub> Ga<sub>1-x-y</sub> Nが、発光半導体素子のp型半導体層を構成すること

を特徴とする請求項4記載の半導体装置の製造方法。

【請求項6】

半導体層にN*i*層を堆積させたのち、アニール処理を施し、次いで、前記N*i*層上に、T*i*層及びA*u*層を順次堆積させたことを特徴とする半導体装置の製造方法において、前記半導体層がn型SiCであることを特徴とする半導体装置の製造方法。

【請求項7】

上記アニール処理の温度が、800以上であることを特徴とする請求項6記載の半導体装置の製造方法。

【請求項8】

上記アニール処理を施したのち、T*i*層を堆積する前にフッ酸系溶剤による処理を行うことを特徴とする請求項7記載の半導体装置の製造方法。 10

【請求項9】

上記n型SiCが、発光半導体素子のn型半導体層を構成することを特徴とする請求項6乃至請求項8のいずれか1項に記載の半導体装置の製造方法。

【請求項10】

上記n型SiC上に、p型Al<sub>x</sub>In<sub>y</sub>Ga<sub>1-x-y</sub>N(但し、0<x<1, 0<y<1)を最上層とする多層構造を設けると共に、前記p型Al<sub>x</sub>In<sub>y</sub>Ga<sub>1-x-y</sub>NにN*i*層を堆積させたのち、前記N*i*層上に、T*i*層3及びA*u*層4を順次堆積させたことを特徴とする請求項6乃至9のいずれか1項に記載の半導体装置の製造方法。

【請求項11】

上記n型SiCに対するn側電極を形成したのち、上記p型Al<sub>x</sub>In<sub>y</sub>Ga<sub>1-x-y</sub>Nに対するp側電極を形成することを特徴とする請求項10記載の半導体装置の製造方法。 20

【請求項12】

上記N*i*層、T*i*層、及び、A*u*層のうち、少なくとも、T*i*層及びA*u*層を所定の形状にエッチングして電極を形成することを特徴とする請求項4乃至11のいずれか1項に記載の半導体装置の製造方法。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は半導体装置及びその製造方法に関するものであり、特に、GaN系化合物半導体からなる短波長発光素子のオーミック電極構造及びその製造工程に特徴がある半導体装置及びその製造方法に関するものである。 30

【0002】

【従来の技術】

近年、青色から近紫外領域に波長を有する短波長半導体レーザの開発が盛んであり、GaN系化合物半導体は、直接遷移型を有し、バンド・ギャップが1.95~6eVまで変化するため、青色半導体レーザ用材料等として研究されている。

【0003】

特に、3年前の日亜化学によるGaN高輝度LEDの発表を境に、ZnSe系でネックになっている信頼性に関して耐環境性に優れるGaN系化合物半導体が見直され、また、去年の注入励起によるレーザ発振の成功の報告(必要ならば、S. Nakamura et al., Japanese Journal of Applied Physics, vol 35, p. L74, 1996参照)により、世界中で研究者の大きな増加を見ている。 40

【0004】

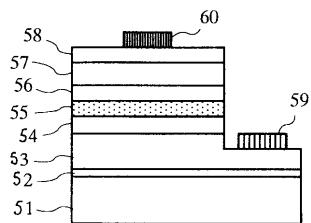

このGaN系化合物半導体は、ウルツ鉱型化合物半導体であるため、類似の結晶構造を有する六方晶系のサファイア基板或いは6H-SiC基板上にMOVPE法(有機金属気相成長法)を用いてエピタキシャル成長させていたので、ここで、図9を参照して従来の短波長発光素子を説明する。

【0005】

## 図9参照

まず、(0001)面を主面とするサファイア基板51上に、GaN低温バッファ層52を介して、n型Al<sub>0.1</sub>Ga<sub>0.9</sub>Nクラッド層53、n型GaN光ガイド層54、In<sub>0.1</sub>Ga<sub>0.9</sub>N活性層55、p型GaN光ガイド層56、p型Al<sub>0.1</sub>Ga<sub>0.9</sub>Nクラッド層57、及び、p型GaNコンタクト層58をMOVPE法によってエピタキシャル成長させたのち、エッチングによりn型Al<sub>0.1</sub>Ga<sub>0.9</sub>Nクラッド層53の一部を露出させて、Ti/Au電極59からなるn側電極を設けると共に、p型GaNコンタクト層58上にはNi/Au電極60からなるp側電極を設けていた。

## 【0006】

また、サファイア基板の代わりにn型の6H-SiC基板を用いた場合には、n型SiC基板の裏面にNi/Au電極等を形成することになる。

## 【0007】

## 【発明が解決しようとする課題】

しかし、従来の短波長発光素子の場合、p型半導体層及びn型半導体層に対するNi/Au電極（上記以外に必要ならば、例えば、特開平3-46379号公報、特開平8-316529号公報、或いは、特開昭61-272968号公報参照）において、オーミックコンタクト電極となるNi層とボンディングメタル層となるAu層との密着性が悪く、電極が剥がれやすいという問題がある。

## 【0008】

また、Ni/Au電極以外に、Ti/Ni/Au構造の電極も提案（必要ならば、特開昭61-43461号公報、特開昭55-115392号公報、或いは、特開昭57-15446号公報参照）されており、アニール処理によりTiが拡散し、Ni層とAu層との密着性は向上するが、膜厚を直接コントロールすることが可能なTi層を形成する方法に比べて密着性や信頼性が劣るという問題がある。

## 【0009】

また、Ni/Ti/Pt/Au構造の電極も提案（必要ならば、特開昭61-69148号公報、或いは、特開平8-250704号公報参照）されているが、Ni/Ti及びTi/Ptの密着性は良好であるものの、Pt/Auの密着性が悪いという問題がある。

## 【0010】

さらに、n型SiC或いはp型AlInGaNについては、Ni層をコンタクト層とするのに比べ、上述のTi/Ni/Au、或いは、Ni·Cr/(Ti)/Au（例えば、特開昭61-272968号公報参照）、或いは、Au·Ge/Ni/Au（例えば、特開平5-291609号公報参照）等の構造では、密着性のみならず、オーミック性にも問題がみられた。

## 【0011】

したがって、本発明は、p型Al<sub>x</sub>In<sub>y</sub>Ga<sub>1-x-y</sub>N及びn型SiCに設ける電極の剥離を防止することを目的とする。

## 【0012】

## 【課題を解決するための手段】

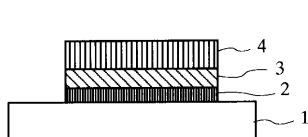

図1は本発明の原理的構成の説明図であり、この図1を参照して本発明における課題を解決するための手段を説明する。

## 図1参照

(1) 本発明は、半導体装置において、n型SiCからなる半導体層1上にNi層2、Ti層3、ボンディングメタル層としてのAu層4を順次積層させたことを特徴とする。

## 【0017】

この様に、n型SiCからなる半導体層1に対するオーミックコンタクト層としてのNi層2とボンディングメタル層としてのAu層4との間に、Ti層3を介在させることによって密着性が高まり、電極の剥離を防止することができる。

## 【0018】

(2) また、本発明は、上記(1)において、n型SiCが、発光半導体素子のn型半

導体層を構成することを特徴とする。

【0019】

この様な構成のn型SiCに対するn側電極は、n型SiCを基板とする青色半導体レーザや青色発光ダイオード、或いは、SiC青色発光ダイオード等の発光半導体素子用のn側電極として好適である。

【0020】

(3) 本発明は、上記(1)または(2)において、n型SiC上に設ける積層構造の最上層としてのp型 $Al_xIn_yGa_{1-x-y}N$ (但し、 $0 < x < 1, 0 < y < 1$ )を設けるとともに、このp型 $Al_xIn_yGa_{1-x-y}N$ に接するNi層2と、ボンディングメタル層としてのAu層4との間にTi層3を介在させたことを特徴とする。 10

【0021】

この様に、n型SiC基板を用いたGaN系半導体装置に対しては、n側電極及びp側電極として、同じNi/Ti/Au構造の電極によって密着性の良好な電極を構成することができる。

【0024】

(4) また、本発明は、半導体層1にNi層2を堆積させたのち、アニール処理を施し、次いで、その上に、Ti層3及びAu層4を順次堆積させたことを特徴とする半導体装置の製造方法において、半導体層1がp型 $Al_xIn_yGa_{1-x-y}N$ (但し、 $0 < x < 1, 0 < y < 1$ )であり、且つ、アニール処理の温度が800以下であることを特徴とする。 20

【0025】

この様に、Ni層2をオーミックコンタクト層とした電極が、ノンアロイコンタクトである場合には、Ni層2を堆積させたのち、Ti層3及びAu層4の堆積前にアニール処理を施すことによって、Ni層2の耐溶剤性、例えば、耐エッチング性を高めることができ、また、ノンアロイコンタクトでない場合には、アニールを行うことによってオーミック性を高めることが必要になる。

【0027】

この様な構造の電極は、p型 $Al_xIn_yGa_{1-x-y}N$ に対して好適であり、p型 $Al_xIn_yGa_{1-x-y}N$ に対するNi層2は、ノンアロイコンタクトであるので、Ni層2、Ti層3、及び、Au層4をアニール処理を施すことなく連続して堆積させても良い。 30

【0029】

アニール処理の温度が800を越えると、p型 $Al_xIn_yGa_{1-x-y}N$ とNi層2との合金化反応が進み、p側電極のオーミック性が劣化するので、アニール処理の温度は800以下とすることが望ましい。

【0030】

(5) また、本発明は、上記(4)において、p型 $Al_xIn_yGa_{1-x-y}N$ が、発光半導体素子のp型半導体層を構成することを特徴とする。

【0031】

この様な構成のp側電極の製造工程を、青色半導体レーザや青色発光ダイオード等の発光半導体素子のp側電極の製造工程として採用することにより、発光半導体素子のp側電極の剥離を防止して信頼性を高めることができる。 40

【0032】

(6) また、本発明は、半導体層1にNi層2を堆積させたのち、アニール処理を施し、次いで、その上に、Ti層3及びAu層4を順次堆積させたことを特徴とする半導体装置の製造方法において、半導体層1がn型SiCであることを特徴とする。

【0033】

この様な電極の製造方法は、n型SiCに対して好適であり、n型SiCに対するNi層2は、ノンアロイコンタクトでないので、Ni層2を堆積させたのち、アニール処理を施すことが必要になる。

【0034】

(7) また、本発明は、上記(6)において、アニール処理の温度が800以上であることを特徴とする。

【0035】

アニール処理の温度が800未満であると、n側電極として良好なオーミック性が得られない、800以上とすることが望ましく、また、結晶の劣化防止の観点から1100以下とすることが望ましい。

【0036】

(8) また、本発明は、上記(7)において、アニール処理を施したのち、Ti層を堆積する前にフッ酸系溶剤による処理を行うことを特徴とする。

【0037】

この様に、アニール処理を施したのち、Ti層を堆積する前にフッ酸系溶剤、例えば、フッ酸水溶液、或いは、バッファードフッ酸(緩衝フッ酸)による処理を行うことによって、Ti層3及びAu層4の密着性をより向上することができる。

【0038】

(9) また、本発明は、上記(6)乃至(8)のいずれかにおいて、n型SiCが、発光半導体素子のn型半導体層を構成することを特徴とする。

【0039】

この様な構成のn側電極の製造工程を、n型SiCを基板とした青色半導体レーザや青色発光ダイオード、或いは、SiC発光ダイオード等の発光半導体素子のn側電極の製造工程として採用することにより、発光半導体素子のn側電極の剥離を防止して信頼性を高めることができる。

【0040】

(10) また、本発明は、上記(6)乃至(9)のいずれかにおいて、n型SiC上に、p型Al<sub>x</sub>In<sub>y</sub>Ga<sub>1-x-y</sub>N(但し、0<x<1, 0<y<1)を最上層とする多層構造を形成すると共に、このp型Al<sub>x</sub>In<sub>y</sub>Ga<sub>1-x-y</sub>NにNi層2を堆積させたのち、その上に、Ti層3及びAu層4を順次堆積させたことを特徴とする。

【0041】

上記の様な電極の製造工程は、n型SiC基板上にGaN系半導体を積層させた半導体装置に対するn側電極及びp側電極の双方に適用することによって、剥離のないn側電極及びp側電極を構成することができる。

【0042】

(11) また、本発明は、上記(10)において、n型SiCに対するn側電極を設けたのち、p型Al<sub>x</sub>In<sub>y</sub>Ga<sub>1-x-y</sub>Nに対するp側電極を形成することを特徴とする。

【0043】

上述の様に、p型Al<sub>x</sub>In<sub>y</sub>Ga<sub>1-x-y</sub>Nに対するアニール温度は800以下であり、n型SiCに対するアニール温度は800以上であるので、n側電極を形成したのちに、p側電極を形成することが必要となる。

【0044】

(12) また、本発明は、上記(4)乃至(11)のいずれかにおいて、Ni層2、Ti層3、及び、Au層4のうち、少なくとも、Ti層3及びAu層4を所定の形状にエッチングして電極を形成することを特徴とする。

【0045】

この様に、Ni層2、Ti層3、及び、Au層4を全面に設けたのち、少なくとも、Ti層3及びAu層4を所定の形状にエッチングして電極を形成することによって、電極の密着性をより改善することができる。

【0046】

【発明の実施の形態】

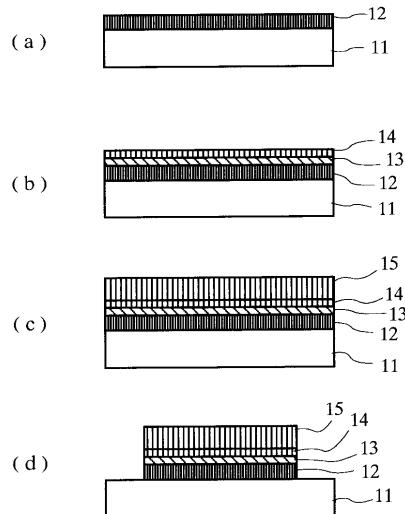

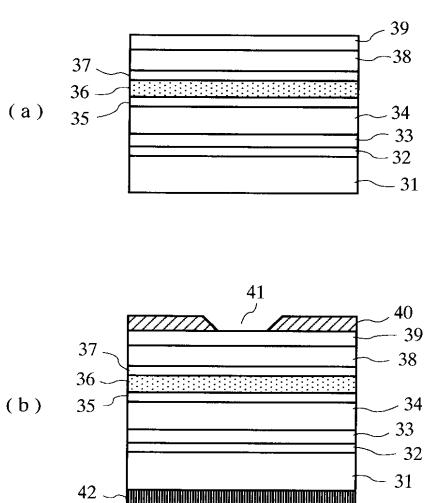

ここで、図2及び図3を参照して、本発明の第1の実施の形態を説明する。

なお、図2は、本発明の第1の実施の形態の製造工程の説明図であり、図においては、説明を簡単にするために、素子構造を省略して最上層のp型GaN層に対するp側電極の形

10

20

20

30

30

40

50

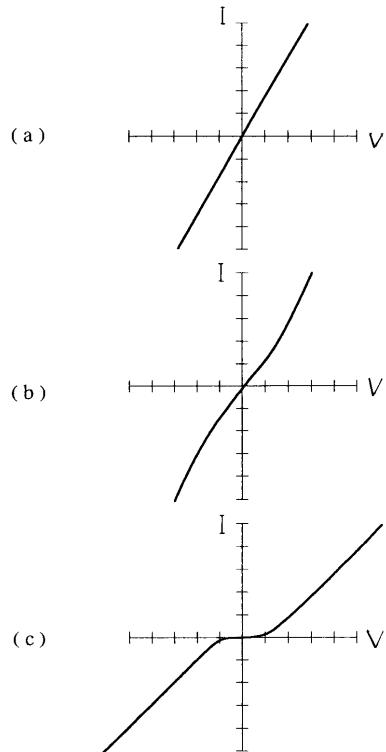

成工程を示すものであり、また、図3は、本発明の第1の実施の形態の電極のオーミック性の熱処理温度（アニール処理温度）依存性の測定結果を示す図である。

【0047】

図2(a)参照

まず、p型GaN層11を有機洗浄及び酸洗浄してその表面を清浄化した後、EB（電子ビーム）蒸着法を用いて、p型GaN層11上に、厚さ0.05～0.3μm、例えば、0.3μmのNi層12をオーミックコンタクト層として堆積させる。

【0048】

次いで、N<sub>2</sub>雰囲気中で、400～800、例えば、400で、60秒～25分、例えば、5分間のアニール処理を施す。

10

このアニール処理によってNi層12の耐溶剤性、例えば、耐エッチャント性が高まる。

【0049】

図2(b)参照

次いで、同じくEB蒸着法を用いて、厚さ0.03～0.1μm、例えば、0.05μmのTi層13、及び、厚さ0.03～0.4μm、例えば、0.05μmのAu蒸着層14を順次堆積させる。

【0050】

図2(c)参照

次いで、電解メッキ法を用いて、Au蒸着層14上に、厚さ0.5～5μm、例えば、2.0μmのAuメッキ層15を堆積させる。

20

【0051】

図2(d)参照

最後に、マスク（図示せず）を用いてシアン系エッチャントのテクニストリップ金を用いてAuメッキ層15及びAu蒸着層14を所定パターンにエッティングし、次いで、フッ素系エッチャント、例えば、0.2%フッ酸水溶液、或いは、2%バッファードフッ酸を用いてTi層13をエッティングし、次いで、硝酸水溶液、硫酸水溶液、または、塩酸水溶液、例えば、40%硝酸水溶液を用いてNi層12をエッティングすることによって、p型GaN層11に対するp側電極が完成する。

【0052】

この様な、Ni/Ti/Au構造の電極は、中間にTi層を介在させているので、従来のNi/Au構造のp側電極に比べて密着性が高まり、ポンディング圧力等の物理的な衝撃によっても剥離しにくくなり、発光半導体素子の信頼性が向上する。

30

【0053】

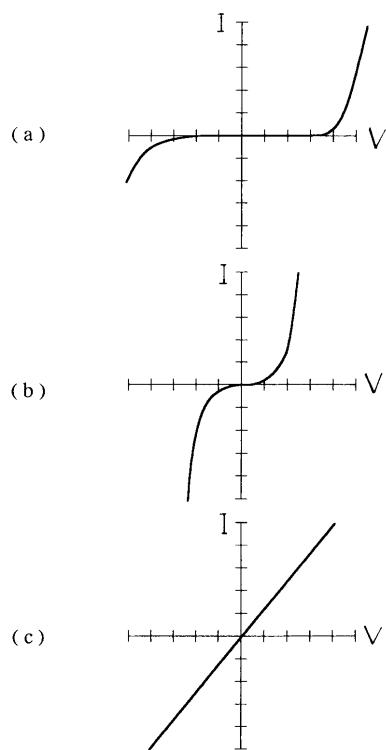

図3(a)参照

図3(a)は、400でアニール処理を行った場合の、p側電極の電流-電圧特性(I-V特性)の測定結果を示す図であり、低抵抗で、且つ、直線性の良好な従来のNi/Au電極と同様のオーミック特性を示している。

なお、図において、縦軸の1目盛りは50μAを表し、横軸の1目盛りは2Vを表しており、図3(b)及び(c)も同様である。

【0054】

40

図3(b)参照

図3(b)は、600でアニール処理を行った場合の、p側電極のI-V特性の測定結果を示す図であり、比較的低抵抗ではあるが、低バイアス電圧時に高抵抗化する傾向が見られる。

【0055】

図3(c)参照

図3(c)は、800でアニール処理を行った場合の、p側電極のI-V特性の測定結果を示す図であり、高抵抗化すると共に、低バイアス電圧側における非直線性が顕著になり、p型GaN層11とNi層12との間の合金化反応が進行していることを示している。

50

## 【0056】

したがって、800 以上の温度によるアニール処理を行った場合には、オーミック性が劣化し、電気的特性の良好な発光半導体素子を得ることが困難になるので、アニール処理温度は800 以下が望ましい。

## 【0057】

なお、Niオーミックコンタクトは、ノンアロイコンタクトであるので、400 以下のアニール処理を施しても、そのオーミック性は400 のアニール処理の場合と殆ど変わらない。

## 【0058】

また、Ni層12 のアニール工程は必ずしも必須の工程ではないが、Ni層12 の耐溶剤性を高めるためには、400 以上の熱処理が必要となる。 10

## 【0059】

また、このアニール処理は、Ti層13 及びAu層14 の堆積前に行なうことが肝要であり、Ti層13 及びAu層14 の堆積後に行なった場合には、メタルの層間拡散、或いは、p型GaN層11への拡散等により半導体素子の電気的特性が劣化する。

## 【0060】

また、上記の第1の実施の形態の説明においては、メタル層の堆積手段として、EB蒸着法を用いているが、Ni層12 及びAu蒸着層14 についてはEB蒸着法に限られるものではなく、例えば、通常の抵抗加熱による蒸着法を用いても良いものである。

## 【0061】

また、上記の第1の実施の形態の説明においては、Ti層13 とAu蒸着層14 の厚さを0.5 μm 及び0.5 μm にしているが、夫々、0.03 μm 及び0.03 μm にしても良いのである。 20

## 【0062】

さらに、上記の第1の実施の形態においてはAuメッキ層15 を設けているが、Auメッキ層15 を用いずに、Ti層13 の厚さを0.05 μm にすると共に、Au蒸着層14 の厚さを0.38 μm 以上、例えば、0.45 μm に堆積するだけでも良い。

## 【0063】

また、上記の第1の実施の形態においては、説明を簡単にするために、p側電極を設ける半導体層をp型GaN層として説明しているが、この様な電極構造はp型Al<sub>0.1</sub>Ga<sub>0.9</sub>N層等の他のp型GaN系化合物半導体、即ち、p型Al<sub>x</sub>In<sub>y</sub>Ga<sub>1-x-y</sub>N (但し、0 < x < 1, 0 < y < 1) にも適用されるものである。 30

## 【0064】

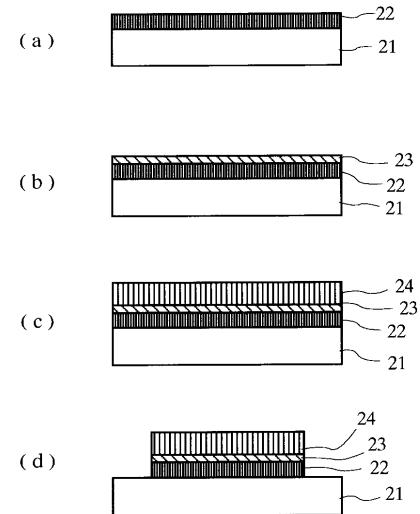

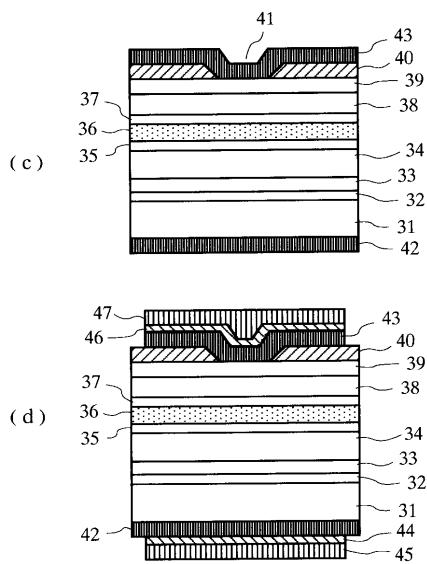

次に、図4 及び図5 を参照して、本発明の第2の実施の形態を説明する。

なお、図4は、本発明の第2の実施の形態の製造工程の説明図であり、図においては、説明を簡単にするために、素子構造を省略してn型SiC層に対するn側電極の形成工程を示すものであり、また、図5は、本発明の第2の実施の形態の電極のオーミック性の熱処理温度(アニール処理温度)依存性の測定結果を示す図である。

## 【0065】

図4 (a) 参照 40

まず、n型SiC層21 を有機洗浄及び酸洗浄してその表面を清浄化した後、EB(電子ビーム)蒸着法を用いて、n型SiC層21 上に、厚さ0.05~0.3 μm、例えば、0.3 μm のNi層22 をオーミックコンタクト層として堆積させる。

## 【0066】

次いで、N<sub>2</sub> 雰囲気中で、800~1100 、例えば、900 で、30秒~5分、例えば、5分間のアニール処理を施す。

このアニール処理によってNi層12 の耐溶剤性、例えば、耐エッチャント性が高まる。

## 【0067】

図4 (b) 及び (c) 参照

次いで、同じくEB蒸着法を用いて、厚さ0.03~0.1 μm、例えば、0.05 μm 50

の Ti 層 23、及び、厚さ 0.38 μm 以上、例えば、0.5 μm の Au 蒸着層 24 を順次堆積させる。

【0068】

図 4 (d) 参照

最後に、マスク（図示せず）を用いてシアン系エッチャントのテクニストリップ金を用いて Au 蒸着層 24 を所定パターンにエッチングし、次いで、フッ素系エッチャント、例えば、0.2% フッ酸水溶液、或いは、2% バッファードフッ酸を用いて Ti 層 23 をエッチングし、次いで、硝酸水溶液、硫酸水溶液、または、塩酸水溶液、例えば、40% 硝酸水溶液を用いて Ni 層 22 をエッチングすることによって、n 型 SiC 層 21 に対する n 側電極が完成する。

10

【0069】

この様な n 型 SiC 層 21 に対する、Ni / Ti / Au 構造の電極も、中間に Ti 層を介在させているので、従来の Ni / Au 構造の n 側電極に比べて密着性が高まり、ポンディング圧力等の物理的な衝撃によっても剥離しにくくなり、発光半導体素子の信頼性が向上する。

【0070】

図 5 (a) 参照

図 5 (a) は、600 でアニール処理を行った場合の、n 側電極の電流 - 電圧特性 (I - V 特性) の測定結果を示す図であり、低バイアス電圧においてはほとんど電流が流れず、オーミック性を示さない。

20

なお、図において、縦軸の 1 目盛りは 50 μA を表し、横軸の 1 目盛りは 2 V を表しており、図 5 (b) も同様である。

【0071】

図 5 (b) 参照

図 5 (b) は、800 でアニール処理を行った場合の、n 側電極の I - V 特性の測定結果を示す図であり、比較的低抵抗ではあるが、低バイアス電圧時に高抵抗化する傾向が見られる。

【0072】

図 5 (c) 参照

図 5 (c) は、900 でアニール処理を行った場合の、n 側電極の電流 - 電圧特性 (I - V 特性) の測定結果を示す図であり、低抵抗で、且つ、直線性の良好な従来の Ni / Au 電極と同様のオーミック特性を示している。

30

なお、図において、縦軸の 1 目盛りは 5 mA を表し、横軸の 1 目盛りは 0.2 V を表している。

【0073】

したがって、800 未満の温度によるアニール処理を行った場合には、オーミック性が得られず、電気的特性の良好な発光半導体素子を得ることが困難になるので、アニール処理温度は 800 以上、且つ、結晶の劣化防止の観点から 1100 以下が望ましい。

【0074】

また、この場合のアニール処理も、Ti 層 23 及び Au 蒸着層 24 の堆積前に行なうことが肝要であり、Ti 層 23 及び蒸着 Au 層 24 の堆積後に行なった場合には、メタルの層間拡散、或いは、n 型 SiC 層 21 への拡散等により半導体素子の電気的特性が劣化する。

40

【0075】

また、この場合、Ni / Ti / Au 構造を全面に蒸着したのちエッチングによりパターン化しているので、各電極の密着面積が大きくなるので、密着性が向上する。

【0076】

なお、上記の第 2 の実施の形態の説明においても、メタル層の堆積手段として、EB 蒸着法を用いているが、Ni 層 22 及び Au 蒸着層 24 については EB 蒸着法に限られるものではなく、例えば、通常の抵抗加熱による蒸着法を用いても良いものである。

【0077】

50

また、上記の第2の実施の形態において、アニール処理後に、酸洗浄、例えば、バッファードフッ酸による洗浄を行うことにより、Ti/Au層との密着性がさらに改善される。

【0078】

また、上記の第2の実施の形態においては、Ni層22も選択エッチングによりポンディングパッド以外の領域を除去しているが、Ni層22はエッチングせずに、Ti層23及びAu蒸着層24のみを選択的にエッチングしても良いものである。

【0079】

次に、図6及び図7を参照して、本発明の第3の実施の形態の製造工程を説明する。

図6(a)参照

まず、(0001)面、即ち、c面を主面とする六方晶の6H-SiCからなるn型SiC基板31を厚さ80~200μm、より好適には100~120μmになるように研磨したのち、有機洗浄及びフッ酸等による酸洗浄してその表面を清浄化した後、n型SiC基板31上に、有機金属気相成長法(MOVPE法)を用いて、例えば、厚さ50nmのn型AlGaNバッファ層32を成長させる。

【0080】

引き続いて、厚さ0.5μmのn型GaN中間層33、厚さ0.5μmで、不純物濃度が $1.0 \times 10^{18} \text{ cm}^{-3}$ のn型AlGaNクラッド層34、厚さ100nmのGaN光ガイド層35、MQW活性層36、厚さ100nmのGaN光ガイド層37、厚さ0.5μmで、不純物濃度が $1.0 \times 10^{17} \text{ cm}^{-3}$ のp型AlGaNクラッド層38、及び、厚さ、0.5μmで、不純物濃度が $1.0 \times 10^{17} \text{ cm}^{-3}$ のp型GaNコンタクト層39を順次成長させる。

【0081】

なお、この場合のMQW活性層36は、厚さ5nmのアンドープIn<sub>0.03</sub>Ga<sub>0.97</sub>Nバリア層と厚さ5nmのアンドープIn<sub>0.15</sub>Ga<sub>0.85</sub>N井戸層を交互に成長させたものであり、また、n型AlGaNクラッド層34及びp型AlGaNクラッド層38のAl組成比は0.09である。

【0082】

図6(b)参照

次いで、EB蒸着法を用いてn型SiC基板31の裏面に厚さ0.03~0.5μm、例えば、0.3μmのNi層42をオーミックコンタクト層として堆積させたのち、N<sub>2</sub>雰囲気中で、900~1100、例えば、900で、30秒~5分、例えば、5分間のアニール処理を施したのち、バッファードフッ酸或いはフッ酸水溶液を用いて洗浄する。このアニール処理によってNi層42の耐溶剤性、例えば、耐エッチャント性が高まり、また、洗浄によって次工程で堆積させるTi/Au層との密着性が改善される。

【0083】

次いで、p型GaNコンタクト層39の表面を有機洗浄及び酸洗浄を行ったのち、p型GaNコンタクト層39上に厚さ0.2~0.4μm、例えば、0.25μmのSiO<sub>2</sub>膜40を形成し、次いで、エッチングにより幅1~12μmのコンタクトホール41(ストライプ状開口)を形成する。

【0084】

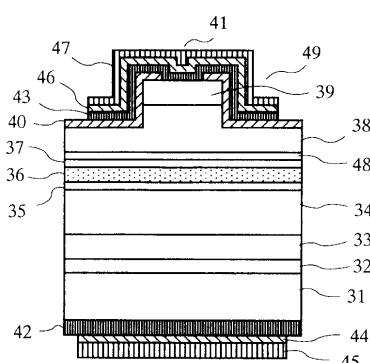

図7(c)参照

次いで、p型GaNコンタクト層39の露出表面を有機洗浄及び酸洗浄を行ったのち、p型GaNコンタクト層39側の全面に厚さ0.03~0.5μm、例えば、0.3μmのNi層43をオーミックコンタクト層として堆積させる。

【0085】

次いで、N<sub>2</sub>雰囲気中で、400~800、例えば、400で、60秒~25分、例えば、5分間のアニール処理を行う。

このアニール処理によってNi層43の耐溶剤性、例えば、耐エッチャント性が高まる。

【0086】

図7(d)参照

10

20

50

30

40

50

次いで、同じくEB蒸着法を用いて、p型GaNコンタクト層39側に厚さ0.03~0.1μm、例えば、0.05μmのTi層46、及び、厚さ0.38μm以上、例えば、0.45μmのAu層47を順次堆積させる。

【0087】

次いで、ボンディングパッドに対応する大きさの300μm×700μmのマスク(図示せず)を用いてシアン系エッチャントのテクニストリップ金を用いてAu層47を所定パターンにエッティングし、次いで、フッ素系エッチャント、例えば、0.2%フッ酸水溶液、或いは、2%バッファードフッ酸を用いてTi層46をエッティングし、次いで、硝酸水溶液、硫酸水溶液、或いは、塩酸水溶液、例えば、40%硝酸水溶液を用いてNi層43をエッティングすることによって、p側電極を形成する。

10

【0088】

次いで、同じくEB蒸着法を用いて、n型SiC基板31側に厚さ0.03~0.1μm、例えば、0.05μmのTi層44、及び、厚さ0.38μm以上、例えば、0.45μmのAu層45を順次堆積させる。

【0089】

次いで、ボンディングパッドに対応する大きさの300μm×700μmのマスク(図示せず)を用いてシアン系エッチャントのテクニストリップ金を用いてAu層45を所定パターンにエッティングし、次いで、フッ素系エッチャント、例えば、0.2%フッ酸水溶液、或いは、2%バッファードフッ酸を用いてTi層44をエッティングすることによって、n型SiC層21に対するn側電極を形成し、最後に、適当な荷重でスクライプのキズをいれ、劈開を行うことによって青色半導体レーザが完成する。

20

【0090】

この様に、第3の実施の形態においては、同じ材料及び同じ工程によって形成した同じNi/Ti/Au構造の電極を用いてn側電極及びp側電極の双方を形成することができる。製造工程を簡素化することができる。

【0091】

なお、上記の第3の実施の形態におけるp側電極は、上記の第1の実施の形態及びその変形例によって構成しても良く、また、n側電極は、上記の第2の実施の形態及びその変形例によって構成しても良い。

【0092】

30

また、この第3の実施の形態においては、アニール処理温度の関係から、n型SiC基板31に対してNi層42を形成したのち、p型GaNコンタクト層39に対するNi層43形成することが必須であるが、Ti層44/Au層45及びTi層46/Au層47の形成順序及びパターニング順序は適宜変更し得るものである。

【0093】

例えば、上記の図7(c)の様にn型SiC基板とp型GaNコンタクト層にNi層を形成したのち、n型SiC基板とp型GaNコンタクト層の双方にTi/Au層を順次形成し、次いで、n側電極及びp側電極をボンディングパッドに相当する大きさにエッティングしても良く、n側電極及びp側電極のどちらのボンディングパッドを先に形成しても良いものである。

40

【0094】

次に、図8を参照して本発明の第4の実施の形態を説明するが、オーバーフロー防止層を設ける工程、及び、リッジを構成する工程を加える以外は上記の第3の実施の形態と同様である。

図8参照

まず、n型SiC基板31上に、有機金属気相成長法(MOVPE法)を用いて、n型AlGaNバッファ層32、n型GaN中間層33、n型AlGaNクラッド層34、GaN光ガイド層35、MQW活性層36、オーバーフロー防止層となるp型AlGaN層48、GaN光ガイド層37、p型AlGaNクラッド層38、及び、p型GaNコンタクト層39を順次成長させる。

50

## 【0095】

次いで、 $\text{CHF}_3$  を用いたドライ・エッティングによって、p型 GaN コンタクト層 39 及び p型 AlGaN クラッド層 38 を選択的にエッティングしてリッジ 49 を形成する。

## 【0096】

後は、第 3 の実施の形態と同様に、EB 蒸着法を用いて n型 SiC 基板 31 の裏面に Ni 層 42 を堆積させたのち、 $\text{N}_2$  雰囲気中でアニール処理を施したのち、バッファードフッ酸或いはフッ酸水溶液を用いて洗浄する。

## 【0097】

次いで、p型 GaN コンタクト層 39 及び p型 AlGaN クラッド層 38 の露出表面を有機洗浄及び酸洗浄を行ったのち、全面に  $\text{SiO}_2$  膜 40 を形成し、次いで、エッティングによりコンタクトホール 41 (ストライプ状開口) を形成し、次いで、p型 GaN コンタクト層 39 の露出表面を有機洗浄及び酸洗浄を行ったのち、p型 GaN コンタクト層 39 側の全面に Ni 層 43 を堆積させる。

10

## 【0098】

次いで、 $\text{N}_2$  雰囲気中でアニール処理を行ったのち、同じく EB 蒸着法を用いて、p型 GaN コンタクト層 39 側に Ti 層 46 及び Au 層 47 を順次堆積させ、次いで、ポンディングパッドに対応する大きさの  $300 \mu\text{m} \times 700 \mu\text{m}$  のマスクを用いて Au 層 47、Ti 層 46、及び、Ni 層 43 を順次エッティングすることによって p 側電極を形成する。

## 【0099】

次いで、同じく EB 蒸着法を用いて、n型 SiC 基板 31 側に Ti 層 44 及び、Au 層 45 を順次堆積させたのち、ポンディングパッドに対応する大きさの  $300 \mu\text{m} \times 700 \mu\text{m}$  のマスクを用いて、Au 層 45 及び Ti 層 44 を順次エッティングすることによって、n型 SiC 層 31 に対する n 側電極を形成し、最後に、適当な荷重でスクライブのキズをいれ、劈開を行うことによって青色半導体レーザが完成する。

20

## 【0100】

以上、本発明の各実施の形態を説明してきた様に、本発明の半導体装置の主な対象は、半導体レーザ或いは発光ダイオード等の発光半導体素子であるが、本発明は、必ずしも発光半導体素子に限られるものではなく、GaN 系化合物半導体を用いた他の非発光性の半導体素子にも適用されるものであり、また、SiC のみを用いた半導体装置、例えば、SiC 青色発光ダイオードにも適用されるものである。

30

## 【0101】

## 【発明の効果】

本発明によれば、GaN 系化合物半導体からなる半導体装置の p 側電極及び n 側電極を、Ni / Ti / Au 構造としたので、電気的特性を損なうことなく密着性が向上し、電極の剥離が防止されるので、GaN 系化合物半導体装置の信頼性向上に寄与し、ひいては、青色半導体レーザや青色発光ダイオードの実用化に寄与するところが大きい。

## 【図面の簡単な説明】

【図 1】本発明の原理的構成の説明図である。

【図 2】本発明の第 1 の実施の形態の製造工程の説明図である。

【図 3】本発明の第 1 の実施の形態の電極のオーミック性の熱処理温度依存性の説明図である。

40

【図 4】本発明の第 2 の実施の形態の製造工程の説明図である。

【図 5】本発明の第 2 の実施の形態の電極のオーミック性の熱処理温度依存性の説明図である。

【図 6】本発明の第 3 の実施の形態の途中までの製造工程の説明図である。

【図 7】本発明の第 3 の実施の形態の図 6 以降の製造工程の説明図である。

【図 8】本発明の第 4 の実施の形態の説明図である。

【図 9】従来の短波長発光素子の説明図である。

## 【符号の説明】

|     |                                                   |    |

|-----|---------------------------------------------------|----|

| 2   | N i 層                                             |    |

| 3   | T i 層                                             |    |

| 4   | A u 層                                             |    |

| 1 1 | p 型 G a N 層                                       |    |

| 1 2 | N i 層                                             |    |

| 1 3 | T i 層                                             |    |

| 1 4 | A u 蒸着層                                           |    |

| 1 5 | A u メッキ層                                          |    |

| 2 1 | n 型 S i C 層                                       |    |

| 2 2 | N i 層                                             | 10 |

| 2 3 | T i 層                                             |    |

| 2 4 | A u 蒸着層                                           |    |

| 3 1 | n 型 S i C 基板                                      |    |

| 3 2 | n 型 A l G a N バッファ層                               |    |

| 3 3 | n 型 G a N 中間層                                     |    |

| 3 4 | n 型 A l G a N クラッド層                               |    |

| 3 5 | G a N 光ガイド層                                       |    |

| 3 6 | M Q W 活性層                                         |    |

| 3 7 | G a N 光ガイド層                                       |    |

| 3 8 | p 型 A l G a N クラッド層                               | 20 |

| 3 9 | p 型 G a N コンタクト層                                  |    |

| 4 0 | S i O <sub>2</sub> 膜                              |    |

| 4 1 | コンタクトホール                                          |    |

| 4 2 | N i 層                                             |    |

| 4 3 | N i 層                                             |    |

| 4 4 | T i 層                                             |    |

| 4 5 | A u 層                                             |    |

| 4 6 | T i 層                                             |    |

| 4 7 | A u 層                                             |    |

| 4 8 | p 型 A l G a N 層                                   | 30 |

| 4 9 | リッジ                                               |    |

| 5 1 | サファイア基板                                           |    |

| 5 2 | G a N 低温バッファ層                                     |    |

| 5 3 | n 型 A l <sub>0.1</sub> G a <sub>0.9</sub> N クラッド層 |    |

| 5 4 | n 型 G a N 光ガイド層                                   |    |

| 5 5 | I n <sub>0.1</sub> G a <sub>0.9</sub> N 活性層       |    |

| 5 6 | p 型 G a N 光ガイド層                                   |    |

| 5 7 | p 型 A l <sub>0.1</sub> G a <sub>0.9</sub> N クラッド層 |    |

| 5 8 | p 型 G a N コンタクト層                                  |    |

| 5 9 | T i / A u 電極                                      | 40 |

| 6 0 | N i / A u 電極                                      |    |

【図1】

本発明の原理的構成の説明図

1: 半導体層

2: Ni層

3: Ti層

4: Au層

【図2】

本発明の第1の実施の形態の製造工程の説明図

11: p型GaN層

12: Ni層

13: Ti層

14: Au蒸着層

15: Auメッキ層

【図3】

本発明の第1の実施の形態の電極のオーミック性の熱処理温度依存性の説明図

【図4】

本発明の第2の実施の形態の製造工程の説明図

21: n型SiC層

22: Ni層

23: Ti層

24: Au蒸着層

【図5】

本発明の第2の実施の形態の電極のオーミック性の熱処理温度依存性の説明図

【図6】

本発明の第3の実施の形態の途中までの製造工程の説明図

31: n型SiC基板

32: n型AlGaNバッファ層

33: n型GaN中間層

34: n型AlGaNクラッド層

35: GaN光ガイド層

36: MQW活性層

37: GaN光ガイド層

38: p型AlGaNクラッド層

39: p型GaNコンタクト層

40: SiO<sub>2</sub>膜

41: コンタクトホール

42: Ni層

【図7】

本発明の第3の実施の形態の図6以降の製造工程の説明図

31: n型SiC基板

32: n型AlGaNバッファ層

33: n型GaN中間層

34: n型AlGaNクラッド層

35: GaN光ガイド層

36: MQW活性層

37: GaN光ガイド層

38: p型AlGaNクラッド層

39: p型GaNコンタクト層

40: SiO<sub>2</sub>膜

41: コンタクトホール

42: Ni層

43: Ni層

44: Ti層

45: Au層

【図8】

本発明の第4の実施の形態の説明図

31: n型SiC基板

32: n型AlGaNバッファ層

33: n型GaN中間層

34: n型AlGaNクラッド層

35: GaN光ガイド層

36: MQW活性層

37: GaN光ガイド層

38: p型AlGaNクラッド層

39: p型GaNコンタクト層

40: SiO<sub>2</sub>膜

41: コンタクトホール

42: Ni層

43: Ni層

44: Ti層

45: Au層

46: Ti層

47: Au層

48: p型AlGaN層

49: リッジ

## 【図9】

従来の短波長発光素子の説明図

- 51 : サファイア基板

52 : GaN低温バッファ層

53 : n型Al<sub>0.1</sub>Ga<sub>0.9</sub>Nクラッド層

54 : n型GaN光ガイド層

55 : In<sub>0.1</sub>Ga<sub>0.9</sub>N活性層

56 : p型GaN光ガイド層

57 : p型Al<sub>0.1</sub>Ga<sub>0.9</sub>Nクラッド層

58 : p型GaNコンダクト層

59 : Ti/Au電極

60 : Ni/Au電極

---

フロントページの続き

(56)参考文献 特開平10-335699(JP,A)

特開平09-045889(JP,A)

特開平10-214847(JP,A)

特開平10-027946(JP,A)

特開平11-340580(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L33/00

H01S5/00-5/50

H01L21/28