(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7516040号**

**(P7516040)**

(45)発行日 令和6年7月16日(2024.7.16)

(24)登録日 令和6年7月5日(2024.7.5)

(51)国際特許分類

|         |                  |         |        |

|---------|------------------|---------|--------|

| H 0 1 L | 33/30 (2010.01)  | H 0 1 L | 33/30  |

| H 0 1 L | 21/205 (2006.01) | H 0 1 L | 21/205 |

F I

請求項の数 20 (全21頁)

(21)出願番号 特願2019-231018(P2019-231018)

(22)出願日 令和1年12月23日(2019.12.23)

(65)公開番号 特開2020-102629(P2020-102629)

A)

(43)公開日 令和2年7月2日(2020.7.2)

審査請求日 令和4年12月8日(2022.12.8)

(31)優先権主張番号 107146841

(32)優先日 平成30年12月24日(2018.12.24)

(33)優先権主張国・地域又は機関

台湾(TW)

(73)特許権者 598061302

晶元光電股 ふん 有限公司

E p i s t a r C o r p o r a t i o n

台灣新竹科學工業園區新竹市東區力行路

21號

21, Li - hsin Rd., Sci

ence - based Industr

ial Park, Hsinchu 30

0, TAIWAN

(74)代理人 100107766

弁理士 伊東 忠重

(74)代理人 100070150

弁理士 伊東 忠彦

(74)代理人 100091214

弁理士 大貫 進介

最終頁に続く

(54)【発明の名称】 半導体素子

**(57)【特許請求の範囲】****【請求項1】**

半導体スタック層を含む半導体素子であって、

前記半導体スタック層は、

第一格子定数を有し、且つ第一側及び該第一側に相対する第二側を有する第一型半導体構造；

前記第一側に位置し、P又はAsを含むがNを含まず、且つ放射線を発するアクティブ構造であって、前記放射線のピーク波長は、1000 nm ~ 2000 nmの間にある、アクティブ構造；及び

前記第二側に位置し、第二格子定数を有し、且つIII-V族化合物半導体材料を含む第一接觸層を含み、

前記第二格子定数と前記第一格子定数との間の差は、少なくとも0.5 %である、半導体素子。

**【請求項2】**

請求項1に記載の半導体素子であって、

前記アクティブ構造は、四元化合物半導体を含む、半導体素子。

**【請求項3】**

請求項2に記載の半導体素子であって、

前記四元化合物半導体は、AlInGaAs又はInGaAsPである、半導体素子。

**【請求項4】**

請求項2又は3に記載の半導体素子であって、

前記第一接触層のエネルギーギャップは、前記アクティブ構造及び前記第一型半導体構造のエネルギーギャップよりも大きい、半導体素子。

**【請求項5】**

請求項1から4のうちの何れか1項に記載の半導体素子であって、

前記第一型半導体構造は、Nを含まない三元又は二元化合物を含む、半導体素子。

**【請求項6】**

請求項1から5のうちの何れか1項に記載の半導体素子であって、

前記第一接触層は、 $1 \times 10^{18} / \text{cm}^3$ よりも大きい第一ドーピング濃度を有する第一ドーピングを含む、半導体素子。

10

**【請求項7】**

請求項1から6のうちの何れか1項に記載の半導体素子であって、

前記第一接触層は、GaAsを含む、半導体素子。

**【請求項8】**

請求項1から7のうちの何れか1項に記載の半導体素子であって、

前記第一接触層の厚さは、5 nm ~ 100 nmの範囲内である、半導体素子。

20

**【請求項9】**

請求項1から8のうちの何れか1項に記載の半導体素子であって、

前記半導体スタック層は、前記第一接触層と前記第一型半導体構造との間に位置する第一ウィンドウ層を更に含み、

前記第一ウィンドウ層と前記第一接触層は、同じ材料、又は、異なる材料を有する、半導体素子。

**【請求項10】**

請求項1から9のうちの何れか1項に記載の半導体素子であって、

前記半導体スタック層は、前記第一接触層と前記第一型半導体構造との間に位置する緩衝層を更に含む、半導体素子。

30

**【請求項11】**

請求項9に記載の半導体素子であって、

前記半導体スタック層は、第二型半導体構造及び第二ウィンドウ層を更に含み、

前記アクティブ構造は、前記第二型半導体構造と前記第一型半導体構造との間に位置し、

前記第二型半導体構造は、前記アクティブ構造と前記第二ウィンドウ層との間に位置する、半導体素子。

40

**【請求項12】**

請求項11に記載の半導体素子であって、

前記第二ウィンドウ層の材料は、前記第一ウィンドウ層の材料と同じである、半導体素子。

**【請求項13】**

請求項12に記載の半導体素子であって、

前記第二ウィンドウ層の材料及び前記第一ウィンドウ層の材料は、InPを含む、半導体素子。

50

**【請求項14】**

請求項11に記載の半導体素子であって、

前記第二ウィンドウ層は、第三格子定数を有し、

前記第三格子定数と前記第二格子定数との間の差は、少なくとも0.5%である、半導体素子。

**【請求項15】**

請求項1から4のうちの何れか1項に記載の半導体素子であって、

第一電極及び第二電極を更に含み、

前記第一電極及び前記第二電極は、前記半導体スタック層の対向する両側、又は、前記半導体スタック層の同じ側に位置する、半導体素子。

50

**【請求項 16】**

請求項15に記載の半導体素子であって、

基板を更に含み、

前記第一型半導体構造は、前記第一接触層と前記基板との間に位置する、半導体素子。

**【請求項 17】**

請求項16に記載の半導体素子であって、

反射構造を更に含み、

前記反射構造は、前記半導体スタック層の下に位置する、半導体素子。

**【請求項 18】**

請求項17に記載の半導体素子であって、

前記反射構造は、バリア層、前記バリア層の上に位置する反射接着層、及び前記反射接着層の上に位置する反射層を含む、半導体素子。

10

**【請求項 19】**

請求項18に記載の半導体素子であって、

導電構造を更に含み、

前記導電構造は、前記反射構造と前記半導体スタック層との間に位置する、半導体素子。

**【請求項 20】**

請求項19に記載の半導体素子であって、

絶縁層を更に含み、

前記絶縁層は、前記導電構造と前記半導体スタック層との間に位置する、半導体素子。

20

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体素子に関し、特に、格子定数差を有する半導体素子に関する。

**【背景技術】****【0002】**

科学技術の日進月歩に伴い、半導体素子は、情報伝送、エネルギー変換などの分野において非常に重要な役割を果たしており、関連する材料の研究開発も持続的に行われている。例を挙げて言えば、半導体材料は、各種の光電素子、例えば、発光ダイオード(light emitting diode、LED)、レーザーダイオード(laser diode、LD)、太陽電池(solar cell)、パワー素子(power device)、音波センサー(acoustic wave sensor)などに応用することができ、また、照明、表示、通信、検出、電源システムなどの分野に応用することもできる。

30

**【0003】**

発光ダイオードの発光の原理は、電流を印加してN型半導体層中の電子とP型半導体層中の正孔とを結合させることで、電気エネルギーを光エネルギーに変換するものである。発光ダイオードは、消費電力が低く、使用寿命が長いなどの利点を有するので、従来の光源に代えて、交通信号機、バックライトモジュール、各種の照明、医療機器などに大量応用されている。赤外線を発する発光ダイオードは、検出システム、認識システム、監視システム及び車載用光源の面においても大きい市場及び潜在力を持っている。

40

**【発明の概要】****【発明が解決しようとする課題】****【0004】**

本発明の目的は、格子定数差を有する半導体素子を提供することにある。

**【課題を解決するための手段】****【0005】**

本発明の幾つかの実施例によれば、半導体素子が提供され、それは、

第一型半導体構造であって、第一格子定数を有し、且つ第一側及び該第一側に相対する

第二側を有するもの；

アクティブ構造であって、第一型半導体構造の第一側に位置し且つ放射線をし、該放射

50

線のピーク波長は、1000 nm ~ 2000 nm の間にあるもの；及び

第一接觸層であって、第一型半導体構造の第二側に位置し、第二格子定数を有し、且つ  $1 \times 10^{18} / \text{cm}^3$  よりも大きい第一ドーピング濃度を有する第一ドーパントを含むものを含み、そのうち、第二格子定数と第一格子定数との間の差は、少なくとも 0.5 % である。

#### 【図面の簡単な説明】

##### 【0006】

以下、図面を参照しながら本発明の実施例について詳しく説明する。なお、図面では、各種の特徴が寸法に比例して描かれているものでなく、例示に過ぎない。また、本発明の特徴をより明確に示すために、素子のサイズを任意に拡縮する場合もある。

10

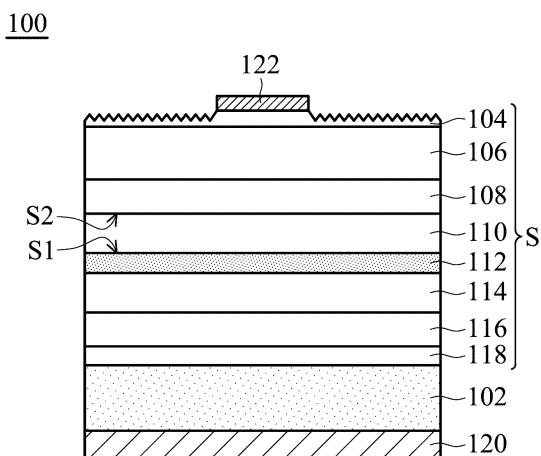

【図1】一実施例における半導体素子の断面図である。

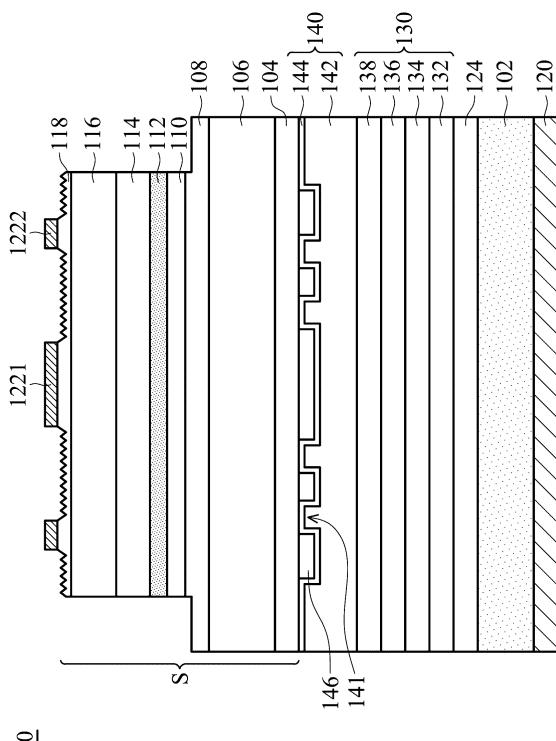

【図2】一実施例における半導体素子の断面図である。

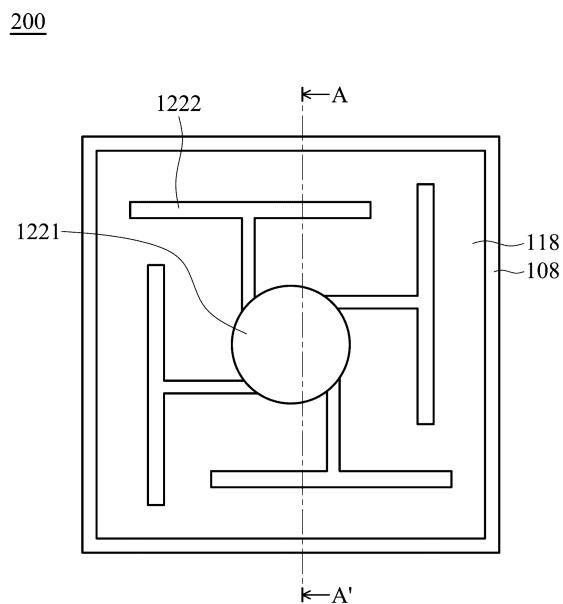

【図3】一実施例における半導体素子の上面図である。

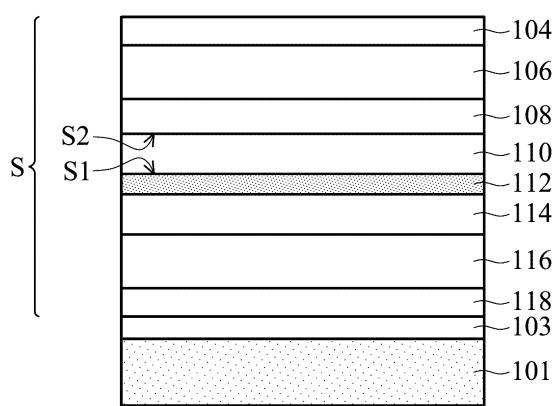

【図4A】図2における半導体素子を製造する段階の断面図である。

【図4B】図2における半導体素子を製造する段階の断面図である。

【図5】一実施例における半導体素子の一部範囲の元素の濃度と深さとの関係図である。

【図6】他の実施例における半導体素子の断面図である。

【図7】他の実施例における半導体素子の断面図である。

【図8】一実施例における半導体素子のパッケージ構造図である。

20

#### 【発明を実施するための形態】

##### 【0007】

以下、幾つかの実施例を説明することにより、当業者が本発明をより容易に理解し得るようにする。なお、これらの実施例は、例示に過ぎず、本発明を限定するものでない。また、当業者は、ニーズに応じて、以下に記載の実施例を調整しても良く、例えば、プロセスの順序を変更し、及び／又は、幾つかのステップを増減しても良い。

##### 【0008】

また、以下に述べる実施例をもとに、他の素子又はステップを増設しても良い。例を挙げて言えば、「第一層／構造に第二層／構造を形成する」というような記載は、第一層／構造が第二層／構造に直接接觸する実施例を含む可能性があり、第一層／構造と第二層／構造との間に他の素子を有することで、第一層／構造が第二層／構造に直接接觸しない実施例を含む可能性があり、第一層／構造と第二層／構造との空間上での相対的関係は、装置の異なる方位での操作又は使用によって変わることもある。また、本発明は、異なる実施例において参照符号としての数字及び／又は字母を重複して使用することがあり、このような重複使用は、簡略化及び明確化するためであり、異なる実施例間の関係を表すためでない。さらに、本明細書では、「実質的にX材料からなる」層というような表現は、該層の主な組成がX材料であることを表すが、ドーパントや不可避不純物も含むことを排除しない。

30

##### 【0009】

本発明の実施例では、特別な説明がない限り、化学式が「定比化合物 (stoichiometric compound)」及び「非定比化合物 (non-stoichiometric compound)」を含んでも良く、そのうち、「定比化合物」は、例えば、第3族元素の総量が第5族元素の総量と同じであることを指し、「非定比化合物」は、例えば、第3族元素の総量が第5族元素の総量とは異なることを指す。例を挙げて言えば、化学式が AlGaAs であることは、第3族元素 Al 及び／又は Ga を含み、また、第5族元素 As も含むことを表し、そのうち、第3族元素 (Al 及び／又は Ga) の総量は、第5族元素 (As) の総量と同じであっても良く、異なっても良い。

40

##### 【0010】

また、化学式で示す各化合物が定比化合物であるときに、AlGaAs は、 $\text{Al}_{x_1}\text{Ga}_{(1-x_1)}\text{As}$  を表し、そのうち、 $0 < x_1 < 1$  であり、AlInP は、 $\text{Al}_{x_2}\text{In}_{(1-x_2)}\text{P}$  を表し、そのうち、 $0 < x_2 < 1$  であり、AlGaInP は、 $(\text{Al}_{y_1}\text{Ga}_{(1-y_1)})_{1-x_3}\text{In}_{x_3}\text{P}$  を表し、そのうち、 $0 < x_3 < 1$  であり、且つ  $0 < y_1 < 1$  であり、AlGaInAs は、 $(\text{Al}_{y_2}\text{Ga}_{(1-y_2)})_{1-x_4}\text{In}_{x_4}\text{As}$  を表し、そのうち

50

、 $0 < x_4 < 1$ であり、且つ $0 < y_2 < 1$ であり、AlGaNは、 $Al_{x_5}Ga_{(1-x_5)}N$ を表し、そのうち、 $0 < x_5 < 1$ であり、AlAsSbは、 $AlAs_{x_6}Sb_{(1-x_6)}$ を表し、そのうち、 $0 < x_6 < 1$ であり、InGaPは、 $In_{x_7}Ga_{1-x_7}P$ を表し、そのうち、 $0 < x_7 < 1$ であり、InGaAsPは、 $In_{x_8}Ga_{1-x_8}As_{1-y_3}Py_3$ を表し、そのうち、 $0 < x_8 < 1$ であり、且つ $0 < y_3 < 1$ であり、InGaAsNは、 $In_{x_9}Ga_{1-x_9}As_{1-y_4}Ny_4$ を表し、そのうち、 $0 < x_9 < 1$ であり、且つ $0 < y_4 < 1$ であり、AlGaAsPは、 $Al_{x_{10}}Ga_{1-x_{10}}As_{1-y_5}Py_5$ を表し、そのうち、 $0 < x_{10} < 1$ であり、且つ $0 < y_5 < 1$ であり、InGaAsは、 $In_{x_{11}}Ga_{1-x_{11}}As$ を表し、そのうち、 $0 < x_{11} < 1$ である。

### 【0011】

説明の便宜のため、以下、4つ1組の（即ち、4つの元素からなる）発光ダイオードを例として本発明を説明するが、本発明は、これに限定されない。本発明は、他の種類の半導体素子、例えば、2つ1組（2つの元素からなる）、3つ1組の（3つの元素からなる）発光ダイオード又は他の半導体素子に応用することもでき、また、半導体素子の2つの電極は、それぞれ、半導体素子の両側に位置しても良く、半導体素子の同じ側に位置しても良い。なお、ここでは、前記「4つ1組」（即ち、四元）、「3つ1組」（即ち、三元）、及び「2つ1組」（即ち、二元）は、それぞれ、発光ダイオードの半導体スタック層が4種類、3種類、及び2種類の元素からなる化合物を含むことを意味する。

### 【0012】

以下、本発明の幾つかの実施例に基づいて半導体素子を説明し、それは、特に、近赤外線(near-infrared ray、NIR)を発する発光素子に適用される。本実施例では、半導体素子が提供され、該半導体素子が発光ダイオードであるときに、出光面に近い接触層及び／又はウインドウ層は、光を吸収しない材料（以下、光不吸収材料という）を用いる。この光不吸収材料の吸収波長は、アクティブ構造の発光波長とは異なるので、アクティブ構造が発する光を吸収せず、発光効率を向上させることができる。また、その後のプロセスにおいて追加のステップで接触層を除去する必要がないため、製造ステップを減少させることができる。また、接触層及び／又はウインドウ層に対して粗化プロセスを行うことで、半導体素子の輝度を更に向上させることができる。幾つかの実施例では、アクティブ構造の材料は、4つ1組の化合物半導体、例えば、AlInGaAs又はInGaAsPを含んでも良く、光不吸収材料は、2つ1組の化合物半導体、例えば、GaAs又はInPを含んでも良い。もう1つの実施例では、アクティブ構造は、AlInGaAsであり、又は、実質的にAlInGaAsからなり、光不吸収材料は、実質的にGaAs又はInPからなり、また、他の実施例では、アクティブ構造は、InGaAsPであり、又は、実質的にInGaAsPからなり、光不吸収材料は、実質的にGaAs又はInPからなる。

### 【0013】

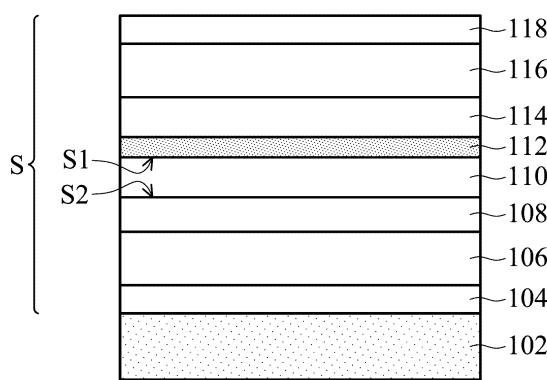

第1図は、一実施例における半導体素子100の断面図である。半導体素子100は、ベース102及びベース102に位置する半導体スタック層Sを含む。半導体スタック層Sは、第一接触層104、第一ウインドウ層106、緩衝層108、第一型半導体構造110、アクティブ構造112、第二型半導体構造114、第二ウインドウ層116、及び第二接触層118を含む。

### 【0014】

幾つかの実施例では、半導体スタック層Sは、エピタキシャル方法でベース102に成長し又は接続することができ、即ち、ベース102は、成長基板又は非成長基板であっても良い。ベース102は、その上の半導体スタック層S及び他の層又は構造を支持するために用いられ、ベース102は、アクティブ構造112が発する光に対して透明、半透明、又は不透明であっても良く、また、導体、半導体、又は絶縁体であっても良い。本実施例では、半導体素子100は、垂直型形態であるので、ベース102は、導電材料であり、且つ金属材料、金属合金材料、金属酸化物材料、半導体材料、又は炭素含有材料を含む。金属材料は、Cu、Al、Cr、Sn、Au、Ni、Ti、Pt、Pb、Zn、Cd、Sb、又はCoを含み、金属合金材料は、これらの金属材料を含む合金であり、半導体材料は、IV族半導体又はIII-V族半導体、例えば、Si、Ge、SiC、GaN、GaP、GaAs、AsGaP、InPなどを含んでも良いが、これに限られず、金属酸化物材料は、ITO、InO、SnO、CTO、ATO、AZO、ZTO、GZO、IWO、ZnO、又はIZOを含んでも良いが、これに限定されず、炭素含有材料は、DLC(Diamond-Like

10

20

30

40

50

carbon)又はグラフェン(Graphene)を含んでも良いが、これに限定されない。もう1つの実施例では、半導体素子100が非垂直型形態であるときに、ベース102は、絶縁材料、例えば、サファイア(sapphire)、グラス(glass)、絶縁窒化物(例えば、SiN)、絶縁酸化物(例えば、SiO<sub>2</sub>)などを含んでも良い。本実施例では、半導体素子は、近赤外線発光素子であり、ベース102の材料は、InP又はGaAsを含み、例えば、ベース102の材料は、InP又はGaAsであり、或いは、実質的にInP又はGaAsからなる。

#### 【0015】

幾つかの実施例では、第二接触層118、第二ウィンドウ層116、第二型半導体構造114、アクティブ構造112、第一型半導体構造110、緩衝層108、第一ウィンドウ層106、及び第一接触層104の形成は、エピタキシャル方法により、順に、ベース102又は成長基板(図示せず)に成長することができ、エピタキシャル方法は、MOCVD(Metal Organic Chemical Vapor Deposition)、MBE(Molecular Beam Epitaxy)、HVPE(Hydride Vapor Phase Epitaxy)、類似する方法、又はこれらの組み合わせを含む。10

#### 【0016】

幾つかの実施例では、第一接触層104、第一ウィンドウ層106、第一型半導体構造110、アクティブ構造112、第二型半導体構造114、第二ウィンドウ層116、及び第二接触層118の材料は各自、独立して第3、第5族(「III-V族」ともいう)化合物半導体材料を含んでも良く、例えば、AlGaInAs、AlGaAs、AlInAs、GaInAs、AlAs、GaAs、InAs、AlGaInP、AlGaP、AlInP、GaInP、AlP、GaP、InP、AlInGaN、AlInN、AlGaN、InGaN、AlAsSb、AlSb、AsSb、InGaAsP、InAsP、GaAsP、InGaAsN、InAsN、GaAsN、InN、AlGaAsP、AlAsP、又は類似する第3、第5族化合物半導体材料を含んでも良い。20

#### 【0017】

第1図に示すように、アクティブ構造112は、第一型半導体構造110と第二型半導体構造114との間に位置する。本発明による半導体素子100が発光素子であるときに、第一型半導体構造110及び第二型半導体構造114は、例えば、クラッド層(cladding layer)及び/又は閉じ込め層(confinement layer)であり、それぞれ、電子及び正孔を提供し、且つ活性層よりも大きいエネルギーギャップを有し、これにより、電子及び正孔がアクティブ構造112中で結合して発光する確率を向上させることができる。アクティブ構造112は、放射線を発することができる。例を挙げて言えば、近赤外線発光素子について、該放射線は、1000 nm ~ 2000 nmの間にあるピーク波長(peak wavelength)を有し、好ましくは、1200 nm ~ 1800 nmの間にあるピーク波長、例えば、1250 nm ~ 1650 nmを有する。30

#### 【0018】

半導体素子100は、SH(single heterostructure)、DH(double heterostructure)、DDH(double-side double heterostructure)、又はMQW(multiple quantum wells)構造を含んでも良い。幾つかの実施例では、アクティブ構造112は、MQW構造であり、それは、交互にスタックされる複数のバリア層(barrier layer)及び複数の井戸層(well layer)を含み、バリア層は、井戸層よりも高いエネルギーギャップを有する。幾つかの実施例では、バリア層及び井戸層は各自、独立して4つ1組の材料又は3つ1組の材料を含んでも良い。幾つかの実施例では、アクティブ構造112は、Al、Ga、In、P、又はAsを含んでも良く、好ましくは、Nが含まれない4つ1組の化合物、例えば、AlGaInAs、InGaAsPである。40

#### 【0019】

第1図に示すように、第一型半導体構造110及び第二型半導体構造114は、それぞれ、アクティブ構造112の両側に位置し、第一型半導体構造110及び第二型半導体構造114は、単層又は複数層であっても良く、且つエネルギーギャップがアクティブ構造112よりも大きく、キャリア(carrier)をアクティブ構造112に閉じ込め、且つアクティブ構造112のキャリアオーバーフローを有效地に防止し、及び/又は、それぞれ、電子及び正孔をアクティブ構造112に提供するために用いられる。幾つかの実施例では、第一型半導体構造110及び第二型半導体構造114は、第3、第5族半導体材料を含んでも良く、好適な例は、前述

10

20

30

40

50

の通りであるため、ここでは、その詳しい説明を省略する。幾つかの実施例では、第一型半導体構造110及び第二型半導体構造114は、好ましくは、Al、Ga、As、P、In、又はこれらの組み合わせを含み、且つ好ましくは、Nが含まれない3つ1組又は2つ1組の化合物、例えば、InAlAs又はInPである。

#### 【0020】

幾つかの実施例では、第一型半導体構造110は、第一導電型を有し、第二型半導体構造114は、第二導電型を有し、そのうち、第一導電型は、第二導電型とは異なる。例を挙げて言えば、第一導電型及び第二導電型は、それぞれ、P型及びN型であっても良く、或いは、それぞれ、N型及びP型であっても良い。第一型半導体構造110及び第二型半導体構造114は、例えれば、異なるドーパント(dopant)を添加することで異なる導電型を有し、例えれば、第一型半導体構造110は、第一ドーパントを有し、第二型半導体構造114は、第一型半導体構造110の第一ドーパントとは異なる第二ドーパントを有する。具体的に言えば、これらのドーパントは、Mg、Zn、Si、Teなどを含んでも良い。幾つかの実施例では、エピタキシャル成長期間内でイン・サイチュ(in-situ)ドーピングを行うこと、及び/又は、エピタキシャル成長後にP型又はN型ドーパントを用いて植え込み(implanting)プロセスを実行することにより、第一型半導体構造110及び第二型半導体構造114のドーピングを行うことができる。例を挙げて言えば、本実施例では、第一型半導体構造110のドーパントがZnであり、且つ第二型半導体構造114のドーパントは、Siである。

10

#### 【0021】

一実施例では、第一型半導体構造110中のドーパントのドーピング濃度及び第二型半導体構造114中のドーパントのドーピング濃度は各自、独立して $1 \times 10^{16} / \text{cm}^3 \sim 5 \times 10^{18} / \text{cm}^3$ の範囲にあっても良い。一実施例では、第一型半導体構造110中のドーパントのドーピング濃度は、第二型半導体構造114中のドーパントのドーピング濃度よりも大きくても良い。例を挙げて言えば、第一型半導体構造110中のドーパントのドーピング濃度は、 $1 \times 10^{17} / \text{cm}^3 \sim 1 \times 10^{18} / \text{cm}^3$ であり、好ましくは、 $3 \times 10^{17} / \text{cm}^3 \sim 8 \times 10^{17} / \text{cm}^3$ であり、第二型半導体構造114中のドーパントのドーピング濃度は、 $3 \times 10^{16} / \text{cm}^3 \sim 1 \times 10^{18} / \text{cm}^3$ であり、好ましくは、 $5 \times 10^{16} / \text{cm}^3 \sim 9 \times 10^{17} / \text{cm}^3$ である。幾つかの実施例では、第一型半導体構造110の厚さ及び第二型半導体構造114の厚さは各自、独立して $100 \text{ nm} \sim 1200 \text{ nm}$ の範囲にあっても良く、例えば、ともに $200 \text{ nm} \sim 1000 \text{ nm}$ の範囲にある。

20

#### 【0022】

本発明の実施例の記載は、第一接触層104及び第一ウィンドウ層106が同じ光不吸收材料を含み、且つ光不吸收材料がGaAsであり、第一型半導体構造110、アクティブ構造112、第二型半導体構造114、第二ウィンドウ層116、及び第二接触層118は各自、独立して任意の適切な材料を含んでも良いケースを例とするが、本発明は、これに限定されない。もう1つの実施例では、第一接触層104及び第一ウィンドウ層106は各自、独立して異なる光不吸收材料を含んでも良く、例えば、それぞれ、GaAs及びInPである。また、第二接触層118及び第二ウィンドウ層116は、同じ又は異なる光不吸收材料を含んでも良く、第一接触層104及び第一ウィンドウ層106は各自、独立して任意の適切な材料を含んでも良い。或いは、他の実施例では、第一接触層104、第一ウィンドウ層106、第二接触層118、及び第二ウィンドウ層116は、光不吸收材料を含み、これらの光不吸收材料は、同じであっても良く、異なっても良い。

30

#### 【0023】

第1図に示すように、半導体素子100は、第一型半導体構造110の上方に位置する第一接触層104を、第一型半導体構造110が第一接触層104とベース102との間に位置するよう含む。具体的に言えば、第一型半導体構造110は、第一側S1及び第一側S1に相対する第二側S2を含み、第二側S2は、第一側S1に比べてベース102から離れる。アクティブ構造112は、第一側S1に設置され、第一接触層104は、第二側S2に設置される。第一接触層104のエネルギー・ギャップは、アクティブ構造112及び第一型半導体構造110のエネルギー・ギャップよりも大きく、これにより、第一接触層104が光を吸収することによる半導体素

40

50

子100の効率低下を避けることができる。一実施例では、第一接触層104のエネルギーギヤップとアクティブ構造112のエネルギーギヤップとの差は、0.3eV～0.8eVであり、好みしくは、0.4eV～0.7eVである。

#### 【0024】

また、第一型半導体構造110は、第一格子定数(lattice constant)を有し、第一接触層104は、第二格子定数を有し、そのうち、第一格子定数は、第二格子定数とは異なり、即ち、第一型半導体構造110と第一接触層104は、格子不整合(lattice mismatch)である。第一型半導体構造11が単層からなるときに、該単層の格子定数が第一格子定数として定義される。第一型半導体構造11が複数層からなるときに、これらの複数層の格子定数の平均値(算術平均)が第一格子定数として定義される。幾つかの実施例では、第二格子定数と第一格子定数との間の差は、少なくとも0.5%であり、例えば、1%～6%の範囲にあり、好みしくは、2%～5%であり、より好みしくは、3%～4.5%である。上述の第二格子定数と第一格子定数との差D1は、以下の式(1)により計算され、そのうち、d1は、第一格子定数を表し、d2は、第二格子定数を表す。

10

#### 【0025】

$$\text{差D1} = ((d2 - d1) / d2) \times 100\% \dots \text{式(1)}$$

本実施例では、第一型半導体構造110の材料は、In<sub>0.53</sub>Al<sub>0.47</sub>Asであり、又は、実質的にIn<sub>0.53</sub>Al<sub>0.47</sub>Asからなり、第一格子定数は、5.848であり、第一接触層104の材料は、GaAsであり、又は、実質的にGaAsからなり、第二格子定数は、5.653であり、第二格子定数と第一格子定数との間の差は、3.45%である。また、任意の適切な方式で格子定数を得ても良い。例を挙げて言えば、TEM(transmission electron microscopy)による回折パターン(diffraction pattern)を用いて、第一型半導体構造110及び第一接触層104の格子定数を解析しても良く、或いは、格子定数情報は、温度300kでXRD(X-線回折)により取得しても良い。本発明の内容では、「格子定数」が、ひずみが実質的に無い(unstrained)層の格子定数a<sub>0</sub>と定義されている。

20

#### 【0026】

一実施例では、第一接触層104の厚さは、5nm～100nmの範囲にあっても良く、例えば、50nmである。また、第一接触層104の表面は、選択的に粗化構造を有しても良く、これにより、アクティブ構造112が発する光が半導体スタック層S中で全反射を行う確率を減少させ、光取り出し効率(light extraction efficiency)を向上させ、半導体素子100の輝度をより一層向上させることができる。

30

#### 【0027】

第1図に示すように、第一ウインドウ層106は、第一接触層104と第一型半導体構造110との間に設けられる。第一ウインドウ層106は、半導体素子100の光取り出し効率を増大し、及び/又は、電流を半導体スタック層Sに均一に分散させるために用いられる。一実施例では、第一ウインドウ層106及び第一接触層104は、同じ材料であり、即ち、第一ウインドウ層106及び第一接触層104は、同じ格子定数を有し(ともに第二格子定数を有する)、且つ第一型半導体構造110の第一格子定数との差は、少なくとも0.5%であり、例えば、第一接触層104及び第一ウインドウ層106の材料は、ともに、GaAsであり、又は、実質的にGaAsからなる。もう1つの実施例では、第一接触層104及び第一ウインドウ層106は、異なる材料を有し、第一ウインドウ層106は、第一格子定数との差が0.5%よりも小さい格子定数を有しても良い。他の実施例では、第一ウインドウ層106の材料は、ベース102の材料と同じであっても良く、例えば、第一接触層104は、GaAsであり、又は、実質的にGaAsからなり、第一ウインドウ層106及びベース102は、ともに、InPであり、又は、実質的にInPからなる。

40

#### 【0028】

また、第一接触層104及び第一ウインドウ層106の導電型は、第一型半導体構造110の導電型と同じであっても良い。例を挙げて言えば、第一接触層104、第一ウインドウ層106、及び第一型半導体構造110の導電型は、ともにP型であり、第一接触層104、第一ウインドウ層106、及び第一型半導体構造110には、ともに同じドーパント、例えばZnを有す

50

る。第一接触層104及び第一ウインドウ層106のドーピングは、エピタキシャル成長期間内でイン・サイチュ(in-situ)ドーピングを行うこと、及び／又は、エピタキシャル成長後にドーパントを用いて植え込み(implanting)を行うことにより行われる。第一接触層104中のドーパントのドーピング濃度は、第一型半導体構造110のドーピング濃度よりも大きく、且つ $1 \times 10^{18} / \text{cm}^3$ よりも大きく、これにより、第一接触層104と、その上の電極構造との間に比較的低い抵抗値を持たせることができ、好ましくは、第一接触層104のドーパントのドーピング濃度は、例えば、 $2 \times 10^{18} / \text{cm}^3 \sim 5 \times 10^{19} / \text{cm}^3$ の範囲にある。第一ウインドウ層106は、第一型半導体構造110よりも厚い厚さ、又は／及び、比較的低いドーピング濃度を有し、これにより、光取り出し率を増大し、又は、横向き電流分散能力を向上させることができる。

10

#### 【0029】

第一接触層104中のドーパントのドーピング濃度は、第一ウインドウ層106中のドーパントのドーピング濃度とは異なる。幾つかの実施例では、第一ウインドウ層106中のドーパントのドーピング濃度は、第一接触層104中のドーパントのドーピング濃度よりも小さい。一実施例では、第一ウインドウ層106中のドーパントのドーピング濃度は、 $2 \times 10^{16} / \text{cm}^3 \sim 1 \times 10^{19} / \text{cm}^3$ の範囲にあっても良く、例えば、 $4 \times 10^{16} / \text{cm}^3 \sim 8 \times 10^{18} / \text{cm}^3$ である。

#### 【0030】

幾つかの実施例では、第一ウインドウ層106の厚さは、第一接触層104の厚さより大きくて良い。一実施例では、第一ウインドウ層106の厚さは、 $300 \text{ nm} \sim 10000 \text{ nm}$ の範囲にあっても良く、好ましくは、 $500 \text{ nm} \sim 8000 \text{ nm}$ の範囲にあり、本実施例では、例えば $7000 \text{ nm}$ である。

20

#### 【0031】

第1図に示すように、緩衝層108は、第一ウインドウ層106と第一型半導体構造110との間に、第一型半導体構造110と第一ウインドウ層106との間のエネルギーレベル差を軽減するために設置される。具体的に言えば、第一ウインドウ層106の価電子帯エネルギーレベルと、第一型半導体構造110の価電子帯エネルギーレベルとの間には、価電子帯エネルギーギャップ(valence band energy、Ev)差があり、第一ウインドウ層106の伝導帯エネルギーレベルと、第一型半導体構造110の伝導帯エネルギーレベルとの間には、伝導帯エネルギーギャップ(conduction band energy、Ec)差があり、価電子帯エネルギーギャップ差及び／又は伝導帯エネルギーギャップ差が大き過ぎるときに、追加の電圧差を提供してキャリアを伝送する必要があり、これにより、半導体素子に高順方向電圧差(forward voltage、Vf)が生じやすくなり、半導体素子の飽和電流低下又は早期失効などの問題を来すことがある。よって、第一ウインドウ層106と第一型半導体構造110との間に緩衝層108を設置することで、このような問題を避けることができる。緩衝層108は、第一型半導体構造110の価電子帯エネルギーレベルと第一ウインドウ層106の価電子帯エネルギーレベルとの間にある価電子帯エネルギーレベルを有し、緩衝層108は、第一型半導体構造110の伝導帯エネルギーレベルと第一接触層104の伝導帯エネルギーレベルとの間にある伝導帯エネルギーレベルを有し、これにより、第一型半導体構造110と第一ウインドウ層106との間のエネルギーレベル差を緩和し、半導体素子100の信頼度を向上させることができる。もう1つの実施例では、第一ウインドウ層106は、選択的に設置されても良く、半導体素子100が第一ウインドウ層106を含まないときに、緩衝層108は、第一接触層104と第一型半導体構造110との間に設置し、且つ第一接触層104及び第一型半導体構造110に直接接觸することができる。前述のように、緩衝層108は、第一接触層104と第一型半導体構造110との間のエネルギーレベル差を軽減することができる。

30

#### 【0032】

幾つかの実施例では、緩衝層108の材料は、4つ1組の半導体化合物、例えば、AlGaInAs又はInGaAsPを含んでも良い。第一接触層104がGaAsであり、又は、実質的にGaAsからなり、且つ第一型半導体構造110がInAlAsであり、又は、実質的にInAlAsからなるときに、緩衝層108の材料は、 $(\text{Al}_x\text{Ga}_{1-x})_{0.47}\text{In}_{0.53}\text{As}$  ( $0 < x < 1$ ) であり、又は、実質的

40

50

に $(Al_xGa_{1-x})_{0.47}In_{0.53}As$  ( $0 < x < 1$ ) からなる。もう1つの実施例では、第一接触層104がGaAsであり、又は、実質的にGaAsからなり、且つ第一型半導体構造110がInPであり、又は、実質的にInPからなるときに、緩衝層108の材料は、InGaAsPであり、又は、実質的にInGaAsPからなる。

#### 【0033】

緩衝層108が第一型半導体構造110と、第一ウィンドウ層106(又は、第一接触層104)との間に位置するときに、緩衝層108は、第一型半導体構造110及び第一ウィンドウ層106(又は、第一接触層104)と同じ導電型を有し、三者は、同じドーパントを含んでも良い。一実施例では、緩衝層108中のドーパントのドーピング濃度は、 $5 \times 10^{16} / cm^3 \sim 2 \times 10^{18} / cm^3$  の範囲にあっても良く、例えば、 $5 \times 10^{17} / cm^3 \sim 1 \times 10^{18} / cm^3$  である。また、緩衝層108の厚さは、10nm～200nmの範囲にあっても良く、例えば、100nmである。

10

#### 【0034】

緩衝層108は、オプション(optional)であり、幾つかの実施例では、緩衝層108を設置してなくても良く、即ち、第一ウィンドウ層106は、第一型半導体構造110に直接接触する。また、実際の製品の特性に応じて緩衝層108の位置及び数量を調整しても良い。他の幾つかの実施例では、2層以上の緩衝層を設置しても良く、これらの緩衝層は、同じ又は異なる材料及び/又はドーピング濃度を有しても良い。例を挙げて言えば、幾つかの実施例では、第二型半導体構造114と第二ウィンドウ層116との間に追加の緩衝層(図示せず)を設置しても良い。

#### 【0035】

第1図に示すように、第二ウィンドウ層116は、第二型半導体構造114とベース102との間に設けられ、第二ウィンドウ層116は、第一型半導体構造110の第二側S2から離れる。幾つかの実施例では、第二ウィンドウ層116の材料は、第3、第5族半導体材料を含んでも良い。幾つかの実施例では、第二ウィンドウ層116の材料は、透明導電材料を含んでも良い。例を挙げて言えば、第二ウィンドウ層116の材料は、金属酸化物材料又は半導体材料を含んでも良いが、これに限定されない。金属酸化物は、ITO、InO(indium oxide)、SnO(tin oxide)、CTO(chromium titanium oxide)、ATO(antimony tin oxide)、AZO(aluminum-doped zinc oxide)、ZTO(zinc tin oxide)、GZO(gallium doped zinc oxide)、IWO(indium tungsten oxide)、ZnO、MgO(magnesium oxide)、又はIZOを含んでも良いが、これに限られない。半導体材料は、InP、GaAs、AlGaAs、GaPなどを含んでも良いが、これに限定されない。第一ウィンドウ層106の材料は、第二ウィンドウ層116の材料を参照することができる。一実施例では、第二ウィンドウ層116の材料は、第一ウィンドウ層106の材料と同じであり、例えば、すべては、InPであり、又は、実質的にInPからなる。他の実施例では、第二ウィンドウ層116の材料は、第一ウィンドウ層106の材料とは異なり、それぞれは、InP及びGaAsであり、或いは、それぞれは、実質的にInP及びGaAsからなる。

20

#### 【0036】

第二ウィンドウ層116は、第一接触層104の第二格子定数とは異なる第三格子定数を有する。幾つかの実施例では、第三格子定数と第二格子定数との間の差は、少なくとも0.5%であり、例えば、1%～6%の範囲にあり、好ましくは、2%～5%であり、より好ましくは、3%～4.5%である。前述のように、任意の適切な方式で第二ウィンドウ層116の第三格子定数を解析することができる。幾つかの実施例では、第三格子定数と第一格子定数との間の差は、0.5%以下であり、また、もう1つの実施例では、第三格子定数と第一格子定数との差は、0.2%よりも小さく且つ0よりも大きい。上述の第三格子定数と第一格子定数との差D2は、以下の式(2)で計算され、そのうち、d1は、第一格子定数を表し、d3は、第三格子定数を表す。

30

#### 【0037】

$$\text{差D2} = ((d3 - d1) / d3) \times 100\% \dots \text{式(2)}$$

一実施例では、第二ウィンドウ層116中のドーパントのドーピング濃度は、 $1 \times 10^{16} / cm^3$  よりも大きくても良く、例えば、 $2 \times 10^{16} / cm^3 \sim 1 \times 10^{18} / cm^3$  の範囲にある。幾

40

50

つかの実施例では、第二ウィンドウ層116の厚さは、第一ウィンドウ層106の厚さよりも小さくても良い。もう1つの実施例では、第二ウィンドウ層116の厚さは、第二型半導体構造114の厚さよりも大きく、或いは、第二ウィンドウ層116は、第二型半導体構造114に比べて、比較的低いドーピング濃度を有し、これにより、光取り出し率を増大し、又は、横向き電流分散能力を向上させることができる。幾つかの実施例では、第二ウィンドウ層116の厚さは、100 nm ~ 1000 nmの範囲にあっても良く、例えば、500 nmである。

#### 【0038】

第1図に示すように、第二ウィンドウ層116とベース102との間には、選択的に第二接触層118を設置しても良く、第二接触層118は、第一型半導体構造110の第二側S2から離れる。第二接触層118の材料は、第3、第5族半導体材料を含んでも良く、好適な例は、前述の通りであるため、ここでは、その詳しい説明を省略する。第二接触層118及び第二ウィンドウ層116の導電型は、第二型半導体構造114の導電型と同じである。例を挙げて言えば、第二接触層118、第二ウィンドウ層116、及び第二型半導体構造114の導電型はともにN型であり、第二接触層118、第二ウィンドウ層116、及び第二型半導体構造114はともに同じドーパント、例えば、Siを含む。第二接触層118中のドーパントのドーピング濃度は、第二ウィンドウ層116中のドーパントのドーピング濃度とは異なる。幾つかの実施例では、第二接触層118中のドーパントのドーピング濃度は、第二ウィンドウ層116中のドーパントのドーピング濃度よりも大きい。一実施例では、第二接触層118中のドーパントのドーピング濃度は、 $5 \times 10^{17} / \text{cm}^3$ よりも大きくて良く、これにより、第二接触層118とベース102との間は、比較的低い抵抗値を有し、例えば、第二接触層118のドーパントのドーピング濃度は、 $1 \times 10^{18} / \text{cm}^3 \sim 1 \times 10^{20} / \text{cm}^3$ の範囲にある。

10

#### 【0039】

半導体素子100は、それぞれ半導体素子100の相対する両側に位置する第一電極122及び第二電極120を含む。例えば、本実施例では、第一接触層104は、第一型半導体構造110と第一電極122との間に位置し、ベース102は、第二電極120と第二型半導体構造114との間に位置し、これにより、垂直型半導体素子100を形成する。なお、本発明は、これに限定されず、他の幾つかの実施例では、第一電極122及び第二電極120は、ベース102の同じ側に位置することで、水平型半導体素子を形成しても良い。一実施例では、第一接触層104は、第一型半導体構造110と第一電極122との間に形成され、且つ第一電極122の位置にのみ対応する。

20

#### 【0040】

第一電極122及び第二電極120は、すべて、外部電源に接続されて電流を半導体素子100に導入するために用いられる。幾つかの実施例では、第一電極122の材料及び第二電極120の材料は各自、独立して金属材料、合金材料、金属酸化物材料、又は炭素含有材料を含んでも良い。例を挙げて言えば、金属材料は、Al、Cr、Cu、Sn、Au、Ni、Ti、Pt、Pb、Zn、Cd、Sb、又はCoを含んでも良いが、これに限定されず、合金材料は、これらの金属を組み合わせた合金を含み、金属酸化物材料は、ITO、InO、SnO、CTO、ATO、AZO、ZTO、GZO、IWO、ZnO、又はIZOを含んでも良いが、これに限定されない。炭素含有材料は、DLC又はグラフェンを含んでも良いが、これに限られない。

30

#### 【0041】

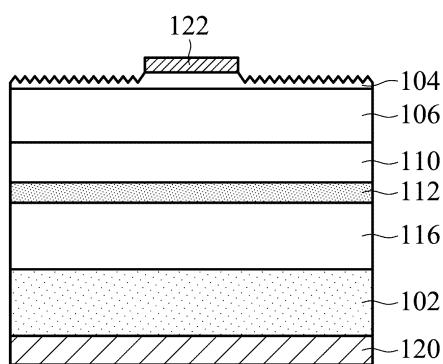

第2図は、一実施例における半導体素子200の断面図であり、第3図は、一実施例における半導体素子200の上面図である。第2図は、第3図のAA'線に沿った断面図に相当する。第2図では、第1図と同じ符号で同じ素子を示し、また、これらの素子の材料及び特性は、前述と同様であるため、ここでは、その詳しい説明を省略する。本実施例の半導体素子200は、第1図に示す半導体素子100に比べて、1回のチップ接続プロセスを経つから、半導体スタック層Sの順序は、第1図とは逆であり、第一型半導体構造110は、ベース102とアクティブ構造112との間に位置する。さらに、接続プロセス後に、第二接触層118及び第二ウィンドウ層116は、アクティブ構造112が発する光の進行経路に位置するので、第二接触層118及び第二ウィンドウ層116は、光不吸収材料を使用することで、第二接触層118及び第二ウィンドウ層116のエネルギーギャップを、それぞれ、アクティブ構造112の

40

50

エネルギー・ギヤップよりも大きくすることができ、例えば、光不吸收材料は、InPを使用する。なお、チップ接続プロセスについては、後述する。

#### 【0042】

第1図の半導体素子100に比べて、半導体素子200は、ベース102、半導体スタック層S、第一電極122、及び第二電極120の他に、反射構造130、導電構造140、及びベース102と半導体スタック層Sとの間に位置する接続層124を更に含む。また、本実施例では、第一接触層104は、選択的に省略されても良く、また、第二接触層118、第二ウィンドウ層116、及び第二型半導体構造114の格子定数、エネルギー・ギヤップ差、ドーピング濃度、厚さなどの特性は、それぞれ、第1図に示す第一接触層104、第一ウィンドウ層106、及び第一型半導体構造110の関係を参照することもできる。本実施例では、第2～3図に示すように、第二電極122は、半導体スタック層Sの上表面のほぼ中心位置に位置する電極パッド1221、及び、電極パッド1221に接続され且つ電極パッド1221を離れる方向へ延伸する複数の延伸電極1222を含み、延伸電極1222は、電流を半導体スタック層Sに均一に拡散させるために用いられる。10

#### 【0043】

具体的に言えば、半導体素子200は、反射構造130とベース102との間に位置する接続層124を含み、これにより、反射構造130とベース102とを接続することができる。幾つかの実施例では、接続層124は、複数の従属層(図示せず)を含んでも良く、接続層124の材料は、導電材料、例えば、金属酸化物材料、半導体材料、金属材料、金属合金材料、又は炭素含有材料を含んでも良い。例を挙げて言えば、金属酸化物は、ITO、InO、SnO、CTO、ATO、AZO、ZTO、GZO、ZnO、ICO(indium cerium oxide)、IWO、ITiO(indium titanium oxide)、IZO、IGO(indium gallium oxide)、又はGAZO(gallium and aluminum codoped zinc oxide)を含んでも良いが、これに限定されない。半導体材料は、GaPを含んでも良いが、これに限られない。金属材料は、Cu、Al、Sn、Au、Ag、Pb、Ti、Ni、Pt、又はWを含んでも良いが、これに限定されない。金属合金材料は、これらの金属材料を含む合金である。炭素含有材料は、グラフェン(Graphene)を含んでも良いが、これに限定されない。20

#### 【0044】

反射構造130は、ベース102と半導体スタック層Sとの間に設置され、アクティブ構造112が発する光を反射し、半導体素子200の光取り出し効率(Light Extraction Efficiency、LEE)を増大するために用いられる。幾つかの実施例では、反射構造130の材料は、金属材料又は金属合金材料を含んでも良いが、これに限定されない。金属材料は、Cu、Al、Sn、Au、Ag、Pt、又はWを含んでも良いが、これに限られず、金属合金材料は、これらの金属材料を含む合金である。30

#### 【0045】

幾つかの実施例では、第2図に示すように、反射構造130は、第三接触層132、第三接觸層132の上に位置するバリア層134、バリア層134の上に位置する反射接続(接着)層136、及び反射接続層136の上に位置する反射層138を含んでも良い。第三接触層132は、下方の接続層124と低抵抗の接触を形成することができる。バリア層134は、接続層124の材料の、プロセス期間内での反射層138への拡散による反射層138の構造の破壊を防止することで、反射層138の反射率を維持することができる。反射接続層136は、反射層138とバリア層134とを接続するために用いられる。反射層138は、アクティブ構造112が発する光を反射することができる。なお、本発明は、これに限定されず、例えば、反射構造130は、より多くの構造を含んでも良く、また、第三接触層132、バリア層134、反射接続層136、及び反射層138の材料は各自、独立して同じ又は異なる金属材料又は金属合金材料を含んでも良い。金属材料は、Cu、Al、Sn、Au、Ag、Pb、Ti、Ni、Pt、又はWを含んでも良いが、これに限定されず、金属合金材料は、これらの金属材料を含む合金である。40

#### 【0046】

導電構造140は、反射構造130と第一接触層104との間に位置する。導電構造140は、50

アクティブ構造112が発する光に対して透明であり、第一接触層104と反射構造130との間の電流の伝導及び拡散を向上させるために用いられる。幾つかの実施例では、導電構造140は、反射構造130と共同でODR(Omni-Directional Reflector)を形成することで、半導体素子200の光取り出し効率(light extraction efficiency、LEE)を更に増大することができる。幾つかの実施例では、導電構造140の材料は、金属酸化物材料、炭素含有材料、又はこれらの材料の組み合わせを含んでも良い。金属酸化材料は、ITO、InO、SnO、CTO、ATO、AZO、ZTO、GZO、ZnO、ICO、IWO、ITiO、IZO、IGO、又はGAZOを含んでも良いが、これに限定されない。炭素含有材料は、グラフェンを含んでも良いが、これに限られない。

#### 【0047】

10

幾つかの実施例では、第2図に示すように、導電構造140は、反射構造130の上方に位置する第一導電層142、及び、半導体スタック層Sと第一導電層142との間に位置する第二導電層144を含む。幾つかの実施例では、第一導電層142の材料は、第二導電層144の材料と異なっても良い。具体的に言えば、第一導電層142の材料と第二導電層144の材料とは、少なくとも1つの元素が異なり、例えば、第一導電層142の材料は、IZOであり、第二導電層144の材料は、ITOである。

#### 【0048】

幾つかの実施例では、第2図に示すように、第二導電層144と第一接触層104との間には、絶縁層146が設置され、絶縁層146は、第二導電層144に直接接觸する。幾つかの実施例では、絶縁層146の材料は、アクティブ構造112が発する光に対しての透過率が90%よりも大きいものを選択しても良く、また、絶縁層146の材料は、酸化物絶縁材料又は非酸化物絶縁材料を含んでも良い。例を挙げて言えば、酸化物絶縁材料は、SiO<sub>x</sub>又は類似する材料を含んでも良く、非酸化物絶縁材料は、SiNx、BCB(benzocyclobutene)、COC(cyclo olefin copolymer)、又はフルオロカーボンポリマー(fluorocarbon polymer)を含んでも良い。他の幾つかの実施例では、絶縁層146の材料は、ハロゲン化物又はIIA族及びVII族の化合物、例えば、CaF<sub>2</sub>(calcium fluoride)又はMgF<sub>2</sub>(magnesium fluoride)を含んでも良く、一実施例では、絶縁層146の材料は、1.6よりも小さい屈折率を有する。

20

#### 【0049】

幾つかの実施例では、絶縁層146は、絶縁層146を貫通する複数の孔141を含むことで、導電構造140がこれらの孔141を経由して半導体スタック層Sに直接接觸して電気接続されるようにさせることができる。

30

#### 【0050】

幾つかの実施例では、第2図に示すように、第二接触層118及び/又は第二ウインドウ層116の頂面に対して粗化プロセスを行い、それに粗化表面を持たせることで、アクティブ構造112が発する光を散乱させ、半導体素子200の光取り出し効率を向上させることができる。

#### 【0051】

第4A～4B図は、一実施例における半導体素子を製造する各段階の断面図であり、チップ接続プロセスを説明するためのものである。この実施例では、ベース102が非成長基板である。第4A図に示すように、半導体スタック層Sは、成長基板101にエピタキシャル成長し、半導体スタック層Sと成長基板101との間には、選択的に犠牲層103が設置されても良く、また、第4B図に示す後続プロセスにおいて犠牲層103を除去することで、第一接触層104、第一ウインドウ層106、緩衝層108、第一型半導体構造110、アクティブ構造112、第二型半導体構造114、第二ウインドウ層116、及び第二接触層118が成長基板101を離脱するようにさせることができる。幾つかの実施例では、第二接触層118形成前に、成長基板101に犠牲層103を形成しても良い。幾つかの実施例では、半導体素子は、犠牲層103を有せず、第二接触層118を成長基板101に直接形成しても良い。他の幾つかの実施例では、第二接触層118と成長基板101との間には、更に緩衝構造(図示せず)を設けることで、第二接触層118及びその上の各層の格子欠陥を減少させ、半導体スタック層Sの

40

50

エピタキシャル品質を向上させても良い。他の実施例では、半導体素子は、犠牲層103を有しないが、成長基板101と第二接觸層118との間に位置するエッティング停止層(図示せず)を含み、その後、エッティングにより成長基板101をエッティングして除去するときに、エッティング停止層は、半導体スタック層Sを保護する機能を有し、これにより、半導体スタック層Sのエッティングプロセスにおける破壊を避けることができ、例えば、エッティング停止層の材料は、InGaAs又はInGaPであり、或いは、実質的にInGaAs又はInGaPからなる。

#### 【0052】

また、幾つかの実施例では、犠牲層103は、第二接觸層118の材料とは異なるエッティング選択比を有する材料、例えば、AlAs(aluminum arsenide)を含む。幾つかの実施例では、犠牲層103の移除は、エッティングエッティングプロセス、ドラーエッティングプロセス、レーザー剥離プロセス(laser lift-off, LLO)、又はこれらの組み合わせを用いても良い。10

#### 【0053】

第4B図は、一実施例における半導体素子のある製造段階の断面図であり、基板トランスマスター技術により、第一接觸層104、第一ウィンドウ層106、緩衝層108、第一型半導体構造110、アクティブ構造112、第二型半導体構造114、第二ウィンドウ層116、及び第二接觸層118を接着層(図示せず)で非成長基板(ベース102)に接着し、接着層は、第一接觸層104と非成長基板との間に位置する。続いて、犠牲層103を除去することで、第二接觸層118を成長基板101から離脱させるが、本発明は、これに限定されない。上下反転することで、第一接觸層104、第一ウィンドウ層106、緩衝層108、第一型半導体構造110、アクティブ構造112、第二型半導体構造114、第二ウィンドウ層116、及び第二接觸層118の非成長基板上での配置は、第4A図中の成長基板101上での配置とは逆である。具体的に言えば、第4A図に示すように、上下反転前に、アクティブ構造112は、第一型半導体構造110と成長基板101との間に位置し、第4B図に示すように、上下反転後に、第一型半導体構造110は、非成長基板とアクティブ構造112との間に位置する。20

#### 【0054】

また、成長基板101は、半導体材料、例えば、SiC(silicon carbide)、GaAs(gallium arsenide)、GaP(gallium phosphide)、GaAsP(gallium arsenide phosphide)、ZnSe(zinc selenide)、InP(indium phosphide)などを含んでも良いが、これに限定されない。幾つかの実施例では、成長基板101の材料は、サファイア(sapphire)を含んでも良いが、これに限られない。非成長基板の材料及び成長基板101の材料は、同じであっても良く、異なっても良く、多数の実施例では、非成長基板は、成長基板101とは異なる特性を有し、例えば、成長基板101に比べて、非成長基板は、より高い熱伝導性、電気伝導率、透明度、又は機械的強度を有する。30

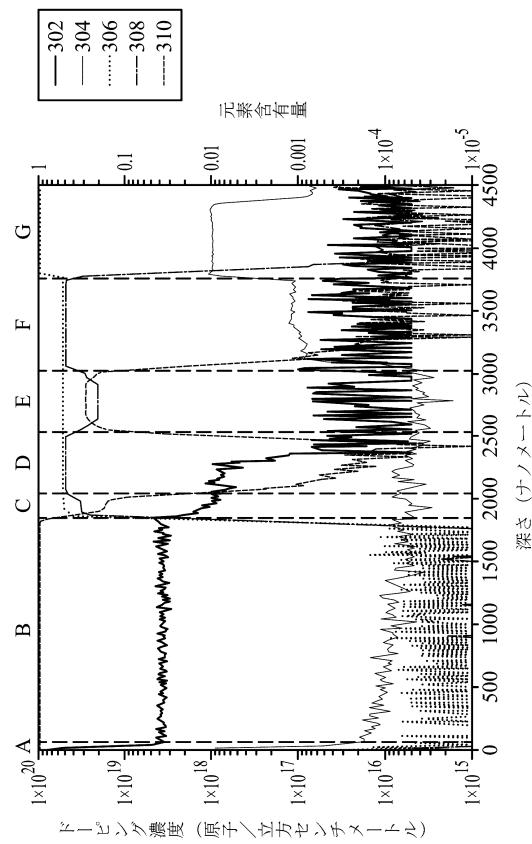

#### 【0055】

第5図は、一実施例における半導体素子の一部範囲の元素の濃度と深さ、及び、ドーパントのドーピング濃度と深さの関係図である。具体的に言えば、第5図は、第1図の半導体素子100における一部構造の二次イオン質量分析法(secondary ion mass spectrometer, SIMS)による質量分析図である。なお、本発明は、これに限定されず、他の技術を用いて、半導体素子100の一部範囲における元素の濃度と深さの関係図を得ても良い。ここで、前述の深さとは、ベース102から離れる一側から、ベース102に近い一側への方向上での深さを指し、即ち、ベース102に近いほど、深さが深い。40

#### 【0056】

第5図に示すように、半導体素子100中の各層の深さ及び順序に従って、質量分析図は、大抵7つの領域A-Gに分かることができる。A領域は、実質的に第一接觸層104の位置に対応し、B領域は、実質的に第一ウィンドウ層106の位置に対応し、C領域は、実質的に緩衝層108の位置に対応し、D領域は、実質的に第一型半導体構造110の位置に対応し、E領域は、実質的にアクティブ構造112の位置に対応し、F領域は、実質的に第二型半導体構造114の位置に対応し、G領域は、実質的に第二ウィンドウ層116の位置に対応する。

#### 【0057】

第5図に示すように、質量分析図は、第一ドーパント302、第二ドーパント304、第一

10

20

30

40

50

元素306、第二元素308、及び第三元素310を含む。第一接触層104、第一ウィンドウ層106、緩衝層108、及び第一型半導体構造110は、第一ドーパント302を有し、第一ドーパント302は、これらの層の導電型をP型にすことができ、第一ドーパントは、Znである。第二型半導体構造114及び第二ウィンドウ層116は、第二ドーパント304を有し、第二ドーパント304は、これらの層の導電型をN型にすことができ、第二ドーパントは、Siである。第一元素、第二元素、及び第三元素は、各層の主体(host)を構成する元素であり、第3族元素又は第5族元素であっても良く、第5図では、第一元素は、インジウムであり、第二元素は、アルミニウムであり、第三元素は、ガリウムであり、すべては、第3族元素であり、第一元素の原子量は、第三元素の原子量よりも大きく、第二元素の原子量は、第三元素の原子量よりも小さい。第一ドーパント302及び第二ドーパント304の濃度は、左の縦軸に示され、第一元素306、第二元素308、及び第三元素310の含量は、右の縦軸に示される。右の縦軸に示される元素の含量は、単一の元素の含量の各層中の相対的関係を示すものである。

#### 【0058】

A領域では、第一ドーパント302(Zn)は、最も高い濃度を有し、その濃度は、 $1 \times 10^{18} / \text{cm}^3$ よりも大きく、第一ドーパント302の濃度は、深さの増加に伴って遙減する。具体的に言えば、A領域中のZnドーパントは、第一ドーピング濃度を有し、C領域中のZnドーパントは、第二ドーピング濃度を有し、第二ドーピング濃度は、第一ドーピング濃度よりも小さい。また、E領域中のZnドーパントは、第三ドーピング濃度を有し、第二ドーピング濃度は、第一ドーピング濃度と第三ドーピング濃度との間にある。B領域中のZnドーパントは、第四ドーピング濃度を有し、第四ドーピング濃度は、第一ドーピング濃度と第二ドーピング濃度との間にある。幾つかの実施例では、第一ドーピング濃度と第二ドーピング濃度(第一ドーピング濃度 / 第二ドーピング濃度)の比は、10 ~ 100である。

#### 【0059】

G領域中の第二ドーパント304(Si)は、最も高いドーピング濃度を有し、その濃度は、約 $1 \times 10^{18} / \text{cm}^3$ である。具体的に言えば、G領域中のSiドーパントは、第五ドーピング濃度を有し、F領域中のSiドーパントは、第六ドーピング濃度を有し、第五ドーピング濃度は、第六ドーピング濃度よりも大きい。幾つかの実施例では、第五ドーピング濃度と第六ドーピング濃度の比は、約2 ~ 約100である。

#### 【0060】

G領域中の第一元素306(In)は、最も大きい含量を有し、第一元素306の含量は、深さの増加に伴って遙増する。具体的に言えば、C領域、D領域、E領域、及びF領域は、実質的にほぼ同じ含量のIn 306を含み、C領域、D領域、E領域、及びF領域中のIn含量のそれぞれと、A領域中のIn含量との比がすべて1000よりも大きいので、A領域がInを含まないと見なすことができる。ここで、「含まない」とは、「非故意添加」を指す。

#### 【0061】

D領域及びF領域中の第二元素308(AI)の含量は、E領域中の第二元素308の含量よりも大きい。D領域及びF領域は、実質的にほぼ同じ含量のAI 308を含み、D領域及びF領域中のAI含量のそれぞれと、A領域中のAI含量との比はすべて1000よりも大きいので、A領域がAIを含まないと見なすことができる。同様に、D領域及びF領域中のAI含量のそれぞれと、G領域中のAI含量との比はすべて1000よりも大きいので、G領域がAIを含まないと見なすこともできる。

#### 【0062】

A領域及びB領域の第三元素310(Ga)は、最も高い含量を有し、E領域のGa含量は、A領域及びB領域中のGa含量よりも小さい。A領域及びB領域中のGa含量に比べて、D領域、F領域、及びG領域中Ga含量は極めて小さく、具体的に言えば、A領域中のGa含量と、D領域、F領域、及びG領域中のGa含量との比がすべて1000よりも大きいので、D領域、F領域、及びG領域がGaを含まないと見なすことができる。

#### 【0063】

10

20

30

40

50

第6図は、もう1つの実施例における導体素子300の断面図である。便宜のため、同じ符号で同じ又は類似する構造を示す。これらの構造の形成方法及び材料は、前述と同様であるため、ここでは、その詳しい説明を省略する。この実施例では、半導体素子100に比べて、半導体素子300は、第二型半導体構造114、第二接触層118、及び緩衝層108を含まない。また、半導体素子300は、ダブルヘテロ構造(DH)であり、アクティブ構造112の材料は、4つ1組の化合物半導体、例えば、InGaAsPであり、第一接触層104の材料は、2つ1組の化合物半導体、例えば、GaAsである。一実施例では、第一ウインドウ層106の材料は、第二ウインドウ層116の材料と同じであり、且つ第一型半導体構造110の材料と異なっても良く、例えば、第一ウインドウ層106及び第二ウインドウ層116の材料は、ともに、InPであり、又は、実質的にInPからなる。もう1つの実施例では、第一接触層104及び第一ウインドウ層106は、同じ材料、例えば、GaAsを含み、且つ第二ウインドウ層116の材料とは異なり、第二ウインドウ層の材料は、例えば、InPである。また、半導体素子300の第二ウインドウ層116中のドーパントのドーピング濃度は、 $8 \times 10^{17} / \text{cm}^3$ よりも小さくても良く、例えば、 $1 \times 10^{16} / \text{cm}^3 \sim 5 \times 10^{17} / \text{cm}^3$ の範囲にある。

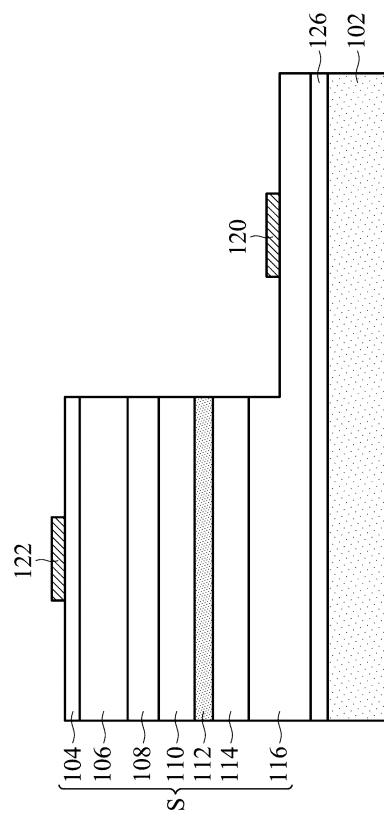

#### 【0064】

第7図は、他の実施例における半導体素子400の断面図である。便宜のため、同じ符号で同じ又は類似する構造を示す。これらの構造の形成方法及び材料は、前述と同様であるから、ここでは、その詳しい説明を省略する。この実施例では、第一電極122及び第二電極120は、ベース102の同じ側に位置し、水平型半導体素子400を形成する。もう1つの実施例では、選択的に、半導体スタック層Sとベース102との間に接続層126を設けても良い。接続層126の材料は、絶縁材料を含んでも良く、例を挙げて言えば、絶縁材料は、SiO<sub>2</sub>、Al<sub>2</sub>O<sub>3</sub>、AIN、BCBなどを含んでも良いが、これに限定されない。これらの実施例では、上述のベース102は、アクティブ構造112が発する光に対して透明である材料を使用することで、半導体素子がベース102側から光を射出するようにさせることができ、また、半導体素子は、フリップチップ(flip-chip)方式で、第一電極122及び第二電極120を下に向けて回路板に接続するようにさせることができる。

#### 【0065】

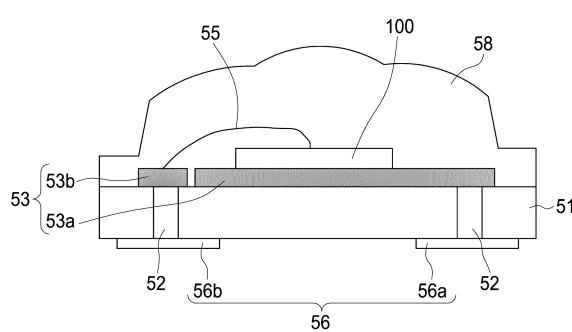

第8図は、一実施例における半導体素子のパッケージ構造図である。第8図に示すように、パッケージ構造500は、半導体素子100、パッケージプレート51、載置体53、接続線55、接触構造56、及びパッケージ材料58を含む。パッケージプレート51は、セラミック又はグラス材料を含んでも良い。パッケージプレート51には、複数の貫通孔52がある。貫通孔52は、導電性材料、例えば、金属などを充填することで、導電又は/及び放熱を助けることができる。載置体53は、パッケージプレート51bの一方側の表面に位置し、且つ導電性材料、例えば、金属を含む。接触構造56は、パッケージプレート51の他方側の表面に位置する。本実施例では、接触構造56は、接触パッド56a及び接触パッド56bを含み、接触パッド56a及び接触パッド56bは、貫通孔52により載置体53と電気接続することができる。一実施例では、接触構造56は、放熱パッド(thermal pad)(図示せず)を更に含んでも良く、それは、例えば、接触パッド56aと接触パッド56bとの間に位置する。半導体素子100は、載置体53に位置し、本発明の任意の実施例に記載の半導体素子であっても良い。本実施例では、載置体53は、第一部分53a及び第二部分53bを含み、半導体素子100は、接続線55により、載置体53の第二部分53bと電気接続される。もう1つの実施例では、半導体素子100が載置体53に設置されず、パッケージプレート51に直接設置され、且つ接触構造56と電気接続を形成することができる。

#### 【0066】

接続線55の材質(材料)は、金属、例えば、金、銀、銅、アルミニウム、又はこれらのうちの少なくとも任意の1つの元素を含む合金を含んでも良い。パッケージ材料58は、半導体素子100を覆い、半導体素子100を保護する効果を有する。具体的に言えば、パッケージ材料58は、樹脂材料、例えば、エポキシ樹脂(epoxy)、シリコーン樹脂(silicone)などを含んでも良い。パッケージ材料58は、半導体素子50が発する第一光を第二光に変換する複数の波長変換粒子(図示せず)を更に含んでも良い。第二光の波長は、第一光の波長

よりも大きい。他の実施例では、上述のパッケージ構造500中の半導体素子100は、半導体素子200又は300であっても良く、或いは、幾つかの実施例では、パッケージ構造500は、複数の半導体素子100、200、及び／又は300を含み、これらの半導体素子100、200、及び／又は300は、直列接続、並列接続、又は直並列接続されても良い。

#### 【0067】

本発明の幾つかの実施例では、半導体素子が提供され、この半導体素子中の1つ又は複数の接触層及び／又はウィンドウ層は、吸収波長がアクティブ構造の発光波長とは異なる材料を使用し、これにより、アクティブ構造が発する光が接触層及び／又はウィンドウ層により吸収されることを避け、発光効率を向上させることができ、また、輝度に影響する接触層及び／又はウィンドウ層を除去するステップを省略することもできる。さらに、接触層に対して粗化プロセスを行うことで、発光効率をより一層向上させることができる。10

#### 【0068】

また、本発明の幾つかの実施例では、半導体素子における接触層と半導体構造との間に緩衝層を設置することで、接触層と第一型半導体構造又は第二型半導体構造との間の価電子帯エネルギーレベル及び／又は伝導帯エネルギーレベルの差を緩和し、半導体素子の飽和電流低下又は早期失効などの問題を避け、半導体素子の信頼度を向上させることもできる。

#### 【0069】

本発明による半導体素子は、照明、表示、通信、検出、電源システムなどの分野における製品、例えば、照明器具、監視器、携帯電話、タブレットコンピュータ、車載用計器盤、テレビ、検出器、コンピュータ、ウェアラブルデバイス(例えば、腕時計、ブレスレット、ネックレスなど)、交通信号機、屋外表示器などに応用することができる。20

#### 【0070】

以上、本発明の好ましい実施形態を説明したが、本発明はこの実施形態に限定されず、本発明の趣旨を離脱しない限り、本発明に対するあらゆる変更には本発明の技術的範囲に属する。

#### 【符号の説明】

##### 【0071】

100、200、300、400：半導体素子

101：成長基板

102：ベース

103：犠牲層

104：第一接触層

106：第一ウィンドウ層

108：緩衝層

110：第一型半導体構造

112：アクティブ構造

114：第二型半導体構造

116：第二ウィンドウ層

118：第二接触層

122：第一電極

120：第二電極

124：接続層

130：反射構造

132：第三接触層

134：バリア層

136：反射接続層

138：反射層

140：導電構造

141：孔

10

20

30

40

50

142 : 第一導電層

144 : 第二導電層

146 : 絶縁層

302 : 第一ドーパント

304 : 第二ドーパント

306 : 第一元素

308 : 第二元素

310 : 第三元素

500 : パッケージ構造

51 : パッケージプレート

52 : 貫通孔

53 : 載置体

53a : 第一部分

53b : 第二部分

55 : 接続線

56 : 接触構造

56a、56b : 接触パッド

58 : パッケージ材料

S : 半導体スタック層

S1 : 第一側

S2 : 第二側

10

20

## 【図面】

【図1】

【図2】

30

40

200

50

【図3】

【図4 A】

10

【図4 B】

20

【図5】

30

40

50

【図6】

300

【図7】

10

【図8】

500

20

30

40

50

---

フロントページの続き

(72)発明者 モン - ヤン チェヌ

台湾 シンチュ シティ , サイエンス - ベースド インダストリアル パーク , リ - シン ロード 21

(72)発明者 ジュン - ジェヌ リ

台湾 シンチュ シティ , サイエンス - ベースド インダストリアル パーク , リ - シン ロード 21

審査官 村井 友和

(56)参考文献 特開 2000-196196 (JP, A)

特表 2010-539731 (JP, A)

特開 2004-071896 (JP, A)

国際公開第 2018/151157 (WO, A1)

特開平 06-037405 (JP, A)

特開 2008-263015 (JP, A)

特開 2014-082321 (JP, A)

特開 2012-175052 (JP, A)

特開 2012-190985 (JP, A)

特開 2006-351974 (JP, A)

米国特許出願公開第 2004/0051113 (US, A1)

特開 2013-030606 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01L 33/00 - 33/46