(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5727036号

(P5727036)

(45) 発行日 平成27年6月3日(2015.6.3)

(24) 登録日 平成27年4月10日(2015.4.10)

(51) Int.Cl.

F 1

H01L 21/8247 (2006.01)

H01L 27/115 (2006.01)

H01L 21/336 (2006.01)

H01L 29/788 (2006.01)

H01L 29/792 (2006.01)

H01L 27/10 434

H01L 29/78 371

請求項の数 12 (全 10 頁)

(21) 出願番号 特願2013-544873 (P2013-544873)

(86) (22) 出願日 平成23年12月19日 (2011.12.19)

(65) 公表番号 特表2014-504015 (P2014-504015A)

(43) 公表日 平成26年2月13日 (2014.2.13)

(86) 國際出願番号 PCT/US2011/065923

(87) 國際公開番号 WO2012/087974

(87) 國際公開日 平成24年6月28日 (2012.6.28)

審査請求日 平成26年1月24日 (2014.1.24)

(31) 優先権主張番号 12/973,631

(32) 優先日 平成22年12月20日 (2010.12.20)

(33) 優先権主張国 米国(US)

(73) 特許権者 504378124

スパンション エルエルシー

アメリカ合衆国 カリフォルニア州 94

088-3453 サニーベイル テグウ

イン ドライブ 915

(74) 代理人 100079108

弁理士 稲葉 良幸

(74) 代理人 100109346

弁理士 大貫 敏史

(72) 発明者 チェン, トゥンーシエン

アメリカ合衆国, カリフォルニア州 95

014, クパチーノ, ボリンジャー ロード 7435

最終頁に続く

(54) 【発明の名称】電荷トラップ電界効果トランジスタにおけるプロセスマージンのエンジニアリング

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に複数のシャロートレンチアイソレーション領域を形成することと、

基板上にトンネル誘電体領域を形成することと、

前記トンネル誘電体領域および前記シャロートレンチアイソレーション領域上に第1窒化物層を形成することと、

前記第1窒化物層の一部を、前記トレンチアイソレーション領域の頂部までエッチバックすることと、

前記エッチバックされた第1窒化物層上に第2窒化物層を形成することと、

前記シャロートレンチアイソレーション領域の頂部まで前記第1および第2窒化物層の一部を酸化し、前記トンネル誘電体領域上に電荷トラップ領域を、かつ、前記電荷トラップ領域上にブロッキング誘電体領域を形成することと、

前記ブロッキング誘電体領域上にゲート領域を形成することと、を含み、

前記シャロートレンチアイソレーション領域の頂部は、前記基板から上方に所定量延在し、

前記第1窒化物層の厚さは、前記シャロートレンチアイソレーション領域が前記基板から上方に延在する前記所定量の1/3~2/3の厚さである、

方法。

## 【請求項 2】

前記第1窒化物層は、シリコンリッチ窒化物層を含む、請求項1に記載の方法。

10

20

**【請求項 3】**

前記第2窒化物層は、シリコンリッチ窒化物層を含む、請求項1又は2に記載の方法。

**【請求項 4】**

前記電荷トラップ領域は、窒化シリコンを含む、請求項1～3のいずれか1項に記載の方法。

**【請求項 5】**

前記トンネル誘電体領域は、酸化シリコンを含む、請求項1～4のいずれか1項に記載の方法。

**【請求項 6】**

前記プロッキング誘電体領域は、酸窒化シリコンを含む、請求項1～5のいずれか1項に記載の方法。 10

**【請求項 7】**

前記プロッキング誘電体領域は、酸窒化物を含む、請求項1～6のいずれか1項に記載の方法。

**【請求項 8】**

前記電荷トラップ領域を形成することは、シリコンリッチ窒化物層を化学気相蒸着することを含む、請求項1～7のいずれか1項に記載の方法。

**【請求項 9】**

前記プロッキング誘電体領域を形成することは、窒化シリコン層または酸窒化シリコン層を化学気相蒸着することを含む、請求項1～8のいずれか1項に記載の方法。 20

**【請求項 10】**

前記ゲート領域を形成することは、ポリシリコンを化学気相蒸着することを含む、請求項1～9のいずれか1項に記載の方法。

**【請求項 11】**

前記トンネル誘電体領域を形成することは、前記基板の一部を酸化することを含む、請求項1～10のいずれか1項に記載の方法。

**【請求項 12】**

前記シャロートレンチアイソレーション領域を形成することは、

複数のトレンチをエッティングすることと、

前記トレンチ内に誘電体層を堆積することと、

前記誘電体層をエッチバックし、前記トレンチ内に前記シャロートレンチアイソレーション領域を形成することと、を含む、

請求項1～11のいずれか1項に記載の方法。

**【発明の詳細な説明】****【背景技術】****【0001】**

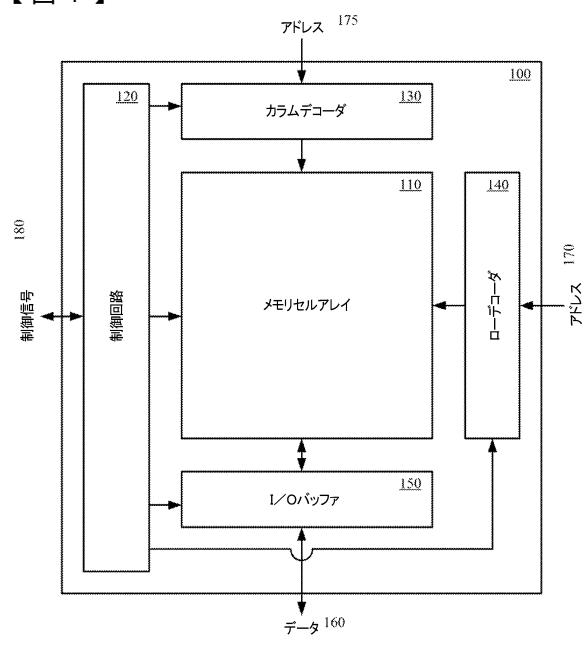

コンピュータ、スマートフォン、デジタルコンテンツプレーヤ（例えば、MP3プレーヤ）、ゲーム機、制御システムなどの数々の電子デバイスにおいて、データ記憶装置は重要な部分である。多くの電子デバイスは、フラッシュメモリなどの不揮発性固体メモリを備える。フラッシュメモリデバイスの一般的なタイプの1つに、電荷トラップ（CT）NAND集積回路（IC）がある。図1は、例示的なCT-NANDベースのフラッシュメモリICを示す。フラッシュメモリIC100では、CT-NANDメモリセルアレイ110と、制御回路120と、カラムデコーダ130と、ローデコーダ140と、入出力（I/O）バッファ150などが、1枚の基板上に組み立てられている。制御回路120、カラムデコーダ130、ローデコーダ140、I/Oバッファ150などは、メモリセルアレイ110内のアドレス170、175にて、フラッシュメモリIC100により受信された信号、フラッシュメモリIC100内への信号、および／または、フラッシュメモリIC100から出力された信号などの様々な制御信号180に従って、データ160の読み出しおよび書き込みを行うように動作する。フラッシュメモリIC100の回路は本技術分野において公知であるため、本技術の実施形態に特有でないフラッシュメモリIC1 40

00の態様については、さらなる説明を省略する。

#### 【0002】

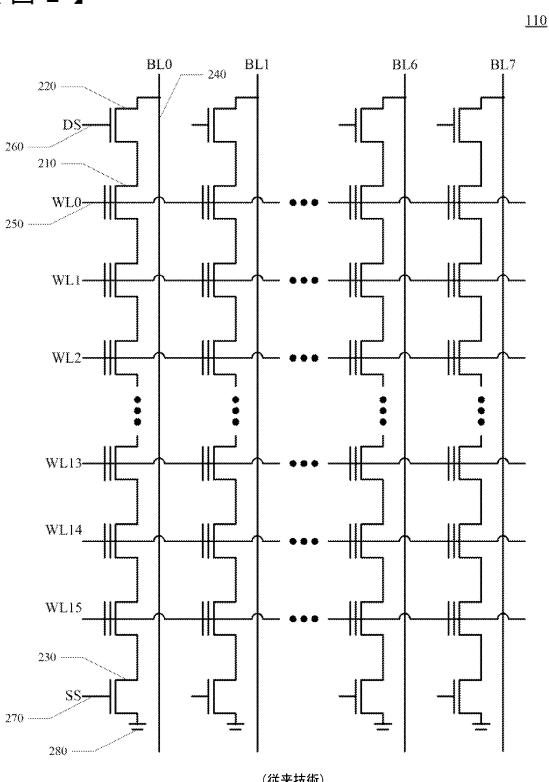

図2を参照すると、例示的なメモリセルアレイが示されている。CT-NANDメモリセルアレイ110は、複数のCT電界効果トランジスタ(FET)210と、複数のドレイン選択ゲート220と、複数のソース選択ゲート230と、複数のピットライン240と、複数のワードライン250と、ドレイン選択信号線260と、複数のソース選択信号線270と、を備える。アレイ110の各カラムは、ドレイン選択ゲート220と、複数のCT-FET210と、ソース選択ゲート230とを含み、これらは、対応するピットライン240と接地電位280との間でソースからドレインに直列接続される。アレイ110の各ローにおける複数のCT-FET210の各々のゲートは、対応するワードライン250に連結される。各ドレイン選択ゲート220のゲートは、対応するドレイン選択信号線260に接続される。各ソース選択ゲート230のゲートは、対応するドレイン選択信号線270に接続される。一実施例において、CT-FETは、シリコン酸化窒化酸化シリコン(SONOS)FETなどであってよい。CT-NANDメモリセルアレイ110は、本技術分野において公知であるため、本技術の実施形態に特有でないCT-NANDメモリセルアレイ110の態様については、さらなる説明を省略する。10

#### 【0003】

CT-NANDメモリセルアレイ110の製造中、各種プロセスにおいて変動性が存在する。例えば、堆積された層の厚さは、ウェーハごとや所定のウェーハ内の領域ごとに変動することがある。同様に、エッチングプロセスにより除去される材料の量は、ウェーハごとや所定のウェーハ内の領域ごとに変動することもある。従って、1つ以上の製造プロセスにおけるプロセス変動性を補償することが可能な改善された製造技法に対する継続的な需要がある。20

#### 【発明の概要】

#### 【0004】

本技術は、以降の説明と、電荷トラップ電界効果トランジスタの製造のためのプロセスマージンのエンジニアリングに関する本技術の実施形態を図示するために使用される付属の図面とを参照することにより、最適に理解することができる。

#### 【0005】

一実施形態において、製造方法は、基板上に複数のシャロートレンチアイソレーション領域を形成することを含む。基板上には、トンネル誘電体領域も形成される。トンネル誘電体領域およびシャロートレンチアイソレーション領域上には、第1の窒化物層が形成される。第1の窒化物層の一部分は、トレンチアイソレーション領域の頂部までエッチバックされる。エッチバックされた第1の窒化物層上には、第2の窒化物層が形成される。第1および第2の窒化物層の一部分は酸化され、トンネル誘電体領域上に電荷トラップ領域が、かつ、電荷トラップ領域上にブロッキング誘電体領域が形成される。その後、ブロッキング誘電体領域上にゲート領域が形成される。30

#### 【0006】

別の実施例形態において、製造方法は、基板上に複数のシャロートレンチアイソレーション領域を形成することを含み、シャロートレンチアイソレーション領域の頂部は、基板から所定量だけ上方に延在する。基板上にトンネル誘電体領域が形成される。トンネル誘電体領域およびシャロートレンチアイソレーション領域上に窒化物層が形成され、窒化物層の厚さは、シャロートレンチアイソレーション領域の頂部が基板から上方に延在する所定量の約半分である。窒化物層の一部分は、トレンチアイソレーション領域の頂部までエッチバックされ、トレンチ間に電荷トラップ領域が形成される。ブロッキング誘電体領域が電荷トラップ領域上に形成され、ゲート領域がブロッキング誘電体領域上に形成される。40

#### 【図面の簡単な説明】

#### 【0007】

本技術の実施形態は、限定を意図せず、例示を目的として、添付の図面に図示されてい50

る。これらの図面において、同一の参照番号は同様の要素を示す。

【0008】

【図1】図1は、従来技術に係る例示的なCT-NANDベースのフラッシュメモリICのブロック図を示す。

【図2】図2は、従来技術に係る例示的なメモリセルアレイのブロック図を示す。

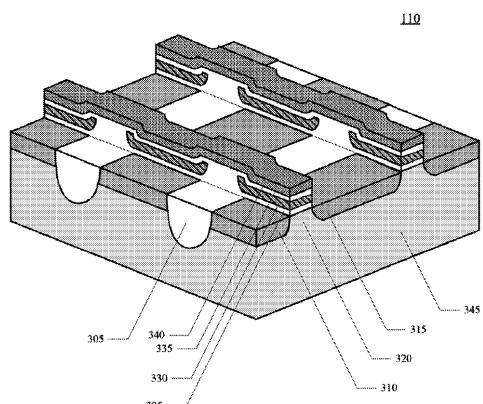

【図3】図3は、本技術の一実施形態に係るメモリセルアレイ構造のブロック図を示す。

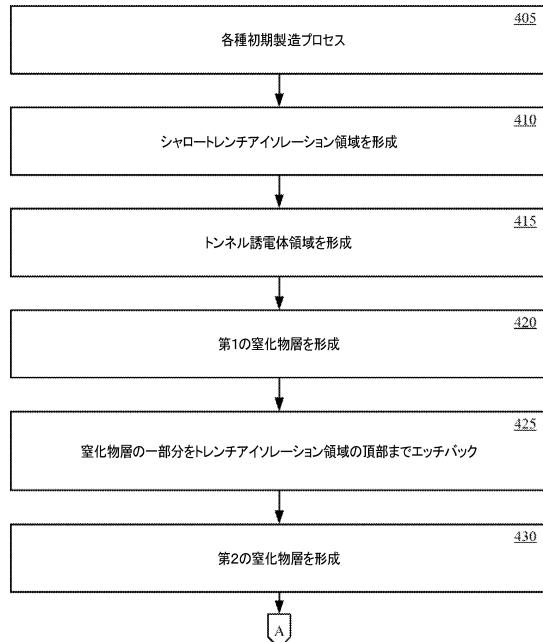

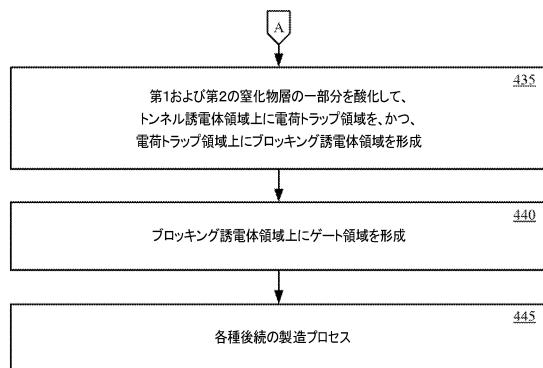

【図4】図4Aおよび図4Bは、本技術の一実施形態に係る電荷トラップ電界効果トランジスタを製造する方法のフロー図を示す。

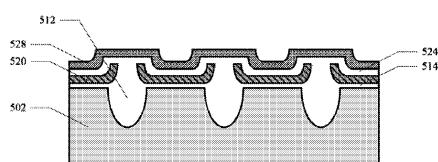

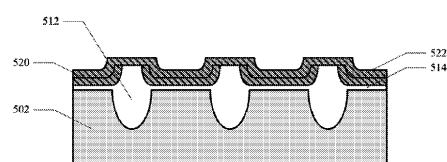

【図5】図5A～図5Iは、本技術の一実施形態に係る電荷トラップ電界効果トランジスタの製造を図示するブロック図である。

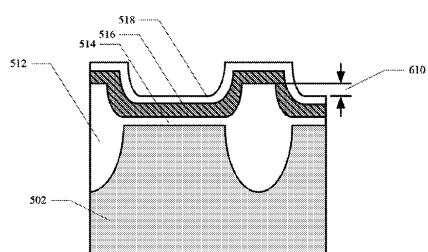

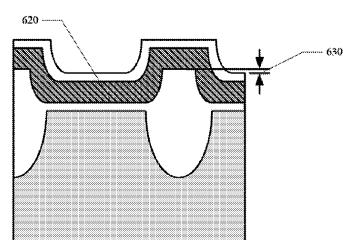

【図6】図6Aおよび図6Bは、本技術の一実施形態に係る電荷トラップ領域に使用される薄い窒化物層および厚い窒化物層のプロセス製造マージンにおける差異を図示するブロック図である。

10

【発明を実施するための形態】

【0009】

添付の図面に例示されている本技術の実施形態について、以下、詳細に説明する。以下、本技術をこれらの実施形態に関連して説明するが、これらの実施形態は、本発明を限定することを意図したものではないことを理解されたい。逆に、本発明は、添付の請求の範囲によって定義される本発明の範囲に含まれ得る変更、改良および同等物を包含することを意図している。さらに、以下の本技術の詳細な説明では、本技術の完全な理解を提供するために、具体的な詳細を数多く記載する。しかし、本技術は、それらの具体的な詳細がなくとも実現できることを理解されたい。その他の場合、公知の方法、手順、構成部品および回路については、本技術の態様を必要に不明瞭にしないように、詳細な説明を省略した。

20

【0010】

本願において、選言的な表現を使用する場合、連言的な表現も含まれることが意図される。定冠詞または不定冠詞の使用は、基数を示すことを意図するものではない。特に、「その(the)」物または「ある(an)」物と言及した場合には、考えられる複数の該物のうちの1つも表すことが意図される。

【0011】

30

図3を参すると、本技術の一実施形態に係るメモリセルアレイ構造が示されている。一実施例において、このメモリセルアレイは、CT-NANDメモリセルアレイ110であり得る。しかし、当然のことながら、本技術の実施形態は、あらゆるCT-FETデバイスに適用することができる。一実施例において、CT-FETの各カラムは、シャロートレンチアイソレーション(STI:shallow trench isolation)領域305により分離されている。各CT-FETは、ドレイン領域310と、ソース領域315と、チャネル領域320と、トンネル誘電体領域(通常、下部誘電体領域とも呼ばれる)325と、電荷トラップ領域330と、プロッキング誘電体領域(通常、上部誘電体領域とも呼ばれる)335と、ゲート領域340と、を含み得る。ソース領域およびドレイン領域310、315は、第1タイプの不純物の高ドーピング濃度を有する基板345の半導体領域であり得る。一実施例において、ソース領域およびドレイン領域310、315は、リンまたはヒ素が高濃度にドープされたシリコンであり得る。チャネル領域320は、第2タイプの不純物の中ドーピング濃度を有する基板345の半導体領域であり、ソース領域315とドレイン領域310との間に横方向に配置される。一実施例では、チャネル領域320は、ホウ素が中濃度にドープされたシリコンであり得る。トンネル誘電体領域325は、チャネル領域320上と、ソース領域およびドレイン領域310、315のチャネル領域320との隣接部分上とにわたって配置された誘電体層であり得る。一実施例において、トンネル誘電体領域325は、酸化シリコン、酸窒化物、酸窒化シリコンなどの層であってよい。電荷トラップ領域330は、トンネル誘電体領域325とプロッキング誘電体領域335との間に配置される誘電体、半導体などの層であり得る。一実施例において、電荷ト

40

50

ラップ領域 330 は、窒化物、シリコンリッチ窒化物などの層であってよい。プロッキング誘電体領域 335 は、電荷トラップ領域 330 とゲート領域 340 との間に配置された誘電体層であり得る。一実施例において、プロッキング誘電体領域 335 は、酸化シリコン、酸窒化物、酸窒化シリコンなどの層であってよい。ゲート領域 340 は、電荷トラップ領域 330 とは反対側のプロッキング誘電体領域 335 上に配置された半導体層または導体層であり得る。一実施例において、ゲート領域 340 は、第 1 タイプの不純物の高ドーピング濃度を有するポリシリコン層であり得る。

#### 【 0012 】

次に、図 4A および 4B を参照すると、本技術の一実施形態に係る CTFET の製造方法が示されている。この CTFET の製造方法について、本技術の一実施形態に係る CTFET の製造を図示する図 5A ~ 5I を参照して詳細に説明する。図 4A および 5A に示すように、プロセスは、クリーニング、堆積、ドーピング、エッチングなどといった半導体ウェーハ基板 502 に対する各種初期プロセスを有する工程 405 から始まり、1 つ以上の領域を形成する。基板 502 は、第 1 タイプのドーパントが第 1 濃度にドープされた半導体であってよい。一実施例において、基板 502 は、ホウ素が中濃度にドープされたシリコンであり得る (P 型)。

10

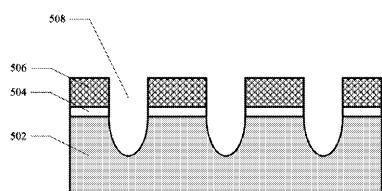

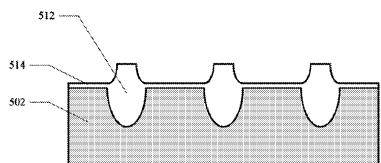

#### 【 0013 】

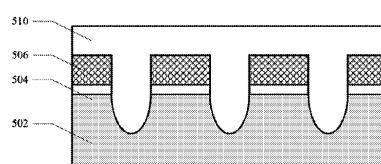

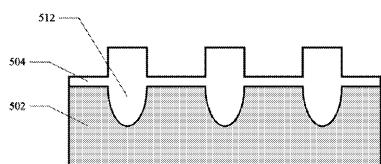

工程 410 において、複数のシャロートレンチアイソレーション領域が形成される。一実施例において、任意の公知の酸化プロセスにより、犠牲酸化物 504 が基板 502 上に形成され得る。その後、犠牲酸化物上には、フォトレジストが堆積され、任意の公知のフォトリソグラフィプロセスによってパターン形成されて、シャロートレンチアイソレーション (STI) マスク 506 を形成する。STI マスク 506 によって露出したメモリセルアレイ内の基板 502 および犠牲酸化物 504 は、その後、任意の公知のエッチングプロセスによって選択的にエッチングされ複数のトレンチ 508 が形成される。次に図 5B を参照すると、トレンチ 508 に誘電体 510 が充填され得る。一実施例において、共形酸化物、スピノンガラスなどが堆積される。図 5C を参照すると、誘電体層 510 は、その後、任意の公知のエッチングプロセスまたは化学的機械的研磨 (CMP) プロセスによってエッチバックされ、通常 STI メサと呼ばれる、基板から所定量だけ上方に延在する部分を有するシャロートレンチアイソレーション領域 512 が形成される。STI マスク 506 は、その後、レジスト剥離またはレジストアッシングといった任意の公知のプロセスにより除去することができる。犠牲酸化物 504 もまた任意の公知の選択的なエッチングプロセスにより除去することができる。

20

#### 【 0014 】

次に、図 5D を参照すると、工程 415 において、トンネル誘電体領域 514 が基板 502 上に形成される。一実施例において、トンネル誘電体領域 514 は、メモリセルアレイ領域において、基板 502 の露出した表面を任意の公知の熱乾燥酸化プロセスにより酸化することにより形成され得る。別の実施例では、トンネル誘電体領域 514 は、任意の公知の化学気相蒸着プロセスにより酸窒化シリコン膜を堆積することによって形成されてもよい。一実施例では、トンネル誘電体領域 514 は、約 3 ~ 8 ナノメートルの厚さに形成され得る。

30

#### 【 0015 】

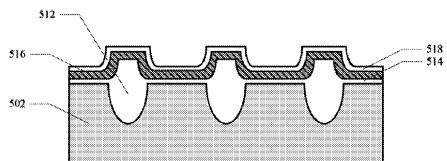

次に、図 5E を参照すると、工程 420 において、第 1 セットの 1 つ以上の窒化物などの層 516 がトンネル誘電体領域 514 上に形成される。一実施例において、第 1 セットの 1 つ以上の窒化物などの層 516 は、化学気相蒸着 (CVD) または原子層堆積 (ALD) といった任意の公知のプロセスによって、窒化物などをトンネル誘電体領域 514 上に堆積することにより形成される。第 1 の窒化物などの層 516 は、シリコン : 窒素の原子比率が約 3 : 4 以上のシリコンリッチ窒化物を含み得る。一実施例において、第 1 セットの 1 つ以上の窒化物などの層は、シャロートレンチアイソレーション領域の頂部が基板から上方に延在する高さの約 3 分の 1 ~ 3 分の 2 の厚さを有し得る。第 1 の窒化物層 516 上には、酸化処理などの任意の公知のプロセスによって犠牲酸化物層 518 が形成され

40

50

てもよい。

**【0016】**

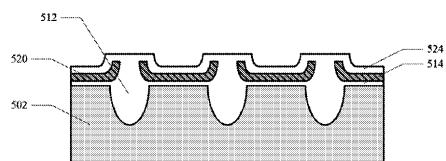

次に図5Fを参照すると、工程425において、第1セットの1つ以上の窒化物などの層の一部分および犠牲酸化物層の一部分は、シャロートレンチアイソレーション領域512の頂部までエッチバック520される。そして、犠牲酸化物層の残りの部分は、エッチバックプロセス後に除去される。

**【0017】**

次に図5Gを参照すると、工程430において、第2セットの1つ以上の窒化物などの層522が、エッチバック後の第1セットの1つ以上の窒化物などの層520上に形成される。一実施例において、第2セットの1つ以上の窒化物などの層522は、エッチバック後の第1セットの窒化物などの層520上に化学気相蒸着(CVD)などの任意の公知のプロセスによって窒化物を堆積することにより形成される。第2セットの窒化物などの層522は、シリコン：窒素の原子比率が約3：4以上のシリコンリッチ窒化物を含み得る。

10

**【0018】**

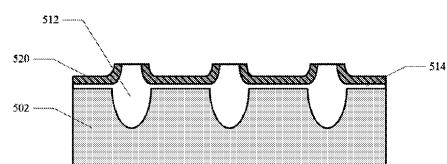

次に、図4Bおよび5Hを参照すると、工程435において、第1および第2の窒化物などの層520、522の一部分は酸化され、トンネル誘電体領域514上に電荷トラップ領域524を、電荷トラップ領域524上にブロッキング誘電体領域526を形成する。一実施例において、窒化物またはシリコンリッチ窒化物520、522は、シャロートレンチアイソレーション領域の頂部まで酸化され、酸窒化物または酸窒化シリコンを形成する。一実施例では、結果的に得られた電荷トラップ領域524は、約4～15ナノメートルの厚さ、結果的に得られたブロッキング誘電体領域526は、約3～8ナノメートルの厚さに形成され得る。

20

**【0019】**

相対的に薄い第1および第2の窒化物などの層を使用すると、有利なことに、エッチバックプロセスマージンが大きくなる。CT-FETをスケーリングする目的のために、薄い第1の窒化物などの層を堆積し、その一部分をエッチバックし、薄い第2の窒化物などの層を堆積し、酸化するプロセスは、有利なことに、STI領域に近接した電荷トラップ領域のウイングの高さを小さくし、かつ、セル間の結合／干渉を減少させる。さらに、薄い第2の窒化物などの層を消費してブロッキング誘電体領域を形成するため、さらにプロセスを複雑化したりエッチバックしたりする必要がない。

30

**【0020】**

別の実施例では、工程430～435において、第2の窒化物層を形成し、それを酸化するプロセスは、省略してもよい。その代わりに、エッチバック後の第1の窒化物層が電荷トラップ領域を形成し、誘電体を堆積してブロッキング誘電体領域を形成してもよい。

**【0021】**

次に、図5Iを参照すると、工程440において、ゲート領域528がブロッキング誘電体領域524上に形成される。一実施例において、化学気相蒸着などの任意の公知のプロセスによって、酸窒化物層または酸窒化シリコン層526上にポリシリコン層528が堆積される。

40

**【0022】**

工程445において、注入、ドーピング、エッティング、クリーニングなどといった各種後続のプロセスに進み、電荷トラップ領域、ブロッキング誘電体領域、およびゲート領域、ならびに／または、ゲート、ソース、およびドレイン端子、周辺回路、相互接続、ビアホール、不活性化層などといった1つ以上の追加領域がさらに形成される。なお、上述したCT-FETの製造方法は、他の追加的なプロセスを含んでもよく、プロセスの順序は、上述した順序とは異なってもよい。

**【0023】**

次に、図6Aおよび6Bを参照すると、薄い窒化物などの層および厚い窒化物などの層を使用して作られた例示的なゲートスタックが示されている。図6Aは、薄い第1の窒化

50

物などの層 516 を堆積することにより製造された C T - F E T のゲートスタックを示しており、薄い第 1 の窒化物などの層 516 は、その後、薄い第 2 の窒化物などの層が堆積され、酸化される前に部分的にエッチバックされることになる。エッチバックプロセスマージンは、610 で示されている。図 6 B は、厚い窒化物などの層 620 を堆積することにより製造されたゲートスタックを示しており、厚い窒化物などの層 620 は、その後、部分的に酸化される前に部分的にエッチバックされることになる。単一の厚い窒化物などの層 620 に対する、より小さいエッチバックプロセスマージンが 630 で示されている。図 6 B と比較して、図 6 A に示した本技術の実施形態のより大きいプロセスマージン 610 は、他のプロセス変動性を補償することにより、有利に、C T - F E T の製造および性能を改善する。例えば、薄い第 1 の窒化物などの層 516 を堆積し、その一部分をエッチバックし、薄い第 2 の窒化物などの層を堆積し、酸化するプロセスは、有利なことに、S T I 領域に近接した電荷トラップ領域のウイングの高さを小さくし、セル間の結合 / 干渉を減少させる。

10

## 【 0024 】

本技術の特定の実施形態についての上記記載は、例示および説明を目的として示した。それらの記載は、絶対的であることを意図せず、また、開示した厳密な形態に本発明を限定することも意図しない。当然ながら、上記の教示を踏まえて多くの改良および変形が可能である。実施形態は、本技術の原理とその実用上の用途について、最適に説明し、それにより当業者が、本技術と、考えられる特定の使用に適した多様な改良を伴う多様な実施形態とを最大限に利用することができるよう選択および記載された。本発明の範囲は、

20 添付の請求の範囲およびそれらの同等物によって定義されることが意図される。

【 図 1 】

【 図 2 】

【図3】

Figure 3

【図4A】

【図4B】

【図5A】

Figure 5A

【図5B】

Figure 5B

【図5C】

Figure 5C

【図5D】

Figure 5D

【図 5 E】

Figure 5E

【図 5 H】

Figure 5H

【図 5 F】

Figure 5F

【図 5 I】

Figure 5I

【図 5 G】

Figure 5G

【図 6 A】

Figure 6A

【図 6 B】

Figure 6B

---

フロントページの続き

(72)発明者 ファン , シエンチン

アメリカ合衆国 , カリフォルニア州 94539 , フリー蒙ト , ナンザ コート 43740

審査官 加藤 俊哉

(56)参考文献 特開2004-363329 (JP, A)

特開2010-278462 (JP, A)

米国特許出願公開第2010/0133646 (US, A1)

特開2009-152369 (JP, A)

特表2006-504264 (JP, A)

米国特許出願公開第2008/0290447 (US, A1)

(58)調査した分野(Int.Cl. , DB名)

H01L 21/8247

H01L 21/336

H01L 27/115

H01L 29/788

H01L 29/792