(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7561563号**

**(P7561563)**

(45)発行日 令和6年10月4日(2024.10.4)

(24)登録日 令和6年9月26日(2024.9.26)

## (51)国際特許分類

|        |                  |     |        |       |   |

|--------|------------------|-----|--------|-------|---|

| H 01 L | 21/822 (2006.01) | F I | H 01 L | 27/04 | E |

| H 01 L | 27/04 (2006.01)  |     | H 01 L | 21/88 | J |

| H 01 L | 21/3205(2006.01) |     | H 01 L | 21/88 | T |

| H 01 L | 21/768(2006.01)  |     | H 01 L | 23/28 | H |

| H 01 L | 23/522(2006.01)  |     | H 01 L | 23/28 | J |

請求項の数 4 (全9頁) 最終頁に続く

(21)出願番号 特願2020-168162(P2020-168162)

(22)出願日 令和2年10月5日(2020.10.5)

(65)公開番号 特開2022-60614(P2022-60614A)

(43)公開日 令和4年4月15日(2022.4.15)

審査請求日 令和5年7月3日(2023.7.3)

(73)特許権者 591036457

三菱電機エンジニアリング株式会社

東京都千代田区九段北一丁目13番5号

(74)代理人 110003166

弁理士法人山王内外特許事務所

山田 淳一

東京都千代田区九段北一丁目13番5号

三菱電機エンジニアリング株式会社内

審査官 市川 武宜

最終頁に続く

(54)【発明の名称】 半導体装置

## (57)【特許請求の範囲】

## 【請求項1】

データを記憶するメモリを有する半導体チップと、

前記メモリに直接接続され、前記半導体チップにおける前記メモリの上部に設けられた

データ読み出し用電極と、

前記半導体チップを収容するパッケージと、

前記パッケージの外表面における前記データ読み出し用電極に対応する位置に設けられた

電極指標部と、を備えた

ことを特徴とする半導体装置。

## 【請求項2】

前記電極指標部は、前記パッケージの外表面に設けられた凹部である

ことを特徴とする請求項1に記載の半導体装置。

## 【請求項3】

前記電極指標部は、前記パッケージの外表面に設けられたマークである

ことを特徴とする請求項1に記載の半導体装置。

## 【請求項4】

パッケージ基板に積層された複数の前記半導体チップと、

前記半導体チップを積層方向に貫通し、前記半導体チップ間の回路を電気的に接続する

貫通電極と、を備え、

前記データ読み出し用電極は、前記パッケージ基板から最も離れて積層された前記半導

体チップにおける前記メモリの上部に設けられた

ことを特徴とする請求項<sub>1</sub>から請求項<sub>3</sub>のいずれか1項に記載の半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、不揮発性メモリを有した半導体装置に関する。

【背景技術】

【0002】

1チップ化または1パッケージ化された半導体装置は、様々な電子機器に利用されている。例えば、ドライブレコーダ、監視カメラまたはスマートフォンといった電子機器は、大容量のデータが取り扱われ、さらにデータに高度なセキュリティが必要とされる。このため、半導体装置に不具合が発生した際に、チップまたはパッケージの内部のメモリからデータを安全に読み出し可能であることが要求される。

10

【0003】

例えば、特許文献1に記載された半導体装置は、モジュール出力端子が非通常状態であるか否かをMON端子から検出し、モジュール出力端子が非通常状態であるときに通常モードからデータ通信モードに移行して、モジュール出力端子ないしはモジュール電源端子を流用してセンサモジュール外部とのデータ通信を行う。これにより、特許文献1に記載された半導体装置は、非通常状態になっても、モジュール出力端子またはモジュール電源端子といった外部端子からデータを取り出すことができる。外部端子は、電極パッドまたはリードフレームである。

20

【先行技術文献】

【特許文献】

【0004】

【文献】特開2015-211068号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、電子機器において、電源トラブルによって半導体装置の外部端子に意図しない高電圧が印加されると、外部端子が破壊されて非導通状態になる場合がある。この場合、特許文献1に記載された半導体装置は、内部のメモリからデータを読み出せなくなるという課題があった。

30

【0006】

本開示は上記課題を解決するものであり、外部端子が非道通状態になってもメモリからデータを読み出すことができる半導体装置を得ることを目的とする。

【課題を解決するための手段】

【0007】

本開示に係る半導体装置は、データを記憶するメモリを有する半導体チップと、メモリに直接接続され、半導体チップにおけるメモリの上部に設けられたデータ読み出し用電極と、半導体チップを収容するパッケージと、パッケージの外表面におけるデータ読み出し用電極に対応する位置に設けられた電極指標部と、を備える。

40

【発明の効果】

【0008】

本開示によれば、メモリに直接接続され、半導体チップにおけるメモリの上部に設けられたデータ読み出し用電極を備えるので、本開示に係る半導体装置は、外部端子が非道通状態になってもメモリからデータを読み出すことができる。

【図面の簡単な説明】

【0009】

【図1】実施の形態1に係る半導体パッケージの構成を示す平面図である。

【図2】実施の形態1に係る半導体チップを示す斜視図である。

50

【図3】実施の形態1に係る半導体パッケージを示す斜視図である。

【図4】実施の形態1に係る半導体パッケージの構造を示す断面図である。

【図5】実施の形態1に係る半導体パッケージの変形例1を示す平面図である。

【図6】実施の形態1に係る半導体パッケージの変形例2の構成を示す部分断面図である。

【発明を実施するための形態】

【0010】

実施の形態1.

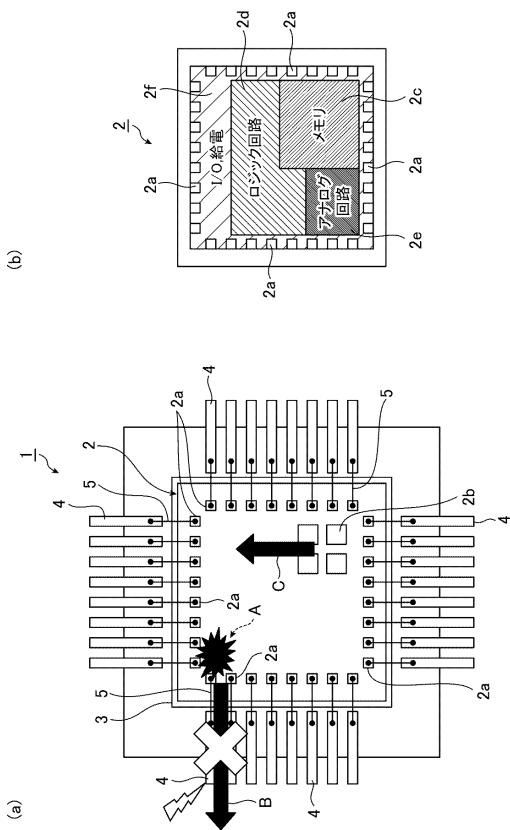

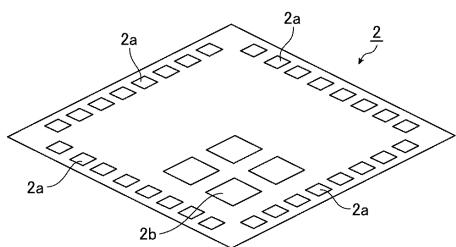

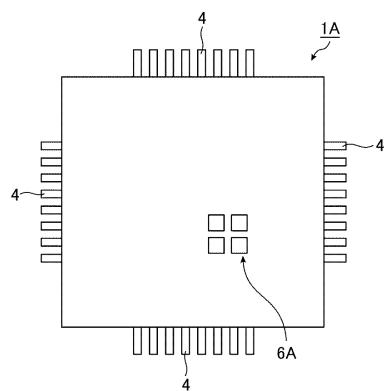

図1は、半導体パッケージ1の構成を示す平面図である。図1(a)は、半導体チップ2を収容する半導体パッケージ1の内部構成を示す平面図であり、内部構成を示すためにパッケージの封止樹脂の記載が省略されている。図1(b)は、半導体チップ2の構成を概略的に示す平面図である。図2は、半導体チップ2を示す斜視図である。半導体パッケージ1は、実施の形態1に係る半導体装置である。半導体チップ2は、パッケージ基板3に配置されている。パッケージ基板3の周縁部には、図1(a)に示すように、外側に伸びた複数のリード4が設けられ、半導体チップ2の周縁部には、複数の電極パッド2aが設けられている。電極パッド2aは、ワイヤ5によってリード4と接続されるポンディングパッドである。

10

【0011】

半導体チップ2は、図1(b)に示すように、メモリ2c、ロジック回路2d、アナログ回路2eおよびインターフェース回路2fが1つのチップに集積された大規模集積回路、いわゆるSoC(System on a Chip)である。メモリ2cは、半導体チップ2が取り扱うデータを記憶する不揮発性メモリであり、例えば、NANDフラッシュメモリである。ロジック回路2dは、デジタル信号を処理し、アナログ回路2eは、アナログ信号を処理する。インターフェース回路2fは、電極パッド2aを介した信号の送受信に加え、インターフェース回路2f、ロジック回路2dおよびアナログ回路2eへの電源の供給を実行する。

20

【0012】

メモリ2cの動作電源は、半導体チップ2の内部で生成され、インターフェース回路2f、ロジック回路2dおよびアナログ回路2eの動作電源とは異なる。このため、メモリ2cは、周辺回路から切り離して動作させることが可能である。

30

【0013】

半導体パッケージ1において、ワイヤ5によって電極パッド2aとリード4とが接続されたものが、外部端子である。外部端子には、電極パッド2aがインターフェース回路2fによってメモリ2cと接続されたものも含まれる。半導体チップ2には、パッケージ基板3と対向する第1の面と、その反対側の第2の面がある。図1(a)は、半導体チップ2を第2の面側から見たものである。半導体チップ2には、図2に示すように、電極パッド2aとは別に、電極パッド2bが設けられている。電極パッド2bは、インターフェース回路2fを介さずにメモリ2cに直接接続され、半導体チップ2におけるメモリ2cの上部に設けられたデータ読み出し用電極である。

【0014】

メモリ2cは、周辺回路から切り離して動作させることができるので、電極パッド2bを介してメモリ2cを直接動作させてデータを読み出すことが可能である。例えば、図1(a)において、破線の矢印Aで示すように、電源トラブルによって耐圧を超える高電圧が外部端子に印加されることで外部端子が破壊されたものとする。図1(a)において、太線の矢印BにX印を付して示すように、メモリ2cに記憶されたデータを、リード4を介して読み出すことができなくなる。

40

【0015】

これに対し、半導体チップ2は、図1(a)において太線の矢印Cで示すように、電極パッド2bを介してメモリ2cを直接動作させることで、メモリ2cからデータを読み出すことが可能である。従来の半導体装置においても、非通常状態になった場合に、半導体チップ2の内部に設けられたメモリからデータを読み出す、いわゆるデータの救済を行う

50

ものがあった。例えば、データを外部に引き出す外部端子の一つとして、データ読み出し専用の端子を設けた半導体装置がある。また、メモリに記憶されたデータを無線で外部に送信する通信回路を設けた半導体装置がある。

#### 【 0 0 1 6 】

しかしながら、データを外部に引き出す外部端子の一つとして、データ読み出し専用の端子を設けた場合、外部端子を介して接続された外部装置との間で発生した電源トラブルなどの不具合によって外部端子が破壊されることがある。この場合、データ読み出し専用の端子を介したデータ読み出しができなくなる。また、半導体装置にデータ読み出し専用端子を新たに追加する場合、外部端子の数が増加されるので、半導体装置の小型化が制限される。同様に、通信回路を設けた半導体装置においても、回路の追加に伴う面積増加によって小型化が制限される。10

#### 【 0 0 1 7 】

半導体パッケージ 1 は、メモリ 2 c に直接接続されて、半導体チップ 2 におけるメモリ 2 c の上部に設けられた電極パッド 2 b を備える。電極パッド 2 b は、通常、外部装置と接続される外部端子ではなく、外部装置との間で発生した不具合の影響を受けない。また、電極パッド 2 b は、メモリ 2 c の上部に設けられるので、電極の追加に伴う面積の増加がなく、半導体パッケージ 1 の小型化が可能である。

#### 【 0 0 1 8 】

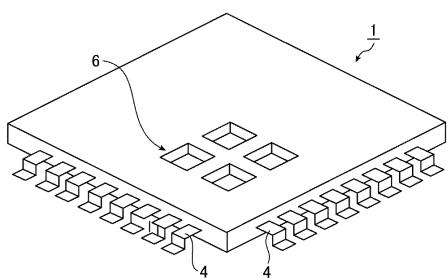

図 3 は、半導体パッケージ 1 を示す斜視図である。半導体パッケージ 1 は、封止樹脂によって半導体チップ 2 がモールドされた、いわゆる S i P ( S y s t e m i n P a c k a g e ) である。半導体パッケージ 1 において、外表面における電極パッド 2 b に対応する位置には、図 3 に示すように、凹部 6 が設けられる。凹部 6 は、半導体パッケージ 1 の外側から電極パッド 2 b の位置を示す電極指標部である。20

#### 【 0 0 1 9 】

図 4 は、半導体パッケージ 1 の構造を示す断面図である。図 4 ( a ) は、通常状態の半導体パッケージ 1 を示す断面図であり、図 4 ( b ) は、電極パッド 2 b を介して、メモリ 2 c からデータを読み出す際の半導体パッケージ 1 を示す断面図である。通常状態の半導体パッケージ 1 において、メモリ 2 c に記憶されたデータは、外部端子を介して読み出され、電極パッド 2 b は使用されない。このため、凹部 6 は、半導体パッケージ 1 の内部に水などが侵入しないように、図 4 ( a ) に示すように、電極パッド 2 b は露出しない程度の深さで形成されている。30

#### 【 0 0 2 0 】

半導体パッケージ 1 が非通常状態になり、メモリ 2 c からデータを救済する必要がある場合、凹部 6 は、電極パッド 2 b が露出するまで凹部 6 の底面が穿たれる。凹部 6 の底面を穿つ方法には、例えば、ドリルを用いて底面に穴を開ける方法があり、または、溶剤を用いて底面を溶かして電極パッド 2 b をパッケージ外部に露出させる方法がある。データの読み取り装置 1 0 0 が備えるプローブ針 1 0 1 は、図 4 ( b ) に示すように、凹部 6 を通して電極パッド 2 b と接触され、電極パッド 2 b を介して、メモリ 2 c に記憶されたデータが読み出される。

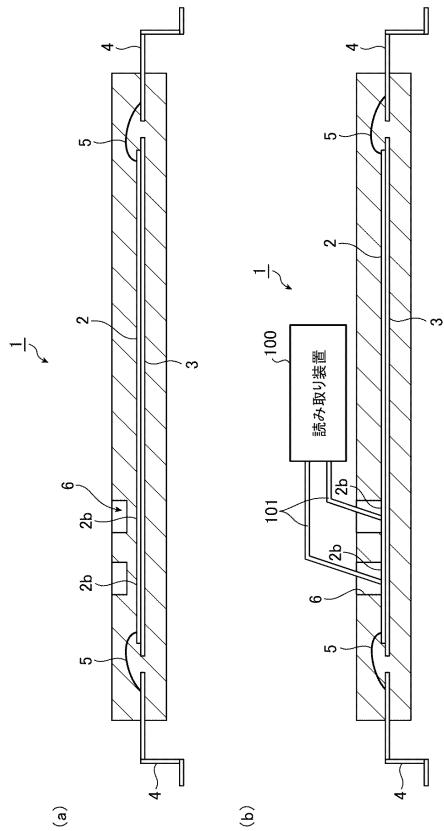

#### 【 0 0 2 1 】

図 5 は、半導体パッケージ 1 の変形例 1 である、半導体パッケージ 1 A を示す平面図である。半導体パッケージ 1 A において、外表面における電極パッド 2 b に対応する位置には、図 5 に示すように、マーク 6 A が設けられる。マーク 6 A は、半導体パッケージ 1 A の外側から電極パッド 2 b の位置を示す電極指標部であり、例えば、シルク印刷によって半導体パッケージ 1 A の外表面に形成されている。マーク 6 A が施された部分に穴を開けるか、または、溶剤を用いてマーク 6 A が施された部分の一部を溶かすことにより、電極パッド 2 b は、パッケージ外部に露出する。外部に露出された電極パッド 2 b は、プローブ針 1 0 1 に接触され、読み取り装置 1 0 0 は、電極パッド 2 b を介してメモリ 2 c に記憶されたデータを読み出す。40

#### 【 0 0 2 2 】

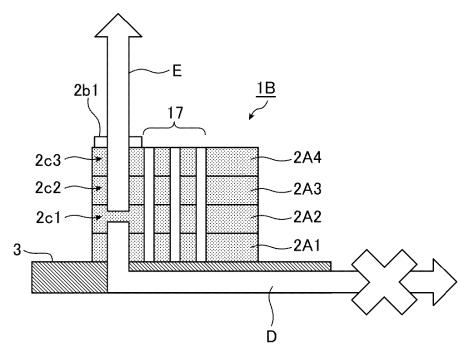

図6は、半導体パッケージ1の変形例2である半導体パッケージ1Bの構成を示す部分断面図であり、内部構成を示すために、パッケージの封止樹脂の記載が省略されている。半導体パッケージ1Bは、図6に示すように、パッケージ基板3上に、半導体チップ2A1、2A2、2A3および2A4が積層された構成を有している。半導体チップ2A1、2A2、2A3および2A4において、半導体チップ間の回路は、ピアホール17により電気的に接続される。ピアホール17は、半導体チップの積層方向に貫通した貫通電極である。

#### 【0023】

パッケージ基板3上に積層された半導体チップ2A1には、半導体チップ2A2、2A3および2A4が備える回路を制御するコントローラとして機能するロジック回路が設けられている。また、半導体チップ2A2、2A3および2A4には、メモリ2c1、2c2および2c3が設けられている。メモリ2c1、2c2および2c3にデータを記憶することができるので、半導体パッケージ1Bは、大容量のデータを保存することが可能である。

10

#### 【0024】

半導体パッケージ1Bは、半導体チップ2A1に設けられた電極パッド2aと、パッケージ基板3に設けられたリード4とが、ワイヤ5によって接続された外部端子を備える。半導体チップ2A4は、外部端子とは別に、電極パッド2b1を備えている。電極パッド2b1は、メモリ2c3に直接接続されており、パッケージ基板3から最も離れた半導体チップ2A4におけるメモリ2c3の上部に設けられたデータ読み出し用電極である。

20

#### 【0025】

メモリ2c1、2c2および2c3は、ピアホール17によって接続されており、半導体パッケージ1Bが通常状態である場合、メモリ2c1、2c2および2c3に記憶されたデータは、矢印Dに示すように、外部端子を介して外部装置に読み出される。外部装置との不具合によって外部端子が破壊された場合、矢印DにX印を付して示すように、外部端子を介したデータ読み出しができなくなる。これに対し、半導体パッケージ1Bでは、矢印Eに示すように、電極パッド2b1を介して、メモリ2c1、2c2および2c3に記憶されたデータが読み出すことが可能である。

#### 【0026】

なお、図3には電極指標部が凹部6である場合を示したが、電極指標部は、メモリ2cの位置を示す凸部であってもよい。また、図5において、マーク6Aが矩形のマークである場合を示したが、電極指標部は、矩形以外の形状のマークであってもよい。電極指標部は、その下部に電極パッド2bがあることが外側から認識可能であればよく、例えば、円形であってもよいし、X印であってもよい。

30

#### 【0027】

また、図3の説明において、凹部6の底面を穿って電極パッド2bを外部に露出させる場合を示したが、凹部6は、電極パッド2bが露出するまで封止樹脂が貫通された孔部であってもよい。この場合、凹部6の開口部は、シール部材によって塞がれる。シール部材は、通常、凹部6の開口部を覆うように強固に接着するが、一定の処理を施すことにより凹部6の開口部から容易に剥がれる部材が好ましい。例えば、接着剤に紫外線硬化樹脂を含むシール部材は、紫外線を照射することにより接着剤が硬化収縮して容易に剥がすことができる。

40

#### 【0028】

以上のように、実施の形態1に係る半導体パッケージ1は、データを記憶するメモリ2cを有する半導体チップ2と、メモリ2cに直接接続され、半導体チップ2におけるメモリ2cの上部に設けられた電極パッド2bとを備える。電極パッド2bは、通常、外部装置と接続される外部端子ではなく、外部装置との間で発生した不具合の影響を受けない。このため、外部端子が非道通状態になってもメモリ2cからデータを読み出すことができる。さらに、電極パッド2bは、メモリ2cの上部に設けられるので、電極の追加に伴う面積の増加がなく、半導体パッケージ1の小型化が可能である。

50

**【0029】**

なお、実施の形態の任意の構成要素の変形もしくは実施の形態の任意の構成要素の省略が可能である。

**【符号の説明】****【0030】**

1 , 1 A , 1 B 半導体パッケージ、 2 , 2 A 1 , 2 A 2 , 2 A 3 , 2 A 4 半導体チップ、 2 a , 2 b , 2 b 1 電極パッド、 2 c , 2 c 1 , 2 c 2 , 2 c 3 メモリ、 2 d 口ジック回路、 2 e アナログ回路、 2 f インタフェース回路、 3 パッケージ基板、 4 リード、 5 ワイヤ、 6 凹部、 6 A マーク、 17 ピアホール、 100 読み取り装置、 101 プローブ針。

10

20

30

40

50

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図 5】

【図 6】

10

20

30

40

50

---

フロントページの続き

## (51)国際特許分類

|                         | F I    |        |       |

|-------------------------|--------|--------|-------|

| H 01 L 23/28 (2006.01)  | H 01 L | 27/04  | U     |

| H 01 L 21/8234(2006.01) | H 01 L | 27/088 | E     |

| H 01 L 27/088(2006.01)  | H 01 L | 27/088 | H     |

| H 01 L 21/336(2006.01)  | H 01 L | 29/78  | 3 7 1 |

| H 01 L 29/788(2006.01)  | H 10 B | 41/27  |       |

| H 01 L 29/792(2006.01)  | H 10 B | 43/27  |       |

| H 10 B 41/27 (2023.01)  | H 10 B | 80/00  |       |

| H 10 B 43/27 (2023.01)  |        |        |       |

| H 10 B 80/00 (2023.01)  |        |        |       |

## (56)参考文献

特開2010-249824 (JP, A)

特開2011-100898 (JP, A)

特開2006-157047 (JP, A)

特開2013-131533 (JP, A)

## (58)調査した分野 (Int.Cl., DB名)

H 01 L 21 / 3205

H 01 L 21 / 336

H 01 L 21 / 768

H 01 L 21 / 822

H 01 L 21 / 8234

H 01 L 23 / 28

H 01 L 23 / 522

H 01 L 27 / 04

H 01 L 27 / 088

H 10 B 41 / 27

H 10 B 43 / 27