(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第4167727号 (P4167727)

(45) 発行日 平成20年10月22日(2008.10.22)

(24) 登録日 平成20年8月8日 (2008.8.8)

(51) Int.Cl. F 1

HO1L 21/8242 (2006.01)

HO1L 27/10 621C

HO1L 27/108 (2006.01)

HO1L 27/10 651

HO1L 27/10 681F

請求項の数 3 (全 33 頁)

(21) 出願番号 特願平9-519581

(86) (22) 出願日 平成8年11月14日 (1996.11.14)

(86) 国際出願番号 PCT/JP1996/003343

(87) 国際公開番号 W01997/019468

(87) 国際公開日 平成9年5月29日 (1997.5.29) 審査請求日 平成14年7月8日 (2002.7.8)

(31) 優先権主張番号 特願平7-300960

(32) 優先日 平成7年11月20日 (1995.11.20)

(33) 優先権主張国 日本国 (JP) (31) 優先権主張番号 特願平7-302460

(32) 優先日 平成7年11月21日 (1995.11.21)

(33) 優先権主張国 日本国(JP) (31) 優先権主張番号 特願平7-340368

(32) 優先日 平成7年12月27日 (1995.12.27)

(33) 優先権主張国 日本国(JP)

||(73)特許権者

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

(74) 代理人

ポレール特許業務法人

(74) 代理人

弁理士 高橋 明夫

|(72) 発明者 木村 紳一郎

東京都国立市谷保6200

||(72)発明者 山中 俊明

埼玉県入間市春日町2-12-2-301

(72) 発明者 伊藤 清男

東京都東久留米市学園町2-17-6

最終頁に続く

# (54) 【発明の名称】半導体記憶装置

# (57)【特許請求の範囲】

### 【請求項1】

第 1 の電界効果トランジスタとキャパシタが形成されるメモリセル領域と第 2 の電界効果トランジスタが形成される周辺回路領域を有する半導体記憶装置であって、

半導体基板と、

半導体基板の上方に形成された第1の絶縁膜と、

前記第1の絶縁膜を貫通する第1のコンタクト孔の内部に<u>のみ</u>形成され、<u>埋め込まれる</u>前記第1の電界効果トランジスタと電気的に接続された第1のプラグと、

前記第1の絶縁摸上に形成された第2の絶縁膜と、

前記第2の絶縁膜上に形成された第3の絶縁膜と、

前記第2の絶縁膜と前記第3の絶縁膜からなる積層膜を貫通して形成され、その底部において前記第1のプラグの上面が露出しているトレンチと、

前記トレンチの底部及び内壁上に形成された蓄積電極と、

前記蓄積電極上に形成されたキャパシタ絶縁膜と、

前記キャパシタ絶縁膜上に形成されたプレート電極と、

前記第2の絶縁膜を貫通する第2のコンタクト孔の内部に<u>のみ</u>形成され<u>、埋め込まれる</u>第2のプラグと、

前記第3の絶縁膜を貫通する第3のコンタクト孔の内部に<u>のみ</u>形成され<u>て埋め込まれ、</u>その下面が前記第2の<u>プラグの</u>上面と接触した第3のプラグと、

前記第3の絶縁膜の上方に形成された第1の配線を有し、

前記キャパシタ絶縁<u>膜と</u>、前記キャパシタ絶縁膜を挟んで対向する前記蓄積電極及び前記 プレート電極とにより前記キャパシタが構成され、前記キャパシタは前記トレンチ内に形 成され、

前記第1の配線と前記第2の電界効果トランジスタが、前記第2のプラグ及び前記第3の プラグを介して電気的に接続されていることを特徴とする半導体記憶装置。

#### 【請求項2】

前記蓄積電極の前記キャパシタ側の表面には凹凸が形成されていることを特徴とする請求項 1 に記載の半導体記憶装置。

## 【請求項3】

前記キャパシタ絶縁膜は、<u>シリコン</u>酸化膜と<u>シリコンナイトライド</u>膜の積層膜、<u>シリコン</u>酸化膜と五酸化タンタル膜の積層膜、<u>シリコンナイトライド</u>膜と五酸化タンタル膜の積層膜、<u>シリコン</u>酸化膜と<u>シリコンナイトライド</u>膜と五酸化タンタル膜の積層膜、BST膜及びPZT膜からなる群から選択された膜であることを特徴とする請求項1に記載の半導体記憶装置。

#### 【発明の詳細な説明】

#### 〔技術分野〕

本発明は半導体記憶装置およびその製造方法に関し、詳しくは、微細化の可能な半導体記憶装置およびこのような半導体記憶装置を容易かつ高い精度で形成することのできる半導体記憶装置の製造方法に関する。

#### 〔背景技術〕

パーソナルコンピュータやワークステーション、さらには、メインフレームコンピュータなどで大量に使用されている半導体記憶装置は、一つのスイッチ用トランジスタと一つのキャパシタを最小単位とする、ダイナミック・ランダム・アクセス・メモリ(Dynamic Random Access Memory:以下、DRAMと略記する)である。このDRAMは、従来、集積度が3年に4倍という割合で向上してきており、現在は、最小寸法が0.35 $\mu$ mという次世代の微細加工技術を用いて生産される、64メガビットDRAMの量産化に向けた開発が進行している。

従来、半導体記憶装置の高集積化は、素子寸法を小さくすることによって達成されてきたが、微細化にともなってキャパシタの面積が減少するため、情報としてキャパシタに蓄積することのできる電荷量が減少する。その結果、信号対雑音比の低下や、アルファ線の分割による信号反転等の問題が生じて信頼性が低下するので、信頼性を維持するためには、十分な蓄積電荷量を確保することが不可欠であり、半導体記憶装置の最大の課題である。キャパシタに蓄積される電荷量は、キャパシタの容量とキャパシタ絶縁膜の比誘電率に比例である。まり、キャパシタの関厚に反比例する。そのため、メモリ素子の比別でありにより、次細化にともなうキャパシタの面積減少による蓄積容量の減少を防ぐために、4 ガビットDRAM以降は、キャパシタの一部をスイッチ用トランジスタや素子分離酸化関シタトDRAM以降は、キャパシタの一部をスイッチ用トランジスタや素子分離酸化関シタトDRAM以降は、キャパシタが使われている。これらの構造を有するキャパシタを用いることによって、6 4 メガビットが実現可能になった。

しかし、メモリセルの面積がこれまでのトレンドに従って、前世代の1/3という割合で縮小を続けると、上記積層容量型のキャパシタやトレンチ容量型のキャパシタのような立体化されたキャパシタを用いたメモリセルでも、キャパシタの面積減少を完全に補償することができず、必要な容量の確保が困難になる。

この問題を解決するため、"王冠型"と呼ばれる立体型蓄積キャパシタが提案されている。この王冠型蓄積キャパシタは、第2図に示したように、電極19を上に凹な形状(王冠型)にして、その内壁と外壁をキャパシタの電極として利用した立体型の蓄積キャパシタである。第2図において、記号1は半導体基板、2は素子間分離酸化膜、3はトランジスタのゲート酸化膜、4はスイッチ用トランジスタのゲート電極、5、5 は基板とは導電型の異なる拡散層領域、6は層間絶縁膜、7は拡散層5 に接続しているビット線、8は

10

20

30

40

層間絶縁膜、13は拡散層5とキャパシタの下部電極を接続する金属、19はキャパシタの下部電極、20はキャパシタ絶縁膜、21はキャパシタのプレート電極、22は層間絶縁膜、23は基板の拡散層に接続する配線、24は層間絶縁膜、25は最上層の配線を、それぞれ示す。

DRAMのキャパシタを、このような王冠型のキャパシタ電極 1 9 を用いた構造とすることによって、蓄積容量は従来より増大できるが、この構造を実現するには、極めて複雑な工程を必要とするばかりでなく、高い段差が生ずるという障害が生ずる。

すなわち、第2図に示したように、メモリセル部(第2図の左側部分)とその周辺のトランジスタ部(第2図の右側部分)の間には、上記王冠型の電極19に起因する大きな段差が生じ、そのため、この段差の上に配置される配線23の形成が困難になる。この理由は、所定のパターンを有する配線23の形成に用いられる光リソグラフィにおいては、使用される縮小投影露光装置の焦点深度が浅く、焦点裕度(焦点が合う範囲)が小さいため、段差の上部と下部の両方に最適な焦点を結ばせることは困難であるためである。しかも、パターンの寸法が小さくなるほど、焦点裕度が小さくなって、最適な焦点が結ばれる範囲がさらに狭くなってしまうためである。

このような段差に起因する配線パターン形成の問題を解決するため、CMP (Chemical Mechanical Polishing)法を用いて基板表面を平坦化する方法が提案されており、ロジックLSIの多層配線の層間絶縁膜の平坦化などに、既に適用されている。

しかし、この C M P 法も、高さが 1 μ m 近い上記王冠型電極 1 9 が既に形成されている基板に適用するのは、下記理由から困難である。第 1 の理由は、非常に薄いキャパシタ絶縁膜が形成されているキャパシタに、力を加えて機械的研磨を行うと、キャパシタ絶縁膜にピンホールや亀裂などが生じて絶縁不良を招く可能性が高いことである。第 2 の理由は、高い段差を有するキャパシタを酸化膜中に埋め込むためには、少なくとも、段差の倍の厚さを有する酸化膜を形成しなければならないが、厚い酸化膜は内部応力が大きく、この大きな内部応力によって、上記第 1 の理由の場合と同様に、キャパシタ絶縁膜の絶縁不良が起こるためである。

製造工程の初期の段階において、メモリセルアレー部のシリコン基板の表面を低くする方法が、特開昭 6 3 - 2 6 6 8 6 6 に提案されているが、段差が大きい場合に適用するのは困難である。

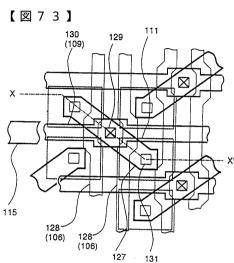

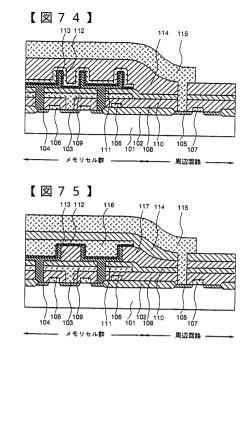

上記王冠型の蓄積キャパシタを有するメモリセルに関しては、特開昭62-48062および特開昭62-1281268に記載されている。このメモリセルの平面配置を第73図に、また第73図のX-X′断面および周辺回路部分の要部の断面を第74図に示した。また、第75図に示した断面構造は、トレンチ内の蓄積電極の内面をキャパシタとして利用した従来の例である。この構造は、王冠型のキャパシタに比較して製造が容易であるという利点を有している。

第73図、第74図および第75図において、記号101はシリコン基板、102はフールド酸化膜、103、104、105ははソースもしくはドレインである高濃度不純物領、106、107はゲート電極、111は蓄積電極、112はキャパシタの誘電体、113はプレート電極、114はシリコン酸化膜、127は活性領域、128はワード線、130はデータ線、129はコンタクト孔、131は接続孔を、それぞれ表す。第74図および第75図から明らかなように、蓄積キャパシタがシリコン基板上に形成されたこれら従来の半導体記憶装置は、メモリセル部と周辺回路の間に大きな段差が存在していた。蓄積容量部が基板の内部に形成されたトレンチ容量型のセルでは、高い段差が基板上にできることはない。また、基板に形成されるトレンチを深くすることによって蓄積容量を大きくできるので、セル面積の縮小にともなう蓄積容量の減少も抑制できる。

しかし、トレンチを形成できる領域の大きさが限られているため、アスペクト比が 4 0 程度という、極めて深く、かつ幅が狭いトレンチを形成する必要がある。さらに、キャパシタの基板内部に埋め込まれる電極とスイッチング用トランジスタの拡散層を、基板の内部で接続しなければならないなど、プロセス上の問題も多く、実用は困難である。

比誘電率が大きい材料、例えば、強誘電体であるPZTなどをキャパシタ絶縁膜に用いれ

10

20

30

40

20

30

40

50

ば、蓄積容量の形状を上記のような複雑な形状にすることなしに、大きな蓄積容量を実現 することが可能である。

しかし、比誘電率が大きいPZTなどをキャパシタ絶縁膜として用いるためには、キャパシタ電極には白金など貴金属の膜を用いねばならない。これら白金など貴金属は、シリコンにとっては汚染源であり、素子の特性を低下させるばかりでなく、従来のホトエッチングによって所定の形状に加工するのが困難である。

さらに、上記PZTなどからなる絶縁膜自体が、ほぼ400 以上の熱処理に耐えられない、長期信頼性に関しては不明な点が多いなど問題が多く、実用化への見通しはたっていない。

データ線上に王冠型のキャパシタを設けた従来のメモリセルおよび隣接する周辺回路領域のMOSFET部を第91図に示した。第91図において、メモリセル領域のMOSFETは、ゲート絶縁膜303、ゲート電極304および高濃度 n 型不純物領域ワード線とデータ線の上部で306、307からなり、このMOSFETには、多結晶シリコンから形成された王冠型キャパシタの蓄積電極317が、ワード線(ゲート電極304)とデータ線(配線電極310)の間の隙間において高濃度 n 型不純物領域307の上に形成された開口部を介して、接続されている。さらに、この蓄積電極317上にはキャパシタ誘電体膜318が形成されており、その上部にはプレート電極319が設けられている。

上記蓄積電極 3 1 7 の形状は筒状になっており、平面部分だけでなく垂直部分の内面および外壁も利用して、キャパシタの有効面積が増加されている。また、データ線上に蓄積電極を設けることによって、キャパシタの有効な面積を最大限に大きくすることができ、さらに、垂直部分の長さを長くする、すなわち筒状の蓄積電極の高さを高くすることによって、容易にキャパシタの静電容量を増加することができる。

こような円筒型キャパシタを有する半導体記憶装置の製造方法を簡単に説明する。まず、 単結晶シリコン基板301上に素子間を絶縁分離するためのフィールド酸化膜302を成 長させ、MOSFETのゲート酸化膜303を形成する。次に、ゲート電極304として 不純物を高濃度に含む多結晶シリコン膜を形成し、それ所定の形状にパターニングした後 イオン打ち込み法を用いて、MOSFETのソース、ドレイン領域となる高濃度n型不 純物領域306、307、308を単結晶シリコン基板301に自己整合で形成する。次 に、シリコン酸化膜309を形成した後、メモリセル領域のMOSFETの高濃度n型不 純物領域106に開口部(図示せず)を形成し、データ線310として不純物を高濃度に 含む多結晶シリコン膜およびタングステンシリサイド膜を順次形成して、所定の形状にパ ターニングする。次に、シリコン酸化膜311を形成した後、メモリセル領域のMOSF E T のソース若しくはドレインである高濃度 n 型不純物領域 3 0 7 上に開口部を形成し、 多結晶シリコン膜とシリコン酸化膜を順次形成し、所定の形状にパターニングした後、さ らに多結晶シリコン膜を形成し、異方性のドライエッチングを行って、平坦部の露出され た多結晶シリコン膜を異方性エッチングして除去することにより、上記シリコン酸化膜の 側壁に多結晶シリコン膜を残存させ、王冠状の蓄積電極317を形成する。次に、キャパ シタ誘電体膜318を形成した後、さらにプレート電極119となる多結晶シリコン膜を 形成し、所定の形状にをパターニングする。最後に、層間絶縁膜であるシリコン酸化膜 1 16と金属配線115であるアルミニウム配線を形成し、周辺回路のMOSFETとメモ リセルが製造される。

上記のように、DRAMの集積度をさらに高くするためには、上記従来の立体化セルでは 対応が困難であり、上記問題を解決できる半導体記憶装置が強く要望されている。

なお、従来のDRAMに関しては、例えば実開昭55-178894、特開昭56-58253、特開昭56-58255、特開昭56-58255、特開昭57-112066 、特開昭59-231351、特開昭62-128168、特開昭63-293967、 特開昭59-231851、特開平1-137666、特開平1-179449、特開平3-214670、特開平5-291526、特開昭59-82761、特開昭62-213273に記載されている。

なお、本明細書では、例えば第91図に示したように、蓄積電極の断面形状が上に凹型で

あり、このような蓄積電極の内面および外面上にキャパシタ絶縁膜とプレート電極が形成されたキャパシタを王冠型キャパシタと称し、ドレンチの内面上に蓄積電極、キャパシタ 絶縁膜およびプレート電極が形成されたキャパシタをトレンチキャパシタと称する。

#### [発明の開示]

本発明の目的は、上記従来の立体型のメモリセルの有する問題を解決し、さらに微細な半 導体記憶装置およびその製造方法を提供することである。

本発明の他の目的は、十分大きな蓄積容量を確保することのできるキャパシタを有する半導体記憶装置およびその製造方法を提供することである。

本発明のさらに他の目的は、基板にトレンチを形成することなしに、十分大きな蓄積容量を得ることができる半導体記憶装置およびその製造方法を提供することである。

本発明のさらに他の目的は、メモリセル部と周辺回路部の間に大きな段差が存在せず、大きな蓄積容量を有する半導体記憶装置およびその製造方法を提供することである。

上記目的を達成するため、本発明は、基板上に積層して形成された複数の絶縁膜を貫通するトレンチを形成し、このトレンチを用いてキャパシタを形成するものである。

上記複数の絶縁膜の下にはさらに他の複数の絶縁膜が設けられ、これら他の複数の絶縁膜には複数の配線層が形成されている。また、上記キャパシタの上にはさらに他の絶縁膜が形成されており、他の配線層がその上に形成されている。最上層の絶縁膜上に取り出す必要がない配線は、キャパシタの下部に形成された上記複数の配線層によって行われ、必要最小限の配線のみが、複数の絶縁膜を貫通する接続プラグを介してキャパシタの下部の配線層から最上層の絶縁膜上に引き出される。そのため、配線の形成には微細加工を行う必要がなく、配線の密度も低くてよいので、配線の形成は極めて容易である。

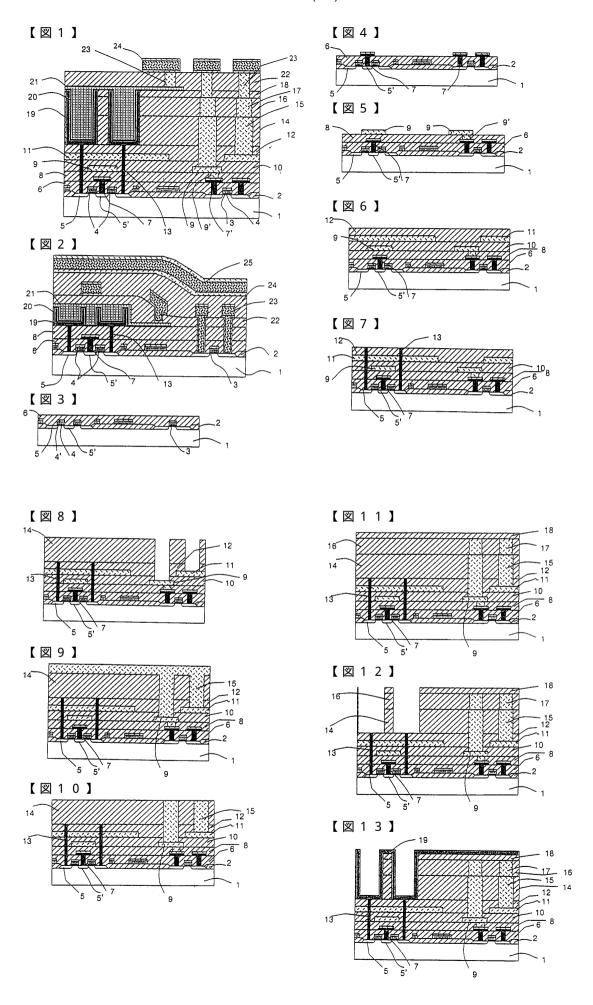

第1図を用いて本発明をさらに詳細に説明する。第1図に示したように、半導体基板1上には、メモリセルのスイッチ用トランジスタであるMOSFET(Metal Oxide Semicond uctor Field Effect Transistor)につながる、ワード線4(MOSFETのゲート電極) および電荷を供給したり引き出したりするためのビット線7が形成され、さらに複数の絶縁膜6、8、10、12、14、16、18が積層して形成されて、表面が平坦化されている。

上記絶縁膜14、16、18を貫通してトレンチが形成され、このトレンチの内部に下部電極19、キャパシタ絶縁膜20およびプレート電極21から構成されるキャパシタが形成されている。

ワード線 4 やビット線 7 の上に厚い絶縁膜が形成されていると、ワード線 4 やビット線 7 への電気的な接続は、この厚い絶縁膜を貫通する接続プラグを介して行わねばならず、コンタクト孔の形成や金属の埋込などが困難である。しかし、本発明では、トレンチキャパシタの下部電極 1 9 とワード線 4 、ビット線 7 の間には、複数層の配線 9 、 1 1 が設けられ、これら複数層の配線 9 、 1 1 がワード線を選択するためのワード母線や、ビット線を選択するためのセレクト線として使用されている。そのため、基板の最上層まで引き上げる必要のない配線は、このような埋込配線で済ますことができ、上記厚い絶縁膜を貫通する接続プラグは不要である。

上記複数層の配線 9、 1 1 の上部にキャパシタが作られ、 8 0 0 程度の熱処理が行われるので、配線 9、 1 1 の材料としては、この熱処理に耐えられる、タングステンやシリサイドを使用することが好ましい。銅は低抵抗という点は好ましいが、熱処理温度は 5 0 0 以下でなければならない。キャパシタ絶縁膜として B S T や P Z T などの高誘電率の誘電体膜を使う場合には、キャパシタ自体の形成温度が 4 0 0 以下であるので、配線材料として銅を用いることができる。

第1図では、埋込まれた複数層の配線 9、11は、メモリセルのワード線 4 やビット線 7 の他にも、周辺回路のトランジスタの配線の一部としても使用されている。また、ビット線 7 と同じ層の配線 7 'を介して、拡散層 5、5 'と配線 9 'の間が接続されているが、配線 9 'を拡散層 5、5 'に直接接続させてもよい。ただしその場合には、拡散層 5、5 'と配線 9 'の同の反応を防ぐために、配線 9 'の一部をバリア金属にする必要がある。キャパシタは、実質的に上記トレンチの内側のみに形成される。これは、キャパシタの形

10

20

30

40

成工程を簡略化するためである。キャパシタの下部電極19は、不純物を高濃度で含む多結晶シリコン膜からなり、この下部電極19は、接続用の多結晶シリコン13を介して上記MOSFETの拡散層5に接続されている。

キャパシタ絶縁膜20としては、酸化シリコン膜と窒化膜シリコン膜の積層膜、酸化シリコン膜と五酸化タンタル膜の積層膜、窒化シリコン膜と五酸化タンタル膜の積層膜、酸化シリコン膜と窒化膜シリコンと五酸化タンタル膜の積層膜、BSTやPZTなどの強誘電体膜など、周知の各種誘電体膜を使用できる。ただし、BSTやPZTを使う際には、下部電極19やプレート電極21には、白金などの貴金属を使用する必要がある。また、下部電極19の表面積を増加させるために、表面に凹凸を形成してもよい。

トレンチの深さは、2 μ m 程度にするのが好ましいが、このようにトレンチが深くなると、埋込配線9、1 1 と最上層の配線2 3 の間の距離が大きくなり、アスペクト比が極めて大きな接続孔の形成およびこのような接続孔への金属の充填が必要であるため、両者の間を接続するための接続プラグを形成するのがが困難になる。

しかし、本発明では、第1図に示したように、トレンチは1枚の厚い絶縁膜ではなく、積層された複数の絶縁膜14、16、18を貫通して形成されている。そのため、各絶縁膜14、16、18を形成する際に、それぞれ接続孔の形成と接続用の金属の充填を行うことができる。このようにすることによって、上記アスペクト比が極めて大きな接続孔の形成およびこのような接続孔への金属の充填を行う必要はなく、下部電極19と拡散層5の間を接続する金属13は容易に形成できる。しかも、上記のように、最上の配線層にまで引き上げなければならない配線の数は多くないので、これら最上層までの引上げに用いられる接続プラグは、あまり高い寸法精度は必要ない。これは、埋込配線を形成したことによって得られた本発明の利点の一つである。

なお、第1図において、1は半導体基板、2は素子間分離酸化膜、3はMOSFETのゲート酸化膜、4はMOSFETのゲート電極(メモリセルではワード線)、5、5′はMOSFETの拡散層、6は層間絶縁膜、7はビット線、7′は周辺MOSFETの拡散層と配線を接続する中間層、8、10、12、16、18、22は層間絶縁膜、9、11は埋込配線、14は絶縁膜、15、17、23は接続プラグ、24は最上層の配線を、それぞれ表す。

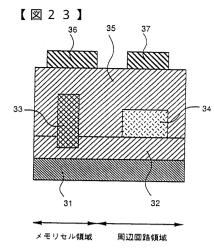

また、上記段差の発生は、下記のようにして効果的に防止される。すなわち、、第23図に模試的に示したように、メモリセル領域に形成された立体的なキャパシタ33と周辺回路領域の配線層34を、MOSFETが形成されたシリコン基板31の上に形成された絶縁膜32の上、もしくは絶縁膜32の上面がキャパシタ33の側部に接するようにそれぞれ設け、これら配線層34上とキャパシタ33を、表面が平坦な絶縁膜35によって覆い、その上に微細なメモリセルアレー内配線36および微細な周辺回路内配線37を設ける

このようにすれば、高さが高い立体的なキャパシタ33が形成されている絶縁膜32の位置に周辺回路の配線層34が形成されているため、メモリセル内のキャパシタによって生じる標高差(段差)が、配線層34によって低減される。そのため、表面が平坦な絶縁膜35を形成してキャパシタや配線層34を覆っても、周辺回路部においてスルーホールやコンタクトホールの深さが深くなることはなく、スルーホールやコンタクトホール内での配線の断線を生ずることなしに、絶縁膜35上に微細な配線36、37を容易に形成できる。

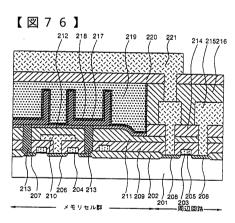

さらに、本発明においては、周辺回路領域における第1の導電膜からなる配線層が、第1の絶縁膜上に設けられ、さらにその上に第2の絶縁膜が設けられる。これら第1および第2の絶縁膜の所定部分を除去して形成された凹部内に王冠型キャパシタが形成され、埋設される。この場合、例えば第76図に示したように、プレート電極219の上面を平坦にすることができ、プレート電極219への電圧の印加をプレート電極219の上部から行うことができる。

#### 【図面の簡単な説明】

第1図は本発明の半導体記憶装置の断面図、

10

20

30

```

第2図は従来の半導体記憶装置の断面図、

第3図は本発明の半導体記憶装置の製造方法を示す図、

第4図は本発明の半導体記憶装置の製造方法を示す図、

第5図は本発明の半導体記憶装置の製造方法を示す図、

第6図は本発明の半導体記憶装置の製造方法を示す図、

第7図は本発明の半導体記憶装置の製造方法を示す図、

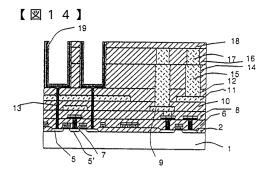

第8図は本発明の半導体記憶装置の製造方法を示す図、

第9図は本発明の半導体記憶装置の製造方法を示す図、

第10図は本発明の半導体記憶装置の製造方法を示す図、

10

第11図は本発明の半導体記憶装置の製造方法を示す図、

第12図は本発明の半導体記憶装置の製造方法を示す図、

第13図は本発明の半導体記憶装置の製造方法を示す図、

第14図は本発明の半導体記憶装置の製造方法を示す図、

第15図は本発明の半導体記憶装置の製造方法を示す図、

第16図は本発明の半導体記憶装置の製造方法を示す図、

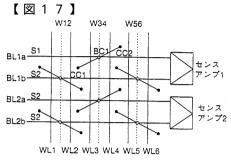

第17図は本発明の実施例2を説明するための概念図、

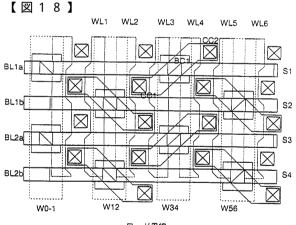

第18図は本発明の実施例2を示すパターン配置図、

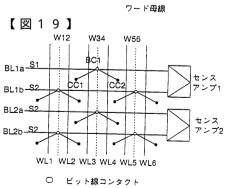

第19図は本発明の実施例3を説明するための概念図、

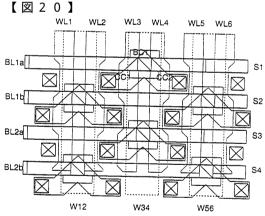

第20図は本発明の実施例3を示すパターン配置図、

20

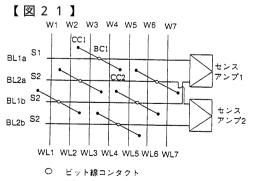

第21図は、本発明の実施例4を説明するための概念図、

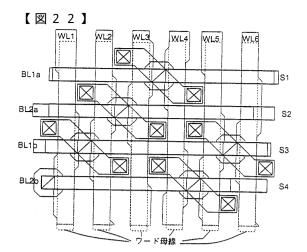

第22図は本発明の実施例4を示すパターン配置図、

第23図は本発明の構成を説明するためのの断面図、

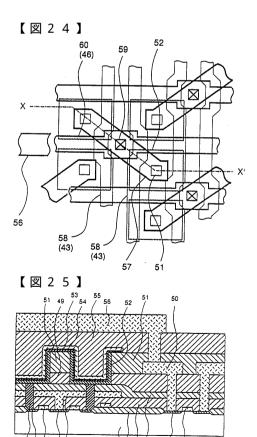

第24図は本発明の実施例5を示す平面図、

第25図は本発明の実施例5を示す断面図、

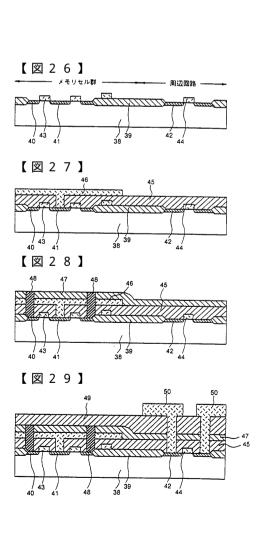

第26図は本発明の実施例5を示す工程図、

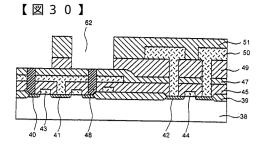

第27図は本発明の実施例5を示す工程図、

第28図は本発明の実施例5を示す工程図、

第29図は本発明の実施例5を示す工程図、

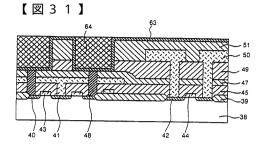

第30図は本発明の実施例5を示す工程図、

30

第31図は本発明の実施例5を示す工程図、

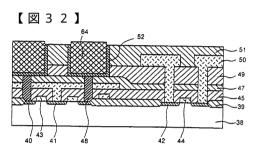

第32図は本発明の実施例5を示す工程図、

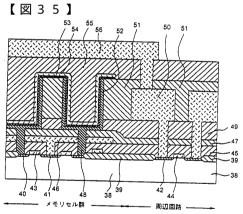

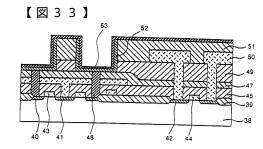

第33図は本発明の実施例5を示す工程図、

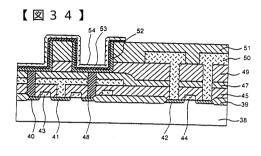

第34図は本発明の実施例5を示す工程図、

第35図は本発明の実施例5を示す断面図、

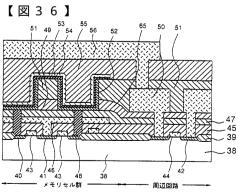

第36図は本発明の実施例5を示す断面図、

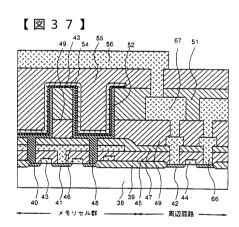

第37図は本発明の実施例5を示す断面図、

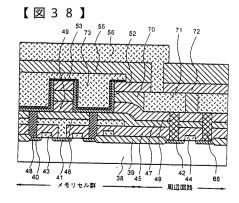

第38図は本発明の実施例6を示す断面図、

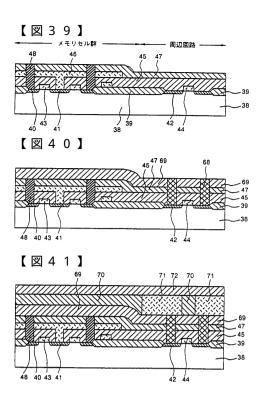

第39図は本発明の実施例6を示す工程図、

第40図は本発明の実施例6を示す工程図、

40

第41図は本発明の実施例6を示す工程図、

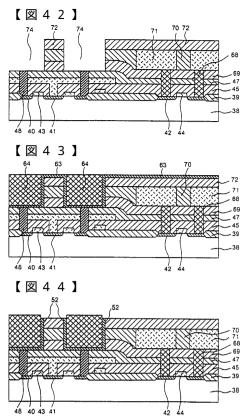

第42図は本発明の実施例6を示す工程図、

第43図は本発明の実施例6を示す工程図、

第44図は本発明の実施例6を示す工程図、

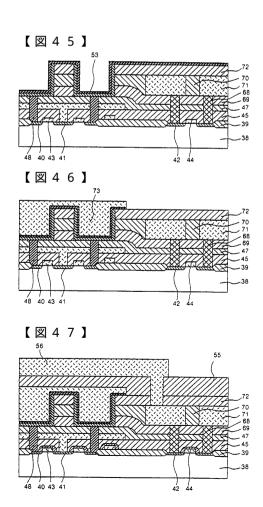

第45図は本発明の実施例6を示す工程図、

第46図は本発明の実施例6を示す工程図、

第47図は本発明の実施例6を示す工程図、

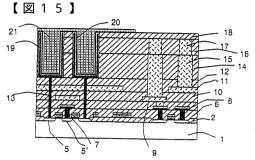

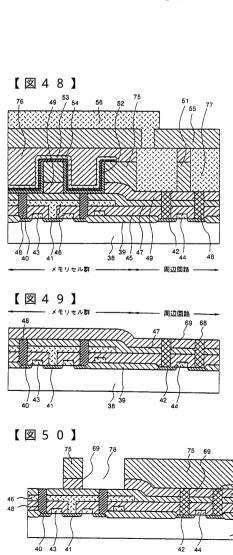

第48図は本発明の実施例7を示す断面図、

第49図は本発明の実施例7を示す工程図、

第50図は本発明の実施例7を示す工程図、

50

第51図は本発明の実施例7を示す工程図、

```

```

第52図は本発明の実施例7を示す工程図、

第53図は本発明の実施例7を示す工程図、

第54図は本発明の実施例7を示す工程図、

第55図は本発明の実施例7を示す工程図、

第56図は本発明の実施例7を示す工程図、

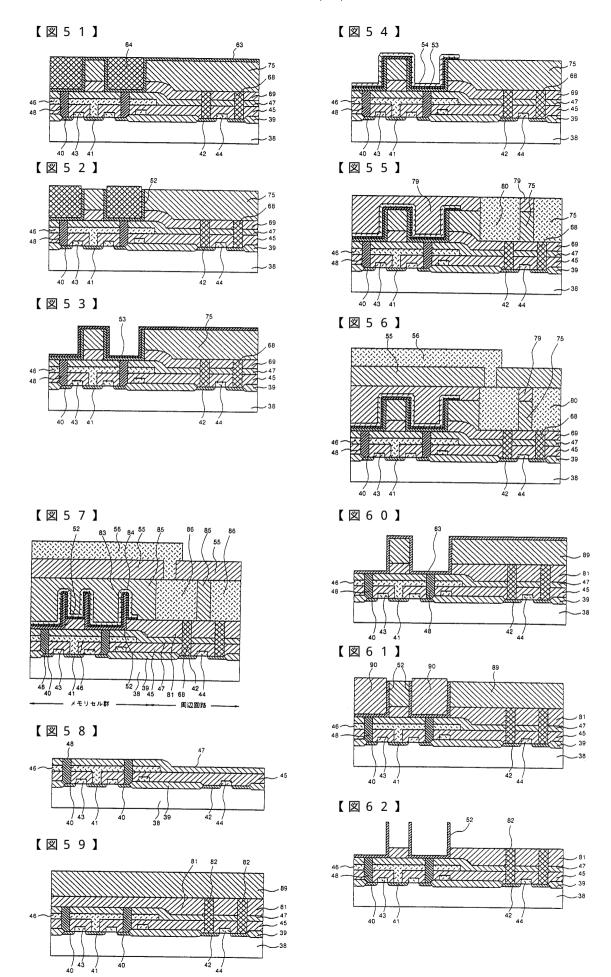

第57図は本発明の実施例8を示す断面図、

第58図は本発明の実施例8を示す断面図、

第59図は本発明の実施例8を示す断面図、

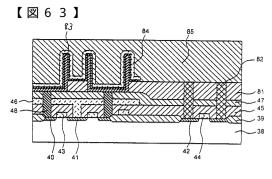

第60図は本発明の実施例8を示す断面図、

10

第61図は本発明の実施例8を示す断面図、

第62図は本発明の実施例8を示す断面図、

第63図は本発明の実施例8を示す断面図、

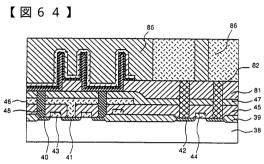

第64図は本発明の実施例8を示す断面図、

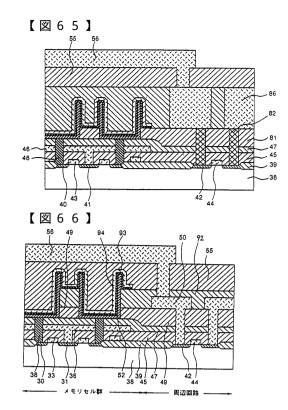

第65図は本発明の実施例8を示す断面図、

第66図は本発明の実施例9を示す断面図、

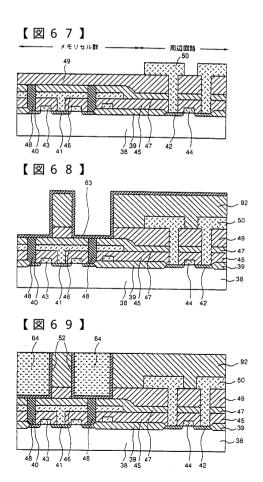

第67図は本発明の実施例9を示す工程図、

第68図は本発明の実施例9を示す工程図、

第69図は本発明の実施例9を示す工程図、

第70図は本発明の実施例9を示す工程図、

20

第71図は本発明の実施例9を示す工程図、

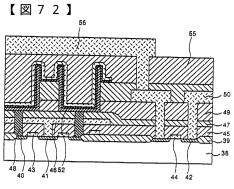

第72図は本発明の実施例9を示す工程図、

第73図は従来の半導体集積回路装置の平面図、

第74図は従来の半導体集積回路装置の断面図、

第75図は従来の半導体集積回路装置の断面図、

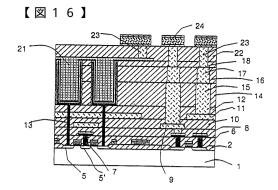

第76図は本発明の実施例10を示す断面図、

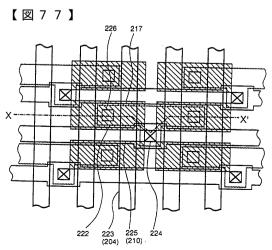

第77図は本発明の実施例10のを示す平面図、

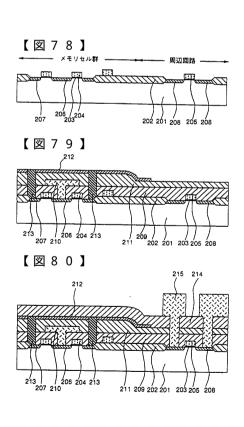

第78図は本発明の実施例10を示す工程図、

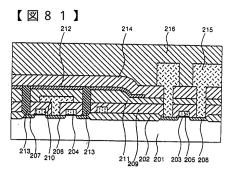

第79図は本発明の実施例10を示す工程図、

第80図は本発明の実施例10を示す工程図、

30

第81図は本発明の実施例10を示す工程図、

第82図は本発明の実施例10を示す工程図、

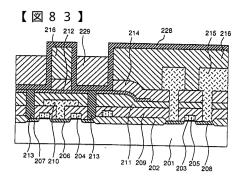

第83図は本発明の実施例10を示す工程図、

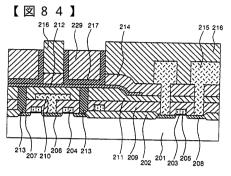

第84図は本発明の実施例10を示す工程図、

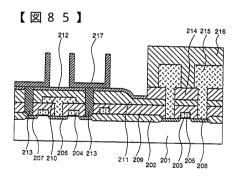

第85図は本発明の実施例10を示す工程図、

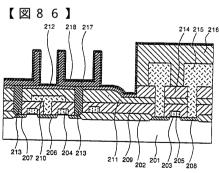

第86図は本発明の実施例10を示す工程図、

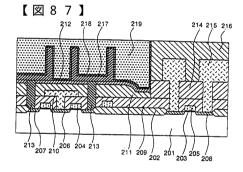

第87図は本発明の実施例10を示す工程図、

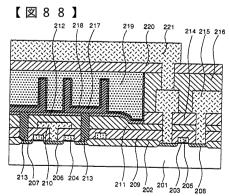

第88図は本発明の実施例10を示す工程図、

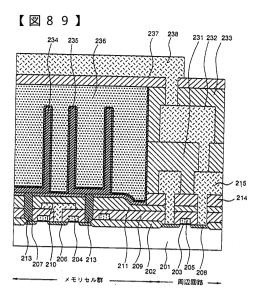

第89図は本発明の実施例11を示す断面図、

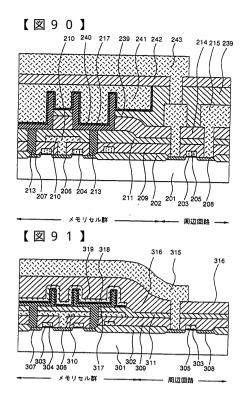

第90図は本発明の実施例12を示す断面図、

40

第91図は従来の半導体記憶装置を示す断面図、

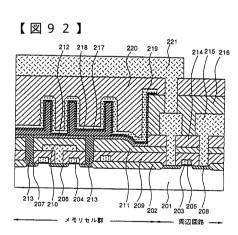

第92図は本発明の実施例13を示す断面図。

〔発明を実施するための最良の形態〕

実施例1

まず、第3図に示したように、半導体基板1の表面に、MOSFETを分離するための素

子間分離酸化膜2を形成した。本実施例では周知のLOCOS法を用いて素子間分離酸化

膜2を形成したが、表面を平坦化できる周知の浅溝分離法を用いてもよい。この場合、周

知のドライエッチ法を用いて深さ 0 . 2 μ m 程度の分離溝を半導体基板 1 に形成した後、

周知のCVD (Chemical Vapor Deposition) 法を用いて膜厚がほぼ0.4μmのシリコ

ンの酸化膜を形成し、溝以外の部分に形成されたシリコン酸化膜を、周知のCMP(Chem

```

ical Mechanical Polishing)法を用いて研磨して除去し、溝内のシリコン酸化膜2のみ

を残せばよい。

次に、上記半導体基板1の表面を洗浄した後に、膜厚7nmのゲート酸化膜3を周知の熱酸化法を用い、酸化温度800 にて形成した。高濃度の不純物を含む厚さ100nmの多結晶シリコン膜4を周知のCVD法を用いて形成し、さらに、抵抗を低減するために、タングステン膜とバリア金属膜の積層膜からなる厚さ100nmの金属膜4′をその上に積層して形成した後、周知のドライエッチ法を用いて所定の形状として、ワード線やゲート電極4を形成し、このゲート電極4をマスクとして用い、基板1とは導電型が逆の不純物イオンとして、砒素を5×10<sup>14</sup>/cm²程度イオン打ち込みし、さらに、950 、10秒アニール処理を行って砒素を活性化して、拡散層5、5′を形成した。なお、メモリセルのスイッチ用トランジスタと周辺回路のn型MOSFETは、イオン打ち込み量は互いに等しくし、また、周辺回路のp型MOSFETにはボロンを同じ量だけイオン打ち込みした。

厚さ  $0.5 \mu m$ のシリコン酸化膜 6 を全面に形成した後、周知の CMP法を用いて、表面の凹凸を平坦化し、ゲート電極 4 の上におけるシリコン酸化膜 6 の厚さをほぼ  $0.15 \mu m$ とした。

次に、第4図に示したように、上記シリコン酸化膜6の所定部分にコンタクト孔を形成し、拡散層5'に接続されたビット線7を形成した。このビット線7としては、高濃度の不純物がドープされた厚さ100nm程度の多結晶シリコン膜の上に、厚さ100nmタングステン・シリサイド膜が積層された、いわゆるポリサイド構造のビット線を形成した。なお、メモリセル領域を示す第4図では、2ビットを1単位として示しており、このため、一つのビット線コンタクトが2本のワード線の間に形成されている。

第4図に示したように、周辺回路においも、上記ポリサイド構造を有する膜を、 n 型 M O S F E T の拡散層と最上部の配線を電気的に接続するための中間層として用いた。この中間層によって M O S F E T のコンタクトが深くなるのが防止されるが、このような中間層を設けなくても本実施例の半導体記憶装置が実現できるのは言うまでもない。また、ビット線 7 としては、本実施例において使用されたポリサイド膜のみではなく、上記ワード線にも使用された、タングステン / バリア金属 / 多結晶シリコンの積層膜など、他の膜を使用してもよい。さらには、多結晶シリコンを使わないで、バリア金属を介して、タングステンを拡散層 5 ' に直接接触させてもよい。

次に、第5図に示したように、シリコン酸化膜8を全面に形成した後、CMP法を用いて表面を平坦化した。上記ビット線7に達するコンタクト孔を形成した後、窒化チタン膜からなる中間膜9'をCVD法によって形成し、さらに800 以上の熱処理に耐えることができる膜厚0.2μmのタングステン膜からなる第1の埋込配線9を形成した。

第5図に示したように、周辺回路を構成するMOSFETの拡散層には、中間層9,を介して埋込配線9が接続されているが、バリア金属を介してタングステンからなる第1の埋込配線9が拡散層に直接接してもよい。タングステンはCVD法によって膜を形成することが可能なため、比較的アスペクト比が高いコンタクト孔にも、高い被覆率でタングステンを接続孔内に埋め込むことができる。その際、タングステンは酸化膜の表面にも堆積されるので、孔内を埋めている部分(接続プラグ)と配線部分が同時に形成できる。本実施例では、CVD法によって形成された窒化チタン膜を上記バリヤ金属として使用した。この工程で形成された埋込配線9は、メモリセルではワード線の母線として使用され、ある特定のワード線を選択するために用いられる。周辺回路では、上層の配線につなぐため

る特定のワード線を選択するために用いられる。周辺回路では、上層の配線につなぐための中間配線として使用されるだけではなく、MOSFET間を互いに接続する配線としても使用される。

次に、第6図に示したように、層間酸化膜10を全面に形成し、CMP法を用いて表面を平坦化した後、上記第1埋込配線9と同様に、タングステン膜からなる接続プラグ(図示せず)および第2埋込配線11を形成し、さらに、層間酸化膜12を形成して、表面を上記と同様に平坦化した。上記層間酸化膜10、12は、いずれも埋め込まれる金属がタングステンであることを考慮して、プラズマCVD法を用いて形成した。この第2埋込配線11は、メモリセルでは、特定のビット線を選ぶためのセレクト線であり、周辺回路にお

10

20

30

40

いては、上層の配線に接続ための中間配線として使用されるだけではなく、MOSFET間を接続する配線としても使用される。本実施例では、第2埋め込み配線11が直接拡散層に接するのではなく、第1埋込配線9を介してMOSFETの拡散層に接触するようにした。

次に、第7図に示したように、ワード線4、ビット線7、第1、第2埋込配線9、11には接触しない深さ約1.5 $\mu$ mのコンタクト孔を形成し、このコンタクト孔を多結晶シリコン13で埋めた。この多結晶シリコンは、キャパシタの下部電極と拡散層5の接続に用いられる。

ギガビット級のメモリでは、上記コンタクト孔の直径は約0.2μmであるから、アスペクト比は7程度と大きくなる。しかし、このコンタクト孔はメモリセルのみに形成され、深さはすべて同じなので、異方性の高い従来のドライエッチ法を用いて形成できる。

また、ビット線 7 を形成する際に、拡散層とキャパシタ下部電極の間のコンタクト部にも、多結晶シリコンを予め埋め込んでおけば、コンタクト孔のアスペクト比を小さくすることができる。

次に、第8図に示したように、層間酸化膜14を全面に形成した後、埋込配線9、11にそれぞれ達するコンタクト孔を形成した。この層間酸化膜14にはトレンチが形成されて、その内壁にトレンチキャパシタが作られるが、このトレンチの深さ、すなわち、層間酸化膜10、12、14の膜厚は、ギガビット級のメモリの場合は、膜厚の合計は2μm程度とする必要がある。

このように膜厚の合計が大きいと、最上層の配線とのコンタクトを形成するのは容易ではないが、本発明では、上記のように、埋込配線 9、11に接続される配線の数は極めて少ないため、コンタクト孔の孔径は最小加工寸法より相当大きくてよい。たとえば、1ギガビットのメモリを形成した本実施例では、最小寸法は0.2µm以下であるが、この工程でのコンタクト孔の直径は0.5µmと大きく、アスペクト比はあまり大きくないので、コンタクト孔の形成は容易であった。

次に、第9図に示したように、厚さがほぼ 0 . 3 μ m のタングステン膜 1 5 を C V D 法を 用いて形成して、上記コンタクト孔をタングステンで埋めた。

第10図に示したように、過酸化水素水を含むスラリーを研磨液として用いた周知のCM P法によって、層間酸化膜14上に堆積されたタングステンを除去し、コンタクト孔の中 のみにタングステン15を残した。上記CMP法は、下地の酸化膜14に対して50倍以 上の選択比でタングステンを除去できるので、酸化膜14をあまり削ることなしに、タン グステンの研磨を行うことができた。

第11図に示したように、膜厚ほぼ1μmの層間酸化膜16および直径0.5μmのタングステンプラグ17を同様にして形成した後、酸化膜18を全面に形成して上記タングステンプラグ17の上面を覆った。

上記層間酸化膜14、16の膜厚の合計はほぼ2μm、コンタクト孔の直径はほぼ0.5μmであるから、アスペクト比はほぼ4であり、1回のタングステンの埋め込みによって、プラグを形成することができ、工程数を削減できた。

次に、第12図に示したように、層間酸化膜14、16、18を貫通し、上記多結晶シリコン13の上端部を露出させるトレンチを形成した。このトレンチは、メモリセル領域のみに形成され、しかも、各トレンチの直径と深さは、それぞれ互いに同じなので、エッチング深さの制御は容易であり、エッチング時間の制御だけで、多結晶シリコン13の表面を露出させることができた。

このトレンチのアスペクト比は7程度であるので、従来のドライエッチング法によって容易に形成できる。なお、層間酸化膜14の下に、窒化膜をエッチングストッパ膜として形成しておくと、トレンチ加工の制御性が向上する。

第13図に示したように、キャパシタの下部電極となる膜厚50nmの多結晶シリコン膜19を全面に形成した。この多結晶シリコン膜19は上記多結晶シリコン13を介して、上記MOSFETの拡散層5と電気的に接続されている。

この多結晶シリコン膜19表面に凹凸を形成した。このように、表面に凹凸を形成するこ

10

20

30

40

とによって、表面積を2倍以上にすることができ、蓄積容量を増加できた。なお、キャパシタの下部電極(蓄積電極)19には、多結晶シリコン以外にも、タングステンや窒化チタンなどを使用することができ、さらには、BSTやPZTなどの高誘電体膜や強誘電体膜をキャパシタ絶縁膜として使用した場合は、白金など貴金属が使用される。

次に、第14図に示したように、上記多結晶シリコン膜19のうち、上記トレンチ内に形成された部分を残し、他の部分はСМР法を用いて除去して、キャパシタ下部電極19を各メモリセル毎に分離して形成した。

第15図に示したように、上記キャパシタ下部電極19の上に、キャパシタ絶縁膜20およびプレート電極21を積層して形成した。本実施例では、上記キャパシタ絶縁膜20には、五酸化タンタル膜とシリコン酸化膜の積層膜を使用し、シリコン酸化膜厚に換算して、3 nmのキャパシタ絶縁膜を実現した。キャパシタ絶縁膜はこれに限ったものではなく、従来用いられたシリコン酸化膜とシリコン窒化膜の積層膜を用いることができ、また、白金など貴金属からなる下部電極を持ちいれば、強誘電体膜をキャパシタ絶縁膜として使うことも可能である。プレート電極21としても、各種周知の導電性材料を使用できるが、本実施例では窒化チタン膜を使用した。キャパシタ絶縁膜としてシリコン酸化膜とシリコン窒化膜の積層膜を用いた場合は多結晶シリコン膜を、強誘電体膜を用いた場合はは白金を、それぞれ使用できる。

次に、第16図に示したように、層間酸化膜22を全面に形成した後、この層間酸化膜2 2にコンタクト孔を形成して、上記プレート電極21およびタングステンのプラグ17の 上端部を露出さた。このコンタクト孔内を金属で埋めてプラグ23を形成した後、最上層 の配線24を周知の方法を用いて形成して、本実施例の半導体記憶装置を完成した。最上 層の配線は密度が非常に小さいので、寸法も非常に大きくてもよく、緩やかな設計ルール を用いることができるので形成は容易である。

## 実施例2

第17図は本発明の第2の実施例を示すメモリアレーの概念図である。第17図に示したように、ワード線WL1~WL6は、縦方向に規則的に配置され、ビット線BL1a、BL1bおよびビット線BL2a、BL2bは、それぞれ1組になってセンスアンプ1とセンスアンプ2に接続されている。

一つのビット線コンタクトBC1(O)は、二つのメモリセルに接続された蓄積容量コンタクトCC1、CC2( )によって共有されている。

第17図から明らかなように、ビット線コンタクトを介して2つの蓄積容量コンタクトの間を結ぶ直線(これはスイッチ用トランジスタのMOSFETの活性領域を示す)は、ワード線WL1~WL6とビット線BL1a~BL2bに対して傾いて配置されている。しかも、傾く方向が、隣接するメモリセル間で異なっている。そのため、各蓄積容量コンタクトCC1、CC2()は、ワード線WL1~WL6とビット線BL1a~BL2bの間の隙間にそれぞれ形成することができる。

本実施例では、ワード線W L 1 ~ W L 6 とビット線 B L 1 a ~ B L 2 b の上方に埋込配線が配置され、しかも、蓄積容量コンタクト形成部を確保するために、第 1 7 図に示したように、点線で示したワード母線W 1 2、W 3 4、W 5 6が、ビット線コンタクトB C 1 1を挟む 2 本のワード線W 1 1とW 1 2、W 1 3とW 1 4、およびW 1 5とW 1 6 に対して 1 本の割合で配置されている。

また、ビット線Blla~Bl2bを選択するためのセレクト線Sl~S4は、ビット線Bl1a~Bl2bとそれぞれ重なるように配置されている。これらのワード母線Wl1~Wl4やセレクト線Sl~S4は、メモリセル上ではコンタクト領域を必要としないので、単に各配線パターンを配置するだけでよい。また、ワード線やビット線に対する本数の割合は本実施例に限られるものでなく、任意に設定できる。

第18図は、第17図に示した配置をさらに実際の配置に近い形で示した配置図である。 ただし、理解を容易にするため、蓄積容量、プレート電極、配線および周辺回路などのパ ターンは、図示が省略されている。

また、第18図では、活性領域が、ビット線B11a~B12bやワード線WL1~WL

10

20

30

40

6に対して45度の角度で配置された場合を示したが、45度に限られるものではなく、 ほかの角度であってもよい。

上記のように、ワード母線W12、W34、W56は、ワード線2本に対して1本の割合でそれぞれ配置されているので、ワード母線W12、W34、W56の幅はワード線WL1~WL6の幅のほぼ2倍となり、緩いレイアウトルールで良い。しかも、上記のように、メモリセル上にはコンタクト領域が存在しないので、配線のみを配置するだけでよい。一方、セレクト線S1、S2、S3、S4とビット線B11a~B12bは、まったく同じ寸法にした。しかも、このセレクト線S1、S2、S3、S4もワード母線W12、W34、W56と同様に、メモリセル上にはコンタクト領域が存在しないので、ビット線のような、線幅が拡がった領域は必要ない。そのため、ワード母線W12、W34、W56およびセレクト線S1、S2、S3、S4は、いずれも規則性の高いパターンを配置することができ、ホトリソフラフィによるパターン形成は容易である。

さらに、パターンの規則性が高いために、位相シフト法に代表される、光の波長よりも小さなパターンを形成できる微細加工技術を適用するのも容易である。

### 実施例3

本実施例では、第19図に示したように、一つのビット線コンタクトBC1を共有する二つのメモリセルの蓄積容量コンタクトCC1、CC2が、ワード母線W12、W34、W56を軸にして鏡面対象となる位置に配置されている。この点が上記実施例2とは異なっているが、基本的なメモリ動作はまったく同じであり、本発明の特徴である埋込配線で作るワード母線やセレクト線の配置も、第20図に示したように、同じであり、実施例2と同様の効果が得られた。

#### 実施例4

本実施例のメモリセルは、第21図に示したように、上記実施例2、3とはパターン配置が異なっている。しかし、製造方法は上記実施例2、3と共通であり、上記実施例1と同じ方法で形成できる。

本実施例のパターン配置の特徴は、特開平3 - 2 1 4 6 7 0 に記載されているように、互いに隣合うメモリセルの蓄積容量コンタクトの間にワード線が配置されている点にある。 実施例2、3において示した配置では、互いに隣合う蓄積容量コンタクトの間には、ワード線が2本配置されていた。そのため、メモリセルには余分な面積が存在し、これが、メモリセル面積の縮小を妨げる要因となっていた。

しかし、第21図に示したパターン配置にすると、ワード線2本分を配置するのに必要だった面積が、1本のワード線を配置できる面積で済むようになり、20%程度の面積縮小ができる。

このようなパターン配置にすると、これまでのビット線配置では同じようなメモリ動作ができないので、特開平3-214670および上記実施例1~3では二つのビット線がペアとなって一つのセンスアンプに接続されていたのを、第21図に示したように、二つのビット線BL2a、BL1bを互いに交差させて、それぞれのセンスアンプ1、2に接続させるようにした。

このような配置にすることよって、メモリセルの面積を縮小できるが、上記実施例 1 ~ 3 では、ワード線 2 本に 1 本の割合で配置していたワード母線 W 1 1 ~ W 1 7 を、第 2 2 図に示したように、ワード線 W 1 ~ W 7 と同じ設計ルールで配置する必要がある。しかし、実施例 1 と同じ方法で容易に形成することができ、実用上問題はない。 実施例 5

本実施例は、本発明をDRAMに適用した例であり、第24図~第38図を用いて説明する

本実施例のメモリセルの平面図を第24図に、第24図におけるX-X'断面構造および周辺回路のMISFET部の断面構造を、第25図の同一図面上に示した。メモリセルのレイアウトは従来と同様であり、ワード線58がY方向に、データ線60がX方向に設けられており、トレンチ型のキャパシタが、これらワード線とデータ線の上部に形成されている。

10

20

30

20

30

40

50

上記トレンチ型のキャパシタは、蓄積電極 5 2 、キャパシタ絶縁膜 5 3 およびプレート電極 5 4 からなっている。上記蓄積電極 5 2 はワード線 5 8 とデータ線 6 0 の間の隙間において、スイッチトランジスタの活性領域 5 7 上に接続され、プレート電極 5 4 は、メモリセル外で所定の電位に固定されている。さらに、トレンチ形状を有する上記蓄積電極 5 2 は、周辺回路部の金属配線 5 0 がその上に形成されている絶縁膜 4 9 およびその上に積層して形成された絶縁膜 5 1 を貫通して形成された深いトレンチの、内側側壁および底面上に形成されている。

次に、本実施例のDRAMの製造法を第26図~第35図を用いて説明する。まず、第26図に示したように、周知の選択酸化法を用いて、素子間分離のためのフィールド酸化膜39を、シリコン基板38上に形成した後、周知の方法によって、MOSFETを形成した。高濃度不純物領域40、41、ゲート電極43およびゲート絶縁膜(図示せず)を有するMOSFETをメモリセル内に、また高濃度不純物領域42、ゲート電極44およびゲート絶縁膜(図示せず)を有するMOSFETを周辺回路に、それぞれ形成した。なお、隣接セルと共通のゲート電極43はワード線58(第24図)として機能する。また、MOSFETの極性はnチャネル、pチャネル何れでもよい。

第27図に示したように、ボロンとリンを含んだシリコン酸化膜45を周知のCVD法を用いて形成し、800 程度の温度でアニールを行って上記シリコン酸化膜45表面をなだらかにした。なお、上記シリコン酸化膜45としては、ボロンやリンが添加されたものではなく、ノンドープのシリコン酸化膜を用いてもよい。

次に、周知のホトリソグラフィとドライエッチングによって、上記シリコン酸化膜 4 5 に開口部 5 9 (第 2 4 図)を形成し、データ線 6 0 (第 2 4 図)となる厚さ 1 0 0 n m程度の配線 4 6 を周知の方法を用いて形成した。なお、配線 4 6 の材料としてはタングステン等の高融点金属膜が好ましいが、タングステン等の高融点金属のシリサイド膜と多結晶シリコン膜の複合膜を用いても支障はない。タングステン等の高融点金属を用いた場合は、シリコン基板との反応を防止する目的で、チタンナイトライド等のバリヤメタル膜を高融点金属膜の下に設けることが好ましい。また、シリコン酸化膜 4 5 の下に、不純物拡散防止のためのノンドープのシリコン酸化膜を形成しておくことが望ましい。

第28図に示したように、厚さがほぼ200nmのシリコン酸化膜47を周知のTEOS(Tetraethoxysilane; Si( $OC_2H_5$ ) $_4$ )ガスを用いた周知のCVD法を用いて、400程度の温度で形成した。次に、スイッチトランジスタのソースまたはドレインとなる高濃度不純物領域40上のシリコン酸化膜45、47の所定部分を除去して、開口部51(第24図)を形成した。不純物が高濃度に添加された厚さ200nm程度の多結晶シリコン膜を周知のLPCVD法によって形成した後、全面異方性のドライエッチングによるエッチバックを行って、上記多結晶シリコン膜を、上記開口部51内のみに残し、他の部分は除去して、上記開口部51を充填するシリコンプラグ48を形成した。なお、本実施例では、高濃度不純物領域40上に直接シリコンプラグ48を形成したが、周知の多結晶シリコン膜のパッドを、用いれば、ゲート電極43とシリコンプラグ48を自己整合で絶縁することもでき、メモリセル面積の縮小に効果的である。

第29図に示したように、厚さがほぼ200nmのシリコン酸化膜49を周知のTEOSガスを用いたCVD法により、ほぼ400 の温度で形成し、シリコン酸化膜45、47、49を貫通するコンタクトホールを周知の方法を用いて形成して、周辺回路部の高濃度不純物領域42の表面を露出させた。次に、厚さ200nmのタングステン膜を周知のスパッタ法もしくはCVD法を用いて形成し、所定の形状にパターニングして周辺回路部の金属配線50を形成した。シリコン酸化膜49の表面を周知のCMP法を用いて平坦化してもよく、この場合は、上記コンタクトホールを埋めるプラグを用いるとよい。また、本実施例では金属配線50の材料としてはタングステンを用いたが、チタンナイトライド等他の高融点金属を用いてもよい。さらに、キャパシタの製造工程を低温化すれば、高融点金属のみではなく、アルミニウムなどの低抵抗金属を用いることができる。

第 3 0 図に示したように、厚さ 0 . 5 ~ 1  $\mu$  m 程度のシリコン酸化膜 5 1 を、周知の T E O S ガスを用いた C V D 法によって 4 0 0 程度の温度で形成し、周知の C M P 法を用い

て表面を平坦化した。次に、周知のホトリソグラフィとドライエッチングを用いて、上記シリコン酸化膜49、51に、シリコンプラグ48に達するトレンチ(開口部)62を形成した。なお、この際、窒化シリコン膜のように、シリコン酸化膜よりエッチング速度が小さい絶縁膜を、エッチングストッパとしてシリコン酸化膜49の下に形成しておけば、上記トレンチ62の形成は極めて容易である。

第31図に示したように、高濃度の不純物がドープされた厚さ50nmの多結晶シリコン膜63を、周知のLPCVD法を用いて形成した。この際、上記トレンチの低部においてシリコンプラグ48と多結晶シリコン膜63が接続される。

次に、厚さがほぼ 1 μ m のホトレジスト膜を全面に塗布した後、異方性ドライエッチングによるエッチバックを行って、上記トレンチ内のみにホトレジスト 6 4 を残し、他の部分は除去した。

第32図に示したように、上記ホトレジスト64をマスクとして用い、上記多結晶シリコン膜63の内、上記トレンチ内以外の部分上に形成された部分をドライエッチングして除去して、キャパシタの蓄積電極52を上記トレンチの内壁上に形成した。

第33図に示したように、上記ホトレジスト54を除去した後、五酸化タンタル( $Ta_2O_5$ )からなるキャパシタ絶縁膜53をCVD法を用いて形成した。このキャパシタ絶縁膜53のシリコン酸化膜換算膜厚は、1ギガビットクラスの大容量ダイナミックRAMの場合は3nm以下にすることが好ましい。なお、本実施例では蓄積電極52としては多結晶シリコン膜を用いたが、タングステンやチタンナイトライド膜など高融点金属膜を用いることもできる。この場合は多結晶シリコン膜のように、表面にの自然酸化膜が形成されることもできる。この場合は多結晶シリコン膜のように、表面にの自然酸化膜が形成されることはないので、キャパシタ絶縁膜の酸化膜換算膜厚を薄くすることができる。また、キャパシタ絶縁膜の材料としてはシリコンナイトライド系の絶縁膜の他、 $SrTiO_3$ 膜や(Ba,Sr)  $TiO_3$ 等の周知の高誘電体絶縁膜やPZT膜のような周知の強誘電体絶縁膜を用いることもできる。

第34図に示したように、厚さがほぼ50nmのタングステン膜からなるプレート電極54を、段差被覆性がすぐれたCVD法を用いて形成した。

最後に、層間絶縁膜として厚さがほぼ400nmのシリコン酸化55を形成し、周辺回路部の金属配線50上の層間絶縁膜55にスルーホールを形成した後、周知の方法を用いて金属配線56を形成して、第25図に示した半導体集積回路装置が完成した。なお、金属配線56はアルミニウムなどの低抵抗金属が好ましく、第35図のようメモリセルアレー内配線として用いることができるため、データ線に接続する信号線や、主ワード線として用いることができる。また、金属配線56を形成する際に、層間絶縁膜55の表面を平坦化するために、周知のプラグ技術やCMP法を適用することもできる。

第35図は、上記第25図よりもトレンチの深さを大きくして、キャパシタの高さを大きくした例を示すものである。この場合は金属配線50の膜厚を第25図の場合の2倍にしたが、その上に形成されるシリコン酸化膜51の膜厚も厚くしても、トレンチの深さを約2倍に深くすることができ、その結果、蓄積電極の高さおよび得られる蓄積電荷量も約2倍になった。

なお、第25図~第35では、金属配線50がその上に形成されている層間絶縁膜であるシリコン酸化膜49の表面が平坦化されているが、第36図に示すように、表面が平坦ではないシリコン酸化膜65の上に金属配線50を形成してもよい。この場合も、第36図から明らかなように、シリコン酸化膜65の上面が、キャパシタが形成されている位置に延在して、蓄積電極52の側面に接しているため、上記金属配線50がその上に形成されたシリコン酸化膜49の表面が平坦である場合(第35図)と同じ効果が得られる。

さらに、上記金属配線50は、周辺回路部における第1層目の配線層であるが、第37図に示したように、二つの金属配線66、67を積層して用いてもよく、配線層をさらにその上に形成してもよい。

本実施例によれば、複数の配線層の上面をキャパシタの位置に延在させることができるので、トレンチの深さを極めて深くすることができ、キャパシタの電極面積が極めて大きいトレンチ型のキャパシタが形成できる。

10

20

30

40

また、本実施例では、金属配線 5 0 は周辺回路部のMOSFETのソースもしくはトレインに接続された信号線であるが、一定の電位を供給するための電源線であってもよく、また、メモリセルアレー領域と周辺回路領域の標高差を緩和するためのダミーパターンとして、フローティングであってもよい。

上記説明から明らかなように、本実施例によれば、高さが大きい立体構造のキャパシタを 形成することができ、メモリセルアレー領域と周辺回路領域に大きな標高差が生じても、 各領域および両領域をまたがる領域に、それぞれ微細な配線を形成できるので、集積密度 の高い半導体集積回路装置を形成できる。

## 実施例6

本実施例は、上記実施例 5 において、銅のようにドライエッチングが困難な材料を金属配線材料として用いた例であり、第38図~第47図を用いて本実施例を説明する。

第38図は、本実施例のDRAMにおけるメモリセルおよび周辺回路のMOSFET部の断面構造を示す図である。第38図から明らかなように、金属配線71は高濃度不純物領域43上に形成された金属プラグ68に接続され、シリコン酸化膜70内に埋め込まれて形成されている。

このような構造のDRAMを下記のように形成した。

まず、実施例5の第26図~第28図に示した方法と同様な方法を用いて、第39図に示した構造を形成した。次に、第40図に示したように、シリコン酸化膜69を形成した後、シリコン酸化膜45、47、69を貫通する接続孔を周知の方法を用いて形成し高濃度不純物領域42の表面を露出させた。タングステン膜を全面に形成した後、全面ドライエッチングを行って、上記タングステン膜のうち、上記接続孔内に形成された部分を残し、他の部分は除去して、タングステンからなる金属プラグ68を形成した。

第41図に示したように、厚さ400nmのシリコン酸化膜70を形成し、周知のホトリソグラフィと異方性ドライエッチングを用いて、上記シリコン酸化膜70に開口部を形成した。なお、上記異方性ドライエッチングを行う際に、低温で形成されたシリコンナイトライド膜を、エッチングストッパ膜として上記をシリコン酸化膜70の下に配置しておくと、エッチング裕度が大きくなり、高い精度で接続孔を形成できた。

次に、厚さ500nmの銅膜を形成した後、CMP法を用いて、シリコン酸化膜70の表面が露出するまで上記銅膜の表面を研磨して平坦にして、上記開口部内のみに銅膜71を残し、銅膜71がシリコン酸化膜70内に埋め込まれた構造を形成した。なお、上記銅膜の形成方法としては、段差被覆性に優れたCVD法を用いた。

次に、第42図に示したように、厚さ100nmのシリコン酸化膜72を周知のCVD法を用いて形成した後、周知のホトリソグラフィと異方性ドライエッチングを用いて、シリコン酸化膜69、70、72を貫通し、シリコンプラグ48に達するトレンチ74を形成した。

以下、第43図~第47図に示した工程に従って処理を行なったが、この工程は、上記実施例5における第31図~第35図に示した工程と同様なので、詳細な説明は省略した。ただし、本実施例ではプレート電極73の表面が平坦化されており、この点が上記実施例5と異なっている。

本実施例によれば、キャパシタの側面に形成される周辺回路部の配線層として低抵抗の銅が用いられているので、高速動作が可能である。なお、本実施例をメモリとロジックが混在したオンチップLSIに適用することによって、キャパシタが形成されている絶縁膜の位置にロジック部の配線層を形成することができる。

# 実施例7

本実施例は実施例5もしくは実施例6におけるDRAMにおいて、金属配線の膜厚をさらに厚くした例であり、第48図~第56図を用いて説明する。第48図は本実施例によるDRAMのメモリセルおよび周辺回路のMISFET部の断面構造図である。第48図に示したように、本実施例では、金属配線77はシリコン酸化膜75、76内に埋め込まれ、金属配線77の上面はキャパシタの上端部より高い。

このようなDRAMの製造方法を、第49図~第56図を用いて説明する。まず、上記実

10

20

30

40

20

30

40

50

施例6の第39図および第40図と同様に処理して、第49図に示す構造を形成した。次に、第50図に示したように、厚さ300nmのシリコン酸化膜75を形成し、周知ホトリソグラフィとドライエッチングを用いて、シリコン酸化膜69、75を貫通するトレンチ78をを形成し、シリコンプラグ48の上面を露出させた。

以下、第51図~第54図に示した工程に従ってキャパシタを形成したが、この工程は、上記実施例5における第31図~第34図に示した工程と同様であるので、詳細な説明は省略する。

次に、第55図に示したように、厚さ400nmのシリコン酸化膜79を形成した後、ホトリソグラフィとドライエッチングを用いて、シリコン酸膜75、79に金属プラグ68に達する開口部を形成した。タングステン、アルミニウムまたは銅等の金属材料膜を全面形成した後、異方性エッチングによる周知のエッチバックを行なって、上記金属膜を、上記開口部内のみに残し、他の部分上からは除去して周辺回路部の金属配線80を形成した

最後に、第56図に示したように、例えば厚さがほぼ400nmのシリコン酸化膜からなる層間絶縁膜55を形成した後、上記金属配線80の表面に達するスルーホールを上記層間絶縁膜55に形成した。さらに、金属配線56を周知の方法を用いて形成し、半導体集積回路装置が完成した。

本実施例によれば、周辺回路部の金属配線の膜厚を上記実施例 5、6より厚くできるため、周辺回路における配線の抵抗値を下げることができ、動作速度がさらに向上した。 実施例 8

本実施例は、立体構造の王冠型とトレンチ型を組み合わせた構造を有するキャパシタを、 DRAMのメモリセルに形成した例であり、第57図~第65図を用いて本実施例を説明 する。

第57図は本実施例によるDRAMの、メモリセルおよび周辺回部におけるMISFET部の断面構造を示す図である。第57図から明らかなように、周辺回路部に形成された金属配線86は、シリコン酸化膜85内に埋め込まれており、その下に形成されたシリコン酸化膜81の上面は、周辺回路部からメモリセル部に延在して、キャパシタの側部に接している。

次に、第58図~第65図を用いて本実施例の製造方法を説明する。まず、第58図に示した構造を形成したが、これまでの工程は、上記実施例5の第28図までの工程と同様であるので、説明は省略する。

第59図に示したように、シリコン酸化膜81を形成した後、シリコン酸化膜45、47、81を貫通する接続孔を形成して、高濃度不純物領域42の表面を露出させた。タングステン膜を全面に形成した後、全面異方性エッチングによるエッチバックを行なって、上記タングステン膜を、上記接続孔内のみに残し、他の部分上からは除去して、タングステンからなる金属プラグ82を形成し、さらに厚さ400nmのシリコン酸化膜89を全面に形成した。なお、シリコン酸化膜81の代わりにシリコンナイトライド膜を用いてもよい。

第60図に示したように、キャパシタの蓄積電極52が形成される領域のシリコン酸化膜81、89に、周知のホトリソグラフィとドライエッチングを用いて、シリコンプラグ48に達するトレンチを形成し、不純物が高濃度に添加された厚さ50nmの多結晶シリコン膜53を、周知のLPCVD法を用いて形成した。これにより、トレンチの底部において、シリコンプラグ48は多結晶シリコン膜63に接続された。

次に、第61図に示したように、ボロンとリンを含むシリコン酸化膜90を周知のCVD法で形成し、所望のアニールを行なった後、全面異方性ドライエッチングによるエッチバックを行なって、上記シリコン酸化膜90を上記トレンチ内のみに残し、他の部分上からは除去した。さらに、上記シリコン酸化膜90をエッチングのマスクとして用いて、多結晶シリコン膜63の露出された部分をドライエッチングして除去した。その結果、キャパシタの蓄積電極52がトレンチ内に形成された。

次に、第62図に示したように、上記トレンチ内に残ったシリコン酸化膜90、および金

属プラグ82上のシリコン酸化膜89を、フッ酸水溶液を用いたウェットエッチングによって除去し、金属プラグ82の表面を露出させた。ここでトレンチ内に埋め込んだシリコン酸化膜90は、ボロンとリンを含んでいるため、シリコン酸化膜89よりフッ酸水溶液でのエッチング速度が速い。そのため、膜厚が厚いにもかかわらず、トレンチ内の酸化膜90は完全に除去された。なお、上記ウェットエッチングでのオーバーエッチングを防止するために、シリコン酸化膜89の下に、低温で形成したシリコンナイトライド等のエッチングストッパを設けることが好ましい。

所定の洗浄を行なった後、第63図に示したように、五酸化タンタル膜からなるキャパシタ絶縁膜83を形成した後、厚さがほぼ50nmののタングステン膜またはチタンナイトライド膜を形成し、ホトリソグラフィとドライエッチングによって不要部分を除去してプレート電極84を形成した。さらに厚さ800nmの厚いシリコン酸化膜85を形成して、表面を平坦化した。

次に実施例6、第42図と同様に処理して金属配線86を形成して、第64図に示した構造を形成した。

最後に、厚さ400nm程度のシリコン酸化膜等の層間絶縁膜55を形成し、周辺回路部の金属配線86上の層間絶縁膜85にスルーホールを形成した後、金属配線56を形成して第65図に示した半導体集積回路装置が完成した。

本実施例によれば、メモリセル内に形成されたキャパシタの蓄積電極 5 2 が王冠状であるため、内壁と外壁の両者を蓄積電極として利用でき、極めて大きな蓄積容量が得られ、ソフトエラー耐性に優れた高集積の半導体集積回路装置が形成できた。

実施例9

本実施例は、王冠型とトレンチ型を組み合わせたキャパシタを有する DRAMメモリの他の例である。第66図~第72図を用いて本実施例を説明する。

第66図は本実施例のDRAMのメモリセルおよび周辺回路のMISFET部の断面構造を示した図である。第66図に示したように、金属配線50はシリコン酸化膜49に形成された開口部内に形成されている。メモリセルのキャパシタは、シリコン酸化膜49、92に接している部分がトレンチ型、シリコン酸化膜55に接している部分が王冠型となっている。従って、金属配線50が形成されているシリコン酸化膜49の上面は、メモリセル領域に延在してキャパシタの側部に接している。

次に、第67図~第72図を用いて本DRAMセルの製造方法説明する。

まず、実施例5の第30図までの工程と同様な工程に従って、第67図に示した構造を形成した。次に、第68図に示したように、厚さ400nmのシリコン酸化膜92を形成し、周知のCMP法を用いて表面を平坦化した後、周知のホトリソグラフィとドライエッチングを用いて、キャパシタの蓄積電極93が形成される部分のシリコン酸化膜49、92に、シリコンプラグ48に達するトレンチを形成した。

次に、不純物が高濃度にドープされた厚さ 5 0 n m の 多結晶シリコン膜 6 3 を、周知の L P C V D 法によって形成した。これにより、シリコンプラグ 4 8 が、トレンチの底部において 多結晶シリコン膜 6 3 に接続された。

厚さ 1 μ m のホトレジストを塗布し、周知の全面異方性ドライエッチングを行なって、第 6 9 図に示したように、トレンチ内のみにホトレジスト 6 4 を残し、他の部分上からは除去した。

次に、上記ホトレジスト64をマスクにして、上記多結晶シリコン膜63の露出された部分をドライエッチングによって除去し、トレンチの内壁上にキャパシタの蓄積電極52を 形成した。

上記ホトレジスト64を除去して所定の洗浄を行なった後、フッ酸水溶液を用いて上記シリコン酸化膜92を厚さ200nmだけエッチした。これにより、第70図に示したように、上記蓄積電極52の上部が上方に突出された。

第71図に示したように、二酸化シリコンより比誘電率が大きい誘電体(本実施例では五酸化タンタルを使用した)からなるキャパシタ絶縁膜93を形成し、厚さがほぼ50nmのタングステンまたはチタンナイトライドなどからなるプレート電極94を周知の方法を

10

20

30

40

20

30

40

50

用いて形成した。なお、キャパシタ絶縁膜93およびプレート電極94の形成方法としては、段差被覆性の良いCVD法を用いた。

最後に、厚さがほぼ400nmのシリコン酸化膜からなる層間絶縁膜55を形成し、周辺回路部の金属配線50上の層間絶縁膜55にスルーホールを形成した後、金属配線56を 形成して第72図に示した本発明の半導体集積回路装置が完成した。

第72図から明らかなように、本実施例によれば、メモリセル内に形成されたキャパシタの蓄積電極52の上部では、内壁上のみではなく、外壁上にもキャパシタ絶縁膜93およびプレート電極94が形成されて、この部分では王冠型キャパシタが形成されている。したがって、トレンチの内壁のみをキャパシタとして用いたトレンチ型キャパシタよりも、大きな蓄積容量が得られ、ソフトエラー耐性に優れた高集積の半導体集積回路装置が形成された。

実施例10

第76図~第88図を用いて本発明によるDRAMの一実施例を説明する。第76図は本実施例メモリセルおよび周辺回路のMOSFET部の断面構造を同一図面上に示した図であり、第77図は上記メモリセルの平面配置を示す図である。第76図のメモリセル部分は、第77図におけるX-X′断面の一部を表わす。

第76図から明らかなように、メモリセル内のMOSFETは、ゲート絶縁膜203、ゲート電極204、ソース・ドレインである高濃度 n 型不純物領域206、207からなり、周辺回路内のMOSFETは、ゲート絶縁膜203、ゲート電極205、ソース・ドレインである高濃度 n 型不純物領域208からなっている。メモリセル内のMOSFETの高濃度 n 型不純物領域206にはデータ線として配線電極210が接続され、さらにその上方には王冠型キャパシタが設けられている。

この王冠型キャパシタは、周辺回路領域の金属配線215が形成されている層間絶縁膜であるシリコン酸化膜214、216が除去された領域に形成されており、蓄積電極217がシリコンプラグ213を介して高濃度n型不純物領域207に接続されている。蓄積電極217の上にはキャパシタ絶縁膜218が形成され、さらにシリコン酸化膜214、216が除去された領域にキャパシタのプレート電極219が埋め込まれて王冠型のキャパシタが形成されている。

第77図では、隣接するメモリセルの位置関係を明確にするために、複数個のメモリセルが配置された図を示した。第77図で、ワード線223はY方向に、データ線225はX方向に、それぞれ配置されており、王冠型のキャパシタ217がこれらワード線223とデータ線225の上部に形成されている。さらにこれらのワード線223とデータ線225の間の隙間の活性領域222上には、上記キャパシタが開口部226を介して接続されている。

第78図~第88図を用いて本実施例をさらに詳しく説明する。まず、第78図に示したように、周知選択酸化法(LOCOS技術)を用いて、シリコン基板201上にフィールド酸化膜202を形成した後、活性領域上にMOSFETを形成する。なお、本実施例ではnチャネルMOSFETを形成したが、pチャネルMOSFETであってもよい。また、ホットキャリアによる素子劣化を低減するため、周知のLDD(Lightly Doped Drain)構造を用いることもできる。さらに周知の自己整合コンタクトを用いるために、ゲート電極204の側壁や上部にシリコンナイトライド等のような絶縁膜を形成してもよい。

次に、ボロンとリンを含んだシリコン酸化膜209を周知のCVD法によって形成した後、800 程度の温度のアニールを行なって、シリコン酸化膜209表面をなだらかにした。なお、シリコン酸化膜209にはボロンやリンを添加したものを用いずノンドープのシリコン酸化膜を用い、他の方法で平坦にしてもよい。また、シリコン酸化膜の表面を平坦にしなくても後の工程に支障はない。

ホトリソグラフィとドライエッチングにより開口部 2 2 4 (第 7 7 図)をシリコン酸化膜 2 0 9 に形成し、データ線 2 2 5 (第 7 7 図)となる厚さ 1 0 0 n m程度の配線電極 2 1 0 を形成し、ホトリソグラフィとドライエッチングによって、所定の形状にパターニング

した。なお、配線電極 2 1 0 の材料としてはタングステン等の高融点金属のシリサイド膜と多結晶シリコン膜の複合膜、もしくはタングステン等の高融点金属膜を用いることができる。また、タングステン等の高融点金属を用いる場合はシリコン基板との反応を防止する目的でチタンナイトライド等のバリヤメタル膜を下層に設けることが好ましい。また、シリコン酸化膜 2 0 9 の下には、不純物拡散防止のためのノンドープのシリコン酸化膜を設けておくことが好ましい。

厚さがほぼ200mmの、ボロンとリンを含んだシリコン酸化膜211をCVD法により形成し、800 程度の温度でアニールを行なって表面をなだらかにした。次に、厚さ100mm程度のシリコンナイトライド膜212をLPCVD法により形成し、MOSFETのソースもしくはドレインとなる高濃度不純物領域207上のシリコンナイトライド膜212およびシリコン酸化膜209、211に、周知のホトリソグラフィとドライエッチングによって開口部226(第77図)を形成し、不純物が高濃度に添加された厚まではよりによって開口部226(第77図)を形成し、全面異方性ドライエはぼ200mmの多結晶シリコン膜をLPCVD法によりに形成し、全面異方性ドライみみにが、第79図に示したように、シリコンプラグ213を形成した。なお、本実施例では、ホトリソグラフィを用いて周辺回路領域上のシリコンナイトライド膜212を除去したが、シリコンナイトライド膜212を周辺回路領域に残したままでもよい。また、本多結晶シリコン膜のパッドを用いれば、ゲート電極204とシリコンプラグ213を自己整合で絶縁することもでき、メモリセル面積の縮小に効果的である。

次に、第80図に示したように、厚さがほぼ200nmのシリコン酸化膜214を、TEOSガスを用いた周知のCVD法によってほぼ400 で形成し、周辺回路部の高濃度不純物領域208上のシリコン酸化膜209、211、214をエッチングして除去し、コンタクトホールを形成した。厚さがほぼ200nmのタングステン膜を、周知のスパッタ法もしくはCVD法を用いて形成し、周知のホトリソグラフィとドライエッチングによって周辺回路部の金属配線215を形成した。ここで、シリコン酸化膜214の表面を周知のCMP法を用いて平坦化してもよい。この場合は上記コンタクトホール内にプラグを形成してもよい。また、本実施例では金属配線215の材料にはタングステンを用いたが、この場合は、チタンナイトライド等のバリヤメタル膜を下に設けると良い。さらに、以降のキャパシタの製造工程を低温化すれば、アルミニウムなどの低抵抗金属を用いることもできる。

第81図に示したように、厚さ0.3~1 $\mu$ mのシリコン酸化膜216をTEOSガスを用いたCVD法を用いて、ほぼ400 で形成し、CMP法を用いて表面を平坦化した。次に、第82図に示したように、周知のホトリソグラフィとドライエッチングを用いて、キャパシタの蓄積電極が形成される部分のシリコン酸化膜214、216に、シリコンプラグ213に達するトレンチ227を形成した。なお、この際、シリコンナイトライド膜212を、エッチングストッパとしてシリコン酸化膜214の下に設けておくことが好ましい。

第83図に示したように、不純物が高濃度に添加された厚さ20~100nmの多結晶シリコン膜228を、周知の減圧CVD(LPCVD)法によって形成した。この際、上記トレンチの底部において、上記シリコンプラグ213と多結晶シリコン膜228が接続された。次に、厚さ1μmのホトレジスト膜を塗布した後、全面異方性ドライエッチングによるエッチバックを行なって、ホトレジスト膜229をトレンチ内のみに残し、他の部分は除去した。なお、上記ドライエッチングを制御して、トレンチ内に残ったホトレジスト膜229の上面の位置は、シリコン酸化膜216の上面からほぼ0.2μm下になるようにした。

次に、上記ホトレジスト膜229をマスクにして、上記多結晶シリコン膜228の露出された部分をドライエッチングして除去し、第84図に示したように、トレンチの内壁上にキャパシタの蓄積電極217を形成した。

上記ホトレジスト膜229を除去し、所定の洗浄を行なった後、フッ酸水溶液を用いて、

10

20

30

シリコン酸化膜216およびその下のシリコン酸化膜214をエッチして除去し、第85 図に示したように、王冠型の蓄積電極217の内面および側面を露出させた。この際、ホトリソグラフィを用い、上記シリコン酸化膜216、214のうち、メモリセルアレー領域に形成された部分はエッチして除去し、周辺回路領域に形成された部分はエッチされずに残るようにした。なお、上記ウェットエッチングの際に、少なくともメモリセルアレー領域のシリコン酸化膜214の下に、シリコンナイトライド膜212があるため、その下の部分がオーバーエッチングされる恐れはない。

第86図に示したように、五酸化タンタル( $Ta_2O_5$ )膜など、シリコン酸化膜より比誘電率の大きな誘電体からなるキャパシタ誘電体膜 218を形成した。キャパシタ誘電体膜 218の形成方法としては、段差被覆性の良いCVD法を用いた。さらに、キャパシタ誘電体膜 218のシリコン酸化膜換算膜厚は、1ギガビットクラスの大容量 DRAMでは 318の 310の 32000 3300 3300 3300 3300 3300 3300 3300 3300 3300 3300 3300 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 330 3

厚さがほぼ300nmの厚いタングステン膜を全面に形成した後、CMP法によって研磨して、第87図に示したように、上記シリコン酸化膜213、216が除去された領域のみに上記タングステン膜を残し、プレート電極219を形成した。なお、本実施例では、CMP法を用いてプレート電極219を形成したが、上記タングステン膜219を形成した後、ホトレジスト膜を形成し、全面ドライエッチバックを行なってもよい。また、プレート電極218の形成方法としては、段差被覆性の良いCVD法が好ましい。

層間絶縁膜として厚さが約200nmのシリコン酸化膜220を形成し、周辺回路部の金属配線215上のシリコン酸化膜216、220を貫通するスルーホールを形成した後、周知の方法を用いて金属配線221を形成して、第88図に示した本発明の半導体記憶装置が完成した。

上記説明から明らかなように、本実施例における半導体記憶装置の製造方法では、半導体基板の主面上に設けられた絶縁膜を平坦化した後、メモリアレー部における絶縁膜の所定部分を選択的に除去し、除去された部分内に上記キャパシタが形成される。

なお、金属配線221としてはアルミニウムなどの低抵抗金属が好ましく、第88図に示したようメモリセルアレー内配線として用いることができるため、データ線に接続する信号線や、ワード母線として用いることができる。また、金属配線221を形成する際に、層間絶縁膜を平坦化するために、周知プラグ技術やCMP法を適用することもできる。なお、本実施例における金属配線215は、周辺回路部の第1層目の配線層であるが、メ

なお、本実施例における金属配線 2 1 5 は、周辺回路部の第 1 層目の配線層であるが、メモリセルのデータ線として用いた配線電極 2 1 0 を周辺回路領域の第 1 層目の配線層として用いてもよい。

さらに、本実施例の蓄積電極 2 1 7 として用いた多結晶シリコン膜の表面を凹凸形状にして蓄積電極 2 1 の表面積を増加させ、蓄積容量をさらに大きくすることもできる。

本実施例によれば、プレート電極219は、シリコン酸化膜216、214が除去された領域に埋め込まれるため、プレート電極219を形成するための余分なホトリソグラフィエ程は必要なく、所要マスク枚数の増加なしに蓄積容量の大きなDRAMが得られる。また、本実施例では金属配線221は周辺回路部のMOSFETのソースもしくはトレインに接続された信号線であるが、一定の電位を供給するための電源線であってもよく、また、メモリセルアレー領域と周辺回路領域の標高差を緩和するためのダミーパターンとして、フローティングであってもよい。

# 実施例11

本実施例は、上記実施例10に示したDRAMにおいて、複数の配線層を周辺回路領域に 形成した例である。第89図は、本実施例のDRAMのメモリセル群およびそれに隣接す 10

20

30

40

る周辺回路領域のMOSFET部の断面図である。

第89図に示したように、周辺回路領域の金属配線215上には、層間絶縁膜として厚さ約0.3  $\mu$ mのシリコン酸化膜231が形成され、さらにその上には厚さ約0.3  $\mu$ mの金属配線232は、上記シリコン酸化膜231に形成された開口部を介して金属配線215に接続されている。さらに、上記金属配線232の上には、層間絶縁膜として厚さ約0.3  $\mu$ mのシリコン酸化膜233が形成され、さらにその上には厚さ約200nmのシリコン酸化膜237が形成されており、このシリコン酸化膜237の上部に形成された金属配線238が、上記シリコン酸化膜233、237を貫通する開口部を介して金属配線238が、上記シリコン酸化膜233、237を貫通する開口部を介して金属配線232に接続されている。また、メモリセル上の王冠型キャパシタは、シリコン酸化膜214、231、233が除去されて形成された深い凹部内に形成されており、王冠形状の蓄積電極234の高さは約1 $\mu$ mと高く、キャパシタのプレート電極236は上記凹部内に埋め込まれて形成されている。

本実施例によれば、0.15平方ミクロンのメモリセル面積でも電荷蓄積用のキャパシタの蓄積容量を約50fFに大きくすることができ、S/N比が高く、ソフトエラー耐性の大きな動作安定性に優れたダイナミックRAM装置が得られた。しかし、本実施例において、さらに配線層の数を増加させて、王冠型の蓄積電極234の高さをさらに高くし、蓄積容量をさらに大きくできることはいうまでもない。

#### 実施例12

第90図は本実施例のDRAMの断面図である。第90図にに示したように、王冠型キャパシタのプレート電極241は、蓄積電極217の内側側面のすべておよび外側側面の一部(上部)を覆っている。本実施例のDRAMの製造方法の特徴は、上記実施例10、第85図に示した工程において、メモリセルアレー領域のシリコン酸化膜214、216を除去する際に、シリコン酸化膜219(第90図では239)のエッチングを途中で止め、第90図に示したように、蓄積電極217の外側では、膜厚が薄くなったシリコン酸化膜239が残るようにした点である。製造方法のその他の点は実施例10と同様である。本実施例によれば、シリコン酸化膜をエッチして凹部を形成する際のエッチングストッパ膜が不要になるので、シリコン酸化膜214の下のシリコン窒化膜212(実施例10、第76図)は不要である。

### 実施例13

第92図は本実施例のDRAMの断面図である。本実施例では、王冠型キャパシタのプレート電極219は、シリコン酸化膜216上に延在しているので、プレート電極219に電位を給電するための配線とは、上記シリコン酸化膜216の上において接続することができる。上記プレート電極219はホトリソグラフィとドライエッチングによりパターニングして形成されるが、この際のパターンのエッジの位置はすべてシリコン酸化膜216上になる。また、プレート電極219は凹部内にすべて埋め込む必要がなく、層間絶縁膜に用いるシリコン酸化膜220をキャパシタが形成されている凹部内に埋め込んで表面が平坦化されている。

本実施例によれば、プレート電極 2 1 9 と給電用の配線を、任意の位置で互いに接続することができ、設計の自由度が増し、チップ面積を縮小することができる。

なお、以上説明した各実施例では金属配線間の層間絶縁膜として、シリコン酸化物より誘電率が大きい膜を用いたが、シリコン酸化膜より誘電率が小さい材料の膜であってもよい。また、上記実施例では王冠型やトレンチ型のキャパシタを有する場合について説明したが、蓄積電極の厚さを厚くして、その上部および側部の表面にキャパシタ絶縁膜とプレート電極を形成した厚膜キャパシタのような立体構造のキャパシタにも応用することができる。

また、上記各実施例は本発明をDRAMに適用した例であるが、メモリセルにキャパシタを有するスタティックRAM、多結晶薄膜トランジスタ(TFT)をメモリセルの負荷素子に用いたスタティックRAM、さらにはキャパシタ絶縁膜に強誘電体を用いたメモリにも本発明が適用できる。また、デジタル回路のや、アナログ回路で一般にに用いられているスイチドキャパシタ、パスコンデンサ、レギュレータに用いる静電容量の大きなキャパ

10

20

30

40

シタなどにも応用できる。

さらに、本発明をメモリとロジックが混在したオンチップLSIに適用することによって、キャパシタが形成されている絶縁膜の位置にロジック部の配線層を形成することもできる。さらに、本発明によれば、キャパシタの位置に形成する周辺回路部の配線層に銅のような低抵抗の金属材料を用いることができ、高速動作が可能な半導体記憶装置がえられる

また、本実発明によれば、トレンチの深さを変えることによって、原理的にはどのような大きさの蓄積容量でも実現できる。しかも、基板にトレンチを形成する従来のトレンチ容量型セルと異なり、トレンチが形成される部分の平面積を大きくできるため、トレンチのアスペクト比を大きくする必要がなく、トレンチのみではなくキャパシタの形成が容易である。

さらに、キャパシタの蓄積電極は、キャパシタの下に形成された接続プラグを介して、MOSトランジスタの拡散領域と電気的に接続できるので、従来のトレンチ容量型セルの最大の課題の一つが解決された。また、トレンチのアスペクト比が大きくないため、シリコン酸化膜とシリコン窒化膜以外の絶縁膜をキャパシタ絶縁膜として使用することも容易である。

キャパシタの下部に配線層が設けられているため、最上層に引上げなければならない配線の数は大幅に低減され、その結果、引き上げる部分の配線の設計ルールは非常に緩やかになり、ギガビット級のメモリでも、16メガビットのルールである0.5 μ m 程度の設計ルールで十分である。

さらに、層間酸化膜の平坦化を容易に行うことができるため、リソフラフィ技術を用いて 微細なパターンを形成するのは容易である。

トレンチの深さを大きくすると、アスペクト比は大きくなるが、本発明ではトレンチが基板の上に形成されるため、トレンチを基板に形成する従来のトレンチ容量型セルに比べて、トレンチが形成される領域の面積をはるかに大きくすることができ、トレンチのアスペクト比は従来よりはるかに小さい。また、キャパシタの蓄積電極を、多結晶シリコンのプラグによって、拡散層と自動的に電気的接触させることができ、これにより、従来のトレンチ容量型セルの最大の課題が解消された。

また、キャパシタ絶縁膜として、シリコン酸化膜と窒シリコン化膜以外の絶縁膜を使用できるので、高い誘電率を有する誘電体をキャパシタ絶縁膜として使用することができ、容量が大きいにもかかわらず、アスペクト比の小さいトレンチキャパシタが実現される。 基板の上方にトレンチが形成されていると、配線を最上層まで引上げるのに必要な距離が

増大するが、本発明では配線層がキャパシタの下部に設けられ、最上層まで引上げなければならない配線の数が大幅に低減されしている。その結果、引き上げる部分の配線の設計ルールは非常に緩やかになり、ギガビット級のメモリでも、寸法は16メガビットのルールである0.5µm程度でよい。そのため、配線製造は極めて容易である。

さらには、各層間膜の表面の平坦化が容易なので、リソフラフィによって微細なパターン を容易に形成することができ、焦点裕度が小さい微細なパターンの形成に極めて有利であ る。

さらに、メモリセルアレー領域と周辺回路領域の間の段差の発生は大幅に緩和され、各領域および両領域をまたがる部分に微細な配線を形成することができるので、ソフトエラー耐性の高い、高信頼で高集積な半導体集積回路装置を形成することができる。

また、メモリセル領域と周辺回路領域の間に大きな段差が生じないので、上記両領域にそれぞれ、および両領域間を結ぶ微細配線を容易に形成できる。

〔産業上の利用可能性〕

以上説明したように、本発明は集積密度が極めて高い大容量のDRAMに好適である。

10

20

30

- 〇 ビット線コンタクト

- 蓄積容量コンタクト

● 蓄積容量コンタクト

● 蓄積容量コンタクト

周辺回路 -

# フロントページの続き

(72)発明者 阪田 健

東京都小平市小川西町4-7-11-401

(72)発明者 関口 知紀

東京都国分寺市西恋ケ窪4-14-6日立第4協心寮

(72)発明者 松岡 秀行

東京都保谷市住吉町6-8-25

# 審査官 正山 旭

(56)参考文献 特開平05-291526(JP,A)

特開平06-045553(JP,A)

特開平06-037272(JP,A)

特開平07-007084(JP,A)

特開平04-010651(JP,A)

特開平03-167874(JP,A)

特開平06-302764(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 21/8242

H01L 27/108