(19)

Bundesrepublik Deutschland

Deutsches Patent- und Markenamt

(10) **DE 699 18 503 T2 2004.11.18**

(12)

## Übersetzung der europäischen Patentschrift

(97) EP 0 985 494 B1

(21) Deutsches Aktenzeichen: 699 18 503.3

(96) Europäisches Aktenzeichen: 99 116 116.7

(96) Europäischer Anmeldetag: 18.08.1999

(97) Erstveröffentlichung durch das EPA: 15.03.2000

(97) Veröffentlichungstag

der Patenterteilung beim EPA: 07.07.2004

(47) Veröffentlichungstag im Patentblatt: 18.11.2004

(51) Int Cl.<sup>7</sup>: **B24B 7/22**

B24B 37/04, B24B 41/06

(30) Unionspriorität:

25360698 08.09.1998 JP

(84) Benannte Vertragsstaaten:

DE, FR, GB

(73) Patentinhaber:

Disco Corp., Tokio/Tokyo, JP

(72) Erfinder:

Kaneda, Yukihiro, Ohta-ku, Tokyo 144-0033, JP;

Takizawa, Shuichi, Ohta-ku, Tokyo 144-0033, JP

(74) Vertreter:

Vossius & Partner, 81675 München

(54) Bezeichnung: **Verfahren zum Schleifen von Halbleiterkörpern**

Anmerkung: Innerhalb von neun Monaten nach der Bekanntmachung des Hinweises auf die Erteilung des europäischen Patents kann jedermann beim Europäischen Patentamt gegen das erteilte europäische Patent Einspruch einlegen. Der Einspruch ist schriftlich einzureichen und zu begründen. Er gilt erst als eingelebt, wenn die Einspruchsgebühr entrichtet worden ist (Art. 99 (1) Europäisches Patentübereinkommen).

Die Übersetzung ist gemäß Artikel II § 3 Abs. 1 IntPatÜG 1991 vom Patentinhaber eingereicht worden. Sie wurde vom Deutschen Patent- und Markenamt inhaltlich nicht geprüft.

## Beschreibung

**[0001]** Die Erfindung betrifft ein Verfahren zum Schleifen eines Halbleiterwafers mit auf einer Oberfläche ausgebildeten Kontakthöckern bzw. Bondhügeln, insbesondere zum Schleifen der bondhügelfreien Oberfläche des Halbleiterwafers, so daß der Wafer auf eine vorgegebene Dicke geschliffen werden kann.

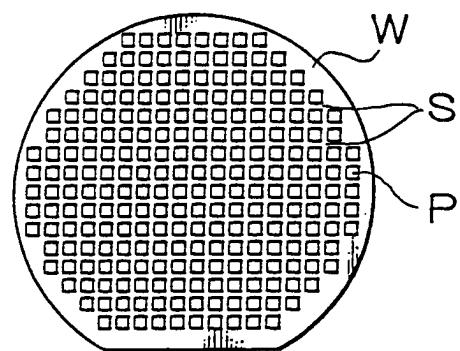

**[0002]** Wie aus **Fig. 8** erkennbar, kann durch Schneiden eines Halbleiterwafers W entlang kreuzweise angeordneten Ritzgräben S zum Trennen des Wafers in kleine Quadrate eine Vielzahl von Chips oder Einzelementen bereitgestellt werden, auf denen jeweils eine integrierte Schaltkreisstruktur ausgebildet ist. Vor dem Vereinzeln wird die Rückseite des Halbleiterwafers auf eine vorgegebene Dicke geschliffen, um seine Wärmespeicherkapazität zu verringern. Dadurch wird außerdem die Verkleinerungsanforderung erfüllt.

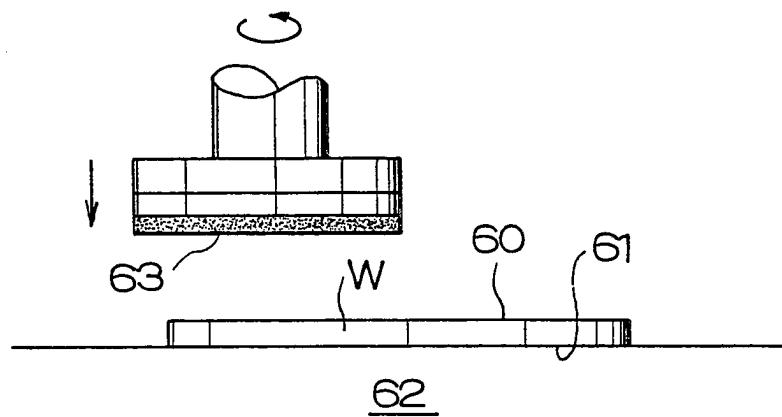

**[0003]** Wie aus **Fig. 9** erkennbar, wird die Vorderseite **61** des Halbleiterwafers W auf den Aufspannteller **62** einer Schleifvorrichtung aufgelegt und angesaugt, und auf die Rückseite **60** des Halbleiterwafers W wird unter einem vorgegebenen Druck eine Schleifscheibe **63** angewandt.

**[0004]** Das Schleifen kann auf gleiche Weise ausgeführt werden, gleichgültig um welche Art von Halbleiterchips es sich handelt: zu kapselnde Einzelchips für die Oberflächenmontage, wie z. B. extrem kleine Chipgehäuse (CSP) oder Chipgehäuse mit Lötpunkten (BGA) oder auf Leiterplatten zu montierende Nacktchips.

**[0005]** Auf derartigen Einzelchips P sind jedoch Bondhügel ausgebildet, um erforderliche Anschlüsse zu ausgewählten Elektroden in Leiterplatten herzustellen. Der Halbleiterwafer W wird geschliffen, wobei er mit seiner bondhügelfreien Rückseite nach oben auf den Aufspannteller **62** aufgelegt wird. Da der Halbleiterwafers W an den Aufspannteller **62** angedrückt wird, bricht er leicht durch die Beanspruchung, was durch die Bondhügel als Gegenkraft zu dem Schub verursacht wird, der dem Halbleiterwafer W durch die Schleifscheibe **63** erteilt wird.

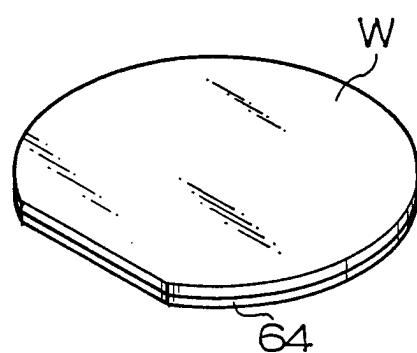

**[0006]** Bei einem Versuch, den Bruch des Halbleiterwafers zu verhindern, wird auf die Vorderseite des Halbleiterwafers W ein Klebeband **64** aufgebracht, wodurch die Bondhügel in der Dicke der Klebstoffschicht versenkt werden können, wie aus **Fig. 10** erkennbar. Ein derartiges Verfahren wird in JP-A-04-297 056 beschrieben. Die ungünstige Wirkung kann jedoch durch Rückgriff auf diese Maßnahme nicht völlig abgeschwächt werden, und noch schlimmer ist, daß nach Entfernen des Bands **64** von dem Halbleiterwafer der Klebstoff dazu neigt, mehr

oder weniger auf dem Halbleiterwafer W zurückzubleiben, wodurch die Qualität der Einzelchips erheblich vermindert wird.

**[0007]** Nach dem Bonden der Bondhügel an ausgewählte Elektroden einer Leiterplatte wird der Zwischenraum zwischen der Leiterplatte und dem Einzelchip gewöhnlich mit Harz gefüllt, wodurch die Kombination aus Einzelchip und Leiterplatte verfestigt wird. Um sicherzustellen, daß zwischen jedem Bondhügel und der Gegenelektrode eine gute elektrische Verbindung hergestellt wird, muß der Bondhügel 0,09 mm hoch sein; um aber die Möglichkeit eines Bruchs des Halbleiterwafers weitgehend zu verringern, muß der Bondhügel eine Höhe von 0,05 mm oder weniger aufweisen. Ungünstigerweise ist diese Notwendigkeit eine Ursache für unvollständiges Bonden zwischen Bondhügeln und Elektroden und führt zu Unterbrechungen zwischen Leiterplatte und Einzelchips.

**[0008]** Eine Aufgabe der vorliegenden Erfindung besteht darin, ein verbessertes Verfahren zum Schleifen von Halbleiterkörpern bereitzustellen. Diese Aufgabe wird mit dem Gegenstand der Ansprüche gelöst.

**[0009]** Ein Vorteil der vorliegenden Erfindung ist die Bereitstellung eines Verfahrens zum Schleifen von Halbleiterkörpern, ohne einen Bruch am Halbleiterwafer oder eine Verunreinigung mit Klebstoff zu verursachen, obwohl Bondhügel verwendet werden, die hoch genug sind, um ein gutes Bonden zwischen Bondhügeln und Elektroden sicherzustellen.

**[0010]** Ein erfindungsgemäßes Verfahren zum Schleifen von Halbleiterkörpern weist die folgenden Schritte auf: Trennen bzw. Vereinzeln eines Halbleiterwafers mit auf einer Oberfläche ausgebildeten Bondhügeln in separate Einzelchips; Auflegen der Chips auf eine Leiterplatte mit ihrer flachen, bondhügelfreien Oberfläche nach oben; Bonden jedes Einzelchips an einen ausgewählten Bereich der Leiterplatte mittels seiner Bondhügel, auf diese Weise Ausbilden einer Chip-Leiterplatte-Kombination; und Fixieren der Chip-Leiterplatte-Kombination auf dem Aufspannteller einer Schleifvorrichtung, um die flachen, bondhügelfreien Oberflächen der Einzelchips zu schleifen, bis sie eine vorgegebene geringere Dicke aufweisen.

**[0011]** Die Leiterplatte kann eine Platte sein, deren Oberfläche für die Montage von Elektronikteilen und Bauelementen vorgesehen ist.

**[0012]** Nach dem Bonden der Einzelchips an die Leiterplatte werden ihre flachen, bondhügelfreien Oberflächen geschliffen, und daher wird die Kraft, die durch die Schleifscheibe auf jeden Einzelchip ausgeübt wird, über die gesamte Oberfläche der Leiterplat-

te verteilt und auf diese Weise ein Bruch des Einzelchips verhindert, der sonst verursacht würde, indem man eine Eingrenzung der Kraft auf die Bondhügel des Einzelchips zuließe. Eine Verunreinigungsquelle, wie z. B. ein Klebstoff, ist nicht vorhanden, und die Höhe der Bondhügel braucht nicht verringert zu werden, um einen Bruch des Halbleiterwafers zu verhindern.

**[0013]** Alle Einzelchips des Halbleiterwafers können gleichzeitig auf die gleiche Dicke geschliffen werden, und daher ist sichergestellt, daß alle Einzelchips die gleiche Dicke aufweisen, wie für die Endprodukte erforderlich.

**[0014]** Das Schleifen von Einzelchips erfolgt nach dem Vereinzeln, und daher können winzige Späne, die beim Vereinzeln erzeugt wurden, während des Schleifens von den Einzelchips entfernt werden.

**[0015]** Weitere Aufgaben und Vorteile der vorliegenden Erfindung werden aus der nachstehenden Beschreibung einer bevorzugten Ausführungsform eines erfindungsgemäßen Schleifverfahrens für Halbleiterkörper verständlich, die in beigefügten Zeichnungen dargestellt ist.

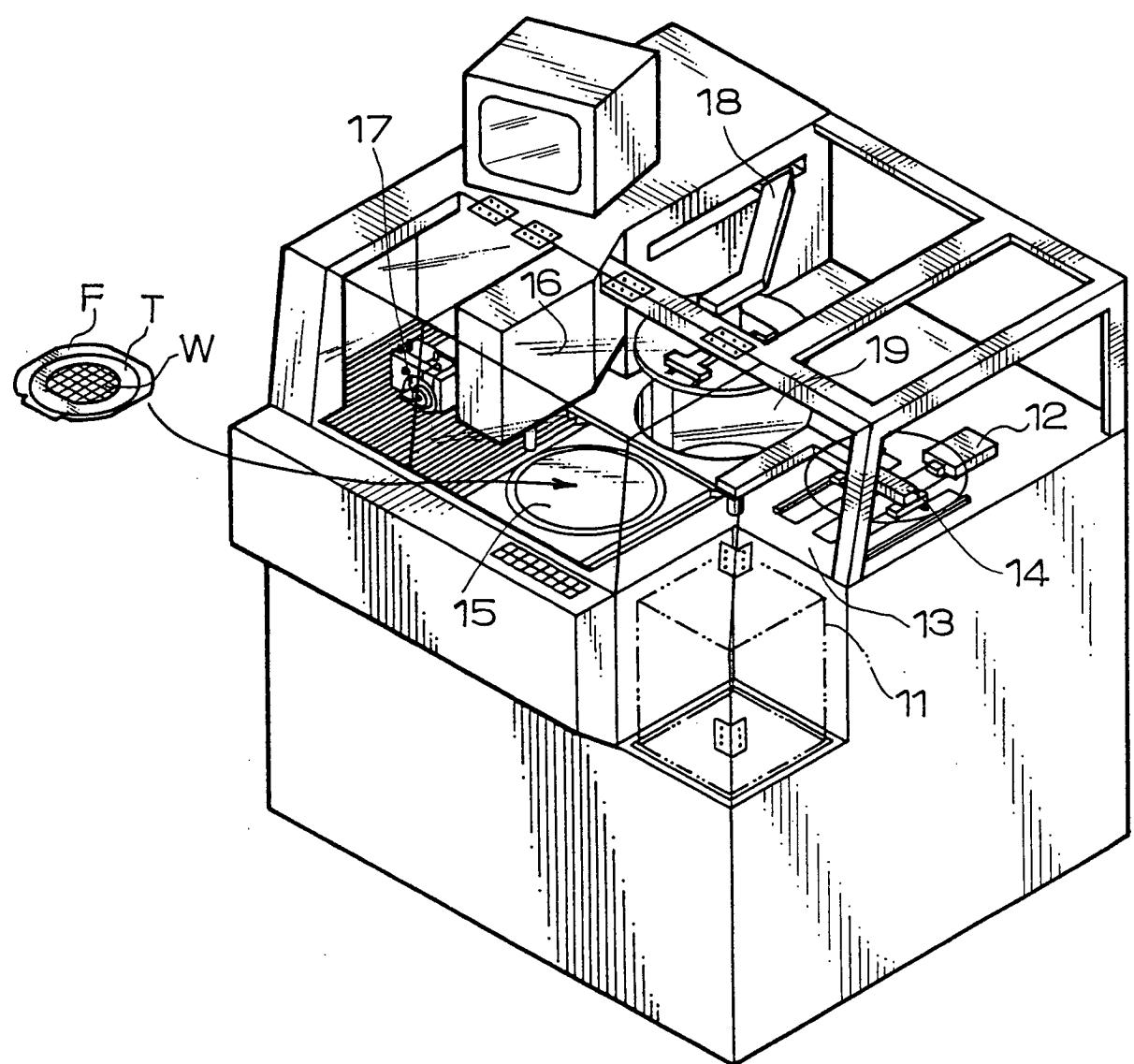

**[0016]** **Fig. 1** zeigt eine perspektivische Ansicht einer Trenn- bzw. Vereinzelungsvorrichtung, auf die das Schleifverfahren gemäß der vorliegenden Erfindung angewandt werden kann;

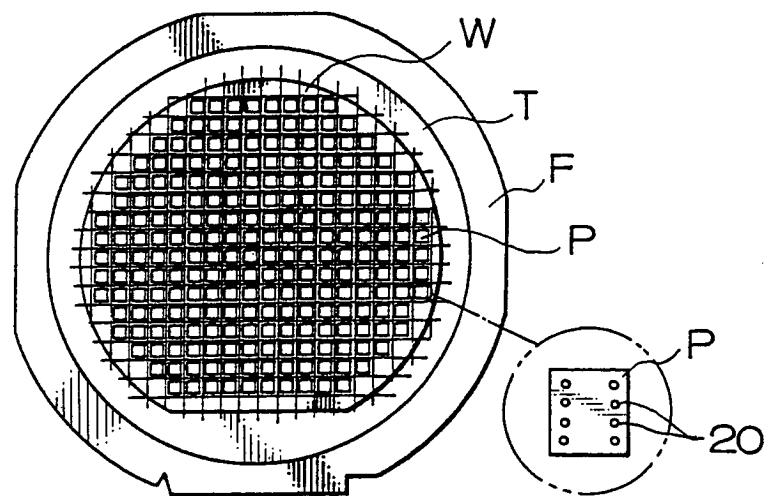

**[0017]** **Fig. 2** zeigt eine Draufsicht eines Halbleiterwafers, der durch die Vereinzelungsvorrichtung gemäß **Fig. 1** vereinzelt werden soll;

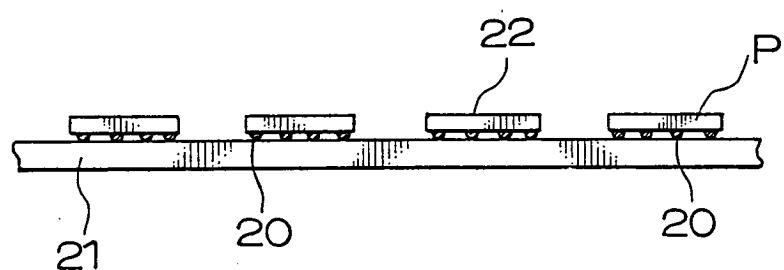

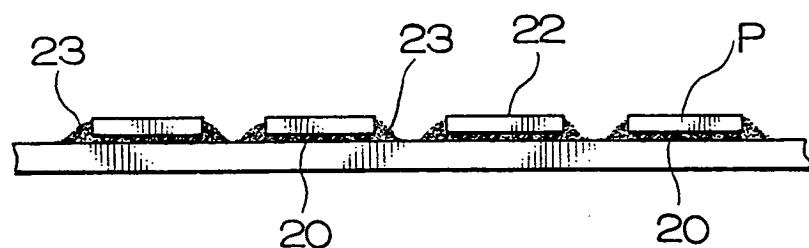

**[0018]** **Fig. 3** zeigt eine Seitenansicht einer CSP-Leiterplatte (Leiterplatte für extrem kleine Chipgehäuse) mit darauf gebondeten Einzelchips;

**[0019]** **Fig. 4** zeigt eine ähnliche Seitenansicht der CSP-Leiterplatte, deren Zwischenraum zwischen Einzelchips und Leiterplatte mit Harz gefüllt ist;

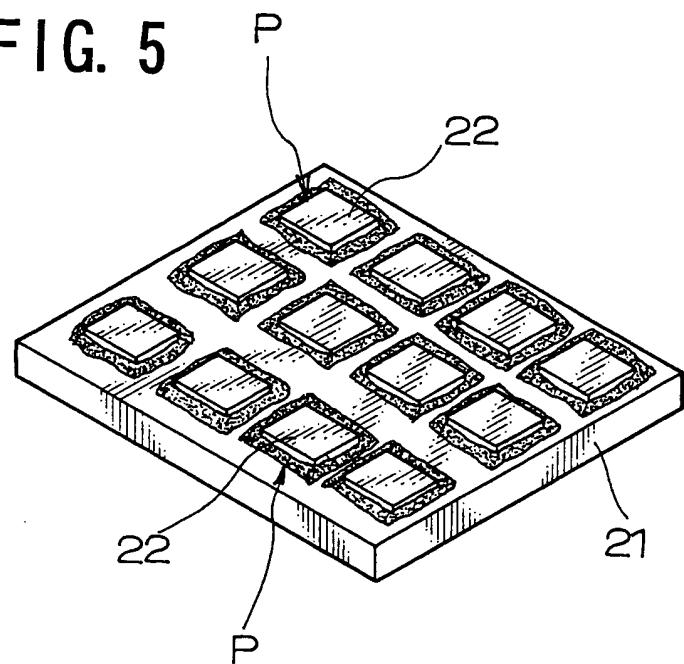

**[0020]** **Fig. 5** zeigt eine perspektivische Ansicht der CSP-Leiterplatte, deren Zwischenraum zwischen Einzelchips und Leiterplatte mit Harz gefüllt ist;

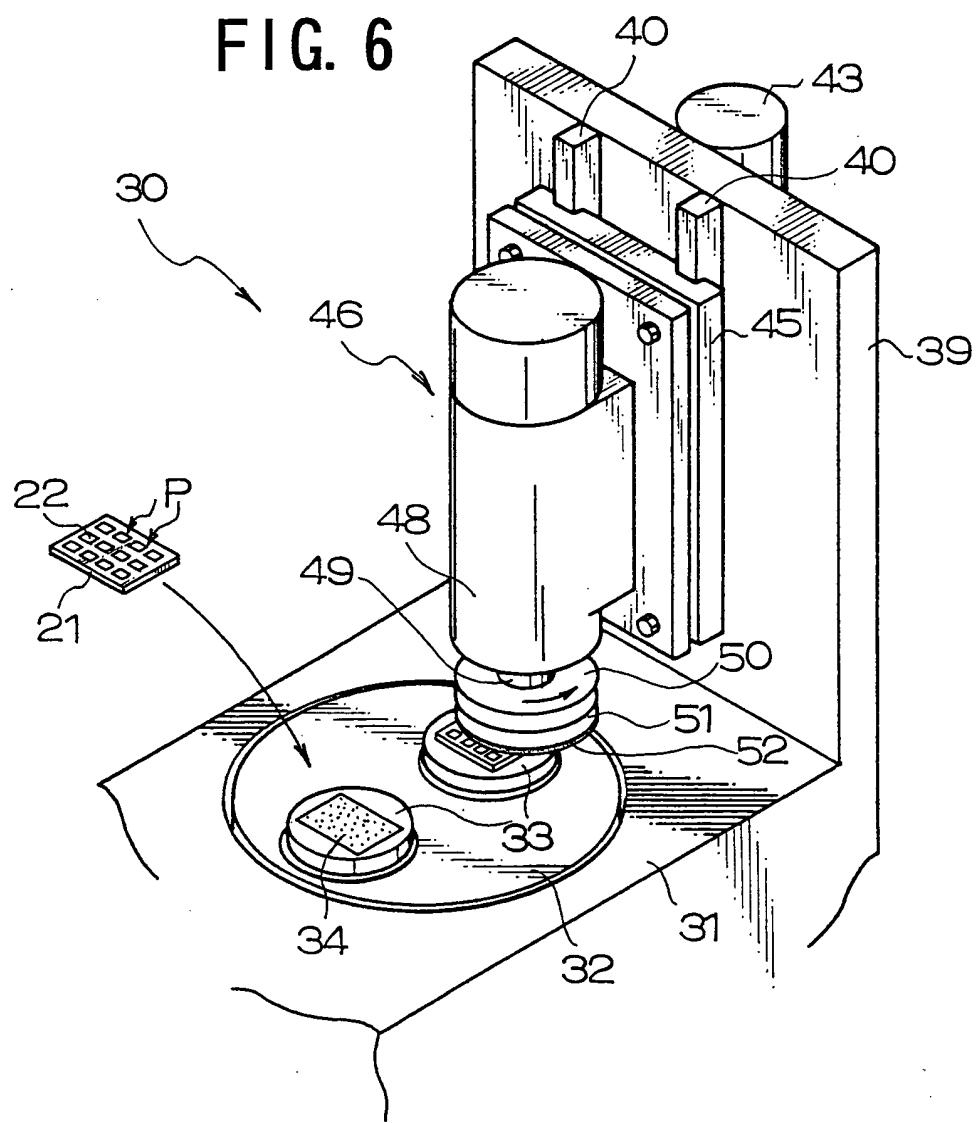

**[0021]** **Fig. 6** zeigt eine perspektivische Ansicht des Hauptschleifteils der Schleifvorrichtung;

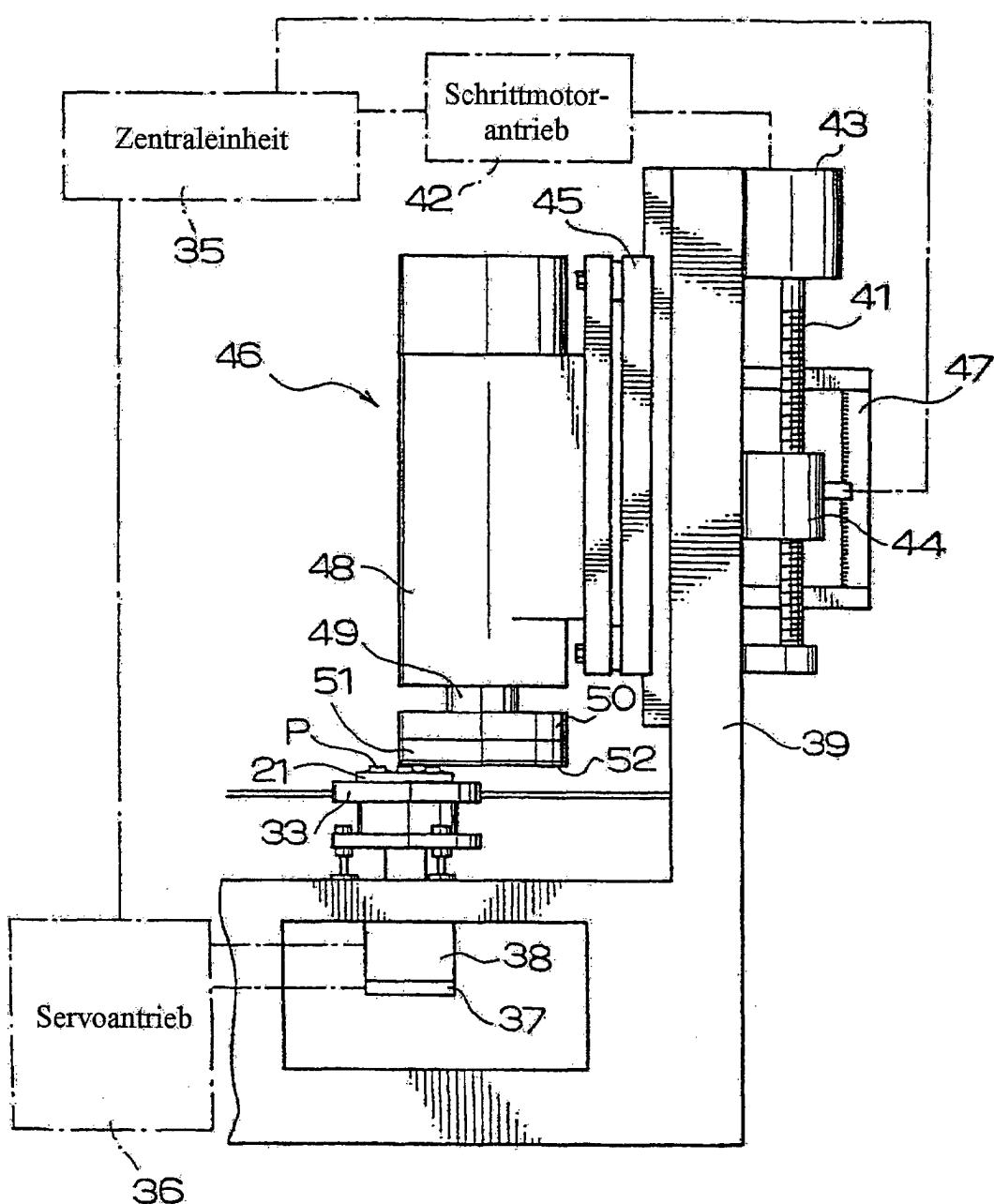

**[0022]** **Fig. 7** zeigt die Konstruktion der Schleifvorrichtung;

**[0023]** **Fig. 8** zeigt eine Draufsicht eines Halbleiterwafers;

**[0024]** **Fig. 9** veranschaulicht, wie die Rückseite des Halbleiterwafers geschliffen werden kann; und

**[0025]** **Fig. 10** zeigt eine perspektivische Ansicht eines Halbleiterwafers mit einem auf einer Seite aufgebrachten Klebeband zum Schutz seiner Bondhügel.

**[0026]** Im folgenden wird die vorliegende Erfindung unter Bezugnahme auf den Fall beschrieben, in dem Halbleiterchips oder Einzelchips an eine CSP-Leiterplatte gebondet werden, die Zwischenräume zwischen den Einzelchips und der Platte mit Harz gefüllt und die oberen Flächen der Einzelchips geschliffen werden.

**[0027]** Wie aus **Fig. 1** erkennbar, wird eine Trennvorrichtung **10** zu Zertrennen bzw. Vereinzeln von Halbleiterwafers **W** verwendet. Alle Halbleiterwafer **W** werden durch Klebebänder **T** an Trägern oder Rahmen **F** befestigt, und die Wafer-Rahmen-Kombinationen in einer Kassette **11** aufeinandergelegt.

**[0028]** Eine ausgewählte Wafer-Rahmen-Kombination wird durch eine Trägereinrichtung **12** aus der Kassette **11** zu einem vorläufigen Speicherbereich **13** transportiert, und dann wird die Wafer-Rahmen-Kombination an eine erste Transporteinrichtung **14** angesaugt. Die erste Transporteinrichtung **14** dreht sich, um die Wafer-Rahmen-Kombination zu einem Aufspannteller **15** zu bringen. Beim Auflegen der Wafer-Rahmen-Kombination auf den Aufspannteller **15** wird sie angesaugt und darauf festgehalten.

**[0029]** Dann wird der Aufspannteller **15** in Richtung der X-Achse bewegt, um die Wafer-Rahmen-Kombination unmittelbar unter eine Justiereinrichtung **16** zu bringen, so daß die kreuzweise angeordneten Ritzgräben **S** mit Hilfe des Mustervergleichsverfahrens erfaßt werden können. Auf diese Weise wird eine Trennscheibe **17** auf einen ausgewählten Ritzgraben **S** in Richtung der Y-Achse ausgerichtet. Danach wird der Aufspannteller **15** in Richtung der X-Achse bewegt, damit die Trennscheibe **17** den Halbleiterwafer **W** entlang dem ausgewählten Ritzgraben **S** trennen kann.

**[0030]** Das Trennen wird kreuzweise entlang den Ritzgräben **S** wiederholt, um den Halbleiterwafer **W** in kleine Quadrate oder Einzelchips zu trennen, wie aus **Fig. 2** ersichtlich (Vereinzelungsschritt). Jeder Einzelchip **P** weist mehrere Bondhügel **20** auf, wie aus dem eingekreisten Teil von **Fig. 2** erkennbar.

**[0031]** Die vereinzelten Wafer-Rahmen-Kombinationen werden durch eine zweite Transporteinrichtung **18** zu einer Waschstation **19** befördert, in der sie gewaschen werden. Danach werden sie durch Schleudern getrocknet, und die trockenen Artikel werden durch die erste Transporteinrichtung **14** transportiert, um in dem vorläufigen Speicherbereich **13** abgelegt zu werden. Schließlich werden sie durch die Trägereinrichtung **12** zur Kassette **11** transportiert.

**[0032]** Vereinzelte Wafer-Rahmen-Kombinationen werden nacheinander aus der Kassette **11** entnommen, und von den Klebebändern **T** werden Einzelchips **P** entfernt (Abnahmeschritt). Jeder Einzelchip **P** wird auf eine CSP-Leiterplatte **21** aufgelegt, wobei seine Bondhügel **20** auf ausgewählte Elektroden der Leiterplatte **21** aufgesetzt und die Bondhügel **20** an die Elektroden angelötet werden, wie aus **Fig. 3** erkennbar.

**[0033]** Abweichend von der herkömmlichen Reihenfolge, bei welcher der Bondschritt auf den Schleifschritt folgt, wird das Bonden ausgeführt, bevor die bondhügelfreien Oberflächen der Einzelchips **P** geschliffen werden, und daher bleibt jeder Einzelchip **P** dick genug, um sowohl dem Druck, der beim Bonden auf den Einzelchip **P** ausgeübt wird, als auch der Spannung zu widerstehen, die aufgrund der Wärmeausdehnung zwischen dem Einzelchip **P** und der CSP-Leiterplatte **21** entsteht. Daher ist nicht zu befürchten, daß die Einzelchips **P** beim Bonden reißen oder brechen.

**[0034]** Beim Bonden der Einzelchips **P** an die CSP-Leiterplatte **21** entsteht zwischen den Einzelchips **P** und der CSP-Leiterplatte **21** ein Zwischenraum von der Höhe der Bondhügel **20** (siehe **Fig. 3**). Der Zwischenraum wird mit Harz gefüllt, um die Einzelchips fest an der CSP-Leiterplatte **21** zu fixieren und die elektrische Leitung zwischen jedem Bondhügel und der Gegenelektrode zu sichern (siehe **Fig. 4**: Integrationsschritt).

**[0035]** Nach Beendigung der Vereinzelungs- und Integrationsschritte in der genannten Reihenfolge ergeben sich CSP-Leiterplatten **21**, auf denen jeweils mehrere Einzelchips **P** montiert sind, wie in **Fig. 5** dargestellt. Die flachen oder bondhügelfreien Oberflächen der Halbleiterchips oder Halbleiterkörper **P** können durch die Schleifvorrichtung **30** geschliffen werden, wie in den **Fig. 6** und **7** dargestellt.

**[0036]** In **Fig. 6** weist die Schleifvorrichtung **30** auf ihrem Bett **31** einen Drehtisch **32** auf, und auf dem Drehtisch **32** sind zwei Aufspannteller **33** angebracht. In jedem Aufspannteller **33** ist eine Saugfläche **34** ausgebildet, und eine ausgewählte CSP-Leiterplatte **21** wird mit der flachen oder bondhügelfreien Fläche jedes Einzelchips **P** nach oben auf die Saugfläche **34** aufgelegt und darauf angesaugt. Der Aufspannteller **33** kann durch einen Servoantrieb **36** und einen dazugehörigen Codierer **37** unter der Steuerung einer Zentraleinheit (CPU) **35** gedreht werden, wie aus **Fig. 7** ersichtlich.

**[0037]** In **Fig. 7** steht eine aufrechte Wand **39** an der Rückseite des Betts **31**, und an der Vorderseite der aufrechten Wand **39** sind zwei parallele Schienen **40** befestigt. An der Rückseite der aufrechten Wand **39** erstreckt sich in vertikaler Richtung eine Schrauben-

spindel **41**. Die Schraubenspindel **41** ist mit einem dazugehörigen Schrittmotor **43** verbunden, der durch einen von der CPU **35** gesteuerten Schrittmotorantrieb **42** angetrieben wird. Ein beweglicher Block **44** befindet sich im Gewindegang mit der Schraubenspindel **41**. Bei einer Drehung des Schrittmotors **43** unter der Steuerung der CPU **35** wird die Schraubenspindel **41** in Drehung versetzt, um den beweglichen Block **44** anzuheben oder abzusenken. Der bewegliche Block **44** ist mit einer Gleitplatte **45** an der Vorderseite der aufrechten Wand **39** verbunden. Die Gleitplatte **45** läuft auf den parallelen Schienen **40** und trägt eine Schleifeinheit **46**. Bei dieser Anordnung wird durch Drehung der Schraubenspindel **41** die Schleifeinheit **46** durch die Kombination aus dem beweglichen Block und der Gleitplatte auf und ab bewegt.

**[0038]** Die vertikale Position des beweglichen Blocks **44** kann an einer linearen Skala **47** bestimmt werden, die an der Rückseite der aufrechten Wand **39** befestigt ist. Als Reaktion auf die momentane Position der Schleifeinheit **46**, angegeben in Einheiten der linearen Skala **47**, führt die CPU eine genaue Steuerung der Vertikalbewegung der Schleifeinheit **46** aus.

**[0039]** Wie aus den **Fig. 6** und **7** erkennbar, weist die Schleifeinheit **46** eine Drehspindel **49** in ihrem Gehäuse **48** auf, und an der Spitze der Drehspindel **49** ist mittels einer dazugehörigen Halterung **50** eine Schleifscheibe **51** befestigt. Ein Teil der Schleifscheibe **51** wird von einem Schleifstein **52** gebildet.

**[0040]** Beim Schleifen der oberen Flächen **22** der Einzelchips **P** durch die Schleifvorrichtung **30** werden zwei CSP-Leiterplatten **21** jeweils auf die Saugflächen **34** der Aufspannteller **33** aufgelegt und angesaugt.

**[0041]** Der Drehtisch **32** wird um einen solchen Winkel gedreht, daß eine ausgewählte CSP-Leiterplatte **21** direkt unter der Schleifeinheit **46** angeordnet werden kann. Die Schleifeinheit **46** wird durch Drehen der Spindel **49** so abgesenkt, daß sie an die Einzelchips **P** anstößt, wodurch deren obere Flächen mit dem Schleifstein **52** um den gleichen Betrag abgeschliffen werden können (Schleifschritt).

**[0042]** Alle Einzelchips **P** werden an der CSP-Leiterplatte **21** befestigt, indem ihre Bondhügel an die Elektroden der Platte **21** angelötet werden und der Zwischenraum zwischen Einzelchips und Platte mit Harz gefüllt wird, und daher wird die Spannung, die durch den Angriff des Schleifsteins **52** an den Oberseiten der Einzelchips **P** verursacht wird, gleichmäßig über die gesamte Oberfläche der darunterliegenden Platte **21** verteilt. Auf diese Weise können keine Einzelchips **P** reißen oder brechen, während sie geschliffen werden, und daher können Einzelchips dünn-

ner geschliffen werden als bisher zulässig. Für den Schutz der Bondhügel ist kein Klebeband erforderlich, und daher ist nicht zu befürchten, daß die Qualität von Halbleiterprodukten durch den zurückbleibenden Klebstoff beeinträchtigt werden kann.

**[0043]** Vorteilhafterweise ist es unnötig, die Höhe der Bondhügel auf weniger als den erforderlichen Wert von etwa 0,09 bis 0,10 mm zu verringern, weil ein Bruch von Einzelchips befürchtet wird, der andernfalls beim Schleifen oft verursacht würde, wie man es beim herkömmlichen Verfahren erlebt. Wegen des Vorbondens und der Harzabdichtung können weder ein Bruch von Einzelchips noch eine Unterbrechung zwischen Elektroden und Bondhügeln hervorgerufen werden.

**[0044]** Außerdem ermöglicht das gleichzeitige Schleifen von Einzelchip-Leiterplatte-Kombinationen vorteilhafterweise, daß einzelne Halbleiterkörper eine genau gesteuerte gleiche Dicke aufweisen und daher alle Halbleiterprodukte von gleichmäßig hoher Qualität sein können.

**[0045]** Das Schleifen nach dem Vereinzeln ermöglicht, daß winzige Späne, die im Verlauf des Vereinzels entstehen, von den Einzelchips entfernt werden.

**[0046]** In dieser speziellen Ausführungsform wird das erfindungsgemäße Verfahren in der Anwendung auf eine CSP-Leiterplatte beschrieben, auf deren Oberfläche Halbleiterchips angebracht sind. Es kann ebenso auf eine BGA-Leiterplatte oder eine Flip-Chip-Leiterplatte angewandt werden.

**[0047]** Anstelle des Bondens und Verfüllens mit Harz können Bondhügel durch einen isotropen Leiter an Gegenelektroden gebondet werden.

### Patentansprüche

1. Verfahren zum Schleifen von Halbleiterkörpern, das die folgenden Schritte aufweist:

Vereinzeln eines Halbleiterwafers (W) mit auf einer Oberfläche ausgebildeten Bondhügeln (20) zu getrennten Einzelchips (P);

Aufsetzen der Einzelchips (P) auf eine Leiterplatte (21) mit ihren flachen, bondhügelfreien Oberflächen (22) nach oben;

Bonden jedes Einzelchips an einen gewählten Bereich der Leiterplatte (21) mittels seiner Bondhügel (20), wodurch eine Einzelchip-Leiterplatte-Kombination gebildet wird; und

Festhalten der Einzelchip-Leiterplatte-Kombination auf dem Aufspannteller (33) einer Schleifvorrichtung (30), um die flachen, bondhügelfreien Oberflächen (22) der Einzelchips (P) so zu schleifen, daß sie eine vorgegebene verminderte Dicke aufweisen können.

2. Verfahren nach Anspruch 1 zum Schleifen von Halbleiterkörpern, wobei die Leiterplatte (21) eine Platte ist, deren Oberfläche für die Montage von Teilen vorgesehen ist.

Es folgen 5 Blatt Zeichnungen

FIG. 1

FIG. 2

FIG. 3

FIG. 4

FIG. 5

FIG. 6

FIG. 7

FIG. 8

FIG. 9

FIG. 10