(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-507020

(P2004-507020A)

(43) 公表日 平成16年3月4日(2004.3.4)

(51) Int.Cl.<sup>7</sup>**G 11 C 5/00**

**G 06 K 19/077**

F 1

G 11 C 5/00

G 06 K 19/00

テーマコード(参考)

5 B 03 5

K

審査請求 未請求 予備審査請求 有 (全 31 頁)

(21) 出願番号 特願2002-520233 (P2002-520233)

(86) (22) 出願日 平成13年8月2日 (2001.8.2)

(85) 翻訳文提出日 平成15年2月14日 (2003.2.14)

(86) 國際出願番号 PCT/US2001/024245

(87) 國際公開番号 WO2002/015191

(87) 國際公開日 平成14年2月21日 (2002.2.21)

(31) 優先権主張番号 09/638,334

(32) 優先日 平成12年8月14日 (2000.8.14)

(33) 優先権主張国 米国(US)

(71) 出願人 503061108

マトリックス セミコンダクター インコ

ーポレイテッド

アメリカ合衆国 カリフォルニア州 95

054 サンタ クララ スコット ブー

ルヴァード 3230

(74) 代理人 100059959

弁理士 中村 稔

(74) 代理人 100067013

弁理士 大塚 文昭

(74) 代理人 100082005

弁理士 熊倉 穎男

(74) 代理人 100065189

弁理士 宍戸 嘉一

最終頁に続く

(54) 【発明の名称】モジュラーメモリデバイス

## (57) 【要約】

モジュラーメモリデバイス(10)は、支持素子(13)と、この支持素子により支持された三次元メモリアレーにより成るメモリユニットと、上記支持素子により支持されそして上記メモリユニットに接続されたデバイスインターフェイスユニット(18)と、上記支持素子により支持されそして上記デバイスインターフェイスユニットに接続された電気コネクタ(12)とを備えている。メモリアレーは、デジタル媒体、例えば、デジタルテキスト、デジタル音楽、デジタル像及びデジタルビデオのためのデジタル媒体記憶装置として使用するのに良く適している。デジタルインターフェイスユニットは、ある場合には必要とされない。

**【特許請求の範囲】****【請求項 1】**

支持素子と、

現場でプログラム可能な複数のメモリセルより成る三次元メモリアレーを含むメモリユニットであって、上記支持素子により支持されたメモリユニットと、

上記支持素子により支持されて上記メモリユニットに接続された電気コネクタとを備えたモジュラーメモリデバイス。

**【請求項 2】**

上記支持素子により支持されそして上記メモリユニット及び電気コネクタに接続されたデバイスインターフェイスユニットを更に備えた請求項 1 に記載の発明。 10

**【請求項 3】**

上記メモリユニット及びデバイスインターフェイスユニットは、単一の基体に製造され、そしてその基体は、上記支持素子により支持される請求項 2 に記載の発明。

**【請求項 4】**

上記デバイスインターフェイスユニットは、 $8 \text{ mm}^2$  以下の基体面積内に適合される請求項 2 に記載の発明。 20

**【請求項 5】**

上記メモリセルのメモリは、一度書き込みのメモリセルより成る請求項 1、2、3 又は 4 に記載の発明。

**【請求項 6】**

上記メモリセルは、基体  $1 \text{ mm}^2$  当たりのメモリセルの面積密度が  $3 \times 10^7$  以上の状態で基体上に配列される請求項 1、2、3 又は 4 に記載の発明。 20

**【請求項 7】**

上記メモリアレーは、デジタルテキスト、デジタル音楽、デジタル像、デジタル像のシーケンス、デジタルビデオ及びその組合せより成るグループから選択された少なくとも 1 つのデジタル媒体ファイルを記憶する請求項 5 に記載の発明。

**【請求項 8】**

上記メモリアレーは、デジタルテキスト、デジタル音楽、デジタル像、デジタル像のシーケンス、デジタルビデオ及びその組合せより成るグループから選択された少なくとも 1 つのデジタル媒体ファイルを記憶する請求項 6 に記載の発明。 30

**【請求項 9】**

現場でプログラム可能なメモリセルの複数のスタック層より成る三次元メモリアレーを含むメモリユニットを備え、

上記メモリセルは、各デジタル状態によって特徴付けられ、そのデジタル状態は、デジタル像、デジタル像のシーケンス、デジタルテキストのページのグループ、デジタル音楽、デジタルマップ、デジタルビデオ及びその組合せより成るグループから選択された少なくとも 1 つのデジタル媒体ファイルを表わすデジタル信号を記憶するものであるデジタル媒体メモリデバイス。

**【請求項 10】**

上記メモリセルは、一度書き込みのメモリセルである請求項 9 に記載の発明。 40

**【請求項 11】**

上記メモリセルは、基体  $1 \text{ mm}^2$  当たりのメモリセルの面積密度が約  $3 \times 10^7$  以上の状態で基体上に配列される請求項 9 に記載の発明。

**【請求項 12】**

上記メモリユニットを支持する支持素子と、

上記支持素子により支持されそして上記メモリユニットに接続されたデバイスインターフェイスユニットと、

上記支持素子により支持されそして上記デバイスインターフェイスユニットに接続された電気コネクタと、

を更に備えた請求項 9 に記載の発明。 50

**【請求項 1 3】**

上記メモリユニット及び上記デバイスインターフェイスユニットは、单一基体上に製造され、そしてその基体は、上記支持素子により支持される請求項 1 2 に記載の発明。

**【請求項 1 4】**

上記デバイスインターフェイスユニットは、 $8 \text{ mm}^2$  以下の面積内に適合される請求項 1 2 に記載の発明。

**【請求項 1 5】**

上記メモリセルの上記デジタル媒体ファイルを現場でプログラムするように動作するデジタル媒体記憶装置に組み合わされた請求項 1 5 に記載の発明。

**【請求項 1 6】**

上記記憶装置は、デジタルカメラを含む請求項 1 5 に記載の発明。 10

**【請求項 1 7】**

上記記憶装置は、デジタルオーディオ再生装置を含む請求項 1 5 に記載の発明。

**【請求項 1 8】**

上記記憶装置は、電子ブックを含む請求項 1 5 に記載の発明。

**【請求項 1 9】**

支持素子と、

基体上に形成されたメモリアレーより成るメモリユニットであって、上記支持素子により支持されたメモリユニットと、

上記メモリアレーと同じ基体上に形成されそして上記メモリユニットに接続されたデバイスインターフェイスユニットと、 20

上記支持素子により支持されそして上記デバイスインターフェイスユニットに接続された電気コネクタと、

を備えたモジュラーメモリデバイス。

**【請求項 2 0】**

上記デバイスインターフェイスユニットは、選択されたプロトコルに対して割り込み管理機能を実施する請求項 1 9 に記載の発明。

**【請求項 2 1】**

上記メモリアレーは、メモリセルの三次元アレーより成る請求項 1 9 に記載の発明。 30

**【請求項 2 2】**

上記メモリアレーは、メモリセルの二次元アレーより成る請求項 1 9 に記載の発明。

**【請求項 2 3】**

上記メモリアレーは、複数の一度書き込みメモリセルより成る請求項 1 9 に記載の発明。

**【請求項 2 4】**

上記一度書き込みメモリセルは、現場でプログラム可能である請求項 2 3 に記載の発明。

**【発明の詳細な説明】****【0 0 0 1】****【技術分野】**

本発明は、不揮発性ソリッドステートメモリアレーを含むモジュラーメモリデバイスに係る。 40

**【0 0 0 2】****【背景技術】**

種々のポータブル型消費者製品は、デジタルデータを捕獲して不揮発式に記憶する。デジタルカメラ及びデジタルオーディオプレーヤは、このような製品の2つの例である。この種の製品のメモリデバイスは、手のひらに載るに充分なほど小さくそしてユーザにより搬送容易なモジュラー装置であるのが好ましい。理想的には、これら記憶装置は、取り外し可能で且つ軽量でなければならず、そして数メガバイトの記憶容量を与えると共に低い実販売価格（ASP）を達成しなければならない。

**【0 0 0 3】**

このようなメモリデバイスに対する1つの公知の解決策は、フラッシュメモリカードとし 50

て知られている。このようなカードは、ユーザの手のひらにフィットし、軽量であり、そして消費者市場のポータブル装置部門のニーズにマッチする記憶容量を与える。しかしながら、フラッシュメモリカードは、この市場部門のコスト要求に充分応えるものではない。コンパクトフラッシュ（登録商標）カードのようなフラッシュメモリカードに対する2000年6月現在のメガバイト当たりのコストは、40メガバイトレベルで\$2ないし4（ASP）である。市場のポータブル装置部門におけるほとんどの消費者向けアプリケーションは、少なくとも40メガバイトの不揮発性記憶を必要とするので、フラッシュメモリカードは、装置全体のコストの顕著な部分を占める。

#### 【0004】

この市場部門に向けて製造される他のメモリカードは、マルチメディアカード（MMC）10を含み、その2000年6月現在のメガバイト当たりのコストは、\$3ないし5（ASP）である。これらメモリカードは、全て、従来の二次元メモリアレーを使用している。

#### 【0005】

##### 【発明の開示】

以下に述べる好ましい実施形態は、不揮発性デジタル記憶を要求する消費者アプリケーションのサイズ、重量、記憶及びコスト要件を満足するものである。これらの実施形態は、支持素子により支持されたメモリアレー及びメモリアレーコントローラと、支持素子により支持されてメモリアレーコントローラに接続された電気コネクタとを備えている。メモリアレーは、現場でプログラム可能な（フィールドプログラマブルな）一度書き込みの三次元メモリアレーであるのが好ましいが、必ずしもそうでなくてもよい。このようなメモリアレーは、ビット当たりのコストが実質的に減少されるという利点を發揮する。デバイスインターフェイスユニットが使用されるときには、コストを最小にするためにそれが高度に一体化されるのが好ましい。メモリユニット及びデバイスインターフェイスユニットの両方のコストを減少することにより、モジュラーメモリデバイスの全体的なコストが、上述した公知技術に比して実質的に減少される。20

このセクションは、一般的な導入部として設けられたもので、特許請求の範囲を何ら限定するものではない。

#### 【0006】

##### 【発明を実施するための最良の形態】

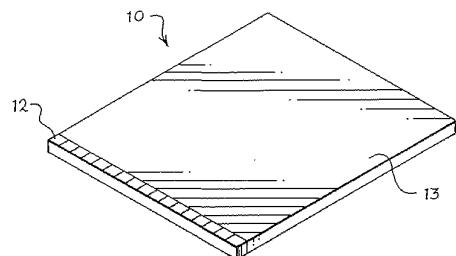

添付図面を参照すれば、図1は、電気コネクタ12を一端に備えたモジュラーメモリデバイス10の全体図である。メモリデバイス10の外面は、図示されたようにハウジング13内に包囲される。ハウジング13は、デバイス10の内部部品を保護し、そして消費者により容易に搬送され且つカメラや電子ブックのような読み取り／書き込み装置に容易に挿入及び除去されるコンパクトなモジュラーハンドヘルドユニットを形成する。コネクタ12は、いかなる適当な形態をとることもでき、この例では、一連の導電性パッドとして構成され、これらパッドは、相手コネクタ（図示せず）の対応コンタクトと嵌合するよう離間配置される。もちろん、いかなる適当なコネクタ12を使用することもでき、本発明は、図1に示されたエッジコネクタに限定されない。30

#### 【0007】

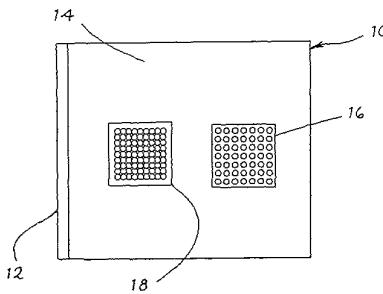

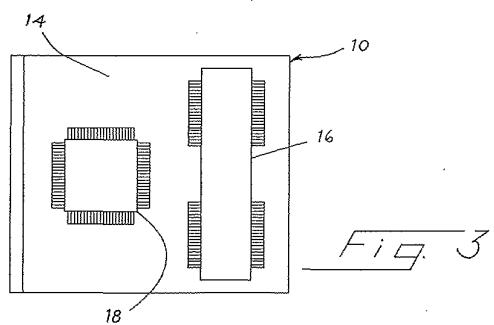

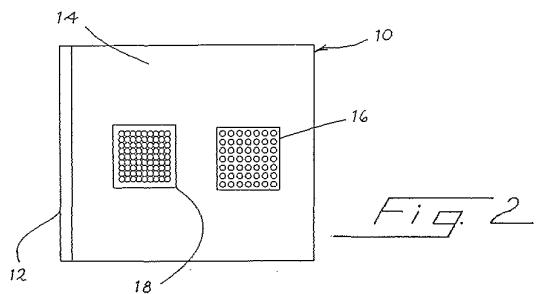

図2は、図1のデバイス10の断面図である。図2に示すように、デバイス10は、この実施形態ではプリント回路板14の形態をとる支持素子を備えている。プリント回路板14は、デバイス10の外面の1つを形成してもよい。プリント回路板14は、メモリユニット16、デバイスインターフェイスユニット18及び電気コネクタ12を支持する。40

#### 【0008】

メモリユニット16は、三次元メモリアレー及びそれに関連したメモリアレーコントローラを含むのが好ましい。好ましいメモリアレーは、基体上に三次元格子に配列された適当な数のメモリセルを含む。ジョンソン氏の米国特許第6,034,882号、クナル氏の米国特許出願第09/560,626号及びジョンソン氏の米国特許出願第09/638,428号に開示された三次元メモリを、メモリアレーとして使用することができる。これら特許文献は、全て、本発明の譲受人に譲渡されたもので、参考としてここに援用する50

。メモリアレーコントローラは、メモリアレーが形成される同じ基体上に形成されるのが好ましく、そしてメモリアレーコントローラは、アドレスデコード回路、読み取り動作のための感知回路、書き込み動作のためのドライブ回路、及びI/O増幅器を含むI/Oインターフェイス回路を備えている。

#### 【0009】

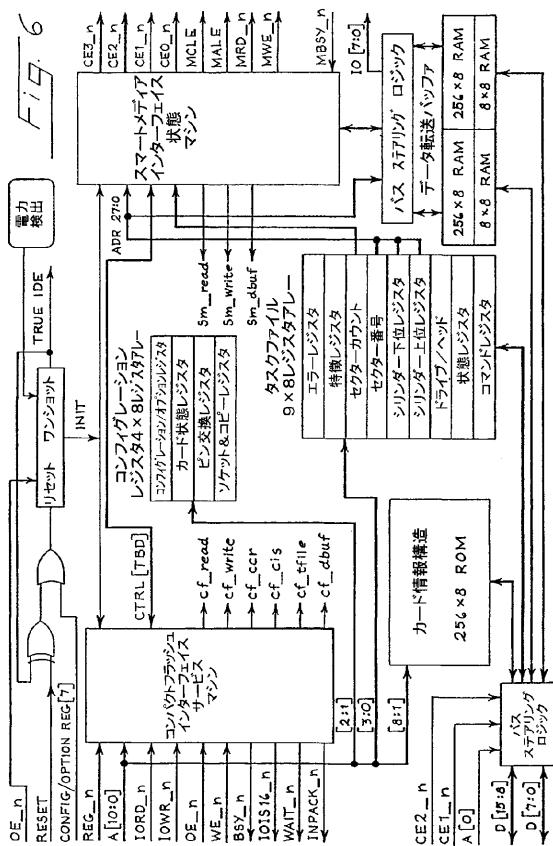

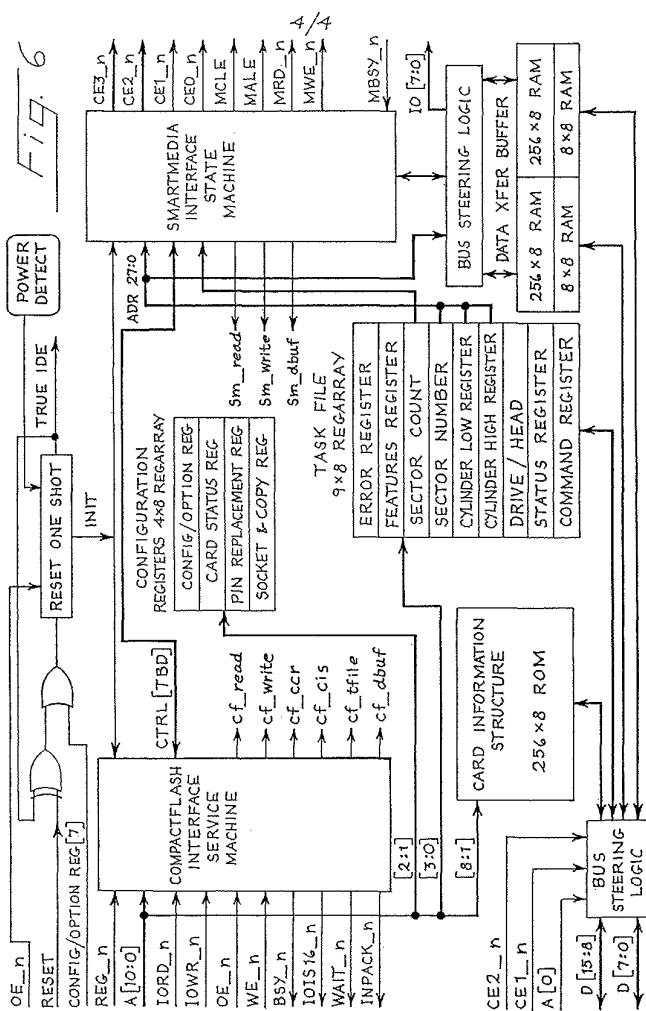

この実施形態のデバイスインターフェイスユニット18は、個別の基体に形成され、そしてプリント回路板14を経てメモリユニット16及び電気コネクタ12に電気的接続される。この実施形態では、メモリユニット16及びデバイスインターフェイスユニット18は、プリント回路板に直接取り付けられる。デバイスインターフェイスユニット18は、シリコン基体の單一片に全てが集積される種々の消費者装置にメモリデバイス10を取り付けられるようにする電圧、クロック周波数及びプロトコルロジックを形成するのに必要な全ての部品を備えている。1つの実施形態では、デバイスインターフェイスユニット18は、使用するプロトコル（例えば、コンパクトフラッシュプロトコルのようなプロトコル）に含まれるタスクファイル、割り込み管理、エラーレポート及びコンフィギュレーションファンクションを実施するための回路（ハードウェア、ソフトウェア及びファームウェアの適当な組合せを使用する）を備えている。

#### 【0010】

図3は、図2の実施形態の変形を示す。図3の実施形態では、デバイスインターフェイスユニット18及びメモリユニット16は、この分野で知られたT S O P又はT Q F Pパッケージのような従来の中間チップパッケージに梱包される。これらのパッケージされた素子は、次いで、従来のやり方でプリント回路板14に組み立てられる。

#### 【0011】

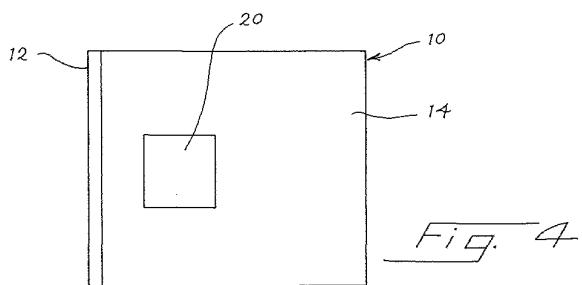

図4の実施形態では、三次元メモリアレー、メモリアレーコントローラ及びデバイスインターフェイスユニットが单一基体20に製造され、これが、中間パッケージをもたずにプリント回路板14に直接取り付けられるのが好ましい。メモリアレーコントローラ及びデバイスインターフェイスユニットは、三次元メモリアレーの下でシリコン基体に製造することができる。この構成は、メモリデバイスの製造コストを減少する。この場合に、メモリアレーコントローラは、上述したI/O増幅器を必要としない。

#### 【0012】

図4の実施形態は、コンパクトフラッシュプロトコルを使用するもののようなアプリケーションに良く適している。この実施形態は、不揮発性メモリセルの二次元又は三次元メモリアレーで実施することができる。

最低コストのコントローラを形成するために、メモリユニット16を所望の標準メモリカードにインターフェイスするのに必要な信号の合計数が決定される。シリコンチップ内部の電源システムを、あらゆる動作条件の下で欠陥のない動作を保証するに充分なほど安定した状態に保持するに必要な電力及び接地接続の数が、次いで、このリストに加えられる。このピンカウント情報は、必要な接続の数を収容する最小の長方形を決定する。この長方形の大きさは、ピン数の1/4と、ピン駆動回路の高さ及び巾の関数である。その結果生じるエッジの長さは、次の式で表わされる。

$$\text{長さ} = (\text{ピン数} / 4) \times \text{ピン駆動回路の巾} + 2 \times \text{ピン駆動回路の高さ}$$

$$\text{ダイ面積} = \text{長さ}^2$$

#### 【0013】

この長さの式が最小にされると、必要なダイ面積がセットされる。次いで、メモリユニット16を選択された標準システムバスに接続するのに必要な所要のロジック機能及び所要の電力又はクロック回路を形成するのに使用可能な面積を、次の式により決定することができる。

$$\text{使用可能な面積} = ((\text{ピン数} / 4) \times \text{ピン駆動回路の巾})^2$$

次いで、必要なコンポーネントの数をコンポーネントの密度で除算したものが上記式の使用可能な面積の計算値に等しくなるように、適当なロジック密度を与えるシリコンプロセス技術が選択される。

10

20

30

40

50

**【 0 0 1 4 】**

上記実施形態では、メモリセルが二次元ではなく三次元に編成されそして形成される。メモリセルの層は多数あり、これらの層は、垂直方向に互いに上下にスタックされる。3つの次元は、「行」、「列」及び「層」と称される。典型的に、行及び列は、その下の基体の上面に一般的に平行であり、そして層は、その下の基体の上面に垂直な方向に沿って互いに離間される。

あるメモリセルは、上方又は下方のいずれかに突出する素子を含み、過去において、「三次元メモリセル」と称されている。しかしながら、これらのメモリセルは、従来の二次元アレーに配列される。これは、メモリセルの多数の層が垂直方向に互いに上下にスタックされたメモリセルの三次元アレーを含むここに開示する三次元実施形態とはかなり相違する。

**【 0 0 1 5 】**

これら実施形態の顕著な特徴は、低コスト三次元編成であることの代わりに、メモリの動作速度を明らかに低下させることである。これら実施形態は、小さなメモリセル及び小さな全チップ面積が与えられると、非常に小さなスイッチングデバイスを使用する。又、小さなスイッチングデバイスは、小さな読み取り電流を与え、これは、読み取リアクセス時間を比較的低速にする。しかしながら、低速のアクセス時間を容易に許容し、そして劇的に安いメモリのコストから多大な利益を引き出す重要なメモリアプリケーションが多数ある。これら低速アプリケーションの多くは、「デジタル媒体記憶」という名の下に集合され、そして次のものを含む。即ち、写真のような静止像のデジタル記憶、音楽及び一般にデジタルオーディオのデジタル記憶、デジタルブック、マップのデジタル記憶、デジタルビデオを含む像のシーケンス、及び当業者に容易に明らかな多数の他の例。デジタル媒体記憶アプリケーションは、版権取得できる資料を有形の表現媒体に固定できるようにする記憶アプリケーションとみなすことができる。このようなアプリケーションの場合、記憶媒体を再書き込みできることは、利点ではなく、実際には、不所望なことすらある。例えば、表現された資料の明確で且つ不变の記録をもつことが重要である。更に、再書き込み可能なメモリデバイスよりも一度書き込みの方がコストは一般的に低い。

**【 0 0 1 6 】**

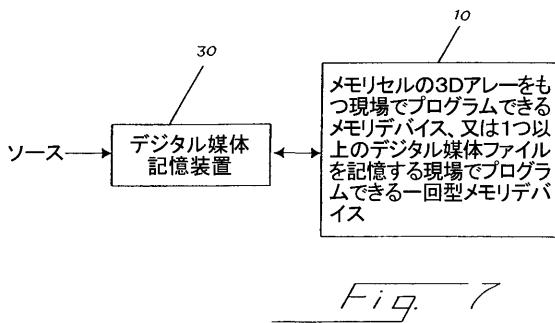

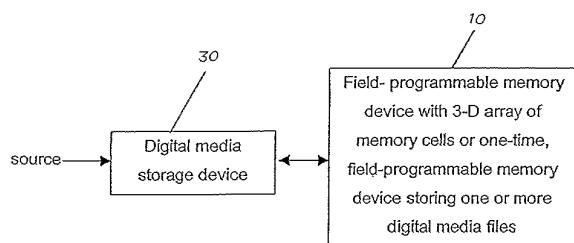

図7は、デジタル媒体記憶装置30と組み合わせて上記メモリデバイス10をロック図の形態で示す。メモリデバイス10は、ここに述べるいかなる形式をとることもでき、そして現場でプログラム可能な一度書き込みのメモリセルの3Dアレーを含むのが好ましい。上述したように、このようなデバイスは、著しく低コストであるという利点を与える。メモリデバイス10は、ユーザがこのメモリデバイス10をデジタル媒体記憶装置30に容易に接続したり取り外したりできるようにする上述した外部コネクタを伴うモジュラーハンドヘルドユニットとして形成される。メモリデバイス10の構造に関する更なる詳細は、米国特許出願第09/638,439号及び第09/638,427号に開示されており、これらは両方とも、本出願と同日に出願され、本発明の譲受人に譲渡され、そしてその全体を参考としてここに援用するものである。別の実施形態においては、米国特許出願第09/639,702号及び第09/639,577号に開示されたような多数書き込み3Dアレーが使用され、これら出願も、本出願と同日に出願され、そして本発明の譲受人に譲渡されたものである。

**【 0 0 1 7 】**

デジタル媒体記憶装置30は、いかなる適當な形態をとることもでき、そして例えば、デジタルカメラ、デジタルオーディオ再生装置、又は電子ブックである。この記憶装置30は、2つの個別の機能を遂行する。第1に、記憶装置30は、例えば、静止像又は移動像を示すか、オーディオファイルを再生するか、又は電子ブックのページを表示することにより、メモリデバイス10に記憶されたデジタル媒体をユーザに表示する。第2に、記憶装置30は、メモリデバイス10を所望のデジタル媒体情報で現場でプログラムするよう使用できる。このため、デジタル媒体記憶装置30は、ソースに接続され、そしてソースからメモリデバイス10へデジタル媒体情報を現場でプログラムする。デジタル媒体ソ

10

20

30

40

50

ースは、いかなる適當な形態をとることもでき、そして別のコンピュータ（図示せず）をしばしば含む。例えば、ソースは、インターネットのようなネットワークを経て或いはレコード店や書店のような店舗に設けられたシステムを経て記憶装置30へデジタル媒体情報を供給し、消費者が所持するメモリデバイス10にデジタル媒体をダウンロードすることができる。又、デジタルデータのソースは、デジタルカメラの場合のように電荷結合装置アレー（CCD）の出力、又は音楽再生・記録装置の場合のようにコーダ・デコーダ（CODEC）の出力を含んでもよいが、これに限定されない。あるアプリケーションでは、ソースは、デジタル媒体記憶装置30を経てではなく直接的にメモリデバイス10にデジタル媒体情報を記憶してもよく、これは、現場でプログラム可能であることの別の例である。一般的に、「現場でプログラム可能（フィールドプログラマブル）」という語は、メモリデバイスの製造が完了した後の時間にユーザにより選択されたファイルをメモリデバイスに書き込むことも包含すると広く解釈される。10

#### 【0018】

ここに説明する実施形態のメモリアレーは、メモリセルの多数の層の垂直スタックを備え、メモリセルは、いかなる所望の形態をとることもでき、ツアン氏の米国特許第5,835,396号、ジョンソン氏の米国特許第6,034,882号及びクナル氏の米国特許出願第09/560,626号に教示されたメモリセルが一例として取り上げられる。しかしながら、ここに述べる好ましい実施形態は、コストを最小にするように設計されており、それ故、メモリセルは、できるだけ小さくされる。

#### 【0019】

メモリセルを小さくするために、微細ピッチのホトリソグラフィーを使用してメモリセルの幾何学的形状がパターン化される。より詳細には、ワード線及びビット線は、約1ミクロン以下の線巾及び約1ミクロン以下の線・線間隔で形成されるのが好ましい。これらF（ホトリソグラフィック特徴サイズ）の値は、更に減少されてもよく、即ち、線巾及び間隔は、約0.25ミクロンより小さいのが更に好ましい。20

#### 【0020】

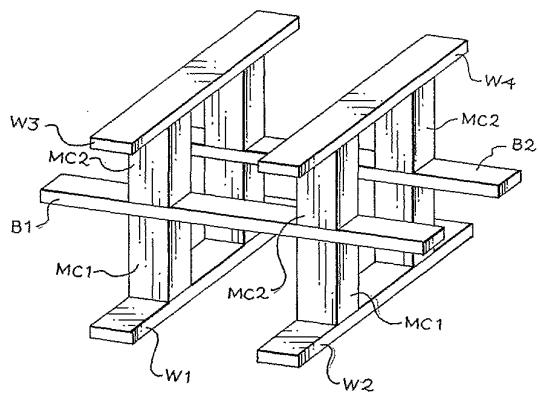

図5は、上述した形式のメモリアレーの一実施形態を示す概略図である。メモリセルMC1、MC2の各々は、状態記憶素子を含む2端子セルである。この実施形態では、メモリセルMC1は、第1レベルに配置され、そしてメモリセルMC2は、第1レベルに対して垂直方向にスタックされた第2レベルに配置される。メモリセルMC1、MC2の端子は、セルの各端に配置される。この点について、「端子」という語は、広く解釈されるべきであり、そして端子は、単にセルの端子部分として実施されてもよいし又はセルの個別層として実施されてもよい。30

#### 【0021】

各メモリセルMC1、MC2の各端子は、各導体又はワイヤと電気的接触する。図5において、メモリセルMC1の下部の導体W1、W2は、ワード線として構成され、そしてメモリセルMC1の上部端子に接続された導体B1、B2は、ビット線として構成され、これらのビット線は、この実施形態では、ワード線W1、W2に実質的に垂直に延びる。従って、メモリセルMC1の各々は、ワード線W1、W2の選択されたものと、ビット線B1、B2の選択されたものをブリッジ接続する。40

#### 【0022】

同様に、第2層のメモリセルMC2は、ビット線B1、B2の選択されたものと、ワード線W3、W4の選択されたものとの間に接続される。この実施形態のワード線W3、W4は、垂直方向にビット線B1、B2のレベルより上にスタックされた別のレベルに配置される。

図5のメモリセルアレーは、基本的な幾何学形状及び材料が、上記ジョンソン氏の特許の図6aないし6gに示されたものと同様でよい。

#### 【0023】

平面図での基本的セルサイズが2F×2Fである実施形態の場合（上記ジョンソン氏及びクナル氏の特許文献に教示されたような）、メモリセルのピッチ（100個の隣接セルの50

全巾を 100 で除算した) は、ワード線又はビット線の方向に約 0.50 ミクロン以下(及び一般的には 2 ミクロン以下)であるのが好ましく、そしてメモリセルにより消費される全面積は、約 0.25 平方ミクロン以下であるのが好ましい。従って、消費されるチップ面積は、垂直スタッツの各層において百万ビット当たり約 0.25 平方ミリメーター以下である。同じ結果を別の言い方で述べると、パッキング密度が、垂直スタッツの各層において平方ミリメーター当たり 4 百万ビット以上である。

#### 【0024】

垂直方向にスタッツすると、所与のサイズのメモリアレーに対して密度が高くなりそしてチップ面積が減少し、即ち 8 層のメモリセルが垂直方向に互いに上下に積層された好ましい実施形態では、密度が、チップ面積 1 平方ミリメーター当たり 3 千 2 百万ビット以上となる。

微細ピッチのリソグラフィーが改善されるので、これらのメモリセルの密度も改善される。次の式は、特徴サイズが F のリソグラフィー世代の場合であって、 $2F \times 2F$  セルの N 層が垂直にスタッツされた場合に、単位面積当たりのパッキング密度(ビット)を示している。

$$\text{パッキング密度} = N / (4F^2)$$

#### 【0025】

パッキング密度が低い本発明の他の実施形態は、 $4F^2$  より大きなメモリセル(例えば、上記ツアン氏の特許の図 6B に示されたメモリセルを参照されたい)を使用できることに注意されたい。これらの大きなメモリセルは、チップ面積が大きくなり、従って、あまり望ましくない。

デバイスインターフェイスユニット 18 の好ましい実施形態が図 6 にブロック図で示されている。この例では、コンパクトフラッシュインターフェイス状態マシンが、コンパクトフラッシュプロトコルに対するタスクファイル、割り込み管理、エラーレポート、及びコンフィギュレーションファンクションを実施し、そしてスマートメディアインターフェイス状態マシンが、スマートメディアプロトコルに対するこれらの機能を実施する。これらの両プロトコルは、当業者に容易に入手できる。図 6 のデバイスインターフェイスユニットは、大きさが  $2.68\text{ mm} \times 2.68\text{ mm}$  で、 $7.18\text{ mm}^2$  の全基体面積を与えるシリコンダイに形成することができる。1 つの実施形態では、上述したモジュラーメモリデバイス 10 を使用して、デジタル媒体、例えば、上記のいずれかのデジタル媒体が記憶される。

#### 【0026】

別の実施形態では、デバイスインターフェイスユニット 18 がデバイス 10 から削除され、そしてメモリユニット 16 のメモリアレーコントローラがプリント回路板 14 によりコネクタ 12 に直接接続される。この場合に、メモリユニット 16 は、ホストシステムのデバイスインターフェイスユニットによって制御される。

上記実施形態は、3D メモリアレーに向けられたが、別のコスト節減実施形態は、一回プログラム式(O T P)アレーを使用することに向けられる。例えば、電子的にプログラム可能なリードオンリメモリ(P R O M)を使用することができる。このような O T P メモリと、従来の E<sup>2</sup> P R O M 及びフラッシュメモリとの間のコストの差は、相当のものである。

#### 【0027】

3D の一回プログラム式、3D の多数書き込み、又は 2D の O T P の場合に、種々のハウジング材料及びコンフィギュレーションのいずれを使用することもできる。適当な材料は、金属、エポキシ、セラミック、及びプラスチックである。コンフィギュレーションは、従来、フラッシュメモリ又は E<sup>2</sup> P R O M メモリと共に使用されていた標準的モジュールに適合するもの、又は将来開発される規格に適合するものを含む。これらは、コンパクトフラッシュ、スマートメディア、マルチメディアカード、セキュアデジタルミュージックイニシエーティブ(S D M I)、ソニーメモリスティック及び他の規格を含むが、これらに限定されない。コンフィギュレーションは、個別又は非一体化のデバイスインターフェ

10

20

30

40

50

イスユニットを含むことができる（即ち、デバイスインターフェイスユニットは、設計上の選択の問題としてメモリユニットチップと一体化されてもよいし又はされなくてもよい）。モジュールは、パッケージされたダイの周りに形成することもできるし、又は各ダイを基体上に直接取り付け、次いで、基体をハウジング内にカプセル封入することもできる。基体は、シリコン、ファイバーガラス又はセラミックであるが、これらに限定されない。

#### 【0028】

以上の説明から、低いコストで製造することができ、小型で且つ軽量であり、そして不揮発性メモリの必要な容量を与える改良されたモジュラーメモリデバイスが提供されたことが明らかであろう。

10

ここで使用した「接続」という語は、直接的に接続される素子及び間接的に接続される素子を含むものと広く解釈されたい。従って、互いに接続される2つの素子は、介在する無名の素子によって接続されてもよい。

#### 【0029】

以上の詳細な説明は、本発明がとり得る多数の形態の若干を説明したに過ぎない。このため、この詳細な説明は、例示に過ぎず、これに限定されるものではない。全ての等効物を包含する特許請求の範囲のみが本発明の範囲を規定する。

#### 【図面の簡単な説明】

【図1】本発明の好ましい実施形態によるモジュラーメモリデバイスの斜視図である。

20

【図2】図1のメモリデバイスの断面図である。

【図3】図1のメモリデバイスの別の実施形態の断面図である。

【図4】図1のメモリデバイスの別の実施形態の断面図である。

【図5】三次元メモリアレーの一部分を示す概略図である。

【図6】図2のデバイスインターフェイスユニット18の好ましい実施形態を示す回路図である。

【図7】デジタル媒体記憶システムに接続されたモジュラーメモリデバイスのブロック図である。

【 四 6 】

【図7】

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

21 February 2002 (21.02.2002)

PCT

(10) International Publication Number

**WO 02/15191 A1**(51) International Patent Classification<sup>7</sup>: G11C 5/06, 5/02 (74) Agent: WEBB, William, A., Brinks Hofer Gilson & Lione, P.O. Box 10087, Chicago, IL 60610 (US).

(21) International Application Number: PCT/US01/24245

(22) International Filing Date: 2 August 2001 (02.08.2001)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

09/638,334 14 August 2000 (14.08.2000) US(71) Applicant: MATRIX SEMICONDUCTOR, INC.

[US/US]; 3230 Scott Boulevard, Santa Clara, CA 95054

(US).(72) Inventors: TRINGALI, J., James, 105 Jordan Avenue,

Los Altos, CA 94022 (US); FARNWALD, P., Michael,

190 Golden Oak Drive, Portola Valley, CA 94028 (US);

LEE, Thomas, H., 939 Bubb Road, Cupertino, CA 95014

(US); JOHNSON, Mark, G., 125 Admire Way, Los Altos,

CA 94022 (US); BOSCH, Derek, J., 765 N. Rengstorff

Avenue #104, Mountain View, CA 94041 (US).

(81) Designated States (national): AE, AG, AL, AM, AT, AU,

AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU,

CZ, DE, DK, DM, DZ, EC, EB, ES, FI, GB, GD, GE, GH,

GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC,

LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW,

MX, MZ, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SI, SK,

SL, TJ, TM, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZW.

(84) Designated States (regional): ARIPO patent (GH, GM,

KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZW), Eurasian

patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European

patent (AT, BE, CH, CY, DE, DK, ES, FI, FR, GB, GR, IE,

IT, LU, MC, NL, PT, SE, TR), OAPI patent (BF, BI, CF,

CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD,

TG).Published:

— with international search report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: MODULAR MEMORY DEVICE

**WO 02/15191 A1**

(57) Abstract: A modular memory device (10) includes a support element (13), a memory unit comprising a three-dimensional memory array carried by the support element, a device interface unit carried by the support element and coupled with the memory unit, and an electrical connector (12) carried by the support element and coupled with the device interface unit (18). The memory array is well suited for use as a digital medium storage device for digital media such as digital text, digital music, digital image or images, and digital video. The device interface unit is not required in all cases.

WO 02/15191

PCT/US01/24245

## MODULAR MEMORY DEVICE

## BACKGROUND

The present invention relates to modular memory devices and that include non-volatile, solid-state memory arrays.

A variety of portable consumer products capture and store digital data in a non-volatile manner. Digital cameras and digital audio players are two examples of such products. The memory devices for this class of products are preferably modular devices that are small enough to be hand-held and easily transported by a user. Ideally, these storage devices should be removable and lightweight, and they should provide a multi-megabyte storage capacity and achieve a low actual sales price (ASP).

One prior-art approach to such memory devices is known as the flash memory card. Such cards fit into the palm of a user's hand, are lightweight, and provide storage capabilities that are matched to the needs of the portable device segment of the consumer market. However, flash memory cards do not adequately address the cost requirements of this market segment. The cost per megabyte as of June 2000 for flash memory cards, such as CompactFlash cards, is between \$2-4 at the forty megabyte level (ASP). Since most consumer applications in the portable device segment of the market require at least forty megabytes of non-volatile storage, flash memory cards represent a significant portion of the cost of the overall device.

Other memory cards built to address this market segment include the Multi-Media Card (MMC), that has a cost per megabyte as of June 2000 of between \$3-5 (ASP). All of these memory cards use conventional two-dimensional memory arrays.

## BRIEF SUMMARY

The preferred embodiments described below satisfy the size, weight, storage and cost requirements of consumer applications requiring non-volatile digital storage. These embodiments include a memory array and a memory

WO 02/15191

PCT/US01/24245

array controller carried by a support element, and an electrical connector carried by the support element and coupled with the memory array controller. The memory array is preferably, though not necessarily, a write-once, three-dimensional, field-programmable memory array. Such memory arrays provide the advantage of substantially reduced cost per bit. When a device interface unit is used, it is preferably highly integrated to minimize cost. By reducing cost of both the memory unit and the device interface unit, the overall price of the modular memory device is substantially reduced as compared with the prior art described above.

This section has been provided by way of general introduction, and it is not intended to limit the scope of the following claims.

#### BRIEF DESCRIPTION OF THE DRAWINGS

FIG. 1 is a perspective view of a modular memory device that incorporates a preferred embodiment of this invention.

FIG. 2 is a cross-sectional view of the memory device of FIG. 1.

FIGS. 3 and 4 are cross-sectional views of alternative embodiments of the memory device of FIG. 1.

FIG. 5 is a schematic view of a portion of a three-dimensional memory array.

FIG. 6 is a schematic diagram of a preferred embodiment of the device interface unit 18 of FIG. 2.

FIG. 7 is a block diagram of a modular memory device connected to a digital media storage system.

#### DETAILED DESCRIPTION OF THE PRESENTLY PREFERRED EMBODIMENTS

Turning now to the drawings, FIG. 1 shows an overall view of a modular memory device 10 that includes an electrical connector 12 at one end. The exterior surfaces of the memory device 10 are enclosed within a housing 13 as shown. The housing 13 protects the internal components of the device 10 and forms a compact, modular, handheld unit that is easily transported and easily inserted into and removed from a read/write device such as a camera or an

electronic book by a consumer. The connector 12 can take any suitable form, and in this example is arranged as a series of conductive pads spaced and arranged to mate with corresponding contacts of a mating connector (not shown). Of course, any suitable connector 12 can be used, and this invention is not limited to the edge connector shown in FIG. 1.

FIG. 2 is a cross-sectional view through the device 10 of FIG. 1. As shown in FIG. 2, the device 10 includes a support element that in this embodiment takes the form of a printed circuit board 14. The printed circuit board 14 may form one of the exterior surfaces of the device 10. The printed circuit board 14 carries a memory unit 16, a device interface unit 18, and the electrical connector 12.

The memory unit 16 preferably includes a three-dimensional memory array and an associated memory array controller. The preferred memory array includes a suitable number of memory cells arranged in a three-dimensional lattice above a substrate. The three-dimensional memories described in Johnson U.S. Patent No. 6,034,882, Knall U.S. patent application serial no. 09/560,626, and Johnson U.S. patent application serial no. 09/638,428 can be used for the memory array. All of these patent documents, which are assigned to the assignee of the present invention, are hereby incorporated by reference. The memory array controller is preferably formed on the same substrate over which the memory array is built, and the memory array controller includes address decoding circuitry, sensing circuitry for read operations, drive circuitry for write operations, and I/O interface circuitry including I/O amplifiers.

The device interface unit 18 in this embodiment is fabricated on a separate substrate and is electrically connected to the memory unit 16 and to the electrical connector 12 via the printed circuit board 14. In this embodiment, both the memory unit 16 and the device interface unit 18 are directly mounted to the printed circuit board. The device interface unit 18 includes all of the components needed to create the voltages, clock frequencies, and protocol logic that allow the memory device 10 to attach to a variety of consumer devices, all integrated into a single piece of silicon substrate. In one implementation, the device interface unit 18 comprises circuitry (using any suitable combination of hardware,

software, and firmware) to implement the task file, interrupt management, error reporting and configuration functions included in the protocol being used (e.g., a protocol such as the CompactFlash protocol).

FIG. 3 shows a modified form of the embodiment of FIG. 2. In the embodiment of FIG. 3 the device interface unit 18 and the memory unit 16 are packaged in conventional intermediate chip packages such as those known in the art as TSOP or TQFP packages. These packaged elements are then assembled onto the printed circuit board 14 in the conventional manner.

In the embodiment of FIG. 4, the three-dimensional memory array, the memory array controller and the device interface unit are fabricated on a single substrate 20, which is preferably directly mounted to the printed circuit board 14, without an intermediate package. The memory array controller and the device interface unit can be fabricated on a silicon substrate, under the three-dimensional memory array. This arrangement minimizes fabrication cost of the memory device. In this case, the memory array controller may not require I/O amplifiers as described above.

The embodiment of FIG. 4 is well-suited for applications such as those using the CompactFlash protocol. This embodiment can be implemented with either a two- or three-dimensional memory array of non-volatile memory cells.

In order to build a minimal-cost controller, the total number of signals required for interfacing the memory unit 16 to the desired memory card standard is determined. The number of power and ground connections required to keep the power system inside of the silicon chip stable enough to guarantee flawless operation under all operating conditions is then added to this list. This pin count information determines the smallest rectangle that accommodates the number of required connections. The dimensions of the rectangle are a function of one fourth the number of pins and the height and width of the pin driver circuitry. The following equations describe the resultant edge length:

$$\text{length} = \left( \frac{\text{number\_of\_pins}}{4} \right) \times \text{driver\_width} + 2 \times \text{driver\_height};$$

$$\text{die\_area} = \text{length}^2.$$

Once the length equation is minimized, the required *die\_area* is set. The area usable for creating the required logic functions and any required power or clocking circuitry needed to connect the memory unit 16 to the chosen system bus standard can then be determined by the following equation:

$$\text{usable\_area} = \left( \left( \frac{\text{number\_of\_pins}}{4} \right) \times \text{driver\_width} \right)^2.$$

A silicon process technology is then chosen that gives an appropriate logic density such that the number of required components divided by the component density equals the *usable\_area* calculation from the previous equation.

In the embodiments described above, memory cells are organized and built in three dimensions rather than two. There are several layers of memory cells, and the layers are vertically stacked above one another. The three dimensions are called "rows", "columns", and "layers". Typically, the rows and columns are generally parallel to the upper surface of an underlying substrate, and the layers are separated from one another along a direction perpendicular to the upper surface of the underlying substrate.

Some memory cells contain an element that protrudes either upwardly or downwardly, and have in the past been referred to as a "three dimensional memory cell". However these memory cells are arrayed in a conventional two-dimensional array. This is quite different from the three-dimensional embodiments described herein, which include a three-dimensional array of memory cells, with several layers of memory cells stacked vertically above one another.

A significant feature of these embodiments is that they explicitly decrease memory operating speed, in exchange for low cost, three-dimensional organization. These embodiments use very small switching devices, giving a small memory cell and a small total chip area. The small switching devices also give a small read current, which makes the read access time relatively slow. However, there are several important memory applications which can easily tolerate a slow access time, and which derive tremendous benefit from dramatically lower memory cost. Many of these low-speed applications may be

collected together under the name "digital media storage" and include the following: digital storage of still images such as photographs, digital storage of music and digital audio in general, digital books, digital storage of maps, sequences of images including digital video, and numerous other examples which will be readily apparent to those skilled in the art. Digital media storage applications can be considered as storage applications by means of which copyrightable material may be fixed in a tangible medium of expression. For such applications, re-writability of the storage medium may not be an asset, and in fact may even be undesirable. For example, it may be important to have an unambiguous and immutable record of the expressed material. Moreover, cost is generally lower for write-once than for rewritable memory devices.

FIG. 7 shows in block diagram form the memory device 10 described above in combination with a digital media storage device 30. The memory device 10 can take any of the forms described herein, and it preferably includes a 3-D array of write-once, field-programmable memory cells. As explained above, such a device provides the advantage of unusually low cost. The memory device 10 is formed as a modular, hand-held unit with an external connector as described above to allow a user to readily connect the memory device 10 to the digital media storage device 30 and to remove it. Further details regarding the structure of the memory device 10 are described in U.S. Patent Applications Serial Nos. 09/638,439 and 09/638,427, both filed on the same date as the present application, assigned to the assignee of the present invention, and hereby incorporated by reference in their entirety. In alternative embodiments, a multi-write 3-D array may be used, such as that described in the U.S. Patent Application Serial Nos. 09/639,702 and 09/639,577, both filed on the same date of this present application and assigned to the assignee of this invention.

The digital media storage device 30 can take any suitable form, and may for example be a digital camera, a digital audio playback device, or an electronic book. The storage device 30 performs two separate functions. First, the storage device 30 presents to the user the digital media stored in the memory device 10, as for example by showing still or moving images, playing audio files, or

displaying the pages of an electronic book. Second, the storage device 30 can be used to field program the memory device 10 with the desired digital media information. For this purpose, the digital media storage device 30 is connected to a source, and field programs digital media information from the source to the memory device 10. The digital media source can take any suitable form, and will often include another computer (not shown). For example, the source may provide digital media information to the storage device 30 via a network such as the Internet or via a system provided in a store such as a record store or a book store for downloading digital media into the memory device 10 provided by a consumer. The source of digital data may also include but is not limited to the output of a charge coupled device array (CCD) as in a digital camera or the output of a coder-decoder (CODEC) as in a music player-recorder. In some applications, the source may store the digital media information in the memory device 10 directly, rather than by way of the digital media storage device 30, and this is another example of field programmability. In general, the term "field programmable" is intended broadly to encompass writing into the memory device a file selected or chosen by a user at a time after fabrication of the memory device has been completed.

The memory array of the embodiments described herein includes a vertical stack of multiple layers of memory cells, and the memory cell may take any desired form; memory cells taught in Zhang US Patent 5,835,396, Johnson US Patent 6,034,882, and Knall US patent application Serial No. 09/560,626 may be taken as examples. However the preferred embodiments described herein have been designed to minimize cost, and the memory cells are therefore as small as possible.

To make the memory cells small, fine-pitch photolithography is used to pattern the geometric shapes of the memory cells. In particular, the wordlines and bitlines are preferably formed with a linewidth no larger than approximately 1 micron, and a line-to-line spacing no larger than about 1 micron. These values of F (the photolithographic featuresize) may be further reduced; it is more preferable that the linewidth and spacing be smaller than approximately 0.25 microns.

Figure 5 shows a schematic representation of one embodiment of a memory array of the type described above. Each of the memory cells MC1, MC2 is a two-terminal cell that includes a state storage element. In this embodiment, the memory cells MC1 are arranged at a first level, and the memory cells MC2 are arranged at a second level that is vertically stacked with respect to the first level. The terminals of the memory cells MC1, MC2 are disposed at the respective ends of the cell. In this connection, the term "terminal" is intended broadly, and a terminal may be embodied simply as a terminal portion of the cell, or as a separate layer of the cell.

Each of the terminals of each of the memory cells MC1, MC2 is in electrical contact with a respective conductor or wire. The conductors W1, W2 at the bottom of the memory cells MC1 in the view of Figure 1 are configured as wordlines, and the conductors B1, B2 connected to the upper terminals of the memory cells MC1 are configured as bitlines, which in this embodiment run substantially perpendicularly to the wordlines W1, W2. Thus, each of the memory cells MC1 bridges a selected one of the wordlines W1, W2 and a selected one of the bitlines B1, B2.

Similarly, the memory cells MC2 of the second layer are connected between selected ones of the bitlines B1, B2 and selected wordlines W3, W4. The wordlines W3, W4 in this embodiment are disposed on another level, vertically stacked above the level of the bitlines B1, B2.

The memory cell array of Figure 5 can be similar in basic geometry and materials to that described in Figures 6a through 6g of the above-identified Johnson patent.

For embodiments in which the basic cell size in plan view is 2F by 2F (such as taught by the above-identified Johnson and Knall patent documents), the pitch of the memory cell (the total width of 100 adjacent cells, divided by 100) is preferably no larger than about 0.50 microns (and generally no larger than 2 microns) in either the wordline or bitline direction, and the total area consumed by a memory cell is preferably no larger than approximately 0.25 square microns. The chip area consumed is then approximately  $\leq 0.25$  square millimeters per million bits on each layer of the vertical stack. Stating the same

WO 02/15191

PCT/US01/24245

result another way, the packing density is  $\geq 4$  million bits per square millimeter on each layer of the vertical stack.

Vertical stacking increases density and decreases chip area for a given size of a memory array; in a preferred embodiment having eight layers of memory cells vertically stacked above one another, the density is  $\geq 32$  million bits per square millimeter of chip area.

As fine-pitch lithography improves, the density of these memory cells improves as well. The following equation shows the packing density in bits per unit area, for a lithography generation whose featuresize is  $F$  and for a vertical stack of  $N$  layers of  $2F$  by  $2F$  cells:

$$\text{packing density} = N / (4F^2).$$

It should be noted that other, less densely packed, embodiments of the present invention can use memory cells that are larger than  $4F^2$  (see, e.g. the memory cell shown in Figure 6B of the above-identified Zhang patent). These larger memory cells result in a larger chip area and are thus less desirable.

A preferred embodiment for the device interface unit 18 is described in block diagram form in Figure 6. In this example, the CompactFlash Interface State Machine implements the task file, interrupt management, error reporting and configuration functions for the CompactFlash protocol, and the SmartMedia Interface State Machine implements these functions for the SmartMedia protocol. Both of these protocols are readily available to those skilled in the art. The device interface unit of Figure 6 can be fabricated on a silicon die measuring 2.68 millimeters by 2.68 millimeters, providing a total substrate area of 7.18 square millimeters. In one embodiment the modular memory device 10 described above is used to store digital media, such as any of the digital media described above.

In another embodiment, the device interface unit 18 is deleted from the device 10, and the memory array controller of the memory unit 16 is coupled directly to the connector 12 by the printed circuit board 14. In this case, the memory unit 16 may be controlled by a device interface unit on the host system.

While the foregoing embodiments are directed to a 3-D memory array, another cost-reducing embodiment is directed to using a one-time programmable

(OTP) array. For example, an electronically programmable read only memory (PROM) can be used. The cost differential between such an OTP memory and a conventional E<sup>2</sup>PROM and Flash memory can be substantial.

For either the 3-D one-time programmable, the 3-D multi-write, or the 2-D OTP, any of a variety of housing materials and configurations can be used. Suitable materials include metal, epoxy, ceramic, and plastic. Configurations can include those that are compatible with any standard modules that have in the past been used with Flash memory or E<sup>2</sup>PROM memory, or any future-developed standards. These include but are not limited to the CompactFlash, SmartMedia, MultiMediaCard, Secure Digital Music Initiative (SDMI), Sony MemoryStick and other standards. The configurations can include a separate or unintegrated device interface unit (i.e., the device interface unit can be integrated with the memory unit chip or not as a matter of design choice). The modules can be built around packaged dies, or each die can be mounted directly on a substrate that is in turn encapsulated within the housing. The substrate can be but is not limited to silicon, fiberglass or ceramic.

It should be apparent from the foregoing that an improved modular memory device has been described that can be fabricated at low cost, that is small and lightweight, and that provides the required capacity of non-volatile memory.

As used herein, the term "coupled with" is intended broadly to cover elements that are coupled directly as well as elements that are coupled indirectly. Thus, two elements that are coupled with one another may be coupled by means of an intervening, unnamed element.

The foregoing detailed description has described only a few of the many forms that this invention can take. For this reason, this detailed description is intended by way of illustration, and not by way of limitation. It is only the following claims, including all equivalents, that are intended to define the scope of this invention.

**CLAIMS**

1. A modular memory device comprising:

a support element;

a memory unit comprising a three-dimensional memory array

comprising a plurality of field-programmable memory cells, said memory unit

carried by the support element; and

an electrical connector carried by the support element and coupled

with the memory unit.

2. The invention of Claim 1 further comprising:

a device interface unit carried by the support element and coupled

with the memory unit and the electrical connector.

3. The invention of Claim 2 wherein the memory unit and the device

interface unit are fabricated on a single substrate, and wherein the substrate is

carried by the support element.

4. The invention of Claim 2 wherein the device interface unit fits within

a substrate area of no more than 8 mm<sup>2</sup>.

5. The invention of Claim 1, 2, 3 or 4 wherein the memory cells

memory comprise write-once memory cells.

6. The invention of Claim 1, 2, 3 or 4 wherein the memory cells are

arrayed on a substrate with an area density no less than 3x10<sup>7</sup> memory cells per

square millimeter of substrate.

7. The invention of Claim 5 wherein the memory array stores at least

one digital media file selected from the group consisting of digital text, digital

music, a digital image, a sequence of digital images, digital video, and

combinations thereof.

8. The invention of Claim 6 wherein the memory array stores at least

one digital media file selected from the group consisting of digital text, digital

music, a digital image, a sequence of digital images, and digital video, and combinations thereof.

9. A digital media memory device comprising:

a memory unit comprising a three-dimensional memory array comprising a plurality of stacked layers of field-programmable memory cells;

said memory cells characterized by respective digital states, said digital states storing a digital signal representing at least one digital media file selected from the group consisting of: a digital image, a sequence of digital images, a group of pages of digital text, digital music, a digital map, digital video, and combinations thereof.

10. The invention of Claim 9 wherein the memory cells are write-once memory cells.

11. The invention of Claim 9 wherein the memory cells are arrayed on a substrate with an area density no less than about  $3 \times 10^7$  memory cells per square millimeter of substrate.

12. The invention of Claim 9 further comprising:

a support element that carries the memory unit;

a device interface unit carried by the support element and coupled with the memory unit; and

an electrical connector carried by the support element and coupled with the device interface unit .

13. The invention of Claim 12 wherein the memory unit and the device interface unit are fabricated on a single substrate, and wherein the substrate is carried by the support element.

14. The invention of Claim 12 wherein the device interface unit fits within an area of no more than 8 mm<sup>2</sup>.

15. The invention of Claim 15 in combination with a digital media storage device operative to field program said digital media file in said memory cells.

16. The invention of Claim 15 wherein the storage device comprises a digital camera.

17. The invention of Claim 15 wherein the storage device comprises a digital audio playback device.

18. The invention of Claim 15 wherein the storage device comprises an electronic book.

19. A modular memory device comprising:

a support element;

a memory unit comprising a memory array fabricated on a substrate, said memory unit carried by the support element;

a device interface unit fabricated on the same substrate as the memory array and coupled with the memory unit; and

an electrical connector carried by the support element and coupled with the device interface unit.

20. The invention of Claim 19 wherein the device interface unit implements an interrupt management function for a selected protocol.

21. The invention of Claim 19 wherein the memory array comprises a three-dimensional array of memory cells.

22. The invention of Claim 19 wherein the memory array comprises a two-dimensional array of memory cells.

23. The invention of Claim 19 wherein the memory array comprises a plurality of write-once memory cells.

24. The invention of Claim 23 wherein the write-once memory cells are field programmable.

WO 02/15191

PCT/US01/24245

1/4

Fig. 1Fig. 2

WO 02/15191

PCT/US01/24245

2/4

WO 02/15191

PCT/US01/24245

3/4

Fig. 5

WO 02/15191

PCT/US01/24245

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                         | International application No.<br>PCT/US01/24245 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                                                 |

| IPC(7) : G11C/ 5/06, G11C/ 5/02<br>US CL : 365/72, 51<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                         |                                                 |

| <b>B. FIELDS SEARCHED</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                         |                                                 |

| Minimum documentation searched (classification system followed by classification symbols)<br>U.S. : 365/72, 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                         |                                                 |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched<br>N/A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                         |                                                 |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>EAST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                         |                                                 |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                         |                                                 |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                      | Relevant to claim No.                           |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | US 5,943,254 (BAKEMAN ET AL.) 24 AUGUST 1999 (24/08/1999) see entire document.                                                                                                                                                          | 1-3, 5, 9-10, 12-13,<br>19, 21, 23-24           |

| Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                         | 4, 6-8, 11, 14, 20, 22                          |

| A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | US 5,818,748 (BERTIN ET AL.) 06 OCTOBER 1998 (06/10/1998) see entire document.                                                                                                                                                          | 1-14 & 19-24                                    |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C. <input type="checkbox"/>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                         | See patent family annex.                        |

| <p>* Special categories of cited documents:</p> <p>"A" document defining the general state of the art which is not considered to be of particular relevance</p> <p>"E" earlier application or patent published on or after the international filing date</p> <p>"L" document which may throw doubt on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)</p> <p>"O" document referring to an oral disclosure, use, exhibition or other means</p> <p>"P" document published prior to the international filing date but later than the priority date claimed</p> <p>"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention</p> <p>"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone</p> <p>"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art</p> <p>"&amp;" document member of the same patent family</p> |                                                                                                                                                                                                                                         |                                                 |

| Date of the actual completion of the international search<br>18 September 2001 (18.09.2001)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Date of mailing of the international search report<br><i>16 NOV 2001</i>                                                                                                                                                                |                                                 |

| Name and mailing address of the ISA/US<br>Commissioner of Patents and Trademarks<br>Box PCT<br>Washington, D.C. 20231<br>Facsimile No. (703)305-3230                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Authorized officer<br><br>David Lam<br>Telephone No. (703) 306-9122<br><b>Deborah Parry-Leaper</b><br>Paralegal Specialist<br>Technology Center 2800 |                                                 |

Form PCT/ISA/210 (second sheet) (July 1998)

|                                                                                                                                   |                                     |                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>INTERNATIONAL SEARCH REPORT</b>                                                                                                |                                     | International application No.<br>PCT/US01/24245                                                                                                                                                                              |

| <b>Box I Observations where certain claims were found unsearchable (Continuation of Item 1 of first sheet)</b>                    |                                     |                                                                                                                                                                                                                              |

| This international report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons: |                                     |                                                                                                                                                                                                                              |

| 1.                                                                                                                                | <input type="checkbox"/>            | Claim Nos.:<br>because they relate to subject matter not required to be searched by this Authority, namely:                                                                                                                  |

| 2.                                                                                                                                | <input type="checkbox"/>            | Claim Nos.:<br>because they relate to parts of the international application that do not comply with the prescribed requirements to such an extent that no meaningful international search can be carried out, specifically: |

| 3.                                                                                                                                | <input checked="" type="checkbox"/> | Claim Nos.: 15-18<br>because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).                                                                                 |

| <b>Box II Observations where unity of invention is lacking (Continuation of Item 2 of first sheet)</b>                            |                                     |                                                                                                                                                                                                                              |

| This International Searching Authority found multiple inventions in this international application, as follows:                   |                                     |                                                                                                                                                                                                                              |

| 1.                                                                                                                                | <input type="checkbox"/>            | As all required additional search fees were timely paid by the applicant, this international search report covers all searchable claims.                                                                                     |

| 2.                                                                                                                                | <input type="checkbox"/>            | As all searchable claims could be searched without effort justifying an additional fee, this Authority did not invite payment of any additional fee.                                                                         |

| 3.                                                                                                                                | <input type="checkbox"/>            | As only some of the required additional search fees were timely paid by the applicant, this international search report covers only those claims for which fees were paid, specifically claims Nos.:                         |

| 4.                                                                                                                                | <input type="checkbox"/>            | No required additional search fees were timely paid by the applicant. Consequently, this international search report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.:             |

| <b>Remark on Protest</b>                                                                                                          |                                     | <input checked="" type="checkbox"/> The additional search fees were accompanied by the applicant's protest.<br><input type="checkbox"/> No protest accompanied the payment of additional search fees.                        |

Form PCT/ISA/210 (continuation of first sheet(1)) (July 1998)

---

フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,CH,CY,DE,DK,ES,FI,FR,GB,GR,IE,IT,LU,MC,NL,PT,SE,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NO,NZ,PL,PT,RO,RU,SD,SE,SG,SI,SK,SL,TJ,TM,TR,TT,TZ,UA,UG,UZ,VN,YU,ZA,ZW

(74)代理人 100074228

弁理士 今城 俊夫

(74)代理人 100084009

弁理士 小川 信夫

(74)代理人 100082821

弁理士 村社 厚夫

(74)代理人 100086771

弁理士 西島 孝喜

(74)代理人 100084663

弁理士 箱田 篤

(72)発明者 トリンガリ ジェイ ジェイムス

アメリカ合衆国 カリフォルニア州 94022 ロス アルトス ジョーダン アヴェニュー

105

(72)発明者 フームウォルド ピー マイケル

アメリカ合衆国 カリフォルニア州 94028 ポートラ ヴァリー ゴールデン オーク ド

ライヴ 190

(72)発明者 リー トーマス エイチ

アメリカ合衆国 カリフォルニア州 95014 クーパーティノ バブ ロード 939

(72)発明者 ジョンソン マーク ジー

アメリカ合衆国 カリフォルニア州 94022 ロス アルトス アービューロ ウエイ 12

5

(72)発明者 ボッシュ デレック ジェイ

アメリカ合衆国 カリフォルニア州 94043 マウンテン ビュー ノース レングストルフ

アヴェニュー 765 #104

F ターム(参考) 5B035 BA03 BB09 BC00 CA01 CA08 CA29